## NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

## **THESIS**

A RELIABILITY STUDY ON THE EFFECTS OF HTOL AND HIGH-CURRENT DENSITY STRESS TESTING ON COMMERCIAL-GRADE VERTICAL N-TYPE PD/GAN SCHOTTKY DIODES

by

Burnell A. Clemmer

September 2021

Thesis Advisor: Todd R. Weatherford Second Reader: Matthew A. Porter

Approved for public release. Distribution is unlimited.

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC, 20503.

| , ,                                                                                                                             |                                          |              |                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------|--------------------------------------------------------|

| 1. AGENCY USE ONLY (Leave blank)                                                                                                | 2. REPORT DATE<br>September 2021         | 3. REPORT TY | YPE AND DATES COVERED Master's thesis                  |

| 4. TITLE AND SUBTITLE A RELIABILITY STUDY ON THE HIGH-CURRENT DENSITY STORENTICAL N-TYPE PD/GAN S  6. AUTHOR(S) Burnell A. Clem | RESS TESTING ON COMMER<br>CHOTTKY DIODES | CCIAL-GRADE  | 5. FUNDING NUMBERS                                     |

| 7. PERFORMING ORGANIZA<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                  | ATION NAME(S) AND ADDR                   | ESS(ES)      | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER         |

| 9. SPONSORING / MONITOR<br>ADDRESS(ES)<br>N/A                                                                                   | ING AGENCY NAME(S) ANI                   | )            | 10. SPONSORING /<br>MONITORING AGENCY<br>REPORT NUMBER |

| 11. SUPPLEMENTARY NOTE official policy or position of the D                                                                     |                                          |              | he author and do not reflect the                       |

| 12a. DISTRIBUTION / AVAIL. Approved for public release. Dist                                                                    |                                          |              | 12b. DISTRIBUTION CODE<br>A                            |

#### 13. ABSTRACT (maximum 200 words)

Traditional silicon-based power electronics have approached their performance limits for high-power electronic applications. The U.S. Navy is actively pursuing the implementation of wide bandgap (WBG) semiconductor materials to realize reliable devices for use in high-power, high-current, and high-voltage applications. Gallium nitride (GaN) is a promising candidate for these applications due to its inherent material properties, and recent efforts to produce high quality bulk GaN have begun to enable the production of commercial-grade devices. However, much is still unknown regarding the reliability of GaN devices, especially Schottky diodes, which are often affected by issues involving barrier height inhomogeneity (BHI). First, a stress testing system capable of taking in-situ current-voltage-temperature (I-V-T) measurements while applying electrical stress was constructed. Next, a sample of commercial-grade vertical n-type palladium/gallium nitride (Pd/GaN) Schottky diodes were subjected to a series of step current and constant current stress tests. Current densities above 1.3 kA/cm^2 were achieved. Finally, the effects of electrical stress on material properties were observed through comparison of pre-, post-, and in-situ I-V-T data. The in-situ I-V-T measurements enabled degradation to be observed as a function of stress time. Results show that significant degradation to the material properties of the Schottky diodes occurs within the first few hours of stress testing.

| 14. SUBJECT TERMS gallium nitride, wide bandgap semiconductors, high-power electronics, high temperature operating life, barrier height inhomogeneity, reliability testing, high current density, barrier height inhomogeneity |                                                       |                                                      | 15. NUMBER OF<br>PAGES<br>155<br>16. PRICE CODE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified                                                                                                                                                                             | 18. SECURITY CLASSIFICATION OF THIS PAGE Unclassified | 19. SECURITY CLASSIFICATION OF ABSTRACT Unclassified | 20. LIMITATION OF<br>ABSTRACT<br>UU             |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release. Distribution is unlimited.

# A RELIABILITY STUDY ON THE EFFECTS OF HTOL AND HIGH-CURRENT DENSITY STRESS TESTING ON COMMERCIAL-GRADE VERTICAL N-TYPE PD/GAN SCHOTTKY DIODES

Burnell A. Clemmer Lieutenant, United States Navy BS, University of Virginia, 2013

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

#### NAVAL POSTGRADUATE SCHOOL September 2021

Approved by: Todd R. Weatherford

Advisor

Matthew A. Porter Second Reader

Douglas J. Fouts

Chair, Department of Electrical and Computer Engineering

#### **ABSTRACT**

Traditional silicon-based power electronics have approached their performance limits for high-power electronic applications. The U.S. Navy is actively pursuing the implementation of wide bandgap (WBG) semiconductor materials to realize reliable devices for use in high-power, high-current, and high-voltage applications. Gallium nitride (GaN) is a promising candidate for these applications due to its inherent material properties, and recent efforts to produce high quality bulk GaN have begun to enable the production of commercial-grade devices. However, much is still unknown regarding the reliability of GaN devices, especially Schottky diodes, which are often affected by issues involving barrier height inhomogeneity (BHI). First, a stress testing system capable of taking in-situ current-voltage-temperature (I-V-T) measurements while applying electrical stress was constructed. Next, a sample of commercial-grade vertical n-type palladium/gallium nitride (Pd/GaN) Schottky diodes were subjected to a series of step current and constant current stress tests. Current densities above 1.3 kA/cm<sup>2</sup> were achieved. Finally, the effects of electrical stress on material properties were observed through comparison of pre-, post-, and in-situ I-V-T data. The in-situ I-V-T measurements enabled degradation to be observed as a function of stress time. Results show that significant degradation to the material properties of the Schottky diodes occurs within the first few hours of stress testing.

## TABLE OF CONTENTS

| I.   | INT       | RODUCTION                                                | 1  |

|------|-----------|----------------------------------------------------------|----|

|      | A.        | MOTIVATION                                               | 1  |

|      | В.        | RELATED WORK                                             | 2  |

|      | <b>C.</b> | OBJECTIVE                                                | 3  |

|      | D.        | ORGANIZATION                                             | 4  |

| II.  | BAC       | KGROUND AND THEORY                                       | 5  |

|      | A.        | GaN SEMICONDUCTOR TECHNOLOGY                             | 5  |

|      |           | 1. GaN Material Properties                               | 5  |

|      |           | 2. GaN Device Structures                                 |    |

|      |           | 3. Bulk GaN Fabrication                                  | 8  |

|      | В.        | IDEAL THEORY OF SCHOTTKY DIODES                          | 9  |

|      |           | 1. Energy Band Theory                                    |    |

|      |           | 2. Electrostatic Characteristics                         |    |

|      |           | 3. Current Transport Process                             | 15 |

|      |           | 4. I-V and I-V-T Relationships                           | 17 |

|      | <b>C.</b> | NON-IDEAL THEORY OF SCHOTTKY DIODES                      | 20 |

|      |           | 1. Formation of the Schottky Barrier                     | 20 |

|      |           | 2. SBH Inhomogeneity and Potential Distribution          | 22 |

|      |           | 3. Electron Transport                                    | 25 |

|      | D.        | GaN RELIABILITY RESEARCH                                 | 30 |

|      |           | 1. Reliability Research Involving GaN Schottky Diodes    | 31 |

|      |           | 2. HTOL Stress Testing Involving Commercial GaN Devices. | 32 |

| III. | EXP       | ERIMENTAL STRESS TEST SYSTEM DESIGN                      | 33 |

|      | A.        | HTOL SYSTEM OVERVIEW                                     | 33 |

|      | В.        | HTOL SYSTEM CRITICAL DESIGN ASPECTS                      | 35 |

|      |           | 1. Custom Semiconductor Stress Testing Modules           | 36 |

|      |           | 2. Autonomous Control                                    |    |

|      | С.        | HTOL SYSTEM TEMPERATURE CONTROL AND PERFORMANCE          | 41 |

| IV.  | PRE       | -STRESS CHARACTERIZATION AND EXPERIMENTAL                |    |

|      | ME        | THODOLOGY                                                | 45 |

|      | A.        | COMMERCIAL GAN SCHOTTKY DIODE OVERVIEW                   | 45 |

|      | В.        | INITIAL CHARACTERIZATION AND CLASSIFICATION              |    |

|      |           | PROCESS                                                  | 46 |

|     |           | 1.     | Device Classification                       | 47 |

|-----|-----------|--------|---------------------------------------------|----|

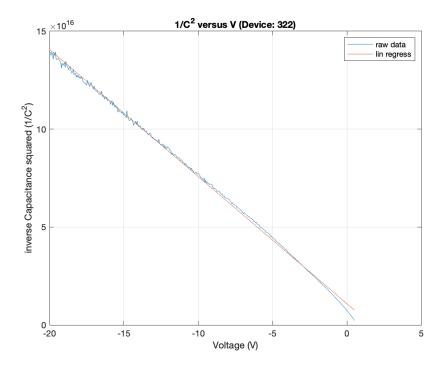

|     |           | 2.     | Impurity Concentrations                     | 49 |

|     | <b>C.</b> | PRE    | E-STRESS DEVICE MEASUREMENTS                | 51 |

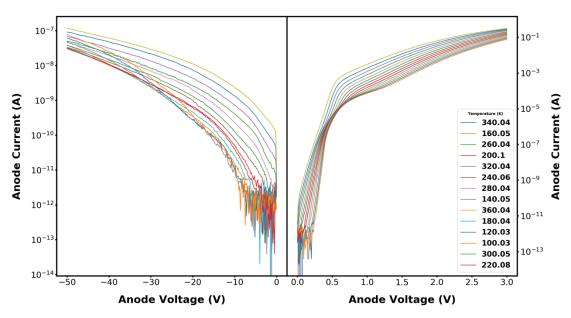

|     |           | 1.     | Pre-stress I-V-T Measurements               | 51 |

|     |           | 2.     | Pre-stress Barrier Height Measurements      | 53 |

|     |           | 3.     | Pre-stress Forward Resistance Measurements  |    |

|     | D.        | ELF    | ECTRICAL STRESS TEST METHODS                | 57 |

|     |           | 1.     | Preliminary Stress tests                    | 57 |

|     |           | 2.     | Formal Stress tests                         |    |

| V.  | IN-S      | SITU R | ESULTS AND POST-STRESS CHARACTERIZATION     | 59 |

|     | A.        | STE    | CP-CURRENT STRESS TEST DATA                 | 59 |

|     |           | 1.     | Reverse Leakage Current                     | 59 |

|     |           | 2.     | Barrier Height                              | 61 |

|     |           | 3.     | Forward Resistance                          | 63 |

|     |           | 4.     | Inhomogeneity Spread                        | 64 |

|     | В.        | CO     | NSTANT CURRENT STRESS TEST DATA: 2.1 A      | 66 |

|     |           | 1.     | Reverse Leakage Current                     | 67 |

|     |           | 2.     | Barrier Height                              | 68 |

|     |           | 3.     | Forward Resistance                          | 70 |

|     |           | 4.     | Inhomogeneity Spread                        | 71 |

|     | <b>C.</b> | CO     | NSTANT CURRENT STRESS TEST DATA: 2.2 A      | 73 |

|     |           | 1.     | Reverse Leakage Current                     | 73 |

|     |           | 2.     | Barrier Height                              |    |

|     |           | 3.     | Forward Resistance                          |    |

|     |           | 4.     | Inhomogeneity Spread                        | 78 |

|     | D.        | POS    | ST-STRESS DEVICE MEASUREMENTS               |    |

|     |           | 1.     | Post-stress I-V-T Measurements              | 80 |

|     |           | 2.     | Post-stress Barrier Height Measurements     |    |

|     |           | 3.     | Post-stress Forward Resistance Measurements |    |

| VI. | CON       | NCLUS  | SIONS AND FUTURE WORK                       | 87 |

|     | A.        | CO     | NCLUSIONS                                   | 87 |

|     | R         | THE    | THE WORK                                    | QQ |

| APPENDIX A. HTOL SYSTEM ADDITIONAL TEC CONVERGENCE CURVES9                  | )1         |

|-----------------------------------------------------------------------------|------------|

| APPENDIX B. COMPLETE TABLE OF CHARACTERIZED DEVICES9                        | )5         |

| APPENDIX C. INITIAL CHARACTERIZATION AND CLASSIFICATION I-V PLOTS9          | <b>)</b> 7 |

| APPENDIX D. PRE-STRESS I-V-T PLOTS10                                        | )3         |

| APPENDIX E. PRE-STRESS BARRIER HEIGHT MEASUREMENTS10                        | )7         |

| APPENDIX F. PRE-STRESS FORWARD RESISTANCE VERSUS TEMPERATURE MEASUREMENTS11 | 1          |

| APPENDIX G. POST-STRESS I-V-T PLOTS11                                       | l <b>5</b> |

| APPENDIX H. POST-STRESS BARRIER HEIGHT MEASUREMENTS11                       | 9          |

| APPENDIX I. POST-STRESS FORWARD RESISTANCE MEASUREMENTS                     | 23         |

| LIST OF REFERENCES12                                                        | 27         |

| INITIAL DISTRIBUTION LIST13                                                 | 31         |

## LIST OF FIGURES

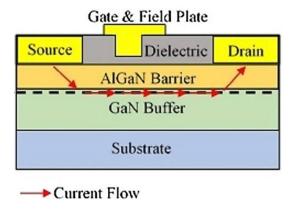

| Figure 1.  | Generic cross-section schematic of Al/GaN/GaN HEMT structure.  Source: [5]                                            | 7  |

|------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Schematic cross-sections of vertical Schottky (top) and PN (bottom) diodes. Source: [7].                              | 8  |

| Figure 3.  | Energy band diagram for an ideal Schottky contact between a metal and an n-type semiconductor. Source: [12].          | 10 |

| Figure 4.  | Response of the (n-type) MS contact to an applied DC bias. Source: [12]                                               | 12 |

| Figure 5.  | Electrostatic variables in an MS ( <i>n</i> -type) diode under equilibrium conditions. Source: [12].                  | 14 |

| Figure 6.  | Five observed current transport processes for a <i>n</i> -type Schottky diode. Source: [13]                           | 15 |

| Figure 7.  | Negligible and dominant current components in forward biased.  Source: [12]                                           | 16 |

| Figure 8.  | Theoretical and experimental semi-logarithmic I-V plot for an example <i>n</i> -type GaN Schottky diode. Source: [4]. | 18 |

| Figure 9.  | Richardson plot for a <i>n</i> -type GaN Schottky diode. Source: [4]                                                  | 19 |

| Figure 10. | Energy Band diagram at a MS interface. Source: [14].                                                                  | 21 |

| Figure 11. | Example geometries used for potential distribution analysis. Source: [15]                                             | 23 |

| Figure 12. | The effects of radius of low SBH patch on potential pinch-off. Source: [15]                                           | 24 |

| Figure 13. | Potential distribution surrounding a narrow low SBH strip. Source: [15]                                               | 25 |

| Figure 14. | I-V traces of Si Schottky barrier at varying temperatures. Source: [15]                                               | 27 |

| Figure 15. | Half-Gaussian distribution example.                                                                                   | 28 |

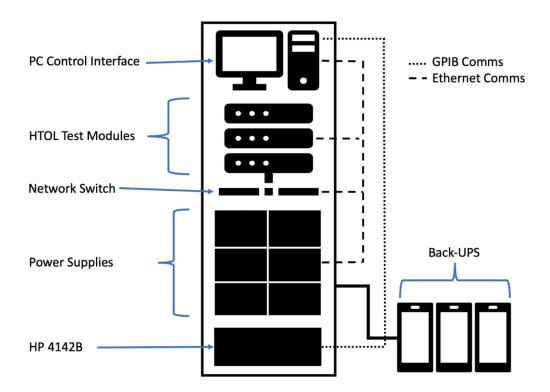

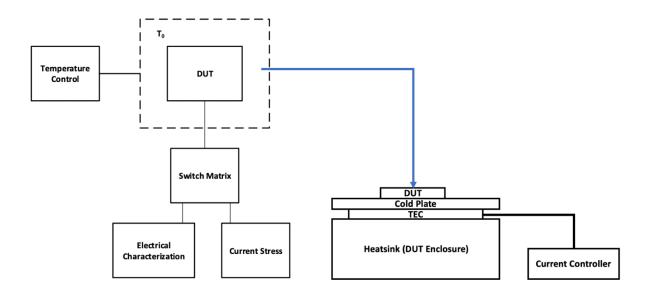

| Figure 16. | Block diagram of HTOL system with instrument control and communication paths.                                         | 34 |

| Figure 17. | Image of constructed HTOL system with two stress test modules         | 35 |

|------------|-----------------------------------------------------------------------|----|

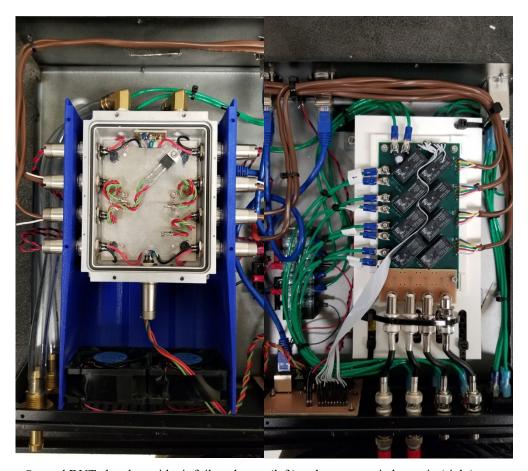

| Figure 18. | Image of an opened HTOL stress test module                            | 37 |

| Figure 19. | Close-up image of HTOL stress test module components                  | 38 |

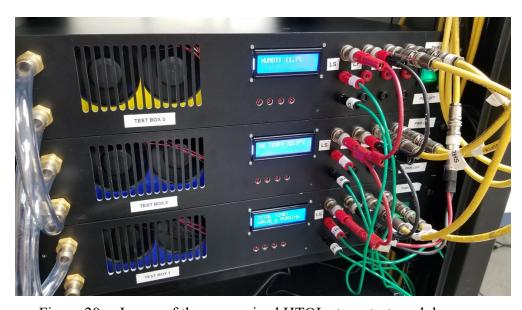

| Figure 20. | Image of three energized HTOL stress test modules                     | 39 |

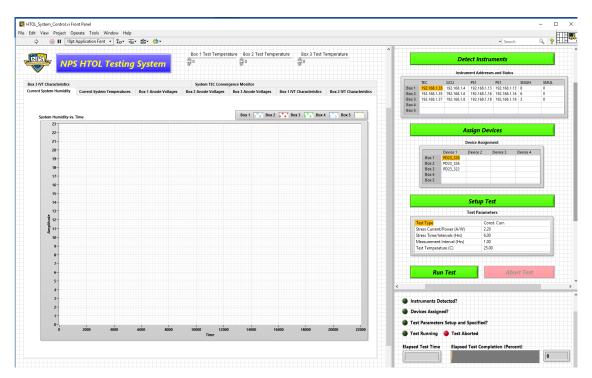

| Figure 21. | Screenshot of HTOL testing system control front panel in LabVIEW      | 40 |

| Figure 22. | Block diagram of HTOL system control.                                 | 42 |

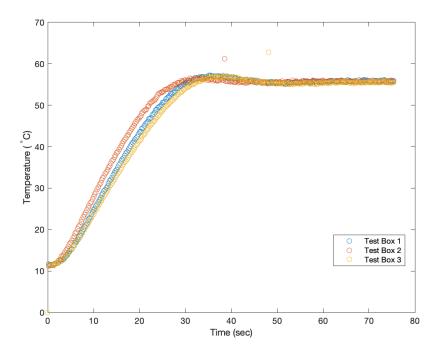

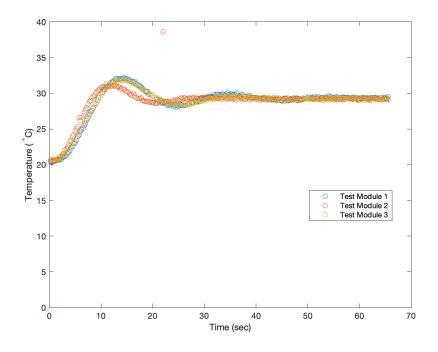

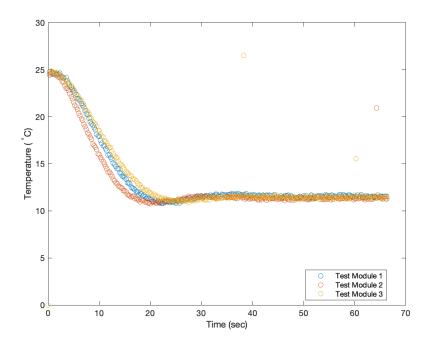

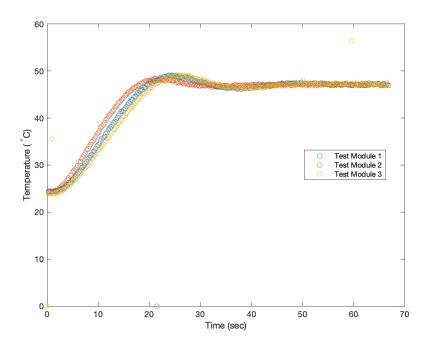

| Figure 23. | HTOL system TEC convergence from 10 °C to 60 °C.                      | 43 |

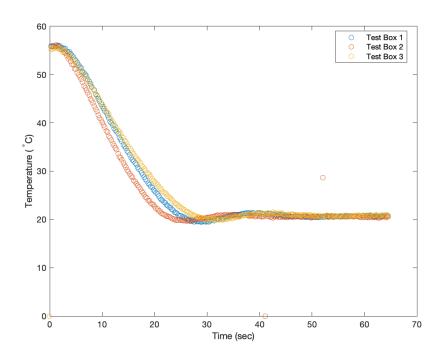

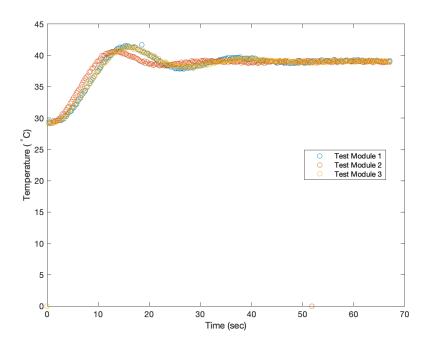

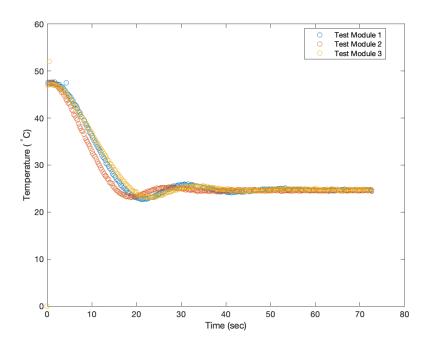

| Figure 24. | HTOL system TEC convergence from 60 °C to 20 °C.                      | 43 |

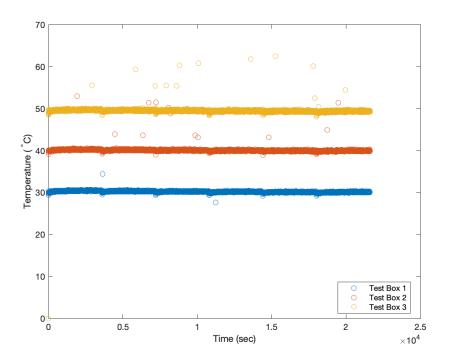

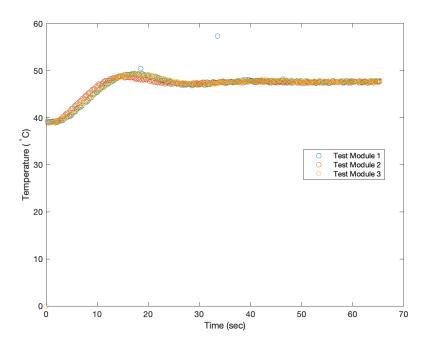

| Figure 25. | HTOL testing system temperature stability plot                        | 44 |

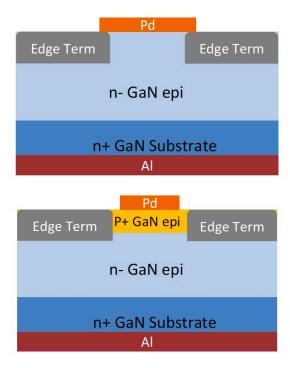

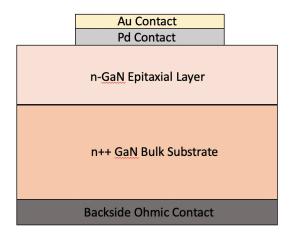

| Figure 26. | Commercial vertical <i>n</i> -type Pd/GaN Schottky diode architecture | 45 |

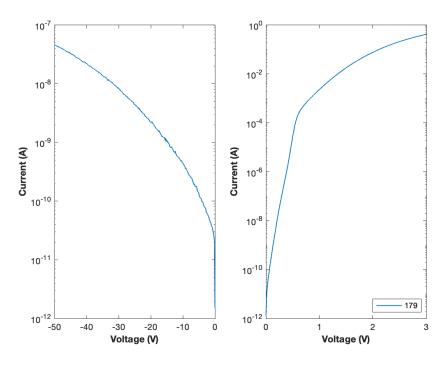

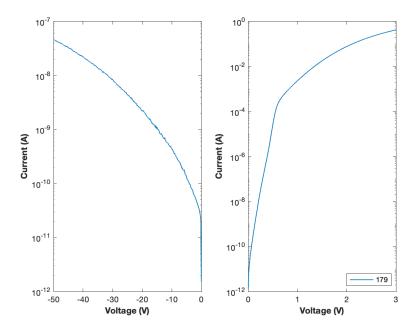

| Figure 27. | Device 179 I-V plot at room temperature, classified as a single diode | 48 |

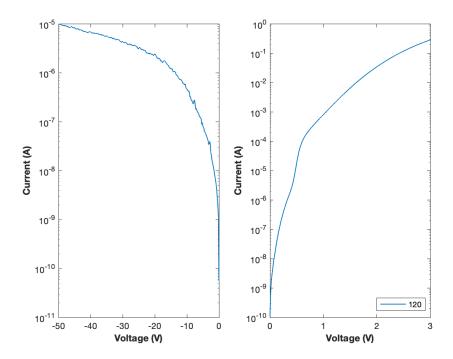

| Figure 28. | Device 120 I-V plot at room temperature, classified as a double diode | 49 |

| Figure 29. | Device 322 C-V plot.                                                  | 50 |

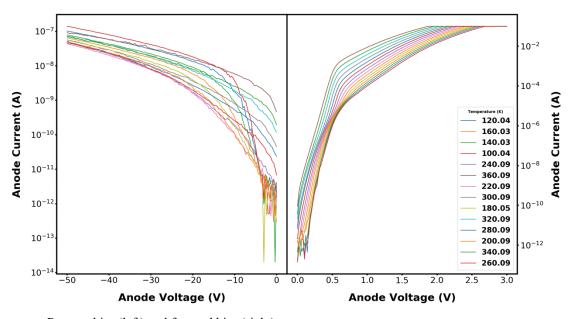

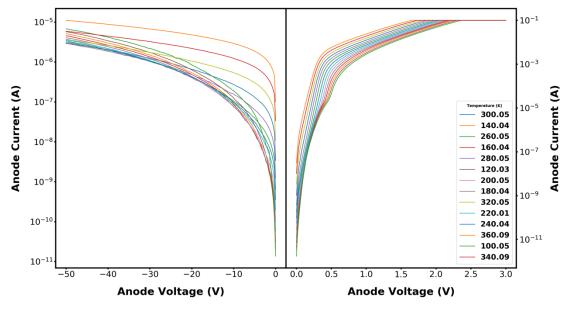

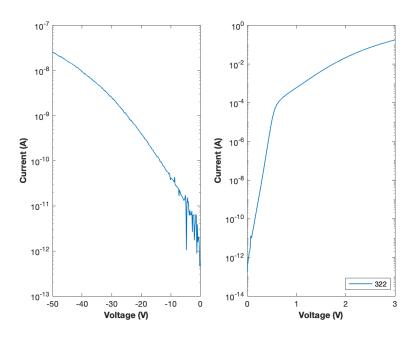

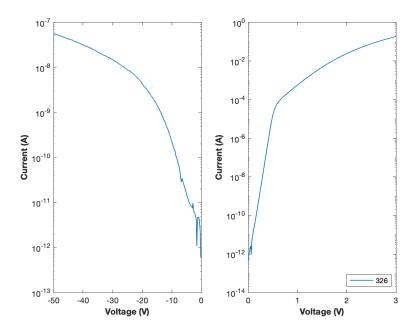

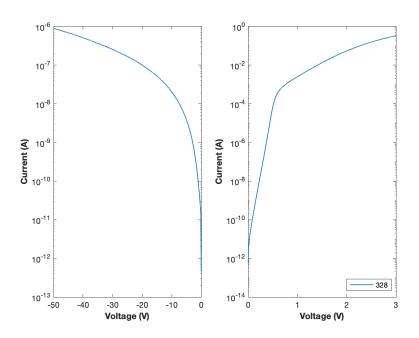

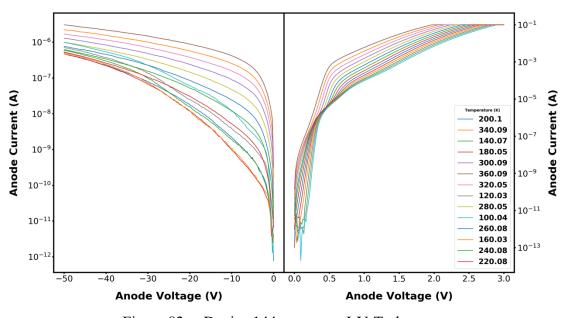

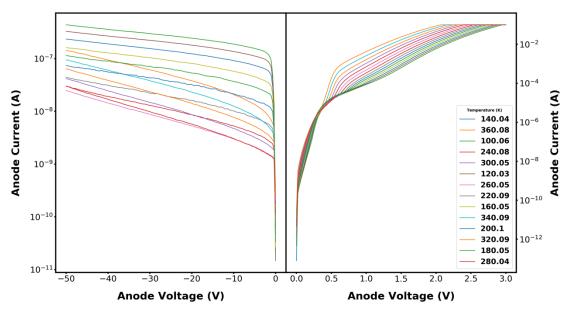

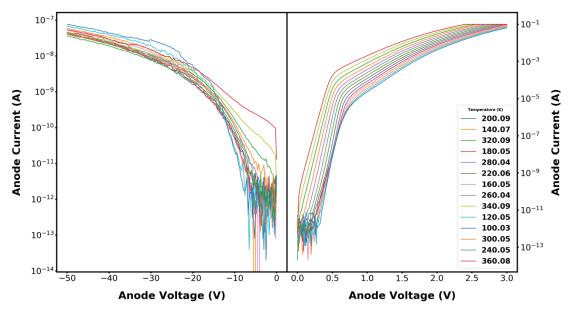

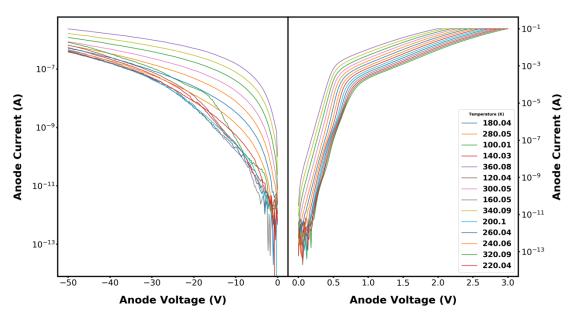

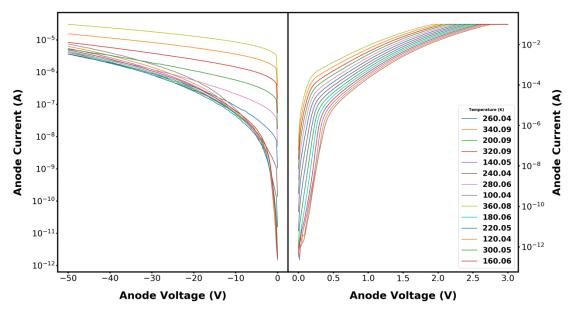

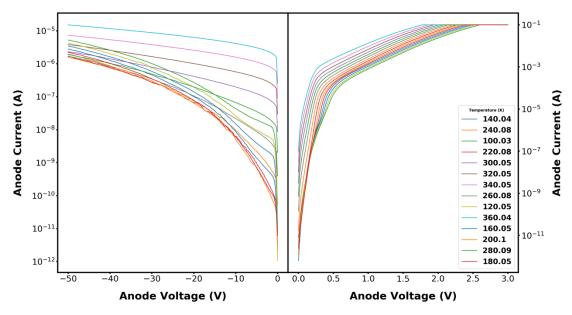

| Figure 30. | Device 179 (SD) pre-stress I-V-T plot                                 | 52 |

| Figure 31. | Device 120 (DD) pre-stress I-V-T plot.                                | 53 |

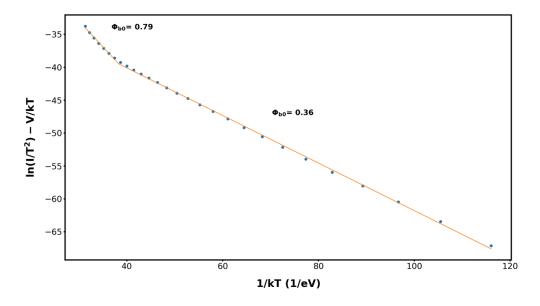

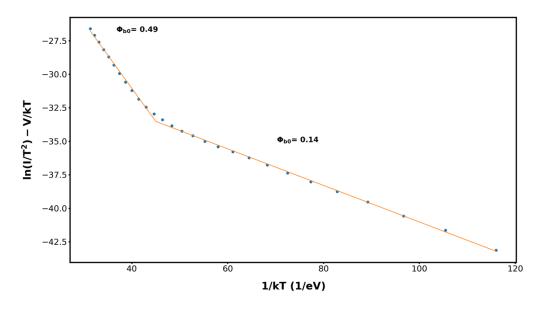

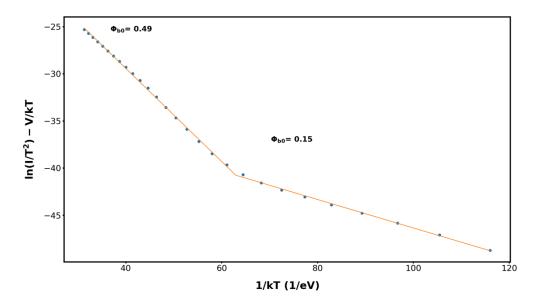

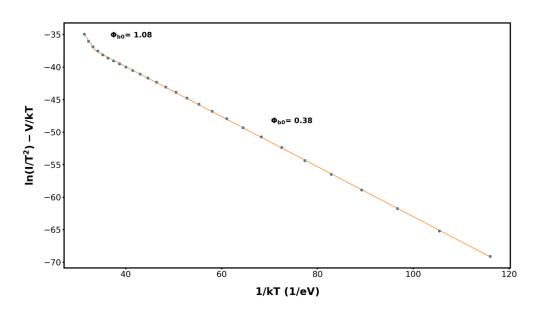

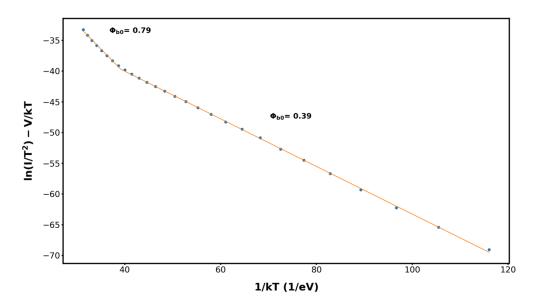

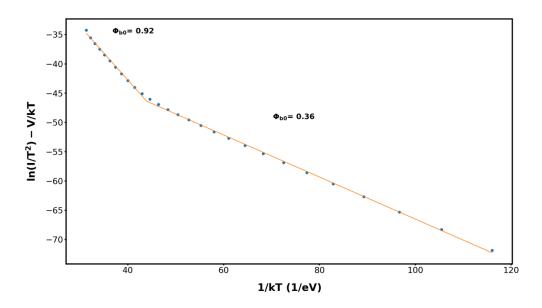

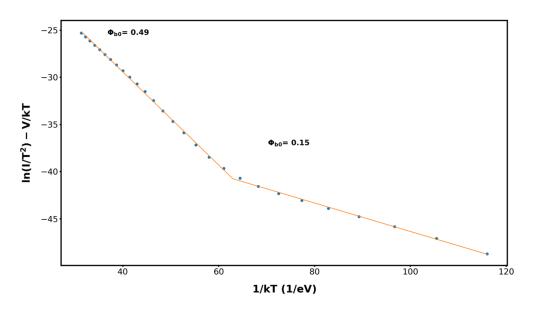

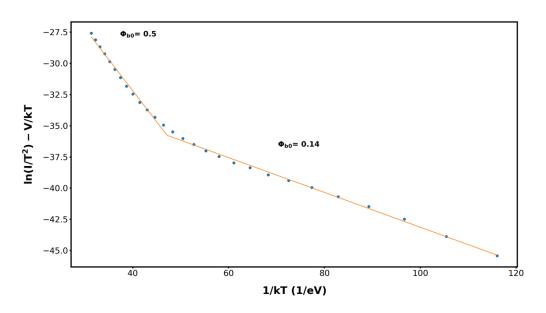

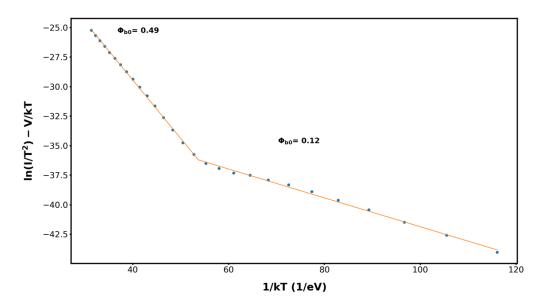

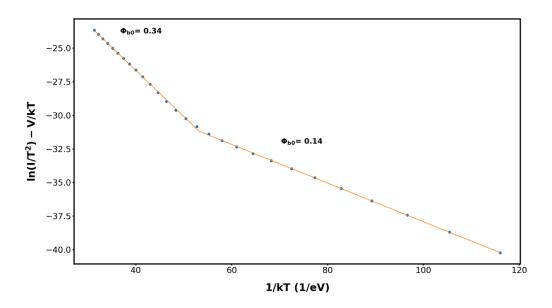

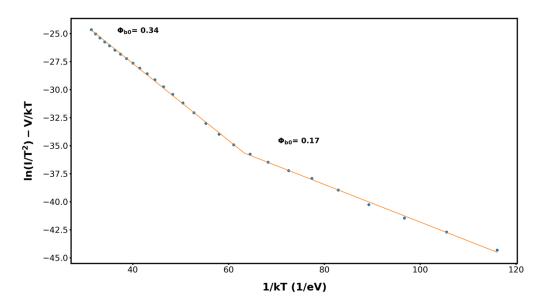

| Figure 32. | Device 179 (SD) pre-stress Richardson plot                            | 54 |

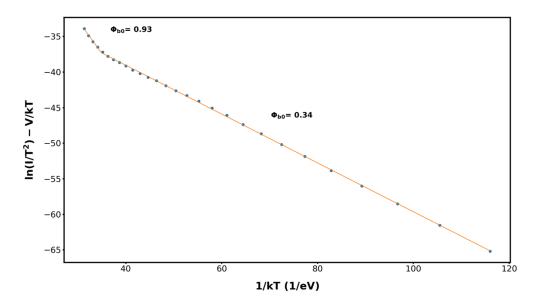

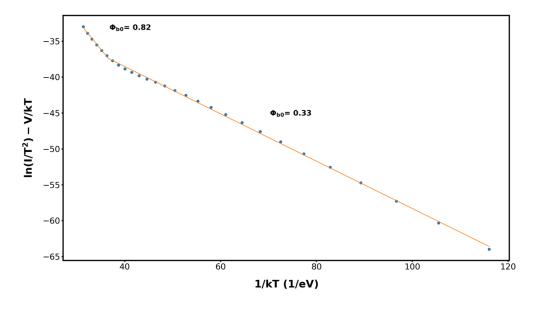

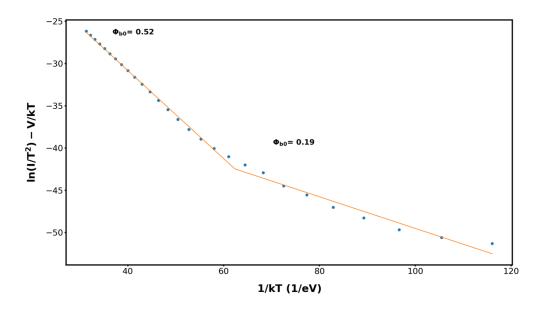

| Figure 33. | Device 120 (DD) pre-stress Richardson plot                            | 55 |

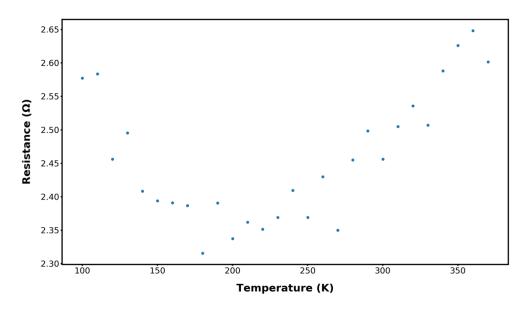

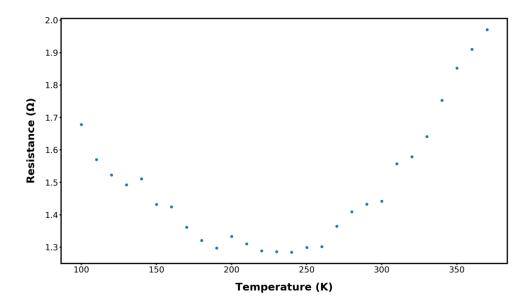

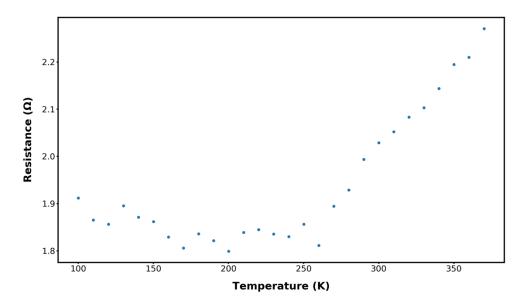

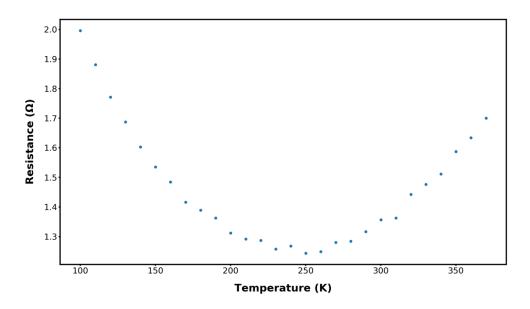

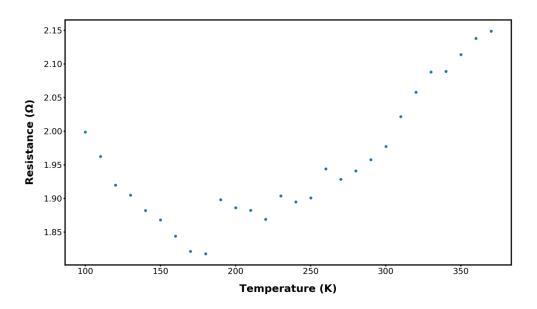

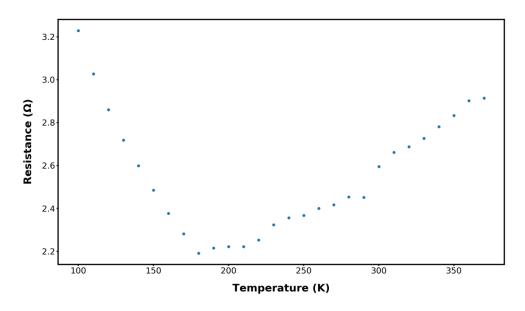

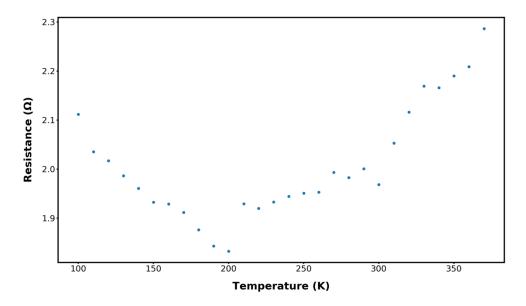

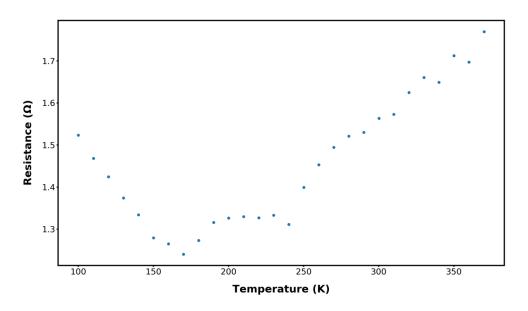

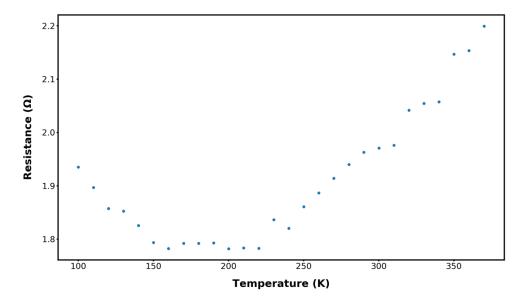

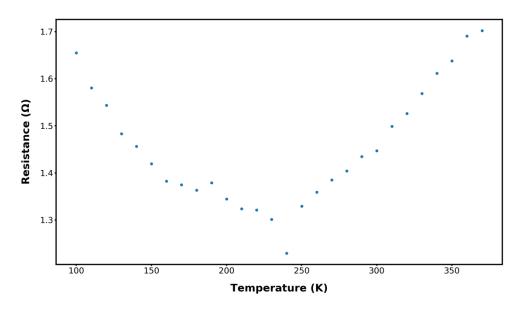

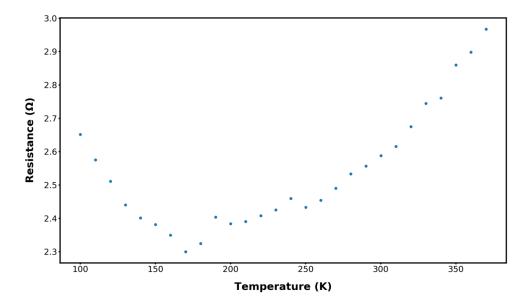

| Figure 34. | Device 179 (SD) pre-stress R <sub>on</sub> versus temperature plot    | 56 |

| Figure 35. | Device 120 (DD) pre-stress R <sub>on</sub> versus temperature plot    | 56 |

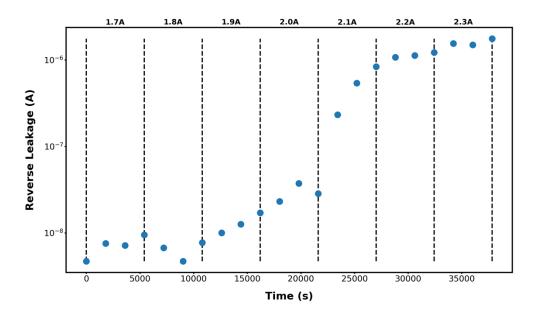

| Figure 36. | Device 143 (SD) I <sub>rev</sub> versus stress-time plot.             | 60 |

| Figure 37. | Device 165 (DD) I <sub>rev</sub> versus stress-time plot              | 61 |

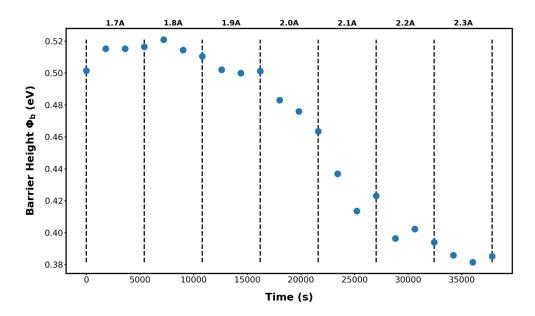

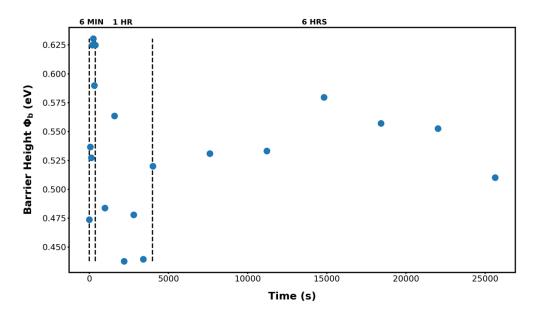

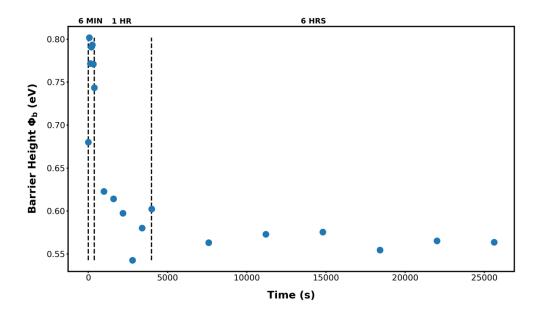

| Figure 38. | Device 143 (SD) Φ <sub>b</sub> versus stress-time plot                | 62 |

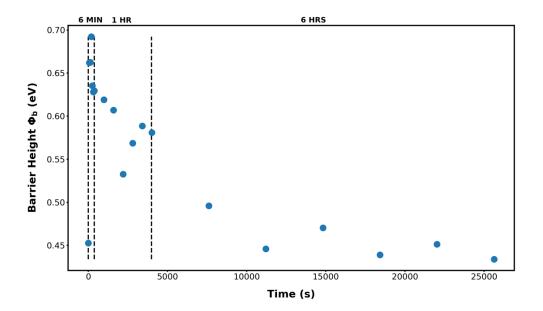

| Figure 39. | Device 165 (DD) Φ <sub>b</sub> versus stress-time plot                | 62 |

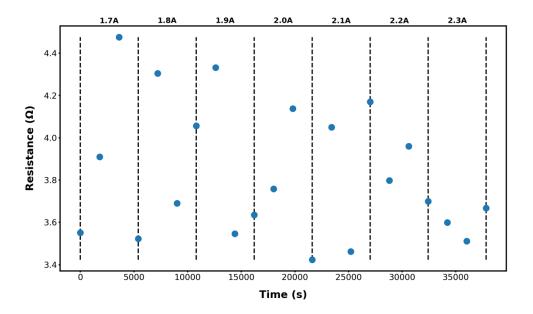

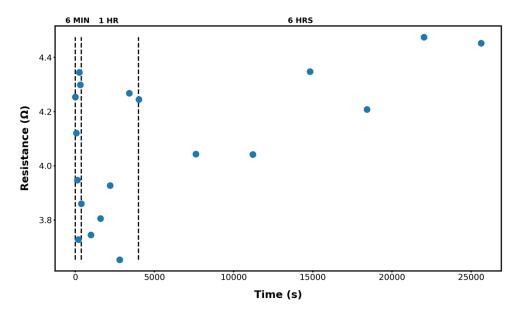

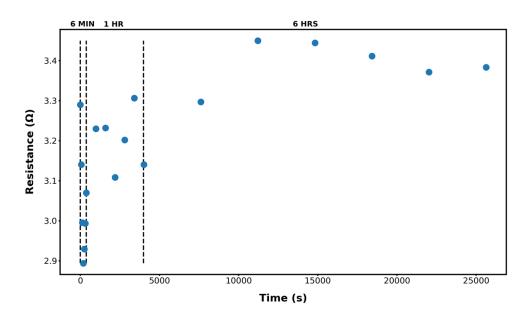

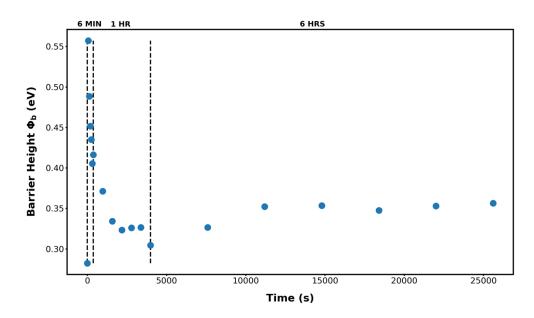

| Figure 40. | Device 143 (SD) R <sub>on</sub> versus stress-time plot  | 63 |

|------------|----------------------------------------------------------|----|

| Figure 41. | Device 165 (DD) R <sub>on</sub> versus stress-time plot. | 64 |

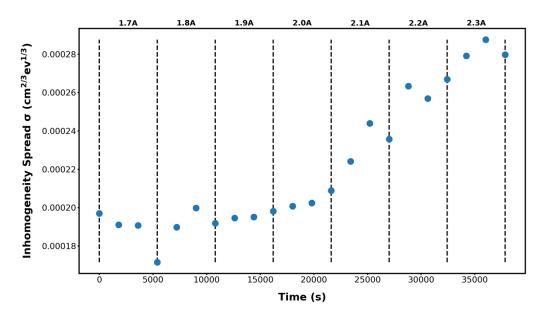

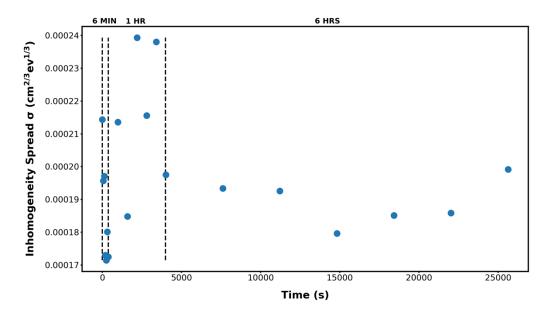

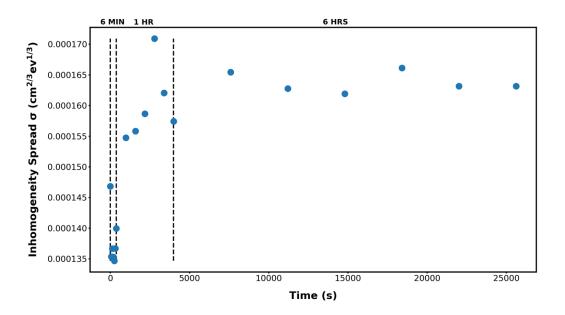

| Figure 42. | Device 143 (SD) σ versus stress-time plot                | 65 |

| Figure 43. | Device 165 (DD) σ versus stress-time plot                | 66 |

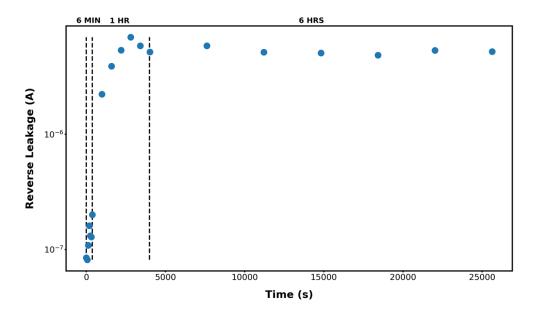

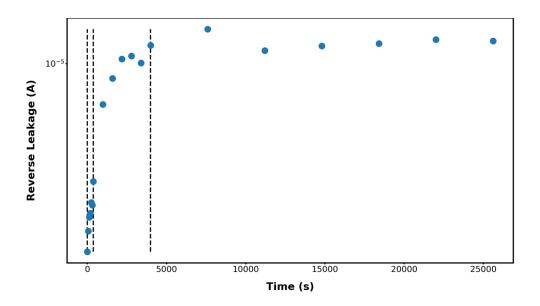

| Figure 44. | Device 179 (SD) I <sub>rev</sub> versus stress-time plot | 67 |

| Figure 45. | Device 19 (DD) I <sub>rev</sub> versus stress-time plot  | 68 |

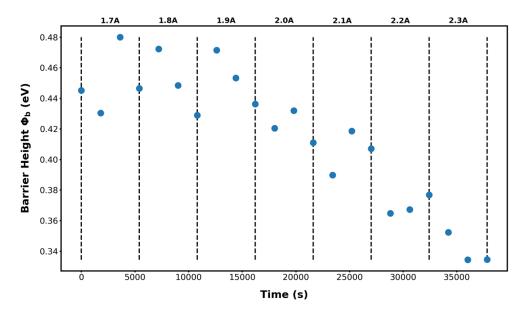

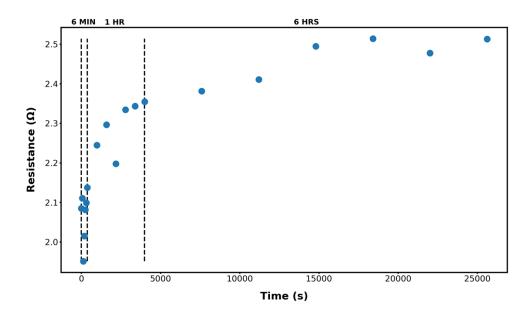

| Figure 46. | Device 179 (SD) Φ <sub>b</sub> versus stress-time plot   | 69 |

| Figure 47. | Device 19 (DD) Φ <sub>b</sub> versus stress-time plot    | 69 |

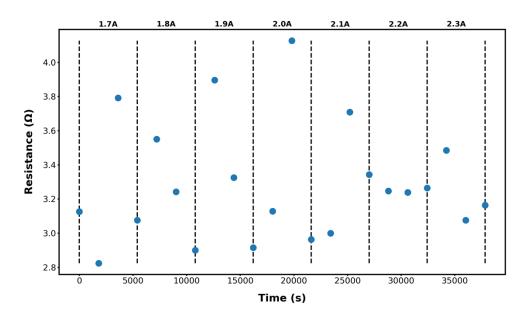

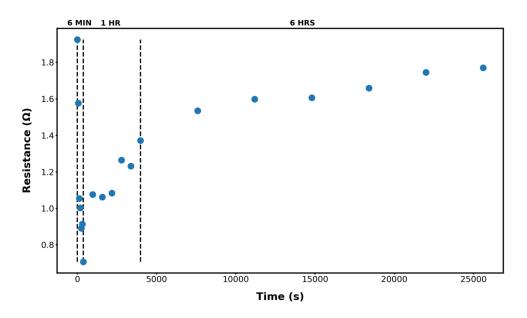

| Figure 48. | Device 179 (SD) R <sub>on</sub> versus stress-time plot  | 70 |

| Figure 49. | Device 19 (DD) R <sub>on</sub> versus stress-time plot   | 71 |

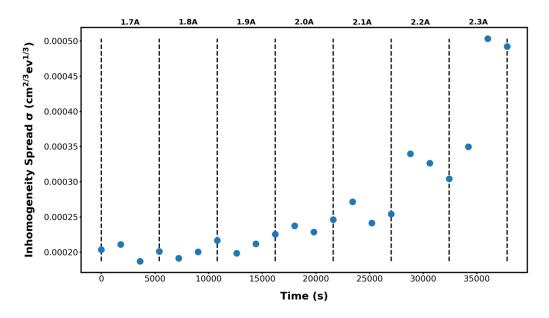

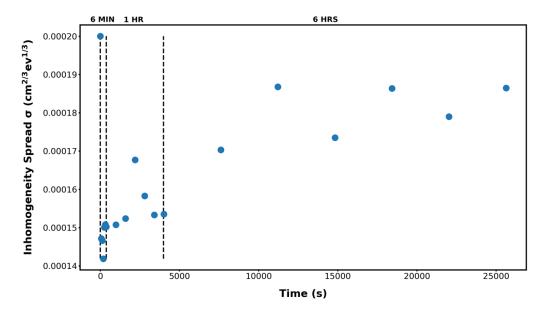

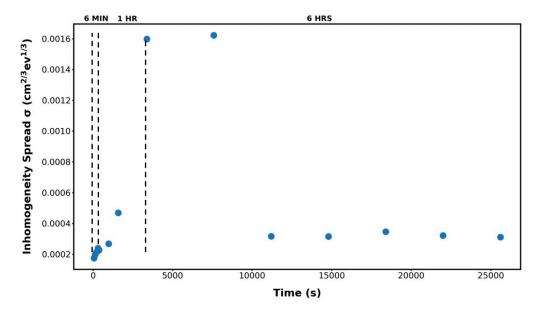

| Figure 50. | Device 179 (SD) σ versus stress-time plot                | 72 |

| Figure 51. | Device 19 (DD) σ versus stress-time plot                 | 72 |

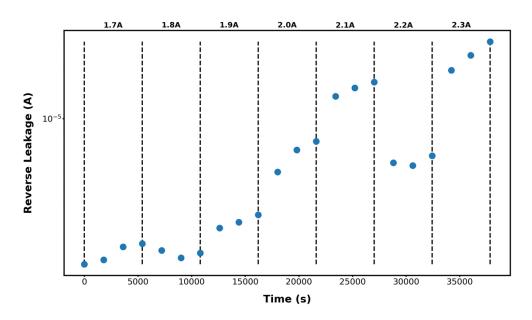

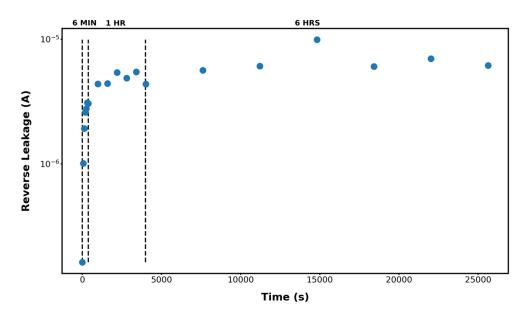

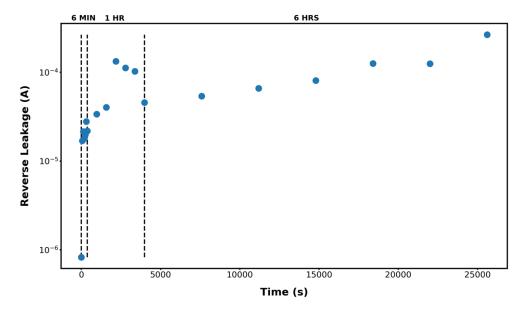

| Figure 52. | Device 328 (SD) I <sub>rev</sub> versus stress-time plot | 74 |

| Figure 53. | Device 178 (DD) I <sub>rev</sub> versus stress-time plot | 74 |

| Figure 54. | Device 328 (SD) Φ <sub>b</sub> versus stress-time plot   | 75 |

| Figure 55. | Device 178 (DD) Φ <sub>b</sub> versus stress-time plot   | 76 |

| Figure 56. | Device 328 (SD) R <sub>on</sub> versus stress-time plot  | 77 |

| Figure 57. | Device 144 (DD) R <sub>on</sub> versus stress-time plot  | 77 |

| Figure 58. | Device 328 (SD) σ versus stress-time plot                | 78 |

| Figure 59. | Device 178 (DD) σ versus stress-time plot                | 79 |

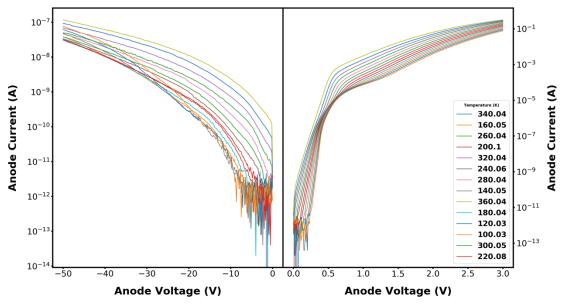

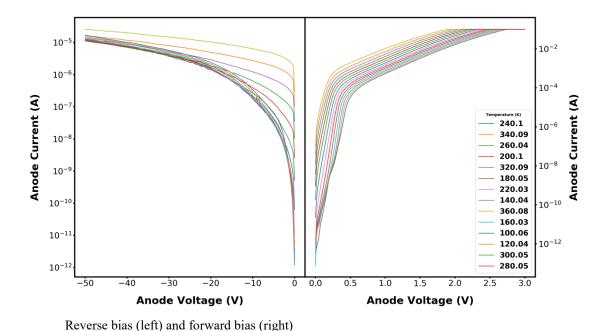

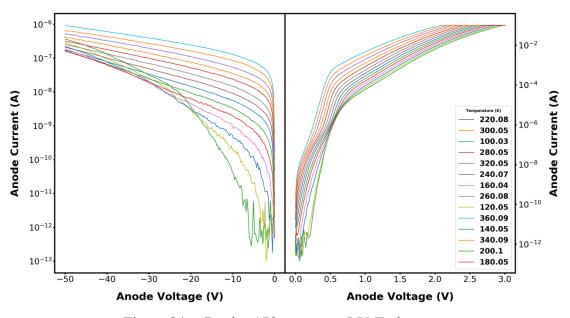

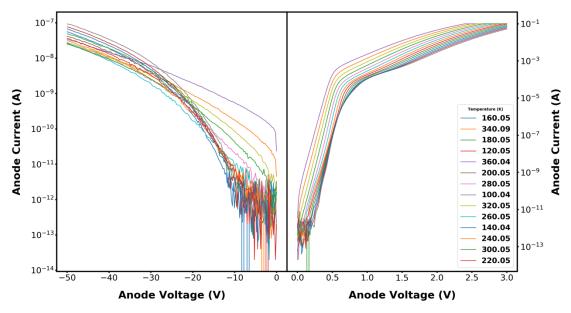

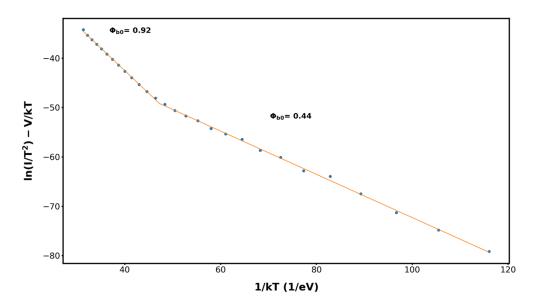

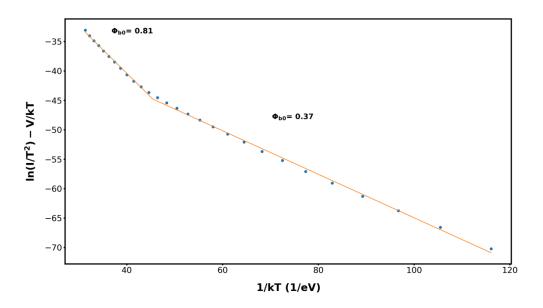

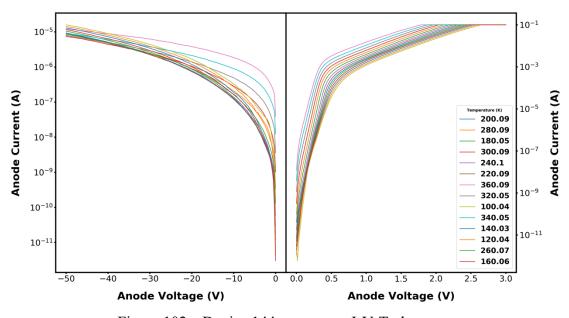

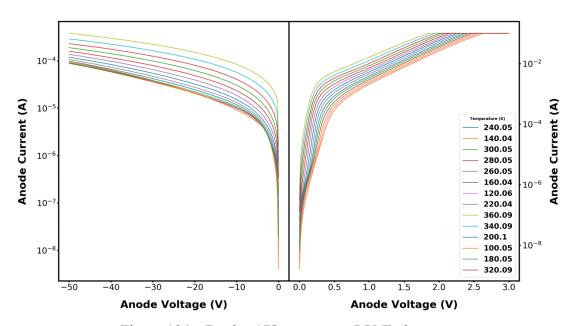

| Figure 60. | Device 179 (SD) post-stress I-V-T plot                   | 80 |

| Figure 61. | Device 120 (DD) post-stress I-V-T plot                   | 81 |

| Figure 62. | Device 179 (SD) post-stress Richardson plot              | 82 |

| Figure 63. | Device 120 (DD) post-stress Richardson plot              | 83 |

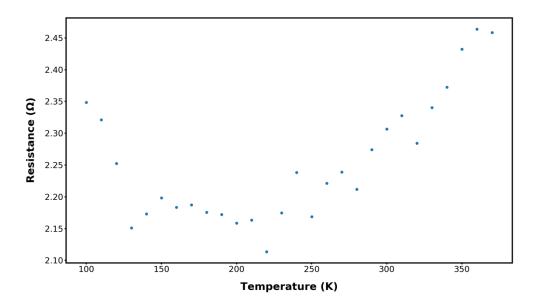

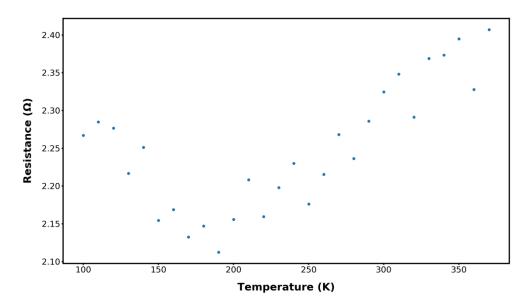

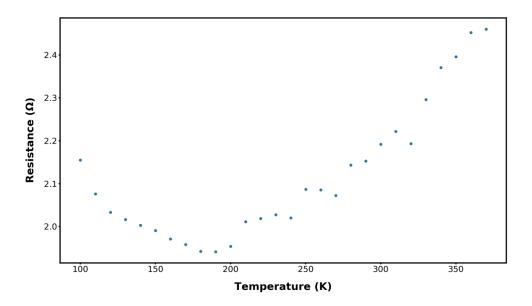

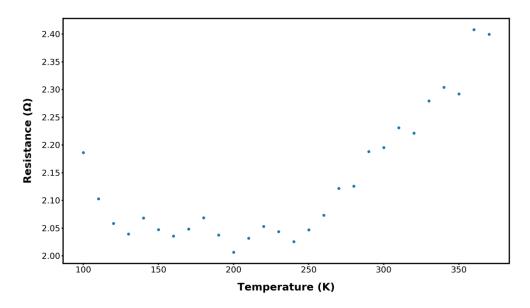

| Figure 64. | Device 179 (SD) post-stress R <sub>on</sub> versus temperature plot | 84  |

|------------|---------------------------------------------------------------------|-----|

| Figure 65. | Device 120 (DD) post-stress R <sub>on</sub> versus temperature plot | 85  |

| Figure 66. | HTOL system TEC convergence from 20 °C to 30 °C.                    | 91  |

| Figure 67. | HTOL system TEC convergence from 30 °C to 40 °C.                    | 92  |

| Figure 68. | HTOL system TEC convergence from 40 °C to 50 °C.                    | 92  |

| Figure 69. | HTOL system TEC convergence from 50 °C to 25 °C.                    | 93  |

| Figure 70. | HTOL system TEC convergence from 25 °C to 10 °C.                    | 93  |

| Figure 71. | HTOL system TEC convergence from 25 °C to 50 °C.                    | 94  |

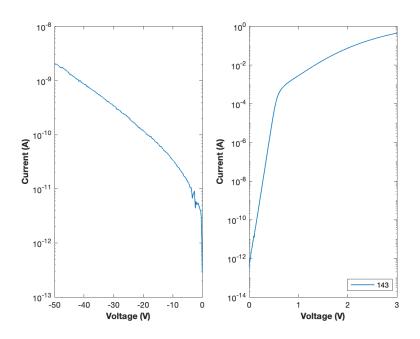

| Figure 72. | Device 143 I-V plot at room temperature                             | 97  |

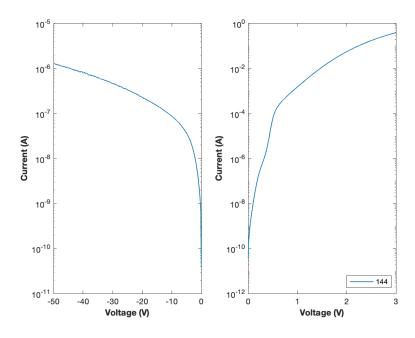

| Figure 73. | Device 144 I-V plot at room temperature                             | 97  |

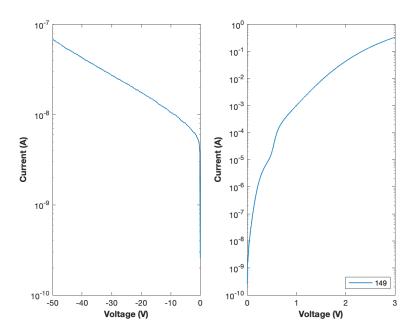

| Figure 74. | Device 149 I-V plot at room temperature                             | 98  |

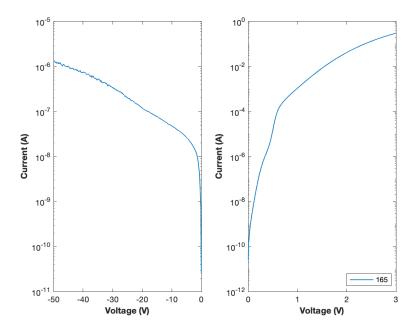

| Figure 75. | Device 165 I-V plot at room temperature                             | 98  |

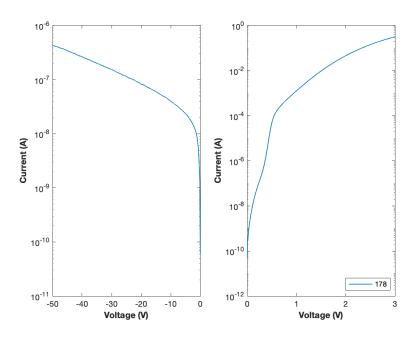

| Figure 76. | Device 178 I-V plot at room temperature                             | 99  |

| Figure 77. | Device 179 I-V plot at room temperature                             | 99  |

| Figure 78. | Device 322 I-V plot at room temperature                             | 100 |

| Figure 79. | Device 326 I-V plot at room temperature                             | 100 |

| Figure 80. | Device 328 I-V plot at room temperature                             | 101 |

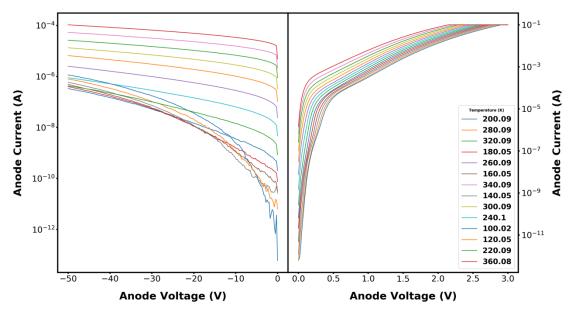

| Figure 81. | Device 19 pre-stress I-V-T plot                                     | 103 |

| Figure 82. | Device 144 pre-stress I-V-T plot                                    | 103 |

| Figure 83. | Device 149 pre-stress I-V-T plot                                    | 104 |

| Figure 84. | Device 178 pre-stress I-V-T plot                                    | 104 |

| Figure 85. | Device 322 pre-stress I-V-T plot                                    | 105 |

| Figure 86. | Device 326 pre-stress I-V-T plot                                    | 105 |

| Figure 87. | Device 328 pre-stress I-V-T plot                                    | 106 |

| Figure 88. | Device 19 pre-stress Richardson plot                                | 107 |

| Figure 89.  | Device 144 pre-stress Richardson plot                          | 107 |

|-------------|----------------------------------------------------------------|-----|

| Figure 90.  | Device 178 pre-stress Richardson plot                          | 108 |

| Figure 91.  | Device 322 pre-stress Richardson plot                          | 108 |

| Figure 92.  | Device 326 pre-stress Richardson plot                          | 109 |

| Figure 93.  | Device 328 pre-stress Richardson plot                          | 109 |

| Figure 94.  | Device 19 pre-stress R <sub>on</sub> versus temperature plot   | 111 |

| Figure 95.  | Device 144 pre-stress R <sub>on</sub> versus temperature plot  | 111 |

| Figure 96.  | Device 149 pre-stress R <sub>on</sub> versus temperature plot  | 112 |

| Figure 97.  | Device 178 pre-stress R <sub>on</sub> versus temperature plot  | 112 |

| Figure 98.  | Device 322 pre-stress R <sub>on</sub> versus temperature plot  | 113 |

| Figure 99.  | Device 326 pre-stress R <sub>on</sub> versus temperature plot  | 113 |

| Figure 100. | Device 328 pre-stress R <sub>on</sub> versus temperature plot  | 114 |

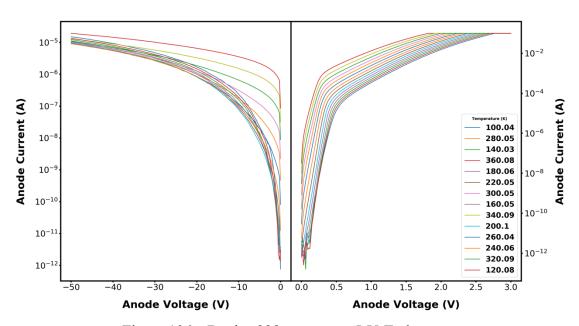

| Figure 101. | Device 19 post-stress I-V-T plot                               | 115 |

| Figure 102. | Device 144 post-stress I-V-T plot                              | 115 |

| Figure 103. | Device149 post-stress I-V-T plot                               | 116 |

| Figure 104. | Device 178 post-stress I-V-T plot                              | 116 |

| Figure 105. | Device 326 post-stress I-V-T plot                              | 117 |

| Figure 106. | Device 328 post-stress I-V-T plot                              | 117 |

| Figure 107. | Device 19 post-stress Richardson plot                          | 119 |

| Figure 108. | Device 144 post-stress Richardson plot                         | 119 |

| Figure 109. | Device 149 post-stress Richardson plot                         | 120 |

| Figure 110. | Device 178 post-stress Richardson plot                         | 120 |

| Figure 111. | Device 326 post-stress Richardson plot                         | 121 |

| Figure 112. | Device 328 post-stress Richardson plot                         | 121 |

| Figure 113. | Device 144 post-stress R <sub>on</sub> versus temperature plot | 123 |

| Figure 114. | Device 149 post-stress R <sub>on</sub> versus temperature plot     | 123 |

|-------------|--------------------------------------------------------------------|-----|

| Figure 115. | Device 178 post-stress for R <sub>on</sub> versus temperature plot | 124 |

| Figure 116. | Device 326 post-stress R <sub>on</sub> versus temperature plot     | 124 |

| Figure 117. | Device 328 post-stress R <sub>on</sub> versus temperature plot     | 125 |

## LIST OF TABLES

| Table 1. | Relevant material properties of Si, SiC, and GaN. Adapted from [5]6                  |

|----------|--------------------------------------------------------------------------------------|

| Table 2. | Parameters for electron transport at an inhomogeneous Schottky barrier. Source: [15] |

| Table 3. | Assigned IP addresses                                                                |

| Table 4. | Table of device average values measured and calculated for Pd/GaN Schottky diodes    |

| Table 5. | GaN Schottky diode initial characterizations and classifications47                   |

| Table 6. | GaN Schottky diode impurity concentrations                                           |

| Table 7. | GaN Schottky diode stress testing conditions                                         |

| Table 8. | Complete table of characterized Pd/GaN Schottky diodes, part 1 of 295                |

| Table 9. | Complete table of characterized Pd/GaN Schottky diodes, part 2 of 296                |

#### LIST OF ACRONYMS AND ABBREVIATIONS

AC Alternating Current

ALT Accelerated Lifetime Testing

BHI Barrier Height Inhomogeneity

C-V Capacitance-Voltage

DC Direct Current

DD Double Diode

DUT Device Under Test

FL Fermi-Level

GaN Gallium Nitride

GCU General Control Unit

GPIB General Purpose Interface Bus

HEMT High Electron Mobility Transistor

HTOL High Temperature Operating Life

IP Internet Protocol

ISR Interface Specific Region

I-V Current-Voltage

I-V-T Current-Voltage-Temperature

MS Metal-Semiconductor

Pd Palladium

PN P-type-N-type

SBH Schottky Barrier Height

Si Silicon

SiC Silicon Carbide SD Single Diode

TEC Thermoelectric Cooler

TCU Temperature Control Unit

WBG Wide Bandgap

#### **ACKNOWLEDGMENTS**

I want to thank all the hardworking professors and support staff within the Electrical and Computer Engineering Department and at the Naval Postgraduate School. I would also like to thank all of my academic colleagues for the friendships created across multiple services and nations. The knowledge gained, experiences had, and bonds formed will last a lifetime. Specifically, I would like to thank my thesis advisor and co-advisor, Dr. Todd Weatherford and Mr. Matthew Porter, respectively, for their advice, guidance, and assistance accomplishing this great feat and academic achievement. Next, I would like to thank LCDR Dave Reinhardt for his friendship and support while at NPS and throughout my career. I would also like to thank CDR Clay Herring for his leadership and mentorship during my time at NPS. Finally, I would like to thank my parents, Sue and Burnie Clemmer, for their continued love and encouragement throughout my life. None of this would have been possible without their support.

#### I. INTRODUCTION

#### A. MOTIVATION

The U.S. Navy has been at the forefront of technological innovation in the United States. It revolutionized the use of steam engines, gas turbines, and nuclear power to enhance its sea power, increasing its ability to operate over greater distances for longer periods of time. In recent years, there has been an increasing interest in advancing electric power and energy systems; naturally, the U.S. Navy should lead the way for implementing such technology, continuing to enhance its power projection.

Critical research in the field of advanced electric power is already underway. The U.S. Navy is researching high-power electronic materials for solid-state power components, power conversion, and direct current (DC) distribution systems [1]. Enhancing electrical power systems reduces the dependence on consumable fuel systems of the U.S. Navy, a limiting factor for operations at sea.

Advanced combat systems, such as the railgun, high-energy lasers, high-power radars, and electronic warfare (EW) systems, all have demanding power and energy needs. These systems currently operate using bulky electrical power systems, relying on numerous alternating current (AC) components to produce and store energy in large battery banks which have inherently low power density. This poses a problem for outfitting naval vessels, which have limited space available and strict weight requirements. Advancements in high-power electronics will lead to an increase in floodable length of a ship, freeing up vital weight and space, and will enable the utilization of the abovementioned systems.

However, as with any military technology, power electronics need to meet high reliability standards. Although early reliability testing at academic facilities, such as the Naval Postgraduate School (NPS) and United States Naval Academy (USNA) has occurred, neither of these institutes presently has a robust and permanent means of conducting reliability testing for power electronic devices. Commercial systems capable of conducting standard high-temperature operating life (HTOL) testing and accelerated life testing (ALT) exist, but they are designed for large-scale research and are rather expensive.

They are capable of testing hundreds of devices at a time. NPS and the USNA have a need for a small-scale HTOL stress test system to conduct lower-level student research.

To meet the power requirements expected for the aforementioned systems, the U.S. Navy is exploring the use of several wide bandgap (WBG) semiconductors for power electronics [1], [2]. Due to their material properties, WBG materials show promise in their ability to outperform silicon devices for more robust power electronics. WBG semiconductors enable high operating voltages, faster switching frequencies, higher operating temperatures, and higher power densities. A key wide bandgap material that is being considered for use is gallium nitride (GaN), which promises to outperform traditional Si power devices and promises significant savings in power efficiency and density in power electronic circuits through its use as the baseline material for fabricating electronic devices. Though GaN has been in use for years by the Navy as a material for RF and optoelectronic applications, the technology to fabricate high power GaN devices on native (bulk) GaN substrates, a necessity for power devices, is still maturing, and much is still unknown regarding the reliability properties and long-term performance characteristics of devices fabricated on bulk GaN. A key basic power device is the Schottky diode, which is used in numerous power electronic applications due to the low switching speed and reasonably high blocking voltage capability of the device. While high power GaN Schottky diodes have been proven in research, little research has been conducted on the reliability of these devices. Understanding the reliability of high power GaN Schottky diodes is a requirement for successful integration into future Navy warfighting platforms.

#### B. RELATED WORK

In 2009, a doctoral student at Pennsylvania State University conducted research involving WBG semiconductors, as detailed in [3]. He investigated the Schottky contacts of several WBG semiconductors, namely silicon carbide (SiC), gallium nitride (GaN), and zinc oxide (ZnO). His research involved electrically characterizing Schottky diodes through current-voltage-temperature (I-V-T) measurements. He observed the effects of barrier height inhomogeneities (BHI) with respect to the Richardson constant. A portion of

his objective was to develop a new method of extracting the Richardson constant from electrical measurements.

In 2016, a student at NPS conducted reliability research on GaN [4]. Specifically, he accompanied characterization and reliability testing on vertical n-type GaN Schottky contacts. He conducted accelerated lifetime tests on multiple GaN Schottky contacts using a stress-measure-stress system. He completed 170 hours of testing at current densities of 2.3 kA-cm<sup>-2</sup>. He examined the degradation physics of a variety of Schottky contact metals, including molybdenum, molybdenum-gold, and chromium-gold.

#### C. OBJECTIVE

This research effort was divided into two main objectives. The first was to design and build a small scale HTOL stress testing system capable of electrically stressing and characterizing Schottky diodes. The stress system was intended to be used at NPS and USNA for current and future reliability research. The system needed to conduct a series of stress-measure-stress tests over a course of several hours while taking simultaneously extracting in-situ characterization data through I-V-T measurements, under forward and reverse voltage bias. Once constructed and verified operational, the HTOL system was used to execute reliability tests on commercial vertical *n*-type GaN Schottky diodes.

The second objective of this work was to examine the effects of high current density electrical stress on vertical palladium (Pd) GaN Schottky diodes grown on high quality bulk GaN substrates. Stress testing was accomplished through stepped current and constant current tests. This effort investigated the presence of BHI and any impacts it may have on device degradation. This research examined observations of "single" and "double" diode characteristics present within our diodes. Pre- and post-stress I-V-T measurements were used along with in-situ I-V-T measurements to characterize devices before, during and after stress testing. I-V-T measurements were used to extract useful Schottky parameters, such as reverse leakage current, forward series resistance, barrier height, and inhomogeneity spreading factor. Finally, these parameters were analyzed as a function of stress time to better understand how these devices degrade over time.

Few reliability research efforts have focused on GaN Schottky diodes, and of those that have, many have yet to provide conclusive results. No specific stress testing research efforts on commercial vertical *n*-type GaN Schottky diodes involving in-situ measurements and observations of degradation as a function of stress-time could be found. Therefore, this research is unique and provides insight into how GaN Schottky diodes degrade and what effects high current density have on their material and electrical properties.

#### D. ORGANIZATION

Chapter II contains all the necessary background information for this research; it reviews GaN technology used for power electronics, the ideal and non-ideal theory for Schottky diodes, and relevant reliability research involving GaN. Chapter III summarizes the HTOL system design, construction, and performance characteristics. Chapter IV introduces the vertical n-type GaN Schottky diodes used in this research and discusses the experimental methodology. Chapter V presents the results and findings of this research. Finally, concluding remarks and recommendations for future work are included in Chapter VI.

#### II. BACKGROUND AND THEORY

This chapter presents the necessary background information required to understand the objective of this research. The chapter is separated into four sections. The first section includes a background of GaN technology as it applies to power electronics. The second and third sections review the ideal and non-ideal theory of Schottky diodes, respectively. Current reliability research involving GaN and HTOL testing for power electronic devices is presented in the fourth section.

#### A. GaN SEMICONDUCTOR TECHNOLOGY

Silicon (Si) has been the dominate material of choice for most semiconductor devices in the industry. Si has a high material abundance, relatively good semiconductor properties, and is easy to fabricate into electronic devices; however, it is reaching its performance limits [5]. Operational limits are strictly dependent on the material properties of Si. Researchers are investigating a variety of new WBG materials, specifically SiC and GaN, to replace Si power devices. SiC is currently the choice WBG semiconductor technology for many commercialized power electronics; however, GaN has potential to be the next technology for future power electronic devices due to the greater inherent mobility of charge carriers in the material, resulting in lower on-state resistances in devices. GaN technology is still maturing, and much is still unknown surrounding the reliability of GaN, making it a prime material for academic research. This section reviews the properties of GaN as they relate to Si and SiC, fabrication processes, and device structures of GaN.

#### 1. GaN Material Properties

WBG semiconductors are described as any material having a bandgap substantially in excess of the bandgaps of materials currently in general use, such as Si [6]. This amount is further defined as a bandgap of 2.2 eV or higher. Both SiC and GaN have a bandgap in excess of 2.2 eV and therefore are classified as wide bandgap semiconductor.

Semiconductors have a large range of material properties, but only a few need to be discussed as they relate directly to power electronic applications. Relevant properties include bandgap ( $E_g$ ), critical electric field ( $E_c$ ), carrier mobility ( $\mu$ ), and thermal conductivity [5]. A summary of these properties can be found in Table 1. Carrier mobility could be for holes or electrons, but electron mobility is generally the desired property used for power applications. Materials with larger bandgaps have lower intrinsic carrier concentrations which reduces reverse leakage current when a device is operating under blocking conditions. The critical electric field of a material is inversely related to the required thickness of the drift region of the material to achieve a desired breakdown voltage and on-state resistance. If the field strength is larger, the drift region thickness is smaller, reducing the resistance and subsequent conduction losses while in the on-state. Carrier mobility is proportional to the achievable power switching speeds; thus, a higher mobility enables power electronic device to operate at higher frequencies. Finally, thermal conductivity is related to the ability of the material to dissipate conducted heat losses. A higher value indicates the material is more effective at dispersing heat, which can lower system cost by reducing the need for external heat sinks.

Table 1. Relevant material properties of Si, SiC, and GaN. Adapted from [5].

| Material Property                                   | <u>Si</u> | 4H-SiC | GaN |

|-----------------------------------------------------|-----------|--------|-----|

| Bandgap (eV)                                        | 1.12      | 3.26   | 3.4 |

| Critical electric field (10 <sup>6</sup> V/cm)      | 0.3       | 3.5    | 3.3 |

| Electron mobility (cm $^2$ /V × sec)                | 1500      | 650    | 990 |

| Electron saturation velocity (10 <sup>6</sup> /sec) | 10        | 20     | 25  |

| Thermal conductivity (W/cm $^2 \times$ K)           | 1.5       | 5      | 1.3 |

Based on the described material properties, GaN is a promising material for power electronics. Advantages of GaN comprise of a bandgap that is about three times greater than Si, slightly higher than SiC and a critical electric field that is 10 times greater than Si, and slighter smaller than SiC. The main disadvantage of GaN is its lower thermal conductivity, almost five times smaller than that of SiC and slightly smaller than Si [5].

#### 2. GaN Device Structures

Before discussing fabrication methods used for GaN it is worth briefly introducing the two types of device structures, namely lateral and vertical. These structures are named for the direction in which current flows through the device. Due to limitations in the fabrication process, GaN-based device structures have been primarily lateral, but recent research efforts have enabled more feasible vertical structures.

High electron mobility transistors, or HEMTs, are the primary example of a lateral device. GaN HEMTs have a high operating frequency and decent transport properties but require a large amount of space be left between the gate and drain to achieve high breakdown voltages [5]. Current density ratings of HEMTs are generally low, as large area lateral devices severely reduce switching times and are not practical. This limitation prevents the use of HEMTs in medium to high-power applications where large current density ratings are crucial. Figure 1 shows an example of a generic GaN HEMT structure.

Figure 1. Generic cross-section schematic of Al/GaN/GaN HEMT structure. Source: [5].

Additional limitations of GaN lateral devices arise from the buffer layers. Buffer layers are susceptible to charge trapping, reducing device electrical and thermal performance. Increased stress across the buffer layers restricts their thickness, limiting breakdown voltages. Vertical structures are much more desirable for high-power applications. Since they do not require buffer layers and have thick epitaxial layers, they can achieve higher breakdown voltages while maintaining good electrical and thermal performance characteristics [7]. Example cross-sections of vertical GaN device structure are shown by Figure 2.

Figure 2. Schematic cross-sections of vertical Schottky (top) and PN (bottom) diodes. Source: [7].

#### 3. Bulk GaN Fabrication

Despite the material advantages of GaN, there are additional technical hurdles that must be overcome to make it viable for commercialized power devices. Unlike Si and SiC which have well established and economic production processes for bulk substrates, GaN has historically lacked a growth process for achieving high-quality bulk native substrates [5]. GaN power devices have been fabricated using non-native substrates, namely Si, SiC, and Sapphire, limiting growth to lateral device structures with thin films of GaN. Furthermore, the processes used to fabricate GaN on non-native materials result in higher defect densities, greater than  $10^8$  cm<sup>-2</sup>, making them less effective for power applications [7].

Fabrication of lateral GaN devices on foreign substrates has been effective and is the focus of several research efforts; see [8] through [10]. However, producing low-defect density bulk-GaN is critical to realizing reliable, high-performing vertical power devices. Researchers are actively pursuing methods to achieve affordable, low-defect density bulk-GaN for use in power device fabrication [11]. Ueno et al. was able to fabricate vertical

GaN Schottky barrier diodes with a forward current of 5A and blocking voltage of 600V on a bulk GaN substrate with a dislocation density less than 10<sup>6</sup> cm<sup>-2</sup>. Additional strides in growth processes have allowed researchers to achieve defect densities below 10<sup>5</sup> cm<sup>-2</sup> [7].

Nitride-based materials, such as GaN, cannot use traditional crystal growth methods. Epitaxial growth processes are required to fabricate high quality GaN substrates [5]. These methods include high pressure thermodynamic methods such as ammonothermal growth, and chemical reaction-based deposition methods such as liquid phase epitaxy (LPE), hydride vapor phase epitaxy (HVPE), and metalorganic chemical vapor deposition (MOCVD). The most widely used of method is MOCVD.

#### B. IDEAL THEORY OF SCHOTTKY DIODES

Schottky diodes are a fundamental electronic device. They can be found in electronic circuits as standalone components or as a part of Schottky contacts formed by gate metals of more complex power devices. Schottky diodes also serve as useful research platforms. Electrical characterization of Schottky diodes provide novel information as to the quality and performance characteristics of material substrates and epitaxial layers [3]. Moreover, Schottky diodes fabricated from WBG materials demonstrate desirable properties for applications in high-power electronics.

#### 1. Energy Band Theory

Schottky barrier diodes are rectifying contacts formed at Metal-Semiconductor (MS) junctions. Ideal MS rectifying contacts have three assumed properties. First, the metal and semiconductor are assumed to be in intimate contact, without any additional layers between the two surfaces. Second, interdiffusion between metal and semiconductor has not occurred; Third, there are no surface charges or other surface defects, or impurities, at the MS junction [12]. Finally, the doping level of the semiconductor must be kept sufficiently low as to not allow tunneling current, which generally leads to the formation of ohmic contacts between the metal and the semiconductor.

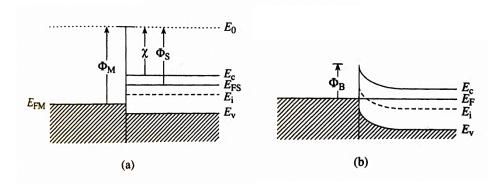

As with any semiconductor, drawing the energy band diagram is essential to understanding the theory. The band diagrams for an ideal Schottky contact just before and

after equilibrium is reached can be seen in Figure 3.  $E_c$ ,  $E_{FS}$ ,  $E_i$ , and  $E_v$  are the same energies as they would be for the *n*-type material of a PN diode.  $E_0$  is referred to as the vacuum level and is used in determining the work function ( $\Phi$ ) of a material.  $E_{FM}$  is the Fermi level of the metal,  $\Phi_M$  is the metal work function,  $\chi$  is the electron affinity, and  $\Phi_S$  is the semiconductor work function.

$\Phi_M$  is a basic property of the metal, varying from 3.66 eV to 5.15 eV [12]. Likewise,  $\Phi_S$  is dependent on  $\chi$ , an inherent property of the semiconductor, and the difference between  $E_c$  and  $E_{FS}$  under flat band conditions, shown in Figure 3(a).

$$\Phi_S = \chi + (E_C - E_F) \tag{1}$$

Figure 3(b) shows the band diagram of the Schottky contact once equilibrium has been reached. Electrons transfer from the semiconductor to the metal due to the availability of empty states at a lower energy, causing a depletion region and barrier to form until  $E_{FM}$  equals  $E_{FS}$ .  $\Phi_B$  is known as the barrier height and for an ideal n-type Schottky diode is given by

$$\Phi_B = \Phi_M - \chi,\tag{2}$$

and is often referred to as the Schottky-Mott relationship.

(a) An instant after the contact formation. (b) Under the equilibrium conditions.

Figure 3. Energy band diagram for an ideal Schottky contact between a metal and an n-type semiconductor. Source: [12].

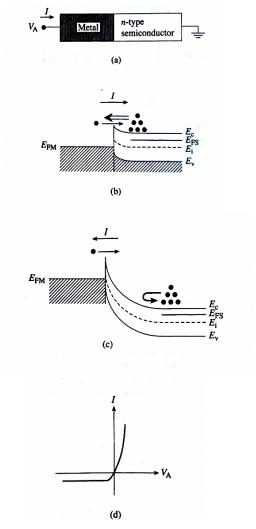

Appling a positive voltage across an *n*-type Schottky diode, based on the polarities described by Figure 4(a), lowers E<sub>FM</sub> in relation to E<sub>FS</sub>, reducing the perceived barrier. Electrons in the semiconductor will eventually flow exponentially over the barrier to the metal, forward biasing the device, as shown in Figure 4(b). If the polarity of the applied voltage is reversed then E<sub>FM</sub> will raise above E<sub>FS</sub>, increasing the perceived barrier to electrons in the semiconductor and blocking them from flowing into the metal as shown in Figure 4(c). In either case, the perceived barrier from the metal into the semiconductor remains the same and a constant, yet small, amount of leakage current flows into the semiconductor. Figure 4(d) shows the rectifying properties of the current-voltage (I-V) relationship for an ideal n-type Schottky diode [12].

(a) Definition of current and voltage polarities. (b) Energy band diagram and carrier activity when  $V_A > 0$ . (c) Energy band diagram and carrier activity when  $V_A < 0$ . (d) Deduced general form of I-V characteristics.

Figure 4. Response of the (n-type) MS contact to an applied DC bias. Source: [12].

#### 2. Electrostatic Characteristics

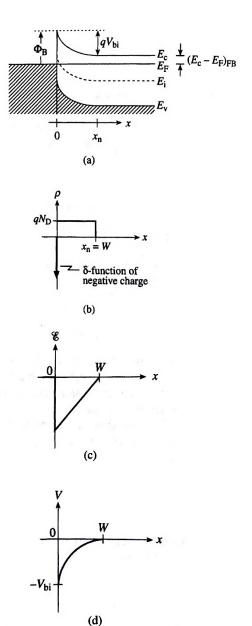

As with the band theory, the electrostatics of a Schottky diode are comparable to many concepts derived from PN diodes [12]. For this analysis, doping levels,  $N_D$ , are assumed to be uniform through the device. Schottky diodes have a built-in voltage potential,  $V_{bi}$ , as described by

$$V_{bi} = \frac{1}{q} \left[ \Phi_B - (E_c - E_F) \right]. \tag{3}$$

where q is the charge of an electron and is shown by Figure 5(a).

A depletion region forms at the MS interface and extends into the semiconductor until charge distribution becomes neutral again. In a PN diode, the depletion region extends into the n-side and p-side of the device, effectively neutralizing the effective charge polarity seen across the region by the opposing polarity. However, a Schottky diode does not have a p-side to balance out the effective charge build-up on the n-side. As a result, excess negative charge builds up on the metal side of the MS interface, provided by the free electrons in the metal [12]. Charge density,  $\rho$ , can be described as a  $\delta$ -function at the interface with a constant distribution into the semiconductor for the width, W, of the depletion region and is shown in Figure 5(b).

$$\rho = \begin{cases} N_D, 0 \le x_n \le W \\ 0, x_n > W \end{cases} \tag{4}$$

Using Poisson one-dimensional equation and solving Equation (4) for electric field yields the following solution:

$$\mathcal{E}(x) = -\frac{qN_D}{K_S \varepsilon_0}, 0 \le x_n \le W \tag{5}$$

which is graphically represented in in Figure 5(c).  $K_S$  is the dielectric constant of a material, 8.9 for GaN, and  $\varepsilon_0$  is the vacuum permittivity. Knowing that the electric field is equal to the voltage potential divided by a known distance, the electrostatic potential is determined to be

$$V(x) = -\frac{qN_D}{2K_S\varepsilon_0}(W - x)^2, 0 \le x_n \le W.$$

(6)

Figure 5(d) shows the electrostatic potential.

(a) Band diagram at equilibrium. (b) Charge density at equilibrium. (c) Electric field at equilibrium. (d) Electrostatic potential as a function of position at equilibrium.

Figure 5. Electrostatic variables in an MS (*n*-type) diode under equilibrium conditions. Source: [12].

Finally, the depletion width can be deduced by solving the electrostatic potential at x equals to zero, yielding a solution identical to that of a p+-n junction [12].

$$W = \left[\frac{2K_S\varepsilon_0}{qN_D}(V_{bi} - V_A)\right]^{\frac{1}{2}} \tag{7}$$

# 3. Current Transport Process

The current transport processes within a Schottky diode are where the theory diverges from that of a PN diode. PN diodes are commonly referred to as minority carrier devices since the dominant current component under forward bias comes from the recombination of minority carriers in the depletion region. Schottky diodes, on the other hand, are considered to be majority carrier devices [12]. The dominant component of current transport for a high mobility *n*-type Schottky diode is due to thermionic emission [13].

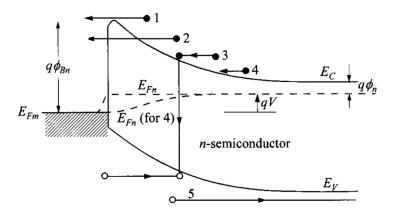

There are five independent mechanisms of current transport within a Schottky diode [13]. Minority carrier current transport processes within the depletion region, such as recombination-generation (R-G) and minority carrier injection still occur in a Schottky diode. Electrons can tunnel through the Schottky barrier and diffuse from the semiconductor into the metal. However, by time additional current transport processes become relevant, tunneling current adds such a small amount to the total current that it is generally considered negligible in Schottky diodes used for rectification purposes [12]. Figure 6 shows the five separate mechanisms of current transport in a Schottky diode.

Mechanisms of current transport are (1) thermionic emission, (2) quantum-mechanical tunneling, (3) recombination-generation, (4) carrier diffusion from the semiconductor to the metal, and (5) minority carrier injection.

Figure 6. Five observed current transport processes for a *n*-type Schottky diode. Source: [13]

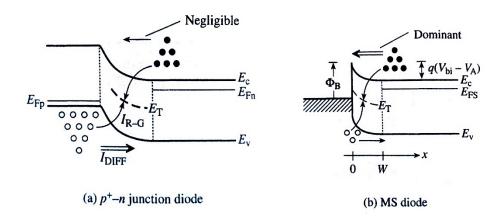

Figure 7 shows the differences between the current transport processes of a PN diode and a Schottky diode, to include the negligible and dominant current components under forward bias.

(a) Current transport process of a p<sup>+</sup>-n junction diode. (b) Current transport process of a MS (*n*-type) diode.

Figure 7. Negligible and dominant current components in forward biased. Source: [12].

If an electron traveling towards the surface of the MS interface has a high enough velocity, then it will be capable of overcoming the potential barrier. Assuming there are a certain number of electrons, each with a velocity great enough to surmount the barrier, then the total current can be derived for the group of electrons by summing the contribution from each electron [12]. Thermionic emission is considered a ballistic transport process for these reasons. It can easily be shown that the equation describing thermionic emission for an ideal Schottky diode is

$$I = I_{sat} \left( e^{\left( \frac{qV_A}{\eta kT} \right)} - 1 \right), \tag{8}$$

and the saturation current component is given by

$$I_{sat} = AA^*T^2e^{\left(-\frac{q\Phi_B}{kT}\right)}. (9)$$

A is the area of the diode,  $\eta$  is ideality factor, k is Boltzmann constant, q is the charge of an electron,  $V_A$  is the applied bias voltage, and T is the temperature. The ideality factor is assumed equal to one for the ideal theory.  $A^*$  is known as the Richardson constant and determined by

$$A^* = \frac{4\pi q m^* k^2}{h^3} \tag{10}$$

where  $m^*$  is the effective mass of an electron and h is Plank constant.

## 4. I-V and I-V-T Relationships

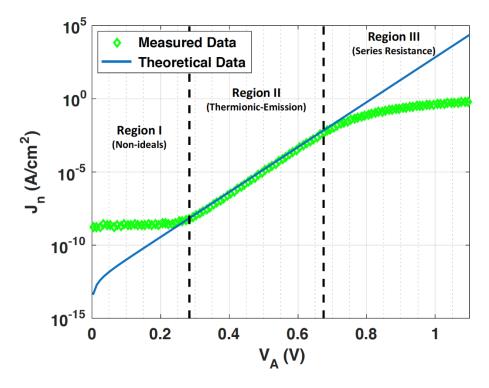

A distinct relationship between current and voltage is formed by Equations (8) and (9). A semi-logarithmic plot of theoretical and experimental I-V data for an example *n*-type GaN Schottky diode is shown in Figure 8. The plot can be divided into three separate regions [4]. Region I shows how the additional current components and other non-ideal factors add to the predicted current level as determined by thermionic emission alone. Region II shows the relationship once thermionic emission takes over as the dominant current component. Region III shows the limiting effects of series on-state resistance, lowering the expected current level.

Figure 8. Theoretical and experimental semi-logarithmic I-V plot for an example *n*-type GaN Schottky diode. Source: [4].

A linear fit can be obtained by taking the natural logarithm of Equation (8) and applying it to region II.

$$ln(I) = ln(I_{sat}) + \frac{q}{nkT}V_A$$

(11)

The y-intercept of Equation (11) yields the  $I_{sat}$  and the ideality factor can be determined from the slope of the linear fit. Once the saturation current is determined, the barrier height can be determined by taking the natural logarithm of Equation (9) and solving for  $\Phi_B$ .

$$\Phi_B = \frac{kT}{q} ln \left( \frac{AA^*T^2}{I_{sat}} \right) \tag{12}$$

Accurately determining the Richardson constant is critical to determining the correct barrier height of a Schottky diode. While the ideal Richardson constant is solely a function of the electron effective mass in the bulk of the semiconductor, measuring the

actual value of A\* can be difficult since it is highly dependent on individual MS contacts and depends on several factors, such as annealing temperatures, fabrication and metallization processes, and surface cleaning [14]. Researchers have shown small variations, less than 0.026 eV, from derived values for barrier height, even for large errors, up to a few orders of magnitude, in A\*, but a more accurate method for solving barrier exists using the temperature dependency of the I-V relationship. A\* can be determined for an individual Schottky contact from experimental data and solved independent of surface variations through I-V-T measurements. This method is known as the activation-energy analysis and involves determining I<sub>sat</sub> at each temperature across a range [14].

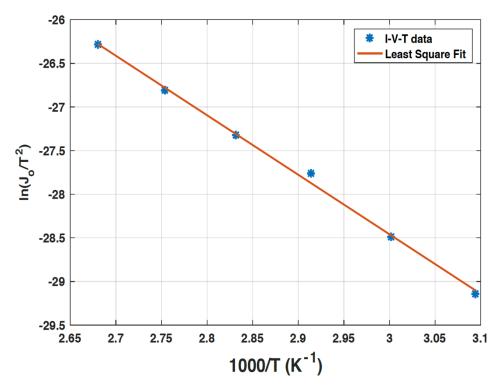

An activation-energy analysis of the saturation current produces what is known as a Richardson plot and enables  $\Phi_B$ ,  $\eta$ , and  $A^*$  graphically determined. The Richardson plot is generated by plotting each calculated saturation current divided by temperature squared versus q/kT. Figure 9 shows an example of Richardson plot for a n-type GaN Schottky diode.

Figure 9. Richardson plot for a *n*-type GaN Schottky diode. Source: [4].

The Richardson constant and barrier height can be extracted from taking the natural logarithm of Equation (9) and using a linear fit. The example shown in Figure 9 uses a least-squares fit.

$$ln\left(\frac{I_{sat}}{AT^2}\right) = ln(A^*) - \frac{q\Phi_B}{kT}$$

(13)

$A^*$  is determined from the y-intercept of the Richardson plot and  $\Phi_B$  is solved from the slope of the linear fit.

#### C. NON-IDEAL THEORY OF SCHOTTKY DIODES

The ideal theory of a Schottky diode made several assumptions regarding the MS interface which made solving electrical processes and visualizing the energy band diagrams easier. The theory assumed a homogenous barrier with no physical or chemical interactions between the metal and semiconductor at the MS interface. However, experimentally measured values of the Schottky barrier height (SBH), as described by Equation (2), the current, as described by Equations (8) and (9), and ideality factor show a deviation from the Schottky-Mott model [14]. Experimental observations also show a non-linear relationship in I-V curves when the current is plotted on a logarithmic scale at the voltage ranges where the thermionic emission current should dominate.

Tung [14] determined that experimentally measured values of the SBH often described the average barrier height, vice the true SBH. His analysis of the SBH and use of the idea of barrier height inhomogeneity (BHI) also accounted for other experimentally observed phenomena which deviate from ideal theory. These phenomena include leakages and edge-related currents, greater-than-unity ideality factors, T<sub>0</sub> anomaly, temperature dependence of the ideality factor, and "soft" reverse characteristics [15].

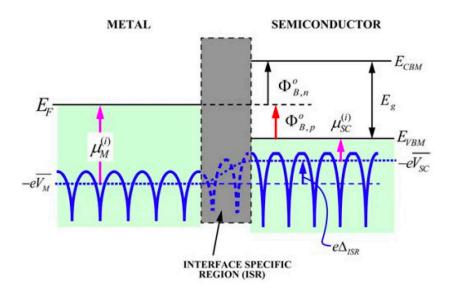

## 1. Formation of the Schottky Barrier

The Schottky barrier that is formed from an MS interface is a critical component in determining the operating characteristics of a device. The SBH dictates many of the electrical properties for current transport across the device [14]. The ideal theory assumes a uniform distribution of states with an average electrostatic potential, yet there are innate

discontinuities between the electronic energy states at the MS interface which lead to non-linear I-V characteristics. Figure 10 shows the difference between the described electrostatic distribution.

Curved solid lines indicate the electrostatic potential energy. Dotted lines indicate average electrostatic potential.

Figure 10. Energy Band diagram at a MS interface. Source: [14].

The underlying physics behind the formation of Schottky barriers has been an unsettled topic of interest among researchers for decades and has been determined to be a complicated function of surface conditions, metal type, and variation due to differing chemical surface preparations used to fabricate Schottky diodes [15]. Atomic-level interactions between at the MS interface was the focus of early research. The concept of Fermi-level (FL) pinning was suggested as the main cause deviation from ideality and gave rise to interface specific region (ISR) models.

Two widely and historically used ISR models include the Bardeen model and the metal-induced gap states (MIGS) model. The Bardeen model explains FL pinning through the formation of a dielectric layer at the semi-conductor surface [16]. The dielectric layer is formed from the inherent space charge region of the Schottky diode and by a build-up

of electrons at the surface states, assuming the density of states is high enough. Once the MS interface is formed, the surface states charge causes a pinning effect on the FL, causing an energy-level independent of the work function. The MIGS model is based on the ideas that gap states, due to defects or foreign contaminant atoms, exist at the MS interface causing electronic states to exist within the energy band gap and similarly pinning the FL [4]. Both models to provide a qualitative means to analysis FL pinning of the Schottky barrier, but fail to explain the magnitude of deviation of the measured SBH and the physics at the atomic level within the ISR.

## 2. SBH Inhomogeneity and Potential Distribution

A more accurate and modern ISR model is the Equilibrium of Electrochemical Potential (EECP) model, proposed by Tung [17]. The EECP model explained observations of FL pinning due to polarization of interfacial chemical bonds between metal and semiconductor atoms, vice surface states or MIGS. Furthermore, his model provided an explanation for the Schottky BHI, since a change in chemical bonds across the MS interface from crystalline mismatches or other defects results in localized variations of the SBH [4].

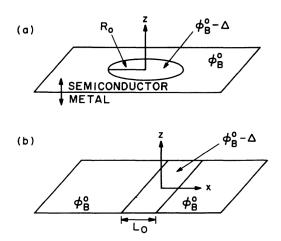

Since the SBH will vary locally along the MS interface, the potential distribution can be approximated using a dipole-layer approach. Each potential variation across the layer of dipoles is treated as a perturbation in the analysis of the MS interface [15]. The most relevant form of SBH inhomogeneity to this research is that of a small region of low SBH surrounded by region of high SBH. The area of high SBH is assumed to be relatively uniform in comparison to the low SBH region. The low SBH region is modeled by either a small circular patch or a narrow semi-infinite linear strip, as shown by Figure 11.

(a) Potential distribution of a circular path. (b) Potential distribution of a narrow strip.

Figure 11. Example geometries used for potential distribution analysis. Source: [15].

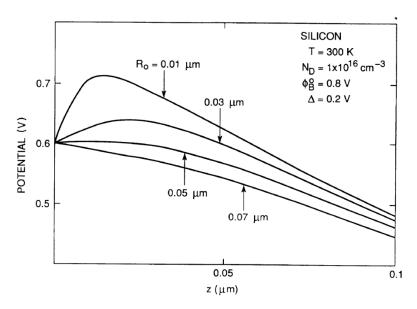

It is important to note that the size of the low SBH patch affects the potential pinch-off within that region and has a significant impact on the transport properties of the MS interface. Potential pinch-off occurs because of the surrounding area of high SBH on the low-SBH region and is more easily achieved if patch is smaller in radius, or the strip is narrower. Figure 12 shows the effect of the size of the radius of a small circular patch under forward and reverse potential bias.

Figure 12. The effects of radius of low SBH patch on potential pinch-off. Source: [15].

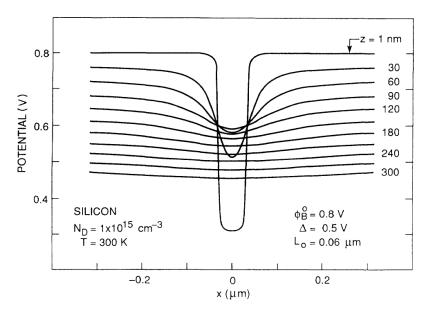

The pinch-off creates a saddle point that and can be effectively represented by a point-dipole approximation. This phenomenon can be seen in Figure 13, which shows the horizontal cross-section of a three-dimensional potential difference along a narrow strip placed along the x=0 axis and the potential well that develops around the low SBH strip and the surrounding high SBH region [15]. Essentially, the two-dimensional effect of the potential pinch-off in the low barrier height region is to make the effective barrier height for carriers traveling through the low SBH patch dependent upon the bias applied to the contact.

Figure 13. Potential distribution surrounding a narrow low SBH strip. Source: [15].

A detailed analysis of the potential distribution and the dipole-layer and pointdipole approximations is provided by Tung in [15].

## 3. Electron Transport

Once the electric potential surrounding the saddle point is determined, the current flowing through the region can be determined through some further analysis and modifications to the thermionic emission equation, Equation (8). Tung [15] goes through an in-depth analysis starting with an isolated region with low SBH then a Schottky barrier containing many low SBH regions, with a sharp distribution and with a broad distribution. From Tung analysis, the total current through the Schottky barrier with a sharp distribution is given by

$$I_{total} = AA^*T^2e^{\left(-\beta\Phi_B^0\right)}\left(e^{(\beta V_a)} - 1\right) \times \left(1 + \frac{4c_1\pi\eta^{\frac{2}{3}}\gamma_0}{9\beta V_{bb}^{\frac{2}{3}}}e^{\left(\frac{\beta\gamma_0V_{bb}^{\frac{1}{3}}}{\eta^{\frac{1}{3}}}\right)}\right), \tag{14}$$

where  $\beta = 1/kT$ ,  $c_1$  is the total density of patches, and  $V_{bb}$  is the band bending at the MS junction, assuming a uniform SBH,  $\Phi_B^0$ . The parameters  $\eta$  and  $\gamma$  will be defined later in this section. Using a more generalized statistical distribution of inhomogeneity, Equation (14) can be rewritten as

$$I_{total} = AA^*T^2e^{\left(-\beta\Phi_B^0\right)}\left(e^{\left(\beta V_a\right)} - 1\right) \times \left(1 + f(V_{bb})e^{\left(\beta^2\kappa V_{bb}^{\xi}\right)}\right). \tag{15}$$

A subsequent and more detailed explanation about the statistical analysis used and how Equation 15 is derived will be provided towards the end of this section.

The total current flowing through the Schottky diode is essentially made up of two distinct current components [15]. The first is the average current across the entire surface based on the uniform "high" barrier height,  $\Phi_B^0$ . The second is the added current flowing through the low-SBH regions. The effective barrier height of the Schottky diode for this component is

$$\Phi_{eff} = \Phi_B^0 - \beta \kappa V_{bb}^{\xi}. \tag{16}$$

The effective SBH is a temperature dependent term despite the fact electrostatic barrier height of regions of low SBH are effectively independent of temperature [15]. The dependence upon temperature arises from the averaging of thermionic emissions across an inhomogeneous surface. Since  $\Phi_B^0$  is temperature dependent then I<sub>total</sub> must also depend on temperature. Another noteworthy temperature dependence caused by BHI is that of the ideality factor, leading to greater-than-unity values. The ideality factor has dependence on temperature and voltage and can be approximated as

$$\eta_{tot} \approx 1 + \xi \beta \kappa V_{bb}^{\xi - 1}. \tag{17}$$

The temperature dependence of the ideality factor has been observed experimentally across a variety of MS junctions and no one theory could properly account for the variance, commonly referred to as the "T<sub>0</sub> anomaly" [15]. It is shown to be present in any diode if the junction current can be written in the following form,

$$I_{total} = AA^*T^2 e^{\left(-\frac{q\Phi_B^0}{k_B(T+T_0)}\right)} \left(e^{\left(\frac{qV_a}{k_B(T+T_0)}\right)} - 1\right).$$

(18)

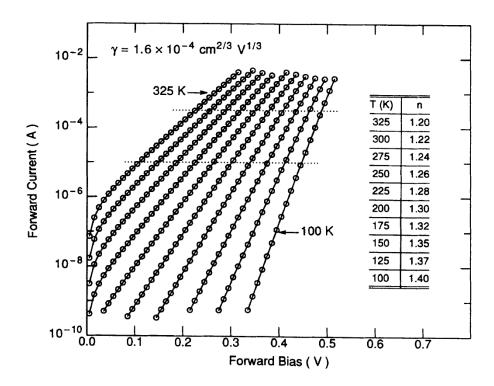

Historically, the T<sub>0</sub> effect had been attributed to an exponential distribution of the density of interface states within an interface layer; however, the measured variation across similar devices was too great to be explained by this theory. BHI provides a better explanation of the dependence on temperature and is more consistent with observed results [15]. Two general observations can be made as the temperature is lowered across an inhomogeneous SBH. First, the ideality factor increases as the bias is increased and, second, as temperature is lowered for a device with low SBH regions, the measured junction current is dominated by regions of low SBH and therefore yields a higher ideality factor. Figure 14 shows these observations for a Silicon Schottky diode.

Figure 14. I-V traces of Si Schottky barrier at varying temperatures. Source: [15].

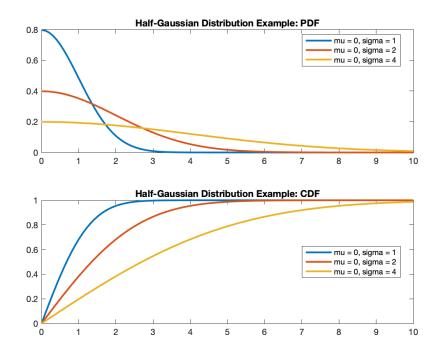

Tung analysis of BHI provides a set of topology specific parameters for a patch, and strip, and assumes a positive half-Gaussian statistical distribution of patch sizes, or

strips, with the mean of the distribution set to zero [15]. The regional density of patches is shown as  $N(\gamma)d\gamma$  and uses the random patch parameter  $\gamma$  between  $\gamma$  and  $\gamma + d\gamma$ .

$$N(\gamma) = \frac{\sqrt{2}c_1}{\sqrt{\pi}\sigma_1} e^{\left(-\frac{\gamma^2}{2\sigma_1^2}\right)}, \gamma > 0,$$

$$N(\gamma) = 0, \qquad \gamma < 0. \tag{19}$$

Figure 15 shows a generic example of a half-Gaussian distribution with varying values of sigma,  $\sigma$ , to better illustrate the concept described in Equation (19).

Figure 15. Half-Gaussian distribution example.

Assuming low SBH patches are spatially separated enough to not interact with each other, the total current at a given bias can be solved by applying the half-Gaussian distribution described in Equation (19) and integrating over all patches:

$$I_{total} = AA^*T^2e^{\left(-\beta\Phi_B^0\right)}\left(e^{(\beta V_a)} - 1\right) \times \left\{ \frac{4\sigma_1^2C_1\pi\eta^{\frac{1}{3}}}{9V_{bb}^{\frac{1}{3}}}e^{\left(\frac{\beta^2\sigma_1^2V_{bb}^{\frac{2}{3}}}{2\eta^{\frac{1}{3}}}\right)} \times \left(1 + erf\left(\frac{\beta\sigma V_{bb}^{\frac{1}{3}}}{\sqrt{2}\eta^{\frac{1}{3}}}\right)\right) + 1 \right\}.$$

(20)

The error function from Equation (20) can be reduced to equal 1 under typical environmental conditions, temperature, doping levels, and other material properties. In doing so, Equation (20) simplifies to equal Equation (15) as presented earlier in this section.

Tung electron transport parameters include two critical metrics which to describe the inhomogeneity of a Schottky contact. The first is the integrated spatial concentration of the patches or strips which the distribution is normalized to, represented as  $c_1$  for circular patches and  $c_2$  for strips, and given in units of cm<sup>-2</sup>. The second is the measure of the statistical standard deviation, or spread, of inhomogeneity through the Schottky contact, denoted  $\sigma_1$  for patches and  $\sigma_2$  for strips. It is based on the random patch parameter,  $\gamma$ , which is a combination of physical properties of the patch to include size, as well as material characteristics such as the dielectric constant and doping level. Due to the units of the variables chosen for the distributions, the units of the standard deviation are given as cm<sup>-2/3</sup>eV<sup>-2</sup>. Table 2 shows Tung parameters for electron transport.

Table 2. Parameters for electron transport at an inhomogeneous Schottky barrier. Source: [15]

| Parameter             | Patch                                               | Strip                                                                          |  |

|-----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------|--|

| ξ                     | 2/3                                                 | 1/2                                                                            |  |

| к                     | $\frac{\sigma_1^2}{2\eta^{2/3}}$                    | $\frac{\sigma_2^2}{2\eta^{1/2}}$                                               |  |

| f(β,V <sub>bb</sub> ) | $\frac{8c_1\sigma_1^2\pi\eta^{1/3}}{9V_{bb}^{1/3}}$ | $\frac{c_2\pi\sigma_2^{3/2}\sqrt{\beta}\eta^{1/8}L_{strip}}{1.46V_{bb}^{1/8}}$ |  |

It is important to note that although the parameters for patches and strips are different, the total junction current for each case yields the same expression as shown by Equation (15). The constant values for  $\xi$  and  $\kappa$  and the function  $f(\beta, V_{bb})$  are used for their respective patch parameters to solve for the total current.

BHI provides a useful understanding the physics taking place at an MS junction and more accurately describes the physics of electron transport through an inhomogeneous Schottky contact. It gives rise to one of the critical problems for power electronics through a phenomenon known as current crowding. Due to inhomogeneity of the Schottky contact, current tends to flood the areas of low SBH, limiting current in the device while simultaneously increasing the series resistance [15]. Higher series resistance drives up power consumption and higher device temperatures, negatively impacting the reliability of power devices.

#### D. Gan reliability research

The study of GaN-based device structures has continued to gain popularity amongst researchers since the early 1980s. In 1983, Kahn et al. [18] examined the electrical and material properties of GaN. It was shown that GaN has a higher electron mobility and higher electric breakdown voltage than both Si and SiC. There results validated the theoretical advantages that GaN could have over Si and SiC for uses in power electronic applications.

As fabrication methods have improved, the theoretical expectations of the performance of GaN-based began to be realized, specifically for lateral RF devices. However, most reliability studies involving GaN have still concentrated on lateral devices, specifically high electron mobility transistors (HEMTS). Research concerning vertical GaN structures have targeted PN diodes and heterostructure field effect transistors (HFETs) [5]. Schottky GaN Schottky diodes are of particular interest for power electronics because their on-state voltage is approximately 3 times smaller than that of a GaN PN diode, resulting in significantly lower conduction losses.

## 1. Reliability Research Involving GaN Schottky Diodes

In 2001, Chen et al. [19] conducted a thermal stability study of Ni/Ta n-GaN Schottky contacts and observed the effects through electrical measurements. I-V measurements were taken after a variety of thermal annealing conditions were applied to the diodes. There experiment varied in annealing time from five minutes up to one hour and temperatures ranging from 300 °C up to 800 °C. The team found that after one hour of annealing at 700 °C, that a high quality Schottky diode with an ideality factor of 1.16 and a barrier height of 1.24 eV could be attained.

In 2008, Parish et al. [20] measured the forward bias I-V characteristics of n-GaN Schottky diodes over a large temperature range from 70 to 400 K. Their observations of the I-V curves showed a two-step kink on the semi-logarithmic plots, or double-diode type behavior. In their analysis the team used a model of two discrete diodes in parallel to fit the curves, each with a distinct SBH. They found one such barrier to correlate to the results expected for an ideal diode, matching Capacitance-Voltage (C-V) measurements and flatband I-V measurements, while the other exhibited a reduced SBH with temperature dependence.

In 2013, J. Shin et al. [21] investigated the barrier height inhomogeneity (BHI) of the gate metal for AlGaN/GaN Schottky diodes. Their analysis included electro-reflectance spectroscopy and X-ray photoelectron spectroscopy measurement for different types of Schottky gate metals, including Au, Pt, Pd, and Ni, and concluded the BHI on the gate metal depends on the type of Schottky gate metals used.

In 2016, R. P. Tompkins et al. [22] conducted I-V measurements on GaN power Schottky diodes and presented data on device characteristics including the breakdown voltage,  $V_b$ , specific on-resistance,  $R_{on\text{-}sp}$ , ideality factor, n, and barrier height,  $\Phi_b$ . They also conducted I-V-T measurements, assessing properties as a function of temperature from 25 to 250 °C in increments of 25 °C.

## 2. HTOL Stress Testing Involving Commercial GaN Devices

HTOL testing has been critical to GaN research in evaluating its reliability. HTOL testing used for ALT, projecting the lifetime of commercial grade devices. Most recent studies involving GaN Schottky diodes have been conducted on experimental Schottky contacts, not fully packaged devices. Although this is useful for understanding how GaN Schottky contacts perform, it is not indicative of how a packaged device will perform. The process of packaging devices adds more variables that may impact the overall functionality and reliability of the device. However, in 2014, Wu et al. [23] conducted a series of high temperature DC stress tests on 600V GaN power switches, HEMTs, fabricated on Si.