# UNCLASSIFIED

# AD NUMBER

## ADB011607

# LIMITATION CHANGES

# TO:

Approved for public release; distribution is unlimited.

# FROM:

Distribution authorized to U.S. Gov't. agencies only; Test and Evaluation; FEB 1976. Other requests shall be referred to Air Force Avionics Lab., Wright-Patterson AFB, OH 45433.

# AUTHORITY

WL/AFSC(IST) ltr 12 Apr 1991

THIS PAGE IS UNCLASSIFIED

AFAL-TR-76-28

ADB 011607

FET POWER AMPLIFIER

Texas Instruments Incorporated

April 1976 TECHNICAL REPORT AFAL-TR-76-28 Final Technical Report for Period | March 1975 - 30 November 1975

Distribution limited to U.S. Government agencies only; test and evaluation; February 1976. Other requests for this document must be referred to Air Force Avionics Laboratory, AFAL/DHM, Wright-Patterson AFB, Ohio 45433.

AIR FORCE AVIONICS LABORATORY AIR FORCE WRIGHT AERONAUTICAL LABORATORIES AIR FORCE SYSTEMS COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OHIO

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

This final report was submitted by Texas Instruments Inc., Dallas, Texas 75222, under contract F33615-75-C-1123, job order number 69CK0135, with the Air Force Avionics Laboratory, Wright-Patterson AFB, Ohio 45433. Chern I. Huang, AFAL/DHM-1, is the project engineer for the project.

This technical report has been reviewed and is approved for publication.

Chern Huang

CHERN I. HUANG Project Engineer Microwave Device Group

RICHARD L. REMSKI Actg. Chief, Microwave Device Group Microwave Technology Branch

FOR THE COMMANDER

WILLIAM J. EDWARDS Actg. Chief, Electronic Tech. Div. Air Force Avionics Laboratory

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

AIR FORCE - 1 JUNE 76 - 125

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered) **REPORT DOCUMENTATION PAGE READ INSTRUCTIONS** BEFORE COMPLETING FORM IMBED 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER AFAL TR-76-28 TITLE (and Subtitle) TYPE OF REPORT & PERIOD COVERED Final Technical Report -0 FET POWER AMPLIFIER . 5-30 Nove Marca -08-76-04 V CONTRACT OF GRANT NUMBER(.) AUTHORA W. R./Wisseman; V./Sokolov 0 R. L./Adams; H. Q./Tserng F33615-75-C-1123 hull H. M. /Macksey , PERFORMING ORGANIZATION NAME AND ADDRESS 10. PROGRAM ELEMENT, PROJECT, TASK AREA & WORK UNIT NUMBERS Texas Instruments Incorporated Central Research Laboratories V Project No. 69CK 13500 North Central Expressway Task No. 0135 Dallas, Texas 75222 CONTROLLING OFFICE NAME AND ADDRESS 12. REPORT DATE Air Force Avionics Laboratory April 76 Air Force Systems Command Wright-Patterson Air Force Base, Ohio 45433 105 14. MONITORING AGENCY NAME & ADDRESS(II dillerent from Controlling Office) 15. SECURITY CLASS. (of this report) UNCLASSIFIED 154. DECLASSIFICATION/DOWNGRADING SCHEDULE 16. DISTRIBUTION STATEMENT (of this Report) Distribution limited to U.S. Government agencies only; test and evaluation; February 1976. Other requests for this document must be referred to Air Force Avionics Laboratory, AFAL/DHM, Wright-Patterson AFB, Ohio 45433. 17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Report) 16) AF-69CK, 18. SUPPLEMENTARY 19. KEY WORDS (Continue on reverse side if necessary and identify by block number) GaAs Field Effect Transistor (FET) GaAs Epitaxial Growth, FET Power Amplifiers IMPATT Amplifier STRACT (Continue on reverse side if necessary and identify by block number)  $oldsymbol{\lambda}$  This program had as its objective the development of an X-band GaAs FET power amplifier. Advances were made in materials, device, and microwave circuit technology during the course of the amplifier development. Devices with 2400 µm gate width from nine device runs (seven different epitaxial slices) produced I W or more at 9 GHz with 4 dB gain and power-added efficiencies of 20 to 30%. Two device chips were connected in parallel to give a total gate width of 4800  $\mu m$ . In this case, an output power of 2.5 W was DD 1 JAN 73 1473 EDITION OF 1 NOV 65 IS OBSOLETE OVER UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered) 403 833-

And the second second

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

achieved at 8 GHz with 4.0 dB gain and 25% power-added efficiency.

An output power (cw) of 360 mW was achieved with a gain of 20.5 dB at 9.3 GHz for a three-stage FET amplifier. The 3 dB bandwidth was 1.0 GHz (8.9 to 9.9 GHz). This performance exceeded the contract goals. A microstrip hybrid FET (three-stage)/IMPATT amplifier was fabricated that had an output power of 1.2 W with 26 dB gain at 9.5 GHz with a 700 MHz 3 dB bandwidth. This amplifier also met the performance goals. Two three-stage FET amplifiers and two FET/IMPATT hybrid amplifiers were delivered to AFAL.

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE(When Data Entered)

#### FOREWORD

This project was initiated by the Air Force Avionics Laboratory and was under the direction of Dr. Chern Huang (AFAL/DHM). This report is a summary of the entire research program conducted from 1 March 1975 to 30 November 1975.

The work described herein was carried out at the Central Research Laboratories of Texas Instruments Incorporated, 13500 North Central Expressway, Dallas, Texas 75222. The program was initially directed by Dr. D. N. McQuiddy and was completed under the direction of Dr. W. R. Wisseman. Other principal contributors were Dr. R. L. Adams, Dr. H. M. Macksey, Dr. V. Sokolov, and Dr. H. Q. Tserng.

| Project Monitor          | Air Force Avionics Laboratory<br>Dr. C. Huang (DHM)        |  |  |

|--------------------------|------------------------------------------------------------|--|--|

| Contract Number          | F33615-75-C-1123                                           |  |  |

| Project Number           | 69ск                                                       |  |  |

| Task Number              | 0135                                                       |  |  |

| Contractor Report Number | 08-76-04                                                   |  |  |

| Reporting Period         | 1 March 1975 through 30 November 1975                      |  |  |

| Submitted                | 31 December 1975                                           |  |  |

| Authors                  | W. R. Wisseman, R. L. Adams,<br>H. M. Macksey, V. Sokolov, |  |  |

H. Q. Tserng

### TABLE OF CONTENTS

| SECTION |      | PAC                                                        | <u>E</u> |

|---------|------|------------------------------------------------------------|----------|

| I       | INTR | ODUCTION AND SUMMARY                                       | 1        |

| ΙI      | DEVI | CE DESIGN CONSIDERATIONS                                   | 3        |

|         | Α.   | Basic Structure, Device Physics, and<br>Equivalent Circuit | 3        |

|         | Β.   | Device Parameter Selection                                 | 5        |

| III     | MATE | RIALS GROWTH AND CHARACTERIZATION                          | Э        |

|         | Α.   | Substrate Characterization                                 | Э        |

|         |      | 1. Specifications                                          | 9        |

|         |      | 2. Evaluation                                              | 9        |

|         | Β.   | Epitaxial Growth                                           | I .      |

|         |      | 1. Growth Process                                          | I        |

|         |      | 2. Growth Procedure 1                                      | 3        |

|         |      | 3. Structures Grown                                        | 5        |

|         |      | 4. Characterization 18                                     | 8        |

|         |      | 5. Optimization                                            | Э        |

|         |      | 6. Discussion 1                                            | Э        |

| ΙV      | DEVI | CE FABRICATION                                             | 1        |

|         | Α.   | Review of Structures Investigated                          | 1        |

|         |      | 1. Planar Device Structures                                | 1        |

|         |      | 2. Nonplanar Device Structure                              | 6        |

|         | Β.   | Process Studies                                            | 0        |

|         |      | 1. Ohmic Contacts                                          | 0        |

|         |      | 2. Recessed Gate                                           | 6        |

|         |      | 3. Channel Conductance                                     | 8        |

|         |      | 4. Schottky Gate Metallization                             | 3        |

|         |      | 5. Gate Finger Width                                       | 3        |

|         | с.   | Fabrication Process                                        | 6        |

| V       | EVAL | _UATION                                                    | 9        |

|         | Α.   | Low Frequency Evaluation                                   | 9        |

|         |      | 1. Photomask Evaluation Features (Test Bar) 4              | 9        |

|         |      | 2. Visual Screen and Reliability                           | 9        |

٧

PRECEDING PAGE, BLANK NOT FILMED

## TABLE OF CONTENTS

### (Continued)

| SECTION |      |       |                                       | PAGE |

|---------|------|-------|---------------------------------------|------|

|         |      | 3.    | Capacitance-Voltage (C-V) Measurement | 51   |

|         |      | 4.    | Current-Voltage (I-V) Measurement     | 51   |

|         | Β.   | Micr  | rowave Evaluation                     | 53   |

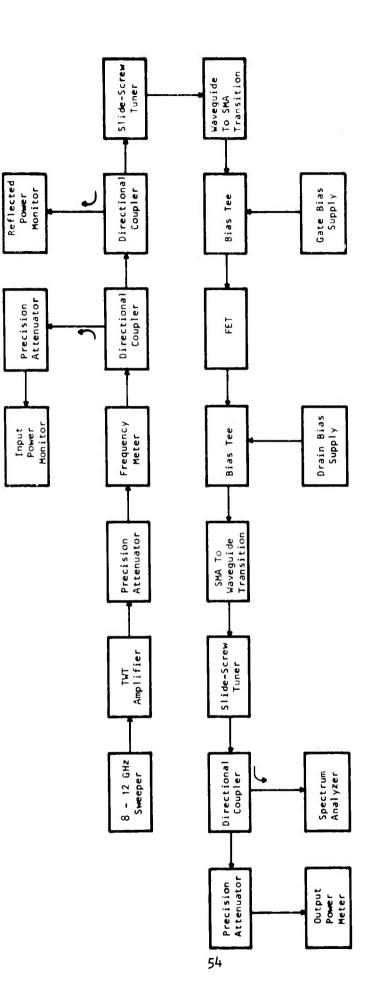

|         |      | 1.    | Test Circuit Description              | 53   |

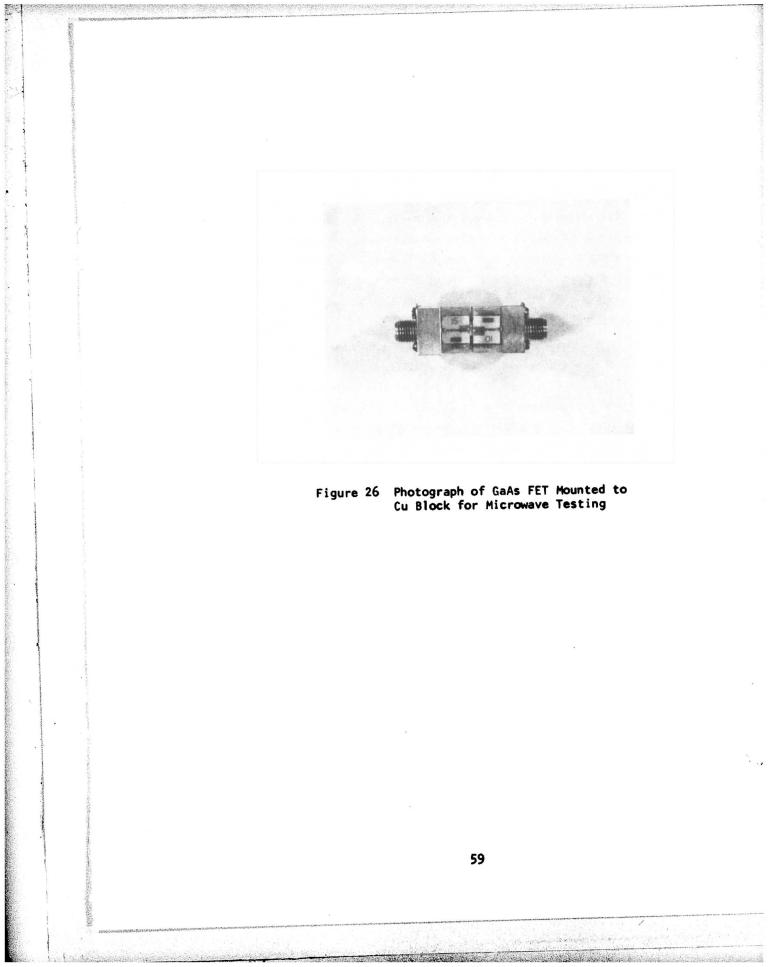

|         |      | 2.    | Device Mounting Configuration         | 55   |

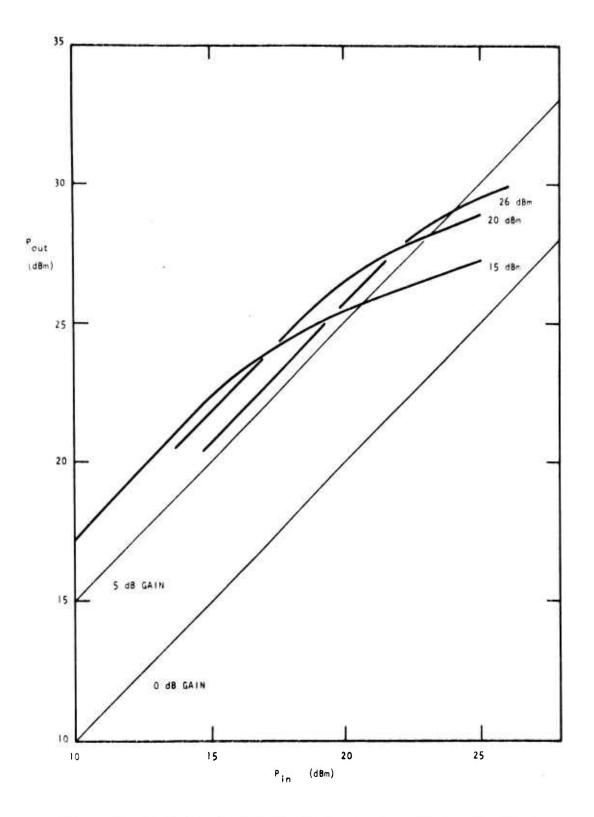

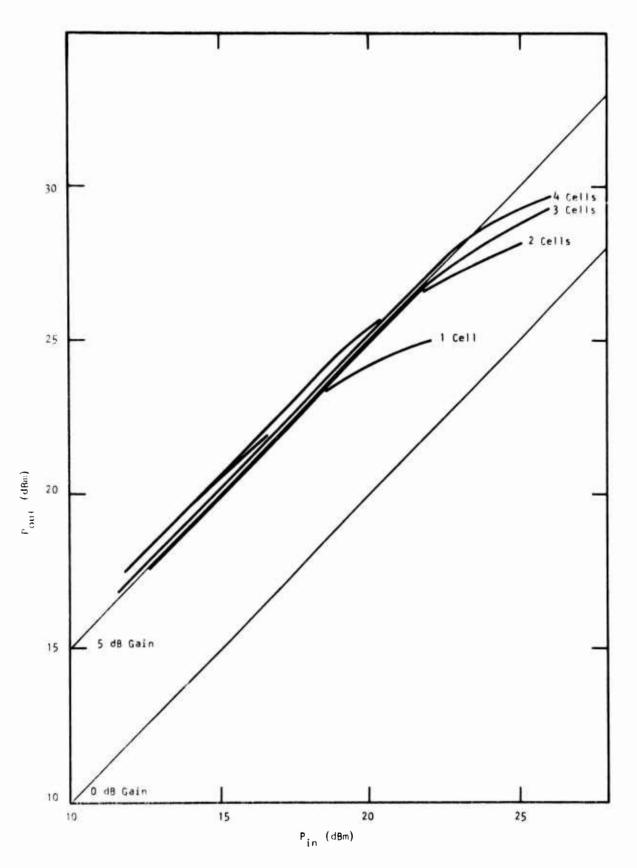

|         |      | 3.    | Microwave Performance                 | 60   |

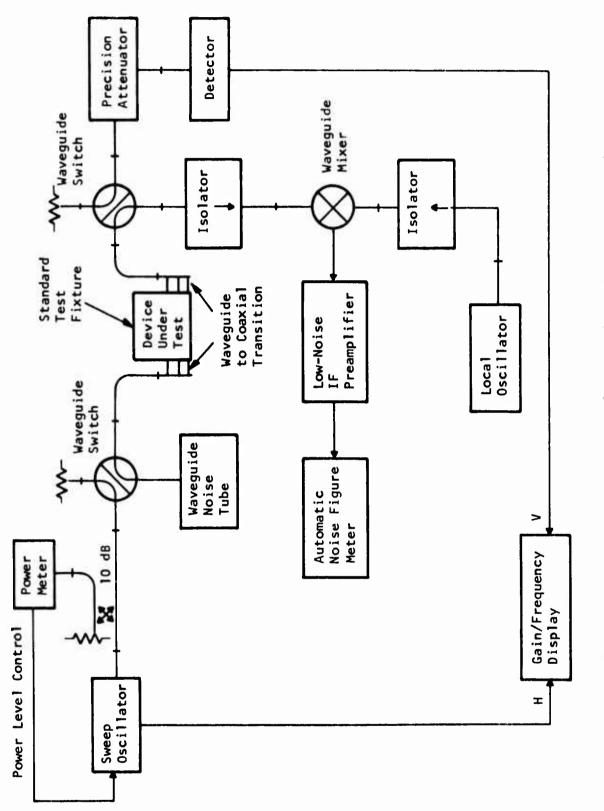

|         |      | 4.    | Noise Measurement                     | 67   |

| VI      | MICR | OSTRI | IP AMPLIFIER DEVELOPMENT              | 71   |

|         | Α.   | Devi  | ice Characterization                  | 73   |

|         | Β.   | FET   | Amplifier Design Theory               | 78   |

|         | С.   | Sing  | gle-Stage FET Amplifier               | 80   |

|         | D.   | Mult  | tistage Amplifiers                    | 80   |

|         | Ε.   | Modu  | ule Integration                       | 83   |

| VII     | CONC | LUSIO | ONS AND RECOMMENDATIONS               | 104  |

|         | REFE | RENCE | ES                                    | 105  |

## LIST OF ILLUSTRATIONS

| FIGURE |                                                                                                                          | PAGE |

|--------|--------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Simplified Sketch of the Basic GaAs FET Device Structure                                                                 | 4    |

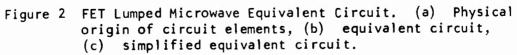

| 2      | FET Lumped Microwave Equivalent Circuit                                                                                  | 6    |

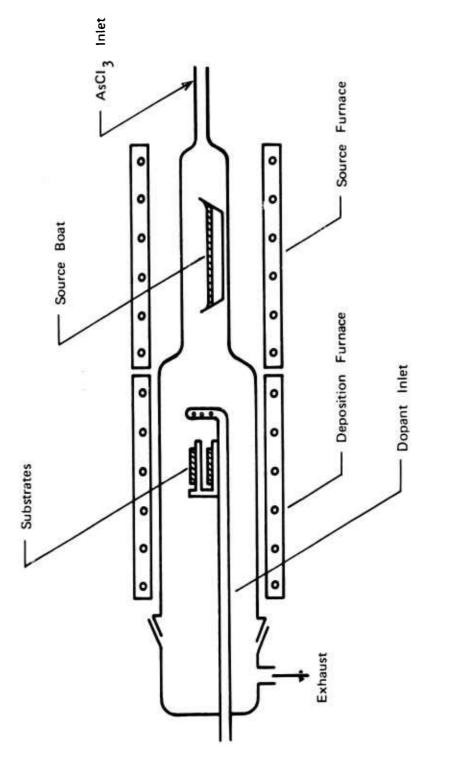

| 3      | Schematic of Epitaxial Reactor                                                                                           | 12   |

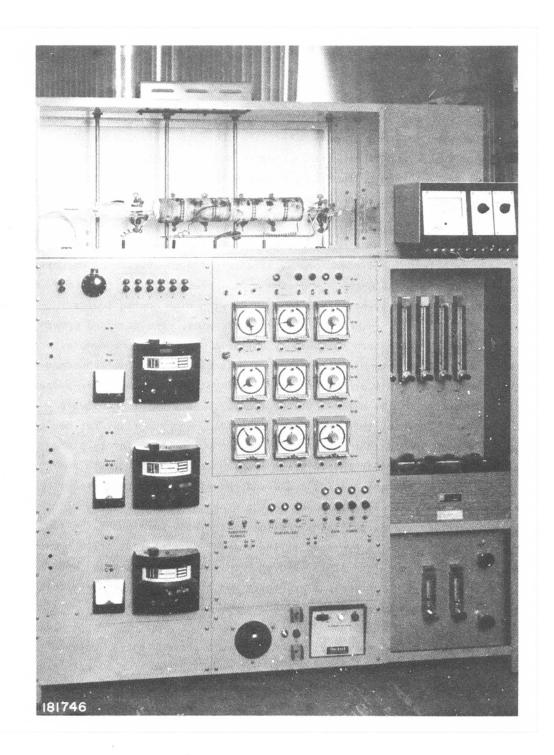

| 4      | Automatic GaAs Epitaxial Reactor                                                                                         | 14   |

| 5      | Cleaved and Etched Cross Section of FET Slice with<br>Semi-Insulating Layer                                              | 17   |

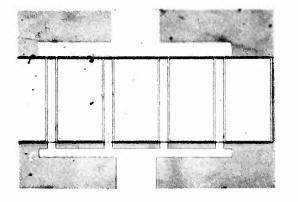

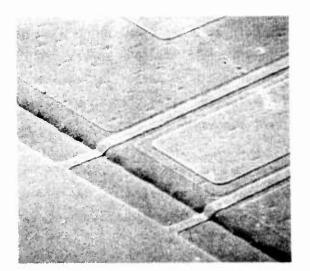

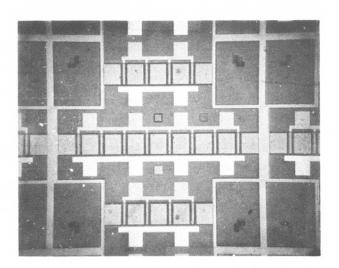

| 6      | Photographs of 2000 µm Gate Width GaAs FET                                                                               | 22   |

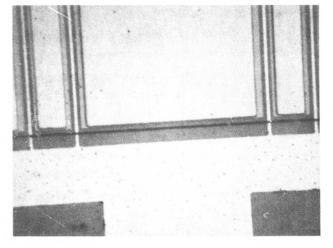

| 7      | Photographs of 1200 μm and 2400 μm Gate Width GaAs FETs<br>Fabricated from E-Beam Delineated Photomasks                  | 23   |

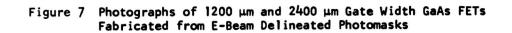

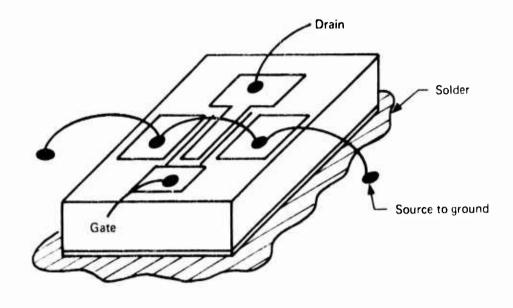

| 8      | Four-Cell GaAs Power FET                                                                                                 | 25   |

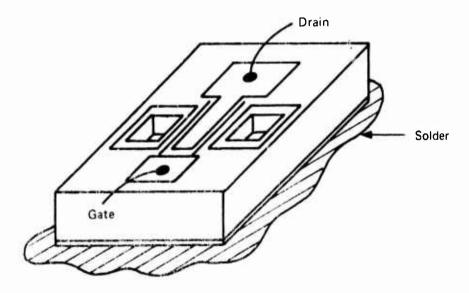

| 9      | Double-Source FET with Conventional Bond Wires to Ground<br>Compared with Plated-Through Interconnected Source Grounding | 27   |

### LIST OF ILLUSTRATIONS

(Continued)

## FIGURE

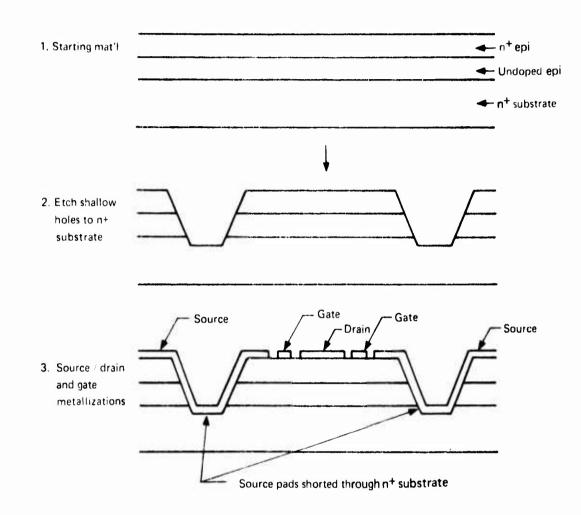

| 10 | Schematic Cross Section of Structure for Plated-Through<br>Ground Source Interconnection                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------|

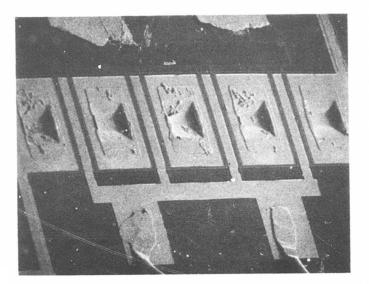

| 11 | Plated-Through Ground Source Pad Interconnection                                                                                |

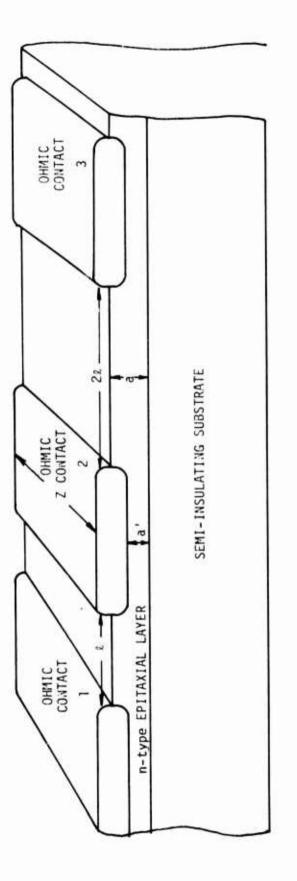

| 12 | Contact Resistance Measurement Geometry                                                                                         |

| 13 | Comparison of Current-Voltage Characteristics of Devices<br>Having AuGe/Ni Ohmic Contacts and AgInGe Ohmic Contacts             |

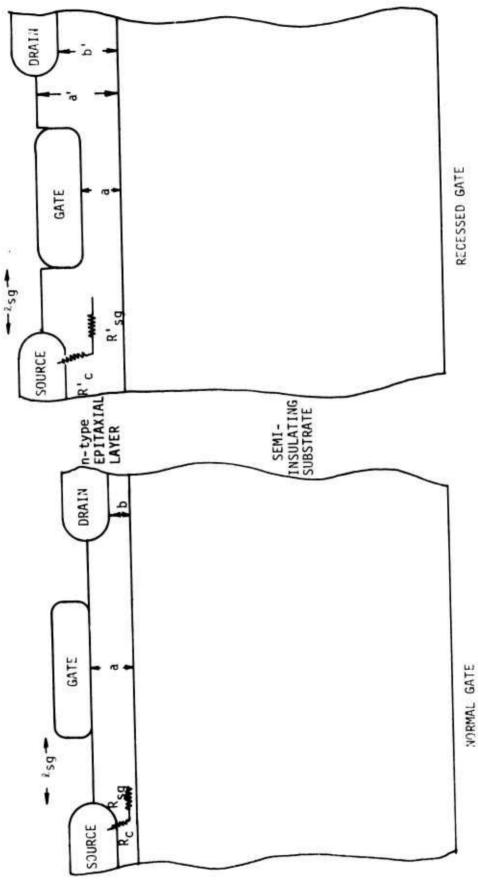

| 14 | Effect of Recessing the Gate on Parasitic Resistance                                                                            |

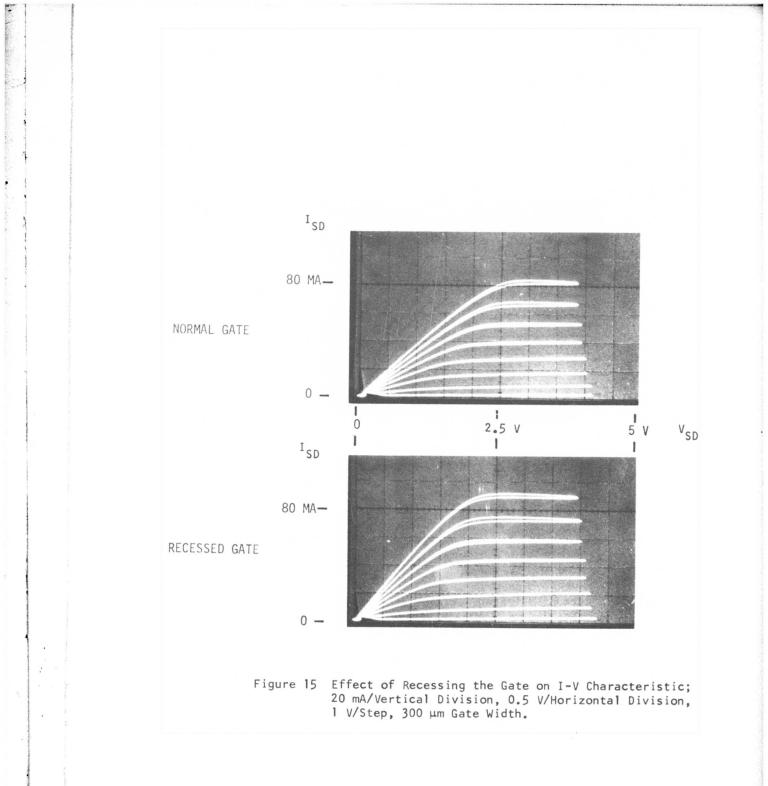

| 15 | Effect of Recessing the Gate on I-V Characteristic                                                                              |

| 16 | Current-Voltage Characteristic of GaAs FET Having a Total Gate Width of 1200 $\mu m$                                            |

| 17 | Analysis of Elements Contributing to Source-Drain Resistance<br>of GaAs FET of Figure 16                                        |

| 18 | Reverse Saturation Current as a Function of Anneal Temperature<br>of Al and Cr/Au Schottky Barriers                             |

| 19 | Device Gain at 9 GHz as Function of Aluminum Gate<br>Metallization Thickness                                                    |

| 20 | Planar Device Fabrication Process                                                                                               |

| 21 | GaAs FET Test Bar                                                                                                               |

| 22 | Carrier Concentration vs Depth for a Number of GaAs FET Slices 52                                                               |

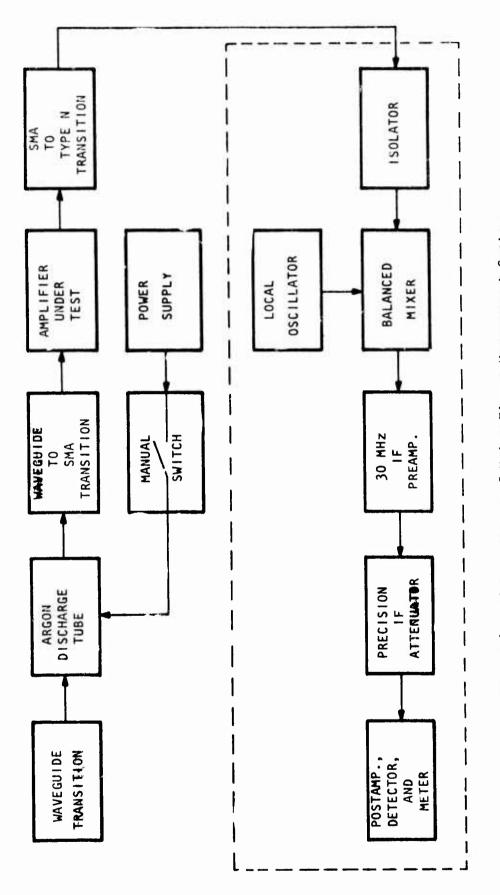

| 23 | Block Diagram of Gain and Output Power Measurement<br>Equipment                                                                 |

| 24 | SEM of Four-Cell GaAs FET Mounted in the Flipped Configuration<br>on a Cu Block                                                 |

| 25 | SEM of Four-Cell GaAs FET Mounted in the Upright<br>Configuration on a Cu Block                                                 |

| 26 | Photograph of GaAs FET Mounted to Cu Block for<br>Microwave Testing                                                             |

| 27 | Dependence of 9 GHz Performance on Tuning for 2400 $\mu$ m<br>Gate Width GaAs FET V <sub>ds</sub> = 8 V, V <sub>g</sub> = -3 V  |

| 28 | 9 GHz Performance of One to Four Cells of the Same GaAs FET<br>Tuned for Maximum Output Power at 4 dB Gain                      |

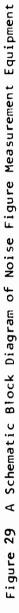

| 29 | A Schematic Block Diagram of Noise Figure Measurement<br>Equipment                                                              |

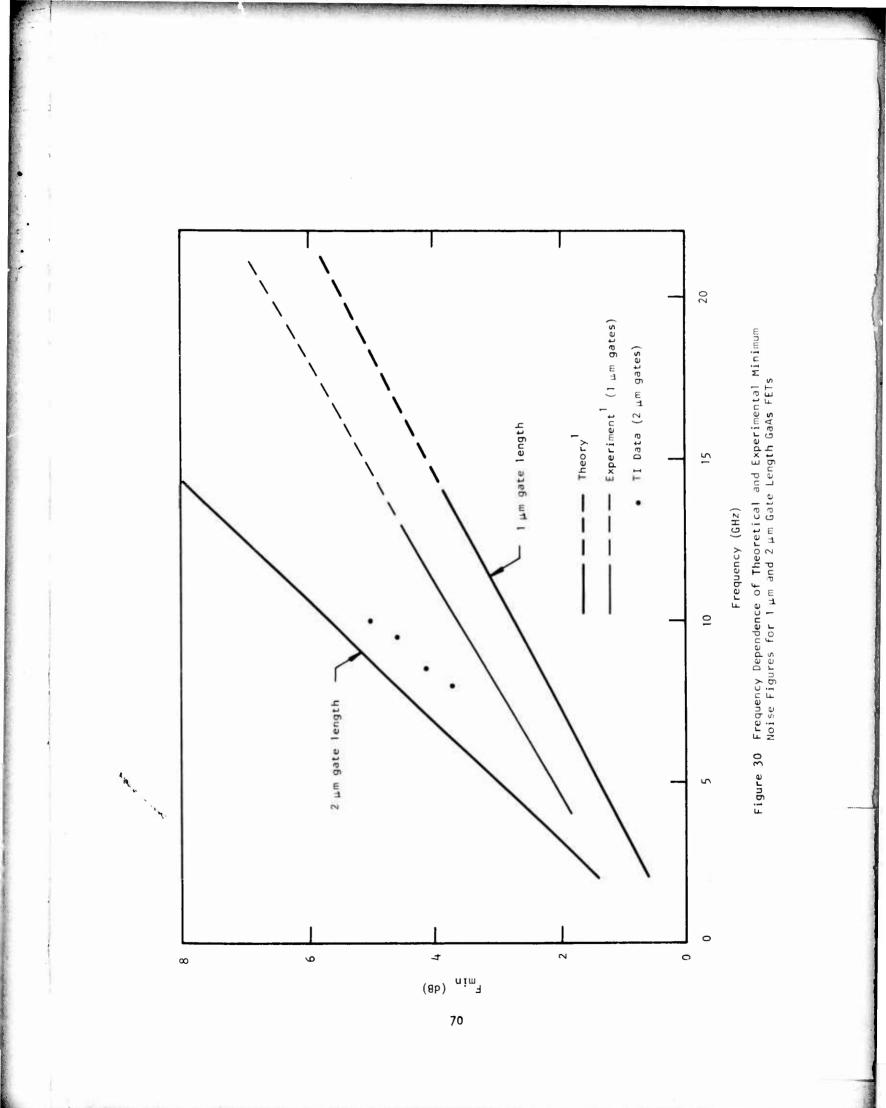

| 30 | Frequency Dependence of Theoretical and Experimental Minimum Noise Figures for 1 $\mu m$ and 2 $\mu m$ Gate Length GaAs FETs 70 |

## LIST OF ILLUSTRATIONS

(Continued)

| FIGURE |                                                                                                            | PAGE |

|--------|------------------------------------------------------------------------------------------------------------|------|

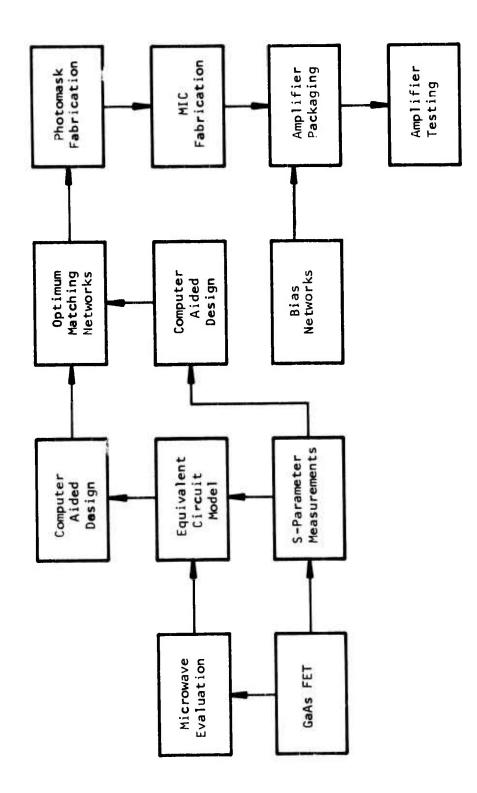

| 31     | Flow Chart of the FET Amplifier Design Task                                                                | 72   |

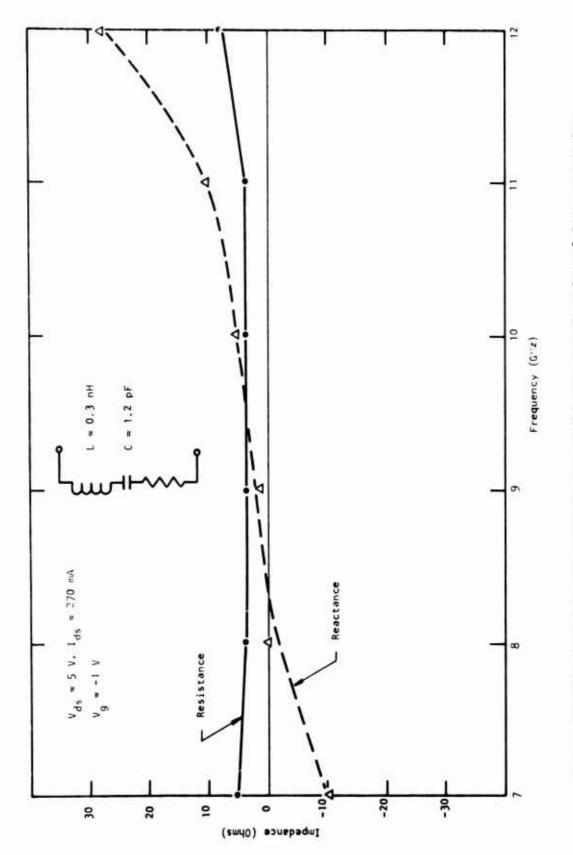

| 32     | Input Impedance of a 1200 $\mu m$ Gate Width FET as a Function of Frequency Under Optimum Bias Conditions  | 75   |

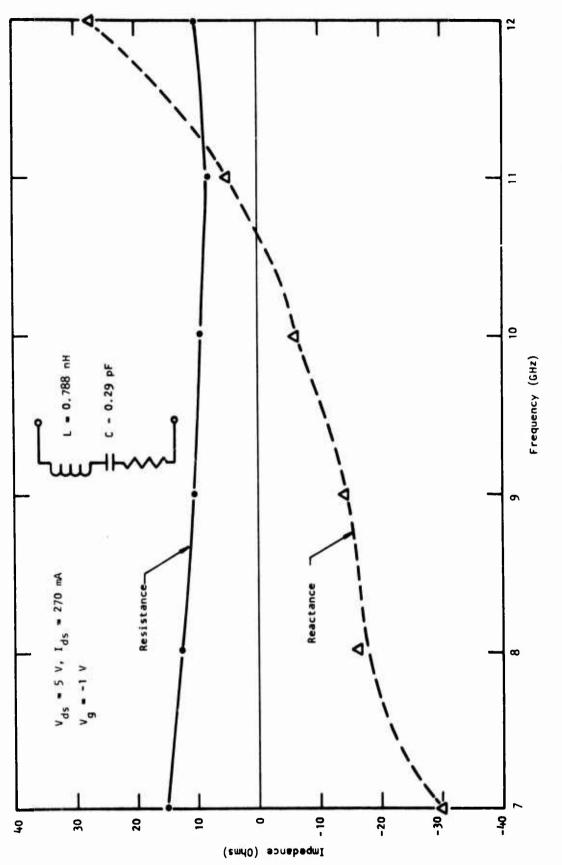

| 33     | Output Impedance of a 1200 $\mu m$ Gate Width FET as a Function of Frequency Under Optimum Bias Conditions | 76   |

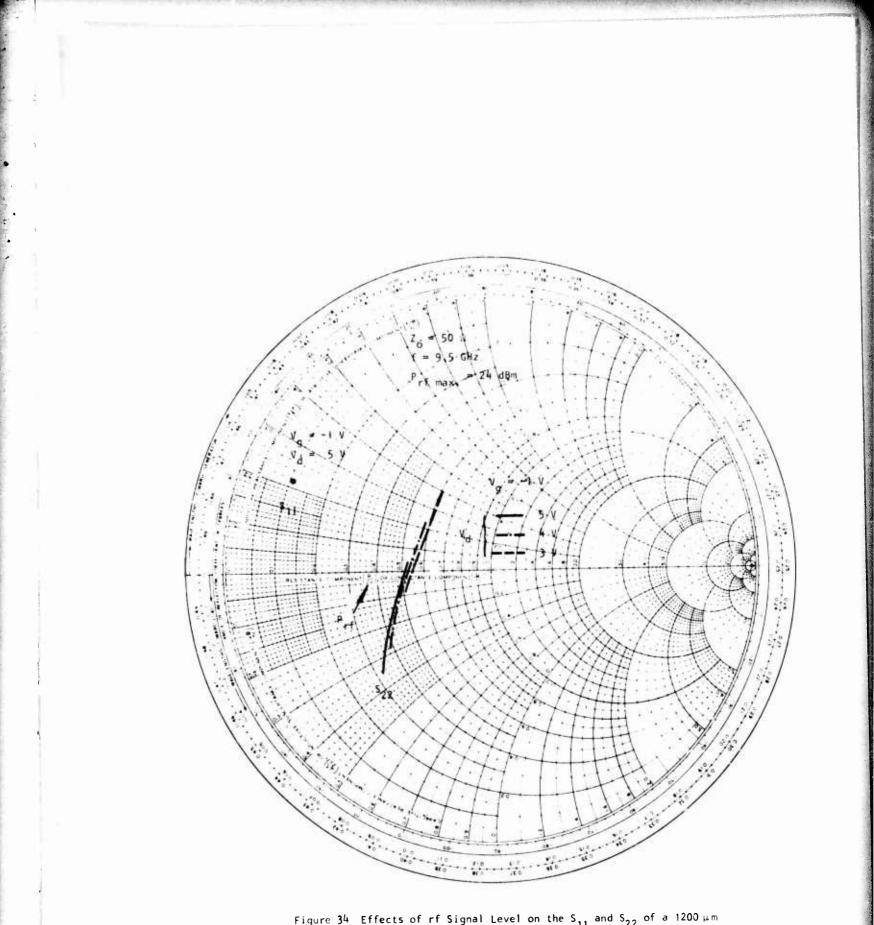

| 34     | Effects of rf Signal Level on the S $_{11}$ and S $_{22}$ of a 1200 $\mu m$ Gate Width FET                 | 77   |

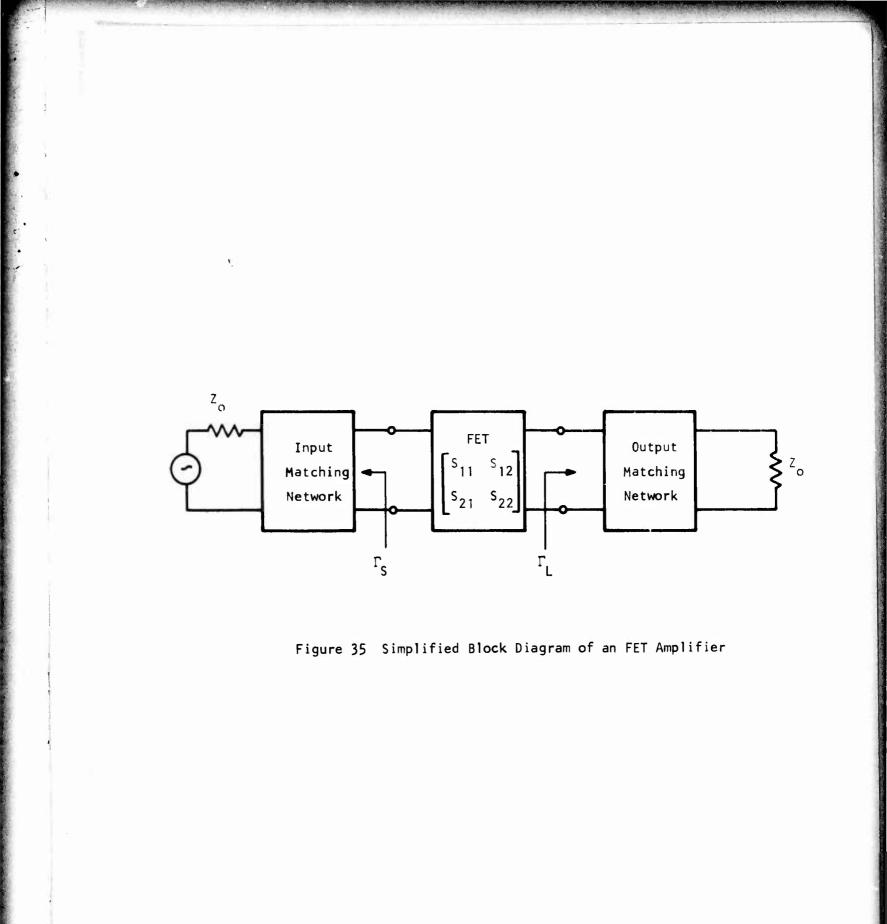

| 35     | Simplified Block Diagram of an FET Amplifier                                                               | 79   |

| 36     | A Simple Microstrip FET Amplifier                                                                          | 81   |

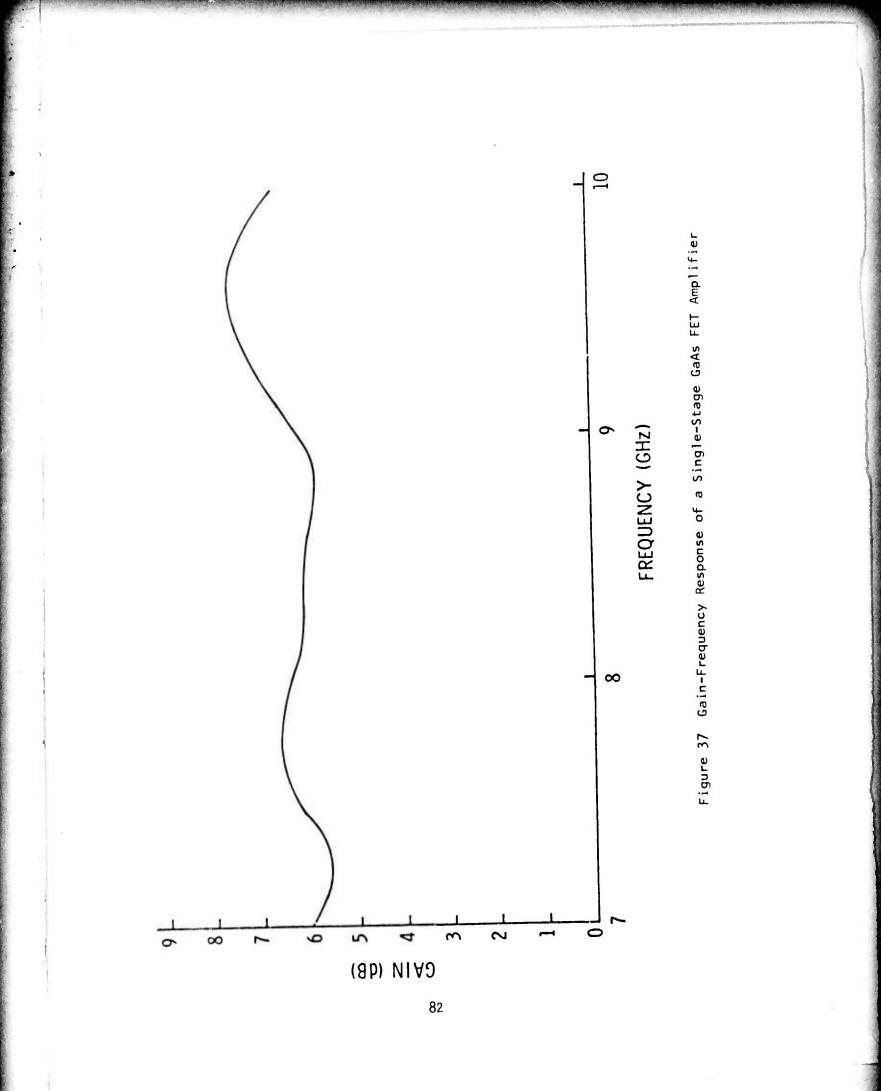

| 37     | Gain-Frequency Response of a Single-Stage GaAs<br>FET Amplifier                                            | 82   |

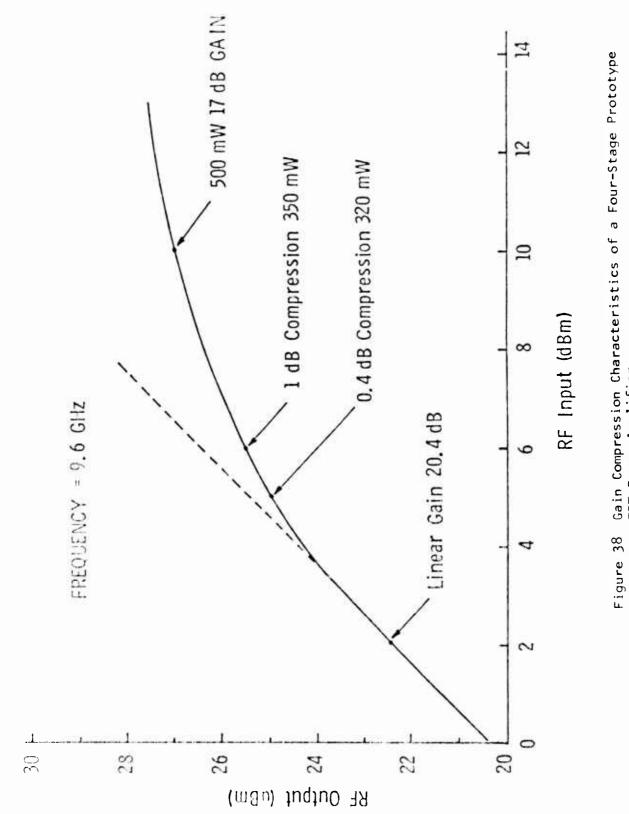

| 38     | Gain Compression Characteristics of a Four-Stage<br>Prototype FET Power Amplifier                          | 84   |

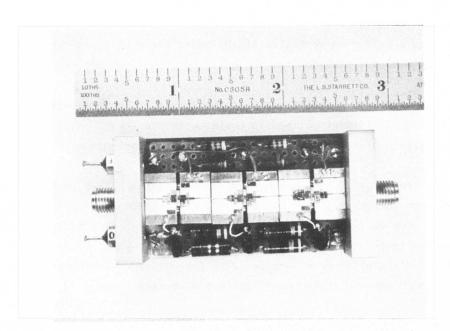

| 39     | Photograph of Three-Stage Power FET Amplifier                                                              | 85   |

| 40     | An FET (Three-Stage)/IMPATT Hybrid Amplifier                                                               | 87   |

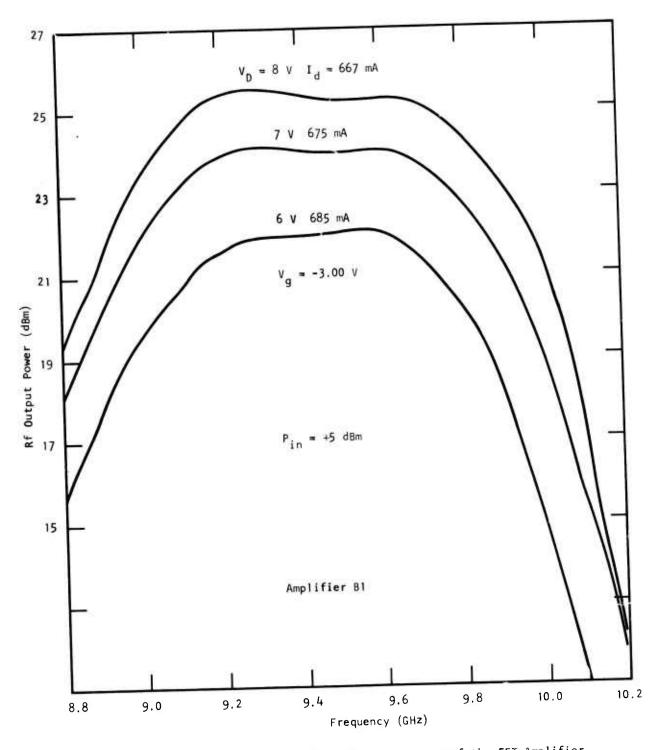

| 41     | Output Power Versus Frequency Response of the FET<br>Amplifier Shown in Figure 39                          | 88   |

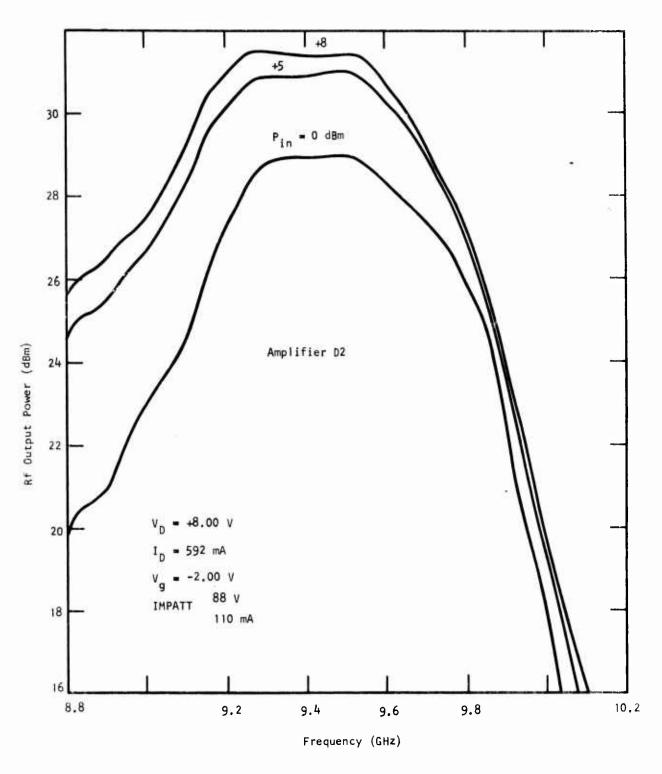

| 42     | Output Power Versus Frequency Response of the FET/IMPATT<br>Hybrid Amplifier Shown in Figure 40            | 89   |

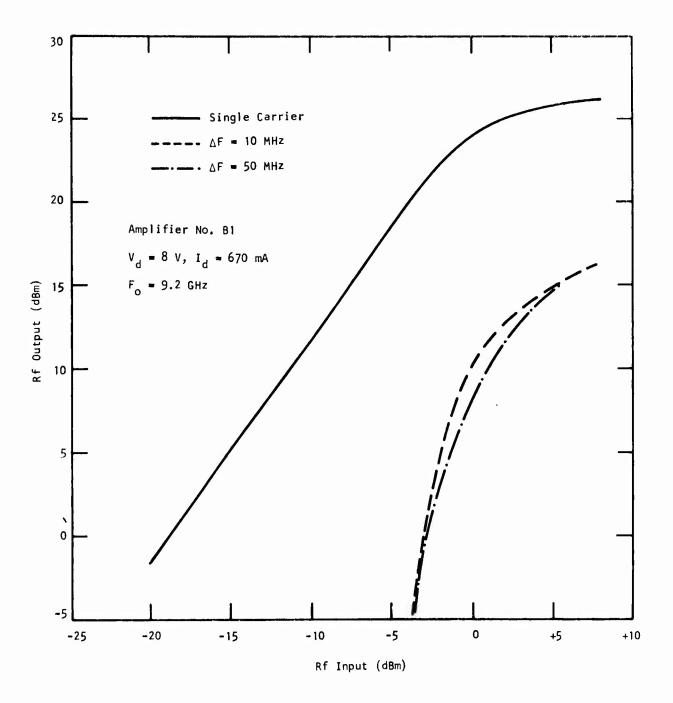

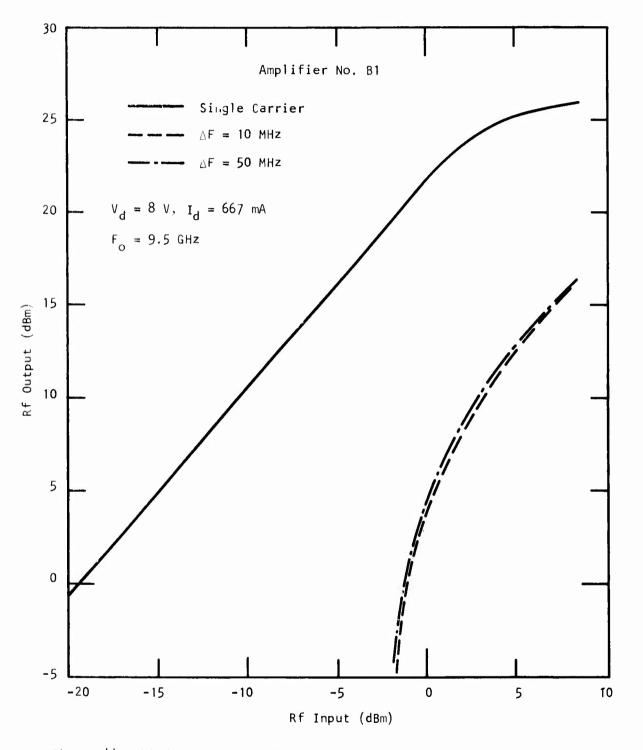

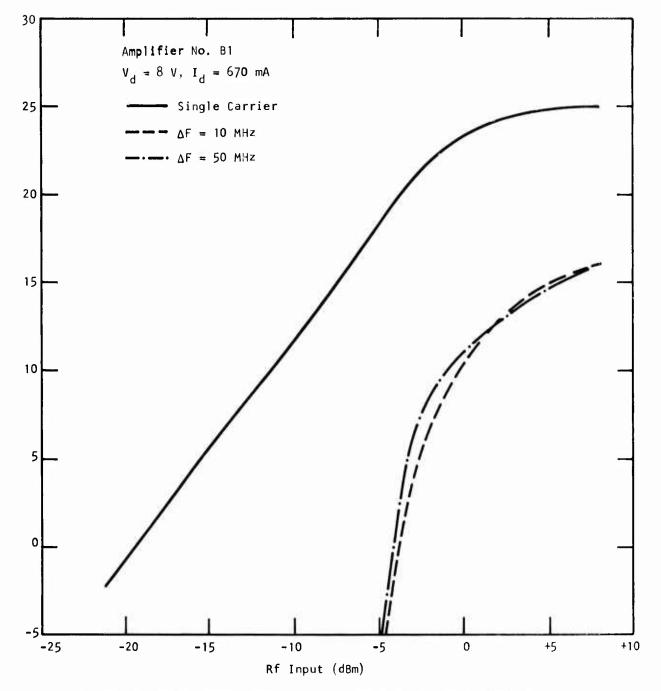

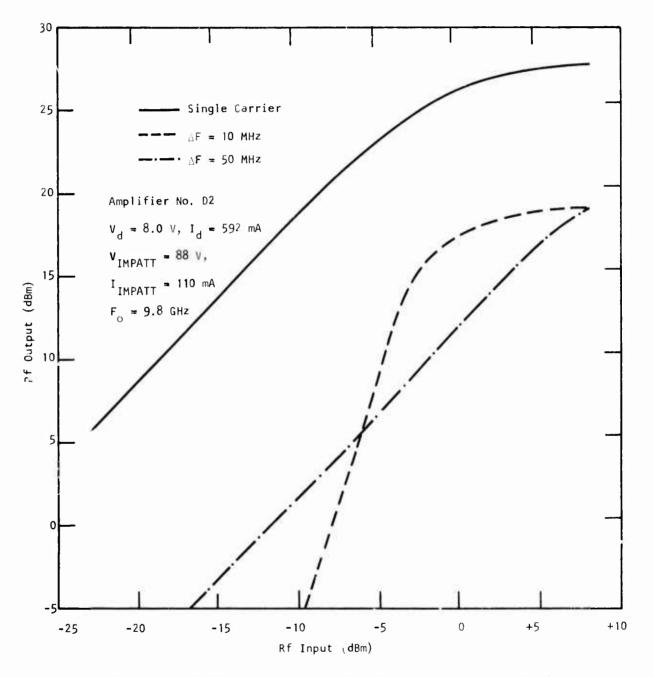

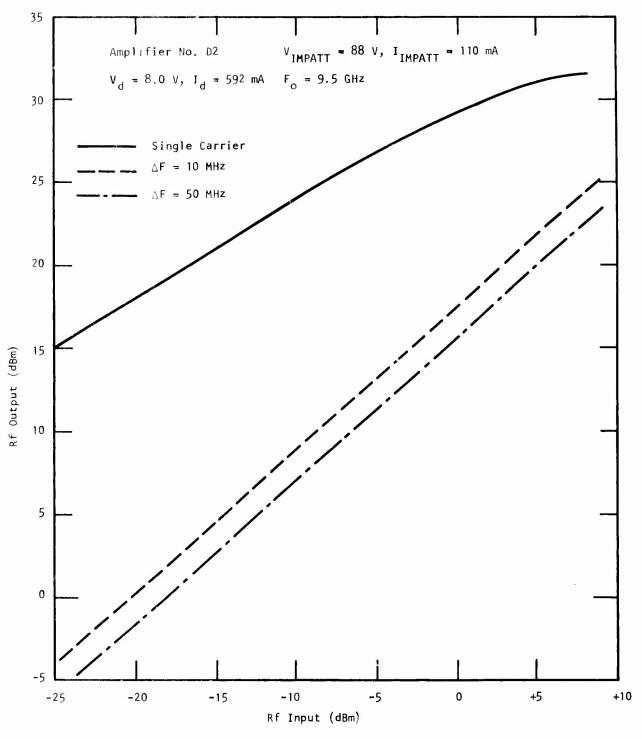

| 43     | Third-Order Intermodulation Product vs Input Level at<br>Lower Band Edge of the Three-Stage FET Amplifier  | 91   |

| 44     | Third-Order Intermodulation Product vs Input Level at Band<br>Center of the Three-Stage FET Amplifier      | 92   |

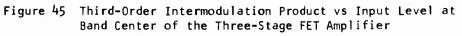

| 45     | Third-Order Intermodulation Product vs Input Level at<br>Band Center of the Three-Stage FET Amplifier      | 93   |

| 46     | Third-Order Intermodulation Product vs Input Level at the Lower Band Edge of the Hybrid Amplifier          | 94   |

| 47     | Third-Order Intermodulation Product vs Input Level at the Upper Band Edge of the Hybrid Amplifier          | 95   |

| 48     | Third-Order Intermodulation Product vs Input Level at the Band Center of the Hybrid Amplifier              | 96   |

| 49     | Block Diagram of Noise Figure Measurement System                                                           | 99   |

|        |                                                                                                            |      |

The Area and a star

## LIST OF TABLES

| TABLE |                                                                                                                        | PAGE |

|-------|------------------------------------------------------------------------------------------------------------------------|------|

| 1     | Measured Contact Resistance for Different Ohmic Contact Alloys                                                         | 34   |

| 2     | Dependence of Output Power on Frequency and Number of Cells Connected for a GaAs Power FET (Gate Length - 1.8 $\mu m)$ | 56   |

| 3     | GaAs Power FET Performance                                                                                             | 61   |

| 4     | Dependence of Output Power on Frequency and Number of Cells Connected for a 2.4 $\mu m$ Gate Length GaAs FET           | 65   |

| 5     | Effect of GaAs Power FET Mounting Schemes on 9 GHz<br>Performance                                                      | 66   |

| 6     | Minimum Noise Figures of GaAs Power FETs Mounted on Cu Blocks                                                          | 69   |

| 7     | X-Band GaAs FET Amplifier Specifications                                                                               | 71   |

Contraction of the

A TRANSPORT

#### SECTION I

#### INTRODUCTION AND SUMMARY

This is the final report for a nine-month program carried out under Contract No. F33615-75-C-1123, for the development of an FET power amplifier. The amplifier is designed to operate at 9.5 GHz with a 600 MHz 3 dB bandwidth and 20 dB gain and to deliver 300 mW cw output power. The FET amplifier is to be used with an IMPATT single-stage amplifier to give an output power of 1.2 W with 26 dB gain over the same frequency band.

Although the end goal of this program was the development of multistage amplifiers that meet the specifications given above, a major device development effort was also required, since suitable covices for the amplifier were not available at the outset of the program.

The program was divided into three phases: (1) GaAs epitaxial growth and transistor process optimization, (2) large signal transistor circuit development, and (3) multistage amplifier design. Significant progress was made on all three phases of the program; however, throughout most of the program the major effort was devoted to Phase I. FET microwave performance was well below that required to meet the amplifier specifications until the last one and a half to two months of the program. At that point, the device mounting scheme was changed, and a significant improvement in microwave performance was achieved. With devices mounted in the new configuration, the microwave performance improved to the extent that it became relatively straightforward to design and build amplifiers that met the program goals.

Some of the major accomplishments that were made in this program include:

- Establishment of the materials growth and device fabrication capabilities required for the development of high power GaAs FETs.

- (2) Development of a device mounting scheme that can be reproducibly achieved with high bonding yield and that gives state-of-the-art microwave performance.

- (3) Achievement of high power performance at X-band with devices from many different epitaxial slices. At the completion of the program, nineslices had yielded devices that delivered 1 watt or more at 9 GHz with 4 dB gain.

- (4) Attainment of the highest FET output power presently reported at X-band:

2.5 watts at 8 GHz with 4 dB gain and 25% power-added efficiency (4800 μm gate width).

- (5) Development of a three-stage FET amplifier that exceeded the performance specifications. The amplifier delivers 360 mW of cw output power at 9.3 GHz. The gain is 20  $\pm$  0.5 dB over the 9.1 to 9.8 frequency band, and the 3 dB bandwidth is 1.0 GHz.

- (6) Development of a hybrid FET (three-stage)/IMPATT amplifier that meets the performance specifications. The amplifier delivers 1.2 W with 26 dB gain at 9.5 GHz with a 3 dB bandwidth of 9.1 to 9.8 GHz.

The remainder of this report is organized as follows. Device design is covered in Section II. Section III reports the details of the work on material growth and characterization. Device fabrication is discussed in Section IV. Section V describes device evaluation and includes a summary of the most significant microwave performance results. The microstrip amplifier development is covered in Section VI, and performance results are given in this section for the amplifiers that were delivered at the completion of the program. Finally, conclusions and recommendations are given in Section VII.

#### SECTION II

#### DEVICE DESIGN CONSIDERATIONS

In this section the basic physics of GaAs FET operation is described, and a discussion of the factors influencing the choice of the various device parameters is given. The values chosen for the present power FET design are enumerated.

#### A. Basic Structure, Device Physics, and Equivalent Circuit

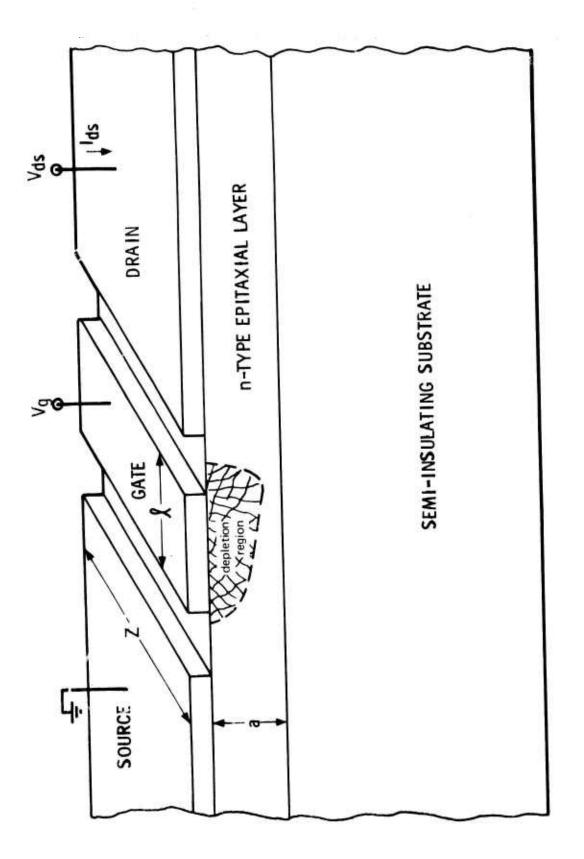

To understand the operation of the GaAs FET, refer to the simplified sketch of the basic device structure shown in Figure 1. An n-type layer of uniform shallow donor doping N<sub>d</sub> and thickness a is grown epitaxially on an insulating substrate. Ohmic "source" and "drain" contacts of width Z are placed as shown. Between them is a Schottky barrier "gate" of length  $\ell$ . In normal operation the source is grounded and a positive voltage + V<sub>ds</sub> is applied to the drain, causing current I<sub>ds</sub> to flow from drain to source under the gate. The n-type GaAs under the gate is depleted of carriers in the Schottky barrier space-charge region, with a negative gate voltage V<sub>g</sub> increasing the depletion depth. Thus, changes in gate voltage modulate the drain current I<sub>ds</sub>. If V<sub>g</sub> is large enough, the depletion region of the gate reaches the insulating substrate, and conduction is entirely "pinched off" ( $|V_{g}| \equiv V_{p}$ ).

As  $V_{ds}$  increases with  $V_g = 0$ ,  $I_{ds}$  increases linearly at first, and then saturates at a current  $I_{dss}$  beginning at a threshold voltage  $V_T$ . This saturation is caused by the forward drain bias effectively reverse-biasing the gate and pinching off the conducting channel. Also contributing to current saturation is the fact that at higher drain voltages the electrons are excited into the low mobility (100) conduction band minima, causing their velocity to saturate. The saturation current decreases as  $V_g$  is made more negative. In actual operation, the dc values of  $V_{ds}$  and  $V_g$  are fixed such that the device is biased into saturation, an rf signal is applied between the gate and source, and the amplified signal is available across the drain and source.

Figure 1 Simplified Sketch of the Basic GaAs FET Device Structure

One of the reasons the FET is superior to bipolar devices at high frequencies is that it is a majority carrier device. The response time is not limited by the charge storage capacitance of p-n junctions or long minority carrier diffusion times. The essential limitation is the charging of the Schottky barrier (fast compared to p-n junctions) and the electron transit time from source to drain. The transit time is very short, since the carriers are drifting rather than diffusing. Even relatively modest dimensions such as a 2  $\mu$ m gate length and 6  $\mu$ m source-drain spacing give a maximum frequency of oscillation of approximately 30 GHz. A 1/2  $\mu$ m gate length device would have a maximum frequency of oscillation approaching 100 GHz. The major source of noise in a bipolar transistor is shot noise in the collector-base junction. This, of course, is not present with the FET, and very low noise operation is possible.

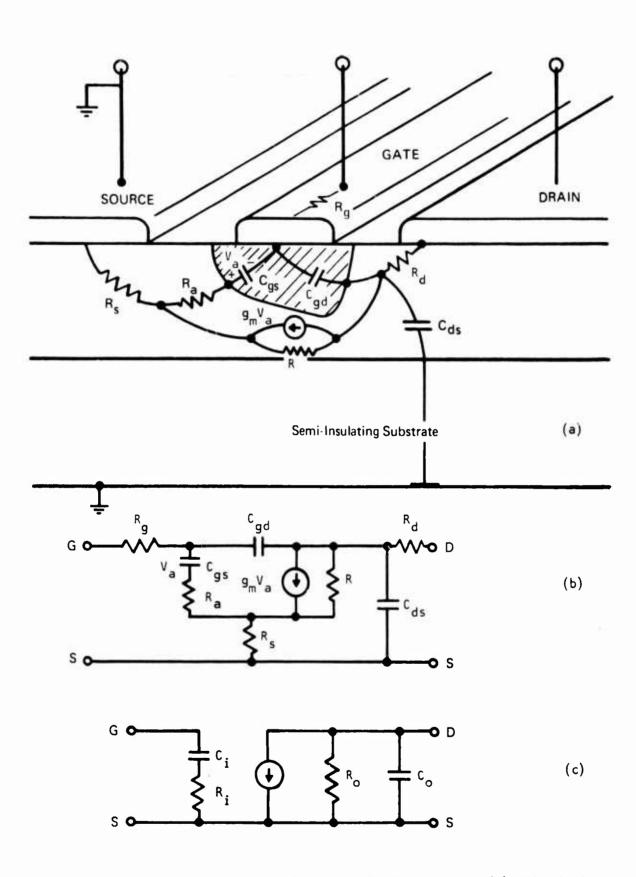

An equivalent circuit is often derived for active semiconductor devices to aid in impedance matching, analysis of microwave results, etc. The physical origin of the equivalent circuit elements for the GaAs FET is shown in Figure 2(a). The circuit itself is shown in Figure 2(b). In this figure R<sub>g</sub> is the (parasitic) resistance of the gate metal; R<sub>s</sub> is the (parasitic) source-gate (including contact) resistance; R<sub>d</sub> is the (parasitic) drain-gate (including contact) resistance; V<sub>a</sub> is the applied voltage and g<sub>m</sub> is the device transconductance; C<sub>gs</sub> is the gate-tosource capacitance (capacitance of gate depletion region); R<sub>i</sub> is the resistance; R is the reciprocal of the drain-to-source conductance; and C<sub>ds</sub> is the drain-tosource capacitance. Because of the very low feedback capacitance C<sub>gd</sub> and the high channel resistance R, the simple equivalent circuit shown in Figure 2(c) can be used for design calculations.

#### B. Device Parameter Selection

In GaAs power FET design, there are several constraints on the selection of device parameters, and trade-offs must be made between these constraints in

And the state

arriving at an optimum device structure. The transconductance and maximum frequency of oscillation ( $f_{max}$ ) increase with increasing carrier concentration, but the breakdown voltage and epitaxial thickness for a given pinch-off voltage decrease. Current-carrying capacity increases with epitaxial thickness, but consequent increasing pinch-off voltage results in higher operating voltages with resultant increased intervalley scattering noise.<sup>1</sup> In addition, the higher voltage may approach the breakdown voltage of the material. The net result of these considerations is that for high power X-band GaAs FETs, a donor concentration  $N_d \sim 1 \times 10^{17}$  cm<sup>-3</sup> and epitaxial thickness a  $\sim 0.3 \,\mu\text{m}$  ( $V_p \sim 5V$ ) are employed.

Decreasing the gate length increases  $f_{max}$  and results in devices with higher gain and lower noise figure at a given frequency. In addition, the gate capacitance is decreased, making the input impedance easier to match. Shorter gate length devices are difficult to fabricate using conventional photolithography, however. A gate length of 2  $\mu$ m has been chosen because it provides devices having useful gain at X-band without excessive photolithographic alignment problems.

Increasing the total gate width increases the device power-handling capability, but the increased gate-source capacitance and reduced real impedance  $[R_a \text{ of Figure 2(b)}]$  make the input impedance more difficult to match. In addition, there is a reduced device yield with large gate widths due to gate breakage and shorting. The individual gate stripes must be short enough so that the attenuation and phase shift of a signal moving along the stripe (acting as an RC transrission line) is not significant. A longer gate stripe will require a thicker metallization for its resistance to remain unchanged. For X-band power amplification a total device gate width of 2400  $\mu$ m has been chosen. An N<sub>d</sub> and a above this gives a device current of several hundred milliamps under typical bias conditions, which corresponds to 2 to 5 W dc power dissipation at drain voltages low enough to prevent avalanche breakdown (V<sub>ds</sub> = 5 to 10 V). This gives approximately 1 W rf output power if the drain efficiency is a

reasonable 20 to 40%. With a 2  $\mu$ m gate length the real part of the input impedance is around 1  $\Omega$ , which can be matched with microstrip circuits. The gate fingers are 150  $\mu$ m each, so a total of 16 are needed. These are contained in four independent cells, so if one is broken or shorted it is still possible to fabricate an 1800  $\mu$ m gate width device from the three good cells.

The chip size must be small enough so that it is not a significant fraction of a wavelength at the operating frequency from one end to the other in order to prevent interference effects. A reasonable size is less than  $\lambda/8 \cong 0.05$  inch at X-band (in GaAs). The device thickness must be small to facilitate heat transfer to the mounting block, but not so small that the chips break easily and are difficult to handle. Also, when the slice becomes too thin, the gate and drain bonding pad capacitances to the ground plane become excessive. The chip size used is 0.020 inch  $\times$  0.040 inch; the large dimension is close to the minimum possible with 0.003 inch wide source pads, since nine pads are needed to accommodate the 16 gate fingers. The device thickness chosen is approximately 0.004 inch.

The gate bonding pad capacitance to ground should be small relative to the gate capacitance; this requirement is usually satisfied by making the pad as small as possible, consistent with ease in bonding, and placing it on insulating material. Both gate and drain bonding pads are approximately 0.005 inch × 0.005 inch.

Finally, it is desirable to minimize the source-gate and gate-drain spacings and contact resistances, since these result in parasitic resistances in series with the active region that reduce gain and increase the noise figure. A source-drain separation of 6  $\mu$ m was chosen, since it is the smallest compatible with ease in aligning the 2  $\mu$ m gate.

#### SECTION III

#### MATERIALS GROWTH AND CHARACTERIZATION

Throughout the program, epitaxial GaAs structures have been supplied for FET device fabrication. Due to previous experience at Texas Instruments in the areas of Gunn, IMPATT, varactor, and multiplier diodes, the development of the FET materials growth technology has proceeded very rapidly. Work has been directed toward the growth of single-layer FET structures as well as multilayered structures where the buffer layer is introduced to remove the active layer from intimate contact with the substrate. As with most microwave devices, material is needed that has high mobility and a low degree of compensation. The remaining parts of this section describe the approaches used to obtain the desired structures.

#### A. Substrate Characterization

#### 1. Specifications

Compared to other microwave devices, the FET structure is unique in that the epitaxial layer is grown on a high-resistivity substrate and the entire active layer may be only a few thousand angstroms thick. Therefore, the role of the substrate is a critical consideration in any successful device program. Throughout the program, the specifications to the substrate vendors have been as follows:

- (1) Resistivity >  $10^7$  ohm-cm (chromium or chromium/oxygen doping)

- (2) Etch pit density  $< 10^4/cm^2$

- (3) Minimum area > 1 in. $^2$ /wafer

- (4) Cut and polished on one side to  $15 \pm 1$  mil.

#### 2. Evaluation

When the wafers are received, a series of tests and inspections is carried out on random wafers from each crystal. The first inspection is merely

an optical examination of the polished surface to determine if any foreign matter or scratches are present that will degrade the quality. If no visible faults are observed, the wafers are placed in a sulfuric acid, hydrogen peroxide, water (8:1:1) mixture and etched for ten minutes. The wafers are again examined optically to determine the presence of any crystal degradation revealed by the 8:1:1 etch. If the results reveal no problem, the wafer is subjected to a third evaluation.

The purpose of the third test is to determine if there is any high temperature surface conversion on the wafer that will give rise to a thin (2000 to 4000 Å) conducting channel at the epitaxial layer/substrate interface. Obviously, this conversion would have a very negative effect on device performance. For this experiment the sample is heated in a hydrogen ambient at 800°C for two hours. After cool-down and removal of the wafer, a thin film of aluminum is evaporated on the surface and a pattern of annular rings is defined on the surface by standard photolithographic techniques. The resistance between rings is then measured to ensure that the original value,  $> 10^7$  ohm-cm, is preserved.

This series of tests is applied to two or three wafers from each crystal, depending on ingot dimensions. If any test results prove negative, all the wafers from that crystal are rejected.

Wafers are selected at random from various crystals for confirmation of resistivity and etch pit density (epd). The resistivity is measured as described above, but without the heat treatment, and the epd is verified by using a molten KOH etch for 15 minutes. Once wafers of acceptable quality have been identified, epitaxial growth is the next step.

#### B. Epitaxial Growth

#### 1. Growth Process

Epitaxial GaAs layers can be grown by either vapor phase or liquid phase techniques. For growth of FET structures, the vapor phase system is preferred because (1) high quality surfaces are routinely obtained; (2) the doping level can be adjusted by merely altering the gas phase dopant concentration, as opposed to saturation of a new melt; and (3) the process is capable of multislice deposition.

Of the possible vapor phase systems, the arsenic trichloride  $(AsCl_3/Ga/H_2)$  approach has emerged as the most successful for growth of microwave material. Epitaxial growth systems using AsCl\_3 have been in use at Texas Instruments since 1964.

A schematic drawing of an  $AsCl_3$  deposition system is shown in Figure 3. During the actual growth operation, palladium-diffused hydrogen is passed through an  $AsCl_3$  saturator, and the resulting saturated gas stream enters the main reactor tube. Upon entering the hot zone upstream from the source, the  $AsCl_3$  is reduced by hydrogen to form arsenic and hydrogen chloride. This mixture then passes over a boat filled with gallium, where the arsenic tends to dissolve until the source is saturated. When the gallium source becomes saturated, a crust of GaAs forms on the surface, and the necessary conditions for growth are established. With this saturated gallium, the following steady state reaction occurs at the source:

$$4 \operatorname{HCl}(g) + 4 \operatorname{GaAs}(s) \rightarrow 4 \operatorname{GaCl}(g) + 2 \operatorname{H}_{2}(g) + \operatorname{As}_{L}(g).$$

(1)

This mixture of gallium monochloride, hydrogen, and arsenic then passes into the deposition region, which is held at a lower temperature (750°C). There the thermodynamic equilibria are such that the reverse of the source reaction occurs, and

GaAs is epitaxially formed on the substrate. Figure 4 illustrates the epitaxial deposition system used for this program. Once the substrates are loaded into the reactor, this system functions in an automatic mode until growth is complete and the furnaces are returned to room temperature. The system can be used to grow sequential layers required in the multilayered structures.

#### 2. Growth Procedure

The growth techniques used for FET structure are modifications of normal procedures used for growth of n-type layers on  $n^{\dagger}$  substrates. The alterations were necessary to grow very thin layers (2500 to 4000 Å) with high doping levels, approximately 1 x  $10^{17}$  cm<sup>-3</sup>, on semi-insulating substrates. The standard growth run begins with an in situ vapor etch followed by epitaxial growth. Some samples are grown with no vapor etch, thus minimizing the time necessary to establish steady state growth conditions. This procedure places stringent demands on wafer preparation prior to insertion of the wafer into the reactor. Samples of acceptable surface quality were grown by this procedure, optimized, and submitted for device processing. A second scheme that was tried is one in which the wafer is placed in a special seed holder so that the wafer is exposed to only a nongrowth atmosphere of hydrogen during the heating cycle and the establishment of steady state conditions. The wafer is positioned in the etching atmosphere only after steady state conditions are established. Following the etch portion of the run, the wafer is withdrawn into the hydrogen filled chamber until steady state growth conditions are established. Then it is removed from the hydrogen ambient and placed in the growth environment. This procedure was tried, again, in an effort to minimize epitaxial film growth in non-steady state conditions.

In addition to the above variations in growth procedures, a series of experiments to determine the optimum flow rate was made. Flows from 60 cc/minute to 200 cc/minute were used, and the resulting surface quality was evaluated. As

の時代の時代の時代の

a mar water to be a second and a second

14

the flows are increased from 60 cc/minute, the surface quality is observed to improve up to a flow rate of approximately 75 cc/minute. Beyond this point, degradation in surface quality is observed, with a flow rate of 120 cc/minute being the worst case. After passing through this minimum, the surface quality again improves, with flows of approximately 175 to 200 cc/minute giving surfaces superior to any other flow rate. This high rate is also optimum in the growth of the chromium-doped buffer layers to be discussed later in this section.

The influence of deposition temperature has also been investigated. Temperatures from 780°C to 740°C have been used for layer deposition. Within this range the surface quality as well as device performance show no correlation with deposition temperature.

#### 3. Structures Grown

During the course of the program, the above discussed techniques were applied in the growth of four epitaxial structures: n-type layers on high resistivity, chromium-doped substrates; n-type layers on undoped buffer layers on chromium-doped substrates; n-type layers on chromium-doped buffer layers on chromium-doped substrates; and n-type layers on chromium-doped buffer layers on n-type substrates. The growth of single layers on high resistivity substrates was used extensively in the early portion of the program, both with and without vapor etching. In addition, layers were grown using the modified holder allowing for the hydrogen ambient during the establishment of steady state conditions. These single-layered structures were evaluated through device performance and found to demonstrate high power operation, > 1 W at 9 GHz with 4 dB gain.

Samples have also been grown using buffer layers, both undoped and chromium-doped. The role of the buffer layer is to enhance surface quality by

physically isolating the active n-type layer from the substrate, since the crystalline quality of the substrate is inferior to that of the epitaxial layer. The undoped buffer layers are grown from 1 to  $5 \,\mu$ m thick with carrier concentrations corresponding to the background level of the reactor, 5 to  $11 \times 10^{14}/\text{cm}^3$ . Sequential growth is achieved using the automatic system described previously. Following epitaxial optimization, devices fabricated from the wafers have been found to have high power performance, i.e., > 1 W at 9 GHz with 4 dB gain.

Samples grown with the chromium-doped buffer layers have not been as successful as the previously discussed material. The initial work with chromium-doped buffer layers was with the n<sup>+</sup>/high resistivity buffer/high resistivity substrate structure. Chromium was introduced in the form of chromium oxychloride (chromyl chloride),  $CrO_2C\ell_2$ , by the following high temperature reaction with hy-drogen:

$$3 \operatorname{cr0}_{2}\operatorname{Cl}_{2} + 3 \operatorname{H}_{2} \rightarrow \operatorname{cr0}_{3} \cdot \operatorname{Cr}_{2} + 6 \operatorname{HCl}_{2}.$$

(2)

The Cr0, is further reduced by hydrogen,

$$CrO_3 + 3H_2 \rightarrow Cr + 3H_2O_1,$$

(3)

and forms the chromium used as the acceptor necessary to produce semi-insulating material. Double epitaxial layers have been grown that have reverse breakdown values greater than 500 V for the buffer layer, indicative of high resistivity, and a top active layer with the desired carrier concentration,  $N_d \sim 1 \times 10^{17}$  cm<sup>-3</sup>. A cleaved cross section of such a structure is shown in Figure 5. The role of the buffer layer is clearly demonstrated in this figure. As can be seen, a large nonuniformity existed in the substrate after vapor etching, but the imperfection is missing at the n-type/buffer layer interface, enhancing surface regularity.

Figure 5 Cleaved and Etched Cross Section of FET Slice with Semi-Insulating Layer Buffer - 16 µm 北京市市にいた Sample #N162698-8 N<sup>-</sup> 1.5 μm Substrate ÷ 17 2

Devices fabricated from these wafers have not demonstrated the same high level of performance as earlier structures. Possible reasons for the inferior performance are discussed in a subsequent portion of this section.

The final structure grown for use with the plated-through ground device scheme was the most difficult of the four. It consists of an n<sup>+</sup> layer and a high resistivity layer grown sequentially on an n<sup>+</sup> substrate. The insulating buffer layer is required in this case to isolate the source and drain. This situation was complicated by the fact that the substrate out-diffuses an n-type dopant, Ta, that must be compensated by the Cr in different concentrations as the run progresses. By the end of the run, the concentration of n-type dopant is greatly reduced because the epitaxially grown layers have covered most of the n-type substrate. Following growth of the thick buffer layer (20  $\mu$ m) the top n<sup>+</sup> layer is sequentially grown with a carrier concentration of approximately 1 x 10<sup>17</sup> cm<sup>-3</sup>. Of the many attempts to grow this structure, very few met all the desired parameters. Most samples were rejected because the resistivity in the buffer layer was too low or the quality of the surface was poor.

#### 4. Characterization

Following growth of the various structures, the wafers are characterized in terms of thickness and carrier concentration. The thickness is measured optically on a cleaved and etched cross section of each wafer using conventional microscopy. The carrier concentration is measured by two techniques. One is the point contact method,<sup>2</sup> which is a quick and nondestructive evaluation technique that gives a close approximation of carrier concentration and a qualitative estimate of thickness for the very thin layers. As a verification for these values, random samples have been chosen on which aluminum is evaporated and the concentration determined by conventional C-V procedures. The agreement in the two methods is close in most cases.

#### 5. Optimization

Following growth and characterization, samples are optimized if they are within specifications. The optimization technique consists of etching with a kinetically limited etch,  $\frac{3}{100}$  followed by anodic oxidation. <sup>4</sup> In all cases, samples are grown thicker than required for device work and then thinned. This post-growth thinning ensures that the Schottky barrier is fabricated not on the surface formed during growth termination, but rather under steady-state conditions. Since growth termination is not instantaneous, the final portion of the epitaxial layer would have a composition of other than steady state proportions. Optimization consists of thinning the layer with the kinetically limited etch until the point contact indicates the thickness is approaching optimum values for the carrier concentration of that wafer. The sample is then anodically oxidized until the final thickness is achieved. This self-limiting technique, through current limitation, results in a large-area wafer that has an optimum carrier concentration-thickness combination for device processing. Anodic oxidation can also be used to determine thickness uniformity of a sample by observing the color of the as-grown oxide and the number of oxidation steps necessary for optimization.

#### 6. Discussion

A number of wafers have been grown from which transistors have been fabricated that have shown performances in excess of 1 W at 9 GHz with 4 dB gain. These wafers have been conventional single  $n^+$  layers on high resistivity substrates or  $n^+$  layers on undoped buffer layers on high resistivity substrates. Samples with chromium-doped buffer layers on n-type or high resistivity substrates produced less desirable results. It is believed that these latter two structures do not have the carrier concentration uniformities of the first two. This belief is based on the observation of the color scheme produced with the anodic oxidation procedure. On the successful structures, the anodically grown oxide follows a

definite orderly clearing pattern with optimization, while the oxide pattern on the samples with chromium-doped layers is very nonuniform in color across a wafer. For successful doping with  $CrO_2C/2$ , a great deal more effort must be spent in enhancing the uniformity of both carrier concentration and surface smoothness.

#### SECTION IV

#### DEVICE FABRICATION

The GaAs FET device design and fabrication processes continued to evolve throughout the course of the contract. The three planar device structures that were studied and the differences between them are briefly described. A nonplanar structure is also discussed. A number of experimental studies were conducted to improve the device processing; these studies and their results are described. Finally, the current GaAs power FET fabrication process is examined.

#### A. Review of Structures\_Investigated

The three planar device structures and the plated-through ground structure are described. In all cases gate lengths are nominally 2  $\mu$ m; N<sub>d</sub> ~ 1 × 10<sup>17</sup>/cm<sup>3</sup>, and V<sub>b</sub> ~ 5 V.

#### 1. Planar Device Structures

Photographs of the first structure studied are shown in Figure 6. The total gate width is 2000  $\mu$ m in eight gate fingers (250  $\mu$ m each), all of which are connected to a single gate bonding pad. Source pads are 0.005 inch wide. Half the devices on the slice have four gate fingers (1000  $\mu$ m total gate width). Output powers were only 100 to 150 mW with 4 dB gain at 8 GHz from the 1000  $\mu$ m gate width devices. Poorer putput powers were obtained from the 2000  $\mu$ m devices. This poor performance is partially the result of the high parasitic resistances present with the AgInGe ohmic contacts and nonrecessed gates then in use (see Section IV.B for a discussion of parasitic resistances).

In an attempt to improve these results, the structure shown in Figure 7 was developed. There are 1200  $\mu$ m and 2400  $\mu$ m gate width devices on the slice. The masks were fabricated by electron beam definition, so a significant fraction of the slice is taken up by alignment marks. Individual gate stripes were

# A) LOW MAGNIFICATION

# **B) HIGHER MAGNIFICATION**

# **C) SEM PHOTOGRAPH**

(a) LOW MAGNIFICATION

(b) ACTIVE AREA DETAIL

shortened to 150  $\mu$ m, necessitating additional gate fingers. The 0.005 inch source pad width makes a large chip length (0.060 inch for 2400  $\mu$ m gate width) necessary. The capability to recess gates and plate-up source pads is included, but all gate fingers are interconnected on the chip, giving a low yield of good devices.

1200  $\mu$ m gate width devices of this design have reached a maximum of 300 mW output power at 9 GHz with 4 dB gain. Devices that have 2400  $\mu$ m gate widths are no better, however. Most of the improvement over the previous design is probably due to reduction in parasitic resistance through use of recessed gates and AuGe/Ni ohmic contacts.

The current GaAs power FET design is shown in Figure 8. Total gate width is still 2400  $\mu$ m contained in four 600  $\mu$ m (four gate stripes) cells, but source pad width has been reduced to 0.003 inch, allowing a chip width reduction to 0.040 inch. The individual cells are not connected on the slice (connections are made with bond wires), which, in conjunction with the higher device packing density, provides a much higher yield of usable devices having at least 1200 µm gate width. This higher yield, coupled with the fact that one in four chips is made up of test patterns (discussed in Section V.A.1), provides a much greater capability for studying the effects of various processing, mounting, bonding, etc., changes. When mounted on ceramic substrates (as were the two previous device types), 1200 µm gate width devices from several slices have had output powers of 300 to 400 mW at 9 GHz with 4 dB gain. Devices with 1800  $\mu$ m and 2400  $\mu$ m gate widths are slightly better. These improvements over the previous design are partly due to deeper gate recession and smaller chip size (a smaller fraction of a wavelength from one end to the other). As discussed in Section V.B.2, the mounting of these latest GaAs FETs directly to Cu blocks instead of alumina substrates has resulted in a further multiplication of the output power by a factor of 2 to 3.

#### 2. Nonplanar Device Structure

It was originally thought that a major limitation on GaAs power FET performance would be the inductance of the bond leads interconnecting the multiple source pads. For this reason the design of Figure 9 was devised. In this design the source pads are interconnected through an  $n^+$  substrate. A schematic cross section of the slice is shown in Figure 10. A high resistivity buffer layer and an n-type active layer are grown on an  $n^+$  substrate, as described in Section III.B.3. Holes are etched through the buffer layer to the substrate, and electrical connections are made by metallization in the holes plated through ground. No source leads are necessary, and very low inductance contacts are possible. The high resistivity buffer layer should be at least 20  $\mu$ m thick to prevent excessive gate and drain bonding pad capacitance.

Figure 11 is a photograph of such a structure with a 20  $\mu$ m Cr-doped buffer layer. The problem encountered is that as the holes are etched, they become wider at the top, and for a 20  $\mu$ m depth they approach the edges of a 0.005 inch wide source pad. If the high resistivity layer is made thinner, the gate and drain pad capacitances become excessively large; and if the source pads are made wider to permit deeper holes, the chip size becomes too large for a gate width of more than about 1200  $\mu$ m (eight gate stripes). The device of Figure 11 is a compromise with the holes etched as deeply as possible (about 20  $\mu$ m). The source pads are interconnected, but since the hole depth is about the same as the buffer layer thickness, the resistance of the connection is excessive. This causes the current to saturate at  $\sim$  3.5 V instead of the 2 to 2.5 V typical of planar devices and results in 1 to 2 dB lower microwave gain than with a comparable planar device under the same conditions. Because of the difficulty in making a low resistance interconnection and the additional difficulty of growing a high quality high resistance buffer layer, this idea has been abondoned in favor of the planar approach. As discussed in Section V.B.2, source lead inductance is not now thought to be a significant problem with GaAs power FETs.

A) conventional bonding

b) Plated through ground sources

Figure 9 Double-Source FET with Conventional Bond Wires to Ground Compared with Plated-Through Interconnected Source Grounding

The second strange

Figure 10 Schematic Cross Section of Structure for Plated-Through Ground Source Interconnection

STATISTICS STATES

#### B. <u>Process Studies</u>

It is extremely important that all parasitic resistances be reduced to the lowest possible values. It is also important that the gate metallization be reliable (Schottky barrier properties do not change with time) and of sufficient thickness to prevent excessive attenuation of the input rf signal. The experiments leading to the improvement of these parameters are described in this subsection.

#### 1. Ohmic Contacts

Operation of GaAs FETs at high power levels requires very low resistance ohmic contacts. Excessive contact resistance seriously degrades the device transconductance and thus the rf gain. Because the ohmic contacts are fabricated in an n-type layer on a semi-insulating substrate, the conventional contact resistance measurement technique<sup>5</sup> is not applicable, and a different scheme must be employed. Three contacts with separations  $\ell$  and  $2\ell$  (where  $\ell \simeq 3 \ \mu$ m) are fabricated as shown in Figure 12. They are placed on a mesa of width Z (or are cleaved to that width) so that all the electric field lines will be straight lines perpendicular to the contact edges. The resistance of the n-type layer between contacts 1 and 2 is then found by simply treating it as a resistor of resistivity,  $\rho$ , length,  $\ell$ , and area, Za. The contacts are fabricated exactly as with the actual devices and are overcoated with Au to spread the current evenly across the contact width.

When the resistance between two contacts is measured, it is made up of three components: the resistance of each contact,  $R_c$ ; the resistance of each probe,  $R_p$ ; and the resistance of the n-type layer, R (length  $\ell$ ) or R' = 2R (length  $2\ell$ ). Define  $R_{ab}$  as the measured resistance between contacts a and b. Then

$$R_{12} = 2 R_{c} + 2 R_{p} + R \tag{4}$$

$$R_{23} = 2 R_{c} + 2 R_{p} + 2 R.$$

(5)

.

By subtracting R<sub>23</sub> from 2 R<sub>12</sub>, the resistance of the n-type layer is eliminated (assuming  $\rho$  and a are uniform), and one has

$$R_{c} \left(\frac{\Omega}{mm \text{ gate width}}\right) = \left[\frac{2R_{12} - R_{23}}{2} - R_{p}\right] \left[\frac{Z(mm)}{1 \text{ mm}}\right] . \tag{6}$$

Rather than use probes for which R can depend on probe pressure, wires are bonded to each contact and R can be measured by bonding two wires to the same contact.

During the contact alloying process, the alloy depth is not known (a' in Figure 12 is unknown) so the specific contact resistance,  $r_c (in \Omega - cm^2)$ , in general cannot be calculated exactly. The resistance in  $\Omega/mm$  gate width is therefore used to compare different samples. It can be shown that the contact resistance is given by

$$R_{c} = \frac{1}{Z} \sqrt{\frac{r_{c}\rho}{a'}} , \qquad (7)$$

where  $\rho$  = GaAs resistivity, and in two cases (where a' is known)  $r_c$  can be determined from the measured values of  $R_c$ . The two cases are a' = a (no alloy penetration into the GaAs) and penetration to the substrate. In these cases one has

$$r_{c} = \frac{R_{c}^{2} Z^{2} a}{\rho} \quad a' = a \tag{8}$$

$$\mathbf{r}_{c} = \mathbf{R}_{c} \mathbf{Z} \mathbf{a} \qquad \mathbf{a}^{\prime} = \mathbf{0}. \tag{9}$$

Calculation of  $r_c$  in these limits allows some comparison with the results of others. When  $R_c$  becomes very small, the calculated values of  $r_c$  for these two cases are not drastically different in the range of Z, a, and  $\rho$  employed for GaAs FETs.

The contact resistance has been measured for AgInGe, AuGe, and AuGe/Ni alloyed contacts on several different slices. The AgInGe contact<sup>5</sup> (90 weight % Ag, 5% In, 5% Ge) was initially used because of its very sharp edge definition compared to AuGe, which balls up significantly when alloyed. The AgInGe contact is alloyed for five seconds at 600°C in flowing Ar. More recently, eutectic composition AuGe with a 200 to 400  ${\rm \AA}$  Ni overcoat<sup>6</sup> has become the standard GaAs FET ohmic contact in this laboratory. These contacts have an edge definition as sharp as that of AgInGe contacts, and significantly lower resistance. Robinson has shown' that when the AuGe/Ni is heated, the Ni diffuses through the AuGe to the AuGe-GaAs interface, increasing the wetability and giving a much more uniform alloy. The contact resistance results are shown in Table 1. The improvement is clearly apparent: the contact resistance using AgInGe is around 2 to 3  $\Omega/mm$ gate width, while with the AuGe/Ni it is in the 0.3  $\Omega$ /mm gate width range. The values of R \_ may be uncertain by a factor of two due to variations in epitaxial thickness, probe resistance, measurement of contact separations, etc. As will be shown shortly, changing from 2 to 3  $\Omega$  to 0.3  $\Omega$  is a reduction from the same order as the channel resistance to a small fraction of that resistance. Although the specific contact resistance is not precisely known, since a' (Figure 12) is not known, it is approximately  $1 \times 10^{-6}$  for the AuGe/Ni contacts.

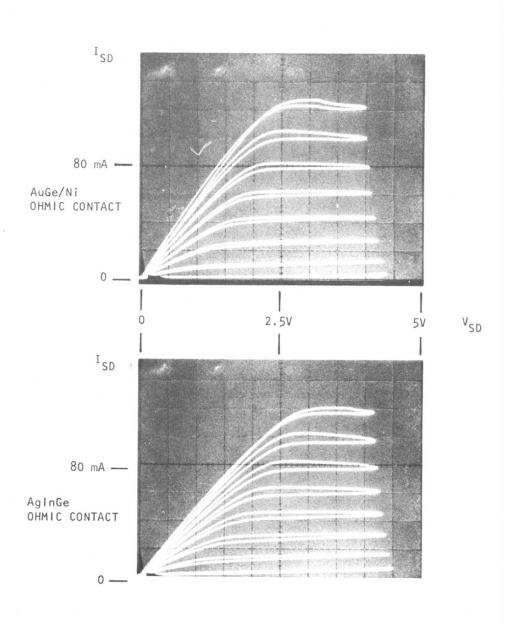

When a slice is cleaved into two portions and the devices on one piece are fabricated with AuGe/Ni contacts with the others having AgInGe, the superiority of the AuGe/Ni is clear. As shown in Figure 13, the saturation voltage is 2.5 V for devices with AuGe/Ni contacts as opposed to 3.0 V for identical devices with the AgInGe. The rf performance is similarly improved; devices with the AuGe/Ni have about 1 dB more gain at a given input power level and bias condition than identical devices with AgInGe contacts.

# Table 1 MEASURED CONTACT RESISTANCE FOR DIFFERENT OHMIC CONTACT ALLOYS

| 2, | SISTANCE r (Q-cm )                   | a′ = 0 | (Alloyed down to   | substrate)                               | 7         | $0.96 \times 10^{-0}$ | 8.7 × 10 <sup>-6</sup> | ч<br>Г | $1.5 \times 10^{-2}$   | $7.4 \times 10^{-1}$ | L       | $5.6 \times 10^{-10}$   | $1.0 \times 10^{-5}$  | $1.05 \times 10^{-5}$ | 9-07    | 5.3 × 10<br>r | $1.8 \times 10^{-2}$ |             |

|----|--------------------------------------|--------|--------------------|------------------------------------------|-----------|-----------------------|------------------------|--------|------------------------|----------------------|---------|-------------------------|-----------------------|-----------------------|---------|---------------|----------------------|-------------|

|    | SPECIFIC CONTACT RESISTANCE r C Cm L | e = ,e | (Very thin         | alloyed region)                          |           | $2.1 \times 10^{-6}$  | $1.4 \times 10^{-3}$   |        | 3.8 × 10 <sup>-0</sup> | $6.2 \times 10^{-7}$ | L-      | 3.6 × 10 <sup>-</sup> / | $1.10 \times 10^{-4}$ | $1.26 \times 10^{-4}$ | لر<br>ا | 3.1 × 10 2    | $1.0 \times 10^{-3}$ |             |

|    |                                      |        | e                  | (ш т)                                    |           | 0.3                   | ~ 0                    |        | 0.25                   | 0.35                 |         | 0.35                    | 0.35                  | 0.35                  |         | 0.35          | 0.25                 |             |

|    |                                      |        | Contact Resistance | R <sub>c</sub> ( $\Omega/mm$ gate width) |           | 0.32                  | c                      | 4.4    | 0.62                   | 0 21                 |         | 0.16                    | 2.8                   | C ~                   | 2.1     | 1.5           | 6.1                  | ,<br>,<br>) |

|    |                                      |        |                    | Ohmic Contact<br>Allov                   |           | AuGe/Ni               |                        | AgInGe | AuGe/Ni                |                      | Auge/NI | AuGe/Ni                 | AaInGe                |                       | Aginue  | AgInGe        | وير                  | DODA        |

|    |                                      |        |                    | Run No                                   |           | Ф                     |                        | А      | A                      |                      | A       | ß                       | Ċ                     | ) (                   | D       | w             | c                    | ¥           |

|    |                                      |        |                    |                                          | 21100 100 | -                     | -                      | 2      | ~                      | <b>`</b>             | 4       |                         |                       |                       |         |               | ı                    | Υ           |

Figure 13 Comparison of Current-Voltage Characteristics of Devices Having AuGe/Ni Ohmic Contacts and AgInGe Ohmic Contacts. 20 mA/vertical division, 0.5 V/horizontal division, 1 V/step, 300 µm gate width.

#### 2. Recessed Gate

The ohmic contact is not the only source of parasitic resistance; the regions between the source and gate,  $R_{sg}$ , and drain and gate,  $R_{dg}$  also act as parasitic resistances and, being of the same dimensions as the active area under the gate, make a significant contribution to the total resistance. When the contact resistance is very low, as with AuGe/Ni, the contribution from these regions may be as much as 2/3 of the total parasitic resistance. One way to significantly reduce the contribution of these parasitic regions is to recess the gate below the epitaxial surface as shown in Figure 14, thus permitting a thicker epitaxial layer for the same pinch-off voltage. Since the resistance of the (source-gate) parasitic region is now  $R_{sg}' = \rho \ell_{sg}/2a'$  instead of  $R_{sg} = \rho \ell_{sg}/2a$ , it is decreased since a' = a + recess depth. The recess depths achieved have been in the range from 500 to 2500 Å, which can lead to as much as 50% reduction in the parasitic resistance. The improvement is not only in the parasitic GaAs resistance; an increase in the epitaxial layer thickness also reduces the contact resistance is changes from

$$R_{c} = \frac{1}{Z} \sqrt{\frac{r_{c}\rho}{b}}$$

$R_{c}' = \frac{1}{Z} \sqrt{\frac{r_{c}\rho}{h'}},$

to

where b' = b + recess depth, and  $r_c$  = specific contact resistance in  $\Omega$  - cm<sup>2</sup>.

Devices fabricated on two halves of the same slice with AuGe/Ni ohmic contacts have shown no difference between them except that one has a slightly thicker epitaxial layer. The gate has been recessed about  $0.07 \ \mu$ m on the slice with the thicker epitaxial layer, which gives devices on both slices the same

i,

37

Start .

pinch-off voltage. Figure 15 compares the I-V characteristics of devices from the two slices. The saturation voltage of the devices with the recessed gate is only 2.3 V, while for the others it is 2.6 V. There is a similar improvement in the relative microwave performance of the devices; devices with recessed gates have approximately 1 dB higher gain than those without under the same operating conditions.

#### 3. Channei Conductance

One of the better devices studied is analyzed in detail to show the numerical contributions of the various parasitic resistances. The I-V characteristic is shown in Figure 16. The source and drain ohmic contacts are AuGe/Ni, and the gate is recessed 1500 Å.

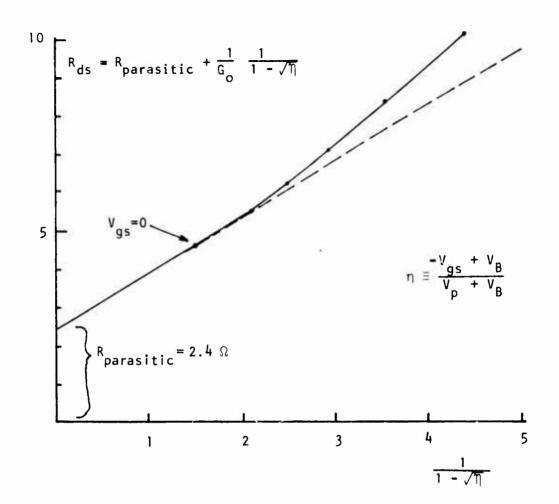

One way to determine the parasitic resistance has been described by Hower and Bechtel<sup>8</sup> and makes use of the fact that when the drain current is zero, the small signal source-drain resistance is given by

$$R_{ds} = R_{parasitic} + \frac{1}{G_0(1 - \sqrt{\eta})}, \qquad (10)$$

where  $G_0$  is the open channel conductance and  $\eta \equiv (-V_{gs} + V_B)/(V_p + V_B)$ .  $V_B$  is the Schottky barrier height at zero bias (approximately 0.7 V for AL), and  $V_p$ is the pinch-off voltage (approximately 5.5 V for this device). The donor concentration,  $N_d$ , is measured to be 1 × 10<sup>17</sup> cm<sup>-3</sup> from the Schottky barrier capacitance at zero bias. When  $R_{ds}$  measured near zero drain bias is plotted as a function of  $1/(1 - \sqrt{\eta})$  as in Figure 17, the extension to  $1/(1 - \sqrt{\eta}) = 0$  gives the parasitic resistance, which is shown here to be 2.4  $\Omega$ . If the epitaxial layer had a uniform carrier concentration and mobility, the graph would be a straight line; since its slope increases with gate bias,  $V_{gs}$ , the  $N_d \mu$  product for this slice decreases as the substrate is approached. The point labeled

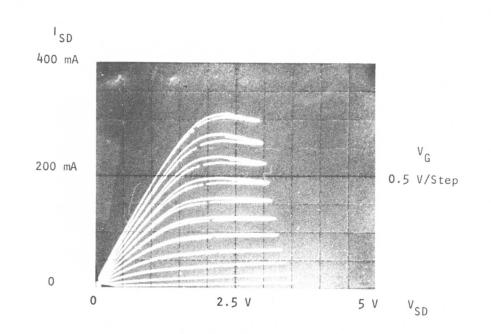

Figure 16 Current-Voltage Characteristic of GaAs FET Having a Total Gate Width of 1200  $\mu$ m. Gate length is  $\ell = 2.4 \ \mu$ m and source-drain spacing is  $\ell_{sd} = 5.9 \ \mu$ m.

Figure 17 Analysis of Elements Contributing to Source-Drain Resistance of GaAs FET of Figure 16

$V_{gs} = 0$  shows that with zero gate bias the resistance between source and drain near zero drain current is 4.6  $\Omega$ , giving a channel resistance of 4.6  $\Omega$  - 2.4  $\Omega$  = 2.2  $\Omega$ .

The epitaxial thickness under the gate is

$$a = \sqrt{\frac{2\varepsilon \left(V_p + V_B\right)}{qN_d}} = 0.29 \ \mu m. \tag{11}$$

The epitaxial thickness in the parasitic regions is a' = a + recessed depth =  $0.44 \mu$ m. The resistivity may be obtained from

$$\rho = \frac{E_{crit} Z(a - 0.1 \ \mu m)}{I} = 0.0188 \ \Omega - cm , \qquad (12)$$

where I is the saturated current with the gate unbiased and  $E_{crit} = 3.3 \times 10^3$  V/cm. In (12), a - 0.1  $\mu$ m = 0.19  $\mu$ m is used because current does not flow through the 0.1  $\mu$ m Schottky barrier depletion region. The resistance of the channel can be calculated from  $_{0}$  and a above and  $\ell$  in Figure 16:

$$R_{channel} = \frac{\rho l}{Z(a - 0.1 \,\mu m)} = 2.0 \,\Omega, \qquad (13)$$

which is similar to the 2.2  $\Omega$  found with Figure 17. The source-gate and draingate resistances can also be calculated using  $\rho$  and a' above and  $\ell_{sd}$  from Figure 16:

$$R_{sg} + R_{dg} = \frac{\rho (\ell_{sd} - \ell)}{Z (a' - 0.1 \,\mu m)} = 1.6 \,\Omega.$$

(14)

For this device, the contact resistance was measured to be  $R_c = 0.3 \Omega$ , and the resistance of bond wires, TC bonds, striplines, etc., contributed another 0.3  $\Omega$  (measured with two wires bonded to the same pad). The total of these parasitic resistances  $R_{sg} + R_{dg} + 2R_{c} + 0.3 \Omega = 1.6 \Omega + 0.6 \Omega + 0.3 \Omega =$ 2.5  $\Omega$  is close to the 2.4  $\Omega$  of Figure 17. One can see that the actual active channel resistance is less than half of the total measured source-drain resistance, and the majority of the parasitic resistance comes from the source-gate and drain-gate regions.

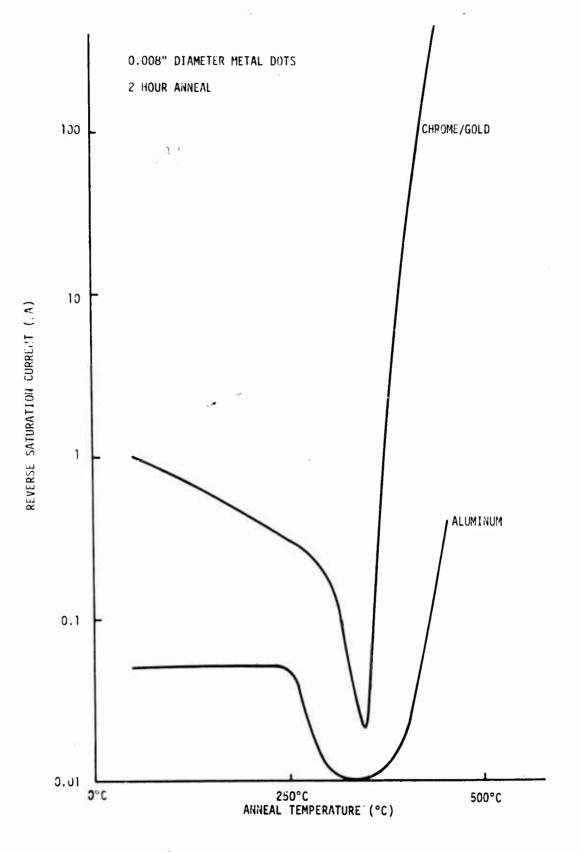

# 4. Schottky Gate Metallization

Both Al and Cr/Au Schottky barriers have been employed as GaAs FET gate metallizations in this laboratory. Aluminum is used exclusively at present because CrAu has been found to react with the GaAs when heated to 300 to  $350^{\circ}$ C. After heating to this temperature for 20 minutes, there is an obvious change in the appearance of the Cr/Au, with the surface growing more bumpy. As shown in Figure 18, the reverse saturation current of the Schottky barrier also increases drastically while that of the aluminum barriers increases relatively little, remaining less than 1  $\mu$ A (for an 8 mil dot) after a two-hour 450°C anneal. These results are similar to those reported by Kim, et al.<sup>9</sup>

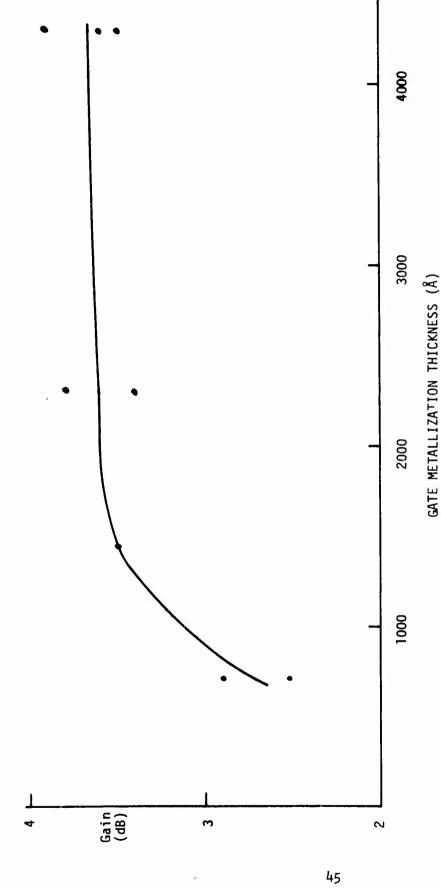

#### 5. Gate Finger Width

To determine the thickness of gate metallization that is necessary to prevent attenuation of the input signal as it travels from the gate pad down the gate stripe (which acts as an RC transmission line), this thickness has been varied across a slice by slowly moving a shield out of the way during the metal evaporation. The devices are thus identical except for the gate metal thickness, and the relative microwave performance can be measured as a function of gate thickness. The gain as a function of gate metallization thickness is plotted in Figure 19 for constant input power level and bias. Thicknesses of 1500 to 2000 Å for individual finger widths of 150  $\mu$ m and 2.5  $\mu$ m gate lengths are sufficient to maximize gain. The resistance of an individual gate stripe from one end to the other has been measured to be approximately what one would calculate from the observed dimensions and the bulk resistivity of A $\ell$ .

Figure 18 Reverse Saturation Current as a Function of Anneal Temperature of AL and Cr/Au Schottky Barriers

Device Gain at 9 GHz as Function of Aluminum Gate Metallization Thickness. (Input power is 15 dBm,  $V_{ds} = 5 V$ ,  $V_{gs} = -1 V$ , total gate width is 1200 µm, individual gate stripe width is 150 µm, device mounted upright on ceramic.) Figure 19

#### C. Fabrication Process

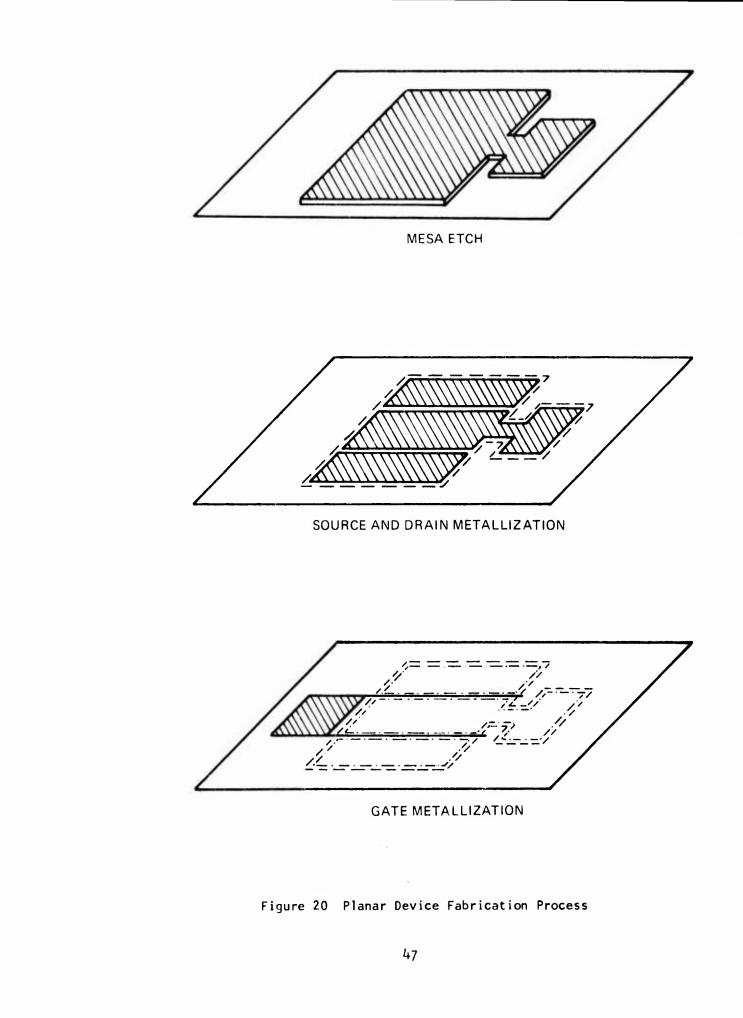

The fabrication process now being used for GaAs power FETs at Texas Instruments is described below; the process is relatively simple, with only four major steps.  $^{10}$  The first three steps for a two gate stripe device are shown in Figure 20.

# Mesa Etch

Following epitaxial thinning, the first major processing step is to etch mesas through the thin n-layer to the semi-insulating substrate with room temperature  $8 H_2 SO_4/H_2 O_2/H_2 O$ . This isolates the source and drain terminals except for the channel under the gate and provides an insulated surface for the gate bonding pad. A mesa height of 0.5 to 1.0  $\mu$ m is adequate to isolate adjacent mesas (resistances of 1 to 10 M  $\Omega$ ).

## • <u>Source/Drain Ohmic Contacts</u>

The second step is the source/drain metallization. A lift-off pattern is defined in AZ-1350 photoresist, and the source/drain metal is evaporated over the slice. The unwanted metal is lifted off by dissolving the photoresist in acetone. This method of metal definition is very simple, gives sharp edge definition, and is capable of extremely fine geometries. The metal remaining on the source and drain is then alloyed into the GaAs, forming an ohmic contact.

The ohmic contacts are formed by evaporating approximately 2000 Å of eutectic composition AuGe followed by a 200 to 400 Å Ni overcoat. Alloying is accomplished by raising the slice to  $450^{\circ}$ C for several seconds in flowing argon.

#### • Gate Metallization

The third major processing step is the gate metallization. The gate pattern is defined in photoresist, a groove is etched in the GaAs surface for

two seconds with 10  $H_2SO_4/H_2O_2/H_2O_at 5$  to 25°C, and the metal is evaporated and lifted off as with the source and drain. The alignment of the gate in the source-to-drain gap is the most critical step. A 2 µm gate length and a 6 µm source-drain gap are entirely adequate for X-band operation. Gate stripe widths of 150 µm are found to be more than sufficient to eliminate attenuation effects with the gate metallization thicknesses employed (~ 4000 Å). The gate recess depths are in the range of 500 to 2500 Å, which can lead to as much as 50% reduction in the parasitic resistance.

Aluminum is used as the gate metal because of its reliability (see Section IV.B.4). Evaporation is carried out at about 50°C with a glow-discharge prior to deposition to ensure good adhesion. The slice is then annealed at 275°C for 15 minutes to minimize the gate leakage current.<sup>11</sup>

#### Bonding Pad Metallization

Following the gate metallization, a layer of Cr/Au is evaporated on the source and drain to improve current spreading and bondability. A nitride layer is then deposited in the active region, and a thick (10 to 15  $\mu$ m) Au layer is plated to the source pads to simplify bonding. Both the nitride and plated-up source pads protect the active regions from scratches. The slice is then lapped to 0.003 inch to 0.004 inch, metallized on the back, and scribed into individual devices.

#### SECTION V

#### EVALUATION

In this section the GaAs power FETs fabricated as described in the previous section are evaluated. Low frequency studies and X-band performance are discussed.

#### A. Low Frequency Evaluation

Several useful measurements can be performed on the GaAs FETs before actual microwave testing. A test pattern, which is placed periodically across the slice, permits study of the properties of the epitaxial material, ohmic contacts, and Schottky barrier right at the device. In this section the evaluation features on the test bar are described first, followed by a description of the results obtained by using the test bar as well as by measurements on the device structures.

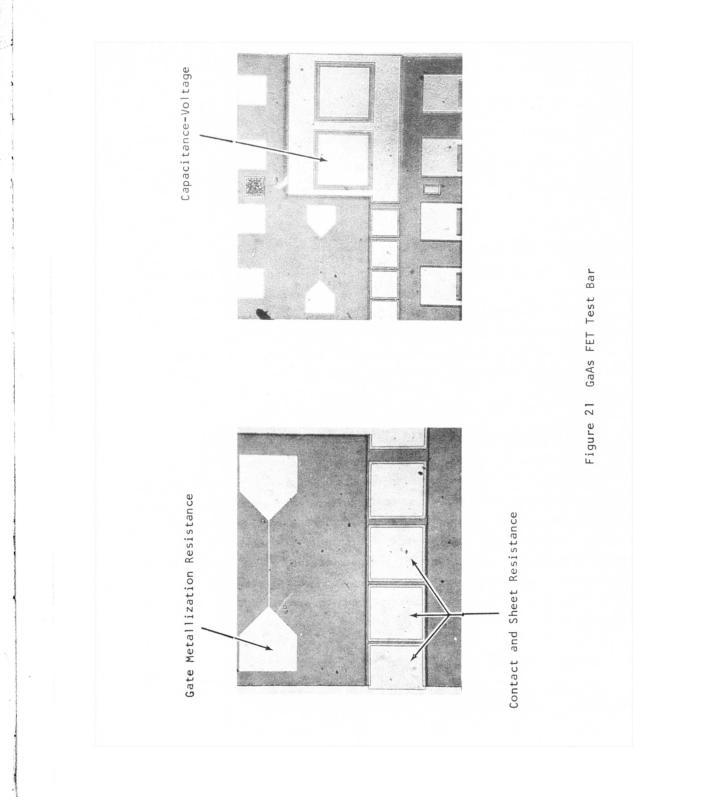

#### 1. Photomask Evaluation Features (Test Bar)

Photographs of the test bar which replaces one device in four are shown in Figure 21. The right-hand photograph is an overview, and details are shown in the left-hand photograph. The contact resistance and epitaxial sheet resistance are measured on the variably spaced ohmic contacts as described in Section IV.B.1, with typical results shown in Table 1. The narrow A& stripe can be used to measure the resistance of the gate stripe, which is found to be approximately what one would calculate from the bulk resistivity and known dimensions. Also, the square Schottky barriers can be used to determine the donor concentration as a function of depth from the C-V characteristics.

## 2. Visual Screen and Reliability

A close visual examination of the GaAs FET chips is an important step. Most four-cell devices (80 to 90%) which appear to have no shorted or broken

4

A. A.

Sector Sector

Statistics of the

.

gates do not short out when voltage is applied. The number of good four-cell devices on a slice is usually in the range from 5 to 25%. The remainder of the devices are not useless, however, as they may be used for lower power (fewer cells) amplifier stages. Virtually all the devices that do fail when voltage is applied (for no readily apparent reason) do so within the first few minutes (most within a few seconds), and those that last beyond this time appear to be reliable when operated at a drain voltage of 8 V.

# 3. Capacitance-Voltage (C-V) Measurement

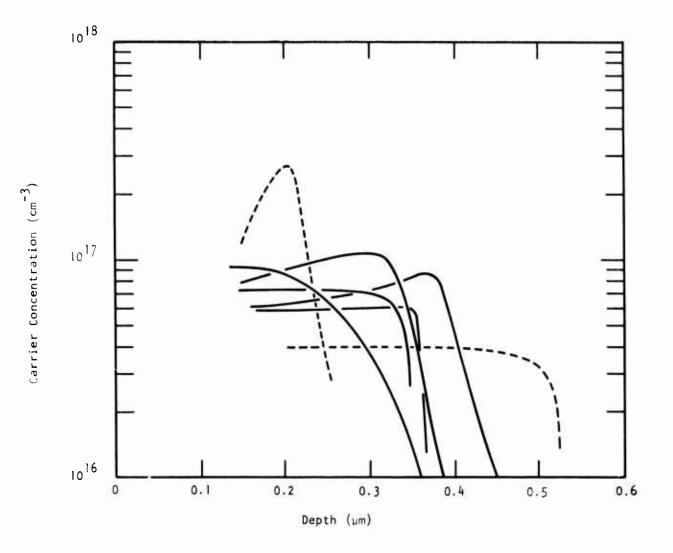

An automatic profiler is used to determine the carrier concentration as a function of depth into the epitaxial layer from the C-V characteristic of the square Schottky barrier on the test bar (see Figure 21). Because of the semi-insulating substrate, both probes are to the upper surface. The increasing series resistance as pinch-off is approached causes the plots to be somewhet distorted in that region. Several such plots are shown in Figure 22; all the curves are from slices that yielded 2400  $\mu$ m gate width devices capable of at least 1 W output power at 9 GHz with 4 dB gain. The dashed curves are from slices near the high and low carrier concentration limits for 1 W output power. Clearly, there is a large range of carrier concentration profiles that will produce good devices. It is apparently very important whether or not the profile is flat or the carrier concentration increases somewhat as the substrate is approached. When the concentration is less than about 5 x 10<sup>16</sup> or above about 1.5 x 10<sup>17</sup> cm<sup>-3</sup>, device performance drops; 8 to 10 x 10<sup>16</sup> cm<sup>-3</sup> appears to be about optimum.

# 4. Current-Voltage (I-V) Measurement

Further information is gained from the device I-V characteristic. Figure 16 showed typical characteristics for a 1200  $\mu$ m gate width device. A