COPY

FILE

This chanteent has been approved for public relocate and sales in the charibution is unlimited.

DTIC AUG 8 1985

85-8-01-158

ILLIAC IV Document No. 225

John A. Perry

ARPA/IPT

1400 Wilson Blod.

Arlington, Va. 22209

Center for Advanced Computation

University of Illinois at Urbana-Champaign

Urbana, Illinois 61801

AN INTRODUCTORY DESCRIPTION OF THE ILLIAC IV SYSTEM

Volume I

by

Stewart A. Denenberg

| Accession For  NTIS GRA&I  DTIC TAB                | APPROVED FOR PUBLIC REDISTRIBUTION IS UNLIMITE | ELEASE,<br>ED (A) |

|----------------------------------------------------|------------------------------------------------|-------------------|

| Unannounced  Justification                         |                                                |                   |

| Prefribution/                                      |                                                | PREVIOUS PAGE     |

| Availability Colos<br>Avail and/or<br>Dist Special |                                                |                   |

| A-1                                                | artment of Computer Sci                        | ence File No. 850 |

| Hill was sively                                    | 'July 15, 19                                   |                   |

This work was supported by the Advanced Research Projects Agency, as administered by the Rome Air Development Center, under Contract No. USAF 30(602)-4144.

9

Li na

To Claire

#### Read This First

2000

This book was written for an applications programmer who would like a tutorial description of the ILLIAC IV System before attempting to read the reference manual. As a tutorial, the level of detail presented in this book is fairly general; particular information can be found in the Burroughs Reference Manual "ILLIAC IV Systems Characteristics and Programming Manual."

In order to use this book most effectively, the Chapters should be read in order. The reader who wants a very quick look at the capabilities of ILLIAC IV may skim just the summaries of parts A, B and C of Chapter I and begin reading on page I-55. He may then read pages II-1 through II-20, skipping the detailed description of the ILLIAC IV Array (pages II-21 to II-41). Pages II-41 through II-73 are optional; the reader should at least look at them and decide for himself. As much of Chapter III as possible should be read—the instruction repertoire, more than anything else, defines the capabilities of a computer. A valid answer to the question "What is ILLIAC IV?" would be to hand the questioner a description of each instruction in the repertoire.

For a more complete understanding, however, the reader should come back and read the sections he skipped on the first pass. It is the nature of ILLIAC IV, to a degree much greater than the conventional computers, that its hardware structure is bound up very closely with its

capabilities. It is therefore necessary that the reader spend the time necessary to understand the architecture of ILLIAC IV.

The Table of Contents in the front of the book is in an abbreviated format while each chapter will be preceded by a finer Table of Contents. A Hardware Glossary which is essentially a glossary for Chapter II is at the end of the book.

T

Chapter I presents the background concepts necessary for an understanding of ILLIAC IV. A short section is devoted to the historical development of digital computers and their evolution is described in terms of the problems that had to be solved. After conventional computer organizations are described, unconventional ones are presented as design options to speed up the operation of a computer. Two design philosophies, overlap and replication, represent two major methods used to increase the computer's operational speed. Overlap is effected by the buffer and pipeline mechanism and replication is embodied in the general multiprocessor using buffering and a modified pipeline mechanism in the instruction execution section.

Chapter II describes the architecture or the hardware structure of ILLIAC IV. The ILLIAC IV Array is discussed in broad terms followed by some illustrative problems which point out some of the similarities and differences between problem-solving on sequential and parallel machines. The problems also serve to illustrate how the hardware components are tied

together. Following is a more detailed description of the ILLIAC IV Array, then another illustrative problem (Laplace's equation describing steady-state temperature distribution in two-dimensions) followed by some data allocation considerations; the ILLIAC IV I/O System is discussed briefly, and some conclusions and opinions end the chapter.

Chapter III presents the Assembly Language ASK in a functional and pragmatic way: a problem is described and then only those ASK instructions necessary for the solution are described. In this way the five problems introduce forty ASK instructions and the flavor of the assembly language which, from a programmer's standpoint, is an indication of the capabilities of ILLIAC IV itself. The five problems are: Summing an array of numbers, Finding the maximum value in an array of numbers, Matrix multiplication, Matrix transpose, and Laplace's equation described in Chapter II.

This book will be issued in three volumes. The first three Chapters represent Volume 1, Chapters IV through VII will comprise Volume 2, and Chapters VIII through XI will be Volume 3. Volumes 2 and 3 will be supplied as soon as they are available.

# Abstract

Written specifically for an applications programmer, the book presents a tutorial description of the ILLIAC IV System. Volume 1 contains three chapters -- Background, Hardware Structure, and The Assembly Language--ASK, as well as a Hardware Glossary. Many illustrative problems are used to educate the beginner in the use of the ILLIAC IV System.

# TABLE OF CONTENTS

## Volume 1

| Chapter  | I    | Background 64 pages                                    |  |  |  |  |

|----------|------|--------------------------------------------------------|--|--|--|--|

| Chapter  | II   | Hardware Structure                                     |  |  |  |  |

| Chapter  | III  | The Assembly LanguageASK 90 pages                      |  |  |  |  |

|          |      | Hardware Glossary 10 pages                             |  |  |  |  |

|          |      | Volume 2                                               |  |  |  |  |

| Chapter  | IV   | ALGOL for FORTRAN Programmers (to be supplied)         |  |  |  |  |

| Chapter  | V    | A High-Level LanguageGLYPNIR (to be supplied)          |  |  |  |  |

| Chapter  | VI   | A High-Level LanguageFORTRAN (to be supplied)          |  |  |  |  |

| Chapter  | VII  | Word Formats (to be supplied)                          |  |  |  |  |

| Volume 3 |      |                                                        |  |  |  |  |

| Chapter  | VIII | The Operating System (to be supplied)                  |  |  |  |  |

| Chapter  |      | Utilities (to be supplied)                             |  |  |  |  |

| _        |      |                                                        |  |  |  |  |

| Chapter  | Х    | Test/Repair Equipment and Diagnostics (to be supplied) |  |  |  |  |

| Chapter  | XI   | Physical Characteristics (to be supplied)              |  |  |  |  |

#### Foreword

This book is based upon the many reports and documents generated at the University of Illinois and the Burroughs Corporation during the design and development of the ILLIAC IV computer. In addition, much of the content of the book was influenced by the material offered in the graduate level computer science course, CS 491, "Architecture, Applications, and Languages for a Parallel Computer" as well as the many one-day, two-day and one-week seminars on ILLIAC IV. I learned a great deal from my "students".

I would like particularly to thank Professor Daniel Slotnick and my friend Mr. George Westlund who provided the overall guidance for this book and whose idea it was to create it in the first place. Much specific help was given me by Walt Heimerdinger in the area of hardware structure, and Jim Stevens and John McMillan in the area of ASK. Mike Sher and Cal Corbin helped proofread and make final suggestions before this book when to press. I am also very grateful to Joyce Fasnacht who cheerfully typed and retyped the many versions of the text with incredible accuracy, and who drafted the original versions of all of the figures from my pencil scratchings.

Any errors you may find are not only my responsibility but become yours also. If you inform me of them I will correct them in the next edition.

Stewart A. Denenberg Urbana, Illinois 1971

## CHAPTER I -- BACKGROUND

## TABLE OF CONTENTS

|          |         |                                                                                                | Page                 |

|----------|---------|------------------------------------------------------------------------------------------------|----------------------|

|          |         | A. Summary                                                                                     | I <b>-</b> 1         |

|          | <b></b> | B. A Review of Digital Computing Machines                                                      | <b>I-</b> 2          |

| 1 June 1 |         | T. Duman,                                                                                      | I-2<br>I-3           |

|          |         | d. THE DITTERMED TOPING                                                                        | I-3<br>I-7           |

|          | Ġ.      | 4. Electronic Numerical Integrator and Calculator (ENIAC) .                                    | I-11<br>I-14         |

|          |         | 5. Electronic Delay Storage Automatic Calculator (EDSAC) 6. University of Manchester Computers | I-16<br>I-20<br>I-22 |

|          |         | C. Unconventional Digital Computer Organizations                                               | I-25                 |

|          | E       | 1. Summary                                                                                     | I-25<br>I-30         |

|          |         | a. Buffer                                                                                      | I-30<br>I-36         |

|          |         | i. Summary                                                                                     | I-36                 |

|          | 15      | iii. A Pipeline Adder                                                                          | I-44<br>I-49         |

|          | •}•     | 3. ReplicationThe Multiprocessor                                                               | I <b>-</b> 51        |

|          | 83      | a. Centralize Memory                                                                           | I-52<br>I-53<br>I-55 |

|          |         | 4. ILLIAC IV                                                                                   | I <b>-</b> 58        |

|          |         | References                                                                                     | I-64                 |

|          |         |                                                                                                |                      |

|          | E       |                                                                                                |                      |

|          |         | I-i                                                                                            |                      |

|          | 3       |                                                                                                |                      |

|          |         |                                                                                                |                      |

# LIST OF FIGURES

| Figure        | e e                                                                                                                      | Page              |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|

| I-1.          | Transmission of Data in Babbage's Machine                                                                                | I <b>-</b> 9      |

| I <b>-</b> 2. | Mercury Delay Line or Ultrasonic Store                                                                                   | I-17              |

| I-3.          | Functional Relations within a Conventional Computer                                                                      | I <b>-</b> 26     |

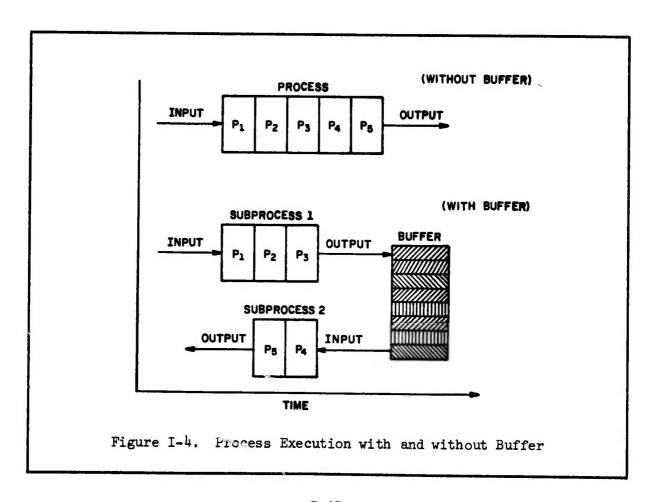

| I-4.          | Process Execution with and without Buffer                                                                                | I-35              |

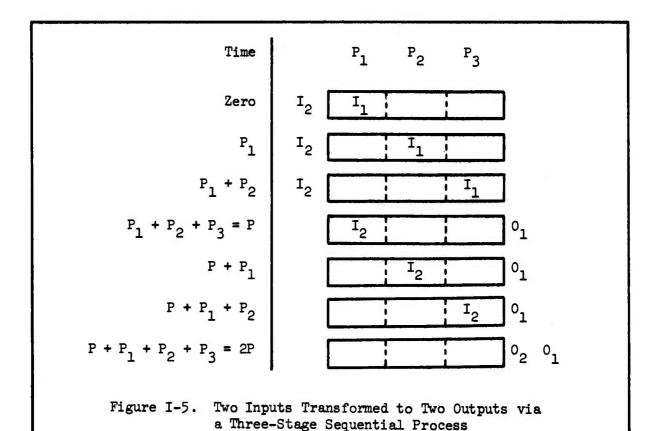

| I-5.          | Two Inputs Transformed to Two Outputs via a Three-Stage Sequential Process                                               | I-37              |

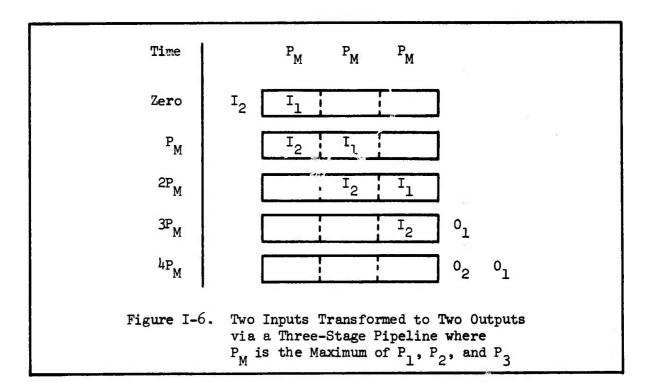

| I <b>-</b> 6. | Two Inputs Transformed to Two Outputs via a Three-Stage Pipeline where $P_M$ is the Maximum of $P_1$ , $P_2$ , and $P_3$ | I <b>-</b> 38     |

| I-7.          | Seven Pairs of Numbers being Added in a Four-Stage Pipeline Adder                                                        | I-48              |

| I-8.          | Functional Relations within a General Multiprocessor                                                                     | I <b>-</b> 51     |

| I <b>-</b> 9. | Multiprocessor with Common (Lumped) Memory                                                                               | I <del>-</del> 52 |

| I-10.         | Functional Block Diagram of Intrinsic Multiprocessor                                                                     | I <b>-</b> 54     |

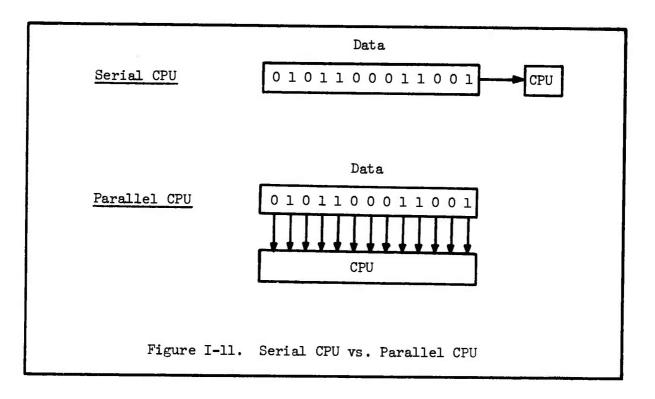

| I-11.         | Serial CPU vs. Parallel CPU                                                                                              | I <b>-</b> 56     |

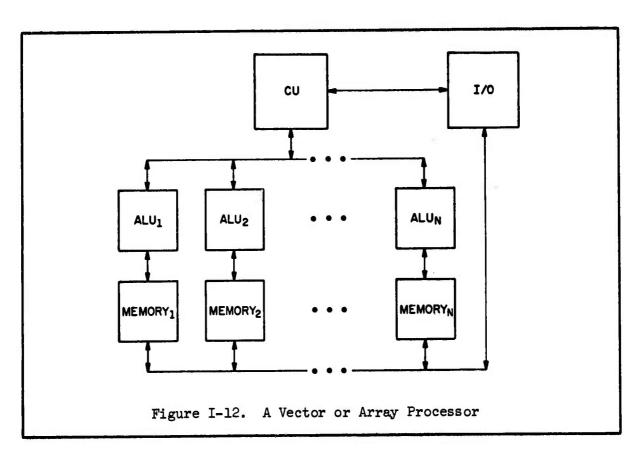

| I-12.         | A Vector or Array Processor                                                                                              | I <b>-</b> 57     |

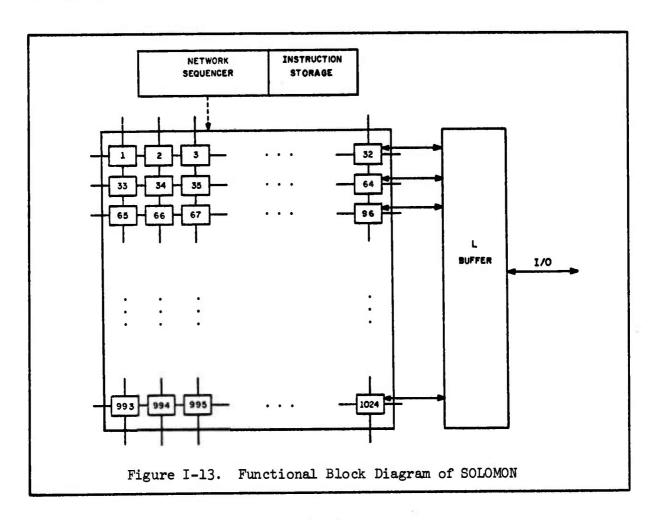

| I-13.         | Functional Block Diagram of SOLOMON                                                                                      | I <b>-</b> 59     |

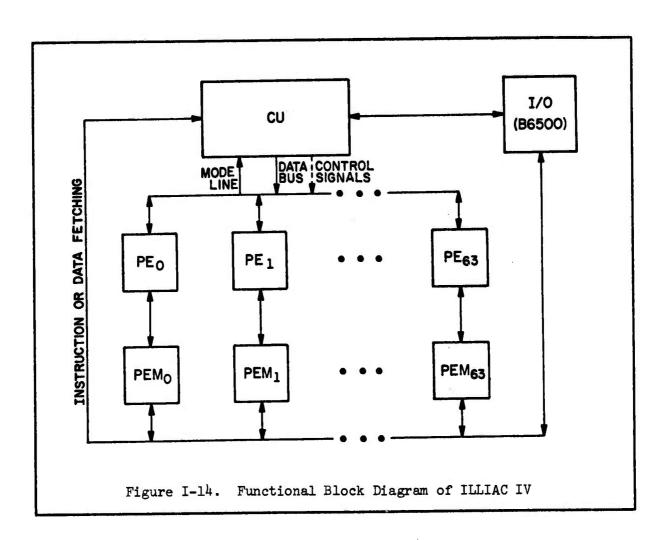

| I-14.         | Functional Block Diagram of ILLIAC IV                                                                                    | I <b>-</b> 61     |

|               |                                                                                                                          |                   |

|               | TABLES                                                                                                                   |                   |

| Table         |                                                                                                                          | Page              |

| I-1.          | Difference Method for Evaluating Polynomial                                                                              | T_h               |

#### CHAPTER I

#### BACKGROUND

#### A. Summary

Chapter I traces out some of the background concepts necessary for an understanding of ILLIAC IV. A short section is devoted to the historical development of digital computers, indicating how computer systems evolved to the Von Neumann state of organization. Also discussed is the tendency computers have had in creating problems themselves. first computers were designed to solve specific applications problems such as computing a table of values for a certain mathematical function or solving a differential equation which described the ballistic path of an artillery shell. As computers became more useful, they started to contribute problems of their own to be solved such as the need for easierto-use programming languages. The most pressing of these problems was the need for faster and faster operating speeds. If the computer could be made to process information at a faster rate, and costs could be held constant, then the per-unit-time cost of processing information would be effectively lowered. The remaining sections of the Chapter describe how Von Neumann organization may be modified to increase operational Two design philosophies to achieve increased speed are discussed: 1) Overlapping the operation of two or more of the functional components of a conventional computer and 2) Replication of one or more of the functional components many times. Since these philosophies are not mutually exclusive, a third option exists whereby both 1) and 2) are effected. Overlap can be achieved by utilizing the Buffer and Pipeline mechanisms; however, the Pipeline is limited to the number of stages into which an operation can be decomposed, and ultimately by the speed of light. The replication philosophy is typified by the general Multiprocessor, but the cost is extremely high. Various re-designs of the Multiprocessor are explored in order to reduce its high cost: Re-centralizing Memory, the Arithmetic and Logic Unit, or the Control Unit. ILLIAC IV is represented as a Multiprocessor with the Control Unit re-centralized. This particular option was chosen for two main reasons: 1) much of the cost of a digital computer is tied up in the Control Unit and 2) there are large classes of problems that can be solved by a single instruction stream which operates on data that can be structured as a vector.

ILLIAC IV also utilizes the Buffer and modified Pipeline mechanisms to overlap the operation of its instruction execution unit.

# B. A Review of Digital Computing Machines

#### 1. Summary

ではないとなっているというというできない。

Perhaps the first computer was a coin. If a computer is a tool used by man to solve a problem, then a coin fits the description. A coin was (and still is) used as a tool to help men make decisions. It is a true binary decision maker: a flip of a coin and a decision is automatically made: heads, one course of action is taken—tails, another. Whether the first computer was a coin, an abacus, Pascal's Calculator or Jacquard's Loom is not argued here; instead the starting point is arbitrarily chosen

with Babbage's machines. The Automatic Sequence Controlled Calculator (Mark I), ENIAC, EDSAC, the University of Manchester Computers, and EDVAC are used to regresent the major chain of machines which evolved to the Von Neumann organization.

# 2. Babbage's Difference Engine and Analytical Engine

## a. The Difference Engine

100

In 1812, when Charles Babbage was an undergraduate at Trinity College, Cambridge, mathematical tables of functions were generated by hand. The production of a table of values for just one mathematical function was a tedious and cumbersome job. A group of over 100 people, called "computers," were trained to follow a finite difference algorithm to compute values of the function over a specific range and for specific interval widths within the specified range.

Let us consider how the function  $f(X) = X^2 + X + 1$  would be calculated over the range  $1 \le X \le 5$  and for an interval width of 1. (See Table I-1.)

It was known at the time that the nth differences of an n-degree polynomial are constant. By convention, the zero-differences  $(D^0)$  are the values of the function.  $D_{\bf i}^0$  is the value of the function at  $X_{\bf i}: f(X_{\bf i}) \equiv D_{\bf i}^0$ . For the simple example used here, when  ${\bf i}=3$ ,  $X_{\bf i}=3$ , and  $D_3^0=13$ . The first differences  $(D^1)$  are found by subtracting previous values of  $D^0$  from succeeding values of  $D^0$ :

Table I-1. Difference Method for Evaluating Polynomial Function  $\chi^2 + \chi + 1$

|          |                  | $f(X) = X^2 + X + 1$ |                |

|----------|------------------|----------------------|----------------|

| <u>i</u> | Xi               | $D_0$ $D_1$          | D <sup>2</sup> |

| 1        | <sub>S</sub> . 1 | 3                    |                |

| 2        | 2                |                      | 2              |

| 3        | 3                | 13                   | 2              |

| 4        | 4                | 21                   | 2              |

| 5        | 5                | 31                   |                |

|                   | Contents of |    |                |  |

|-------------------|-------------|----|----------------|--|

| Step No.          | DO          | Dl | D <sup>2</sup> |  |

| 0 (Initial Value) | 3           | 4  | 2              |  |

| 1                 | 7           | 4  | 2              |  |

| 2                 | 7           | 6  | 2              |  |

| 3                 | 13          | 6  | 2              |  |

| 4                 | 13          | 8  | 2              |  |

| 5                 | 21          | 8  | 2              |  |

| 6                 | 21          | 10 | 2              |  |

| 7                 | 31          | 10 | 2              |  |

$$D_{i}^{1} = f(X_{i+1}) - f(X_{i}) = D_{i+1}^{0} - D_{i}^{0}$$

The second differences are the differences of the first differences and are calculated the same way:

$$D_i^2 = D_{i+1}^1 - D_i^1$$

The top part of Table I-1 shows  $D^0$ ,  $D^1$  and  $D^2$  for the X values. Note that the second differences are constant (the value 2). Also shown is how we can work backwards if we are given  $D_1^0$ ,  $D_1^1$ , and  $D_1^2$  by summing instead of subtracting:

$$D_{i+1}^0 = D_i^0 + D_i^1$$

and

$$D_{i+1}^1 = D_i^1 + D_i^2$$

Therefore, if we have 3 registers to store the values of  $D_0$ ,  $D_1$  and  $D_2$  as we sequentially apply the above two equations we can generate  $D_1^0$  for as long as we wish to compute. All we need are the 3 initial values

$$D_1^0 = 3$$

,  $D_1^1 = 4$  and  $D_1^2 = 2$

In Table I-1, each step is numbered and the direction of addition indicated by an arrow.

The lower part of Table I-1 displays the contents of the three registers,  $D^0$ ,  $D^1$  and  $D^2$  after each step circled in the top part of the table.

It was Babbage's contention that not only could a mechanical machine be built to perform the finite difference algorithm, it would be faster and much more accurate. He had even designed his Difference Engine to print the results directly from the wheels which displayed the numbers, thus eliminating the possibility of a human transcription error.

Babbage fabricated a small Difference Engine which could tabulate a second degree polynomial (or any other function whose second differences were constant) to 8 decimal digits of accuracy. In 1823 he was given a grant by the British government to build a machine that could generate tables for a function whose seventh differences were constant to an accuracy of 20 decimal digits. His ambitious project was never completed. Work stopped in 1833 when Babbage ran into financial difficulties with his engineer who resigned from the project taking with him all of the specially constructed tools for the building of the Engine (under English law at the time, the engineer had the right to do so).

Babbage was probably the first computer designer to run into financial difficulties because the state-of-the-art of technology lagged too far behind the state-of-the-art of conception. His ideas were sound, but his funds were hopelessly inadequate to create the technology which in turn would be used to create his computer.

The Difference Engine was more than just an automatic calculator capable of addition, subtraction and multiplication—it could also perform a procedure or a program. There was only one program that it could perform, however, and that was the finite difference algorithm. From the

point of view of modern computing, the Difference Engine was a singlepurpose computer with no program software; the program was intrinsically

part of the machine, imbedded into the configuration of the gears and

shafts.

## b. The Analytical Engine

The Difference Engine had failed, but Babbage had even greater plans for a new machine, the Analytical Engine. Either he did not realize that his machines could not be built by the existing technology or he was optimistic enough to believe he could supply the ideas for both.

Babbage designed the Analytical Engine to be able to perform more than only one algorithm; so that the <u>program</u> as well as the data could be supplied to the machine as an input, and the machine would process the data according to the instructions of the program.

In order to create a machine of this far-reaching capability, Babbage foresaw the four main functional sections of the modern-day computer:

- · Control Unit

- · Memory Unit

- Arithmetic and Logic Unit

- Input/Output Unit.

The Control Unit was to act on the same principle as the Jacquard Loom Controller: a sequence of plaques with holes punched in them drawn

over a drum by chains. Where Jacquard's Loom used a particular combination of holes in a plaque to specify a weaving operation, Babbage's Difference Engine used each plaque to store an instruction which specified an arithmetic operation. The plaques were drawn over a drum one at a time and the pattern of the holes was sensed mechanically. Each plaque instructed the Engine to perform one well-defined operation and a set of plaques, therefore, constituted a program. Groups of sets of plaques represented a Program Library.

CONTRACTO NOTES

Not only did Babbage design a machine that would execute a program of instructions, he also included the <u>Test-and-Branch</u> type of instruction which is at the very heart of using a program to solve a problem. In his plan, the Analytical Engine had the ability to roll the chain of instruction plaques forward or backward depending on whether the contents of a specified register turned negative during execution of the program. Rolling the chain in either direction is equivalent to a "jump" in the opposite direction in the program.

The Test-and-Branch instruction provides the programmer with an "alternate route" capability while his program is executing. Different sections of the program may be entered and executed based on the values of numbers that were computed in previous sections of the program. An additional benefit of a Test-and-Branch capability is that it affords the programmer a shorthand by which he can specify a large number of program operations with a small number of instructions. By decrementing or incrementing a register until it reaches a specified value, a section of

the program can be executed repeatedly. Without the Test-and-Branch type of capability, a programmer would have to specify every operation with at least one instruction.

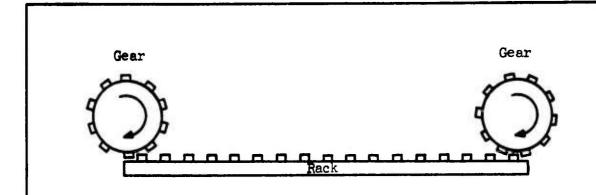

The Memory or "store" as Babbage referred to it, consisted of wheels. The position of a wheel denoted the value it was storing. Numbers were transmitted to and from the "store" by means of racks. The racks were cut to engage the gears of a wheel so that the position of one wheel could be transmitted to another. The racks, of course, could be connected to rods, shafts, or other racks to further transmit the motion. (See Figure I-1.) Since each wheel would store I decimal digit and Babbage proposed

Figure I-1. Transmission of Data in Babbage's Machine

that the "store" have a capacity of 100 numbers of 50 decimal accuracy, this meant the Engine would have 50,000 wheels. Since the instructions were not stored in the memory but were punched into the plaques and thus would not be modified during program execution, Babbage's Analytical Engine was not a stored-program computer.

The Arithmetic Unit was called the "mill". Babbage went to great pains to optimize the design of the mill, particularly the problem of carrying when the sum of two numbers is greater than nine and a digit must be carried over to the next significant position. With customary fastidiousness and foresight, Babbage represented the algebraic sign of a number as a separate wheel which would not be connected to the other wheels during carries.

The Input/Output was to be effected by punch cards much like the punch cards or plaques that supplied instructions to the Engine. Some of the input was to be done manually—the initial settings of the wheels of the "store" were to be done by hand. Babbage also considered the possibility of printing output directly from the wheels of the "store" as he had with the Difference Engine. By embossing the digits on each wheel, they could be inked at the end of a calculation and the results transferred directly to paper. This not only made the results neat and legible but completely bypassed the possibility of a human transcription error.

Babbage estimated the following operation times:

Addition/Subtraction 1 second

Multiplication (50 decimals by 50 decimals) 60 seconds

Division (100 decimals by 50 decimals) 60 seconds

The description for the Analytical Engine prompted some scientifically-inclined people of the day to try their hand at programming.

L. F. Menabrea, a General in the Italian Army, was at the Military Academy

in Turin when he heard Babbage speak on his Analytical Engine to the Italian mathematicians. Menabrea demonstrated how one would solve two simultaneous equations in two unknowns with Babbage's Analytical Engine.

Lady Lovelace, Lord and Lady Byron's daughter, devised many programs; among them, one to calculate Bernoulli numbers from a recurrence formula. In order to calculate the Bernoulli number  $B_n$ , n+1 operations must be performed. Lady Lovelace described how she could store the quantity "n" in a register and decrease it by 1 each time an operation within the cycle was performed; when the number finally turned negative, the cycle had been repeated n+1 times and control could be passed to the next part of the program. She had invented the concept of a loop.

Although Babbage did not build his Analytical Engine, he left the detailed drawings and notebooks which are currently in the Science Museum at South Kensington, England. He defined most of the concepts used in a modern computer, including the most important one which Jacquard had sensed before him: it was possible to build a machine that would automatically simulate a process if the process could be described in terms of a sequence of well-defined operations.

# 3. Automatic Sequence Controlled Calculator (Mark I)

Babbage's work was soon forgotten, because his Analytical Engine was never completed. In 1937, Professor Howard Aiken designed and developed an automatic calculator based on components currently available in IBM

punched card equipment. In cooperation with IBM, Aiken built and presented the calculator to Harvard University in 1944. Harvard named the calculator "Mark I".

The Control Unit of Mark I was primarily a paper tape reader.

Each instruction was punched into a paper tape that was 24 holes wide and fed past a set of 24 rods that made an electrical contact if a hole existed. The first version of Mark I had no Test-and-Branch capability; the best it could do was compare two numbers in different registers and if one was greater, the machine would stop. We might say the machine had a Test-and-Stop instruction.

Mark I was later modified to include a conditional type of instruction. The conditional instruction caused control to be switched from the currently executing paper tape to any of three alternative tapes if the contents of a specified register were zero. Once control had passed to a specified alternative tape, the program was executed from instructions punched on that tape until either the program ended or control was passed back to the original or yet another tape. If control was passed back to the original tape, it would start executing where it left off by virtue of the fact that its physical position in the tape reader had not changed. Endless tapes were used for looping. This method of passing control to a new tape was faster than the method of rolling a set of cards backward or forward as Babbage had proposed, but Babbage's technique is still conceptually closer to the kind of program control that is used today. Neither Mark I nor Babbage's Analytical Engine were stored program computers.

The Storage section of Mark I consisted of wheels as did the Babbage Machine. There were 72 Accumulator Registers each capable of holding a 23-digit computed value, plus 60 sets of switches for holding constants. The switches were set manually and were not under program control.

As with Babbage's Engine, numbers were transmitted to and from Storage by rotating shafts connected to the wheel storage.

Input-Output consisted of a typewriter as well as punched-cards.

The operation speeds of Mark I were:

Addition/Subtraction .3 seconds

Multiplication (23 digits by 23 digits) 6 seconds

Division 11.4 seconds

There was also built-in hardware which computed:

Sin (X) in 60 seconds  $10^{X}$  in 61.2 seconds and  $\log_{10}$  X in 68.4 seconds

all to 23 decimals of accuracy.

Mark I contained more than 760,000 parts and the sound of its thousands of electromechanical relays in operation has been likened to a roomful of ladies knitting.

# 4. Electronic Numerical Integrator and Calculator (ENIAC)

In 1946, the first electronic computer was built by J. Presper Eckert and John W. Mauchly at the University of Pennsylvania. ENIAC was built for the U. S. Army to calculate ballistic tables by integrating an ordinary differential equation. Another type of problem, the interaction of shock waves in a fluid, prompted John Von Neumann to modify some of the logical design of ENIAC.

The Memory Storage section consisted of tubes-triodes and pentodes. The flip-flops were triodes and along with the pentodes (that were used as "AND" circuits and "OR" circuits), there were over 18,000 vacuum tubes and about 1,500 relays in a 20 feet by 40 feet box for the entire machine. In addition there were about 6,000 switches for storing constants that could not be changed by the program.

The Control section consisted of a 100 kc/sec oscillator which produced pulses 2 µsec wide. As the clock generated pulses, the program was executed through the many wires that connected one part of the machine with the others. The programmer did the actual wiring through plugs, sockets, and switches; the various components of the machine were "stimulated" or not depending on whether a wire carrying a pulse reached that component. For example, if an accumulator received a program pulse it would be stimulated to add. Since both instructions and data were represented as trains of electronic pulses, a conditional operation on the sign of a number could easily be programmed by running the wire that carried the sign bit of that number to an accumulator. If a negative sign

is represented by the presence of a pulse, then the accumulator would be "stimulated" if the number was negative; if the number was positive, no pulse would appear and the accumulator would not be "stimulated" and hence not enter into the program. Thus ENIAC had its program "wired" into its hardware. ENIAC also had external switches which caused certain operations to be performed more than once, giving the programmer a looping capability (there were extra switches so that a programmer could loop within loops).

100

ENIAC had an advantage over Mark I in terms of speed; once initial program wiring had been done, instructions could be executed at electronic speed rather than at the speed of a paper tape reader. Changing programs, however, meant a massive rewiring job. Many hundreds of wires had to be re-plugged in order to instruct the machine to perform a different algorithm. At the time it was recognized that switch settings and plugged-wire connections could also be coded in the same way that numbers were coded. If a large capacity storage device were to become available, then the program as well as the data could be stored in the machine. Although ENIAC had only 20 storage locations, one must remember that ENIAC was a special purpose machine built to solve a specific problem—to compute values for ballistic tables, and it performed this function very well.

Each of the 20 storage locations was also an accumulator which could add, subtract, store or fetch independently and simultaneously so that its effective calculating time was very creditable:

Addition/Subtraction 200  $\mu s$  Multiplication (10 decimals by 10 decimals) 2.8 ms Division 6 ms

The Input was 80 column IBM cards and the output was either cards or lights on a display panel.

Although ENIAC actually had its program stored inside of it in the form of wire connections, it was not a stored program machine. The definitive characteristic of a stored program computer is not the fact that a program is stored internally in the computer as opposed to outside on paper tape, for instance. A stored program computer has the ability to modify its instructions as well as its data while it is executing the instructions since both the instructions and the data are "inside" the machine using the same storage medium. Looping and indexing can be done by modifying the address field of an instruction while the program is executing. Instructions can modify, destroy or create other instructions as the program runs. (The stored program concept was responsible for the term "word" coming into use to describe what existed at a location in the memory store. In order to avoid specifying whether the content of a given storage location was to be regarded as a number or an instruction, it became convenient to refer to it as a word of storage.)

# 5. Electronic Delay Storage Automatic Calculator (EDSAC)

EDSAC was the first <u>operational</u> stored program, electronic computer. EDSAC ran its first program at the University of Manchester in May of 1949. The EDVAC, discussed in the next section, was the first stored program, electronic computer to be <u>designed</u>. (Design started on the EDVAC in 1945, while design started on EDSAC at the end of 1946.)

Both EDVAC and EDSAC are considered to be IAS computers since their development was guided by the reports generated at the Institute for Advanced Study (IAS) at Princeton, New Jersey by John Von Neumann and his colleagues in 1945. IAS eventually put forth their own computer in 1952 and the ILLIAC I (University of Illinois), Johniac (RAND Corporation), MANIAC (Los Alamos) and WEIZIAC (Weizman Institute of Israel) soon followed and were patterned after the IAS machine. They all had addition times of about 60 μs and multiplication times on the order of 700 μsec.

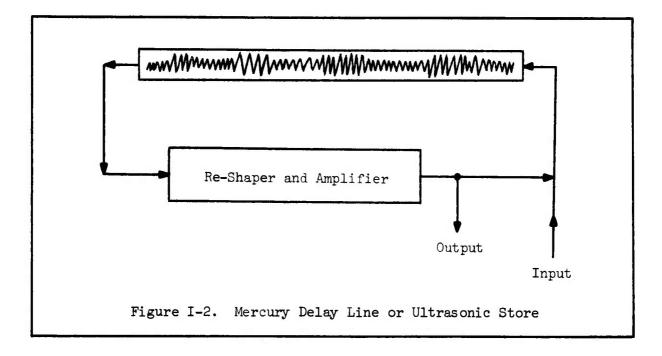

The storage device which permitted both data and instructions to be stored together in EDSAC was a mercury delay line or ultrasonic store. (See Figure I-2.)

A mercury delay line is a tube filled with mercury. A wire coming into the tube carries a train of electronic pulses which are transformed into mechanical vibrations by means of a piezo-electric crystal. The vibrations are transmitted through the column of mercury to another crystal at the other end of the tube which converts the mechanical vibrations into electronic signals. These signals are a bit distorted at this point, so they pass through an electronic network which reshapes and amplifies the pulses before sending them back through the tube again.

The length of the tube and the velocity of a disturbance in mercury define the memory cycle time. The number of bits that can be stored depends on the pulse rate of the clock. A major disadvantage of ultrasonic storage is the long access time. The time required for an accumulator to access a bit in storage varies from near zero, to the time it takes a bit to travel the length of the tube. The access time is on the average, one half the time it takes for a bit pulse to travel from one end of the tube to the other.

Another problem one encounters using the ultrasonic store is the interleaving of instructions and data in the pulse train so that the arithmetic and logic unit is waiting for data a minimum amount of time. (For example, it would not be wise to have an instruction that loaded the accumulator with a number that was stored ahead of the instruction; the accumulator would have to wait a whole memory cycle to get hold of that number.) The practice of laying out the instructions and data in the ultrasonic store in an optimal manner was called optimum programming.

Although vacuum tube flip-flops would have provided a fasteraccess storage medium, they were not yet economical. EDSAC had 30 mercury

delay lines, each of which could hold thirty-two 17-bit numbers. There

were also short mercury "tanks" that held just one number and were used as

registers. The access time in these registers containing only one number

circulating through a tank was shorter than the access time to a number

circulating in main memory. For the main memory, the circulation time or

memory cycle time was 1.1 ms. The other operation times were:

Addition/Subtraction

1.5 ms

Multiplication

4 ms

Division was a subroutine which had a variable operation time.

EDSAC had a single-address instruction format which necessitated the placing of an accumulator in the arithmetic and logic unit to accumulate the results of the one-address operations. EDSAC had two types of Test-and-Branch instructions; one which branched on the contents of a storage location being less than zero and the other which branched on the contents being greater than or equal to zero. It was admitted at the time that even though two tests were redundant, the extra one was included for programming convenience. It must have been around this point in time that the programming profession began.

Input and output were combined on a teleprinter unit which could both type and punch five-position paper tape. Input data could be punched onto paper tape which in turn was fed into EDSAC and output could be displayed via the typewriter part of the teleprinter.

# 6. <u>University of Manchester Computers</u>

EDSAC was merely the <u>name</u> given to the world's first operational computer developed at the University of Manchester. As time passed, EDSAC evolved into a computer system with refinements that expanded the state-of-the-art of computing.

The Williams Tube memory was developed at Manchester in order to increase the speed of memory access. Basically the tube was just a cathode ray tube (CRT) that could store an electrostatic pattern of bits on the face of the tube. Moreover, the bits could be fetched or changed by directing the cathode ray to the appropriate place on the tube. The tubes at Manchester held 1024 spots and could therefore represent 1024 bits of information; the access time was on the order of microseconds.

One of the uses of the Williams tube was what we now call indexing. A Williams tube, called the B-tube (presumably because the letters A and C were already used) was used to represent two registers. When the programmer wrote an instruction, he also referenced the contents of either one of these two registers. The contents of the specified register was added to the address field of the instruction. In practice, the contents of one of the registers was always zero so that when the programmer did not wish to modify his address field, he could reference the register containing the zero value. At the time, some people felt the B registers were of little scientific value and that they were included merely for programmer convenience. It seems the hardware design philosophy was

beginning to change—a problem that now deserved consideration was programming ease. Computers were still being built to solve specific problems, but they were starting to create problems of their own to be solved. The problem set had started to divide into "applications" problems and "systems" problems.

The Manchester computers added a 128 word drum--each word was The drum was slower than tube memory but it was cheaper in terms of cost per bit stored. Where the access time to tube memory was on the order of microseconds, access to the drum was measured in milliseconds. Therefore, the programmers at the University of Manchester were among the first to contend with the problems of memory hierarchy and costeffectiveness in computer operations: if you have a larger, cheaper, and slower memory and a smaller, more expensive, and faster memory, both of which can be accessed by the arithmetic unit, you must consider the problem of making the most effective use of the total computer. If your criterion for effective use is to minimize the idle time of the arithmetic unit then you must keep it supplied with data as fast as you can. One method of achieving this is to feed the small, fast storage from the large, slow one, transferring data in large blocks. The arithmetic unit then fetches from the faster storage. Results from the arithmetic unit are stored to the faster memory, if possible, and eventually can be sent to the large, slow memory.

## 7. Electronic Discrete Variable Automatic Calculator (EDVAC)

EDVAC was the first stored program computer to be <u>designed</u>. In 1945 a report, "Preliminary Discussion of the Logical Design of an Electronic Computing Instrument" by A. W. Burks, H. H. Goldstine, and J. Von Neumann, was prepared under contract to the ENIAC project. This report described the concept of the stored program computer, and made the recommendation that instructions and data be coded using a binary representation.

The report pointed out that although the ENIAC appeared to be a decimal machine, the decimal capability was built up from binary components grouped to respond as decimal components. It was recommended that numbers and instructions be represented inside the machine in terms of the existing binary components and that conversion to a decimal representation be performed in the Input/Output phase by means of a program. In other words, it was proposed to use software rather than hardware to take care of converting from the binary to decimal system and back. The report was distributed at a summer meeting at the University of Pennsylvania in 1946 and was a strong influence on the design of all future computers, in particular EDSAC and EDVAC.

As its primary storage, EDVAC used ultrasonic delay tanks similar to the mercury delay lines used by EDSAC. A tank was 58 cm long and it took  $384~\mu s$  for a disturbance to travel that length, thus the memory cycle time was  $384~\mu s$ . The clock rate was 1 Megacycle so that the tank could hold  $384~\mu s$  or bits of information. Each number was  $44~\mu s$  bits long

followed by 4 "blank" pulses so that a tank stored 8 numbers. The total EDVAC memory was 128 tanks and could store 1024 numbers.

A wire recorder acted as a secondary store with a capacity of 20,000 numbers. As with EDSAC, a memory hierarchy existed with a smaller, faster tank memory to be traded off against a larger, slower wire memory. Numbers were transferred from the wire memory to tank memory in blocks of 50 to 100 so as not to slow the arithmetic and logic unit.

EDVAC used a four-address instruction format. The address field of an instruction, instead of denoting a single address, denoted four locations: the first two locations signified the addresses of the two operands to be used in a binary operation (a binary operation is an operation such as addition, subtraction that involves the use of two operands), the third address indicated where the result was to be stored and the fourth address pointed to the location where the next instruction to be executed was stored. The fourth address has proved to be superfluous if the computer has a test and branch capability and otherwise executes its instructions in sequence. (Assuming that the instructions are stored in a memory where the time to fetch an instruction is not dependent on where in the memory it is stored—this type of memory is sometimes called "random—access".) EDVAC pointed the way to a three-address scheme whereby the instructions were executed in sequence and the three addresses were used in the same way as the first three addresses described above.

A three-address scheme can be very powerful if the programs involve many three-step operations such as A = B + C. However, the trend

was to grow away from a three-address scheme which was more useful in scientific problems than commercial ones (as well as being more costly than a one-address scheme) and eventually settled into the familiar one-address scheme we have on most current generation machines.

Here is another example of the applications problems creating systems problems concerning the shaping of the design of the machine. It would not be useful to design a two-address machine if there were no problems that could be solved with that kind of instruction format. The repertoire of instructions has also evolved under the demands of the problems to be solved. Character handling instructions would not have been implemented so soon and so fully if all problems had been scientific.

The average operation times for EDVAC were:

| Addition/Subtraction | 864 µs |

|----------------------|--------|

| Multiplication       | 2.9 ms |

| Division             | 2.9 ms |

EDVAC appears to have the unhappy distinction of being the first computer to experience large time delays in fabrication even though the proposed design was well within the technical resources available at that time. EDVAC design was started in 1945, but was not considered to be a working machine until 1952. M. V. Wilkes attributes the problems to the much faster clock rate used in EDVAC which necessitated higher quality circuitry that could handle pulses of shorter duration without degradation.

It appears that there is a principle of natural selection that applies to the evolution of computers. Computers are designed to respond to the needs of the environment. If the environment changes too rapidly, some classes of computers may be subject to the fate of the dinosaur. More important, the environment is not a closed system outside of the computer; the computer, as it responds to its environment becomes a part of the environment, and creates new problems to be solved. Machines are then created to solve these problems. We create tools to solve problems that our tools have created.

#### C. Unconventional Digital Computer Organizations

#### 1. Summary

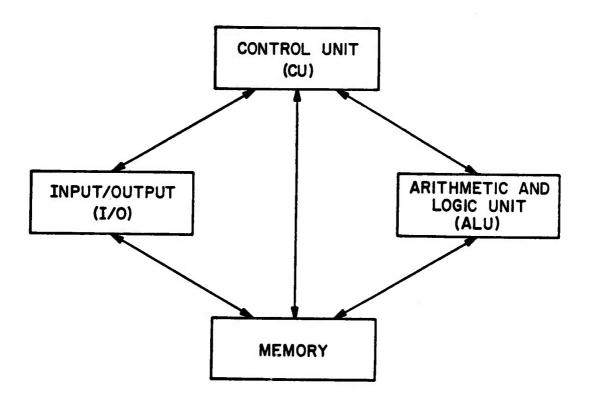

After EDVAC, in the early 1950's, the deluge began. Hundreds, then thousands of computers were manufactured; still, they were generally organized on Von Neumann's concepts. The conventional or Von Neumann organization is shown and described in Figure I-3. Memories became cheaper and faster, and the concept of archival storage was evolved; Control and Arithmetic and Logic Units became more sophisticated; I/O devices expanded from typewriters to magnetic tape units, disks, drum and remote terminals. But the four basic components of a conventional computer (Control Unit, Arithmetic and Logic Unit, Memory and I/O) were all present in one form or another.

The turning away from the conventional organization came in the middle 1960's when the law of diminishing returns began to take effect in

Figure I-3. Functional Relations within a Conventional Computer

The Control Unit (CU) has the function of fetching instructions which are stored in Memory, decoding or interpreting these instructions, and finally generating the microsequences of electronic pulses which cause the instruction to be performed. The performance of the instruction may entail the use or "driving" of one of the three other components. The CU may also contain a small amount of memory called registers that can be accessed faster than the main Memory. The ALU contains the electronic circuitry necessary to perform arithmetic and logical operations. The ALU may also contain register storage. Memory is the medium by which information (instructions or data) is stored. The I/O accepts information which is input to or output from Memory. The I/O hardware may also take care of converting the information from one coding scheme to another.

The CU and ALU taken together are sometimes called a CPU or Central Processing Unit.

the effort to increase the operational speed of a computer. Up until this point the approach was simply to speed up the operation of the electronic circuitry which comprised the four major functional components. (See Figure I-3.)

Electronic circuits appear to be limited in their speed of operation by the speed of light (light travels about one foot in a nanosecond) and many of the circuits were already operating in the nanosecond time range. So, although faster circuits could be made, the amount of money necessary to produce an increase in speed was not justifiable in terms of the small percentage increase of speed.

At this stage of the problem two new approaches evolved:

1) Overlap. The hardware structure of the conventional organization was modified so that two or more of the major functional components (or subcomponents within a major component) could overlap their operations. Overlap means that more than one operation is occurring during the same time interval and thus total operation time is decreased.

Before operations could be overlapped, control sequences between the components had to be de-coupled. Certainly the Control Unit could at least be fetching the next instruction while the Arithmetic and Logic Unit was carrying out the present one.

2) Replication. One of the four major components (or subcomponents within a major component) could be duplicated many times.

(Ten black boxes can produce the result of one black box in one-tenth of the time if the conditions are right.) The replication of I/O devices, for example, was a step taken very early in the evolution of digital computers--large installations had more than one tape drive, more than one card reader, more than one printer.

Since the above two philosophies do not mutually exclude each other, a third approach exists which consists of both of them in a continuously variable range of proportions.

The overlapping philosophy was implemented largely through the Buffer and Pipeline mechanisms. The Pipeline mechanism breaks down an operation into suboperations or stages and decouples these stages from each other. After the stages are decoupled they can be performed simultaneously or, equivalently, in parallel. The Buffer mechanism allows an operation to be decoupled into parallel operation by providing a place to store information.

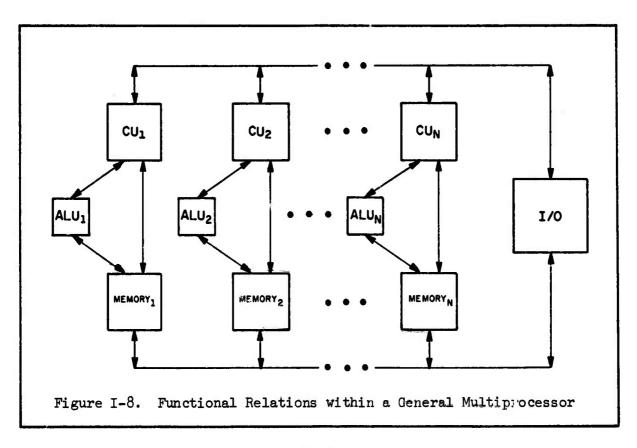

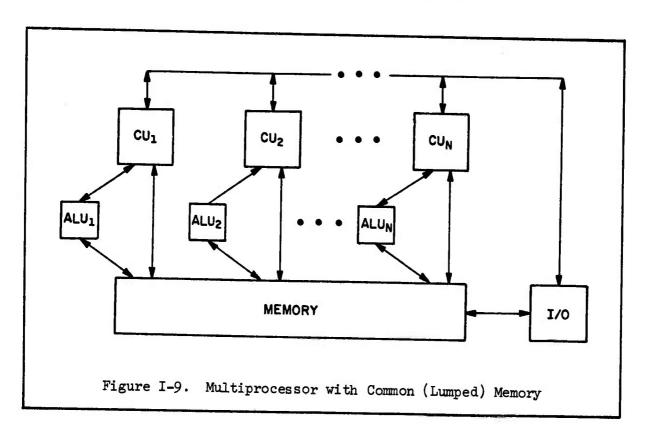

The replication philosophy is exemplified by the general Multiprocessor which replicates three of the four major components (all but

the I/O) many times. The cost of a general Multiprocessor is, however,

very high and further design options were considered which would decrease

the cost without seriously degrading the power or efficiency of the system.

The options consist merely of re-centralizing one of the three major

components which had been previously replicated in the general Multiprocessor-the Memory, the Arithmetic and Logic Unit or the Control Unit.

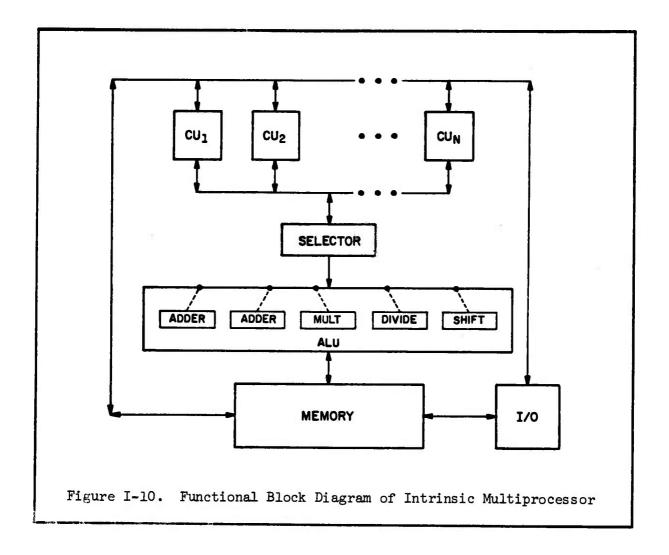

Centralizing the Control Unit gives rise to the basic organization of a

Vector or Array Processor such as ILLIAC IV. This particular option was

chosen for two main reasons:

- 1) Cost. A very high percentage of the cost within a digital computer is associated with Control Unit circuitry. Replication of this component is particularly expensive and therefore centralizing the Control Unit saves more money than can be saved by centralizing either of the other two components.

- 2) There is a large class of both scientific and business problems that can be solved by a computer with one Control Unit (one instruction stream) and many Arithmetic and Logic Units. The same algorithm is

performed repetitively on many sets of different data; the data is

structured as a vector and the vector processor of ILLIAC IV operates on

the vector data. All of the components of data structured as a vector are

processed simultaneously or in parallel.

ILLIAC IV also utilizes the Buffer and Pipeline mechanism to overlap the execution of instructions. This allows a further increase in operational speed as both the replication and overlap design philosophies are applied simultaneously.

#### 2. Overlap Mechanisms

#### a. Buffer

ではなかがからない。最近のないのでは、一条人が大人となって

A buffer is a mechanism which allows a process to be broken down into subprocesses so that the execution of the subprocesses can be overlapped.

Let us use an analogy to demonstrate what a buffer is and why we would like to use one:

Suppose you are mowing your front lawn and you have a bag attached to your mower to collect the grass clippings. Each time this bag fills up, you must stop the mower, detach the bag, and walk around to the back of your house where the trash barrels are. You must then empty the bag of accumulated clippings into the trash barrel, walk back to your mower, attach the wag, and continue mowing.

After some time you come to the realization that you are spending a lot of your time detaching the bag, walking to the trash barrels, emptying the bag, walking back and re-attaching the bag. You remember that you also own a large wheelbarrow that could hold many bag-loads of grass clippings. You now recognize the option of placing the wheelbarrow on the front lawn, and when the grass bag becomes full, you could walk over to the nearby wheelbarrow and empty the bag into the wheelbarrow. When the wheelbarrow became full, then you would have to push it to the trash barrels behind the house, empty the wheelbarrow, and push the wheelbarrow back to the front lawn.

Very naturally the question arises: How many bag-loads must the wheelbarrow be able to hold to justify its use? Fortunately, this problem is very easily solved. Let us look at the times associated with each method.

### Method 1: No wheelbarrow used

$T_1$  = Time to detach bag from mower

T2 = Time to walk from Mower to trash barrel

$T_{3}$  = Time to empty bag into trash barrel

$T_{l_1} = T_{l_2} = Time to walk back from trash barrel to mower$

$T_5 = T_1 = Time to attach bag to mower$

#### Method 2: Wheelbarrow is used as a Buffer

$T_6 = T_1 = Time to detach bag from mower$

$\mathbf{T_7}$  = Time to walk from mower to wheelbarrow

$T_8 = T_3 = Time$  to empty bag into wheelbarrow

$T_9 = T_7 = Time to walk from wheelbarrow to mower$

$T_{10} = T_1 = Time to attach bag to mower$

$T_{11}$  = Time to push wheelbarrow to trash barrel

$T_{12}$  = Time to empty wheelbarrow into trash barrel

$T_{13} = T_{11}$  = Time to push wheelbarrow from trash barrel to front lawn

(Even though the wheelbarrow or bag is lighter on the walk back from the trash barrel, we are assuming it will take the same time as the walk to the trash barrel since grass clippings are very, very light. We also equate the time to attach a grass catcher bag and the time to detach it—

based on actual experience.) Finally, in order to relate all the times  $(T_1 \text{ through } T_{13})$  to each other we assume that the wheelbarrow holds N bag-loads. Therefore, repeating <u>Method 1</u> N times is equivalent (in terms of area of lawn mowed) to performing <u>Method 2</u> once.

The question then becomes: When is

Total time for Method  $1 \ge \text{Total}$  time for Method 2?

or for what value of N is

$$N(T_1 + T_2 + T_3 + T_2 + T_1) \ge N(T_1 + T_7 + T_3 + T_7 + T_1) + T_{11} + T_{12} + T_{11}$$

which reduces to

$$N \geq \frac{2T_{11} + T_{12}}{2(T_2 - T_7)}$$

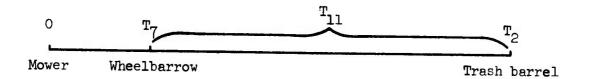

We can see from the diagram below that  $T_2 > T_7$  and assuming  $T_{11} = T_2 - T_7$ ,

we therefore arrive at

$$N \geq \frac{2T_{11} + T_{12}}{2T_{11}}$$

so that in order for Method 2 to be feasible, the wheelbarrow must hold N bag-loads where

$$N \geq 1 + \frac{T_{12}}{2T_{11}}$$

We now see that the size of our buffer wheelbarrow depends only on  $T_{11}$  and  $T_{12}$  or viewed somewhat differently, that the larger N is (the bigger the wheelbarrow we have) the less we have to worry about the effect of  $T_{11}$  and  $T_{12}$ .

If we now enlist another person to help us by emptying the wheelbarrow when it gets full and bringing it back in time to receive the next bag-load, this will reduce the total time of Method 2 by making  $T_{11} = T_{12} = 0$  since these subprocesses are being performed simultaneously with the other subprocess times. Now the question of what size N justifies Method 2 over Method 1 becomes: For what N is:

$$N(T_1 + T_2 + T_3 + T_2 + T_1) \ge N(T_1 + T_7 + T_3 + T_2 + T_1)$$

Using the same reasoning as before we see that

$$2N(T_2 - T_7) \ge 0$$

This relation holds true for all N since  $T_2 > T_7$ . Therefore, this scheme of having a helper who runs the wheelbarrow is a better way to mow a lawn than by yourself. One may have guessed that fact intuitively; however, it is not always clear how a process can be broken down into autonomously performed subprocesses as it is with this particular analogy.

This analogy, although simple-minded, does illustrate what a buffer is and how it works: If a process consists of a series of sub-processes and this process takes "too long" from beginning to end, we can speed up the process time by dividing the total process into at least two subprocesses each of which control themselves autonomously. Between the two subprocesses we place a buffer so that the output from subprocess 1 goes into the buffer and the input to subprocess 2 comes from the buffer. Since the two subprocesses operate autonomously they speed up total process time by overlapping (in time) their performance. The buffer acts as a decoupler of control between subprocess 1 and subprocesses 2 and a place to save things which must be passed between the subprocesses.

It may usually turn out in practice that one process occurs at one rate of speed while another occurs at a greatly different rate of speed. In this case, the processes already existed as separate and distinct, and the placing of a buffer between them is necessary only to insure that the high speed process is not held up by the low speed one. The placing of a buffer between the processes again decreases the total process time by overlapping operations. (See Figure I-4.)

Suppose, for example that subprocesses  $P_1$ ,  $P_2$  and  $P_3$  occur at a very fast rate and that  $P_4$  and  $P_5$  occur slowly. A buffer could be placed between them as shown in the lower part of Figure I-4 and the  $P_1P_2P_3$  process would not be held up waiting on  $P_4$  and  $P_5$ .

Buffers may have another effect on autonomous processes. They not only speed up the rate at which information flows through the

two-process system, they may smooth out the rate of information flow. Without the buffer, one process must wait on another and the outputs of the first process appear and then must wait a variable time until accepted by the second process. This results in a "jerky" flow of information through the system. The buffer acts to accept outputs from the first process as soon as they are generated and will save these outputs until the second process is ready to accept them.

Summing up: a buffer decouples control between a previously sequential set of processes, transforming them into at least two parallel or simultaneous processes; and provides a place to store information which must be passed between the processes.

#### b. Pipeline

### i. Summary

A sequential process can be viewed as a black box that accepts inputs and produces outputs with the added stipulation that the black box cannot accept a new input until the output has been generated for the previous input. In other words, the black box is tied up all of the time in processing just one input.

As an example let us consider a black box (an Adder) that adds two numbers together. Say there are two inputs (the numbers to be added) and one output (the result). If it takes M seconds for the Adder to perform the operation it will take N \* M seconds to add N pairs of numbers. However, if the Adder would accept additional operands to be added while the ones ahead were still in the box then the total time to add N pairs of numbers would certainly decrease. We can do this if the add operation can be broken down into independent stages; as soon as an operand passed through the first stage, the next pair of operands could be accepted by the Adder. This method of dividing the adder into stages and letting the stages run independently is called a "pipeline." The total time to process N operands is speeded up because, once all of the stages in the pipeline are full, results appear out of the end of the pipeline in time increments equal to the processing time of the slowest stage.

#### ii. Background

The pipeline mechanism can be applied to a process that is able to be broken down into two or more stages that can operate independently; the only dependence between stages is that the output of a previous stage becomes the input to a succeeding stage. For example, suppose we have a process that upon closer inspection can be viewed as being made up of three subprocesses. If each subprocess time is  $P_1$ ,  $P_2$  and  $P_3$  then it takes  $P = P_1 + P_2 + P_3$  units of time to transform an input to an output of the process, and consequently if we have N inputs to process then it will take  $N(P_1 + P_2 + P_3)$  units of time to complete the job. Figure I-5 shows how two inputs  $I_1$  and  $I_2$  proceed through our example three-stage sequential process. The outputs  $O_1$  and  $O_2$  are both ready after 2P units of time.

Now let us apply the pipeline mechanism to our example. First we decouple each subprocess by placing a one item "holding buffer" after each subprocess; when a subprocess or stage has completed its job, it places its output into its holding buffer. When all stages are finished they simultaneously pass their outputs to the input part of the next stage. Although this slows the operation of the pipeline down to the rate of the slowest stage, inputs do not have to wait outside the process until the previous input is completely finished—inputs can enter into the process as soon as the first stage has passed its results to the second stage. Since the stages have been decoupled, they can be processing different items or operands simultaneously. Each item moves through the stages of the pipeline or pipe in a semi-finished state of completion (not holding up a following operand) until it appears at the end of the pipe completely processed. See Figure 1-6 which shows how two inputs produce two outputs in a three-stage pipeline.

4

It takes  $P_M + P_M + P_M$  units of time to make the initial filling of the pipeline—after that a finished item appears at the end of the pipe every  $P_M$  units of time where  $P_M$  is the maximum of  $P_1$ ,  $P_2$  and  $P_3$ . Thus the time to process N items via the pipeline mechanism for our 3 stage example is  $3P_M + (N-1) P_M$  units of time.

We can now ask the question (as we did with the Buffer): for what value of N is the sequential process time greater than the pipelined process time, i.e., for what value of N is:

$$N(P_1 + P_2 + P_3) > 3P_M + (N-1) P_M$$

or

$$N(P_1 + P_2 + P_3) > (N+2) P_M$$

Let us say that  $P_{M} = P_{2}$ , then

$$N(P_1 + P_3) + NP_M > NP_M + 2P_M$$

or

$$N > \frac{2P_M}{P_1 + P_3} = \frac{2P_2}{P_1 + P_3}$$

That is, for the pipelined process to be faster than the sequential one, N must be such that the relation N >  $2P_2/P_1+P_3$  is true. For the example we are considering in Figure I-6, N = 2 so that

$$2 > \frac{2P_2}{P_1 + P_3} \text{ or } \frac{P_2}{P_1 + P_3} < 1$$

must hold for the pipeline to be quicker;

thus if  $P_1 = 3$ ,  $P_2 = 4$  and  $P_3 = 2$  so that

$$\frac{P_2}{P_1 + P_3} < 1$$

then for this choice of subprocess times the pipeline would be faster.

The larger N is, the greater the chance that the pipeline is faster than the sequential process for a given set of subprocess times. Let us devise a more general formula for S stages and N items to be pipeline processed:

The sequential process time to process N items through S stages is

$$\begin{array}{ccc}

S \\

N & \sum & P_i \\

i=1

\end{array}$$

The pipelined time is

$$SP_M + (N-1) P_M$$

So we ask: for what  $\mathbb N$  does the following relation hold true?

$$N \sum_{i=1}^{S} P_{i} > SP_{M} + (N-1) P_{M}$$

or

$$N \sum_{i=1}^{S} P_i > NP_M + (S-1) P_M$$

Now, say  $P_{M} = P_{j}$  where  $1 \le j \le S$ , then

or

$$\begin{array}{ccc}

S & & \\

\sum_{i=1}^{S} P_{i} > (S-1) P_{j} \\

i \neq j

\end{array}$$

or (1) N >

$$\frac{(S-1) P_{j}}{\sum_{\substack{i=1 \ i \neq j}}^{\sum}}$$

Since the right hand side of the relation (1) is always greater than 1, we can say that for the pipelined process to be faster than the sequential one, the number of items, N, must be larger than one--again, we might have guessed this intuitively.

Additionally, the gain of the pipeline approach over the sequential one is a function of the number of stages, S, and the distribution of the subprocess times,  $P_i$ . Let us consider two possible distributions for  $P_i$ : The best case (the one in which the pipeline outperforms the sequential method by the highest time ratio) is when all of the subprocess times are equal:

$$P_i = K$$

$i = 1, 2, ..., S$  then  $P_M = K$

and the ratio of sequential time to pipelined time becomes:

$$R = \frac{\sum_{i=1}^{N} P_{i}}{SP_{M} + (N-1) P_{M}} = \frac{NSK}{SK + (N-1) K} = \frac{NS}{S + N - 1}$$

and  $\lim_{N\to\infty} R = S$ ; so we see for this case the pipeline can be up to S times as fast as the sequential process (where S is the number of stages in the pipeline) if we can keep the pipeline full all of the time  $(N \to \infty)$ . The relationship (1) on page I-41 for this case becomes:

$$N > \frac{(S-1) K}{(S-1) K} = 1$$

or  $N > 1$

which means all we need is for N to be greater than one (two items) for the pipeline to be more effective; and the larger N is the better the pipeline looks.

Now let us compare the pipelined and sequential times when the  $\mathbf{P}_{\mathbf{i}}$  have a linear distribution, say

$$P_{i} = i$$

$i = 1, 2, ..., S$  then  $P_{M} = S$

and the ratio of sequential time to pipelined time becomes:

$$R = \frac{\sum_{i=1}^{N} \sum_{j=1}^{S} P_{i}}{SP_{M} + (N-1) P_{M}} = \frac{N(S/2)(S+1)}{S^{2} + (N-1) S} = \frac{N(S+1)}{2(S+N-1)}$$

and  $\lim_{N\to\infty}$  R = (S+1)/2. Comparing this ratio, R, to the constant distribution (P<sub>i</sub> = K) where the ratio is S:

When is

$$S > \frac{S+1}{2}$$

?

The answer is whenever S > 1 or whenever there is more than one stage. So we see that the pipeline outperforms a sequential process by a factor of S when the subprocess times are all the same, and by a factor of (S+1)/2 (not quite as good) when the subprocess times are linearly distributed. Both of these factors are based on the assumption that the peline is kept full all of the time.

The relationship (1) on page I-41 for this second case becomes

$$N > \frac{(S-1) S}{((S-1)/2) S} = 2$$

or  $N > 2$

which means all we need is for N to be greater than two (three items) for the pipeline to be more effective than the sequential process. Note that this is a more stringent requirement than for the constant distribution  $(P_i = K)$  case described first.

There is, however, a finite limit on the number of autonomous subprocesses a process can be broken down into, so that efficiency does reach a maximum value. It should also be clear that for the pipeline mechanism to function at its best efficiency, it should be kept full as much as possible. If the pipe ever drains (runs out of items to be processed) the initial filling up time is very costly since each stage operates at the rate of the slowest stage in the pipe.

# iii. A Pipeline Adder

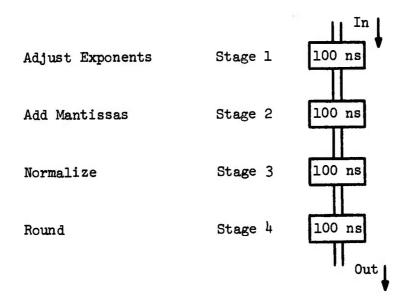

We shall now apply the pipeline mechanism to the adder section of the Arithmetic and Logic Unit of a computer. To illustrate the time speed-up, let us assume that we must add seven pairs of floating point numbers with rounding and normalization. First, let us briefly review the process by which two floating point numbers are added:

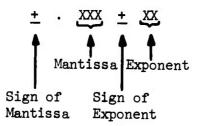

Using a decimal notation we represent a number in the floating point format as follows:

We have allowed 3 significant digits in the Mantissa and two for the Exponent. Thus -.123 + 01 is the same as  $-.123 \times 10^{1}$  in scientific notation or -1.23. Also +.014 - 02 is the same as .00014. We say that a number in floating point format is normalized when the Mantissa is greater than or equal to .1 but less than 1.

$.1 \leq Mantissa < 1.$

Thus +.014 - 02 is not normalized but +.140 - 03 is normalized.

In order to add two numbers in floating point format, we must first equalize their exponents so that their mantissas can be added.

However, when equalizing the exponents we always take the number with the smaller exponent and "promote" the smaller exponent up to the larger one and adjust the mantissa of this number by right shifting by the difference of the exponents. We could not perform a left shift or a significant digit or a normalized number would appear to the left of the decimal point.

After addition of the mantissas, we normalize the result if necessary and finally we round the result so that it can be expressed within 3 significant digits.

In order to perform the four operations

- 1. Adjust Exponents

- 2. Add Mantissas

- 3. Normalize (if necessary)

- 4. Round

we must have an accumulator in our adder that can hold more information than the format we have specified for our floating point numbers. For our 3 significant digit case let us use an accumulator capable of holding numbers of the form

# + X . XXXXXX + XX

This accumulator has an extra position to the left of the decimal point to temporarily store a digit which might overflow as a result of an addition, and it has 6 significant digits to insure accuracy when rounding takes place.

Consider two examples of what steps can occur using actual numbers as operands. We assume that all operands enter into the floating point addition process in normalized form and that the number with the smaller exponent has been placed in the extra length accumulator.

Example 1 Add 123 to 45.6; that is, perform the operation: 123. + 45.6

In normalized form the numbers are:

$$(+.123 + 03) + (+.456 + 02)$$

1. Adjust Exponents:

.123 + 03

+0.045600 + 03 **◄**

This number is in the accumulator

2. Add Mantissas:

+0.168600 + 03

Result in accumulator also

3. No Normalization Necessary

4. Round Result:

+.169 + 03

Number is now back

in 3 significant

digit form.

Example 2 Add 9.99 to .0147; that is, perform the operation: 9.99 + .0147

In normalized form the numbers are:

$$(+.999 + 01) + (+.147 - 01)$$

1. Adjust Exponents: +.999 + 01

+0.001470 + 01

2. Add Mantissas: +1.000470 + 01

3. Normalize: +0.100047 + 02

4. Round: +.100 + 02

Now suppose that the stages of the four step addition process took 70, 100, 60 and 50 nanoseconds (ns) respectively, then the total time to add our seven pairs of numbers in a sequential manner would be

$$7 \times (70 + 100 + 60 + 50) = 1960 \text{ ns}$$

Since each stage can perform its operation autonomously on different operand-pairs, let us "pipeline" the four-stage addition process. Since the slowest stage operates at 100 ns we have

At the end of 400 ns the first result appears at the end of the pipe; after that results come out every 100 ns. (Note that in the sequential process the first result appears after only 280 ns but they continue to be created at that rate.) See Figure I-7 for a snapshot of the pipelined adder every 100 ns. We see from the figure that the total time to add 7 numbers using our four-stage pipeline adder takes only 1000 ns as compared with the 1960 ns sequential addition.

Start

|                                                      |                                |                                   |                                |                      | 900 ns                         | $x_6 + y_6$ $x_5 + y_5$ $x_1 + y_4$                                                                                                                                                               | x2 + y2 |

|------------------------------------------------------|--------------------------------|-----------------------------------|--------------------------------|----------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                      |                                |                                   |                                |                      | 800 ns                         |                                                                                                                                                                                                   | x2 + x2 |

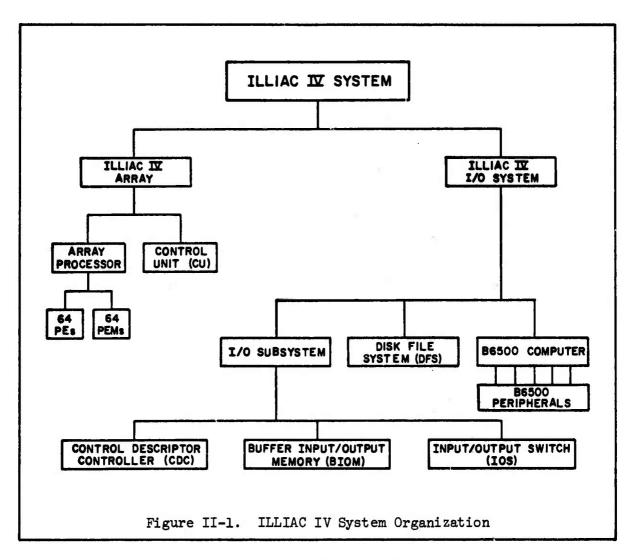

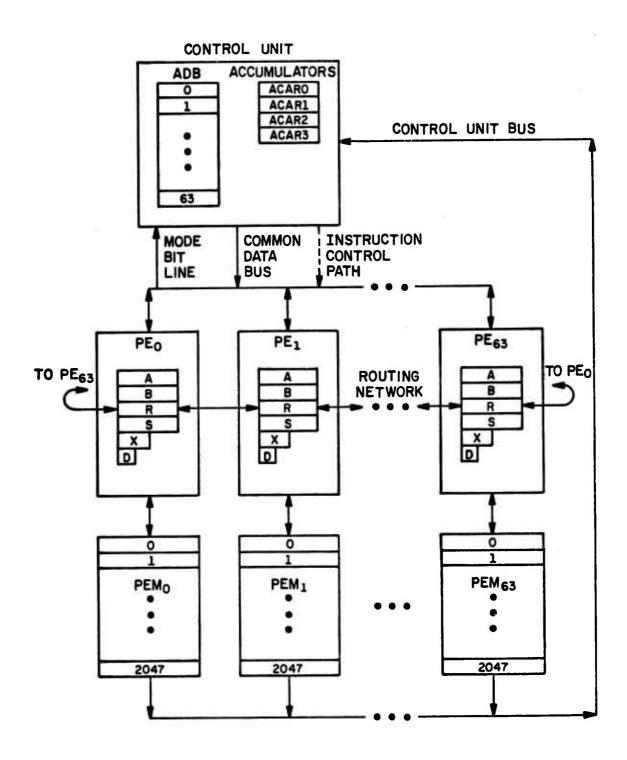

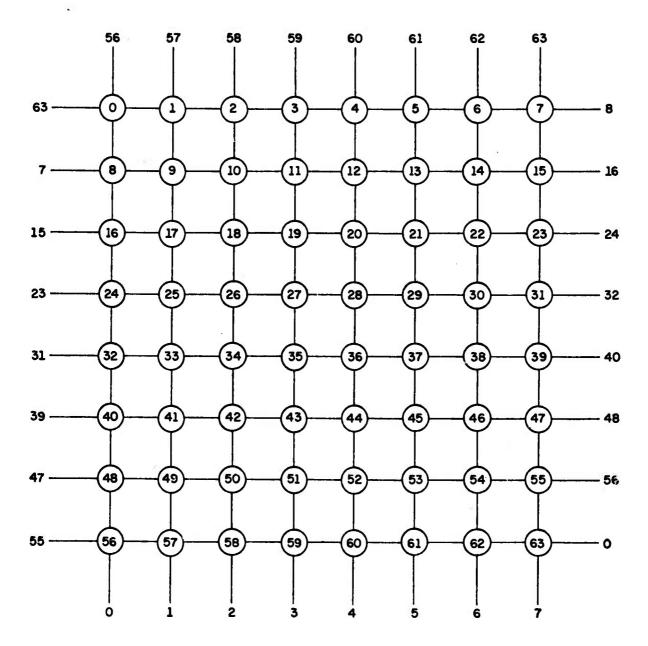

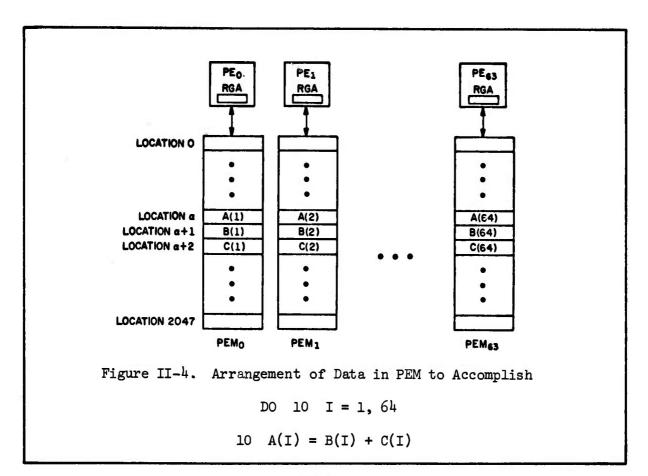

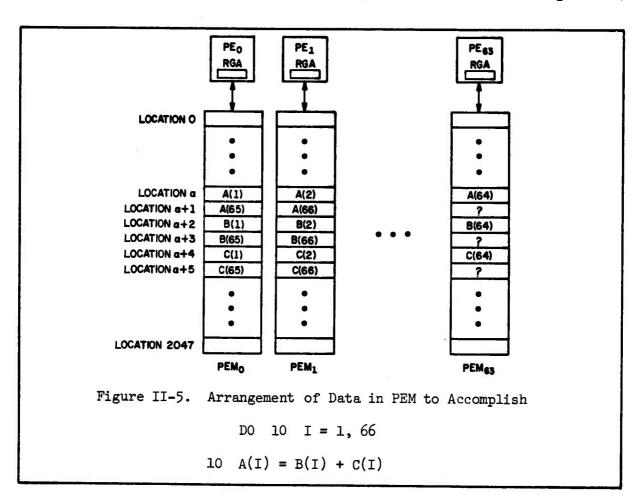

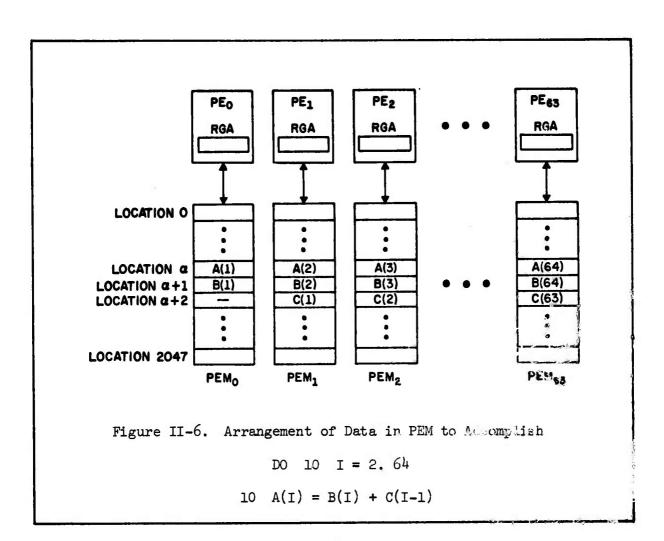

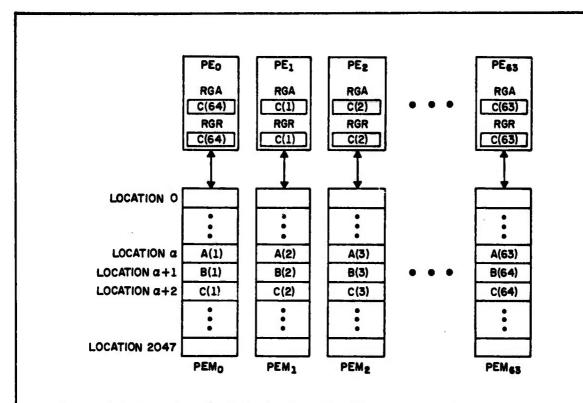

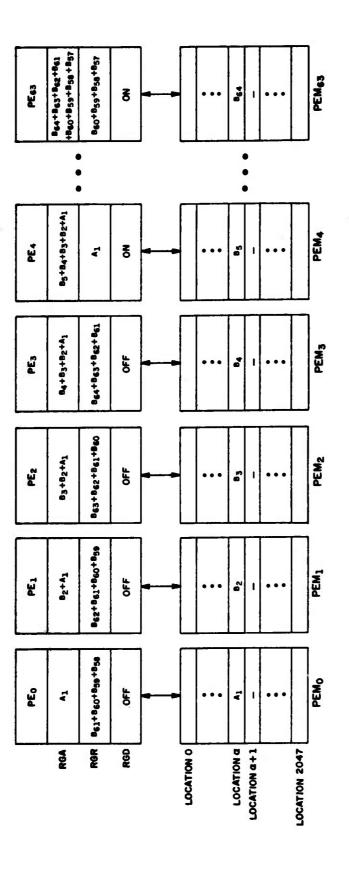

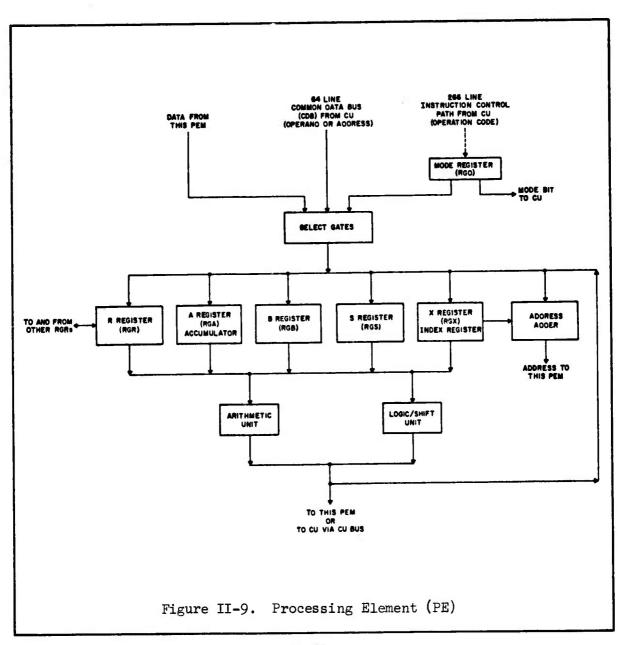

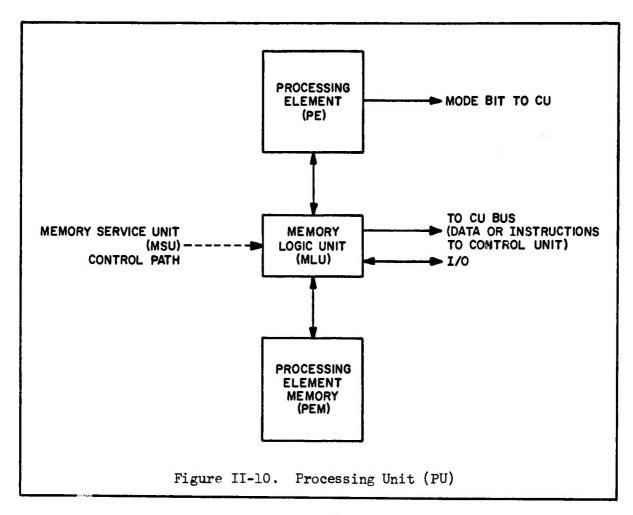

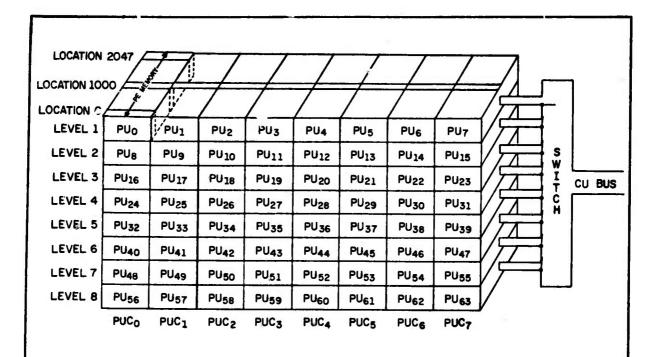

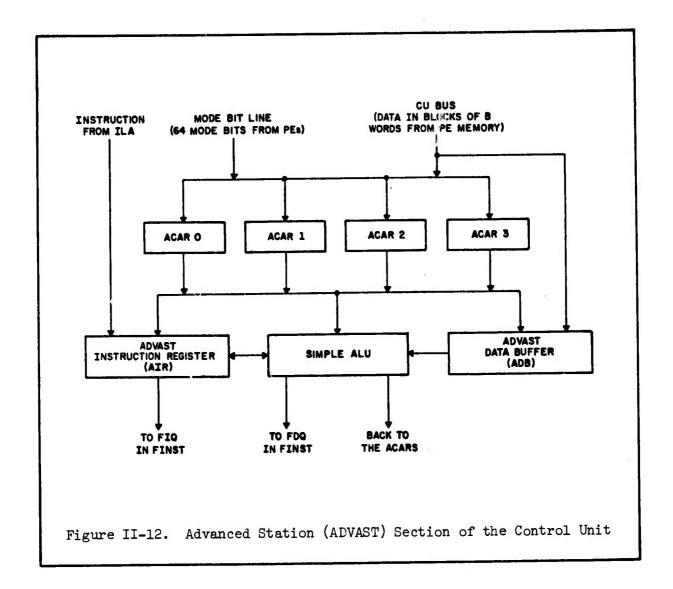

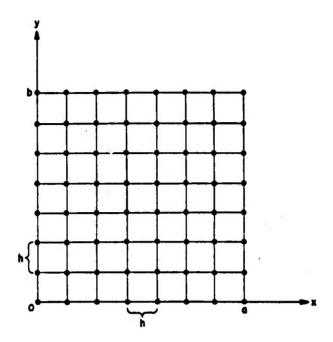

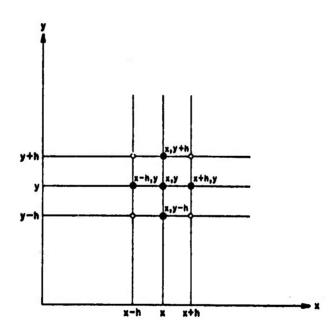

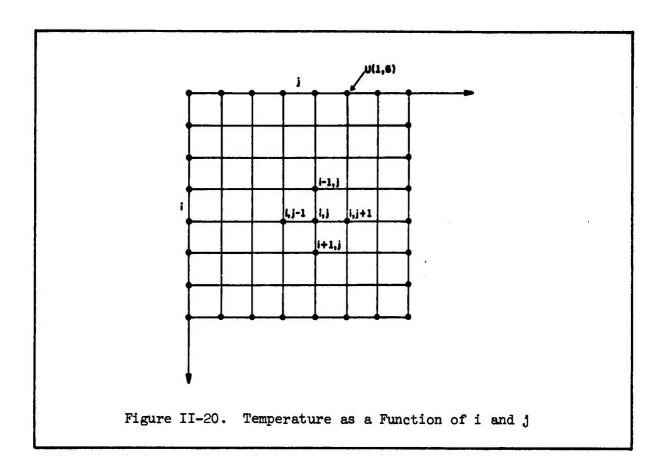

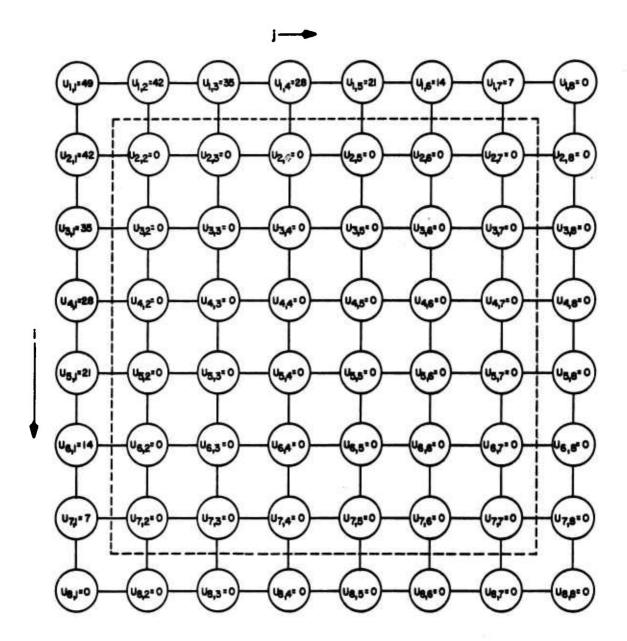

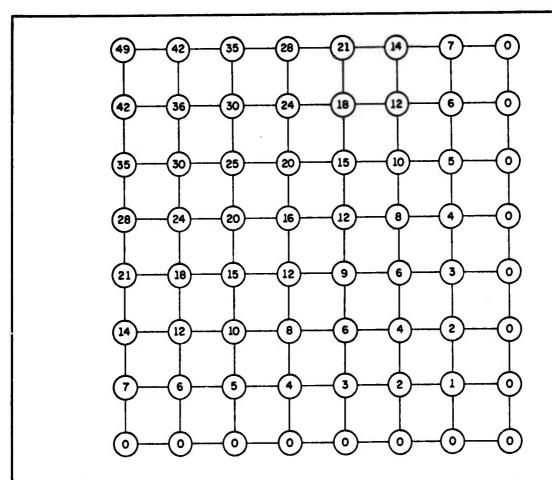

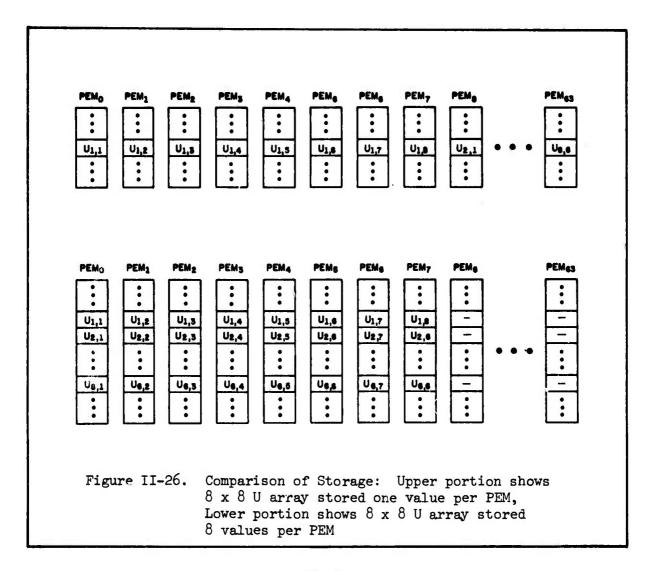

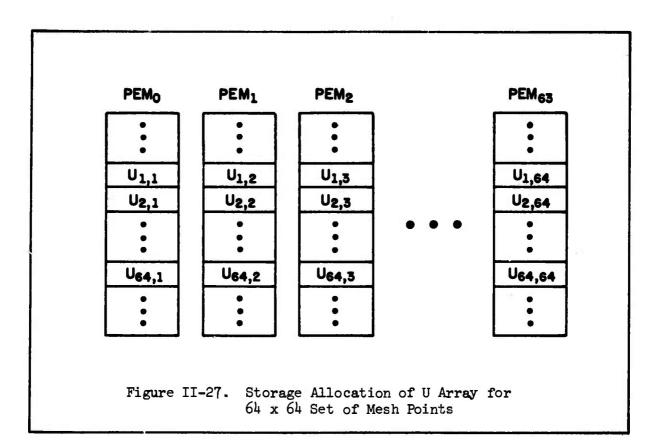

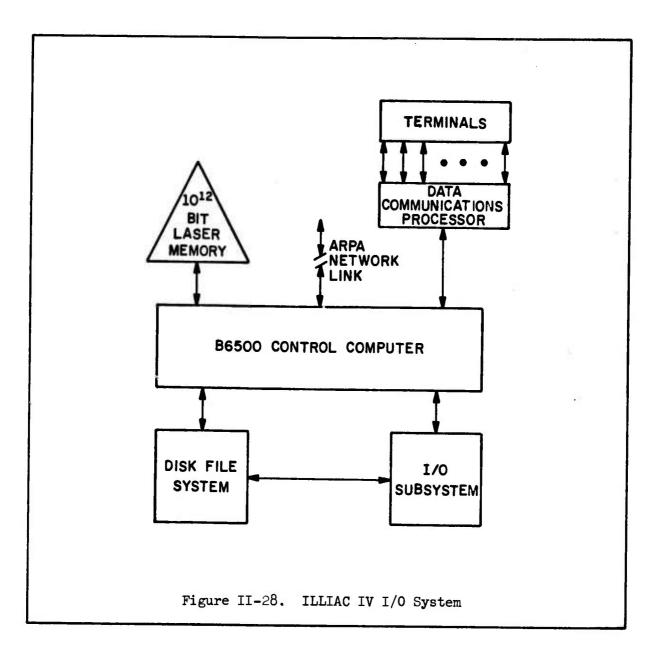

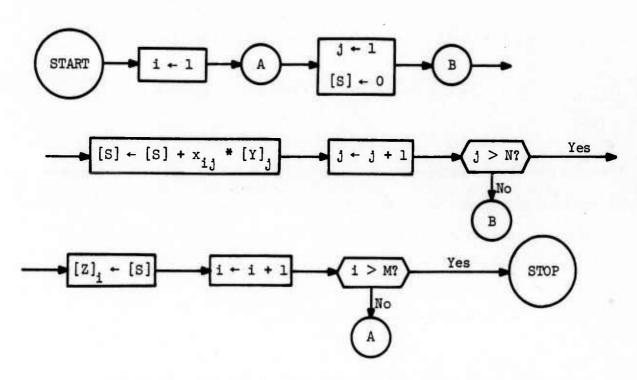

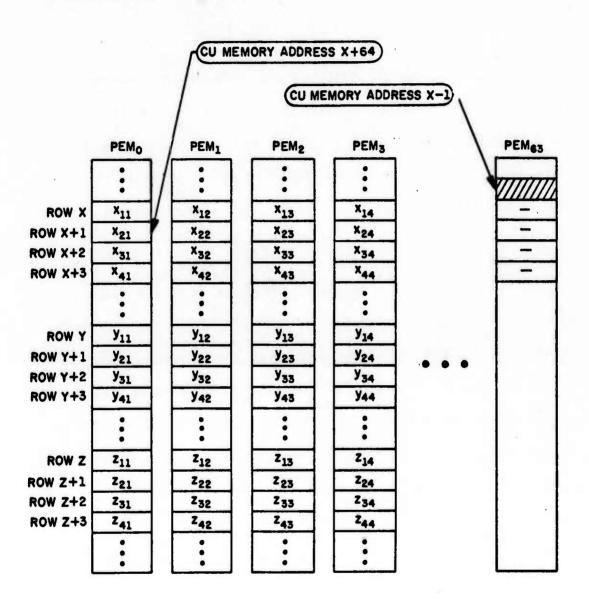

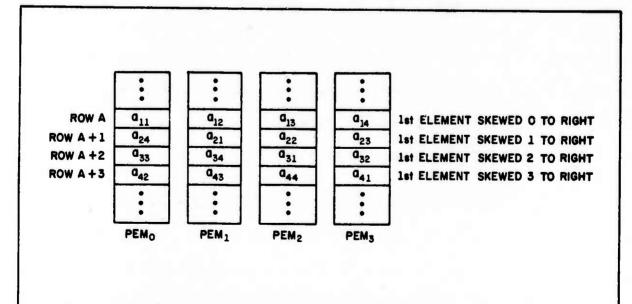

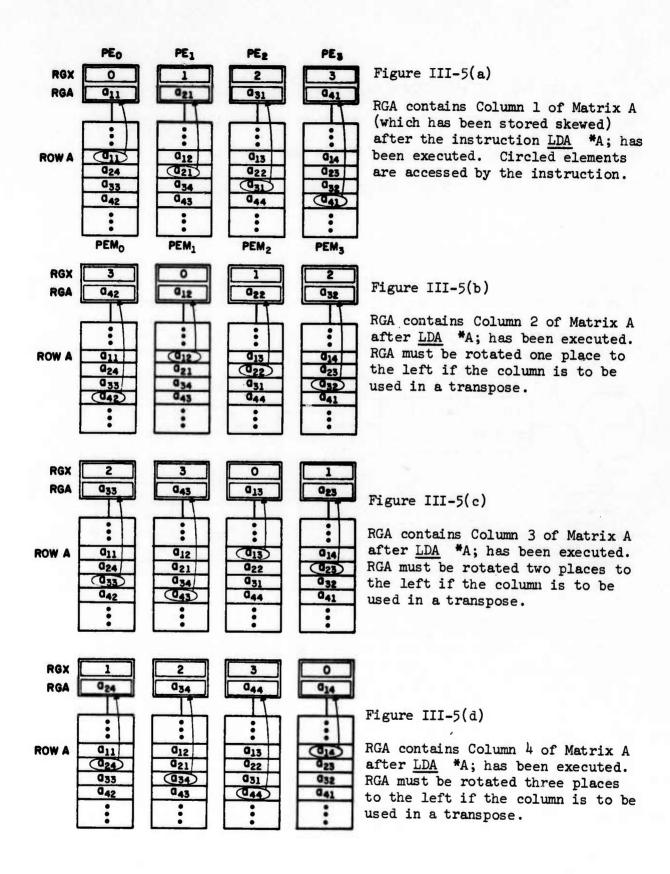

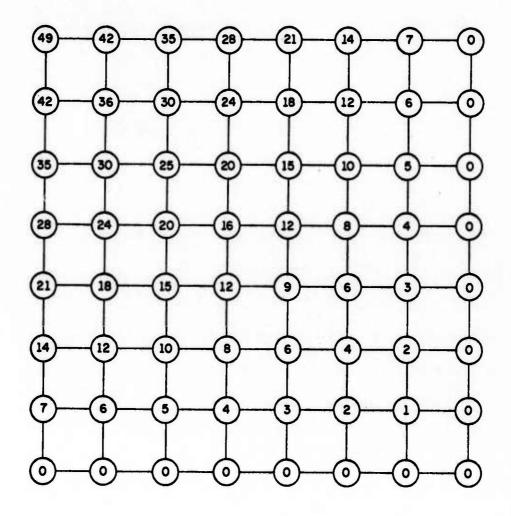

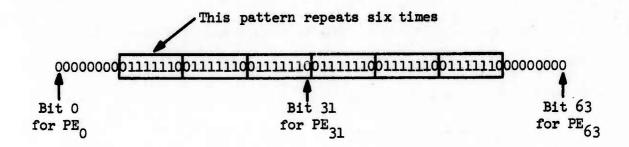

|                                                      |                                |                                   |                                |                      | 700 ns                         | $(x_6, y_6)$<br>$(x_6, y_6)$<br>$(x_6, y_6)$<br>$(x_5, y_5)$<br>$(x_5, y_5)$<br>$(x_5, y_5)$<br>$(x_5, y_5)$<br>$(x_5, y_5)$                                                                      | ۲ + ۲ ا |