| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                   |                                     |                                         | Form Approved<br>OMB No. 0704-0188                                          |                                                     |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|-------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number.<br><b>PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS</b> .                                                                                                                                                                                                                                                                                                                    |                                         |                   |                                     |                                         |                                                                             |                                                     |  |  |  |

| 1. REPORT DAT<br>OCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>ге</b> <i>(DD-MM-YY</i><br>OBER 2014 | (Y) 2. REF        | PORT TYPE<br>CONFERENCE PAPER       |                                         |                                                                             | 3. DATES COVERED (From - To)<br>SEP 2012 – SEP 2014 |  |  |  |

| 4. TITLE AND S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TITLE AND SUBTITLE                      |                   |                                     | 5a. CONTRACT NUMBER<br>FA8750-12-2-0295 |                                                                             |                                                     |  |  |  |

| RANDOM FILL CACHE ARCHITECTUR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |                   | ₹E (PRE PRINT)                      |                                         |                                                                             | 5b. GRANT NUMBER                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                   |                                     |                                         | 5c. PROGRAM ELEMENT NUMBER<br>Other                                         |                                                     |  |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nd Puby Loo                             |                   |                                     |                                         | 5d. PRO                                                                     | 5d. PROJECT NUMBER<br>DHS2                          |  |  |  |

| Fangfei Liu and Ruby Lee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |                   |                                     | 5e. TASK NUMBER<br>PR                   |                                                                             |                                                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                   |                                     |                                         | 5f. WOR                                                                     | K UNIT NUMBER<br>IN                                 |  |  |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>Princeton University<br>Princeton, NJ 08544                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                   |                                     |                                         | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER<br>N/A                          |                                                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                   | E(S) AND ADDRESS<br>ion Directorate | S(ES)                                   |                                                                             | 10. SPONSOR/MONITOR'S ACRONYM(S)<br>AFRL/RI         |  |  |  |

| Air Force Research Laboratory/Information Directorate<br>Rome Research Site/RITA<br>525 Brooks Road<br>Rome NY 13441-4505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                   |                                     |                                         | 11. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER<br>AFRL-RI-RS-TP-2014-051 |                                                     |  |  |  |

| 12. DISTRIBUTION AVAILABILITY STATEMENT<br>Distribution Approved For Public Release; Distribution Unlimited. This report is the result of contracted fundamental<br>research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated<br>10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                   |                                     |                                         |                                                                             |                                                     |  |  |  |

| <b>13. SUPPLEMENTARY NOTES</b><br>© 2014 IEEE/ACM. Proceedings IEEE/ACM International Symposium on Microarchitecture (MICRO). Cambridge, UK, 13-17 Dec 2014. This work was funded in whole or in part by Department of the Air Force contract number FA8750-12-2-0295. The U.S. Government has for itself and others acting on its behalf an unlimited, paid-up, nonexclusive, irrevocable worldwide license to use, modify, reproduce, release, perform, display, or disclose the work by or on behalf of the Government. All other rights are reserved by the copyright owner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                   |                                     |                                         |                                                                             |                                                     |  |  |  |

| <ul> <li>14. ABSTRACT</li> <li>Correctly functioning caches have been shown to leak critical secrets like encryption keys, through various types of cache side-channel attacks. This nullifies the security provided by strong encryption and allows confidentiality breaches, impersonation attacks and fake services. Hence, future cache designs must consider security, ideally without degrading performance and power efficiency. We introduce a new classification of cache side channel attacks: contention based attacks and reuse based attacks. Previous secure cache designs target only contention based attacks, and we show that they cannot defend against reuse based attacks. We show the surprising insight that the fundamental demand fetch policy of a cache is a security vulnerability that causes the success of reuse based attacks. We propose a novel random fill cache architecture that replaces demand fetch with random cache fill within a configurable neighborhood window. We show that our random fill cache does not degrade performance, and in fact, improves the performance for some types of applications. We also show that it provides information-theoretic security against reuse based attacks.</li> <li>15. SUBJECT TERMS</li> </ul> |                                         |                   |                                     |                                         |                                                                             |                                                     |  |  |  |

| Cache; Security; Side Channel Attacks; Cache Collision Attacks; Secure Caches; Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |                   |                                     |                                         |                                                                             |                                                     |  |  |  |

| 16. SECURITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLASSIFICATIO                           | N OF:             | 17. LIMITATION OF<br>ABSTRACT       |                                         |                                                                             | IE OF RESPONSIBLE PERSON<br>BERT DIMEO              |  |  |  |

| a. REPORT<br>U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | b. ABSTRACT<br>U                        | c. THIS PAGE<br>U | UU                                  | 14                                      | 19b. TELEPHONE NUMBER (Include area code)<br>N/A                            |                                                     |  |  |  |

# **Random Fill Cache Architecture**

Fangfei Liu and Ruby B. Lee Princeton Architecture Laboratory for Multimedia and Security (PALMS) Department of Electrical Engineering, Princeton University Princeton, NJ 08544, USA {fangfeil, rblee}@princeton.edu

Abstract-Correctly functioning caches have been shown to leak critical secrets like encryption keys, through various types of cache side-channel attacks. This nullifies the security provided by strong encryption and allows confidentiality breaches, impersonation attacks and fake services. Hence, future cache designs must consider security, ideally without degrading performance and power efficiency. We introduce a new classification of cache side channel attacks: contention based attacks and reuse based attacks. Previous secure cache designs target only contention based attacks, and we show that they cannot defend against reuse based attacks. We show the surprising insight that the fundamental demand fetch policy of a cache is a security vulnerability that causes the success of reuse based attacks. We propose a novel random fill cache architecture that replaces demand fetch with random cache fill within a configurable neighborhood window. We show that our random fill cache does not degrade performance, and in fact, improves the performance for some types of applications. We also show that it provides information-theoretic security against reuse based attacks.

*Keywords*-cache; security; side channel attacks; cache collision attacks; secure caches; computer architecture.

#### I. INTRODUCTION

Recent findings on cache side channel attacks [1]–[7] have shown that correctly functioning caches may leak critical secrets like cryptographic keys, nullifying any protection provided by strong cryptography. These attacks are easy to perform and are effective on all platforms, from embedded systems to cloud servers, that use hardware caches. Therefore, future cache designs must take into account security, ideally without degrading performance and power efficiency.

In cache side channel attacks, an attacker exploits the large timing difference between cache hits and cache misses to infer the key-dependent (i.e., security-critical) memory addresses, and hence the secret information, during the execution of cryptographic programs. We introduce a new classification of cache side channel attacks, depending on how the attacker infers memory addresses: contention based attacks versus reuse based attacks. In contention based attacks [2], [3], [5], the key-dependent memory accesses may contend for the same cache set with the attacker's memory accesses, and result in eviction of one by the other, in a *deterministic* way. This enables the attacker to infer the memory address according to which cache set it maps to. In contrast, the reuse based attacks [4], [6], [8], [9] do not rely

on any resource contention. Instead, they only exploit the reuse of a previously accessed (and cached) security-critical data to correlate the addresses of two memory accesses. We point out that reuse of the cached data is exactly the purpose of a cache, therefore reuse based attacks strike at the heart of a cache and are much harder to defend against.

Several recent work [8], [10]-[14] investigated how to design secure caches to provide built-in defenses against cache side channel attacks. Wang and Lee proposed two general design approaches [11]: the partition-based approach [8], [11], [13], [14] that eliminates the cache contention, and the randomization-based approach [10]–[12] that randomizes the cache contention. However, these approaches only target contention based attacks and are not effective in defeating reuse based attacks. There are also some efforts that try to achieve constant execution time by either not loading security-critical data into the cache at all, or trying to ensure all cache hits whenever security-critical data is accessed, by frequently preloading or reloading all security-critical data [8], [14], [15]. This approach may potentially defeat the reuse based attacks, but at the cost of significant performance degradation, and sometimes enabling other types of attacks.

In this paper, we try to find a general approach against reuse based attacks, as a complement to existing secure cache design approaches. We show that, contrary to conventional wisdom, constant execution time is not the necessary condition to defeat reuse based attacks. Surprisingly, we find that the fundamental demand fetch policy of a cache is a security vulnerability that causes the success of reuse based attacks. With the demand fetch policy, the cache fill is always correlated with a demand memory access, hence the state of a cache reveals information about previous memory accesses. Hence, we propose a general approach against reuse based attacks: re-design the cache fill strategy so that it is de-correlated with the demand memory access. We propose a novel random fill cache architecture with a new security-aware cache fill strategy. The random fill cache architecture takes advantage of the random access pattern found in cryptographic algorithms. Hence, it does not degrade performance. In fact, it is more general and flexible than the demand fetch strategy, and even enables performance improvements for some types of applications. Our main contributions are:

- A new classification of cache side channel attacks as contention based and reuse based attacks,

- A new general approach for securing caches against reuse based attacks: the cache fill strategy must be re-designed to de-correlate the cache fill and demand memory accesses,

- A novel random fill cache architecture with a flexible cache fill strategy, which replaces the demand fetch with random cache fill within a configurable neighborhood window,

- An information-theoretic proof of the security provided by our random fill cache architecture,

- Performance evaluation of the proposed cache architecture and study of the broader performance implications of the random cache fill strategy to programs that are not demand-fetch amenable.

The rest of the paper is organized as follows: Section II gives some background on cache side channel attacks and section III discusses past work. We introduce our new random fill cache architecture in section IV. We provide an information-theoretic proof of the security provided by our random fill cache architecture in section V. We evaluate the performance of our cache architecture in section VI. We discuss the broader performance implications of our cache architecture in security and performance with past work in section VIII and conclude in section IX.

# II. BACKGROUND

#### A. Overview of Cache Side Channel Attacks

The majority of cache side channel attacks exploit the interaction of the key-dependent data flow in a program with the underlying cache (mostly L1 data cache) to learn the secret information. We primarily consider the information flow in which the secret information is directly modulated onto the memory address, in the form of key-dependent table lookups. This is commonly found in the software implementation of cryptographic algorithms. For example, the substitution box (S-box) in the block ciphers (e.g., Data Encryption Standard (DES), Advanced Encryption Standard (AES), Blowfish), and the multipliers table in the public-key algorithms (e.g., RSA) are all implemented as lookup tables indexed by a linear function of the secret key. The attacker is an unprivileged user-level process that aims to infer the keydependent memory addresses, indirectly through the cache behavior.

### B. Classification of Cache Side Channel Attacks

Table I summarizes the classification of all known cache side channel attacks. Cache side channel attacks have been conventionally classified as access-driven attacks and timing-driven attacks [1], based on what can be measured by the attacker. In the access-driven attacks, the attacker can observe which cache lines the victim has accessed by measuring the impact of the victim's cache accesses to the attacker's own accesses. In the timing-driven attacks, the attacker can measure the execution time of the victim process. However, this classification is not helpful in identifying root causes and potential countermeasures. We introduce a new classification: contention based attacks and reuse based attacks, based on how the attacker infers the memory address.

Table I CLASSIFICATION OF CACHE SIDE CHANNEL ATTACKS

|                          | Contention based<br>Attacks | Reuse based<br>Attacks     |  |  |

|--------------------------|-----------------------------|----------------------------|--|--|

| Access-driven<br>Attacks | Prime-Probe Attacks         | Flush-Reload<br>Attacks    |  |  |

| Timing-driven<br>Attacks | Evict-Time Attacks          | Cache collision<br>Attacks |  |  |

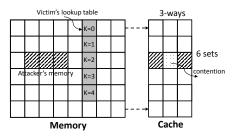

1) Contention based Attacks: The attacker may contend for the same cache set with the victim process and the contention results in eviction of one's cache line by the other. If the contention and eviction is *deterministic*, the attacker can infer the memory address of the victim according to which cache set it maps to. Figure 1 illustrates how this works. There are two variations of contention based attacks:

*Prime-Probe Attack [3], [5]:* The attacker repeats the following operations: 1) Prime: the attacker fills one or more cache sets with his own data. 2) Idle: the attacker waits for a pre-specified Prime-Probe interval while the victim process is running and utilizing the cache. 3) Probe: the attacker process runs again and measures the time to load each set of his data. The Probe phase primes the cache for subsequent observations. If the victim process uses some cache sets during the Prime-Probe interval, some of the attacker's cache lines in these cache sets will be evicted, which causes cache misses and thus a longer load time during the Probe phase.

*Evict-Time Attack [5]:* The attacker repeats the following operations: 1) Evict: the attacker fills one specific cache set with his own data and hence evicts the victim's data in that cache set. 2) Time: the attacker triggers the victim process to perform a cryptographic operation, and measures the total execution time. If the victim accesses the evicted data, his execution time tends to be statistically higher, due to the victim having a cache miss.

Figure 1. How cache contention can be used to infer information. Each square represents a cache line. Each memory line of the victim's lookup table is indexed by a different value of key bits K. The attacker occupies one cache set. The contention with the victim tells the attacker that the victim process has accessed the memory line corresponding to K = 2.

2) Reuse based Attacks: Contention based attacks rely on cache contention to learn where a memory line is placed in the cache. However, reuse based attacks do not care about the location of a memory line in the cache. Instead, they only rely on the fact that a previously accessed data will be cached, hence the reuse of the same data by a later memory access will result in a cache hit. There are two variations of reuse based attacks:

Flush-Reload Attack [6]: The attacker and the victim process may share some address space. In particular, securitycritical data such as the lookup tables can be shared through a shared library. The attacker repeats the following operations: 1) Flush: the attacker flushes the security-critical data out of the cache to eliminate the impact of any previous accesses to the security-critical data. 2) Idle: the attacker waits for a pre-specified Flush-Reload interval while the victim process is running and utilizing the cache. 3) Reload: the attacker process runs again and measures the time to reload the security-critical data. If the victim process accesses some security-critical data during the Flush-Reload interval, the attacker will get a significantly lower reload time, since it will hit in the cache.

*Cache Collision Attack [4]:* The Flush-Reload Attack exploits reuse of the shared data between the victim and the attacker. However, sharing of security-critical data is not common and can easily be disabled by not declaring the security-critical data as read-only. The more serious threat of reuse based attacks is to exploit the reuse of the cached security-critical data *within* the victim process, which represents the intrinsic information leakage of a program. The reuse of data is commonly called *cache collision*, meaning that two memory accesses reference the same memory line. The basic idea of a cache collision attack is to exploit the impact of cache collision on the victim's aggregated execution time.

**Premise of Cache Collision Attacks:** Consider a series of security-critical accesses to lookup table *T*:

$$\dots T[\bullet], T[\bullet], T[x_i], T[\bullet], T[\bullet], T[x_j], T[\bullet], T[\bullet] \dots$$

(1)

Denote the memory block address of x as  $\langle x \rangle$ . For any pair of accesses to  $x_i$  and  $x_j$ , when  $\langle x_i \rangle = \langle x_j \rangle$ , access to  $x_j$ will hit in the cache, whereas when  $\langle x_i \rangle \neq \langle x_j \rangle$ , access to  $x_j$  may or may not hit in the cache, depending on the rest of the sequence and prior cache contents. Statistically, the execution time of the cryptographic operation when  $\langle x_i \rangle =$  $\langle x_j \rangle$  will be less than that when  $\langle x_i \rangle \neq \langle x_j \rangle$ . Assume  $x_i$ and  $x_j$  both depend on the key K, where  $x_i = f(K)$ , and  $x_j = g(K)$ . If the attacker learns  $\langle x_i \rangle = \langle x_j \rangle$  from the timing measurement, he can establish a relationship for the secret key as  $\langle f(K) \rangle = \langle g(K) \rangle$ .

3) Discussion: As pointed out by Wang and Lee [11], the root cause of contention based attacks is the *deterministic memory-to-cache mappings, causing deterministic cache contention*. The root cause of reuse based attacks is

more fundamental, since reuse of the data is the primary goal of a cache. We observe that the hidden assumption of the reuse based attacks is that the access to a securitycritical data will bring the requested memory line into the cache (if not yet cached), which is exactly the *demand fetch* policy of all existing caches, that take advantage of both temporal and spatial locality of a program. With the demand fetch policy, cache fills are always correlated with memory accesses in a deterministic way, and the state of the cache can "remember" information of previous demand accesses.

Resource contention of shared micro-architectural components (either memoryless or storage components) [10], [16]–[18] have been well-known as sources of information leakage. Reuse based attacks are fundamentally different since they do not rely on any resource contention, and represent new threats specific to storage structures such as cache and buffer structures that exploit the locality principle to store recently-used data of a larger storage structure.

# C. Case Study: Cache Collision Attacks against AES

As a concrete example, we show how the cache collision attack works to extract the AES encryption keys (e.g., in the OpenSSL implementation of AES). AES is a block cipher that has 128-bit blocks with three possible key sizes: 128, 192, 256 bits. Depending on the key size, AES performs 10, 12 or 14 rounds, respectively [19]. We use 128-bit keys in our discussion. The output of each round will be the input for the next round, and the operations in each round are implemented as table lookups for performance reasons. OpenSSL uses ten 1-KB lookup tables, five for encryption and five for decryption. Four tables are used in each round except that the final round uses a different lookup table.

To perform the attack, the attacker sends random plaintext blocks to the victim to do AES encryption, and measures the time for each block encryption. Before triggering the next block encryption, the attacker cleans the cache so that each block encryption starts from a clean cache. Cache collision attacks assume that the attacker either knows the plaintext (first-round attack) or the ciphertext (final-round attack).

**First-round attack:** The index of the first round table lookup  $x_i$  is related with the key byte  $k_i$  and plaintext byte  $p_i$  as  $x_i = k_i \oplus p_i$ . If the attacker learns that two memory accesses collide, i.e.,  $\langle x_i \rangle = \langle x_j \rangle$ , he can infer that  $\langle k_i \oplus k_j \rangle = \langle p_i \oplus p_j \rangle$ .

**Final-round attack:** The index of a final round table lookup  $x_u^{10}$  of table  $T_4$  is related with the final round key byte  $k_i^{10}$  and ciphertext byte  $c_i$  as  $T_4[x_u^{10}] \oplus k_i^{10} = c_i$ . Hence, by learning two table lookups  $x_u^{10}$  and  $x_w^{10}$  collide in the final round table lookups, the attacker can infer that  $k_i^{10} \oplus k_j^{10} = c_i \oplus c_j$ .

Since a cache collision of two memory accesses  $x_i$  and  $x_j$  means a lower execution time on average, the attacker can aggregate the time measurements according to the value of the XORed plaintext (or ciphertext) bytes and find the

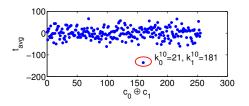

Figure 2. Timing characteristic chart for  $c_0 \oplus c_1$ . The minimum average encryption time occurs at  $c_0 \oplus c_1 = 160$ , implying  $k_0^{10} \oplus k_1^{10} = 160$ .

minimum encryption time. Figure 2 shows the average encryption time for the samples with the same value of XORed  $c_0 \oplus c_1$ . The data is collected by running  $2^{17}$  block encryptions on the cycle-accurate gem5 simulator [20]. The attacker can easily find the point with minimum average encryption time, then he can infer  $k_0^{10} \oplus k_1^{10} = c_0 \oplus c_1 = 160$ . He can get similar timing characteristics for 15 XORed ciphertext bytes ( $c_0 \oplus c_i$ , i = 1, ..., 15), and thus infer 15 XORed key bytes to recover the full 16-bytes key (by guessing just one key byte  $k_0^{10}$ ).

# III. PAST WORK

#### A. Secure Cache Solutions

Designing secure caches can provide much higher performance, and often greater security, than software solutions for mitigating cache side channel attacks. Two general approaches that have been used are partitioning the cache and randomizing the memory-to-cache mapping.

**Partitioning the Cache:** The cache is partitioned into different zones for different processes and each process can only access the cache blocks in its zone, thus eliminating contention between a victim process and an attacker process. Partitioning can be achieved statically or dynamically.

NoMo [13] cache uses static cache partitioning by simply reserving one or more ways of a set for each hardware thread. However, it only works for the case when the victim and the attacker processes are executing simultaneously in a simultaneous multi-threading (SMT) processor.

PLcache [11] performs finer-grained, dynamic partitioning, which does not statically reserve any cache lines for a process; instead it locks a protected cache line into the cache and does not allow it to be evicted by another process. Each cache line is extended with the process identifier and a locking status bit. The architectural support also includes special load/store instructions for fine-granularity locking/unlocking. The special load/store instructions are similar to the normal load/store instructions, except that if the memory access hits in the cache or causes a cache line to be fetched into the cache, the locking status bit is set (lock) or cleared (unlock).

**Randomizing memory-to-cache mapping:** RPcache [11] and Newcache [12] are cache designs using memory-to-cache mapping randomization. In RPcache, there is a permutation table for each trust domain, which can permute the index bits to the cache set. If a process wants to replace cache line X in cache set S, which belongs to a process in another trust domain, a cache line Y in a randomly selected cache set S' will be evicted instead of evicting cache line X. The cache indices of S and S' will be swapped in the process' permutation table and other cache lines in S and S' belonging to the process are invalidated. Therefore, the attacker cannot get useful information from the cache line eviction and replacement.

Newcache [12], [21] can randomize the mapping to each single cache line by adopting a logical direct-mapped cache architecture, hence avoiding the swapping of cache sets and invalidating of other lines in these swapped cache sets - resulting in better performance. Newcache introduces a remapping table as a level of indirection, which stores the mapping from the index bits of the address to a real cache line. Protected processes have different remapping tables, while all unprotected processes share the same remapping table. Newcache can avoid many conflict misses by using a longer index (additional bits) than needed for the actual size of the physical cache - again improving performance. The remapping table is dynamically updated and randomized using a security-aware replacement algorithm, hence randomizing the cache contention between the victim and the attacker.

Both Partitioning and Randomization based approaches only target contention based attacks, and cannot defeat reuse based attacks. These approaches differ from the conventional set-associative caches mainly in where the memory line can be placed in the cache. Consider, for example, the data reuse between memory accesses  $x_i$  and  $x_j$ , in the cache collision attack. For the Partitioning based approaches, access to  $x_i$ will bring the memory line  $\langle x_i \rangle$  into its own cache partition, and accesses to  $x_j$  will hit in the cache when  $\langle x_i \rangle = \langle x_j \rangle$ . Similarly, in randomization based approaches, if memory line  $\langle x_i \rangle$  was brought into a random location in the cache, the second memory access would still result in a cache hit if  $\langle x_i \rangle = \langle x_j \rangle$ . Hence, the root cause of cache collision attacks still holds.

#### B. Constant Execution Time Solutions

Achieving constant execution time in cache accesses [4], [8], [14] could potentially eliminate cache side channel attacks based on the timing difference of cache hits and misses, including reuse based attacks. One drastic approach is to disable the cache for security-critical accesses [8] so that all accesses to security-critical data miss in the cache. This will severely degrade performance. Getting all cache accesses to be hits is ideal, and this can be done using other on-chip storage [22], rather than a cache.

Constant time using a cache can also be approached by "preloading" all the security-critical data into the cache, so that all accesses to them are cache hits. This has been done by rewriting the software cipher to preload all the critical data before each round [15]. However, performance is significantly degraded, and the preloaded data can still be evicted within a round of encryption. With some hardware support, performance may be improved. [14] proposed to use the "informing loads" technique [23] to perform the "preloading". Critical data is loaded using informing load instructions, and on a cache miss, a user-level exception handler is invoked to perform the preloading. Securitycritical data can also be preloaded during context switches [14] and then "locked" in the cache by the cache line locking mechanism of PLcache [11]. "PLcache+preload" is simpler than "informing loads" in terms of hardware and software changes, and has better performance due to less frequent invocation of the preloading routine on context switches rather than cache misses.

Unfortunately, "preloading" based approaches still have scalability and performance issues, and may cause new security problems, which we will discuss in detail in sections VI and VIII.

In this paper, we try to find a general approach against reuse based attacks, as a complement to existing secure cache design approaches, which only defend against contention based attacks. Contrary to conventional wisdom, we also show that constant execution time is not the necessary condition to defeat cache collision attacks and other reuse based attacks. Our defense strategy leads to a simpler hardware based solution, without the need to frequently preload or reload all the security-critical data into the cache.

# IV. RANDOM FILL CACHE ARCHITECTURE

#### A. Random Cache Fill Strategy

Our key insight is that the root cause of reuse based attacks suggests that the cache fill strategy has to be redesigned to de-correlate the cache fill and the demand memory access. We propose using a random cache fill strategy to dynamically achieve the de-correlation. On a cache miss, the missing data is sent to the processor without filling the cache. To still get performance from the cache, we fill the cache with randomized fetches within a configurable neighborhood window of the missing memory line instead. The idea is partially motivated by our observation that accesses to the security-critical data in cryptographic programs usually have random patterns, due to the nonlinearity of the lookup tables (e.g., S-box) and to the random keys. Therefore, randomly fetching the neighborhood memory lines is as good as demand fetching the missing memory line. The random fetching within the spatial locality of the neighboring memory locations is like prefetching, and hence performance may not be degraded, and could even be improved in some cases.

The random cache fill strategy represents a more general and flexible cache fill strategy than the demand fetch policy, and the degree of de-correlation can be configured by changing the random fill window size. We will show in section V that our random cache fill strategy can provide an

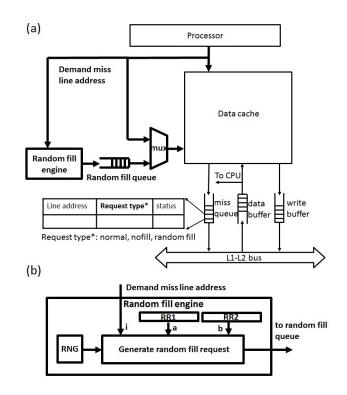

Figure 3. (a) block diagram of random fill cache, (b) blow up of random fill engine

information-theoretic security assurance against reuse based attacks by choosing a proper random fill window size. As a cache fill strategy, it can be built on any existing secure cache architecture (e.g., Newcache [12], [21]) to provide built-in security against all known cache side channel attacks.

### B. Random Fill Cache Architecture

A block diagram of the random fill cache architecture is shown in Figure 3(a). We focus on the L1 data cache since cache side-channels are most effective (fastest) in L1 data caches. It is built upon a conventional non-blocking cache and the hardware addition is very small (highlighted in bold in Figure 3), essentially a random fill engine, a queue and a multiplexer.

1) Hardware for No Demand Fill: In a non-blocking and write-back cache, an entry in the miss queue records the missing memory line address and the status of the request. We add a field to miss queue entries to indicate the request type: normal, nofill or random fill:

- *Normal request* is a demand fetch as in a conventional cache that does demand fill; it fills the cache with the missing line, and the data returned will be sent to the processor.

- *Nofill request* is a demand fetch that directly forwards returned data to the processor while not filling the cache. This leverages the critical word first technique typically implemented to reduce the cache miss latency,

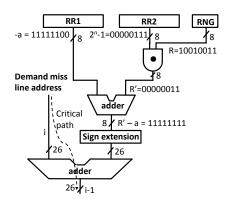

Figure 4. Efficient generation of the address of the random fill request. The example shows a random fill window [i - 4, i + 3].  $RR_1$  stores the lower bound -a = -4 and  $RR_2$  stores the window size mask  $2^3 - 1$ . Both the range registers and RNG are 8-bits in width, and the generated random fill request is i - 1.

so no extra hardware is required to implement the forwarding of data.

• *Random fill request* only fills the cache but does not send any data to the processor.

2) Random Fill Engine (Figure 3(b)): Upon a cache miss, the demand requested memory line will not be filled into the cache. Instead, the random fill engine generates a random fill request with an address within a neighborhood window [i - a, i + b] which is a memory lines before and b memory lines after the demand request for memory line i. The two boundaries a and b are stored in two new range registers, RR1 and RR2, which bound the range of the random number generated from a free running random number generator (RNG). For example, the RNG can be implemented as a pseudo random number generator with a truly random seed. The use of RNG does not impact the cycle time since it is used only during a cache miss and hence is not in the critical path of the processor's pipeline. Furthermore, the random number can be generated ahead of time and buffered. Note that when the range registers are set to zero, randomized cache fill is essentially disabled. In this case, the demand request will be sent as a normal request and no random fill request is generated. The random fill request goes to a random fill queue (a First In First Out (FIFO) buffer) where it waits for idle cycles to lookup the tag array of the data cache. If the random fill request hits in the cache, it is dropped. Otherwise a random fill request is issued and put into the miss queue.

Table II Alternative system calls for configuring random fill window dynamically (only 1 needed)

| Declaration                          | Description                                                                                                         |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| set_RR(int a, int b)                 | set range register $RR_1$ and $RR_2$ to<br>the given value $a$ and $b$ , respectively                               |

| set_window(int lowerBound,<br>int n) | set the lower bound and size of the<br>random fill window to<br><i>lowerBound</i> and 2 <sup>n</sup> , respectively |

3) System Interface: The two range registers, RR1 and RR2, are configurable by the operating system (OS). As shown in Table II, the OS provides a system call set\_RR to set the range registers by the compiler and/or applications. This system call provides a fine-granularity control of the use of the random fill cache. By default, the two range registers are set to zero and the random fill cache works just like the conventional demand-fetch cache. The system call can be inserted before the cryptographic operations either by the compiler or by the applications to enable randomized cache fill. They can be disabled afterwards by another call to set\_RR. The range registers are part of the context of the processor and need to be saved to, and restored from, the process control block (PCB) for a context switch.

4) Optimization: Since it may be non-trivial to generate a random number within an arbitrary bound, we also propose an optimization that constrains bounds a and b so that  $a + b + 1 = 2^n$ , i.e., the window size is a power of two. Instead of set\_RR, a different system call set\_window is implemented: this takes the lower bound of the random fill window (i.e., -a) and the logarithm of the window size (i.e., n) as parameters. Instead of directly storing a and b, the range registers store the lower bound -a and a mask for the window (i.e.,  $2^n - 1$ ), as shown in Figure 4. The masked random number is R' = 3, which when added to the lower bound -4 gives the bounded random number -1. Since the bounded random number can be computed ahead of time, the critical path only consists of one adder that adds the demand miss line address i and the bounded random number (as shown by the dotted arrow).

### V. SECURITY EVALUATION

As shown in Table I, reuse based attacks consist of cache collision attacks and Flush-Reload attacks, which correspond to two information leakage channels: the timing channel and the storage channel. By definition, the timing channel exploits the timing characteristics of events to transfer information [24], [25], whereas the storage channel transfers information through the setting of bits by one program and the reading of those bits by another [24]. We show that our random cache fill strategy is able to completely close the known timing channel and provide a strong information-theoretic security assurance against the storage channel, when the random fill window of the victim process is properly chosen.

#### A. Timing Channel

We analyze known cache collision attacks that exploit the impact of the reuse of security-critical data on the aggregated time. Data reuse always comes in a pair of memory accesses  $(x_i \text{ and } x_j)$ , where  $x_i$  precedes  $x_j$ ). We abstract the impact as the difference of the expected execution time under the conditions of cache collision  $(\mu_1)$  and no collision  $(\mu_2)$ , respectively:

Table III  $P_1 - P_2$  and the number of measurements for a successful cache collision attack, for various window sizes

| window size:            |                | size=1  | size=2    | size=4                                        | size=8                                            | size=16 | size=32 |  |

|-------------------------|----------------|---------|-----------|-----------------------------------------------|---------------------------------------------------|---------|---------|--|

| Random fill + 4-way SA  | $P_1 - P_2$    | 0.652   | 0.332     | 0.127                                         | 0.044                                             | 0.012   | 0.006   |  |

| Kandolli III + 4-way SA | # measurements | 65,000  | 1,866,000 | 16,653,000                                    | 000 no success after trying $2^{24}$ measurements |         |         |  |

| Random fill + Newcache  | $P_1 - P_2$    | 0.576   | 0.292     | 0.119                                         | 0.045                                             | 0.016   | 0.007   |  |

| Random m + Reweache     | # measurements | 244,000 | 2,106,000 | no success after trying $2^{24}$ measurements |                                                   |         |         |  |

$$\mu_{1} = \mu_{0} + P_{1} \cdot t_{hit} + (1 - P_{1}) \cdot t_{miss}$$

$$\mu_{2} = \mu_{0} + P_{2} \cdot t_{hit} + (1 - P_{2}) \cdot t_{miss}$$

(2)

where  $\mu_0$  is the expectation of the aggregated time excluding the security-critical access  $x_j$ ,  $t_{hit}$  and  $t_{miss}$  are the cache hit and miss latencies, respectively.  $P_1$  and  $P_2$  are the cache hit probabilities under the conditions of cache collision and no collision, defined as follows:

$$P_{1} = P(x_{j} \text{ hit} | \langle x_{i} \rangle = \langle x_{j} \rangle)$$

$$P_{2} = P(x_{j} \text{ hit} | \langle x_{i} \rangle \neq \langle x_{j} \rangle)$$

(3)

The expectation of the timing difference  $(\mu_2 - \mu_1)$  is the signal that an attacker wants to extract, which depends on  $P_1$  and  $P_2$  as follows:

$$\mu_2 - \mu_1 = (P_1 - P_2)(t_{miss} - t_{hit}) \tag{4}$$

This means that no information can be extracted from the timing characteristics if  $P_1 - P_2 = 0$  for any arbitrary pair of security-critical accesses. In fact,  $P_1 - P_2$  (or  $\mu_2 - \mu_1$ ) directly reflects the difficulty of the attack. The number of measurements required for a successful attack is related to  $P_1 - P_2$  as:

$$N \approx \frac{2Z_{\alpha}^2}{\left(\frac{(P_1 - P_2)(t_{miss} - t_{hit})}{\sigma_T}\right)^2}$$

(5)

where  $\alpha$  is the desired likelihood of discovering the secret key, and represents how we define a successful attack.  $Z_{\alpha}$ is the quantile of the standard normal distribution for a probability  $\alpha$ .  $\sigma_T$  is the variance of the execution time. Equation (5) is obtained using a derivation similar to that in [26] and [27]. It indicates that when  $P_1 - P_2 = 0$ , the attack cannot succeed (infinite number of measurements are required).

The purpose of the random cache fill strategy is to zero out the signal that an attacker can extract, not just simply add noise to the attacker's measurements. In the following, we show how the random cache fill strategy achieves  $P_1 - P_2 = 0$ . Assume the security-critical data is contained in a contiguous memory region with M cache lines, starting at  $M_0$ . Consider two memory accesses  $x_i$ and  $x_j$  to the security-critical memory lines i and j where  $i, j \in [M_0, M_0 + M - 1]$ , respectively. Further assume 1) the memory line i is not cached yet (i.e., the cache warmup phase) and the memory access  $x_i$  initiates a random fill within window [i - a, i + b], 2) there are no other accesses to memory line *i* in between  $x_i$  and  $x_j$ , 3) the cache state is clean. This represents the best case for the attacker. Then we can calculate the two conditional probabilities:

$$P_{1} = \frac{1}{a+b+1}$$

$$P_{2} = \begin{cases} \frac{1}{a+b+1}, & j \in [i-a,i+b] \\ 0, & j \notin [i-a,i+b] \end{cases}$$

(6)

Equation (6) indicates that for arbitrary i and j, if j is in the random fill window of i,  $P_1 - P_2 = 0$  always holds. The sufficient and necessary condition that gives  $j \in [i-a, i+b]$ is  $a, b \ge M - 1$ . This means that when the random fill window is sufficient to cover the whole lookup table, the random fill cache ensures that  $P_1 - P_2 = 0$  for any pair of security-critical accesses, and hence completely closes the timing channel. However, if we examine  $P_1 - P_2$  for the conventional set-associative cache, and for the Partitioning and Randomization based secure caches, we find that  $P_1 - P_2 \approx 1$  always holds under the same assumptions, since the memory access  $x_i$  will always bring the memory line i into the cache.

Note that a cryptographic program may contain multiple independent lookup tables, so the total size of all the security-critical data may not be small – this is why other solutions which require pre-loading all the security-critical data may fail to scale when the size of security-critical data is large. However, an individual table is usually small and the random fetch window size is determined by the individual table size, and thus is usually relatively small.

**Case Study – Cache Collision Attacks against AES:** In fact, the timing channel can be substantially mitigated even when the window size is small. In this section, we use cache collision attacks against AES as a case study to investigate how the random fill window size impacts the security of a random fill cache. Consider the final round AES table  $T_4$ . It is 1 KB in size and contains 16 cache lines (assume cache line size is 64 bytes). So, a random fill window with a = b = 15 is large enough to cover the whole AES table for any table lookup. There are 16 table lookups to  $T_4$  for each block encryption. We use Monte Carlo simulation to calculate the average  $P_1 - P_2$  for all the table lookup pairs within the 16 table lookups. We perform 100,000 trials in the Monte Carlo simulation and each trial does AES encryption of one block of random plaintext.

Table III shows the average  $P_1 - P_2$  for different random fill window sizes. We include results for two cases: 1) the random fill cache built upon a conventional 4-way setassociative (SA) cache (32 KB in size); 2) the random fill cache built upon Newcache (with the same cache size as the SA cache). The first column with "size=1" in Table III also represents the 4-way SA cache and Newcache with the demand fetch policy. We use a bidirectional random fill window  $[i - 2^n, i + 2^n - 1]$ , because the randomized table lookups in cryptographic algorithms do not favor the forward direction over the backward direction, so a bidirectional random fill window has the best security.

We make the following observations: 1) Both SA cache and Newcache have a large  $P_1 - P_2$ , thus are vulnerable to cache collision attacks (the first column with "size=1"). 2) Our random cache fill strategy is effective against cache collision attacks for both SA cache and Newcache. In fact, as a cache fill strategy, it can be built on any cache architecture. 3)  $P_1 - P_2$  drops dramatically as the window size increases. Note that due to the inaccuracy of the Monte Carlo method, we cannot achieve exactly  $P_1 - P_2 = 0$  when the window size is 32.

We further verify our conclusions by performing real cache collision attacks [4]. The simulator configuration is similar to what we use for the performance evaluation (Table IV) except we minimize the impact of a non-blocking cache by using only 1 miss queue entry for 1 non-blocking cache miss. This configuration favors the attacker since we find that it requires about 1 order of magnitude less samples compared to the baseline configuration in Table IV, which has 4 miss queue entries. The results are shown in Table III. When the window size increases, the number of measurements required increases drastically. When the window size is larger than 4, the attacks all fail after collecting  $2^{24}$ measurements. (It takes more than three weeks of continuous simulation on gem5 to collect  $2^{24}$  measurements). Note that attacking Newcache requires slightly more measurements than attacking the SA cache because cache collision attacks require each measurement to start from a clean cache, and completely cleaning Newcache is harder than cleaning the SA cache, due to Newcache's random replacement algorithm.

#### B. Storage Channel

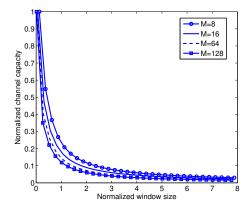

For the storage channel, e.g., in a Flush-Reload attack, we can directly calculate the channel capacity using the channel model in [11]. Similar to the proof for the timing channel, we assume the security-critical data is contained in a contiguous memory region with M cache lines, starting at  $M_0$ . The victim process is the sender who accesses security-critical memory line  $i \in [M_0, M_0+M-1]$ , which can be represented by a random variable S. Let j be the memory line that is randomly filled into the cache due to the access of i, then we have  $j \in [M_0 - a, M_0 + M - 1 + b]$  for the random fill

Figure 5. Channel capacity for different window sizes. The window size is normalized to the size of the security-critical data (contains M cache lines). The channel capacity is normalized to the demand fetch case.

window of the form [i - a, i + b]. Due to the boundary effect, memory lines that are outside the security-critical region may be brought into the cache. Here, we assume the best case for the attacker: the attacker can access the data outside the security-critical region and hence can determine which memory line is brought into the cache. Therefore, the attacker is the receiver who can exactly observe the symbol j, which can be represented by a random variable R. Then the conditional probability that the attacker receives a symbol j given the victim process sends symbol i is

$$P_{ij} = P(R = j | S = i) = \begin{cases} \frac{1}{W} & i - a \le j \le i + b\\ 0 & otherwise \end{cases}$$

(7)

where W is the window size: W = a + b + 1.

The channel capacity is the mutual information of S and R when S satisfies a uniform distribution, i.e., P(S = i) = 1/M. We have the channel capacity as [28]

$$C = \sum_{i,j} P(S = i, R = j) \log \frac{P(S = i, R = j)}{P(S = i) \cdot P(R = j)}$$

$$= \sum_{i,j} \frac{1}{M} P_{ij} \cdot \log \frac{M \cdot P_{ij}}{\sum_{i} P_{ij}}$$

(8)

where M is the number of cache lines of the security-critical data,  $P_{ij}$  is the conditional probability defined in Equation (7).

Figure 5 shows how the window size impacts the channel capacity for various sizes of security-critical data. The channel capacity is normalized to the demand fetch case and the window size is normalized to the size of the security-critical data. Due to the boundary effect, the storage channel cannot be completely closed. However, we find that the channel capacity drops dramatically as the window size increases. For example, the channel capacity is already reduced by more than one order of magnitude when the window size is twice the size of the security-critical region. The impact

Table IV SIMULATOR CONFIGURATIONS

| Parameter                   | Value               |

|-----------------------------|---------------------|

| ISA                         | ALPHA               |

| Processor type              | 4-way out-of-order  |

| L1 instruction cache        | 4-way 32 KB         |

| L2 cache                    | 8-way 2 MB          |

| Cache line size             | 64 bytes            |

| Cache replacement algorithm | LRU                 |

| miss queue entries          | 4                   |

| L1/L2 hit latency           | 1 cycle / 20 cycles |

| DRAM frequency/channels     | DDR3-1600/1         |

of the boundary effect is smaller for larger security-critical regions. As mentioned in section II, the Flush-Reload attack requires the attacker and the victim to share the securitycritical data, which can be easily disabled by not declaring the security-critical data as read-only, hence the information leakage through the storage channel is a less serious threat than the information leakage through the timing channel. Nevertheless, our random fill cache still provides a strong information-theoretic security assurance against this type of side channel leakage even when sharing is allowed.

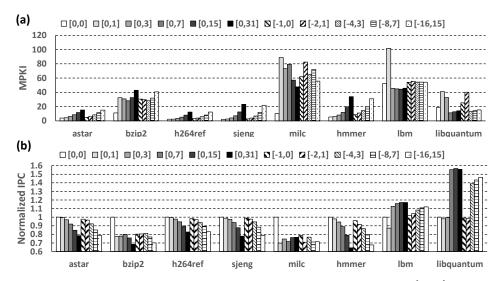

### VI. PERFORMANCE EVALUATION

We implemented our random fill cache on a cycle-accurate simulator, gem5 [20]. We use a 4-way, out-of-order processor with two levels of caches in our performance evaluation, and the baseline configuration is shown in Table IV. The baseline cache is a set-associative cache with least recently used (LRU) replacement algorithm and without a prefetcher. The DRAM models the detailed timing of a single channel DDR3-1600.

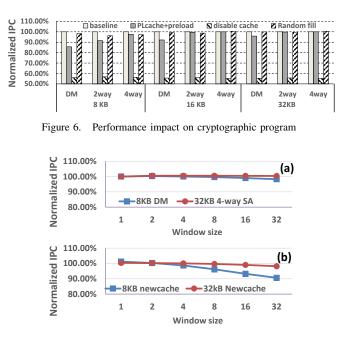

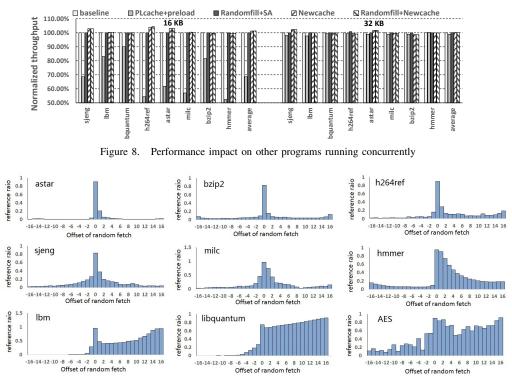

Performance impact on cryptographic algorithm: We first study how the random fill cache performs for cryptographic algorithms. Our workload is the OpenSSL's AES encryption that takes a 32 KB random input and does a cipher block chaining (CBC) mode of encryption. The results are shown in Figure 6 for various cache sizes and associativity. The Instruction Per Cycle (IPC) metric is normalized to the baseline demand-fetched cache with the same cache size and associativity. We also compared the performance with two previous constant-time solutions against the cache collision attacks: the "disable cache" approach disables the cache for security-critical accesses to the 5 AES tables for encryption. The "PLcache+preload" approach pre-loads all the 5 AES tables and uses the locking mechanism provided by the PLcache to lock these tables in the cache. We chose the "PLcache+preload" approach because it has better performance than the "informing loads" approach [14]. The random fill window is configured to be of the form [i - 16, i + 15], which can cover the whole table for any pair of security-critical accesses to the table.

As can be expected, the "disable cache" solution degrades the performance by 45% for all the cache configurations, since security-critical accesses contribute about 24% of

Figure 7. Impact of window size for the random cache fill strategy built on (a) SA cache, (b) Newcache, when running AES

the total accesses to the data cache. The performance of "PLcache+preload" is sensitive to the cache size and associativity. When the cache size is small (8KB), more than half of the cache lines are locked for the security-critical data. It incurs 15% degradation for the direct-mapped (DM) cache and 3% degradation for the 4-way SA cache when the cache size is 8 KB. "PLcache+preload" also does not work well when the associativity is low; it incurs more than 4% degradation for the DM cache even when the cache size is 32 KB. The random fill cache is less sensitive to the cache size and associativity. The performance degradation is less than 3.5% even when the cache size is 8 KB, and there is no degradation for larger caches.

Note that our conclusions are not specific to AES. The reason why the random fill cache can maintain good performance is that it still takes advantage of the spatial locality of the key-dependent data flow. The slight performance degradation when the cache size is small is due to fetching of unused data that is outside the security-critical region. We also study how the performance is impacted when both the L1 and L2 caches are random fill caches. We find that the performance impact is negligible since the L2 cache is large and can better tolerate the potential cache pollution due to the random fill of unused data.

**Impact of window size:** Figure 7(a) shows that when the random fill cache is built upon the SA cache, the performance is not sensitive to the window size for both the worst case (8 KB DM cache) and the best case (32 KB 4-way SA cache). When built upon Newcache (Figure 7(b)), our random fill cache works slightly worse than for the SA cache, when running AES. As the window size increases,

Figure 9. Effectiveness of random cache fill strategy for general workloads

the performance also decreases (maximum degradation is 9% when the window size is 32 for the 8 KB cache). This is because when the window size is large, it is more likely to fetch unused data into the cache and evict frequently-used data through the random replacement algorithm.