|                                                                                                                                                                                                           | Report Docume                                                                                                                                                                                                                                                  | entation Page                                                                                                                                                                                                |                                                                                                                                                                                                         |                                                                                                                                                         | Form Approved<br>1B No. 0704-0188                                                                                                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| maintaining the data needed, and c<br>including suggestions for reducing                                                                                                                                  | lection of information is estimated to<br>completing and reviewing the collect<br>this burden, to Washington Headqu<br>uld be aware that notwithstanding ar<br>DMB control number.                                                                             | ion of information. Send comments<br>arters Services, Directorate for Infor                                                                                                                                  | regarding this burden estimate<br>mation Operations and Reports                                                                                                                                         | or any other aspect of the s, 1215 Jefferson Davis                                                                                                      | nis collection of information,<br>Highway, Suite 1204, Arlington                                                                                                    |  |  |  |

| 1. REPORT DATE<br>OCT 1986                                                                                                                                                                                |                                                                                                                                                                                                                                                                | 2. REPORT TYPE                                                                                                                                                                                               |                                                                                                                                                                                                         | 3. DATES COVERED<br>00-00-1986 to 00-00-1986                                                                                                            |                                                                                                                                                                     |  |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                     |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 5a. CONTRACT                                                                                                                                            | NUMBER                                                                                                                                                              |  |  |  |

| Special- or Genera                                                                                                                                                                                        | l-Purpose Hardwar                                                                                                                                                                                                                                              | e for Prolog: A Con                                                                                                                                                                                          | nparison                                                                                                                                                                                                | 5b. GRANT NUM                                                                                                                                           | /BER                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 5c. PROGRAM ELEMENT NUMBER                                                                                                                              |                                                                                                                                                                     |  |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 5d. PROJECT NU                                                                                                                                          | JMBER                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 5e. TASK NUME                                                                                                                                           | BER                                                                                                                                                                 |  |  |  |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 5f. WORK UNIT                                                                                                                                           | NUMBER                                                                                                                                                              |  |  |  |

| University of Calif                                                                                                                                                                                       | ZATION NAME(S) AND AE<br>ornia at Berkeley,D<br>omputer Sciences,B                                                                                                                                                                                             | epartment of Electr                                                                                                                                                                                          | ical                                                                                                                                                                                                    | 8. PERFORMINO<br>REPORT NUMB                                                                                                                            | G ORGANIZATION<br>ER                                                                                                                                                |  |  |  |

| 9. SPONSORING/MONITO                                                                                                                                                                                      | RING AGENCY NAME(S) A                                                                                                                                                                                                                                          | ND ADDRESS(ES)                                                                                                                                                                                               |                                                                                                                                                                                                         | 10. SPONSOR/M                                                                                                                                           | ONITOR'S ACRONYM(S)                                                                                                                                                 |  |  |  |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)                                                                                                               |                                                                                                                                                                     |  |  |  |

| 12. DISTRIBUTION/AVAII<br>Approved for publ                                                                                                                                                               | LABILITY STATEMENT<br>ic release; distribut                                                                                                                                                                                                                    | ion unlimited                                                                                                                                                                                                |                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                     |  |  |  |

| 13. SUPPLEMENTARY NO                                                                                                                                                                                      | DTES                                                                                                                                                                                                                                                           |                                                                                                                                                                                                              |                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                     |  |  |  |

| special-purpose CI<br>architecture with t<br>SPUR simulators.'<br>size, execution spec<br>mixed instruction a<br>a static code size 14<br>times the number of<br>implementation rec<br>SPUR instruction s | es the performance<br>SC architecture) an<br>agged data). Fourte<br>The two implementa<br>ed, and cache perfor<br>and data cache. We<br>4 times larger than t<br>of machine cycles. T<br>quires a cache that i<br>set to improve its Pr<br>ould greatly reduce | d the Berkeley SPU<br>en standard benchn<br>ations were compare<br>mance. The simulat<br>found that, on avera<br>he PLM, executes 1<br>o have the same mis<br>s 4 to 8 times that of<br>olog execution and o | R processor (a genark programs weed with regard to<br>ted with regard to<br>ted memory syste<br>age, the macro-co<br>6 times more inst<br>as ratio with a mu<br>f the PLM. We all<br>outline the design | eneral-purpos<br>ere run on bo<br>static and dy<br>m included a<br>oded SPUR in<br>tructions, yet<br>ich larger coo<br>lso suggest m<br>i of a special- | se RISC<br>oth the PLM and<br>vnamic program<br>direct-mapped<br>nplementation has<br>requires only 2.31<br>de size the SPUR<br>inor changes to the<br>purpose SPUR |  |  |  |

| 15. SUBJECT TERMS                                                                                                                                                                                         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                     |  |  |  |

| 16. SECURITY CLASSIFIC                                                                                                                                                                                    | CATION OF:                                                                                                                                                                                                                                                     |                                                                                                                                                                                                              | 17. LIMITATION OF<br>ABSTRACT                                                                                                                                                                           | 18. NUMBER<br>OF PAGES                                                                                                                                  | 19a. NAME OF<br>RESPONSIBLE PERSON                                                                                                                                  |  |  |  |

| a. REPORT<br>unclassified                                                                                                                                                                                 | b. ABSTRACT<br>unclassified                                                                                                                                                                                                                                    | c. THIS PAGE<br>unclassified                                                                                                                                                                                 | Same as<br>Report (SAR)                                                                                                                                                                                 | 120                                                                                                                                                     | RESTONSIBLE LENSON                                                                                                                                                  |  |  |  |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std Z39-18 .

# Special- or General-Purpose Hardware for Prolog: A Comparison

Gaetano Borriello Andrew Cherenson Peter Danzig Michael Nelson

Report No. UCB/CSD 87/314 Computer Science Division Department of Electrical Engineering and Computer Sciences University of California Berkeley, California 94720

#### ABSTRACT

This study compares the performance of executing Prolog code on the Berkeley PLM processor (a special-purpose CISC architecture) and the Berkeley SPUR processor (a general-purpose RISC architecture with tagged data). Fourteen standard benchmark programs were run on both the PLM and SPUR simulators. The two implementations were compared with regard to static and dynamic program size, execution speed, and cache performance. The simulated memory system included a direct-mapped mixed instruction and data cache. We found that, on average, the macro-coded SPUR implementation has a static code size 14 times larger than the PLM, executes 16 times more instructions, yet requires only 2.31 times the number of machine cycles. To have the same miss ratio with a much larger code size the SPUR implementation requires a cache that is 4 to 8 times that of the PLM. We also suggest minor changes to the SPUR instruction set to improve its Prolog execution and outline the design of a special-purpose SPUR coprocessor that would greatly reduce the code size and double SPUR's Prolog performance.

#### 1. Introduction

Logic programming has been the subject of much attention since the 1981 announcement that the Japanese Fifth Generation Project [Moto-oka83] would use Prolog as its principal programming language. Many computer researchers in the artificial intelligence community believe that logic programming provides a more direct and natural mapping of problem specifications into machine language than traditional high-level languages. In the past few years, much work has been done to develop high-performance machines for logic programming.

Prolog is the most popular of the logic programming languages. It was designed at the University of Marseille around 1970 by Alain Colmerauer and his associates. In 1977, David Warren at the University of Edinburgh developed the first compiled implementation of Prolog [Warren77]. The compiler ran on a DECsystem-10 and was dramatically faster than previous, interpreted implementations. Since then, many approaches, ranging from advanced compiler techniques to microcoded hardware enhancements, have been used to improve the performance of compiled Prolog code.

Most compiled implementations of Prolog are based on refinements to Warren's original abstract machine (WAM) specification [Warren83]. Warren's instruction set corresponds very closely to the tokens of the Prolog language. Compiling from Prolog to WAM is therefore a simple and straight-forward process that can reasonably be implemented in Prolog itself.

The Berkeley Prolog Machine (PLM) is a special-purpose microcoded processor that uses a slightly modified version of the WAM instruction set [Dobry84c]. Efficient Prolog execution is achieved through the much higher code density of the PLM as compared to conventional, general-purpose architectures. The PLM is expected to run Prolog ten times faster than the compiled implementation for the DEC-2060. The PLM is part of the larger Berkeley Aquarius project whose aim is to build a 16 processor Prolog multiprocessor with a shared synchronization memory [Dobry85].

The Berkeley SPUR (Symbolic Processing Using RISCs) project aims to produce a multiprocessor personal workstation for high-performance general-purpose processing with some support for Lisp and floating-point computation [Hill86]. The SPUR microprocessor is a reduced instruction set computer (RISC) with extensions for tagged data types and a large mixed instruction and data cache. It includes a tightly-coupled coprocessor interface. The first coprocessor to be implemented will be used for high-performance IEEE standard floating-point operations.

Our objective is to show how well Prolog programs can be executed on SPUR, a processor not designed with logic programming applications in mind. We did not compile Prolog directly into SPUR machine code but instead used the output of the PLM compiler and performed a macro-expansion of the PLM/WAM instructions into SPUR instructions. Improvements in performance could certainly be gained by building a Prolog compiler for the SPUR architecture. We chose to use a macro-expansion technique so as to save time (there was no Prolog implementation for SPUR) and also to better compare the two architectures rather than the difference between two compilers. We feel we have achieved our objective of finding a lower bound for Prolog execution using macro-expansion with a few straight-forward optimizations.

If Prolog runs efficiently on SPUR, then Prolog programs can be easily integrated with an operating system, floating point hardware, and other applications programs to create a test-bed for experiments in mixed-paradigm programming systems. Although both SPUR and PLM are the basic elements of larger multiprocessor machines, we did not consider the issues of parallelism inherent in Prolog on either of these two architectures.

The next two sections provide background information on the PLM and SPUR architectures. We then discuss how PLM instructions were translated into SPUR instructions using macro-expansion. Section 4 considers tradeoffs with respect to register allocation, stack usage, and the prolog unification operations in mapping PLM to SPUR. Section 5 presents our performance comparisons results including static and dynamic program size, execution speed, and memory cache effects. We conclude with suggestions to improve Prolog performance with slight modifications to the SPUR architecture or with the use of a special coprocessor.

The appendices contain the programs that perform the macro-expansions, the macro-expansions, and the details of a possible implementation of a Prolog coprocessor for SPUR.

- 2 -

## 2. The PLM Architecture

The Berkeley PLM is a TTL implementation based on the Warren Abstract Machine, the target machine of the first Prolog compiler [Warren77]. Warren implemented a compiler that translates Prolog into abstract machine instructions that were then macro-expanded into DEC-10 machine code. Previous Prolog implementations were interpreters that were usually written in Lisp, and therefore suffered from the inefficiency of being translated twice, once from Prolog to Lisp and again from Lisp to machine code.

Warren's abstract machine is the basis of most of the work being done on special-purpose Prolog hardware. This section describes WAM as modified by Tick and Warren [Tick83, Warren83] and by the Berkeley PLM group [Dobry84b, Fagin85]. Dobry gives detailed descriptions of the PLM in [Dobry84a, Dobry84c, Dobry85]. Clocksin and Mellish [Clocksin81] provide a good foundation for the basics of Prolog and logic programming.

# 2.1. PLM Data Types and Representation

The PLM supports four (tagged) data types: constants, variables, lists, and structures. Constants have a minor type of nil, integer, atom, or floating point. Variables, actually pointers to other data structures, are bound (point to a data cell) or unbound (point to themselves). Lists and structures are cdr-coded to eliminate pointers to successive locations (car and cdr cells are distinguished by using a tag bit). This technique can eliminate up to half the amount of memory necessary to represent lists and structures and many pointer dereferences when a the elements of a list can be kept in a contiguous group of memory locations. Figure 1 summarizes the PLM data types and illustrates their layouts. It is important to note that the PLM tags consist of three orthogonal fields: type, sub-type, and cdr (or bound) bit. All tags also have a bit used by a garbage collection algorithm.

## 2.2. PLM Registers and Data Structures

The PLM organizes memory into

- a code segment;

- five stacks, consisting of the environment stack, choice point stack, "heap", trail stack, and the "push down list";

- sixteen data registers;

- a few mode bits.

These features are described below.

#### 2.2.1. Environment Stack

The environment stack contains activation records of active Prolog clauses. An activation record consists of a pointer to the previous record, a code space address to jump to should the clause succeed, the clause argument count, room to store the clause's local variables, and a pointer to the last choice point entry

| Bound Variable    | var     | 0       | g.c. | -       |         |      |

|-------------------|---------|---------|------|---------|---------|------|

|                   |         |         |      |         |         |      |

| Unbound Variable  | var     | 1       | g.c. | -       |         |      |

|                   |         |         |      |         |         |      |

| Structure         | struct  | 0       | g.c. | -       |         |      |

|                   | L       |         |      | L       | <u></u> | <br> |

| List Head         | list    | 0       | g.c. | -       |         |      |

|                   | L       | 1       | 1,   | 1       |         |      |

| List Continuation | list    | 1       | g.c. | -       |         |      |

|                   | L       | <b></b> |      |         |         |      |

| NIL               | const   | 1       | g.c. | 1 1     |         |      |

|                   | <b></b> |         |      |         |         |      |

| Constant          | const   | 0       | g.c. | subtype |         |      |

|                   |         |         |      |         |         |      |

Figure 1. PLM data types. Tags consist of a two-bit field for the type of data: variable, structure, list, or constant. Variables contain a one-bit field indicating whether they are bound (and point to another data cell) or unbound (and point to themselves). This bit is always zero in structure pointers. In list pointers this field distinguishes car from cdr cells in the cdr-coded data structure supported by the PLM. This bit is also set to indicate a constant is nil. Constants also have another two-bit subtype field. All tags have a bit used by a garbage collection algorithm.

should the clause use the cut operator. (The cut operator increases backtracking efficiency by pruning branches from the depth-first search tree.)

## 2.2.2. Choice Point Stack

This stack contains procedure choice points. A choice point is a set of 15 PLM registers containing the necessary state to backtrack to a previous node in the search tree. It consists of the original procedure arguments, a pointer to the

environment of the calling procedure, a pointer to the top of the heap at the time the procedure was invoked, a pointer to the top of the trail stack at procedure invocation time, a code space address should the procedure succeed, a code space address should backtracking be necessary, and a pointer to the previous choice point (this is needed since the PLM interleaves the choice point stack and the environment stack in the same stack segment).

#### 2.2.3. Heap

Space for dynamically constructed lists and structures is sequentially allocated from the heap, which behaves very much like a stack. Heap space is reclaimed when a procedure fails, but must be garbage-collected periodically since data structures created by successful clauses would not otherwise be reclaimed.

#### 2.2.4. Trail Stack

As Prolog programs perform their pattern matching functions, variables in one data structure are "bound" (i.e. made to point) to the corresponding element of the second data structure. In order to restore the computation's state when a clause fails (pattern matching fails) and backtracking occurs, all variable bindings must be reversible. The trail contains pointers to variables on the heap that have become bound during procedure execution. On goal failure, all trail entries above the saved heap pointer stored in the choice point are read and the variables they point to are unbound.

#### 2.2.5. Push Down List

The push down list is a high-speed stack inside the PLM and is used to store pointers into two data structures that are being unified (i.e. pattern matched). Since lists or structures can contain embedded lists or structures as elements, unification is a recursive process. List or structures are unified in a depth-first, post-order tree traversal. The push down list is an optimization to reduce the complexity of managing another stack in memory and to increase unification performance.

#### 2.2.6. Registers

Finally, the PLM has the following special-purpose registers: a program counter register (P); a goal success program counter (CP); pointers to the top of the environment, choice point, trail, and heap stacks (E, B, Tr, and H respectively); a structure pointer register (S); the procedure argument count register (N); eight argument registers (AX1-AX8); and two bits of control state called the cut bit and the read/write mode bit.

#### 2.3. PLM Instructions

PLM instructions fall into eight classes:

- procedure control instructions that manipulate choice points;

- indexing instructions that perform multi-way branches depending on the type and value of an argument register;

- clause control instructions that manipulate activation records on the environment stack;

- get and put instructions that verify and prepare goal arguments respectively; and

- unify instructions that construct and compare structures and lists one element at a time by pattern matching the corresponding elements.

Instruction lengths range from 1 to 6 bytes. Tailoring the instruction set to the language produces high code density for the PLM. Smaller program sizes result in much improved instruction buffer and cache performance. This will be shown to be the primary reason for the PLM's excellent performance. However, instruction fetching and decoding is greatly complicated due to the variable-length unaligned instruction format.

The PLM's instruction buffer performs the bulk of the instruction prefetching and decoding functions. Instructions are broken up into an 8-bit opcode field, a 32-bit first argument field, and for instructions of more than one argument there is an additional 32-bit field containing the two single-byte second and third arguments. These are presented to the central processor for final decoding and execution. There is only a small set of conditional branch instructions in the PLM. The instruction buffer stops prefetching when one of these instructions is encountered and simply waits for the branch to be resolved. The PLM instruction buffer typically contains from five to sixteen instructions.

## 2.4. Stack Allocation Optimizations for Prolog

Warren included two more memory saving optimizations in his original implementation: environment trimming and tail recursion elimination. Environment trimming frees space from the activation record of a clause as soon as a variable is no longer referenced. This requires an additional field to the call instruction so the size of the activation record can be updated as each subclause of a clause is invoked. Larger memory sizes have probably made this optimization unnecessary.

Tail recursion elimination discards the activation record of a clause before the invocation of the last subclause. This optimization is quite valuable in recursive procedures that would otherwise quickly fill up stack space with unused activation records. The only restriction imposed by this method is that recursive clauses should be purely tail recursive. This condition is usually true in practice and can be enforced in almost every case. However, this important optimization does require a special PLM instruction to move needed variables from the activation record to the heap. The activation record's registers can replace those of the parent clause since failure of the last recursive clause implies a failure of the parent clause, popping both records off the stack.

## 2.5. System Support Functions

PLM instructions are complex since they execute in an indeterminate amount of time (e.g. recursive unification) and they can generate an indeterminate number of memory references per instruction. The first point makes instructions difficult to restart. A large amount of micro-engine state must be preserved between instructions. The second point implies that page faults may occur during the execution of a long instruction. In the current architecture, the PLM is a coprocessor to an NCR-32 main processor that handles memory management and process scheduling functions for the PLM. It is important to note that the PLM cannot be easily context-switched to another Prolog process while a page request is being serviced.

The NCR host processor not only provides virtual memory support but also performs I/O system calls and floating point operations for PLM escape instructions. However, these operations are expensive since they must be performed by a loosely-coupled coprocessor reached through the system bus rather than a tightlycoupled coprocessor reached through a direct interface.

## 3. The SPUR Architecture

The SPUR (Symbolic Processing Using RISCs) architecture is a RISC architecture augmented with special support for LISP processing and floating-point computation. The added capabilities include tagged data types and a tightlycoupled coprocessor interface. SPUR has been designed as a multiprocessor workstation. It has a 128KB cache that maintains data coherency by using hardware support for bus snooping. SPUR extends the work of the earlier Berkeley RISC and SOAR architectures [Katevenis83, Ungar84]. A summary of SPUR and PLM features is listed in Table 1.

#### 3.1. SPUR Registers and Tags

The basic instruction and data word is 32 bits, however, registers are 40 bits wide so as to support an 8-bit data tag. Data is always word-aligned. Tagged data is stored in 2 words containing a total of 64 bits: the first word is the data and the second is the tag. Although the SPUR system bus supports only 32-bit transfers to the processor cache, all other busses are 40 bits wide. Therefore, a penalty for tagged data transfers is only incurred when data is brought into the cache or written back out to memory.

|                                    | Comparison of PLM       | and SPUR                                                                                                                   |

|------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Features                           | PLM                     | SPUR                                                                                                                       |

| architecture                       | tagged CISC             | tagged RISC                                                                                                                |

| target languages                   | Prolog only             | LISP, C & others                                                                                                           |

| instruction size                   | 1 to 6 bytes            | 4 bytes                                                                                                                    |

| cycles per instr.<br>(no misses) † | 1 to 26+                | 1 (2 for stores)<br>4+ for floating-point ops                                                                              |

| avg. cycles/instr.                 | 7                       | 1                                                                                                                          |

| cycle time                         | 100–150 ns              | 100-140 ns                                                                                                                 |

| registers                          | 9 special<br>8 argument | <ul><li>138 GPRs in 8 overlapped windows</li><li>(10 global, 6 input, 10 local, and</li><li>6 output per window)</li></ul> |

| cache                              | separate I&D, 16KB each | mixed I&D, 128KB                                                                                                           |

| instr. buffer size                 | 5 to 16 instructions    | 128 instructions                                                                                                           |

| microcode size                     | 1K x 134 bits           | not applicable                                                                                                             |

Table 1. Summary of features of the PLM and SPUR architectures.

<sup>†</sup> This assumes a perfect memory (i.e. no cache or instruction buffer misses) for both PLM and SPUR. For SPUR, load instructions are assumed to be followed by a non-dependent instructions (as is the case in our implementation). SPUR store intructions stall the pipeline and hence require two cycles. There are 138 general-purpose registers in SPUR organized into 8 overlapped windows of 32 registers. Of these 32, there are 10 global registers accessible in all windows, 6 input registers that overlap with the previous window, 10 local registers that are accessible in only one window, and 6 outputs that overlap with the next window. When a function call is executed, the CPU shifts its current window. Input parameters and output results are passed between functions by using the overlapped registers. All registers are general-purpose except one of the global registers that is hard-wired to a zero value.

Special trap conditions are signaled when the windows overflow (i.e. a function call depth of more than 8 is reached) or underflow and a trap handler is used to move registers to and from memory. When a window is available, function calls proceed very quickly, only when windows overflow or underflow are memory accesses to preserve register state necessary. Halbert and Kessler have shown that window overflows occur less 1% of the time for a window size of 8 [Halbert80].

#### 3.2. SPUR Instructions

Instructions fall into three basic types. Most instructions are register-toregister operations involving the entire 40-bit quantity. Special exceptions are signaled depending on the value of the tags (e.g. adding two pointers). There are also instructions that cause operations to be performed on coprocessor registers (e.g. floating-point add).

The load-to-register and store-from-register instructions are the only instructions that access memory. There are instructions for making either 32-bit untagged data and instruction access as well as full 40-bit tagged access. Specialized instructions are provided for moving data between the cache and the coprocessor registers in sizes corresponding to the IEEE floating-point standard and for transfers between processor and coprocessor registers. Lastly, there are comparison and branch instructions that alter control flow depending on the value of a CPU register, coprocessor register, or data tag.

SPUR is equipped with an on-chip instruction buffer of 128 words. Instructions are prefetched but compete with load and store instructions for access to the mixed instruction and data cache. All instructions are aligned and have uniform argument format, consequently, no alignment or predecoding is necessary. As a result the instruction buffer is a straight-forward on-chip instruction cache.

## 3.3. Pipeline Execution

SPUR has a four-stage pipeline: instruction fetch, register read and an ALU operation either to combine operands or compute and effective address, memory access (for load and store instructions) or nothing (for register-to-register instructions), and register write. The pipeline includes circuitry for forwarding data that may be required by the next instruction and not yet stored back into a register. The effective throughput is therefore one instruction per cycle.

- 9 -

Due to the structure of the pipeline, the effects of load and branch instructions are delayed one cycle beyond their execution. The contents of a register that is loaded from the cache cannot be accessed by the next instruction. It is necessary to include some operations that do not use that register or a NOP in the slot immediately following the load instruction. A similar situation holds for branch instructions. The instruction immediately following a branch will be executed whether or not the branch is taken. SPUR provides special branch instructions that cancel the effects of the subsequent instruction when the branch is taken. However, carefully placement of instructions in the slot following a branch can greatly improve throughput.

## 3.4. SPUR Address Spaces

SPUR has a 38-bit global virtual address space and 32-bit process virtual address space. The high-order two bits of the address select one of four segments and the remaining 30 bits are an offset into the segment. Typically, the first segment contains the operating system and the other three contain the process's code, data, and stack segments, respectively. During address translation, the 2 bit segment number is used to index a set of four segment registers each of which contains an 8-bit global segment number that selects one of 256 segments. The 8-bit segment number is concatenated with the 30-bit offset to form the 38-bit global virtual address.

## 3.5. Coprocessor Interface

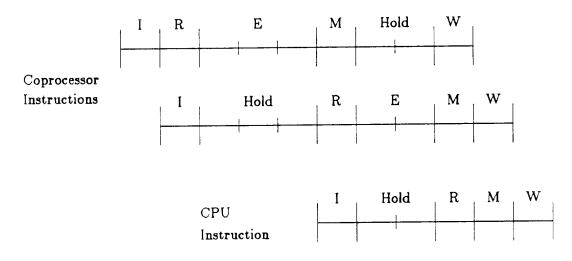

SPUR supports a tightly-coupled coprocessor model. The CPU initiates all data transfers between the coprocessor registers and the cache using a 64-bit wide data bus. All instruction dispatching is performed by the CPU. When the CPU fetches an instruction that is not for the main processor it forwards it to the coprocessor.

The coprocessor interface consists of a set of lines for communicating the coprocessor instruction opcode and register arguments. One control signal indicates to the coprocessor that a new instruction is being presented by the CPU and another indicates the coprocessor has completed execution. When the coprocessor requires more than one cycle for instruction execution it suspends the CPU pipeline by asserting a coprocessor busy signal.

Coprocessors can also operate in parallel with the CPU. All responsibility for waiting the appropriate amount of time for results to be available rests with the CPU. An extra bit in the interface is used to select one of two coprocessors that could both be used in parallel.

#### 3.6. System Support Functions

SPUR handles all its own traps and page faults. For this reason, unlike the PLM, all instructions are restartable and atomic in their operation. The SPUR processor has all the general-purpose instructions and trap handling capability to

directly support an operating system. The PLM would require additional microcode support these functions.

## 4. Implementing Prolog on SPUR

This section describes the mechanics of macro-expanding Prolog into SPUR assembly language and how the state of the PLM is mapped onto the SPUR registers.

## 4.1. Macro-expanding PLM on SPUR

We chose macro-expanding PLM instructions rather than writing a full Prolog compiler for SPUR because its simplicity enabled us to find a lower bound on SPUR Prolog performance in just a few weeks. Undoubtedly, a compiler would achieve much better performance. In this section, we review the design alternatives we considered to represent the PLM's state and describe the design we chose to implement. We also describe the tools we developed to automatically macroexpand PLM instructions to SPUR code.

# 4.1.1. Choice Points, Environments, and Registers

Many of the PLM registers point into its multiple data and activation record stacks. We chose a register allocation scheme that follows the tenet that the optimal register layout is the one that reduces the processor-memory bandwidth. Since choice points are much larger than environment activation records, we decided to exploit SPUR's register windows for choice point buffering. Register windows cannot be used to represent the environment and heap structures since it must be possible to bind to these structures and it would be extremely complex to bind to registers (registers don't have a memory address). Using them as a trail buffer is difficult since trail entries are single words and really require a hardware stack rather than SPUR's overlapping register windows. Also, since access to the trail is strictly LIFO, any buffering scheme would only eliminate a single store and a single load per entry. The Berkeley PLM research group estimated that trail buffering in hardware could at best yield a 1% performance gain [Dobry84c].

Our register usage is shown in Table 2. From this table one can see that there is a close match between the size of a choice point and the size of SPUR register window. Each window keep the argument registers local and overlaps state registers with the preceding and following windows (choice points). This is precisely the type of behavior required, access to the previous choice point is also required in the PLM. Choice point buffering with register windows reduces the instruction data fetch collisions on the try, try\_me\_else, retry, and retry\_me\_else instructions. Rather than interfering with data fetches, the contents of choice point registers can be obtained from internal processor registers rather than a stack frame in memory. Backtracking is accomplished with register move operations and the shifting of register windows. Choice point buffering appears to be the only natural use for SPUR's register windows.

The equivalent of the PLM B register in the SPUR implementation no longer contains a pointer into memory but now points to a register window. This number is incremented when a choice point is pushed and decremented when a

| SP      | UR Regist | er Allocation for PLM       |

|---------|-----------|-----------------------------|

| Type    | Register  | Use                         |

| Globals | 0         | hardwired 0                 |

|         | 1-8       | PLM AX1-AX8                 |

|         | 9         | Pointer to constant table   |

| Inputs  |           | Previous Choice Point       |

| _       | 10        | PLM E register              |

|         | 11        | PLM TR register             |

|         | 12        | PLM H register              |

|         | 13        | PLM B register              |

|         | 14        | PLM BP register             |

|         | 15        | PLM CP register             |

| Locals  |           | Linkage and Temporaries     |

|         | 16        | PLM S mode flag             |

|         | 17        | PLM Cut mode flag           |

|         | 18-25     | PLM AX1-AX8 and CP when     |

|         |           | window becomes choice point |

| Outputs |           | Current Choice Point        |

| -       | 26        | PLM E register              |

|         | 27        | PLM TR register             |

|         | 28        | PLM H register              |

|         | 29        | PLM B register              |

|         | 30        | PLM BP register             |

|         | 31        | PLM CP register             |

**Table 2.** Register allocation for PLM registers in SPUR register windows. Globals are used for the argument registers of the current choice point and for pointers to constant tables. When a choice point needs to pushed onto the stack, the argument register are moved into the local registers and the register window shifted. Otherwise the locals are used for temporaries and the S register, which is not shared across choice points. The overlap of the input and output registers makes the values of the registers of the previous choice point available to the current one.

choice point is popped. The PLM's S register is a local temporary register since its value is not needed across choice points. The ten SPUR local registers are used as temporaries by the macro expansion code. The eight argument registers are kept in global registers. This leaves only a single register (R9) for indexing into a constant table. This originally caused us to suggest that more global SPUR registers would be useful, however, a level of indirection solves this problem at minimal cost.

Since the PLM design includes only a single choice point buffer, we anticipate better performance than the PLM for programs that push and pop choice points often but not too deeply (more than 8). Operations that push choice points account for 10% of the execution time of PLM and, as expected, operations that pop choice points account for only 3% of its operation time. This asymmetry is due to popping multiple choice points during a single cut instruction. Efficient programs perform less backtracking and would be expected to pop more than one choice point in a single operation; a 3:1 push to pop ratio is typical. For programs that do push choice points deeply, our design will suffer the same performance degradation as the PLM. However, this type of behavior is unlikely to be a part of most programs.

An alternative to the register layout that we chose is to eliminate the argument registers (AX) and store the arguments in the procedure activation record as done in other programming languages. However, this requires more load and store instructions that would add to the instruction-data fetch bandwidth bottleneck. The advantage of this method is that it frees the SPUR global registers for other uses. Neither approach requires modification to the PLM compiler and their true merits will best be determined by simulation.

## 4.1.2. Register Windows and the Recursive Unify Operations

Unfortunately, the large size of SPUR's register windows reduces their effectiveness for recursive unification. Recursive unification must save only three registers per invocation. Since 16 new register become available on a window shift, this leaves 13 registers unused. Unrolling the unify code five times would permit the use of 15 of the 16 registers. This seems promising, however, the increased code size could be detrimental to instruction buffer and cache performance. In addition to unrolling the unify code, there are at least two other possible approaches to implementing recursive unify: implementing the recursion stack in memory and using the register windows directly by replacing the overflow/underflow trap handler to save and restore only three registers. Yet another possibility is to have the SPUR hardware provide two window sizes, one as currently implemented and another small one for procedures that may be highly recursive but only require a small number of arguments. We chose the simplest path and implemented our own recursion stack in memory.

## 4.1.3. Macro-expanding PLM Instructions

Although there are papers that describe the PLM instruction set, the PLM simulator [Dobry84a] is the only place that accurately describes the semantics of all PLM instructions. Our approach to macro-expanding PLM to SPUR was to use the model of PLM functionality provided by the PLM level 1 simulator. The simulator is written in C and contains a separate procedure for each PLM instruction. Some of the procedures share common subroutines. Essentially, we handcompiled the procedures in the PLM simulator into SPUR assembly language; the functions that simulated an instruction were made into macros and the common functions were put into a subroutine library loaded with every SPUR program. Since we tried not to deviate from the PLM simulator, we employed minimal optimizations. The only optimizations were to use the SPUR tags to simulate the PLM tags and register windows for choice points.

In addition to the special stack needed for recursive unify, we also had to implement our own procedure call mechanism for calling the common functions. When calling a common function, the arguments are put into temporary registers, the return address is put into a temporary register, and then the SPUR *jump* instruction is used to execute the procedure. No registers have to be saved.

We implemented two of the commonly used large macros as function calls in order to reduce the code size at the expense of four extra instructions, two to call and two to return. Since these macros were complex, the extra overhead is small compared to the number of instructions executed in the function. Table 3 shows the improvements in code size because of this optimization on the Prolog

|            | Static Code  | Size of Mac | ro-expan | ded Benchm  | arks    |         |

|------------|--------------|-------------|----------|-------------|---------|---------|

| Benchmark  | No functions | Functions   | C1 / C2  | Functions   | C2 / C3 | C1 / C3 |

|            | (C1)         | for two     | -        | for 3 more  |         |         |

|            |              | largest     |          | large       |         |         |

|            |              | macros (C2) |          | macros (C3) |         |         |

| conl       | 594          | 414         | 1.44     | 385         | 1.08    | 1.54    |

| con6       | 610          | 430         | 1.42     | 401         | 1.07    | 1.52    |

| divide10   | 4922         | 3988        | 1.23     | 1688        | 2.36    | 2.92    |

| hanoi      | 585          | 385         | 1.52     | 385         | 1.00    | 1.52    |

| log10      | 4606         | 4040        | 1.14     | 1676        | 2.41    | 2.75    |

| mutest     | 2945         | 1703        | 1.73     | 1152        | 1.48    | 2.56    |

| nrev1      | 2153         | 761         | 2.83     | 669         | 1.14    | 3.22    |

| ops8       | 4692         | 3804        | 1.23     | 1632        | 2.33    | 2.88    |

| palin25    | 3982         | 2556        | 1.56     | 1632        | 1.57    | 2.44    |

| pri2       | 2061         | 1933        | 1.07     | 1704        | 1.13    | 1.21    |

| qs4        | 3608         | 1230        | 2.93     | 1038        | 1.19    | 3.48    |

| queens     | 3826         | 3636        | 1.05     | 2998        | 1.21    | 1.28    |

| query      | 4136         | 3942        | 1.05     | 3768        | 1.05    | 1.10    |

| times10    | 4398         | 3988        | 1.25     | 1728        | 2.31    | 2.55    |

| Geom. mean |              |             | 1.45     |             | 1.44    | 2.06    |

**Table 3.** This table shows the reduction in static code size when large commonly used macros are implemented as subroutine calls to a library routine. The first column shows the code size if none of the macros are turned into functions. The second column shows the code size if  $unify\_constant$  and  $unify\_value$  are turned into functions as was done in our macro-expansion. The third column shows the ratio of column 1 to column 2. Column 4 shows the code size if  $get\_list$ ,  $get\_structure$  and  $unify\_variable$  were turned into functions. Columns 5 and 6 show the ratio of column 2 to column 4 and column 1 to column 4 respectively. The bottom row is the geometric mean over all of the benchmarks. A short description of the benchmarks is given in Table 4. benchmarks. It also shows what would happen if we implemented some of the smaller commonly used macros as function calls. We see that the benchmarks with two macros implemented as function calls have a code size 44 percent greater than that attainable if five macros were function calls. Overall, benchmarks that do not use function calls for the macros are over twice as large as benchmarks that use all five.

# 4.1.4. Software to Apply Macro-expansions to Benchmark Programs

Once we had generated the macro-expansions of PLM instructions to SPUR instructions we developed a software system to automatically apply the macro-expansions to the compiled PLM benchmark programs. We developed **preproc** and **postproc**, and used /lib/cpp (a standard Unix utility) as well as **sas** and **sld** (written by the SPUR Lisp group) to generate the macro-expansions. The sequence that transforms a PLM program into SPUR assembly code is:

#### preproc

It takes the PLM instructions and puts them in a format that can be used by /lib/cpp to perform the macro-expansion. It also extracts all constants from the PLM code and puts them into a constant table.

#### /lib/cpp

This program is the standard Unix C preprocessor. Its purpose is to macroexpand the properly formatted PLM instructions into SPUR assembly language.

#### postproc

By the time this program sees the PLM program it has already been macroexpanded to SPUR code. However, most of the macros have labels within them. Since a macro can be used in many different places in the code and labels must be global, there would be many label conflicts if the code was passed to the SPUR assembler. It is the purpose of **postproc** to change all of the labels to global labels.

#### sas and sld

These are the SPUR assembler and loader. They take SPUR assembly code and turn it into object code that runs on the SPUR simulator.

A script to run this sequence of commands to produce a file that runs on the SPUR simulator is shown in Appendix 1.

# 5. Comparison of Prolog Performance on PLM and SPUR

Our goal of running the benchmark programs on the SPUR and PLM simulators and comparing their performance was accomplished in three steps. First we wrote macro-expansion and software development tools and applied these to the benchmarks listed in Table 4. We automatically generated SPUR instructions from their PLM instructions for all but one (ckt2) of these benchmarks programs. Next we ran the macro-expanded programs on the SPUR simulator to determine if the expansions were correct and to generate memory references traces. To verify the correctness of the macro-expansions, we modified the SPUR simulator to print out the data structures generated by the Prolog program. Lastly, we modified the PLM simulator to generate memory traces.

## 5.1. Modifications to the PLM and SPUR Simulators

#### 5.1.1. The PLM Simulator

Two PLM simulators were graciously provided by Tep Dobry of the Aquarius-PLM project. The level 1 simulator simulates the macro-architecture of PLM whereas the level 2 simulator simulates the micro-architecture. We chose to

|          | Prolog Benchmarks                                       |                 |  |  |  |  |  |

|----------|---------------------------------------------------------|-----------------|--|--|--|--|--|

| Name     | Description                                             | Lines<br>of PLM |  |  |  |  |  |

| conl     | Deterministic concatenation of two lists.               | 29              |  |  |  |  |  |

| con6     | Non-deterministic concatenation of two lists.           | 33              |  |  |  |  |  |

| ckt2     | Design of a 2 by 1 MUX using NAND gates.                | 601             |  |  |  |  |  |

| divide10 | Symbolic differentiation using division.                | 222             |  |  |  |  |  |

| hanoi    | Solution to Tower of Hanoi problem with 8 disks.        | 55              |  |  |  |  |  |

| log10    | Symbolic differentiation using logarithms.              | 216             |  |  |  |  |  |

| mutest   | Proof of theorem in Hofstadter's mu math system.        | 142             |  |  |  |  |  |

| nrev1    | Naive reversal of a list of 30 numbers.                 | 73              |  |  |  |  |  |

| ops8     | Symbolic differentiation using a polynomial.            | 214             |  |  |  |  |  |

| palin25  | Program to generate a palindrome.                       | 187             |  |  |  |  |  |

| pri2     | Program to find prime numbers less than 100.            | 141             |  |  |  |  |  |

| qs4      | A quicksort program of 50 numbers.                      | 125             |  |  |  |  |  |

| queens   | Solution to the queens problem on a 4 by 4 chess board. | 267             |  |  |  |  |  |

| query    | A data base query problem.                              | 340             |  |  |  |  |  |

| times10  | Symbolic differentiation using multiplication.          | 222             |  |  |  |  |  |

**Table 4.** The 15 benchmarks used in the PLM performance study [Dobry85]. All have been implemented on SPUR except for ckt2.

instrument the level 1 simulator because it is much easier to understand and modify than the level 2 version. It is important to note that the level 1 simulator was designed to run the benchmarks and is not capable of executing all Prolog programs. Many system support and escape instructions are not implemented. This is the reason that larger benchmark programs were not run.

The simulator, as provided, kept frequency counts of instructions and statistics on the number of reads and writes, dereferences, unifications and bindings. We enhanced the simulator by adding code to output memory reference traces and to compute the number of cycles executed. To generate data for our cache studies, we modified the simulator to log memory reference traces. Very few changes were required to record data references because data references go through the two routines *stick* (data write) and *stuck* (data read). However, more detective work was needed to make sure that all references to the code space ("Cspace") were recorded since constants as well as instructions are stored in Cspace. In addition, we modified the simulator to record the real size of instructions so instruction references also record the size of the instruction being fetched.

The level 1 simulator, unlike the level 2 simulator, does not keep track of the number of cycles executed. We added a table containing the average number of cycles executed for each instruction. The values in the table were derived using the same calculation style as the Berkeley PLM group. Where decisions had to be made, we attempted to calculate the worst case path with the exception of general unify, decdr, and dereference operations since the PLM chose average times for these operations in their calculations. Hence, data structures with multiple dereferences take longer than the table suggests. We compute the total number of cycles executed by a program from the instruction frequency and the cycle tables. The total cycles executed is not a precise value but a lower bound of the real value.

A 'hook' routine was added to **barb** (the SPUR simulator) to handle escape calls. Escapes are functions that cannot be handled by the PLM and must be handled by the host. In our implementation arithmetic comparison escapes are handled in-line, but escapes for I/O and arithmetic are handled in **barb**. Many escapes are analogous to system calls so it is fair not to expect either the SPUR or PLM implementations to handle them in-line.

#### 5.2. Results

We compared the static and dynamic code sizes, number of instructions executed, of the SPUR and PLM versions of the benchmarks in tables 5 and 6. The SPUR versions of the benchmarks are, as expected, uniformly larger than their PLM counterparts. Table 5 shows static sizes of the benchmarks in instructions and bytes. The instruction ratios range from 7.40 (hanoi) to 19.52 (log10). The low ratio for hanoi is because one-half of its PLM instructions map to sequences of 1 or 2 SPUR instructions, fully one-third of the PLM instructions executed map to sequences of just 1 SPUR instruction. The high ratio for log10 is because 40% of

| Static Code Size |         |        |         |        |                 |                |              |  |  |

|------------------|---------|--------|---------|--------|-----------------|----------------|--------------|--|--|

|                  | PI      | JM     | SP      | UR     | S/P             |                |              |  |  |

| Benchmark        | #Instr. | #Bytes | #Instr. | #Bytes | Instr.<br>ratio | Bytes<br>ratio | With<br>func |  |  |

|                  |         |        |         |        | 1200            | 1400           | bytes        |  |  |

| conl             | 28      | 87     | 414     | 1656   | 14.79           | 19.03          | 51.08        |  |  |

| con6             | 32      | 106    | 430     | 1720   | 13.44           | 16.23          | 42.53        |  |  |

| divide10         | 213     | 661    | 3988    | 15952  | 18.72           | 24.13          | 28.36        |  |  |

| hanoi            | 52      | 183    | 385     | 1540   | 7.40            | 8.42           | 23.65        |  |  |

| log10            | 207     | 625    | 4040    | 16160  | 19.52           | 25.86          | 30.32        |  |  |

| mutest           | 141     | 468    | 1703    | 6812   | 12.08           | 14.56          | 20.51        |  |  |

| nrev1            | 71      | 260    | 761     | 3044   | 10.72           | 11.71          | 22.43        |  |  |

| ops8             | 205     | 633    | 3804    | 15216  | 18.56           | 24.04          | 28.44        |  |  |

| palin25          | 178     | 565    | 2556    | 10224  | 14.36           | 18.10          | 23.03        |  |  |

| pri2             | 132     | 383    | 1933    | 7732   | 14.64           | 20.19          | 27.47        |  |  |

| qs4              | 121     | 456    | 1230    | 4920   | 10.17           | 10.79          | 16.90        |  |  |

| queens           | 242     | 723    | 3636    | 14544  | 15.03           | 20.12          | 23.97        |  |  |

| query            | 273     | 1138   | 3942    | 15768  | 14.44           | 13.86          | 16.31        |  |  |

| times10          | 213     | 661    | 3988    | 15952  | 18.72           | 24.13          | 28.35        |  |  |

| Geom. mean       |         |        |         |        | 14.00           | 17.06          | 26.11        |  |  |

Table 5. Static Code Size for the PLM and SPUR Benchmarks. The average number of bytes per PLM instruction is 3.30. There is an additional 697 instructions (1788 bytes) of functions loaded with each SPUR program.

the PLM instructions are either get\_structure (approximately 43 SPUR instructions) or unify\_variable (approximately 29 SPUR instructions). The mean SPUR/PLM ratio for instructions and bytes are 14.00 and 17.06 respectively. The byte ratio is larger because the average PLM instruction is 3.30 bytes. Note that these byte ratios do not include the code for a fixed-size subroutine library loaded with each SPUR benchmark. It is interesting compare the size of this subroutine library (1.8KB) with the size of the PLM microcode (about 17KB).

Comparison of the dynamic code size shows that SPUR executes on average about 16 instructions for each PLM instruction (see Table 6). The hanoi benchmark had the lowest ratio (11.81). The query benchmark has the highest ratio (20.77) for which we do not see a ready explanation. These ratios do not reflect the real amount of work done by the PLM since PLM instructions take from one to over 26 cycles to execute while SPUR instructions only take one cycle to execute. Comparing the number of SPUR instructions executed to the number of PLM cycles executed shows that on average, SPUR, requires 2.31 cycles for each PLM cycle. The SPUR/PLM cycle ratio ranges from 1.96 for hanoi and pri2 to 4.09 for query. Excluding query, the highest ratio is 2.67 for con6.

|            |        | Inst   | ructions | and Cyc | les Exe | cuted    |       |           |      |

|------------|--------|--------|----------|---------|---------|----------|-------|-----------|------|

| Benchmark  | PLM    |        | SP       | SPUR    |         | SPUR/PLM |       | SPUR NOPs |      |

|            | Instr. | Cycles | Instr.   | Cyles   | Instr.  | Cycles   | #     | %         | #    |

| conl       | 43     | 296    | 627      | 672     | 14.58   | 2.27     | 78    | 12.44     | 2    |

| con6       | 133    | 1006   | 2474     | 2685    | 18.60   | 2.67     | 294   | 11.88     | 30   |

| divide10   | 447    | 3512   | 6724     | 7374    | 15.04   | 2.10     | 785   | 11.67     | 2    |

| hanoi      | 11996  | 79097  | 141644   | 154911  | 11.81   | 1.96     | 17095 | 12.07     | 765  |

| log10      | 145    | 1182   | 2859     | 3139    | 19.72   | 2.57     | 330   | 11.54     | 2    |

| mutest     | 12983  | 116967 | 249960   | 263243  | 19.25   | 2.25     | 36021 | 14.41     | 7    |

| nrev1      | 4092   | 31825  | 62216    | 65846   | 15.20   | 2.07     | 7993  | 12.85     | 2    |

| ops8       | 260    | 1935   | 3583     | 3918    | 13.78   | 2.02     | 438   | 12.22     | 4    |

| palin25    | 3540   | 27092  | 64620    | 68838   | 18.25   | 2.54     | 9326  | 14.43     | 11   |

| pri2       | 14567  | 109384 | 195985   | 213929  | 13.45   | 1.96     | 22589 | 11.53     | 579  |

| qs4        | 6596   | 49308  | 96456    | 103648  | 14.62   | 2.10     | 11792 | 12.23     | 2    |

| queens     | 5177   | 36350  | 76575    | 83135   | 14.79   | 2.29     | 9509  | 12.42     | 236  |

| query      | 21973  | 116845 | 456396   | 478223  | 20.77   | 4.09     | 55877 | 12.24     | 1910 |

| times10    | 375    | 2891   | 5410     | 5916    | 14.43   | 2.05     | 650   | 12.01     | 2    |

| Geom. mean |        |        |          |         | 15.81   | 2.31     |       | 12.39     |      |

**Table 6.** Dynamic Code Size for PLM and SPUR. For SPUR, the number of cycles executed is calculated by adding the number of instructions executed to the number of data writes from Table 7, effectively double counting store instructions. This is necessary because the store instruction take two cycles to execute. Using the data from this table and from Table 7, the average number of cycles per SPUR instruction is 1.07.

The percentage of no-op instructions in the SPUR code averages 12.39% (Table 6). Most of the no-op slots in the branch, call and return instructions were not used, but many were used after jumps. The barb hook column in Table 6 measures the number of calls to **barb** to handle I/O and arithmetic operations. Table 7 shows the number of data reads and writes for the benchmarks. Generally, SPUR does 3% more reads and 18% more writes than PLM. The ratio of SPUR/PLM reads ranges from 0.72 (log10) to 1.43 (con1) and the ratio for writes ranges from 0.88 (qs4) to 2.37 (con1). The con1 benchmark has anomalous behavior because it performs almost twice as many reads and writes for SPUR than for PLM.

#### 5.3. Analysis of Memory Traces

Up to now, we have compared performance for the two machines assuming that all memory references are completed in one cycle. This is the type of performance measurement used in [Dobry85]. A more realistic model of performance would consider the memory system used by the architecture. The memory reference traces enable us to do detailed simulations of cache performance and compare the effect of SPUR's increased code size on the miss ratio. The memory trace data was analyzed using the **dineroIII** cache simulator [Hill83, Hill85].

| Number of Data References |             |       |      |        |       |      |  |  |  |

|---------------------------|-------------|-------|------|--------|-------|------|--|--|--|

| Benchmark                 |             | Reads |      | Writes |       |      |  |  |  |

|                           | PLM         | SPUR  | S/P  | PLM    | SPUR  | S/P  |  |  |  |

| conl                      | 21          | 30    | 1.43 | 19     | 45    | 2.37 |  |  |  |

| con6                      | $\cdot$ 225 | 268   | 1.19 | 161    | 211   | 1.31 |  |  |  |