## NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

### RESEARCH, DEVELOPMENT AND TESTING OF A FAULT-TOLERANT FPGA-BASED SEQUENCER FOR CUBESAT LAUNCHING APPLICATIONS

by

Lucas S. Parobek

March 2013

Thesis Co-Advisors:

Herschel H. Loomis, Jr. James H. Newman

Approved for public release; distribution is unlimited

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  | Form Approx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ved OMB No. 0704–0188                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collecti<br>searching existing data sources, gather<br>comments regarding this burden estima<br>Washington headquarters Services, Diro<br>22202–4302, and to the Office of Mana                                                                                                                                                                                                                               | ing and maintaining the data nee<br>the or any other aspect of this col<br>ectorate for Information Operation                                                                                                                                                                                                      | eded, and completing<br>lection of information<br>s and Reports, 1215 Jo                                                                                                                                         | ponse, including the<br>and reviewing the co-<br>including suggestion<br>offerson Davis Highw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | time for reviewing instruction,<br>ollection of information. Send<br>ns for reducing this burden, to<br>yay, Suite 1204, Arlington, VA                                                                                                                                            |

| 1. AGENCY USE ONLY (Leave )                                                                                                                                                                                                                                                                                                                                                                                                                    | blank) 2. REPOR<br>March                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ND DATES COVERED<br>r's Thesis                                                                                                                                                                                                                                                    |

| <ul> <li><b>4. TITLE AND SUBTITLE</b> RESE<br/>A FAULT-TOLERANT FPGA-BA<br/>LAUNCHING APPLICATIONS</li> <li><b>6. AUTHOR(S)</b> Lucas S. Parobek</li> </ul>                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  | 5. FUNDING N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NUMBERS                                                                                                                                                                                                                                                                           |

| 7. PERFORMING ORGANIZAT<br>Naval Postgraduate School<br>Monterey, CA 93943–5000                                                                                                                                                                                                                                                                                                                                                                | 'ION NAME(S) AND ADDR                                                                                                                                                                                                                                                                                              | ESS(ES)                                                                                                                                                                                                          | 8. PERFORMI<br>REPORT NUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ING ORGANIZATION<br>/IBER                                                                                                                                                                                                                                                         |

| 9. SPONSORING /MONITORIN<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                | G AGENCY NAME(S) ANI                                                                                                                                                                                                                                                                                               | O ADDRESS(ES)                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ING/MONITORING<br>PORT NUMBER                                                                                                                                                                                                                                                     |

| <b>11. SUPPLEMENTARY NOTES</b> or position of the Department of De                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                   |

| 12a. DISTRIBUTION / AVAILA                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  | 12b. DISTRIB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                   |

| Approved for public release; distrib<br>13. ABSTRACT (maximum 200 v                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | А                                                                                                                                                                                                                                                                                 |

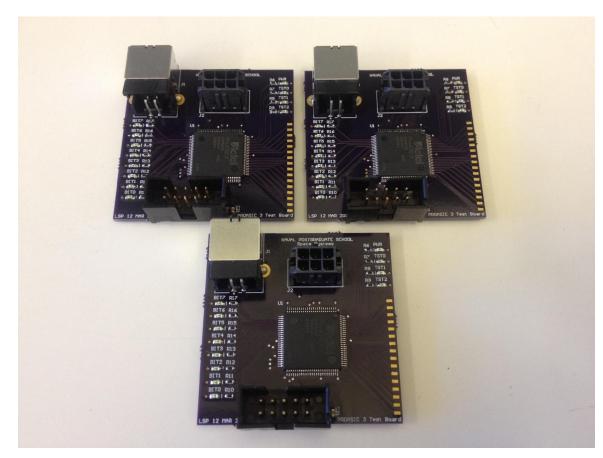

| This thesis concerns various m<br>design. The first specific applic<br>shall be capable of the timing a<br>capability for quick reconfigur<br>toward sequencer construction;<br>further evolves to selection of t<br>on a development kit with a<br>experiments to determine optin<br>selected as the technique for fau<br>schematic design and printed c<br>Board' is fully discussed. A for<br>implementation of fault-tolerat<br>discussed. | ation of this research is a se<br>nd accurate deployment of<br>ration prior to launch. Thi<br>field programmable gate an<br>he Actel ProASIC3 series of<br>nalysis of results provided<br>num resource utilization a<br>alt-tolerant logic implement<br>ircuit board layout. The ma<br>llow-on flight prototype bo | equencer develope<br>multiple CubeSats<br>s research consid<br>rays (FPGAs) are<br>of FPGAs. Initial<br>d. Fault-tolerant<br>nd timing scheme<br>tation in the seque<br>unufacturing, integ<br>ard is designed w | d for deploying (<br>from a host space<br>ers a variety of<br>chosen as the pri-<br>logic test configu-<br>techniques are constructed<br>techniques are constructed<br>to the second second<br>second second second second<br>provide the second second second<br>second second second second<br>second second second second<br>second second second second<br>second second second second second<br>second second second second second<br>second second second second second<br>second second second second second second<br>second second second second second<br>second second second second second second<br>second second second second second second second<br>second second second second second second second second second second<br>second second secon | CubeSats. The sequencer<br>becraft and shall have the<br>hardware for suitability<br>mary device. The design<br>mations are implemented<br>compared with a set of<br>ar redundancy (TMR) is<br>y test boards are built via<br>g of the 'ProASIC3 Test<br>ve hardware allowing for |

| <b>14. SUBJECT TERMS</b> Single-Even<br>(MBU), Field Programmable Gate A<br>(TMR), Quadruple Force Decide R                                                                                                                                                                                                                                                                                                                                    | Array (FPGA), Fault Toleranc                                                                                                                                                                                                                                                                                       | e, Triple Modular R                                                                                                                                                                                              | edundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15. NUMBER OF<br>PAGES<br>224                                                                                                                                                                                                                                                     |

| Actel, Microsemi, ProASIC3, Xilin                                                                                                                                                                                                                                                                                                                                                                                                              | x, Virtex                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16. PRICE CODE                                                                                                                                                                                                                                                                    |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                    | 18. SECURITY<br>CLASSIFICATION OF TH<br>PAGE<br>Unclassified                                                                                                                                                                                                                                                       | ABSTRA                                                                                                                                                                                                           | FICATION OF<br>ACT<br>nclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20. LIMITATION OF<br>ABSTRACT<br>UU                                                                                                                                                                                                                                               |

| NSN 7540-01-280-5500 Standard Form 298 (Rev. 2-89)                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | dard Form 298 (Rev. 2-89)                                                                                                                                                                                                                                                         |

Prescribed by ANSI Std. 239–18

Approved for public release; distribution is unlimited

### **RESEARCH, DEVELOPMENT AND TESTING OF A FAULT-TOLERANT FPGA-BASED SEQUENCER FOR CUBESAT LAUNCHING APPLICATIONS**

Lucas S. Parobek Lieutenant, United States Navy B.S., The Citadel, 2006

Submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

### NAVAL POSTGRADUATE SCHOOL March 2013

Author:

Lucas S. Parobek

Approved by: Herschel H. Loomis, Jr. Thesis Co-Advisor

> James H. Newman Thesis Co-Advisor

Clark Robertson Chair, Department of Electrical and Computer Engineering

### ABSTRACT

This thesis concerns various means of implementing fault tolerance in logic for use in a general payload processor design. The first specific application of this research is a sequencer developed for deploying CubeSats. The sequencer shall be capable of the timing and accurate deployment of multiple CubeSats from a host spacecraft and shall have the capability for quick reconfiguration prior to launch. This research considers a variety of hardware for suitability toward sequencer construction; field programmable gate arrays (FPGAs) are chosen as the primary device. The design further evolves to selection of the Actel ProASIC3 series of FPGAs. Initial logic test configurations are implemented on a development kit with analysis of results provided. Fault-tolerant techniques are compared with a set of experiments to determine optimum resource utilization and timing schemes. Triple modular redundancy (TMR) is selected as the technique for fault-tolerant logic implementation in the sequencer. Preliminary test boards are built via schematic design and printed circuit board layout. The manufacturing, integration and testing of the 'ProASIC3 Test Board' is fully discussed. A follow-on flight prototype board is designed with more extensive hardware allowing for implementation of fault-tolerant techniques and future growth capability. Recommendations for future work are discussed.

### TABLE OF CONTENTS

| I.   | INTI      | RODUCTION                                                  | 1   |  |  |  |

|------|-----------|------------------------------------------------------------|-----|--|--|--|

|      | А.        | PURPOSE                                                    | 1   |  |  |  |

|      | В.        | NAVAL POSTGRADUATE SCHOOL CUBESAT LAUNCHER                 |     |  |  |  |

|      |           | (NPSCUL) BACKGROUND                                        |     |  |  |  |

|      |           | 1. NPSCuL Objective and History                            | 3   |  |  |  |

|      |           | 2. NPSCuL Physical Design Characteristics                  | 3   |  |  |  |

|      |           | 3. History of Sequencer Requirement                        | 5   |  |  |  |

|      |           | 4. Concept of Sequencer Development                        | 6   |  |  |  |

|      |           | 5. Sequencer Requirements and Specifications               |     |  |  |  |

|      | C.        | RELATED WORK AND DOCUMENTATION                             |     |  |  |  |

|      | D.        | CONCEPT OF DEVELOPMENT STRATEGY                            | 10  |  |  |  |

|      | Е.        | THESIS ORGANIZATION                                        | .11 |  |  |  |

| II.  | SEQ       | UENCERS, RADIATION HARDENING, AND FAULT-TOLERANCE          | 13  |  |  |  |

|      | <b>A.</b> | SEQUENCER DESIGN METHODOLOGY                               | 13  |  |  |  |

|      |           | 1. Timing Concerns Specific to Initiating P-POD Deployment |     |  |  |  |

|      |           | 2. Chosen Approach                                         | .14 |  |  |  |

|      | В.        | RADIATION HARDENING                                        |     |  |  |  |

|      |           | 1. Single-Event Effects (SEEs)                             | 16  |  |  |  |

|      |           | a. Single-Event Upsets (SEUs)                              | .17 |  |  |  |

|      |           | b. Single-Event Transients (SETs)                          | .18 |  |  |  |

|      |           | c. Single-Event Latch-ups (SELs)                           | .19 |  |  |  |

|      |           | 2. Total Ionizing Dose (TID)                               | 19  |  |  |  |

|      |           | 3. Testing of FPGA Hardware in Radiation Environments      | 20  |  |  |  |

|      |           | 4. Radiation Protection Approaches                         | 20  |  |  |  |

|      | C.        | FAULT TOLERANCE                                            |     |  |  |  |

|      |           | 1. Scrubbing / Re-programming at Intervals                 |     |  |  |  |

|      |           | 2. Triple Modular Redundancy (TMR)                         |     |  |  |  |

|      |           | a. Block TMR (BTMR)                                        | .24 |  |  |  |

|      |           | b. Local TMR (LTMR)                                        | .25 |  |  |  |

|      |           | c. Global TMR (GTMR)                                       | .25 |  |  |  |

|      |           | d. Distributed TMR (DTMR)                                  | .26 |  |  |  |

|      |           | 3. Quadded Logic                                           |     |  |  |  |

|      |           | 4. Triplicated Interwoven Redundancy (TIR)                 |     |  |  |  |

|      |           | 5. Quadruple Force Decide Redundancy (QFDR)                | 30  |  |  |  |

|      |           | 6. Advantages and Disadvantages of Various Fault-Tolerant  |     |  |  |  |

|      |           | Techniques                                                 | 31  |  |  |  |

|      | D.        | CHAPTER SUMMARY                                            |     |  |  |  |

| III. | FIEI      | LD PROGRAMMABLE GATE ARRAYS AND SELECTION OF               |     |  |  |  |

|      |           | UENCER TECHNOLOGY                                          | 33  |  |  |  |

|      | A. C      | FIELD PROGRAMMABLE GATE ARRAYS                             |     |  |  |  |

|      |           | 1. Physical Construction                                   |     |  |  |  |

|     |     | a. Internal Fabric3                                           | 34        |

|-----|-----|---------------------------------------------------------------|-----------|

|     |     | b. Programmability and Reconfiguration                        | 36        |

|     |     | 2. Historical Overview of FPGA Technology                     | 37        |

|     |     | 3. Types of Modern FPGA Technology                            | 39        |

|     |     | a. Antifuse-based FPGAs                                       | 39        |

|     |     | b. SRAM-based FPGA Implementations4                           | 10        |

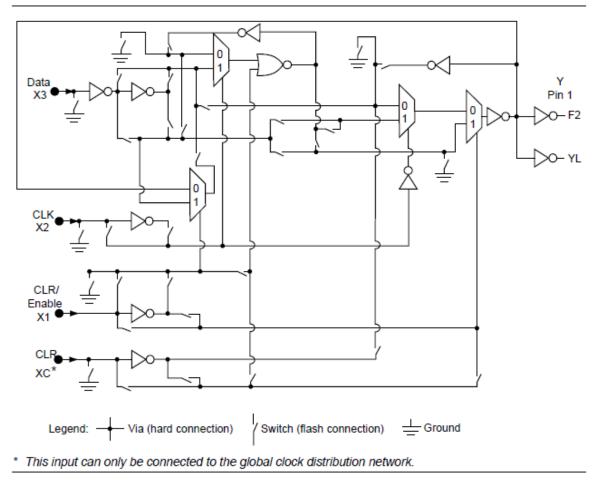

|     |     | c. Flash-based FPGAs4                                         |           |

|     |     | 4. Design Concerns4                                           |           |

|     | B.  | FINAL SELECTION OF ACTEL PROASIC3 SERIES FPGA4                |           |

|     |     | 1. Required FPGA Characteristics4                             |           |

|     |     | 2. Overall Sequencer and Processor Characteristics4           | 14        |

|     |     | 3. Comparisons of Xilinx and Actel FPGAs4                     |           |

|     | C.  | SELECTION OF DEVELOPMENT BOARDS FOR LOGIC                     |           |

|     | 0.  | DESIGN                                                        | 17        |

|     | D.  | CHAPTER SUMMARY                                               |           |

|     |     |                                                               |           |

| IV. |     | DWARE DEVELOPMENT – PROASIC3 TEST BOARDS AND                  |           |

|     |     | LIMINARY FLIGHT PROTOTYPE4                                    |           |

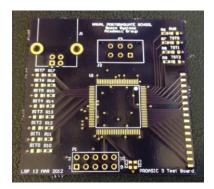

|     | А.  | PROASIC3 TEST BOARD                                           |           |

|     |     | 1. Derived Requirements                                       | 50<br>- 0 |

|     |     | 2. Selection of Board Size and Layer Count                    |           |

|     | _   | 3. Selection of Components                                    | 51        |

|     | В.  | SAD VERSION 3 – FLIGHT PROTOTYPE BOARD5                       |           |

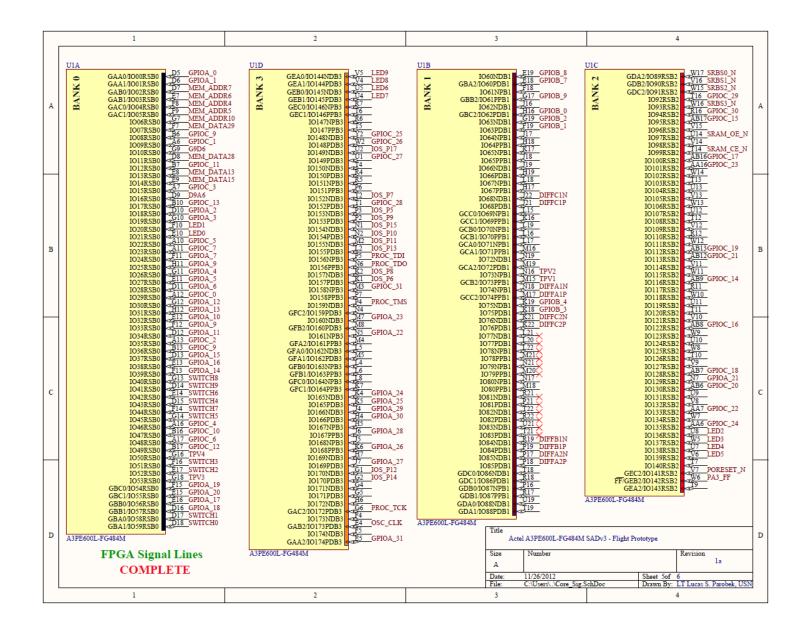

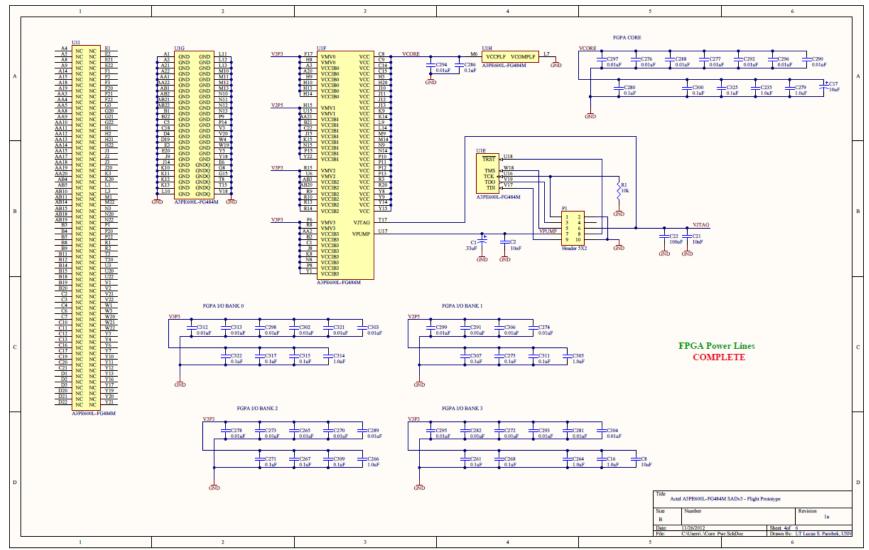

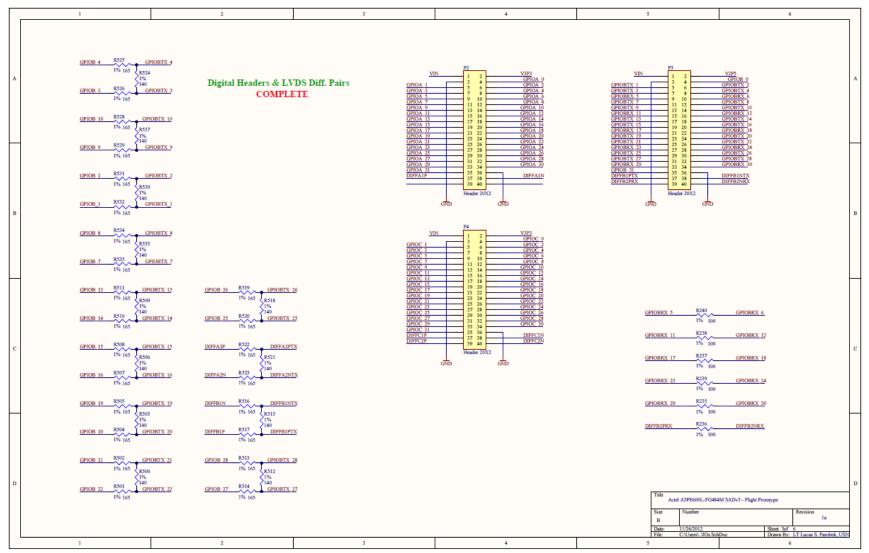

|     |     | 1. Discussion of Specific FPGA5                               |           |

|     |     | 2. Additional Modifications Considered5                       |           |

|     | C.  | CHAPTER SUMMARY5                                              | <b>58</b> |

| V.  | CON | IPARISON OF FAULT-TOLERANCE METHODS FOR USE IN                |           |

|     |     | UENCER LOGIC DEVELOPMENT6                                     |           |

|     | A.  | TMR VERSUS OTHER FAULT TOLERANT APPROACHES                    |           |

|     |     | 1. Maintaining Logic Structures within HDL Languages (Verilog |           |

|     |     | / VHDL and Schematically)                                     | 51        |

|     |     | a. Baseline Design – Seven-Segment LED Counter Example        |           |

|     |     | b. Triplicated Design – Seven-Segment LED Counter             |           |

|     |     | Example                                                       |           |

|     |     | 2. Implementation of Various Redundant Techniques in          | -         |

|     |     | Combinational Logic Designs                                   | 55        |

|     |     | a. Baseline Design – 16×16-bit Array Multiplier               |           |

|     |     | b. Triple Modular Redundancy (TMR)                            |           |

|     |     | c. Quadded Logic                                              |           |

|     |     | d. Triplicated Interwoven Redundancy (TIR)                    |           |

|     |     | e. Stacked Techniques – Quad-TMR & TIR-TMR                    |           |

|     |     | 3. Data Results and Analysis                                  |           |

|     |     | 4. Discussion of Results                                      |           |

|     | B.  | SELECTION OF A FAULT-TOLERANT TECHNIQUE                       |           |

|     | 2.  | 1. Xilinx TMRTool and Mentor Graphics Precision Hi-Rel        |           |

|     |     | 2. A many first of any fight of uping fight in Mission /      | ^         |

|      |             | 2.         | Manual       | Insertion         | of         | TMR      | with     | Schematic                               | and    | HDL        |

|------|-------------|------------|--------------|-------------------|------------|----------|----------|-----------------------------------------|--------|------------|

|      |             |            | Techniqu     | 1es               | •••••      |          | •••••    | •••••                                   |        | 80         |

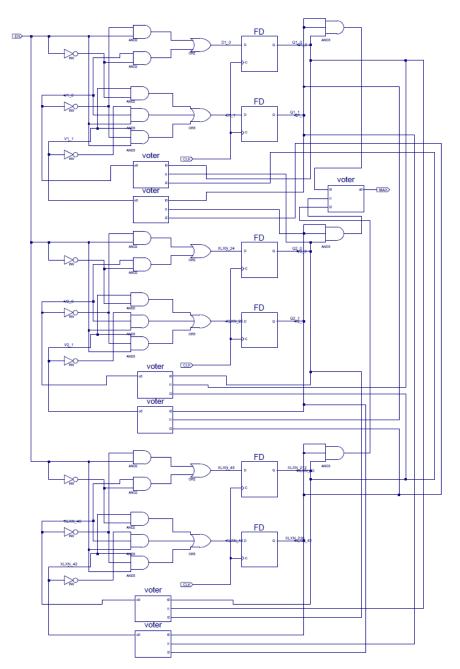

|      | C.          | APPL       | ICATION      | OF TMR            | TO S       | EQUE     | NTIAL    | LOGIC D                                 | ESIGN  | S80        |

|      |             | 1.         | Manual I     | Insertion of      | <b>Fau</b> | lts      | •••••    | ••••••                                  |        | 82         |

|      |             |            | a. Fi        | loating-Inpi      | ut Ca      | se       | •••••    | • • • • • • • • • • • • • • • • • • • • |        | 82         |

|      |             |            | <i>b.</i> 'S | Stuck-at-0' 1     | Logic      | Fault    |          | •••••                                   |        | 83         |

|      |             |            |              |                   |            |          |          | ••••••                                  |        |            |

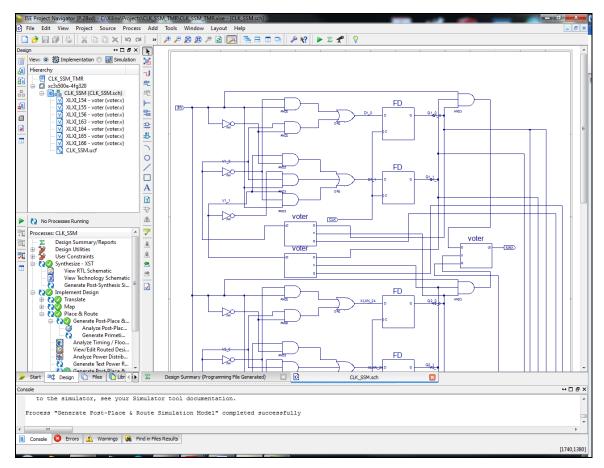

|      |             | 2.         | Modifica     | tion of FSN       | 1 Des      | ign to T | ГMR R    | Representati                            | on     | 85         |

|      |             | 3.         |              |                   |            |          |          | Sequential                              |        |            |

|      | D.          | PREL       |              |                   |            |          |          | IGN                                     |        |            |

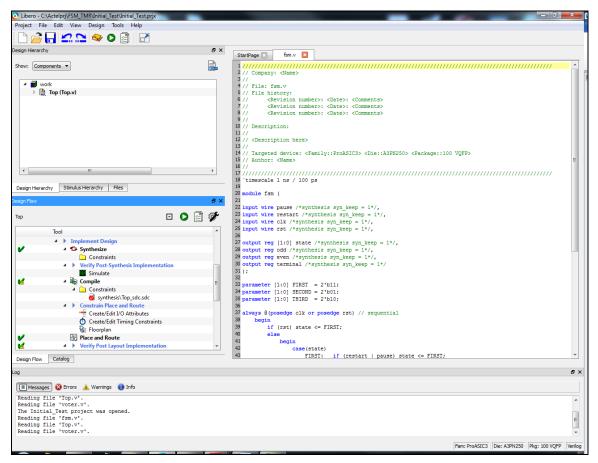

|      |             | 1.         | Conversi     | on of Xiliny      | K HD       | L to Ac  | tel HD   | L                                       |        | 89         |

|      |             | 2.         | Synplify     | <b>Pro Repres</b> | entat      | tions of | FSM I    | Logic                                   |        | 90         |

|      |             | 3.         |              |                   |            |          |          | hin Logic                               |        |            |

|      |             |            |              |                   |            |          |          | HDL                                     |        |            |

|      |             |            |              |                   |            |          |          | C3 FlashR                               |        |            |

|      | Е.          | CHAP       |              |                   |            |          |          | ••••••                                  |        |            |

| VI.  | CON         | CLUSIC     | DNS A        | ND RE(            | TOM        | MEND     | ΔΤΙΟΝ    | NS FOR                                  | FI I'  | TURE       |

| V 1. |             |            |              |                   |            |          |          |                                         |        |            |

|      | A.          |            |              |                   |            |          |          | ••••••                                  |        |            |

|      | А.<br>В.    |            |              |                   |            |          |          | ••••••                                  |        |            |

|      |             |            |              |                   |            |          |          |                                         |        |            |

| APPE | NDIX .      |            |              |                   |            |          |          | S AND                                   |        |            |

|      |             | ELOPM      | ENT TOO      | OL DIFFEI         | REN        | CES      | •••••    | •••••                                   | •••••  | 103        |

|      | A.1         |            |              |                   |            |          |          | RODUCTS                                 |        |            |

|      |             | 1.         |              |                   |            |          |          | ••••••                                  |        |            |

|      |             |            |              |                   |            |          |          | •••••                                   |        |            |

|      |             |            |              |                   |            |          |          | •••••                                   |        |            |

|      |             |            |              |                   |            |          |          | •••••                                   |        |            |

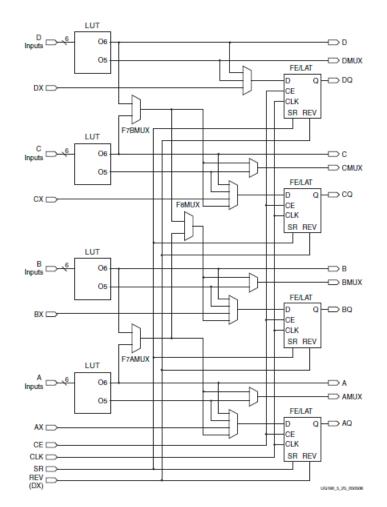

|      |             | 2.         | Hardwar      | re Feature S      | Set        | •••••    | •••••    | •••••                                   | •••••  | 109        |

|      |             |            |              |                   |            |          |          | ••••••                                  |        |            |

|      |             |            |              |                   |            |          |          | ••••••                                  |        |            |

|      |             | 3.         |              |                   | e Re       | quirem   | ents     | •••••                                   | •••••  | 115        |

|      | A.2         | APPE       | NDIX SU      | MMARY             | •••••      |          | •••••    | •••••                                   | •••••• | 115        |

| APPF | <b>NDIX</b> | B.         | PROASI       | C3 TEST 1         | BOA        | RD – R   | REFER    | ENCE, SC                                | нема   | TICS.      |

|      |             |            |              |                   |            |          |          |                                         |        | ,          |

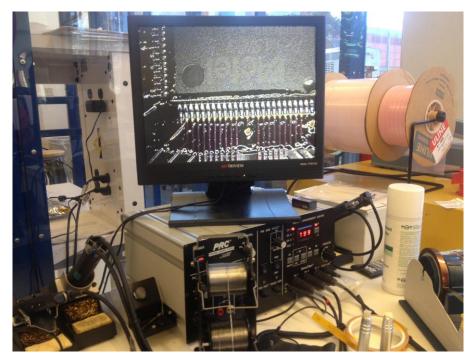

|      | B.1         | -          |              |                   |            |          |          | METHOD                                  |        |            |

|      | 2.1         | 1.         |              |                   |            |          |          | Board Desig                             |        |            |

|      |             | 2.         |              |                   |            |          |          |                                         |        |            |

|      |             | 2.<br>3.   |              |                   |            |          |          | nent Placen                             |        |            |

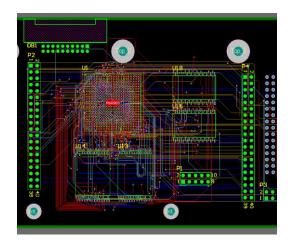

|      |             | <b>4</b> . |              |                   |            |          |          |                                         |        |            |

|      | <b>B.2</b>  |            |              |                   |            |          |          | ••••••                                  |        |            |

|      | B.2<br>B.3  |            | HANICAL      |                   |            |          |          | ND EI                                   |        |            |

|      | <b>D</b> .3 |            |              |                   |            |          |          |                                         |        |            |

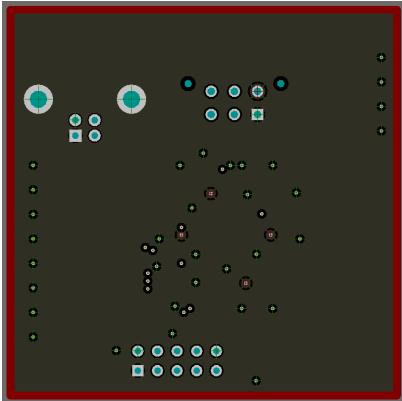

|      | <b>B.4</b>  | 2.D P      | CR LAVE      | R DIAGRA          | MS         | •••••    | •••••    | ••••••                                  | •••••  | 120<br>131 |

|      | B.5         |            |              |                   |            |          |          | ••••••                                  |        |            |

|      | <b>D</b> .0 | 2-D I V    |              |                   |            |          | <b>_</b> | ••••••                                  | •••••• |            |

| <b>B.6</b>   | APPENDIX SUMMARY                                    | 135     |

|--------------|-----------------------------------------------------|---------|

| APPENDIX     | C. SAD VERSION 3 – FLIGHT PROTOTYPE B               | OARD –  |

| REFE         | RENCE, SCHEMATICS, AND PCB LAYOUT DIAGRAMS          |         |

| <b>C.1</b>   | SAD VERSION 3 – FLIGHT PROTOTYPE                    |         |

|              | DEVELOPMENT METHODOLOGY                             |         |

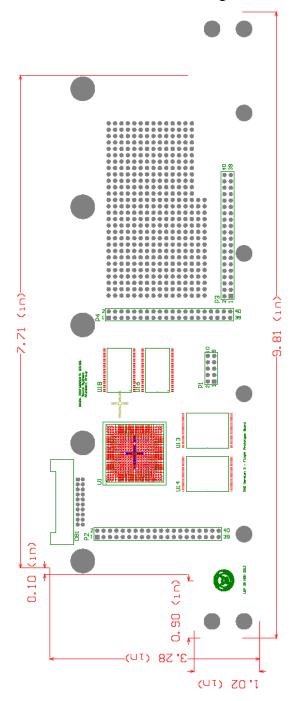

|              | 1. Selection of Board Size and Layer Count          |         |

|              | 2. Selection of Components                          |         |

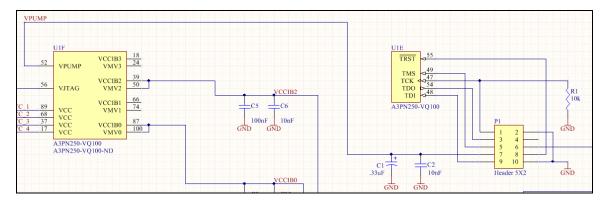

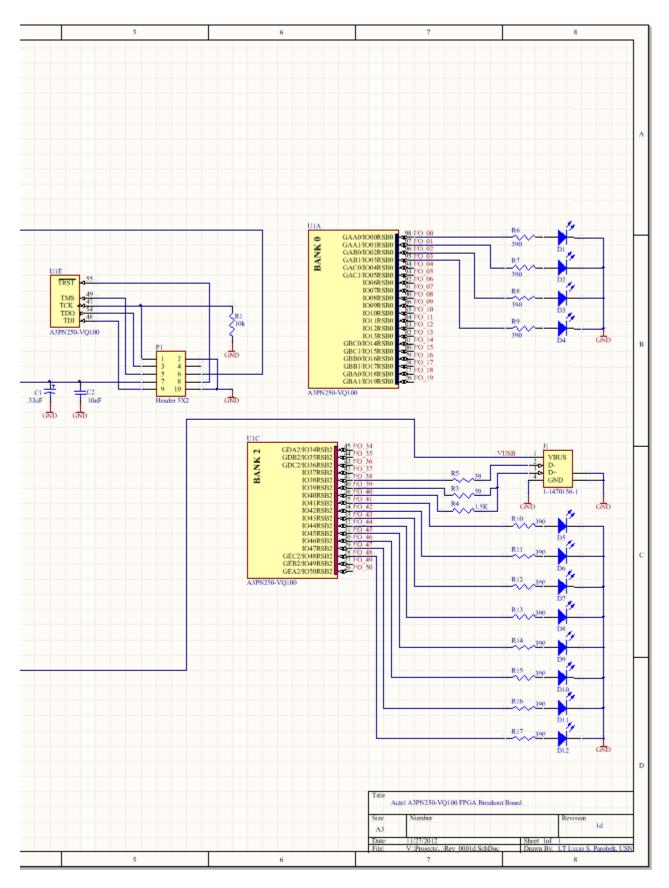

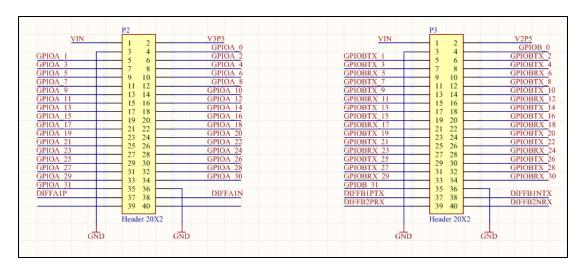

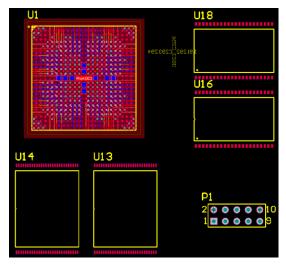

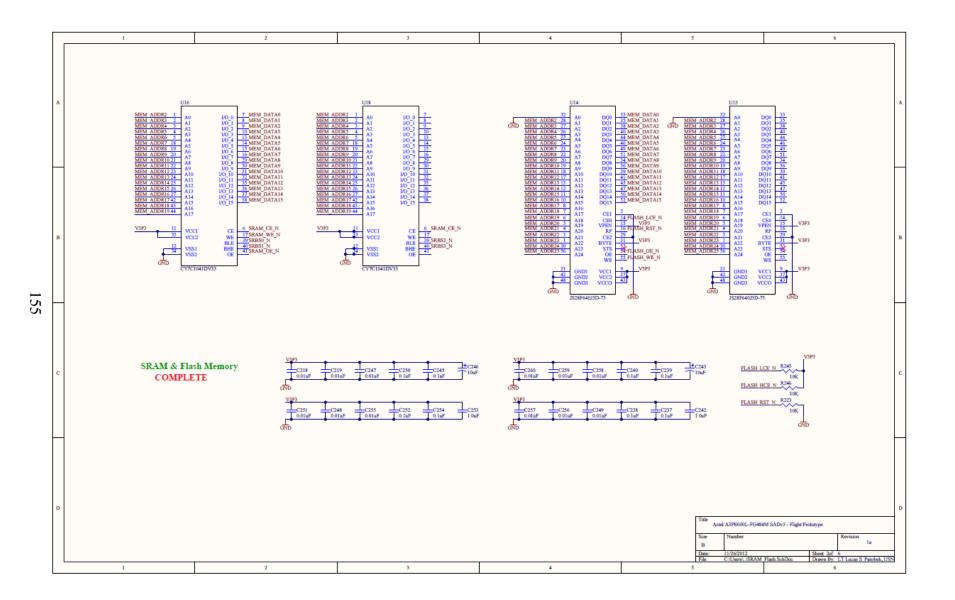

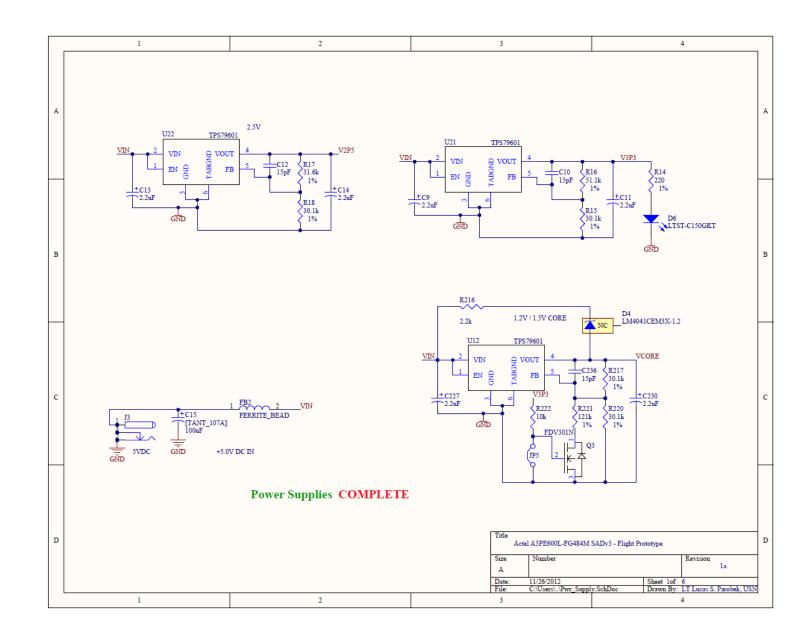

|              | 3. Discussion of Schematic                          | 144     |

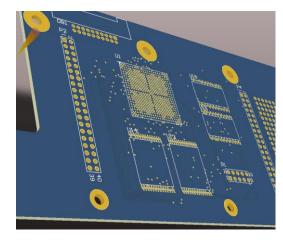

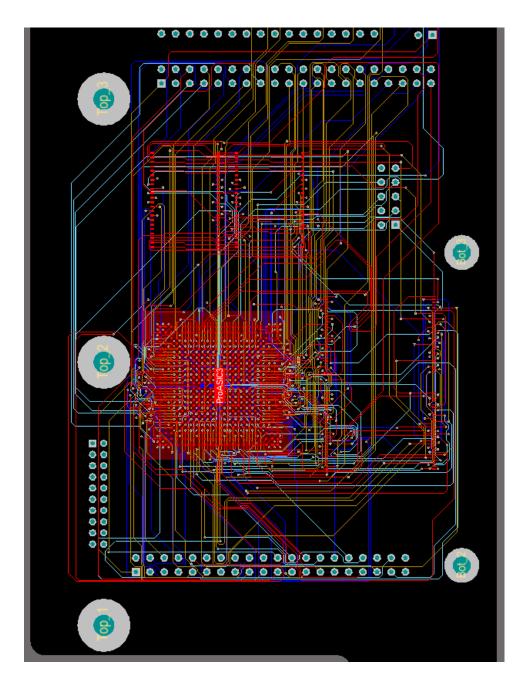

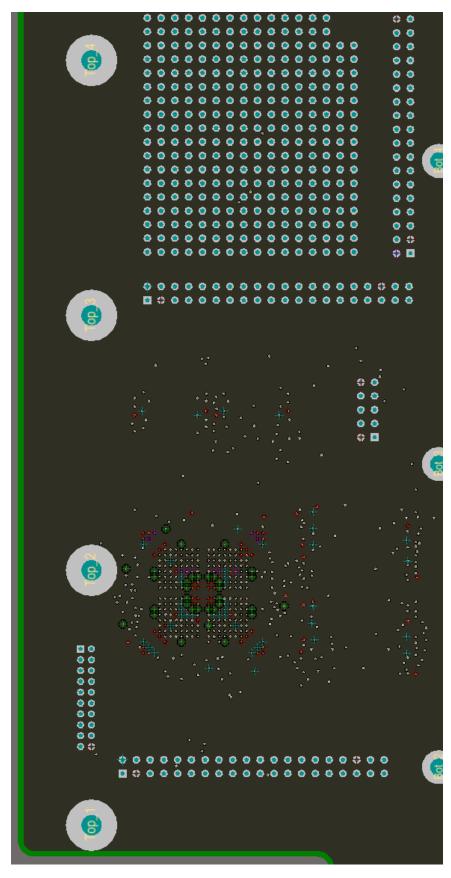

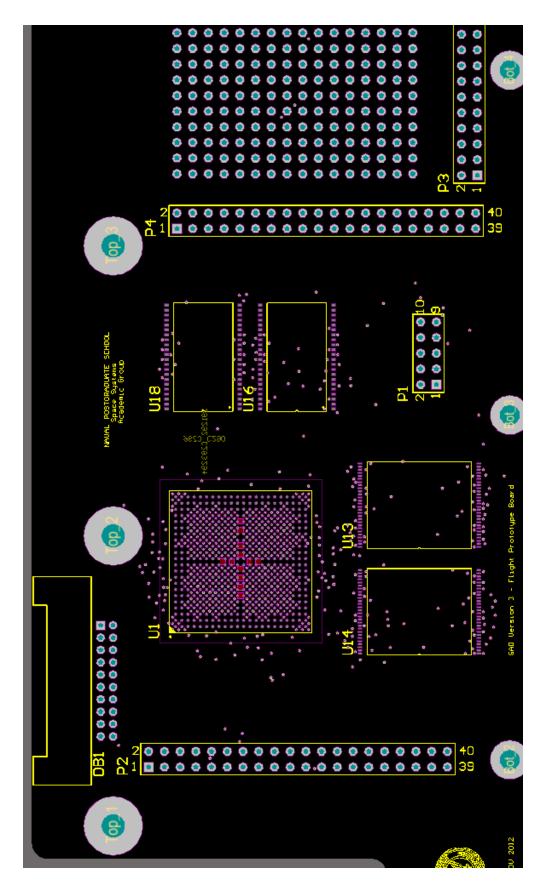

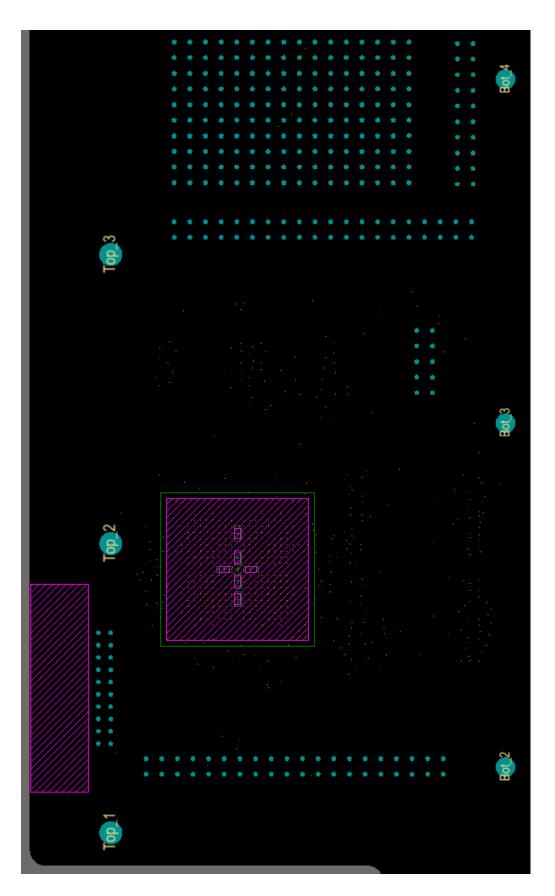

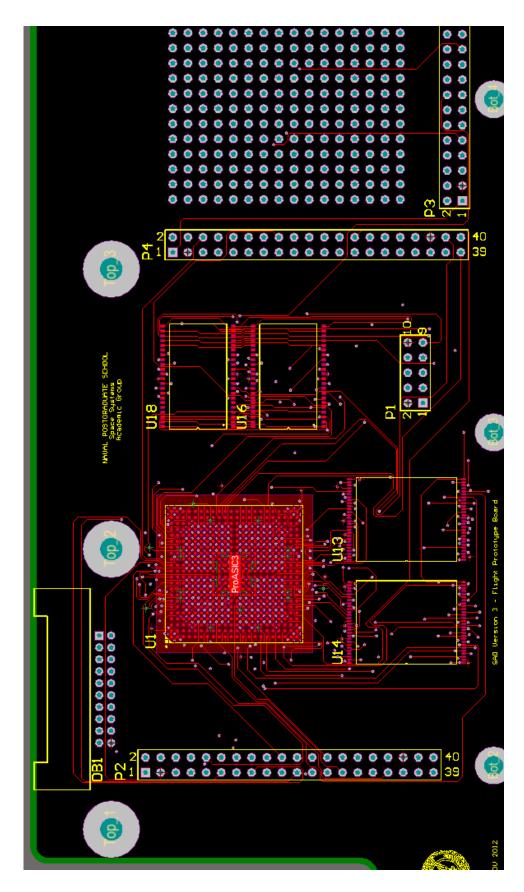

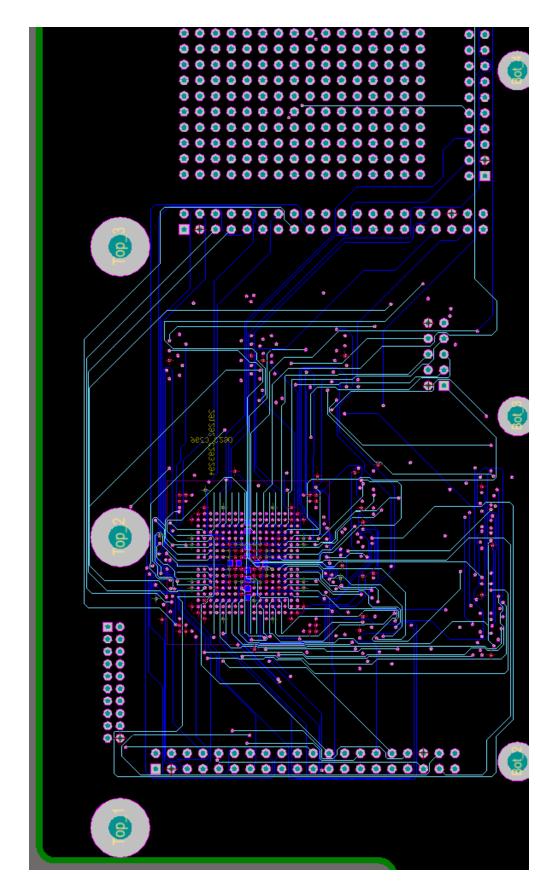

|              | 4. Discussion of PCB Layout and Component Placement |         |

| C.2          | BILL OF MATERIALS<br>MECHANICAL DIMENSIONS AND ELEC | 149     |

| C.3          | MECHANICAL DIMENSIONS AND ELEC                      | CTRICAL |

|              | SCHEMATICS                                          | 151     |

| <b>C.4</b>   | 2-D PCB LAYER DIAGRAMS                              |         |

| C.5          | 3-D PCB COMPONENT PLACEMENT                         |         |

| <b>C.6</b>   | APPENDIX SUMMARY                                    |         |

| APPENDIX     | D. SEQUENCER HDL PRESENTATION                       | 165     |

| D.1.1        | SEVEN-SEGMENT LED COUNTER (BASYS2USERDEM)           |         |

| D.1.2        |                                                     | OUNTÉR  |

|              | (SIMPLESSEGLEDDEMO.VHD)                             |         |

| D.1.3        | SEVEN-SEGMENT LED COUNTER (VOTER.V)                 |         |

| <b>D.1.4</b> | SEVEN-SEGMENT LED COUNTER (TMR SCHEMATIC)           |         |

| <b>D.2</b>   | LAUNCH SEQUENCE GEN                                 | ERATOR  |

|              | (LAUNCH_SEQUENCER.VHD)                              | 171     |

| LIST OF RE   | FERENCES                                            |         |

| INITIAL DIS  | STRIBUTION LIST                                     |         |

### LIST OF FIGURES

| Figure 1.  | Final payload configuration and integration of NPSCuL with eight P-PODs                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.  | NPSCuL with associated Splitter Auxiliary Device (SAD) and external wiring visible                                                                                                          |

| Figure 3.  | Internal wiring harness structure for SAD depicting power and data line split to eight output ports                                                                                         |

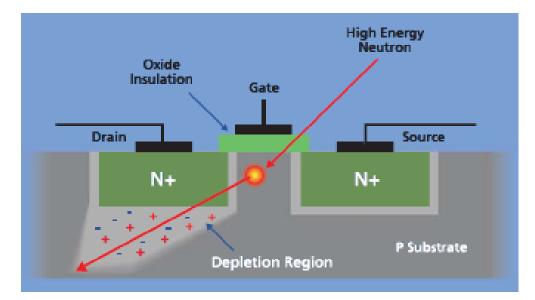

| Figure 4.  | Neutron radiation strike of silicon atom resulting in ejection of heavy ions leading to firm error in transistor (From [21])                                                                |

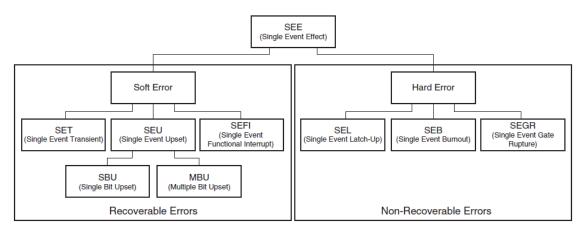

| Figure 5.  | Single-event effects classification diagram illustrating difference between recoverable and non-recoverable errors (From [25])17                                                            |

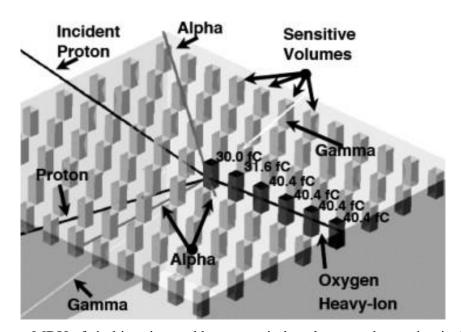

| Figure 6.  | MBU of six bits triggered by proton induced oxygen heavy-ion in 130-nm<br>CMOS memory cells (From [27])                                                                                     |

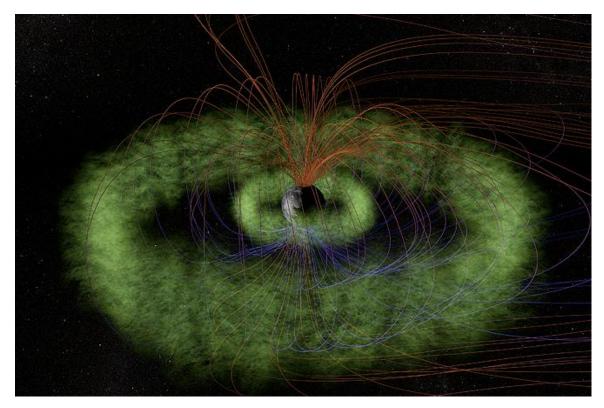

| Figure 7.  | Inner and outer torus-shaped layers of plasma of the Van Allen radiation<br>belts. Energetic electrons form the outer belt; the inner belt consists of<br>protons and electrons (From [39]) |

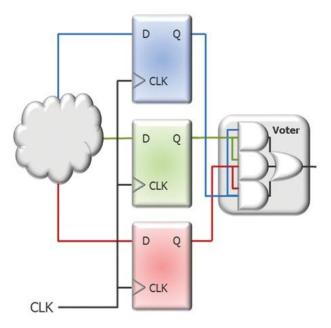

| Figure 8.  | Local TMR with all sequential elements tripled and followed by a majority voter (From [44])                                                                                                 |

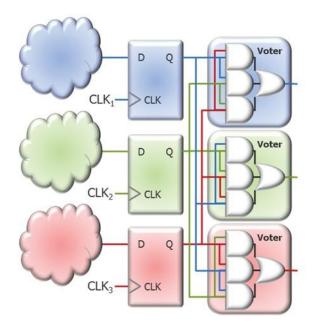

| Figure 9.  | Global TMR with all sequential elements, combinatorial logic, majority voters, clocking signals and global buffers triplicated (From [44])26                                                |

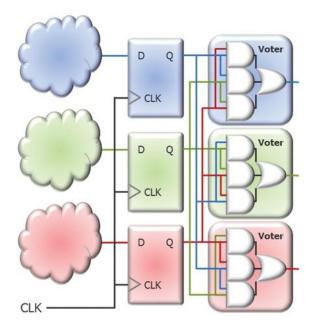

| Figure 10. | Distributed TMR with all sequential elements, combinatorial elements and majority voters triplicated. Clock signal is shared among resources (From [44])                                    |

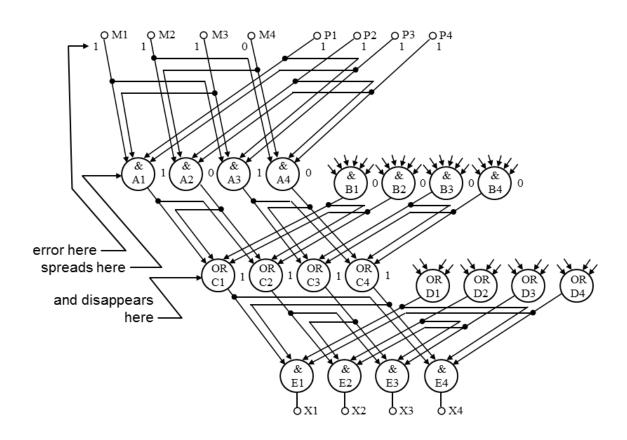

| Figure 11. | Quadded logic illustrating error propagation and masking (From [46])28                                                                                                                      |

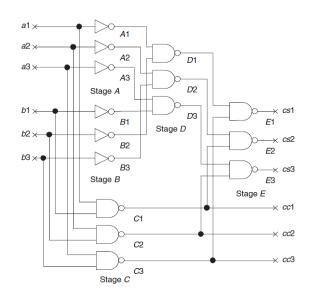

| Figure 12. | Design of TIR half-adder implementation illustrating interwoven connections (From [47])                                                                                                     |

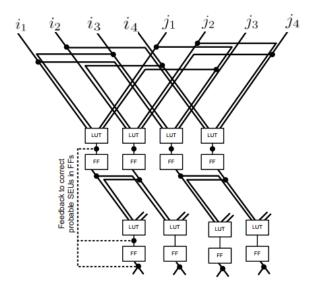

| Figure 13. | QFDR substituting LUTs and FFs constructs for logic gates (From [48])30                                                                                                                     |

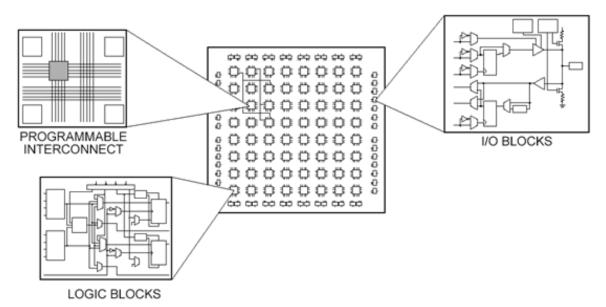

| Figure 14. | Typical FPGA internal architecture consisting of configurable logic blocks, I/O blocks and programmable interconnects (From [54])                                                           |

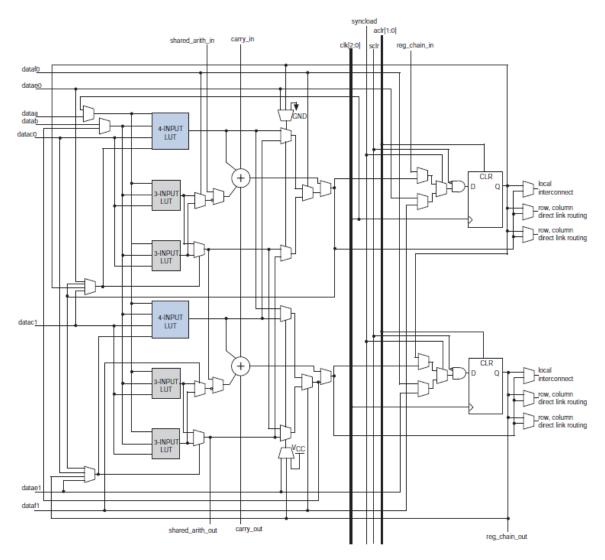

| Figure 15. | Typical FPGA logic cells with associated LUTs, gates, adders, memory devices, and interconnect buffers visible (From [55])                                                                  |

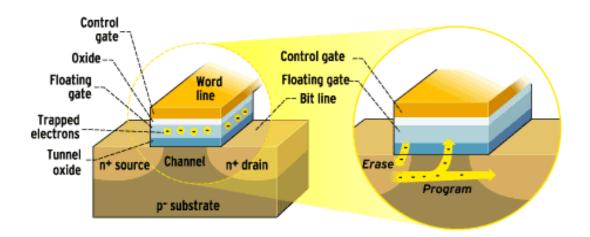

| Figure 16. | Internal flash transistor configuration with charge build-up in floating gate allowing for reconfiguration and nonvolatile storage (From [71])41                                            |

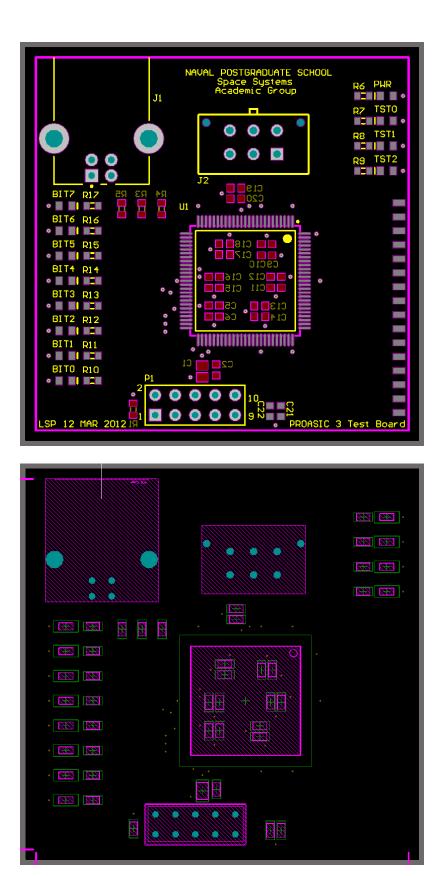

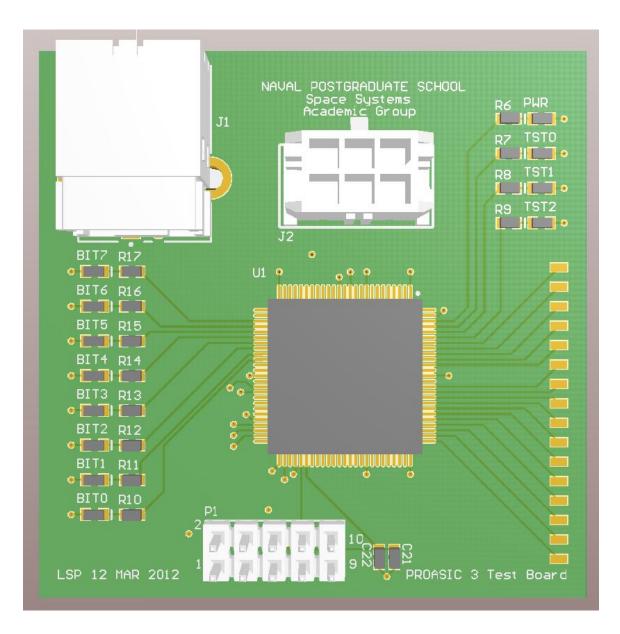

| Figure 17. | Altium Designer interface with separate schematic, 2-D PCB layout, and 3-D component placement views visible on separate monitors (From [73])49                                             |

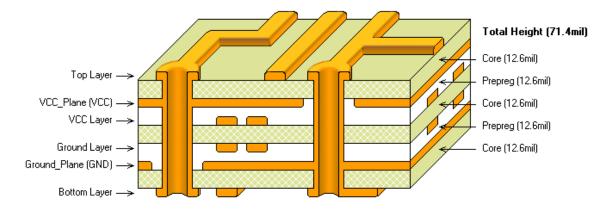

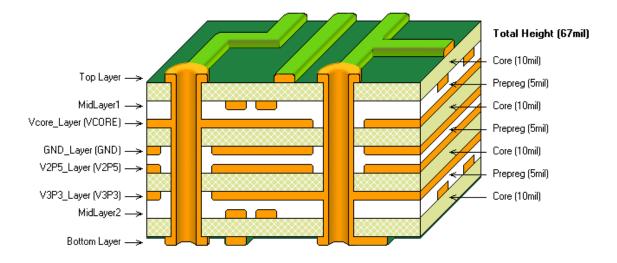

| Figure 18. | Four-layer stack of the ProASIC3 Test Board with internal power planes<br>and external signal layers                                                                                        |

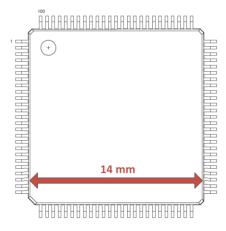

| Figure 19. | ProASIC3 nano VQ100 package of VQFP-type (From [74])                                                                                                                                        |

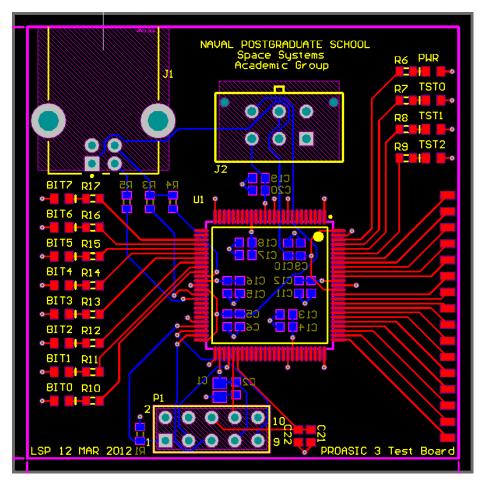

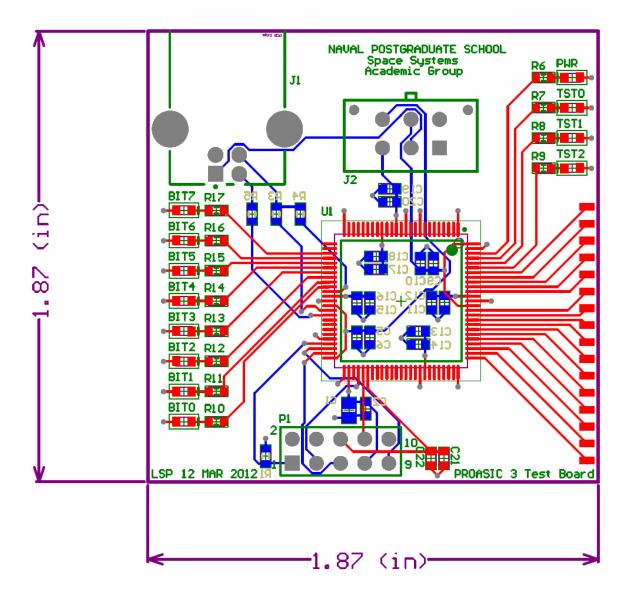

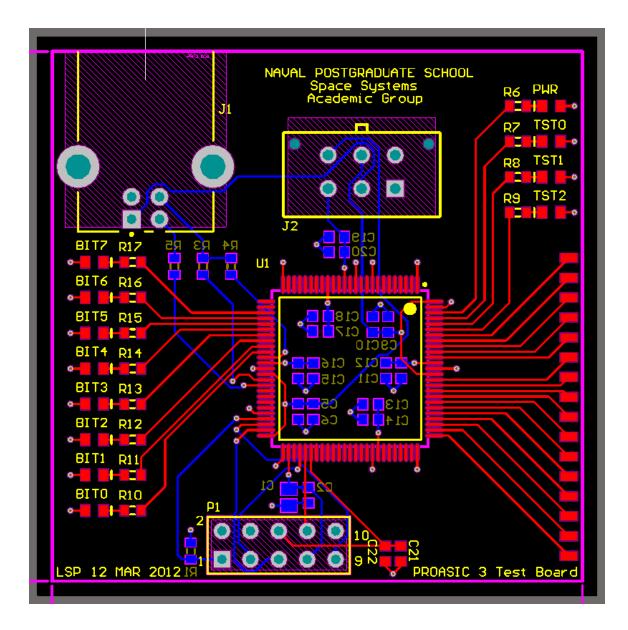

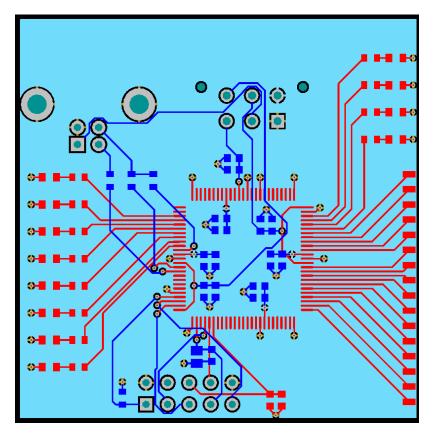

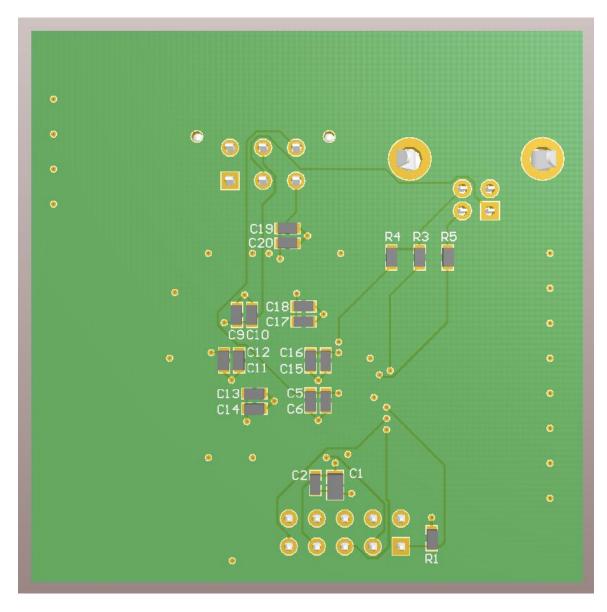

| Figure 20. | ProASIC3 Test Board 2-D PCB layout with all component footprints, signal lines, and vias visible                                                                                            |

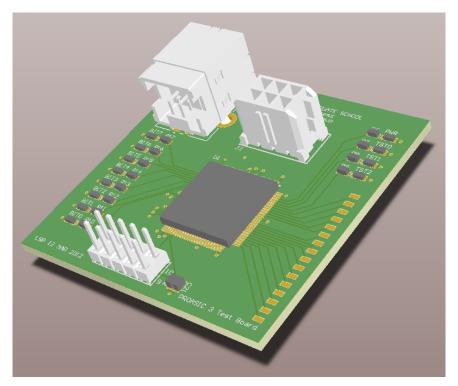

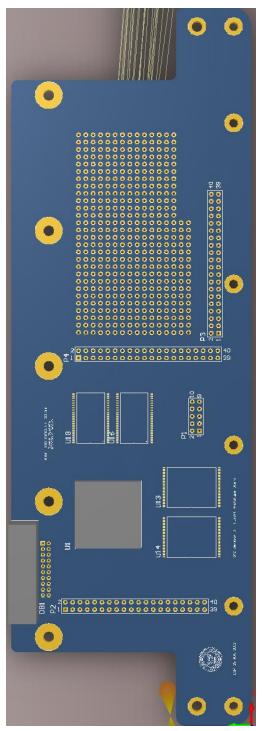

| Figure 21. | ProASIC3 Test Board 3-D isometric view with component models indicating approximate sizing and spacing of integrated board                                                                  |

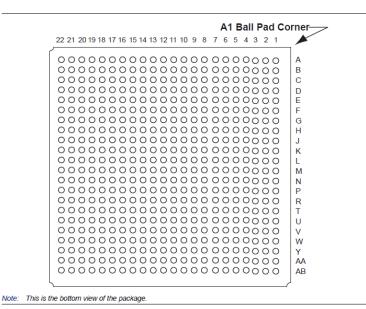

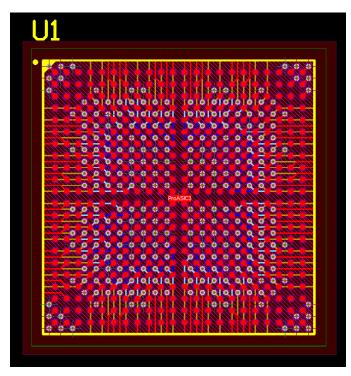

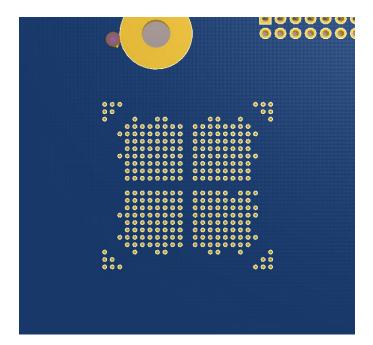

| Figure 22.    | FG484 BGA package of the Actel ProASIC3L A3PE600L FPGA (From [75])           |

|---------------|------------------------------------------------------------------------------|

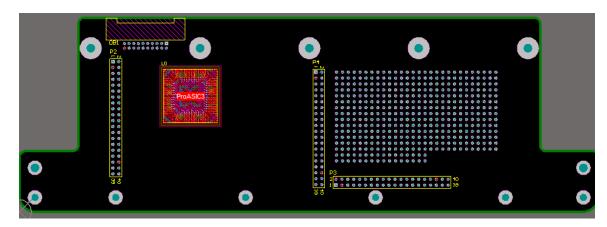

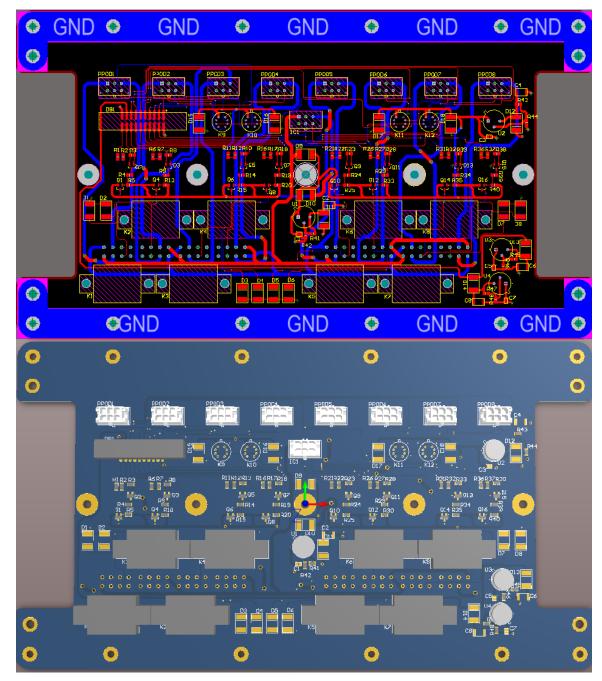

| Figure 23.    | Initial 2-D PCB layout of FPGA, three 40-pin I/O headers, prototyping        |

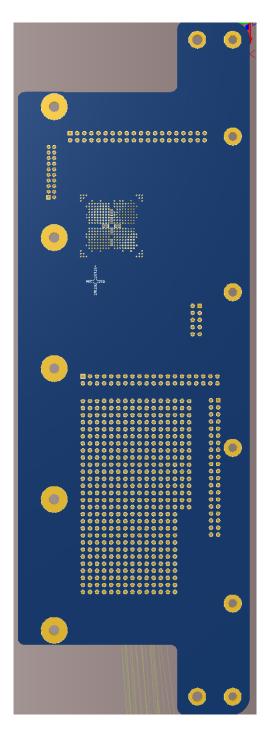

| - 18010 -01   | area, and ribbon-cable connector for relay board attachment                  |

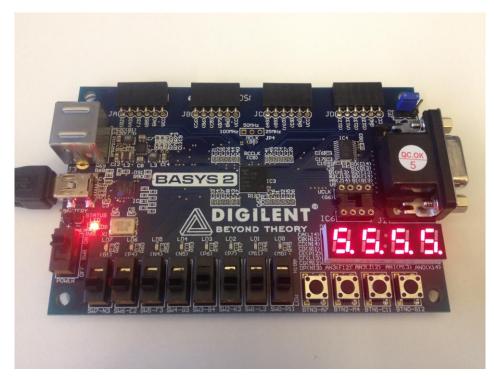

| Figure 24.    | Digilent BASYS2 development board counting with proper state logic62         |

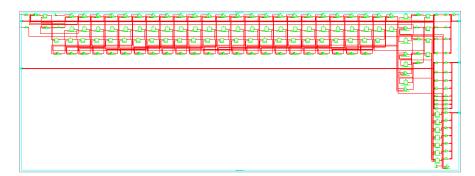

| Figure 25.    | Default gate layout for baseline seven-segment LED counter                   |

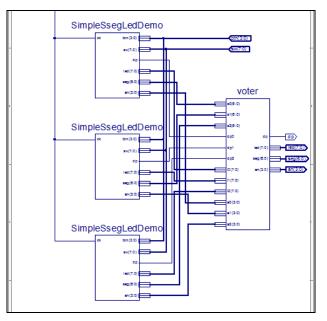

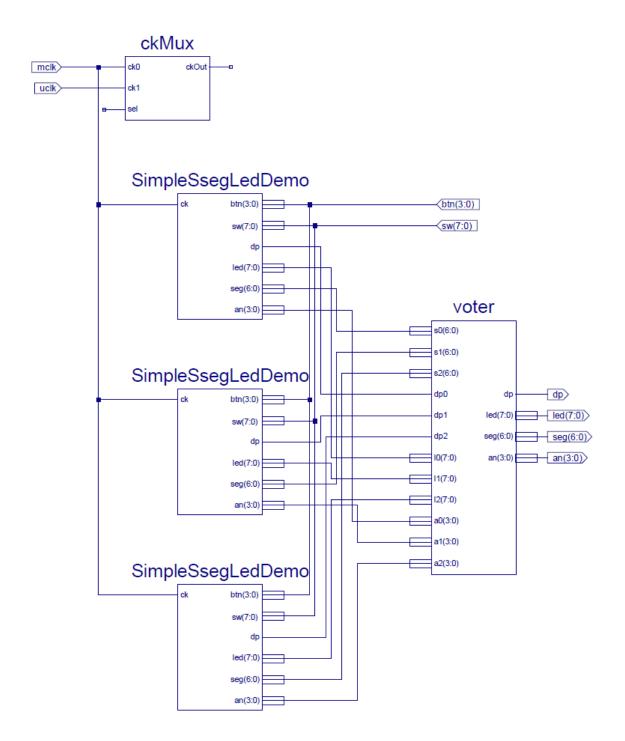

| Figure 26.    | Triplicated seven-segment LED counter example with voting logic              |

| Figure 27.    | Triplicated gate layout with voting logic - seven-segment LED counter64      |

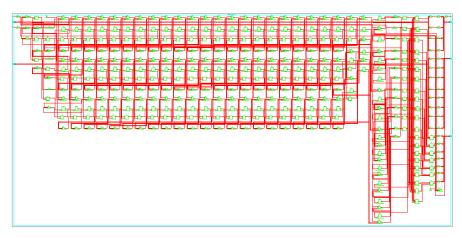

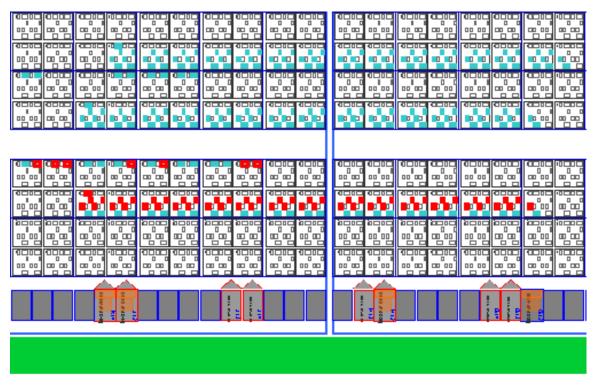

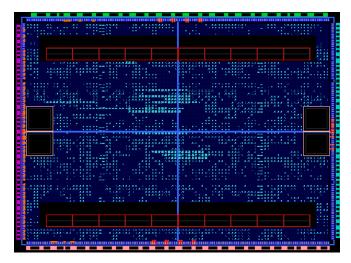

| Figure 28.    | FPGA layout view illustrating placement of three counter structures          |

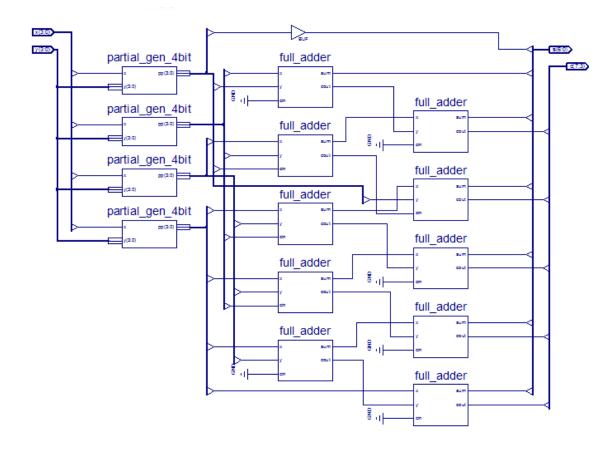

| Figure 29.    | 4×4-bit array multiplier internal structure using partial product generators |

| U             | and full adders                                                              |

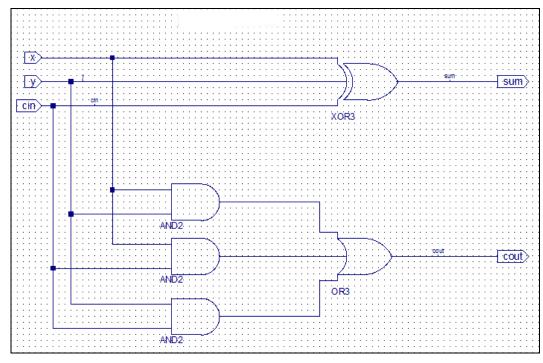

| Figure 30.    | Full adder gate structure for the 16×16-bit array multiplier, baseline       |

| C             | design                                                                       |

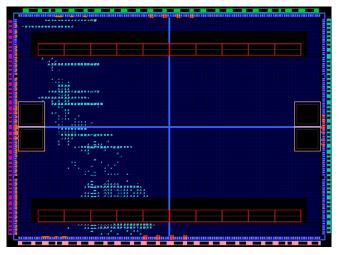

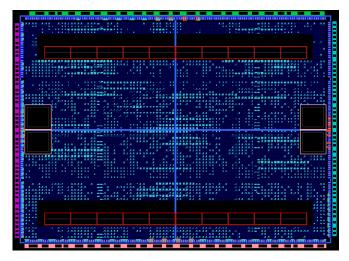

| Figure 31.    | FPGA physical layout of default 16×16-bit array multiplier logic67           |

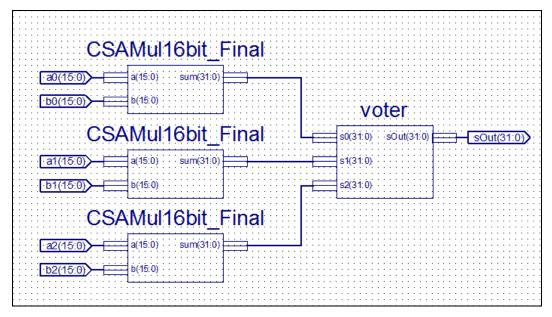

| Figure 32.    | 16×16-bit array multiplier implemented in TMR with voting logic              |

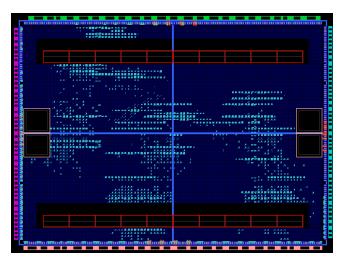

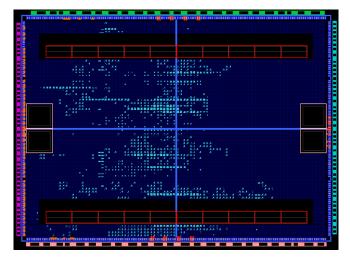

| Figure 33.    | FPGA physical layout of 16×16-bit array multiplier using TMR logic69         |

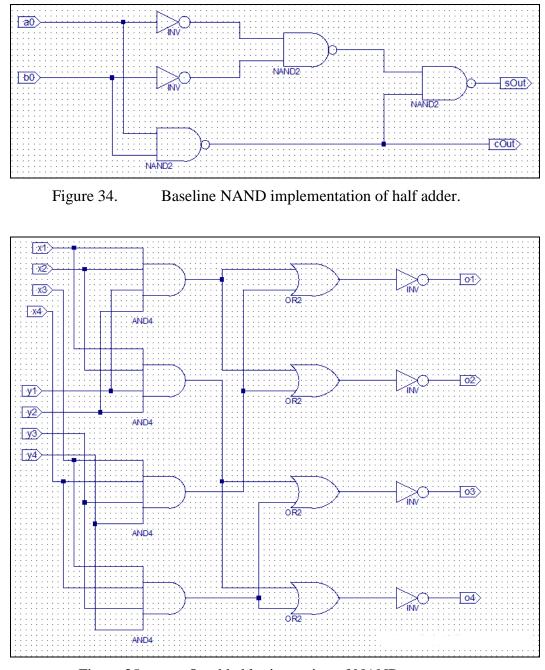

| Figure 34.    | Baseline NAND implementation of half adder                                   |

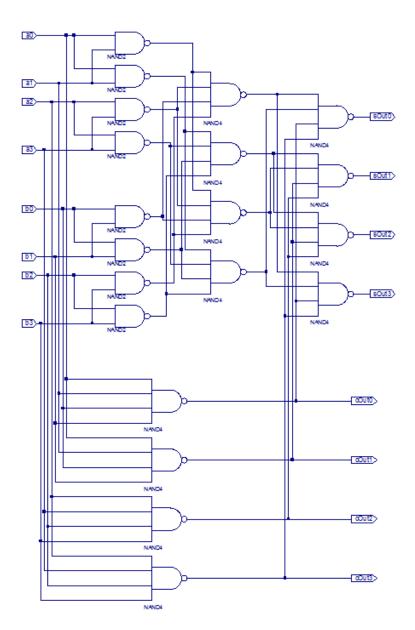

| Figure 35.    | Quadded logic version of NAND gate70                                         |

| Figure 36.    | Quadded logic version of half adder71                                        |

| Figure 37.    | FPGA physical layout of 16×16-bit array multiplier using quadded logic72     |

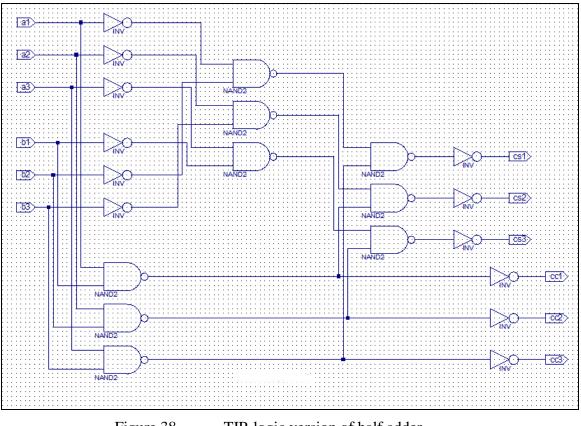

| Figure 38.    | TIR logic version of half adder73                                            |

| Figure 39.    | FPGA physical layout of 16×16-bit array multiplier using TIR logic73         |

| Figure 40.    | FPGA physical layout of 16×16-bit array multiplier using stacked TIR-        |

|               | TMR logic74                                                                  |

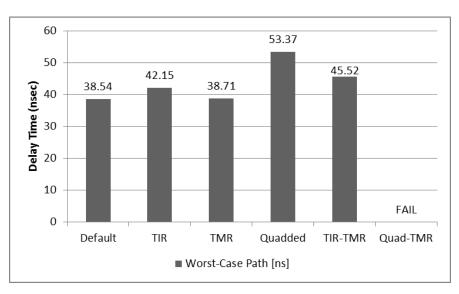

| Figure 41.    | Timing analysis for worst-case paths in various fault-tolerant               |

|               | implementations76                                                            |

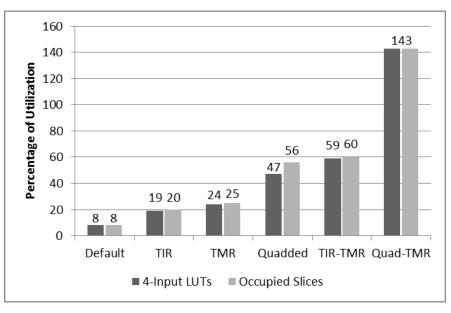

| Figure 42.    | FPGA LUT and slice resource utilization in fault-tolerant                    |

|               | implementations76                                                            |

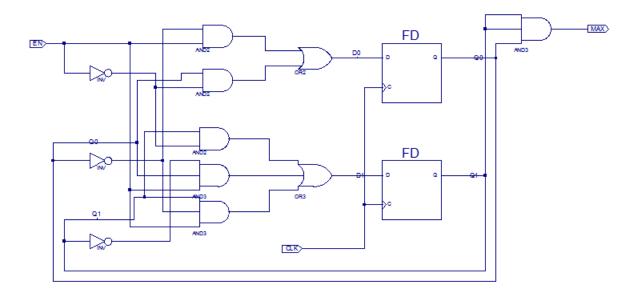

| Figure 43.    | Moore design, clocked synchronous state machine utilizing positive-edge      |

|               | triggered D flip-flops (After [76])81                                        |

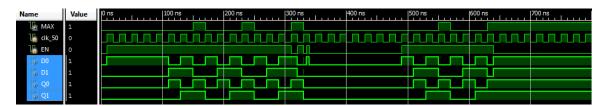

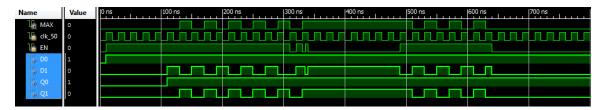

| Figure 44.    | Timing diagram for the Moore-type FSM developed with output, clock,          |

|               | enable and D-FF input/output signals visible (fault-free case)               |

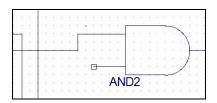

| Figure 45.    | Floating-input case of AND gate second input disconnected, simulating        |

|               | break in circuit or disruption in input                                      |

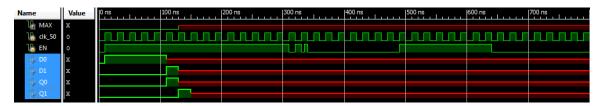

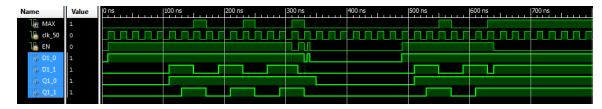

| Figure 46.    | Timing diagram for the Moore-type FSM developed with output, clock,          |

|               | enable and D-FF input/output signals visible (floating-input case)           |

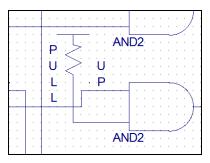

| Figure 47.    | Second input of AND gate tied to logic '0', simulating constant logic zero   |

| <b>F</b> ' 40 | or short in circuit to ground plane                                          |

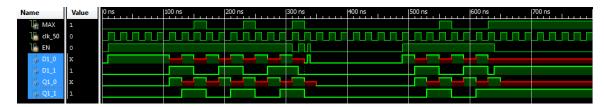

| Figure 48.    | Timing diagram for the Moore-type FSM developed with output, clock,          |

| <b>T</b> ' (0 | enable and D-FF input/output signals visible (constant logic '0' case)       |

| Figure 49.    | Second input of AND gate tied to logic '1', simulating constant logic one    |

| <b>F' 7</b> 0 | or short in circuit to positive voltage plane                                |

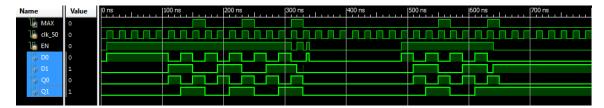

| Figure 50.    | Timing diagram for the Moore-type FSM developed with output, clock,          |

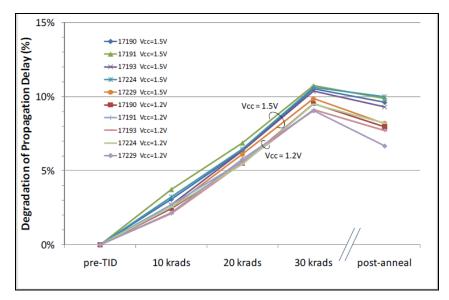

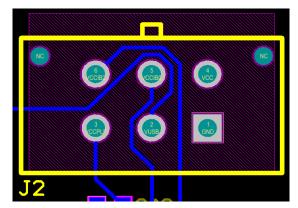

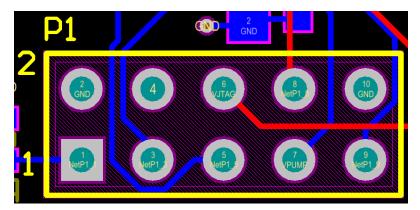

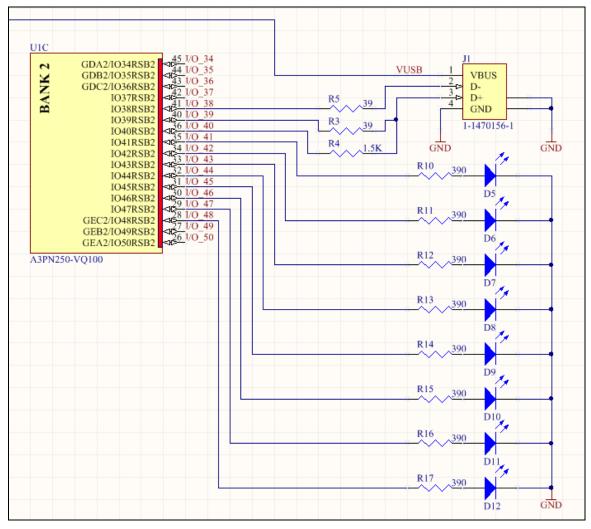

| Element 51    | enable and D-FF input/output signals visible (constant logic '1' case)       |