#### SOFTWARE AND CRITICAL TECHNOLOGY PROTECTION AGAINST SIDE-CHANNEL ANALYSIS THROUGH DYNAMIC HARDWARE OBFUSCATION

THESIS

John Bochert, 1st Lt, USAF AFIT/GCE/ENG/11-01

# DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# SOFTWARE AND CRITICAL TECHNOLOGY PROTECTION AGAINST SIDE-CHANNEL ANALYSIS THROUGH DYNAMIC HARDWARE ${\bf OBFUSCATION}$

#### THESIS

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering

John Bochert, BSEE 1st Lt, USAF

March 2011

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# SOFTWARE AND CRITICAL TECHNOLOGY PROTECTION AGAINST SIDE-CHANNEL ANALYSIS THROUGH DYNAMIC HARDWARE OBFUSCATION

John Bochert, BSEE 1st Lt, USAF

| Approved:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ( when the state of the state o | 14 MAR 201           |

| Dr. Yong Kim, PhD (Chairman)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Date                 |

| Maj. Todd R. Andel, PhD (Member)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14 MAR 11  Date      |

| Mul R. Lund<br>Dr. Michael Grimaila, PhD, CISM, CISSP (Member)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 m 42 2011<br>Date |

| OMby VItage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 Mar 2011          |

| Lt. Col. Jeffrey W. Humphries, PhD (Member)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date                 |

#### Abstract

Side Channel Analysis (SCA) is a method by which an adversary can gather information about cryptographic keys by examining the operations on a microprocessor measuring electromagnetic (EM) emissions or any environment changes the processor creates during the execution of a cryptographic algorithm.

The purpose of this thesis is to devise methods to increase the difficulty of conducting SCA successfully. This thesis makes use of the open-source soft-core Java Optimized Processor (JOP) on a Xilinx Virtex 5 ML506 evaluation board which is used for evaluating the effectiveness of SCA countermeasures in attacks against cryptographic algorithms. Analysis of SCA in attacks against RSA cryptography implemented on the JOP revealed that secret key information was leaked through the ALU and multiplier. In examining the processor in attacks against AES cryptography, the JOP was found to leak secret key information through memory accesses. To increase security this thesis proposes the use of several "double hardware" sets that are dynamically used in such a way to obfuscate the EM emissions to increase security against SCA attacks. In the case of RSA where the ALU and multiplier leaks SCA information, the proposed methods removed a correlation of the JOP emissions by using two separate adders and two separate multipliers. In each case, the adders and multipliers that were alternated were chosen due to their specific difference in power signature used while computing the sum or product, thus effectively obfuscating the bit-group exponentiation functions in Java. In the case of memory correlation and attacks against AES, the proposed methods normalized the power usage of stored values, so that all values being stored look the same. This method increased security by requiring up to 87% more data to successfully attack AES.

#### Acknowledgements

First and foremost, I owe my biggest debt of gratitude to God, for without His constant provision, I would be lost. I would also like to thank Dr. Kim, my advisor, who was always available for discussions of problems and solutions. He was able and willing to impart both knowledge and wisdom to help me accomplish my goals. I would also like to thank the members of my thesis committee (Dr. Grimaila, Lt Col Humphries, and Major Andel) who helped me see problems from different angles in order to solve them different ways. I would also like to thank all of the members of the VLSI group (Cpt Trejo, Cpt Getz, Lt Falkinburg and Lt Stanton) who were there to help me when they could, and there to laugh with (at) me when I made silly mistakes. Lastly, I would like to thank my family. Although far away, they were there for me when I needed someone to talk to.

John Bochert

## Table of Contents

| P                                                                                                                                                                      | age                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Abstract                                                                                                                                                               | . iv                                              |

| Acknowledgements                                                                                                                                                       | v                                                 |

| List of Figures                                                                                                                                                        | . ix                                              |

| List of Tables                                                                                                                                                         | xiv                                               |

| List of Abbreviations                                                                                                                                                  | . xv                                              |

| Introduction                                                                                                                                                           | 1                                                 |

| 1.1 History 1.2 Motivation 1.2.1 Attack Types 1.3 Problem Statement 1.4 Goals and Objectives 1.5 Proposed Protection Methods 1.6 Research Methodology 1.7 Organization | $ \begin{array}{c}3 \\4 \\4 \\5 \\6 \end{array} $ |

| I. Related Work                                                                                                                                                        | 7                                                 |

| 2.1 Differential and Correlation Power Analysis                                                                                                                        | 7                                                 |

| 2.2 Algorithmic Countermeasures                                                                                                                                        | . 11<br>. 12                                      |

| 2.3 Circuit Level Countermeasures                                                                                                                                      | . 13<br>. 13                                      |

| 2.4 Cryptographic Algorithms                                                                                                                                           | . 18<br>. 19                                      |

| 2.5 Java Optimized Processor                                                                                                                                           |                                                   |

| III. | Met | ethodology                                           | 29               |

|------|-----|------------------------------------------------------|------------------|

|      | 3 1 | Proposed Countermeasures against RSA                 | 20               |

|      | 0.1 | 3.1.1 Dual "Asynchronous" In-Line Multiplexed        |                  |

|      |     | Out/inputs Multiplier (DAILMOM)                      | 30               |

|      |     | 3.1.2 Overloading the original JOP multiplier and    |                  |

|      |     | adder                                                | 33               |

|      |     | 3.1.3 RSA Code                                       |                  |

|      | 3.2 |                                                      |                  |

|      |     | 3.2.1 Implementation of Double Stack                 |                  |

|      |     | 3.2.2 Implementation of Double RAM                   |                  |

|      |     | 3.2.3 AES Code                                       |                  |

|      | 3.3 | 3 Testing Overview                                   | 40               |

|      |     | 3.3.1 Goals and Hypothesis                           | 40               |

|      |     | 3.3.2 Approach                                       | 41               |

|      |     | 3.3.3 System Boundaries                              | 41               |

|      |     | 3.3.4 System Services                                | 42               |

|      |     | 3.3.5 Workload                                       | 42               |

|      |     | 3.3.6 Performance Metrics                            | 42               |

|      |     | 3.3.7 System Parameters                              | 42               |

|      |     | 3.3.8 Factors                                        | 43               |

|      |     | 3.3.9 Evaluation Technique                           | 44               |

|      |     | 3.3.10 Experimental Design                           | 44               |

|      | 3.4 | Testing Setup                                        | $\dots \dots 45$ |

| IV.  | Exp | perimental Results                                   | 50               |

|      | 4.1 | Initial Data Collection                              | 50               |

|      | 7.1 | 4.1.1 Initial Attacks                                |                  |

|      |     | 4.1.2 Evaluation of More Dense Mapping Techniques    |                  |

|      |     | 4.1.3 Code Considerations                            |                  |

|      | 4.2 | 2 AES Tests                                          |                  |

|      | 1.2 | 4.2.1 JOP Clean                                      |                  |

|      |     | 4.2.2 JOP With Double Stack                          |                  |

|      |     | 4.2.3 JOP With Double RAM                            |                  |

|      |     | 4.2.4 Obfuscation of Execute Portion of Trace        |                  |

|      |     | 4.2.5 Obfuscation of the RAM write back of the Trace |                  |

|      | 4.3 |                                                      |                  |

|      |     | 4.3.1 JOP without countermeasures                    |                  |

|      |     | 4.3.2 JOP with Double Adder                          |                  |

|      |     | 4.3.3 JOP with DAILMOM                               |                  |

Page

|      |                                      | Page |

|------|--------------------------------------|------|

| V.   | Conclusions and Future Work          | 83   |

|      | 5.1 Conclusions. 5.2 Future Work.    |      |

| A.   | Java Modulo Exponentiation Functions | 86   |

| В.   | Java Software Implementations        | 93   |

| С.   | Java Software Implementations        | 110  |

| D.   | Double Stack                         | 117  |

| E.   | Double RAM                           | 129  |

| Bibl | iography                             | 138  |

## List of Figures

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

| 1      | IBM 4758-001                                                             | 2    |

| 2      | An IBM 4758-001 part potted in urethane, showing membrane and interior   | 3    |

| 3      | Differential Power Analysis                                              | 10   |

| 4      | Correlation Power Analysis                                               | 11   |

| 5      | MDPL AND Gate                                                            | 17   |

| 6      | WDDL AND gate and truth table                                            | 17   |

| 7      | RCDDL Gate Structure                                                     | 20   |

| 8      | AES flow diagram                                                         | 20   |

| 9      | MixColumns function                                                      | 21   |

| 10     | SBox                                                                     | 28   |

| 11     | JOP Block Diagram                                                        | 28   |

| 12     | Original synchronous JOP hardware multiply unit                          | 31   |

| 13     | Dual Asynchronous In-Line Multiplexed Out/inputs<br>Multiplier (DAILMOM) | 38   |

| 14     | VHDL to interleave signals                                               | 38   |

| 15     | System Under Test (SUT)                                                  | 46   |

| 16     | Lecroy 7zi oscilloscope                                                  | 46   |

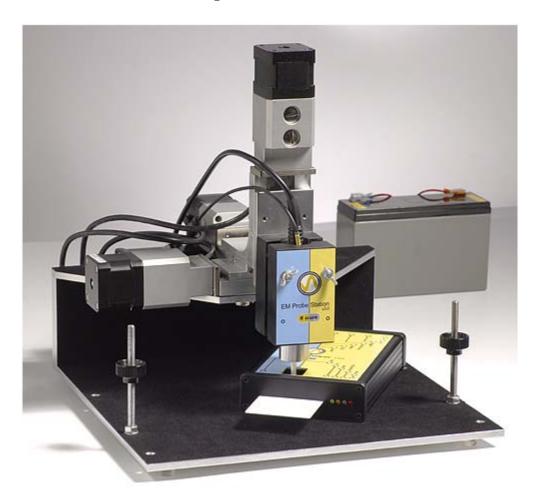

| 17     | EM Probe                                                                 | 47   |

| 18     | RF Probe                                                                 | 47   |

| 19     | RISCure XY table with EM probe                                           | 47   |

| 20     | Laptop and Riscure XY table                                              | 48   |

| 21     | Lecroy oscilloscope being used                                           | 49   |

| Figure |                                                                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 22     | Power supply to Active EM Probe                                                                                                                      | 49   |

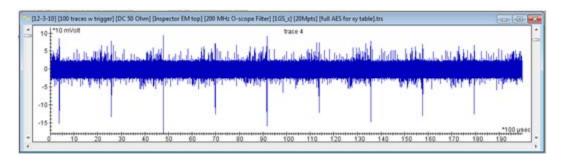

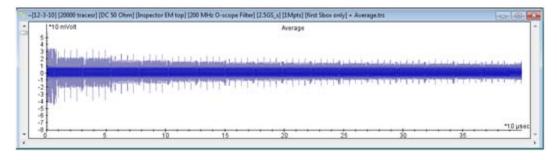

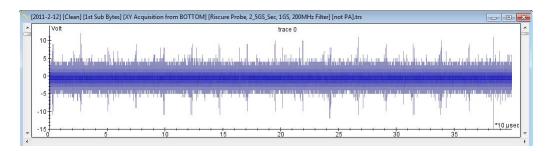

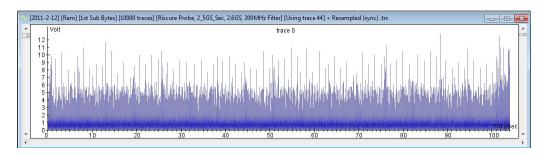

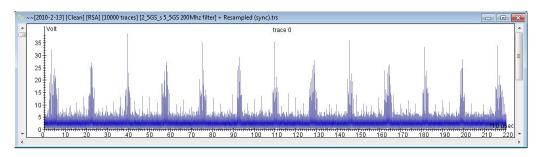

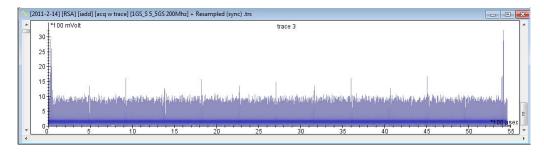

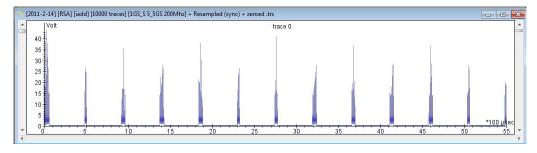

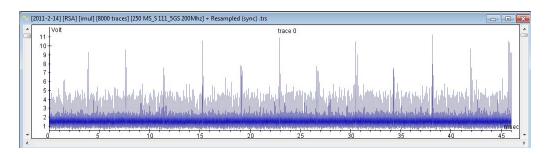

| 23     | Example traces showing periodic nature of AES (10 rounds)                                                                                            | 51   |

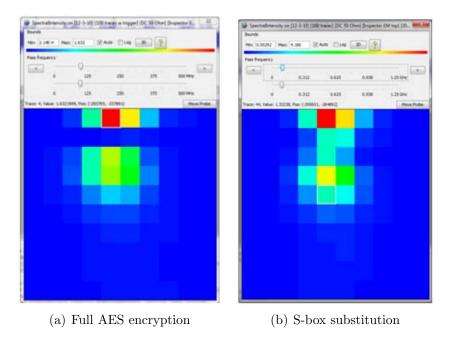

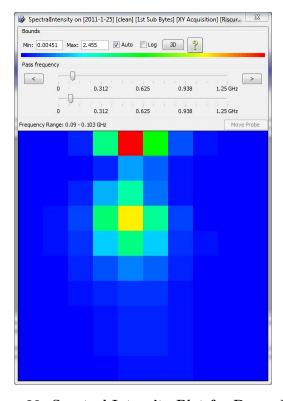

| 24     | Plot of the surface of the FPGA showing only the 99Mhz signal where red shows the largest amount of signal and blue shows the least amount of signal | 52   |

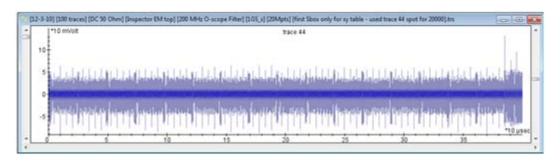

| 25     | trace chosen of S-box substitution                                                                                                                   | 52   |

| 26     | Average S-box substitution trace                                                                                                                     | 52   |

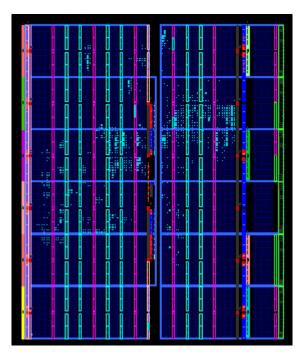

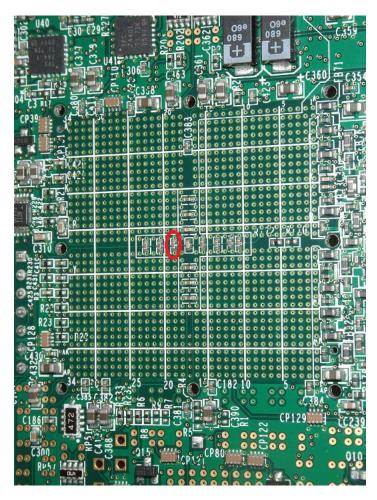

| 27     | Original JOP architecture placed on FPGA                                                                                                             | 54   |

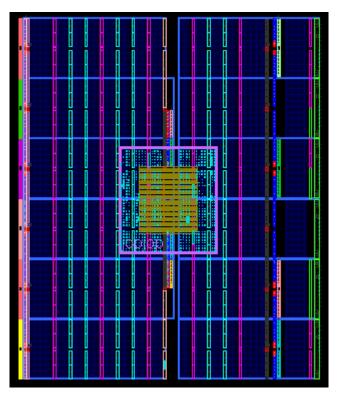

| 28     | Consolidated JOP architecture placed on FPGA                                                                                                         | 55   |

| 29     | Spectral Intensity Plot for Dense JO                                                                                                                 | 55   |

| 30     | Power capacitor giving best SCA information leakage circled in red                                                                                   | 56   |

| 31     | AES SubBytes as seen from the bottom of the FPGA                                                                                                     | 56   |

| 32     | Sub bytes in java code                                                                                                                               | 58   |

| 33     | Subbytes Assembled Code                                                                                                                              | 61   |

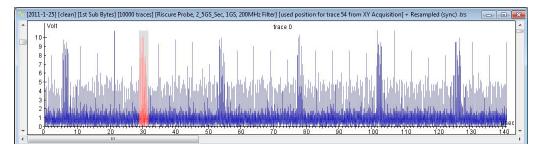

| 34     | Location of AES attack during execute stage for first key byte                                                                                       | 61   |

| 35     | Location of AES attack during RAM writeback for first key byte                                                                                       | 61   |

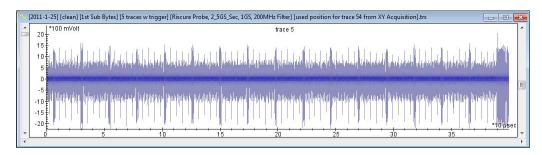

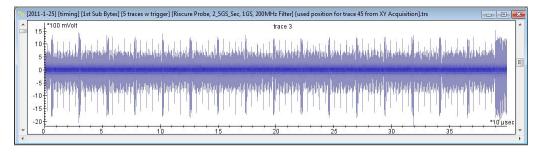

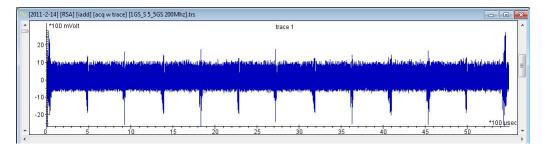

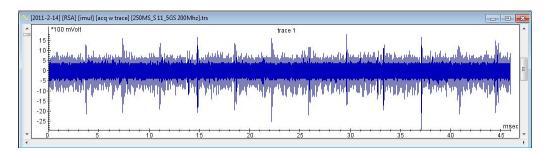

| 36     | AES trace on unprotected JO                                                                                                                          | 62   |

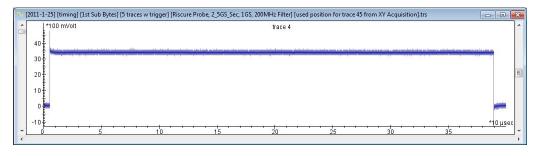

| 37     | Trigger for AES trace on unprotected JO                                                                                                              | 62   |

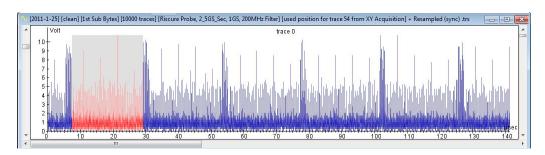

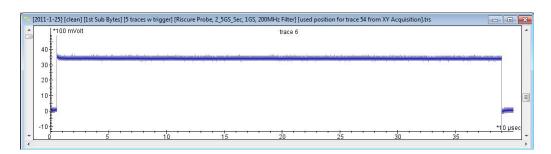

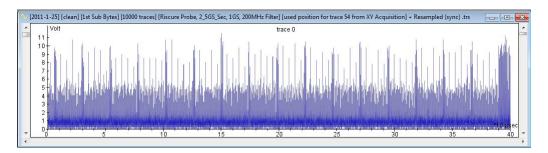

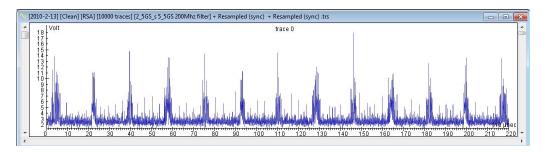

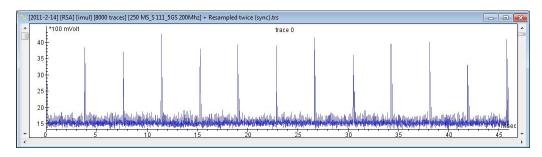

| 38     | AES trace on unprotected JOP after resampling                                                                                                        | 62   |

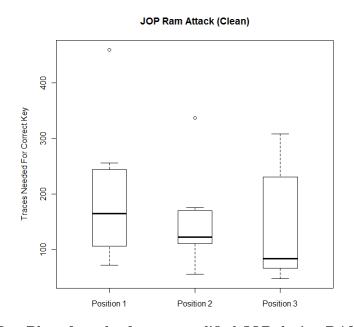

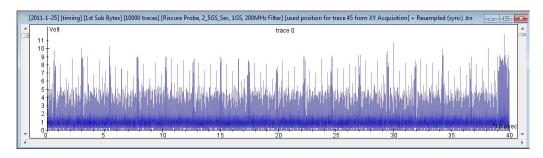

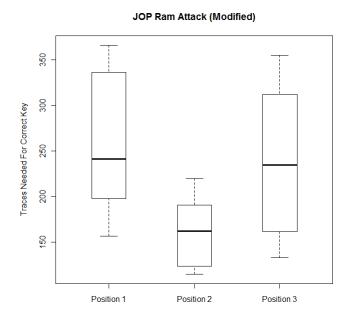

| 39     | Box Plot of results from unmodified JOP during execution stage                                                                                       | 63   |

| Figure | Page                                                                                      |

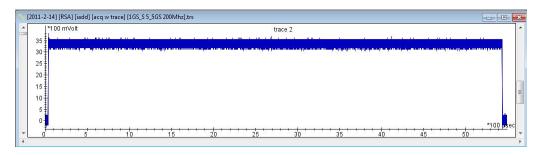

|--------|-------------------------------------------------------------------------------------------|

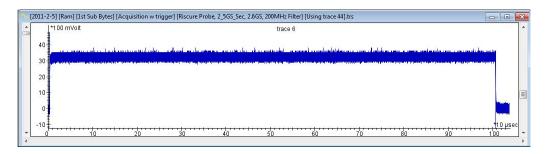

| 40     | Box Plot of results from unmodified JOP during RAM writeback                              |

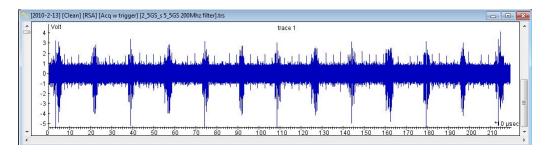

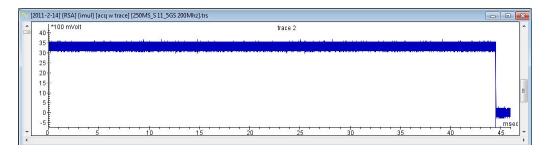

| 41     | AES trace of JOP with double Stack                                                        |

| 42     | Trigger for AES trace of JOP with double Stack                                            |

| 43     | AES trace of JOP with double Stack after resampling                                       |

| 44     | Box Plot of results from JOP with Double Stack during execution stage                     |

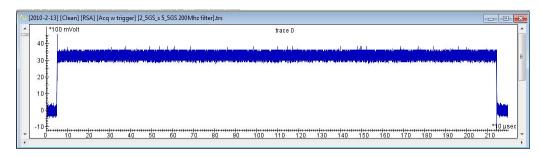

| 45     | AES trace on JOP with double RAM67                                                        |

| 46     | Trigger for AES trace on JOP with double RAM                                              |

| 47     | AES trace on JOP with double RAM after resampling 69                                      |

| 48     | Box Plot of results from JOP with Double RAM during RAM writeback                         |

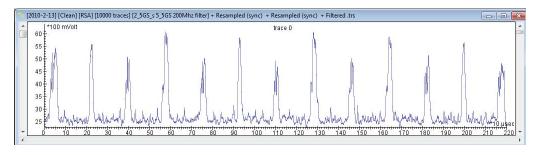

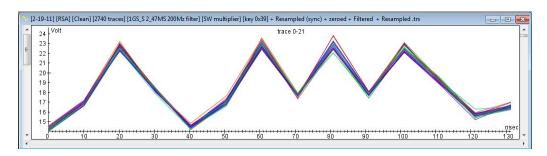

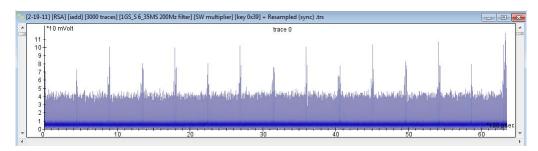

| 49     | Plot of RSA bitgroup exponentiation without countermeasures                               |

| 50     | Plot of trigger for RSA bitgroup exponentiation without countermeasures                   |

| 51     | Plot of RSA bitgroup exponentiation without countermeasures after resampling              |

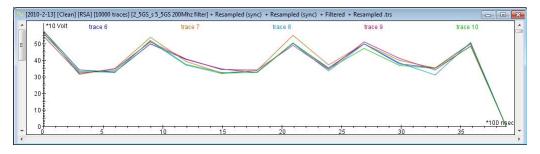

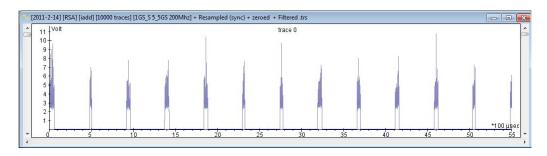

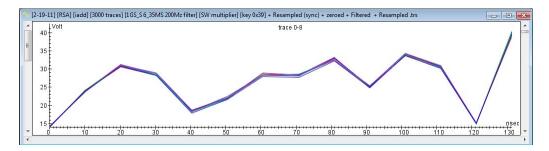

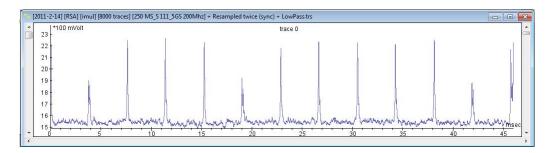

| 52     | Plot of RSA bitgroup exponentiation without countermeasures after second resampling       |

| 53     | Plot of RSA bitgroup exponentiation without countermeasures after a lowpass filter        |

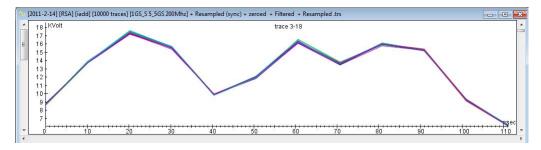

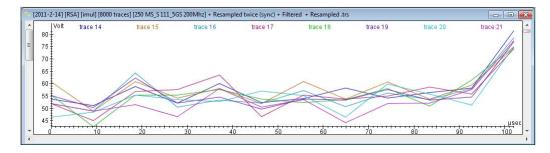

| 54     | Plot of RSA bitgroup exponentiation without countermeasures after the filtered resampling |

| 55     | Plot of RSA bitgroup exponentiation without countermeasures after the filtered resampling |

| Figure |                                                                                                                                                             | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

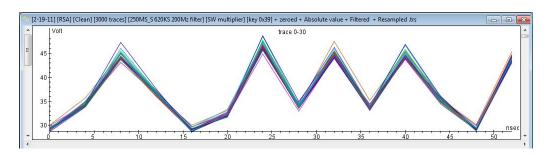

| 56     | Plot of RSA bitgroup exponentiation without countermeasures after the filtered resampling on a sample with an original oscilloscope sampling rate of 250Mhz | 77   |

| 57     | Plot of RSA bitgroup exponentiation with Double Adder                                                                                                       | 78   |

| 58     | Plot of trigger for RSA bitgroup exponentiation with Double Adder                                                                                           | 78   |

| 59     | Plot of RSA bitgroup exponentiation with Double Adder after resampling                                                                                      | 78   |

| 60     | Plot of RSA bitgroup exponentiation with Double Adder after zeroing out noise by hand                                                                       | 78   |

| 61     | Plot of RSA bitgroup exponentiation with Double Adder after a lowpass filter                                                                                | 79   |

| 62     | Plot of RSA bitgroup exponentiation with Double Adder after the filtered resampling                                                                         | 80   |

| 63     | Software version a of multiplier                                                                                                                            | 80   |

| 64     | Plot of RSA bitgroup exponentiation with Double Adder using software multiplier after resampling                                                            | 80   |

| 65     | Plot of RSA bitgroup exponentiation with Double Adder using software multiplier after the filtered resampling                                               | 81   |

| 66     | Plot of RSA bitgroup exponentiation with DAILMOM                                                                                                            | 81   |

| 67     | Plot of trigger for RSA bitgroup exponentiation with DAILMOM                                                                                                | 81   |

| 68     | Plot of RSA bitgroup exponentiation with DAILMOM after resampling                                                                                           | 81   |

| 69     | Plot of RSA bitgroup exponentiation with DAILMOM after resampling a second time                                                                             | 82   |

| 70     | Plot of RSA bitgroup exponentiation with DAILMOM after a lowpass filter                                                                                     | 82   |

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

|        |                                                  |      |

|        |                                                  |      |

| 71     | Plot of RSA bitgroup exponentiation with DAILMOM |      |

|        | after the filtered resampling                    | 82   |

### List of Tables

| Table | Page                                                                                                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | RSA algorithm                                                                                                                                                             |

| 2     | Binary Exponentiation                                                                                                                                                     |

| 3     | Chinese Remainder Theorem                                                                                                                                                 |

| 4     | Bit Group Multipliers                                                                                                                                                     |

| 5     | JOP execution Example A=B+C*D37                                                                                                                                           |

| 6     | FPGA Design Resource Utilization                                                                                                                                          |

| 7     | FPGA Design Resource Utilization                                                                                                                                          |

| 8     | Minimum traces needed for correck key using unmodified JOP looking at the execution portion                                                                               |

| 9     | Minimum traces needed for correct key using unmodified JOP looking at RAM writeback                                                                                       |

| 10    | Minimum traces needed for correck key using Double Stack                                                                                                                  |

| 11    | Minimum traces needed for correck key using JOP with Double RAM                                                                                                           |

| 12    | Results from a two sided T-test on the execution stage of subbytes when comparing the unmodified JOP to the JOP with the double stack without outliers shown in Box Plots |

| 13    | Results from a two sided T-test on the execution stage of subbytes when comparing the unmodified JOP to the JOP with the double stack without outliers shown in Box Plots |

### List of Abbreviations

| Abbreviation | Page                                                                |

|--------------|---------------------------------------------------------------------|

| SCA          | Side Channel Analysis                                               |

| ATMs         | Automated Teller Machines                                           |

| SSL          | Secure Socket Layer                                                 |

| EM           | Electromagnetic                                                     |

| API          | Application Programming Interface                                   |

| RSA          | Rivest, Shamir, and Adleman                                         |

| AES          | Advanced Encryption Standard                                        |

| DAILMOM      | Dual Asynchronous In-Line Multiplexed         Out/inputs Multiplier |

| RAM          | Random Access Memory                                                |

| EMSEC        | Electromagnetic Security                                            |

| CMOS         | Complementary Metal-Oxide Semiconductor                             |

| HW           | Hamming Weight8                                                     |

| HD           | Hamming Distance                                                    |

| SPA          | Simple Power Analysis                                               |

| DPA          | Differential Power Analysis                                         |

| SODPA        | Second Order Differential Power Analysis                            |

| CPA          | Correlation Power Analysis                                          |

| RPI          | Random Process Interrupts                                           |

| RSL          | Random Switching Logic                                              |

| DVFS         | Dynamic Voltage and Frequency Switching                             |

| MDPL         | Masked Dual-Rail Pre-charge Logic                                   |

| Abbreviation | Page |

|--------------|------|

|--------------|------|

| DRP  | Dual-Rail Precharge                                              |

|------|------------------------------------------------------------------|

| DDL  | Dynamic and Differential Logic                                   |

| SOP  | Sum Of Products                                                  |

| JVM  | Java Virtual Machine                                             |

| ALU  | Arithmetic Logic Unit                                            |

| CRT  | Chinese Remainder Theorem                                        |

| JOP  | Java Optimized Processor                                         |

| GNU  | Gnu's Not Unix                                                   |

| FPGA | Field Programmable Gate Array                                    |

| ASIC | Application-Specific Integrated Circuit                          |

| CISC | Complex Instruction Set Computer                                 |

| RISC | Reduced Instruction Set Computer                                 |

| VHDL | Very high speed integrated circuit Hardware Description Language |

| JTAG | Joint Test Action Group                                          |

| JDK  | Java Development Kit                                             |

| RCA  | Ripple Carry Adder                                               |

| CLA  | Carry Look Ahead                                                 |

| SCIO | SimpCon Input/Output                                             |

| SUT  | System Under Test                                                |

| CUT  | Components Under Test                                            |

| CUDA | Compute Unified Device Architecture                              |

| DES  | Data Encryption Standard85                                       |

# SOFTWARE AND CRITICAL TECHNOLOGY PROTECTION AGAINST SIDE-CHANNEL ANALYSIS THROUGH DYNAMIC HARDWARE OBFUSCATION

#### I. Introduction

The introduction chapter begins with a brief introduction into the history of Side Channel Analysis (SCA) attacks to set the stage for the motivation of this thesis. After providing a brief history, this chapter outlines four types of attacks on microprocessors running cryptographic code, and explain which type of attack SCA falls under. At this point, the introduction chapter briefly explains what Side Channel Analysis is and provides a background for how it applies to microcontrollers. At the end of the chapter is the research problem statement, goals and objectives, proposed methods, and an outline of what the next four chapters will contain.

#### 1.1 History

Security and cryptography in electronics have played an integral part in society for several decades. Starting in the 1970s with securing military communication channels and in the civilian sector with Automated Teller Machines (ATMs), the need for security has been on the rise since first being sold on the open market. Secure cryptoprocessors (microprocessors that process cryptographic algorithms) will often be the backbone of security networks like in the case of ATMs. Crypto-processors have also found more widespread use in protecting Secure Socket Layer (SSL) keys and defending proprietary software and algorithms from theft, both from the outside world and from employees. Cryptography has become essential to our society. One can find

crypto-processors in smart cards, decryption keys for pay TV, lottery ticket vending machines, and mobile-phone systems. For all these crypto-processors, companies deploy various means of tamper resistance to prevent system tampering, reproduction, disabling, and reverse-engineering [4].

In the 1970s when crypto-processors were first being used, there was only a need for simple security measures and tamper-resistant hardware. IBM developed the 3614 ATM system for authenticating customers at ATMs with a bank-given PIN. Although it did not employ significant anti-tamper protocols, it contained various algorithms to prevent whole-sale discovery of PINs and other simple methods to prevent employee tampering [5]. In time, cryptographic systems have become more complicated, and their security has greatly increased. The IBM 3848 was one of the first cryptoprocessors to incorporate an active anti-tamper mechanism. It was enclosed in a steal case that would zero out the memory when it was opened. Its successor, the IBM 4758 (see Figures 1 and 2) was a cryptographic engine surrounded by a multilayer tamper-sensing mesh. The mesh was constantly monitored and would zero out all key material if tampering was sensed [10].

Figure 1. IBM 4758-001.

#### 1.2 Motivation

#### 1.2.1 Attack Types.

There are four different classes of attack by which an adversary can attack a crypto-processor: Local Noninvasive Attacks, Semi-Invasive Attacks, Invasive Attacks, and Remote Attacks [4]. Local Noninvasive Attacks involve gaining information about the device through close observation of the device in operation, watching both the Electromagnetic (EM) emissions and various environmental information around the device. Local Noninvasive Attacks was chosen to be the focus of this research because of it's importance because it allows any attacker to circumvent cryptographic algorithms just by having access to the device, and the owner of the crypto system may never even know about the attack. Additionally, although not covered by this thesis, are Semi-Invasive Attacks, Invasive Attacks, and Remote Attacks. Semi-Invasive Attacks do not require damaging of the passivation layer, and instead use lasers to ionize transistors and change its state. This method is difficult to use to extract information due to the variability inherent in trying to ionize specific transistors. Invasive Attacks involve actual damage to the device and connection or monitoring of the device interior. Although this is a useful, because it destroys the device there are large risks associated with this method. Remote Attacks, as in the case of an

Figure 2. An IBM 4758-001 part potted in urethane, showing membrane and interior.

Application Programming Interface (API) like SSL, are done remotely and interface with a device in normal operation. These methods are useful, but they deal solely with programming vulnerabilities and not hardware vulnerabilities [4].

SCA attacks, also known as Local Non-Invasive attacks, are the method by which an adversary can cleverly deduce information about a cryptographic system by watching the interaction of a digital circuit with its surrounding environment. The research is focusing on the attacks because this method allows an adversary to circumvent a secure cryptoalgorithm just by having physical access to the device without the device owner ever knowing their crypto system was compromised. The three most important types of SCA are timing, power-analysis, and EM attacks. In all types, the basic idea is to determine a cryptographic device's secret key by measuring its execution time, power consumption, or electromagnetic field [30].

#### 1.3 Problem Statement

This research addresses the problem of SCA for the cryptographic algorithms, where a cryptography key can be made known to an adversary through close monitoring of the device in operation. Furthermore, this research aims to reduce the susceptibility of cryptography systems to SCA attacks.

#### 1.4 Goals and Objectives

The goal of this research is to propose new methods to protect cryptographic information and critical technology by making dynamic changes to the underlying architecture of a microprocessor. The objectives of this research are to implement SCA vulnerable algorithms, compromise them, and then show an increase in the security of the circuit after incorporation of the proposed secure hardware.

#### 1.5 Proposed Protection Methods

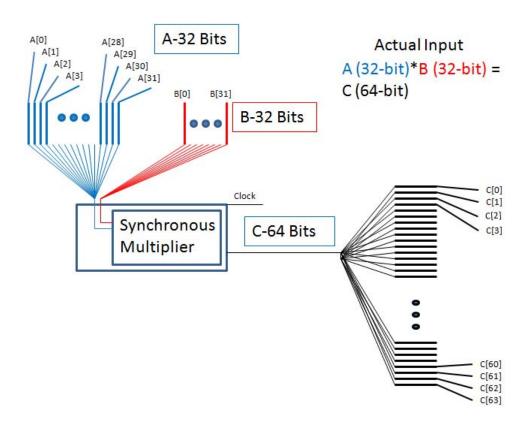

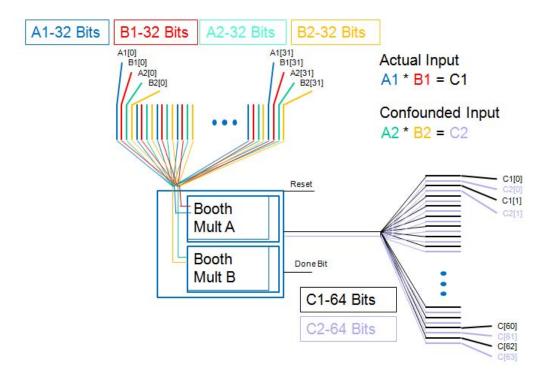

The proposed methods of this research are derived from the hypothesis that by adding multiple hardware units that are functionally the same but structurally different, the EM emissions off the microprocessor can be varied increasing the difficulty to conduct SCA successfully. There are two proposed methods to protect the cryptographic algorithm Rivest, Shamir, and Adleman (RSA) and two proposed methods to protect the cryptographic algorithm Advanced Encryption Standard (AES). To protect RSA, the two proposed methods are a Double Adder and a Dual Asynchronous In-Line Multiplexed Out/inputs Multiplier (DAILMOM). These two proposed countermeasures obfuscate RSA where the algorithm is most vulnerable to SCA attacks, and are used to override the current addition and multiplication functions on the microprocessor. The Double Adder increases the security by alternating the power signature of the add operation each time an addition is called. This is done by using a Carry Look Ahead adder whose power signature to add numbers is front-loaded, and the Ripple Carry Adder whose power signature is evenly distributed during addition. Alternating which adder is used allows for one add to have a front-loaded or an even distribution during addition, and then the next addition operation, regardless of the values being added, will have the other power signature. The DAILMOM uses two multipliers and it's obfuscation is due to the result of the second multiplier being fed arbitrary data that will shape the power signature a different way each time. This overlay of noise whose signature can be manipulated allows for two subsequent multiply operations to have the same data but totally different power signatures. To protect AES, the two proposed methods are a Double Stack and a Double RAM. These two proposed countermeasures aim to protect AES where it is most vulnerable to SCA attacks by changing the way the microprocessor stores values on the stack during the execution stage and how values are saved to the Random Access Memory (RAM) during the writeback of variables. This increase in security is due to when a variable is being saved, it is split into two variables, where each resulting variable being saved always has the same number of logic '1's and '0's. This power normalization allows for the data to always have the same usage, decreasing the power changes in the circuit that SCA looks for.

#### 1.6 Research Methodology

Testing of the proposed methods will be done by implementing both RSA and AES on a microprocessor being implemented on an FPGA. First, the two cryptographic systems will be evaluated for their initial security against SCA. After a baseline security is established, the microprocessor security will be reevaluated with the proposed methods and be recompared to the original microprocessor.

#### 1.7 Organization

Chapter 2 provides background information on current research with SCA and protection against SCA. Chapter 3 details the approach for implementation and evaluation of the stated objectives. Chapter 4 details the results of the experiments and any adjustments required to facilitate the thesis goals. Chapter 5 evaluates the work undertaken and reviews the major contributions of this thesis, which includes future directions for extending this research.

#### II. Related Work

Chapter 2 begins by explaining Differential and Correlation Power Analysis. Chapter 2 then explains the current research in preventing SCA attacks separated into algorithmic countermeasures and circuit level countermeasures. After this, the thesis examines the cryptography algorithms Rivest, Shamir, and Adleman (RSA) and Advanced Encryption Standard (AES) and then goes through the JOP in detail.

#### 2.1 Differential and Correlation Power Analysis

Beginning in June of 1998 with Kocher's initial publication of the susceptibility of cryptosystems to side channel analysis [13] and his follow up article [14], much research has been done to both protect and exploit circuits. Although SCA attacks have become more sophisticated in the last decade, the basic idea of SCA is not new. For example, military circles were aware of the need for EM security since the discovery of crosstalk between telegraph lines of the British army expedition to the Nile and Suakin in 1884-1885. Even in World War I, telephones on the front lines could be eavesdropped by the opposing side at distances of hundreds of yards. Nowadays, "Tempest" military standards help to govern electronic emissions for military devices and for Electromagnetic Security (EMSEC) [1].

#### 2.1.1 Background.

The basic premise of SCA attacks stem from the reality that the switching activity of Complementary Metal-Oxide Semiconductor (CMOS) circuits leak information. When a CMOS circuit charges to a '1' or discharges to a '0', a change in the electric potential creates a change in the electric field which is measurable outside the chip. Generally the quantization of the energy for a given value is derived from either the

Hamming Weight (HW) or the Hamming Distance (HD). In the case of the HW, the value of a given data is the summation of the bits that are in a 'non zero' state. That is to say that the HW of 0x50 (0b01010000) is two, and the HW of 0x03 (0b00000011) is also two while the HW of 0xFF (0b11111111) is eight. The HD however is a measure of the change of a value, measuring the number of bits that change from the previous state to the current state. For example the hamming distance between 0x50 and 0x03 is 4, while the hamming distance between 0x50 and 0xFF is 6. The Hamming Weight can be thought of as the Hamming Distance between the zero value 0x00 and any other value. Commonly, the model used to describe the information leakage off a chip is  $C(t)^{(a,b)} = \lambda HW(a \otimes b) + \beta_t$ , where  $(a \otimes b)$  is the XOR of a and b, HW is the Hamming Weight function,  $\lambda$  is the power consumption used by the circuit when inverting the bit, and  $\beta_t$  is noise [6].

#### 2.1.2 SCA Attack types.

From monitoring the execution time, power consumption and the electric field from a microprocessor, the three main types of SCA attacks used to find secret key information are: Simple Power Analysis (SPA), Differential Power Analysis (DPA), and Second Order Differential Power Analysis (SODPA) [28]. A SPA attack involves directly observing a system's power consumption. This attack is particularly useful when an adversary only has the ability to capture only one encryption because SPA can be done on a single trace. If the attacker knows generally what the processor is doing, an attacker can visually analyze the trace and extract information. This attack is also particularly useful in RSA, where binary exponentiation exacerbates visual timing differences that depend on the key in the power trace.

DPA is significantly more powerful than SPA, but is more complicated and requires many more traces. For DPA to work, one needs to know either the plaintext or ciphertext of each trace. The known plain/ciphertext of each trace is then used with hypothesis testing for the first bit of the key. From this hypothesis and using the knowledge of the plain text for each trace, all of the traces can be separated into two pools: if the resulting bit of the plain text after encryption is a '1' or a '0' given the key hypothesis [20]. With these two pools, statistical analysis can be conducted to search for correlating power biases in the comparisons that will arise for correct key guesses. From these power biases, the correct key can be derived.

Lastly, SODPA is the most powerful SCA tool, but also the most complicated. SODPA is a method employed to overcome the masking countermeasure employed by some SCA defenses. In masking, a defender splits a value Z into d shares  $M_1 \diamond ... \diamond M_d$  such that  $M_1 \diamond ... \diamond M_d = Z$  and where  $\diamond$  is a function like the XOR or modular addition [23]. A masking operation is said to be (d-1)th-order depending on the number of shares d. When a (d-1)th order masking is used, a dth-order DPA can be performed by combining the leakage signals at time intervals  $L(t_1)$ , ...,  $L(t_d)$  resulting from the manipulation of the d shares that make up the value Z. The downside to this attack is that noise effects in the leakage current readings increases exponentially with the number of d shares. Currently there are no designs of higher order masking that are efficient and secure beyond the second order, as such only second order masking is generally used in the protection of block ciphers.

#### 2.1.3 Differential Power Analysis vs Correlation Power Analysis.

There are namely two methods referred to as Differential Power Analysis, the original DPA (also known as the Difference in Means Method) and Correlation Power Analysis (CPA) [11]. The original DPA was the first method used by Kocher in his attack of the cryptographic system. In this attack, one feeds a known plain text to the cryptographic system (or keeps track of the cipher text and works backward

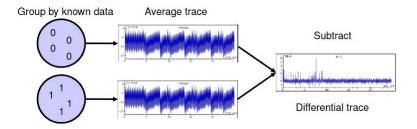

from the traces instead) and records the power trace that corresponds to that data. In order for this attack to work, one needs many traces with many different known plain texts. Then the attacker works down the bits of the key, one by one, making a hypothesis guess as to if that bit is set or not individually. Having done this, the attacker separates all of the traces into two groups, those who the key guess would result in them having '0' for the given value after encryption, and those that the key guess would result in them having a '1' after encryption. Once the traces have been separated, the attacker averages all the traces for each group, and then find the difference of the means. If your key guess was correct, then the difference of means trace results in a power spike. If the key guess was incorrect, then the resulting difference trace would not contain any spikes. This method of separating traces into bit groups, finding the average trace, and then finding the difference in means can be seen in Figure 3 [25].

Figure 3. Differential Power Analysis

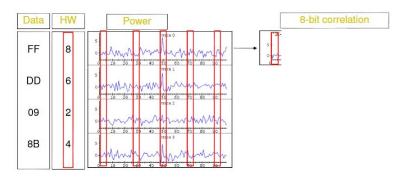

Though often bundled up with traditional Differential Power Analysis under the name of DPA, Correlation Power Analysis is a newer method for power analysis and computes keys in a different fashion. In the case of CPA, linear algebraic methods are used to find keys in the traces. Given many traces with many plain texts, the correlation coefficient is a measure of the linear relationship of the plain text with the trace value at a given instant in time. The correlation power trace is derived by using Pearson's coefficient of correlation on the 'data' values and the 'trace' values for each time instant, and then stepping in time down the trace and finding the resulting

coefficient of correlation for each time instant. Figure 4 shows an example of CPA being used on four traces where the data (FF, DD, 09, and 8B) is being correlated with the values in the first red box to create the first value of the 8-bit correlation. The subsequent red boxes attempt to show the correlation being done at every time instant to create the full 8-bit correlation that is examined for spikes [11] [25].

Figure 4. Correlation Power Analysis

In practice, Correlation Power Analysis' use of linear algebra actually has a significant reduction in the effect of random noise in power traces. So using CPA instead of traditional DPA results in the correct key with fewer traces. For the remainder of this document, when DPA is used on a given sample set, CPA is the method of DPA employed unless otherwise stated. As explained in Chapter 3, these methods of power analysis attacks are accomplished on the data using the third party software, Riscure Inspector.

#### 2.2 Algorithmic Countermeasures

As mentioned earlier, SCA attacks fit into three categories - Simple Power Analysis, Differential Power Analysis, and Second Order Differential Power Analysis. Defenses against these attacks fit into two high-level categories: algorithmic countermeasures and circuit-level countermeasures. Countermeasures can be further classified based on the method by which they try to decouple the power consumption with the

data being processed, these are: masking countermeasures and elimination (hiding) countermeasures [28].

#### 2.2.1 Masking Techniques.

Algorithmic countermeasures try to uncorrelated the output of algorithms with the secret key. Masking at the algorithmic level has the key notion of minimizing the correlation between intermediate values and the secret key [7]. One simple method to accomplish this is to introduce noise into the power consumption measurements. This method is overcome by the introduction of more samples. In theory if the variance of the noise is great, then the necessary sample size might be infeasible, but this method is still surmountable by increasing the number of samples [15].

Another option to the end of masking power traces at the algorithmic level is the introduction of Random Process Interrupts (RPI) during the cryptographic algorithm. This approach can be done by interleaving random dummy commands or "No Operation' (NoOp commands)' randomly throughout the code thus masking the actual execution sequence. Thus RPIs cause time shifts in the corresponding cryptographic operations and thus mismatch amongst them. This mismatch reduces the size of the correct differential spikes by spreading them over several clock cycles in different traces. It also causes an increase in the number of clock cycles needed for analysis proportional to the squared number of the clock cycle variation that occurs. That is to say, if k is the number of clock cycles that the event varies, then the number of necessary traces is proportional to  $k^2$ . Although this increase in the required clock cycles can make a SCA attack infeasible, it does not prevent an attack because the information is still being leaked. In the case of RPIs, the correlation spikes can be reconstructed though by integrating the signal over the number of consecutive clock cycles equal to the greatest number variance in the clock cycles [8]. This method to

overcome RPIs is called the sliding window attack. For this attack, several traces are integrated together and then compared against other integrated traces for the power spikes [17].

Another method for algorithmic masking is to split the key into two halves (duplication method) [9] or more generally, by splitting the key into k shares [7]. However, this method of masking can be circumvented through the use of higher-order differential power analysis. By combing the leakage signals at time intervals  $L(t_1)$ , ...,  $L(t_d)$  that are the resulting leakages from the manipulation of the d shares that make up the value Z, the differential power spike for correct key guesses can be reproduced [23][19][21].

#### 2.2.2 Elimination Techniques.

Elimination is the other method that can be used to confound power variation. The key notion of elimination (hiding) is to remove power variation information from the attacker. Where masking seeks to decouple the power variation from the data being processed, elimination seeks to eliminate it. Four ways that people employ to use elimination are: [15]

- 1 Using constant execution path code

- 2 Choosing operations that leak less information in their power consumption

- 3 Balancing hamming weights and state transitions

- 4 By physically shielding the device

#### 2.3 Circuit Level Countermeasures

#### 2.3.1 Masking Techniques.

Circuit level countermeasures to remove the correlation between a circuit's power characteristics and the data being processed. In CMOS circuitry, power is consumed by the system when an output transitions from a logical 0 to a 1. These power spikes are what an adversary uses in power traces to gleam information. Many masking techniques at the circuit level introduce random power consumptions which are akin to noise. Examples include Random Switching Logic (RSL) [29], masking-AND [34], and Dynamic Voltage and Frequency Switching (DVFS) [35]. The RSL countermeasure adds in random logic paths, masking-AND masks every output with random inputs, and DVFS randomly modulates voltage and switching frequency to introduce randomness into power traces. All of these circuit level masking techniques, however, are still susceptible to glitches. Glitches are the transitions at the output of a gate that occur before the gate switches to the correct output. Because glitches add to the power signature, they are susceptible to leak information, especially when they leak key information before the correct mask is applied [18][3]. RSL uses random input and enable control signals to randomize the power signature and is thus able to avoid the information leakage posed by glitching, but the enable signals need to be carefully timed [3].

A more advanced method for circuit level masking however is Masked Dual-Rail Pre-charge Logic (MDPL) [22]. MDPL uses both masking and dual rail precharged logic to obfuscate the power signature. The masked values are represented as bm = b + m, where b is the actual value and m is the applied mask. Furthermore, the mask, m, is a bit generated randomly and updated every clock cycle. The Dual-Rail Precharge (DRP) logic addresses the glitches that occur in CMOS circuitry by precharging all signals to 0 before every evaluation phase and thereby alternating between the precharge and evaluation states. MDPL also makes use of majority function gates which only change the output once during the precharge phase and once during the evaluation phase. An example of the MDPL AND gate is shown in Figure 5.

The majority function gate goes high when most of the inputs are high, and goes low when most of the inputs are low. The six dual-rail inputs can be seen in the picture as well:  $a_m$ ,  $b_m$ ,  $c_m$ ,  $a'_m$ ,  $b'_m$ , and  $c'_m$ . The dual rail logic claims to have equal capacitances and thus prevents glitching by evaluating both the logic value and its inverse simultaneously. Although the precharge logic aims to prevent glitching, it also has the added benefit of helping to smooth out power use [22]. However, with all these advances, [16] shows that MDPL is susceptible to leakage due to early propagation, which is when a gate calculates the output before all the inputs arrive. Further, [26] shows loading balances that occur due to a lack of routing constraints which can be used to expose a DES key. The mask bit is also fairly easy to remove by examining the trace and seeing if the power trace is above or below the average power consumption. Furthermore as an efficiency note, the necessary power for MDPL increases by more than double due to the dual rail logic and the added mask circuitry and precharging.

#### 2.3.2 Elimination Techniques.

Elimination, as mentioned earlier, attempts to eliminate power variation by making the power consumption of the device constant for any input data. Without any variation in power due to the key, no information is leaked through side channels. Constant power can be achieved by ensuring that a constant power is consumed every clock cycle. This is done in the Dynamic and Differential Logic (DDL) style by ensuring that one of the outputs is charged for any input, be it the output or the complimented output, and it ensures that one output transition occurs in every clock cycle. More specifically, DDL logic is split into a precharge state, where all outputs are at zero, and then an evaluation phase, where at least one output or its compliment goes high [31]. Sense Amplifier Based Logic is an implementation of DDL that uses a dynamic-CMOS logic implementation. Using this implementation of DDL, however,

causes Amplifier Based Logic to have to deal with the effects of cascading circuits and signal integrity issues that derogate the signal and make it inefficient [31].

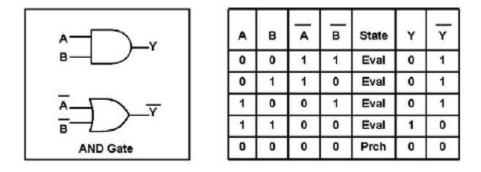

Wave Dynamic and Differential Logic (WDDL) is another implementation of DDL. WDDL uses a static CMOS implementation of AND and OR gates. Each gate in the WDDL has both the gate with the inputs and a complimentary gate with the inverse of the inputs. For example, Figure 6 shows a WDDL and gate with its logic table where "Prch" is the precharge state that the gate goes into between evaluations, and the "Eval" state is the evaluation of the gate given the inputs shown in the figure.

With the shrinking capacitor size, however, it can be seen that the signal propagation capacitance is actually greater than the transistor capacitance so to be truly effective at stopping SCA the output lines need to be placed on the board side by side with the same length of wire. Also with this logic, early propagation can be a problem which needs to be addressed. The WDDL also uses only positive gates, so that the precharge phase can propagate through all gates, which makes logic optimizing difficult. Lastly, to contain all the logic and its compliment would require a cryptosystem implementing WDDL to have at least twice the area and require twice the power as a cryptosystem that does not implement WDDL [32]

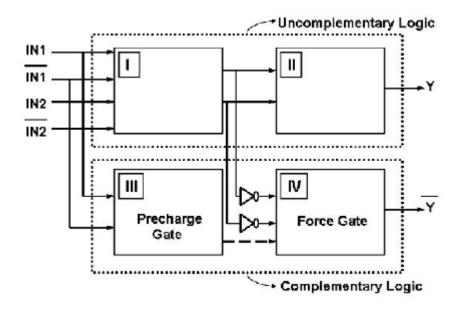

Reduced Complementary Dynamic Differential Logic (RCDDL) is another implementation of DDL. Like WDDL, RCDDL has both the logic and its complimentary logic, but RCDDL seeks to optimize its logic while keeping its security features. To optimize, RCDDL reuses logic gates in the uncomplimented logic while ensuring that a constant capacitance is charged. Unlike WDDL, RCDDL allows the both positive logic (AND/OR) and negative logic (NAND/NOR). The RCDDL gate structure can be seen in Figure 7.

As can be seen in Figure 7, the uncomplimented output, Y, is calculated through Segments I and II. Segments I, III, and IV collectively form the complimented out-

Figure 5. MDPL AND Gate [28]

Figure 6. WDDL AND gate and truth table [28]

put, Y'. The segments are created through using the Sum Of Products (SOP) where Segment I is all but the last step, which is completed in Segment II. Segment III generates the precharge signal which sets IV to drive the complimented output to '0'. This is done locally in every gate, which does away with the need for a precharge phase thus allowing for RCDDL to use negative logic. Because of the reuse of gates with RCDDL, the size and power consumption of RCDDL are smaller than that of WDDL. Additionally, it has been shown that RCDDL has less power variation than WDDL thus making it more secure. Unfortunately, as compared to WDDL, due to the size of the individual RCDDL cells, there is a delay penalty. Early propagation effects also affect RCDDL so there is that added vulnerability. [24]

Although all DDL elimination strategies reduce the power consumption variation, in reality, all methods still have minor power variations. The goal of circuit-level elimination SCA countermeasures is to further minimize with the hope of eventually eliminating these variations [28].

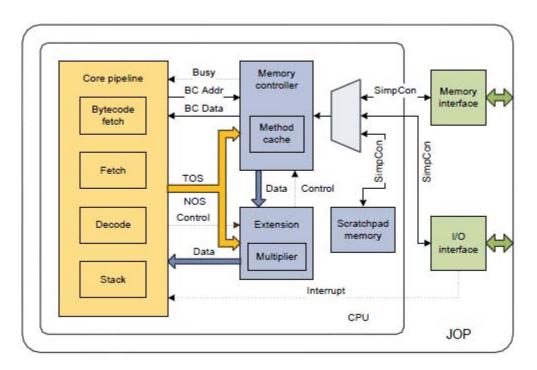

Lastly, in his article [12], Slaman obfuscated EM emissions off the FPGA by changing Java bytecodes. This method had the added benefit of changing both the power and time correlation during code execution. The Java bytecode method of obfuscation however differs from this thesis in that it was all software implemented with no changes to the hardware of the JOP, and was thus written for the Java Virtual Machine (JVM) to protect java code running on the JOP. This thesis however proposes lower level changes by changing the actual hardware, allowing for a wider range of software security.

#### 2.4 Cryptographic Algorithms

Two of the most common algorithms used in the military and in the civilian sector for encryption are the RSA algorithm developed in 1977 and the AES algorithm developed in 2001. In order to better protect the crypto-processor running RSA or AES against SCA attacks, this thesis employs the methods of both masking and elimination techniques to obfuscate the Arithmetic Logic Unit (ALU), the multiplier, and the memory to protect the circuit from EM and power SCA. Before explaining the proposed methods, it is important to first explain in greater detail both cryptography algorithms to better show why certain methods were chosen for obfuscation.

#### 2.4.1 AES.

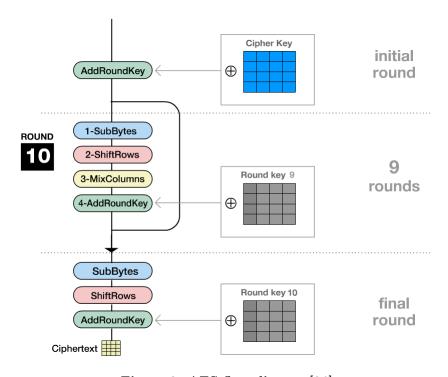

The AES algorithm is a symmetric key crypto-algorithm, using the same secret key to do both the encryption and the decryption of data. The AES flow can be seen in Figure 8.

As can be seen in Figure 8, there are three main segments of the AES algorithm, the initial round, the nine rounds in between, and then the final round. Each of these three segments are made up by the four functions: SubBytes, ShiftRows, Mix-Columns, and AddRoundKey. SubBytes uses a simple substitution algorithm and takes the current text hex values and substitutes the values with known quantities in a "substitution box" (also known as the Sbox). ShiftRows is a function where the data, oriented in a 4x4 matrix, has each of the four rows shifted where the shift amount is different for each row. MixColumns is the function where each column is treated as a four term polynomial and is multiplied modulo  $x^4 + 1$  with a fixed polynomial a(x), given by  $a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$  effectively resulting in the multiplication shown in Figure 9.

Finally, AddRoundKey is the function where the key, modified slightly for each round, is added to the current text [2].

Of those four functions, only AddRoundkey actually manipulates the data based on key, which makes AddRoundkey the important target for key extraction. Each

Figure 7. RCDDL Gate Structure [28]

Figure 8. AES flow diagram[36]

time the function AddRoundKey is called, a different permutation of the key is used, with the first call to AddRoundKey using the original key, and each subsequent call to AddRoundKey using a different version of the key. The second function of importance is SubBytes. SubBytes is a simple substitution algorithm where by the current state of the plain text is used to find the corresponding substitution value in the Sbox. The Sbox is predefined and can be seen in Figure 10. For the SubBytes function, each byte in the current text is evaluated such that the first nibble of the byte corresponds to the row and the second nibble of the byte corresponds to the column. For example, if the byte being considered is 0x19 then the value 0xd4 will be substituted in for the value 0x19. After these first two functions run is when the data is most susceptible to SCA attacks because the known plain text was just XORed by the key and the resulting state undergoes the Sbox substitution where many transistor transactions occur, thus leaking significant information of the current state of the plain text. Therefore, directly after the first SubBytes is the location of the SCA attacks on AES for this thesis.

#### 2.4.2 RSA.

RSA is used in many areas, like in the area of e-commerce where RSA is one of the algorithms used to ensure safe transmissions of data over the internet. For example, a web site like Amazon is able to publish a public key for users all over the world to use but keeps a private key secret. In this manner users are able to encrypt sensitive

$$\begin{bmatrix} S_{0,c}' \\ S_{1,c}' \\ S_{2,c}' \\ S_{3,c}' \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 01 & 01 & 02 & 03 \end{bmatrix} \begin{bmatrix} S_{0,c} \\ S_{1,c} \\ S_{2,c} \\ S_{3,c} \end{bmatrix}$$

Figure 9. MixColumns function

information like credit card numbers and pass the information over the internet to Amazon without fear that an eavesdropper would be able to decrypt the information.

RSA is known as an asymmetric key algorithm because there are two keys, one private and one public. This cryptography scheme with a public and a private key is made secure through difficulty of factoring numbers, but this leaves RSA only computationally secure but not provably secure. The computational security of RSA also means that the security of current RSA keys is based on the inherent difficulty in factoring a public key to get the private key. In theory, the modulus and the exponent (the public key, seen in Table 1 as e and n) has all the information needed to find the private exponent, but due to the difficulty in factoring a very large number, it is normally infeasible to find the private key using the public key. Keys for RSA are chosen based on them being infeasibly large to crack in a polynomial bounded computational time. As technology increases in complexity and power, likewise the key length of "secure" RSA implementations must also increase.