# AFRL-RY-WP-TR-2008-1228

## FUTURE FIELD PROGRAMMABLE GATE ARRAY (FPGA) DESIGN METHODOLOGIES AND TOOL FLOWS

Dr. Michael Wirthlin, Dr. Brent Nelson, Dr. Brad Hutchings, Dr. Peter Athanas, and Dr. Shawn Bohner

**Brigham Young University**

JULY 2008 Final Report

Approved for public release; distribution unlimited.

See additional restrictions described on inside pages

**STINFO COPY**

AIR FORCE RESEARCH LABORATORY SENSORS DIRECTORATE WRIGHT-PATTERSON AIR FORCE BASE, OH 45433-7320 AIR FORCE MATERIEL COMMAND UNITED STATES AIR FORCE

## NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report was cleared for public release by the Defense Advanced Research Projects Agency (DARPA) and is available to the general public, including foreign nationals. Copies may be obtained from the Defense Technical Information Center (DTIC) (http://www.dtic.mil).

AFRL-RY-WP-TR-2008-1228 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH ASSIGNED DISTRIBUTION STATEMENT.

\*//Signature//

ALFRED J. SCARPELLI Project Engineer Advanced Sensor Components Branch Aerospace Components & Subsystems Technology Division //Signature//

BRADLEY J. PAUL, Chief Chief, Advanced Sensor Components Branch Aerospace Components & Subsystems Technology Division Sensors Directorate

//Signature//

WILLIAM J. SISKANINETZ Chief, Aerospace Components & Subsystems Technology Division Sensors Directorate

This report is published in the interest of scientific and technical information exchange, and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

\*Disseminated copies will show "//Signature//" stamped or typed above the signature blocks.

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     |                          |                                                          |                              | Form Approved<br>OMB No. 0704-0188                 |                                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------|----------------------------------------------------------|------------------------------|----------------------------------------------------|-----------------------------------------------------|--|

| The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquaters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 2202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. <b>PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS</b> .                                                                                                                        |                                     |                          |                                                          |                              |                                                    |                                                     |  |

| 1. REPORT DATE (DD-MM-YY)<br>July 2008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |                          |                                                          |                              |                                                    | <b>OVERED (From - To)</b><br>st 2007 – 31 July 2008 |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                                          |                              |                                                    | 5a. CONTRACT NUMBER                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     | TE ARRAY (FPGA) DESIGN   |                                                          |                              | 5b. GRANT NUMBER                                   |                                                     |  |

| METHODOLOGIES AND TOOL FLOWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     |                          |                                                          |                              | FA8650-07-C-7745                                   |                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |                          |                                                          |                              |                                                    | <b>5c. PROGRAM ELEMENT NUMBER</b><br>69199F         |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     |                          |                                                          |                              |                                                    | 5d. PROJECT NUMBER                                  |  |

| Dr. Michael Wirthlin, D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | r. Brent Nels                       | son, and Dr. Brad H      | Hutchings (Brig                                          | ham Young                    |                                                    | ARPS                                                |  |

| University)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (1 D                                | 1 (17: 1 ) D 1           |                                                          | 1.0.                         |                                                    | 5e. TASK NUMBER                                     |  |

| Dr. Peter Athanas and D<br>University)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | r. Shawn Bo                         | ohner (Virginia Pol      | ytechnic Institu                                         | te and State                 |                                                    | ND                                                  |  |

| Oniversity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |                          |                                                          |                              |                                                    | 5f. WORK UNIT NUMBER                                |  |

| 7. PERFORMING ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | INAME(S) AN                         |                          |                                                          |                              |                                                    | ARPSNDBR<br>8. PERFORMING ORGANIZATION              |  |

| Brigham Young Univers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     | ginia Polytechnic I      | nstitute and Stat                                        | te University                |                                                    | REPORT NUMBER                                       |  |

| A-285 ASB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     | cksburg, VA 24061        |                                                          |                              |                                                    |                                                     |  |

| Provo, UT 84602                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     | U,                       |                                                          |                              |                                                    |                                                     |  |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |                          |                                                          |                              |                                                    | 10. SPONSORING/MONITORING<br>AGENCY ACRONYM(S)      |  |

| Air Force Research Laboratory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     |                          | lvanced Research                                         |                              |                                                    | AFRL/RYDI                                           |  |

| Sensors Directorate<br>Wright-Patterson Air Force Bas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OH 45422                            |                          | Information Processing Techniques Office<br>(DARPA/IPTO) |                              |                                                    | 11. SPONSORING/MONITORING                           |  |

| Air Force Materiel Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     | 3701 N. Fairfax Drive    |                                                          |                              | AGENCY REPORT NUMBER(S)<br>AFRL-RY-WP-TR-2008-1228 |                                                     |  |

| United States Air Force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Arlington, V                        | Arlington, VA 22203-1714 |                                                          |                              | AFRL-K1-WF-1K-2008-1228                            |                                                     |  |

| <b>12. DISTRIBUTION/AVAILABILIT</b> Approved for public rele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                   |                          |                                                          |                              |                                                    |                                                     |  |

| <ul> <li>13. SUPPLEMENTARY NOTES<br/>PAO Case Number: DARPA 12314; Clearance Date: 22 Oct 2008. This report contains color.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |                          |                                                          |                              |                                                    |                                                     |  |

| <ul> <li>14. ABSTRACT Interest is growing in the use of FPGA devices for high-performance, efficient parallel computation. The large amount of programmable logic, internal routing, and memory can be used to perform a wide variety of high-performance computation more efficiently than traditional microprocessor-based computing architectures. The productivity of FPGA design, however, is very low. FPGA design is very time consuming and requires low-level hardware design skills. This study investigated this FPGA design productivity problem and identified potential solutions that will provide revolutionary improvements in design productivity. Three research areas that must be addressed to achieve such improvements are significant improvement in reuse of FPGA circuits, identification and deployment of higher level design abstractions, and increasing the number of turns per day to significantly increase the number of design productivity can be increased by 25X over current practice. </li> <li>15. SUBJECT TERMS FPGA, design productivity, computer-aided design</li></ul> |                                     |                          |                                                          |                              |                                                    |                                                     |  |

| 16. SECURITY CLASSIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     | 17. LIMITATION           | 18. NUMBER                                               |                              |                                                    | PONSIBLE PERSON (Monitor)                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>:. THIS PAGE</b><br>Unclassified | OF ABSTRACT:<br>SAR      | <b>OF PAGES</b><br>60                                    | Alfred<br>19b. TELEPH<br>N/A |                                                    | rpelli<br>UMBER (Include Area Code)                 |  |

Г

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std. Z39-18

## **Table of Contents**

|               | es                                                      |    |

|---------------|---------------------------------------------------------|----|

| List of Table | 2S                                                      | iv |

| Acknowledg    | ement                                                   | V  |

| 1 Executi     | ve Summary                                              | 1  |

|               | ound                                                    |    |

|               | GA Devices                                              |    |

|               | GA Use Models                                           |    |

| 2.3 Co        | nventional FPGA Design Methodology                      |    |

| 2.3.1         | Algorithm Development                                   |    |

| 2.3.2         | Architecture Exploration                                |    |

| 2.3.3         | Register Transfer Level (RTL) Design                    | 6  |

| 2.3.4         | Technology Mapping                                      |    |

| 2.3.5         | Verification                                            | 7  |

| 2.3.6         | Run-Time Support                                        | 7  |

| 2.3.7         | Detailed FPGA Design Flow                               | 7  |

| 2.3.8         | Limitations of Existing Tools                           |    |

|               | torical Perspective                                     |    |

| 3 Product     | ivity Model                                             | 13 |

| 3.1.1         | Design Time                                             | 13 |

| 3.1.2         | Number of Turns Required to Complete a Design           |    |

| 3.1.3         | Effect of Reuse on Design Time                          | 14 |

| 3.1.4         | A Final Model                                           | 15 |

| 4 Researc     | h Approaches                                            | 16 |

| 4.1 Rev       | 1se                                                     | 16 |

| 4.1.1         | Library Reuse Infrastructure                            |    |

| 4.1.2         | Architecture Shaping Through Library Standards          |    |

| 4.1.3         | Dual Layer Compilation                                  |    |

| 4.1.4         | Interface Synthesis                                     |    |

| 4.2 Ab        | straction                                               |    |

| 4.2.1         | Parallel Languages and Concurrent Models of Computation |    |

| 4.2.2         | Multi-FPGA Synthesis and Compilation                    |    |

| 4.3 Tu        | ns Per Day                                              |    |

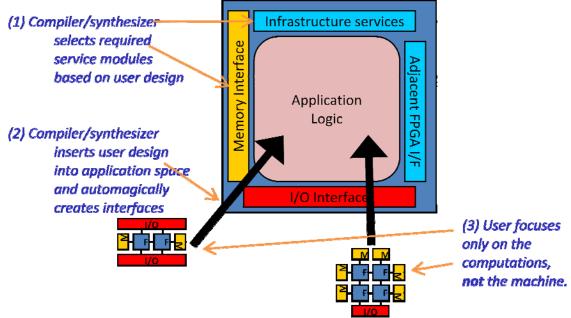

| 4.3.1         | Standard Platform Services                              |    |

| 4.3.2         | Firmware                                                |    |

| 4.3.3         | High-Level Abstraction Debug                            |    |

| 4.3.4         | Summary of Research Approaches                          |    |

| 5 Integra     | ed Research Vision                                      |    |

| 6 Referen     | ices                                                    |    |

| Appendix      |                                                         |    |

|               | ey of Hardware Metrics                                  |    |

|               | of Commercially Available High-Level FPGA Design Tools  |    |

| A.3 FPG       | A Architecture Survey                                   |    |

# List of Figures

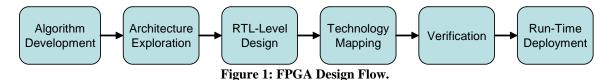

| Figure 1: FPGA Design Flow.                                                          | 6  |

|--------------------------------------------------------------------------------------|----|

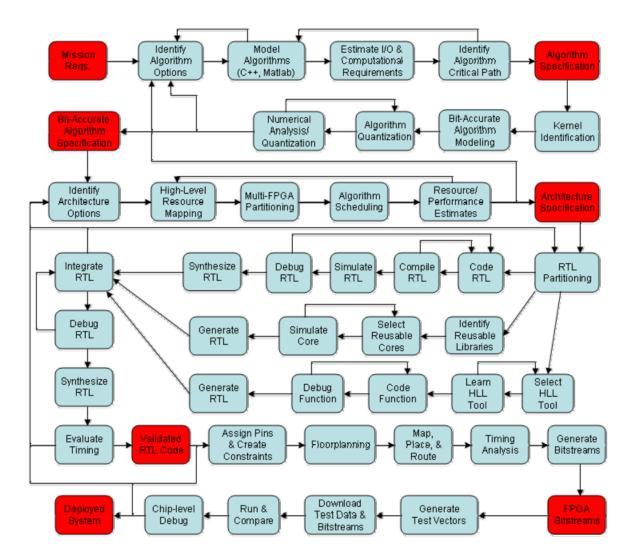

| Figure 2: Detailed FPGA Design Methodology.                                          | 8  |

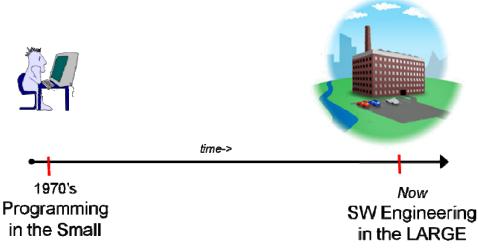

| Figure 3: The Fundamental Shift in Software Development Environments                 | 11 |

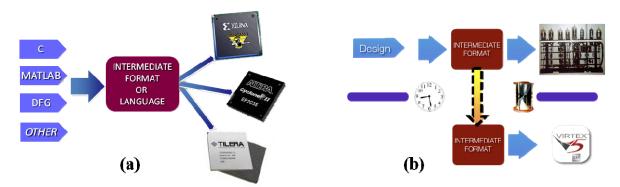

| Figure 4: Two Key Benefits of Hardware Reuse: (a) The Ability to Retarget other      |    |

| Devices, and (b) Mitigation of Obsolescence.                                         | 18 |

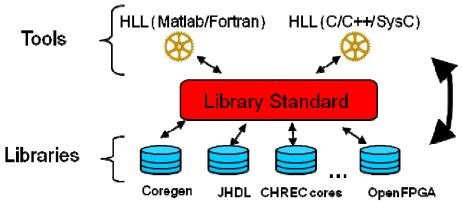

| Figure 5: Library Standard for Reusable FPGA Libraries                               | 19 |

| Figure 6: CORBA-Like Flow for Reconfigurable Computing.                              | 19 |

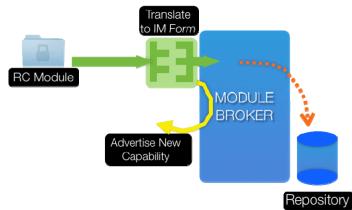

| Figure 7: Catalytic Impact of Architecture Shaping and Leveraging Library Standards. | 21 |

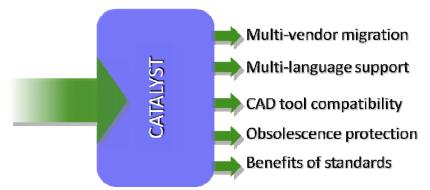

| Figure 8: An Outline of the Dual-Layer Compilation Work of the Reservoir Labs R-     |    |

| Stream Project                                                                       | 23 |

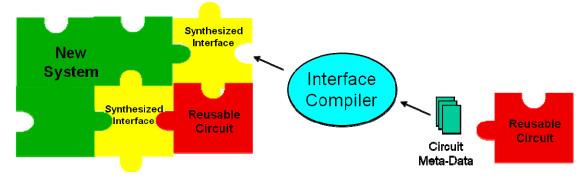

| Figure 9: The Primary Challenge of Integrating Reusable Components is Creating a     |    |

| Custom Interface                                                                     | 24 |

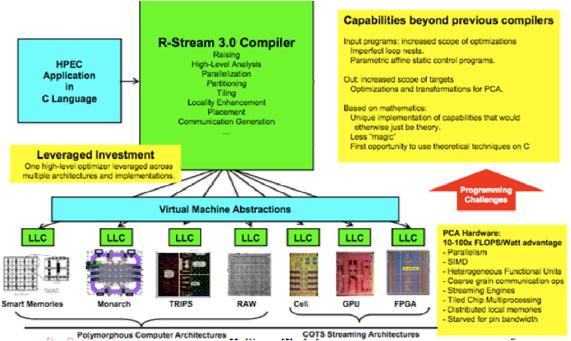

| Figure 10: An Interface Compiler Would Assume the Task of Creating the Logical       |    |

| Interface for a Reusable Component, and Integrate it into an Existing Design         | 24 |

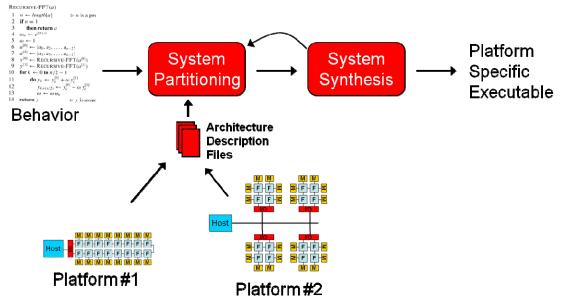

| Figure 11: Multi-FPGA Design Environment.                                            | 28 |

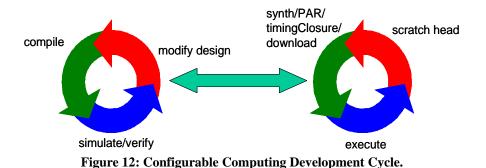

| Figure 12: Configurable Computing Development Cycle.                                 | 29 |

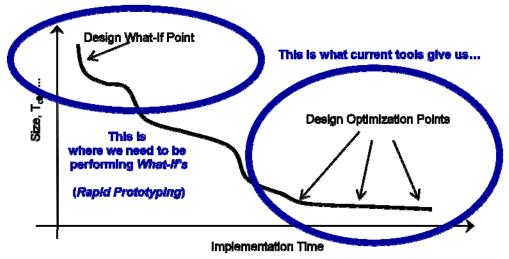

| Figure 13: CAD Tools and Design "What-If Experiments"                                |    |

| Figure 14: Sparse Infrastructure for Configurable Computing Systems                  | 30 |

| 8 · · · · · · · · · · · · · · · · · · ·                                              | 31 |

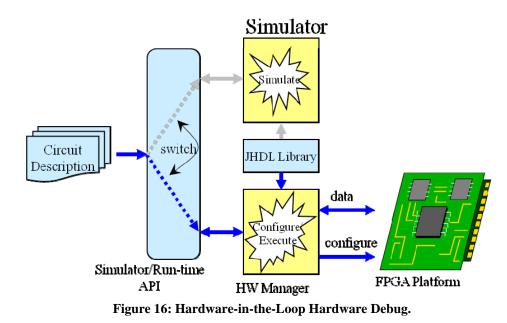

| Figure 16: Hardware-in-the-Loop Hardware Debug.                                      | 32 |

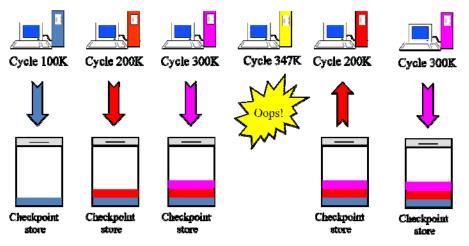

| Figure 17: Checkpointing of Hardware Computations                                    | 32 |

| Figure 18: RC Firmware.                                                              |    |

| Figure 19: Multiple Design Databases in Typical FPGA Design Flow                     |    |

| Figure 20: Unified Database for Cross Tool Linking.                                  |    |

| Figure 21: Relationship between Research Approaches                                  |    |

| Figure 22: Integrated Research Vision.                                               | 38 |

## List of Tables

| Table 1: Density and Capability of Future FPGA Technologies |  |

|-------------------------------------------------------------|--|

| Table 2: Research Thrusts and Models                        |  |

# Acknowledgement

The authors gratefully acknowledge the support of DARPA/IPTO under contract FA8650-07-C-7745 and administered by AFRL/RYDI.

## 1 Executive Summary

The importance of Field Programmable Gate Arrays (FPGAs) for Department of Defense systems is well understood. The Special Technology Area Review (STAR) on FPGAs, for example, clearly indicates that FPGAs are a crucial electronic component in many DoD electronic systems (1). The report indicates that FPGAs will be used within many DoD systems for some time and will likely grow in importance as the performance and architectures of FPGAs improve. FPGAs are used within DoD for the same reasons they are used in commercial systems: reduced time to market, lower NRE costs, infield programmability, lower design and validation costs, and rapid prototyping. FPGAs also offer significant processing performance – by creating custom circuits optimized for a specific application, FPGAs can perform computations much more efficiently than other conventional forms of computing.

Several FPGA architecture trends suggest that FPGAs will become more important in the future. First, FPGAs are closely following Moore's law and are benefiting from the increased logic density available with new process technologies. Second, FPGAs are continually adding more system level functionality such as advanced I/O standards, bus interfaces, and memories. Third, FPGAs are integrating a variety of heterogeneous processing elements such as DSP processors, programmable processors, and computing elements. Fourth, FPGAs are providing multiple processors (both hard and soft) that can be organized into chip-level multiprocessing. This growing density, raw computational throughput, and system functionality suggests that FPGAs will play an increasingly important role in future DoD systems.

While FPGAs provide many benefits, the effort and skill required to create working FPGA designs is growing and consumes significant design resources during system development. The inability to create FPGA designs more productively limits the ability to exploit the growing density, capability, and performance potential of modern FPGA architectures. In fact, one of the key recommendations of the STAR report is the need to address the science and technology gap that includes the advancement of electronic design automation (EDA) for FPGAs. Unless significant advances in FPGA design productivity are made, the full benefits of FPGAs cannot be realized.

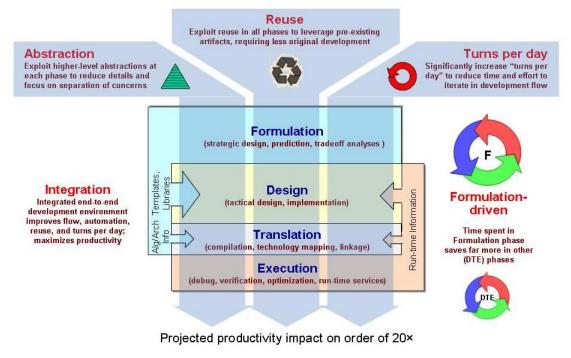

The objective of this effort was to investigate the *full* FPGA tool flow and identify potential solutions at all stages of the tool flow that will provide *revolutionary* improvements in design productivity. In the course of this study we have identified several key challenges limiting design productivity and identified several critical technical research focus areas to address the FPGA design productivity problem. This report summarizes our recommendations and proposes a research plan for solving the most important design productivity challenges. We believe that revolutionary advances can be made in FPGA design productivity with adequate investment in the research areas presented in this report.

The following section (Section 2) summarizes the background material and historical context for both FPGA design and software programming. Section 3 will introduce several metrics and present our "productivity model". This model will be used to identify the most promising approaches for improving design productivity. Section 4 will present the most promising approaches we have identified during the study that we believe will

lead to revolutionary improvements in design productivity. Section 5 will conclude the report by presenting an integrated research vision that summarizes the vision from this study and the study conducted by the companion team made up from members of the National Science Foundation Center for High-Performance Reconfigurable Computing (CHREC).

## 2 Background

### 2.1 FPGA Devices

FPGA design productivity is limited by the so called design productivity gap (2). Silicon density continues to double every 1.5 to 2 years while design capabilities are growing at a much slower rate. Design productivity must improve at a rate similar to Moore's Law just to keep from falling behind. While incremental improvements in design productivity are being made, the rate of growth in design productivity is much lower than Moore's law resulting in increasing design times for each new FPGA generation. Significant effort and investment in design techniques and methods are necessary for closing this design productivity gap.

Most of the largest FPGA devices available today are built using 65 nm technology<sup>1</sup>. These modern FPGAs contain a tremendous amount of logic, computation, and memory resources and can be used for a variety of high-speed digital systems and high-performance computing applications. The growth in density and capability of FPGAs will undoubtedly continue in the future. Table 1 suggests the resources that may become available on future FPGA devices using newer fabrication technologies. If FPGA density keeps pace with Moore's law, we expect the largest FPGAs in a 22 nm technology to contain almost 3 million look-up tables, several thousand dedicated multiplier/DSP blocks, and up to 100Mb of internal memory.

| Year | LUTs                 | DSPs                          | Memory                                   |

|------|----------------------|-------------------------------|------------------------------------------|

| 2007 | 340 k                | 500                           | 10 Mbit                                  |

| 2010 | 700 k                | 1000                          | 21 MBit                                  |

| 2013 | 1,400 k              | 2000                          | 42 MBit                                  |

| 2016 | 2,900 k              | 4300                          | 89 MBit                                  |

|      | 2007<br>2010<br>2013 | 2007340 k2010700 k20131,400 k | 2007340 k5002010700 k100020131,400 k2000 |

Table 1 - Density and Capability of Future FPGA Technologies

While the density of future FPGAs will certainly increase, it is likely that the architecture of future FPGAs will continue to evolve. As more transistors become available, it is likely that the logic and computing resources will become coarser grain and more "hard-core" resources (such as PCI express) will be added to keep up with the latest and highest speed I/O interfaces. We also expect that a variety of new FPGA device families will be introduced to address the needs of specific markets. As such, FPGAs will present a moving target to Computer Aided Design (CAD) tools and we believe it will become increasingly difficult to address the gap between FPGA design productivity and FPGA circuit density.

## 2.2 FPGA Use Models

There has been considerable interest by non-traditional circuit designers to use and "program" FPGAs. These application experts and programmers recognize the benefits of FPGAs and seek ways to exploit the efficiency, reprogrammability, and computational density of FPGAs for their application-specific problems. These non-traditional FPGA programmers come from a variety of backgrounds including signal processing, embedded

<sup>&</sup>lt;sup>1</sup> Altera announced the introduction of the first 40-nm FPGA (Stratix IV) on May 19, 2008.

systems, communications, and high-performance computing. These experts, however, do not have the traditional digital design skills to effectively "program" the FPGA using existing FPGA design tools.

The wide variety of users interested in using FPGAs suggests that new design methods and techniques are needed for FPGA design. We introduce the concept of an FPGA "use model" and define a number of "use models" to clarify the design issues that face FPGA designers and non-traditional FPGA programmers. Each model has a different set of design challenges, design constraints, and programming environments. While we have identified a variety of unique FPGA use models, we will focus on two FPGA use models for this report: *ASIC replacement* and *Configurable Computing*.

**ASIC Replacement** is the most common FPGA use model. In this use model, FPGA devices are used to perform general purpose digital functions that might otherwise be performed in a custom integrated circuit (i.e., the FPGA is used to replace an ASIC). In this use model, the behavior and timing of the FPGA are specified in great detail including clock-cycle accuracy of the interfaces and internal logic. The design goal is to minimize cost (i.e., optimize hardware) and validate circuit functionality (including meeting timing constraints). The design is optimized in a way that allows the least expensive FPGA device to be used in the system. ASIC replacement applications typically involve the design of custom PC boards onto which the FPGA is placed, custom I/O interfaces, custom clocking requirements, etc. Much of the design activity involves creating the register transfer level implementation from some detailed system specification.

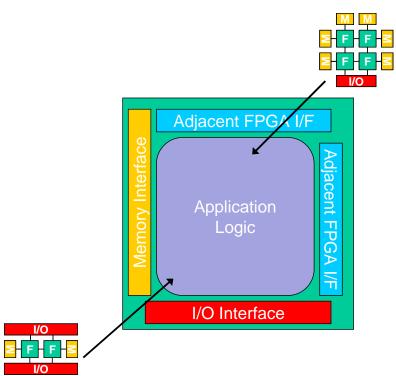

*Configurable computing* is an FPGA use model in which FPGA devices are used to perform application specific *computation*. The large amount of logic resources available in modern FPGAs allows complex calculations and application-specific computations to be performed more efficiently and often with higher performance than more traditional CPU-based architectures (3). Standard platforms and boards are most often used for configurable computing to simplify the design process and facilitate reuse. When mapping a computation onto a configurable computing machine (CCM) the goal is often to get the design to fit into the available FPGA(s) as quickly as possible rather than to optimize the design down to the last gate.

The configurable computing use model has been applied in both high-performance computing (HPC) environments as well as high-performance *embedded* computing (HPEC). In both cases, FPGA designs are created on a standard platform to accelerate an application-specific computation. Unlike the FPGAs in an ASIC replacement use model, the FPGAs in configurable computing are reused for multiple computations. Because the FPGAs are reused and many FPGA designs created for a single design platform, design productivity is far more important for the configurable computing use model than for ASIC replacement.

Several *emerging* FPGA use models are being developed to facilitate the design of FPGAs in a variety of vertical markets. Many FPGAs are now used for Digital Signal Processing (DSP) and stream-based processing. A variety of new design methods are available for simplifying the design of FPGAs by DSP programmers (4). With embedded processor cores available within FPGAs, complex system-on-chip designs can be created within an FPGA. Design methods customized for SOC design have also been created for

FPGAs (5). Many other use models have been developed for a variety of applicationspecific tasks including networking (6), string matching (7) and many others.

A key reason design productivity for configurable computing is so poor is that that the design methods used in configurable computing are primarily the low-level design methods developed for the ASIC replacement use model. The design of configurable computing "programs" is essentially circuit design – low-level digital design methods such as RTL design are used to define complex computation and behavior. In fact, most of the design processes in contemporary configurable computing have direct counterparts in ASIC design (8). ASIC replacement design methods are insufficient for configurable computing and new methodologies are needed to improve design productivity. Development environments are needed for FPGA design that more closely resemble the development environments of traditional programmers and application developers.

While the development environments used by traditional programmers are varied, they possess a number of common traits. First, the languages used are abstract enough that a developer can create code with limited exposure to the underlying hardware structures. Second, developers expect a development environment consisting of compilers, extensive libraries of reusable functions, linkers, loaders, profilers, and symbolic debugging tools. Third, developers expect to work in an interactive development environment where the delay from compilation to debug on the target platform is measured in seconds or minutes, and the creation of *what-if* scenarios during the debug process is simple and efficient.

In contrast, development environments for FPGAs remain primitive by these standards. Developing for FPGAs currently requires detailed knowledge of the target chip's structure, capacity, and capabilities. Little in the way of reusable IP is available and logic analyzers and logic probes remain the key tools for the debug of most FPGA-based designs. Finally, FPGA development tool chains are batch-oriented rather than interactive with compile/link/execute timeframes measured in hours or days rather than seconds or minutes. Future advances in design productivity for FPGAs must significantly simplify the design/programming process of FPGAs for non-traditional FPGA users. In later sections of this report, our recommendations divide broadly into the three categories highlighted in the previous two paragraphs: abstraction, reuse, and development/debug environments.

We have focused our study on technologies and design methods that improve design productivity for *configurable computing* rather than for *ASIC replacement* or any of the other emerging use models. We believe that there is great potential for improving the design productivity for configurable computing and that with sufficient investment in a number of important technical areas, revolutionary improvements in design productivity for configurable computing are possible. While the techniques and ideas we present in this report are targeted towards configurable computing, we believe that many of these ideas can be successfully applied to the ASIC replacement use model and that some improvements in ASIC replacement design productivity are also possible.

### 2.3 Conventional FPGA Design Methodology

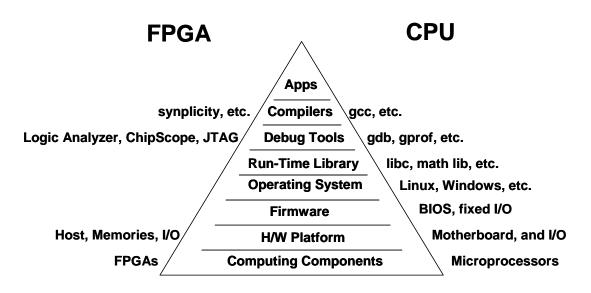

Before suggesting potential solutions to the FPGA design problem, it is useful to discuss the various phases of the conventional FPGA design methodology (i.e., design methodology used in the ASIC replacement use model). Furthermore, it is helpful to contrast these steps with the conventional software development process to highlight the added time, skill, and cost associated with FPGA design. Six broad design steps are highlighted in Figure 1 below and will be described in more detail.

#### 2.3.1 Algorithm Development

Algorithm development is the process of creating and defining the behavior of the algorithm or computation that is intended for the FPGA. This is usually performed in a conventional programming language and tested using a variety of tools and software test benches. This step is common when targeting any computing platform including FPGAs, supercomputers, conventional microprocessors, etc. The focus of this step is to refine the algorithm rather than address implementation specific design details.

#### 2.3.2 Architecture Exploration

Once an algorithm has been defined and verified, it must be targeted to a specific computing architecture. This task is broadly called architecture exploration and is unique for application-specific computing architectures including FPGAs. This step involves the creation of a unique, specialized computing architecture for the computation of interest. There is a very large design space for implementing these architectures and the primary challenge in this step is to identify the lowest cost architecture (size, power, etc.) that meets the computational constraints in as little time as possible. In most cases, this architecture exploration is performed manually by experienced design engineers<sup>2</sup>. This step is not necessary for software development as the hardware architecture is fixed.

### 2.3.3 Register Transfer Level (RTL) Design

Once an architecture has been identified for a computation, the architecture must be described using register transfer level design languages such as VHDL and Verilog. This process is not straight forward and requires the designer/programmer to explicitly schedule operations in time, allocate resources for these operations, and interconnect the resources. Further, the user must specify this architecture using hardware description languages that are unfamiliar to conventional programmers. While tools have recently been created that allow the description of these architectures in languages such as C, most of them require the programmer to be aware of architecture issues such as timing, parallelization, and resource allocation.

<sup>&</sup>lt;sup>2</sup> Several high-level synthesis tools perform architecture exploration manually but these tools are not yet widely adopted by the FPGA design community.

#### 2.3.4 Technology Mapping

After the design has been specified in a standard RTL-design language (or higherlevel C-based language), it must be *mapped* onto the resources of a specific FPGA. This step is broadly called technology mapping and involves the *mapping* of logic to specific FPGA resources, the *placement* of these resources to specific locations within the device, the *routing* of signals between resources, and the generation of FPGA-specific programming bitfiles. Technology mapping is very time consuming – complex optimization algorithms are used to find acceptable logic placement and routing. As the size of FPGAs grows exponentially, the amount of time required for placement and routing grows significantly. An important limitation of FPGA design productivity is the long time required for place and route.

Unlike conventional software development, where compilation occurs in a matter of minutes, FPGA technology mapping may take many hours or days to complete for a complex design. As the density of FPGAs continues to grow exponentially, the time required for this technology mapping will grow to an unacceptable point. Technology mapping time must be reduced to improve FPGA design productivity for configurable computing systems.

#### 2.3.5 Verification

After the computation has been mapped to an architecture and translated into an FPGA circuit, its proper functionality must be verified against the original algorithm description. Verification and debug is much more complicated on FPGA-based systems than conventional software because of the limited visibility within FPGAs, lack of control during execution, and the primitive interfaces and tools available for FPGA-based verification. If there are design errors within an FPGA-based computing system, it is significantly more difficult and time consuming to identify and resolve these problems than with conventional software tools.

#### 2.3.6 Run-Time Support

The final step in the design and "deployment" of FPGA-based systems is providing appropriate run-time support. Unlike conventional processor-based architectures, there is limited support for the loading and managing of FPGA-based computations and interfacing these computations/architectures with conventional processor-based architectures. In most cases, ad-hoc or proprietary interfaces are used for each computing system adding significant time and cost to FPGA-based system design.

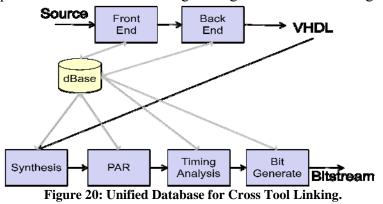

#### 2.3.7 Detailed FPGA Design Flow

A more detailed diagram of the FPGA design flow is shown below in **Figure 2**. While the details of the design methodology are not important for this discussion, there are several observations that are worth emphasizing. First, there are many different activities required to create a valid FPGA design. These design steps require a variety of skills and tools to translate a high-level algorithm into a working FPGA system. FPGA designers must be skilled in each of these steps and tools to effectively create valid FPGA designs. Second, there are many feedback loops in the design process that require iteration, repair, and debugging. Iterations at all levels of the design flow are expected

and multiply the amount of time required to create a valid design. Performing these design iterations significantly increases the overall FPGA design time.

## 2.3.8 Limitations of Existing Tools

Design tools for FPGAs continue to improve and provide the essential design support needed to create designs for today's large, complex, and heterogeneous FPGAs. These tools support the new features found in FPGA architectures and provide the capability to map complex designs to the largest available FPGAs. In addition, a variety of new design abstractions have been introduced to support new users of FPGA. These design abstractions include system on a chip design tools for embedded systems designers, signal flow graph tools for DSP engineers, and even C-based hardware compilers for algorithm experts.

Figure 2: Detailed FPGA Design Methodology.

In spite of these improvements, FPGA designers frequently complain about the design tools. Improvements in FPGA design tools do not seem to keep up with the needs

of the designers. The major limitations of the tools for traditional FPGA designers using FPGAs as an "ASIC replacement" include the following:

- Long place and route times,

- Difficulty meeting timing constraints,

- Difficulty verifying complex designs, and

- Inadequate design abstractions.

The tools for designers using FPGAs primarily for computation (i.e., the configurable computing use model) are primitive compared to traditional software development environments. As described earlier, these designers must use "ASIC" design tools to create computing circuits. There is a large mismatch between the background and skills of the algorithm expert and the current design entry tools required for FPGA design.

While new tools and abstractions for FPGAs are being introduced, these tools have not fundamentally changed the difficulty of FPGA design. In some cases, these new abstractions are not much different from traditional ASIC design and require the programmer to understand clocks, timing, and other low-level digital design concepts. In other cases, the abstractions are too restrictive and limit the ability of the synthesis tools to generate high-quality circuits (i.e., using sequential programming languages to specify concurrent hardware). In summary, the design of FPGA-based computing systems requires a variety of steps that each takes a large amount of time. Significant improvements in design productivity are only possible by addressing each of these steps and integrating these improvements into a cohesive design flow.

#### 2.4 Historical Perspective

While current design methods for configurable computing closely resemble the design methods for ASIC replacement, the design goals and constraints of configurable computing are more closely related to traditional software development. In traditional software design, the programmer specifies high-level behavior and relies on optimizing compilers, profilers, debuggers, and other tools to automatically translate the behavioral description into an efficient implementation. Ideally, FPGA design for the configurable computing use model should look the same – programmers specify behavior in some high-level specification and use a variety of tools to translate this behavior into an efficient implementation onto the FPGA or configurable computing machine. Programmers should *not* be required to learn entirely new tool flows or become FPGA designers to successfully create FPGA circuits on reconfigurable platforms.

In the course of this study, the investigators regularly used software and the stateof-the-art in software productivity as the yardstick to measure various aspects of FPGA productivity. This was done for a few key reasons. First, there are many similarities between software development and FPGA design for computational problems. Since software environments are generally considered more mature than reconfigurable computing environments, this seems to be a good choice for longer-term trend analysis. Secondly, software productivity has progressed dramatically in nearly a half century. It would be a tremendous success if improvements in FPGA productivity could be aligned to the same productivity curves as software.

After reviewing the history of software productivity, the team noted that there have been three notable milestones, or *inflection points* in the course of software evolution that had significantly impacted software productivity. These are:

- 1. The introduction of standard languages and compilers that promoted platform independence and code reuse (namely, the wide acceptance of FORTRAN and related languages).

- 2. The introduction of the linker, which in turn has lead to the preponderance of reusable code libraries.

- 3. Addressing human factors in software development by providing rich debugging environments and rapid turn-around for "what-if" development.

Computer programming started as a craft as computers became relevant in society in the 1960s. Computer programming evolved into a science as more programming languages were developed for a variety of domain specific purposes. In the 1980s it evolved into an engineering discipline as quality and scale became dominant issues. With each successive transition, productivity was improved.

Software productivity has increased steadily since the 1960s. Early on, microcoding was the dominant programming approach. As more convenient machine (processor) structures emerged, assembly languages provided machine abstraction that improved productivity by over an order of magnitude. Then as programming domains such as business and scientific applications were established, third generation languages (3GL) like Cobol and Fortran with control and data flow abstractions led to another order of magnitude improvement in programmer productivity.

In 1970, COBOL was the state of the art, mainframes were in vogue and the personal computer had not hit the market. By the early 1980s, it was clear that software productivity was a key bottleneck in many systems development efforts. In 1986, the Software Productivity Consortium (SPC) and the Software Engineering Institute (SEI) were formed to address the problem. Key areas like fourth generation languages (4GL) and fifth generation languages (5GL) were studied and some progress was made in specific domains where the workflow constructs could be aligned with computing capabilities. Much of the focus at these and other research organizations was on software reuse and integrated development environments. The SEI also started a program in software process that addressed process improvement.

Software environments also underwent a significant structural change since the 1960s. In the 1960s, software tools focused on a model centered on the individual. Code entry, compilation and debugging centered on the capabilities and limitations of individuals, and programming teams were comprised of individualistic effort. Since then, there has been a major shift in this model to now focus on enterprise-level development with philosophical changes encompassing, code lifetime, reuse, verification and deployment (see Figure 3). *Routine coding projects undertaken in today's software engineering environments could not have been accomplished using coding environments of the past.*

Figure 3: The Fundamental Shift in Software Development Environments.

Because of the close relationship between configurable computing design and software programming, it is instructive to look at the major innovations in software productivity over the last fifty years. *We believe that the current design tools and methods for configurable computing are still primitive and resemble the software practices of the 1960s.* Software productivity has progressed dramatically in the past half century and these improvements hold important insights for the configurable computing community. Many of the improvements in software productivity can be applied to configurable computing. The major advances in software productivity can be categorized into one of four different groups:

- 1. **Increased Abstraction**. Major improvements in programmer productivity have been realized by introducing new languages and design methods that reduce the amount of detail required by the programmer. The transition from machine code to assembly language and from assembly language to 3<sup>rd</sup> generation languages (9) allowed programmers to create complex programs without understanding low-level details of the microprocessor architecture.

- 2. **Reusable Artifacts**. An important way of improving software productivity is reusing previously created software artifacts (10). There are many levels of software reuse including reuse of applications, concepts, libraries, design patterns, and portable programs. The recent growth in reusable software components for web-based applications such as web services demonstrates the potential improvements in productivity through reuse.

- 3. **Software Process**. Recognizing that most early software development was done in an ad-hoc manner, new software processes were developed to improve productivity. Productivity improvements of 20% 40% have been demonstrated for small software projects and up to 500% for large software projects (11) (12).

- 4. Automation. Automating tedious tasks played an important role in improving productivity (13). Tools to automate and integrate a variety of tasks have reduced errors and sped software development by over 30%.

As suggested above, configurable computing systems have yet to enjoy even the most basic productivity benefits demonstrated by software. While there are some encouraging signs of progress with new languages and compilation tools, contemporary FPGA design more closely resembles the lowest-level machine code programming of the very earliest computer systems. Significant advances in each of the four areas above are necessary for FPGA design in configurable computing systems to enjoy the benefits in productivity that were demonstrated by traditional software systems.

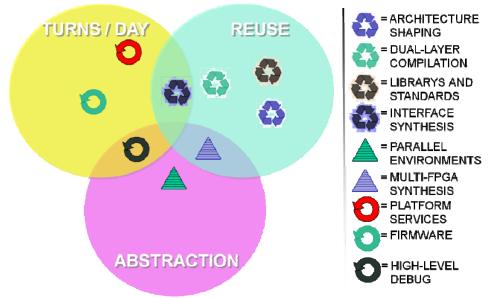

Using advances in software productivity as a guide, we have identified three broad technical areas that are most promising for configurable computing design productivity: *reusing artifacts, raising design abstractions,* and *increasing the interactivity and debug infrastructure* (i.e., "turns per day"). Software productivity has made *significant* advances in the last fifty years by making many advances in each of these areas. These areas of productivity are interrelated and design productivity will significantly increase if advances are made in each of these areas and applied at all levels of the design methodology.

## **3** Productivity Model

Before suggesting approaches and techniques for improving design productivity, we must have a clear definition and measure of design productivity. Closely related to the idea of design productivity are metrics for measuring design productivity. An appendix of this report (see Section 0) contains a sampling of papers we identified in the literature and which illustrate the state of the art in hardware design metrics. In essence, we found two kinds of hardware productivity metrics in the literature. The first and most common relates to input lines of source code created per day and is essentially an attempt to capture the amount of circuitry created per day. A second metric is the ratio of the utility of the system divided by its cost. While this latter metric is a more powerful metric and allows us to capture a variety of characteristics of the design process beyond simply circuitry created per day, we feel that the state-of-the-art in configurable computing design is such that we are not ready for this more complex metric, but prefer to use a simpler metric as a way of exposing what we view to be the most pressing problems in configurable computing design.

During the course of this study we developed a productivity model to guide our investigation (14). Models have limitations and the model we propose is no exception. It is not meant to predict the precise design time required for a given application or design. Rather, it is more qualitative in nature and points out what we believe to be the first-order contributors to design productivity and their inter-relationships.

Our first measure of design productivity is simply the rate at which hardware is developed:

$$DesignProductivity = \frac{CC}{DesignTime}.$$

(1)

Here, *CC* represents the *circuit complexity* of the final design, as measured in gates, LUTs, transistors, etc. The output of hardware design is hardware, a physical artifact that can be measured and that has quantifiable costs in several dimensions (silicon area, power, etc.). Unlike software, our model does not measure the *input* of the design process (i.e., lines of code/day) but rather the physical *output* of the design process (the amount of circuitry produced).

#### 3.1.1 Design Time

The majority of the effort required to complete a hardware design is spent in debug and verification, with values in the 70% range being common. Thus, design time for configurable computing applications strongly depends on the number of design turns required to complete the verification of the design, and the ease with which those design turns can be completed. The design time is proportional to the number of design "turns" and can be approximated as:

$$Days = \frac{Turns}{TPD} , \qquad (2)$$

where, *Turns* is the total number of design iterations required and *TPD* is "turns per day" (debug iterations per day).