# **AFRL-IF-WP-TR-2002-1505**

ON-LINE TESTING AND

RECONFIGURATION OF FIELD

PROGRAMMABLE GATE ARRAYS

(FPGAs) FOR FAULT-TOLERANT (FT)

APPLICATIONS IN ADAPTIVE

COMPUTING SYSTEMS (ACS)

Miron Abramovici

Lucent Technologies, Inc. Circuits & Systems Research Laboratory Agere Systems 600 Mountain Avenue Murray Hill, NJ 07974

John M. Emmert and Charles E. Stroud

Department of Electrical & Computer Engineering University of North Carolina at Charlotte 9201 University City Blvd. Charlotte, NC 28223

**APRIL 2002**

**Final Report for 01 May 1998 – 30 April 2002**

Approved for public release; distribution is unlimited.

INFORMATION DIRECTORATE

AIR FORCE RESEARCH LABORATORY

AIR FORCE MATERIEL COMMAND

WRIGHT-PATTERSON AIR FORCE BASE, OH 45433-7334

## **NOTICE**

USING GOVERNMENT DRAWINGS, SPECIFICATIONS, OR OTHER DATA INCLUDED IN THIS DOCUMENT FOR ANY PURPOSE OTHER THAN GOVERNMENT PROCUREMENT DOES NOT IN ANY WAY OBLIGATE THE US GOVERNMENT. THE FACT THAT THE GOVERNMENT FORMULATED OR SUPPLIED THE DRAWINGS, SPECIFICATIONS, OR OTHER DATA DOES NOT LICENSE THE HOLDER OR ANY OTHER PERSON OR CORPORATION; OR CONVEY ANY RIGHTS OR PERMISSION TO MANUFACTURE, USE, OR SELL ANY PATENTED INVENTION THAT MAY RELATE TO THEM.

THIS REPORT HAS BEEN REVIEWED BY THE OFFICE OF PUBLIC AFFAIRS (ASC/PA) AND IS RELEASABLE TO THE NATIONAL TECHNICAL INFORMATION SERVICE (NTIS). AT NTIS, IT WILL BE AVAILABLE TO THE GENERAL PUBLIC, INCLUDING FOREIGN NATIONS.

THIS TECHNICAL REPORT HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION.

LT JASON LAWSON

Project Engineer

KENNETH LITTLEJOHN, Jeam Leader

Embedded Info Sys Engineering Branch

Information Technology Division Information Directorate

JAMES S. WILLIAMSON, Chief Embedded Info Sys Engineering Branch Information Technology Division Information Directorate

Do not return copies of this report unless contractual obligations or notice on a specific document require its return.

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YY)               | 2. REPORT TYPE                                     | 3. DATES COVERED (From - To)                   |  |  |  |

|-----------------------------------------|----------------------------------------------------|------------------------------------------------|--|--|--|

| April 2002                              | Final                                              | 05/01/1998 - 04/30/2002                        |  |  |  |

| 4. TITLE AND SUBTITLE                   |                                                    | 5a. CONTRACT NUMBER                            |  |  |  |

| ON-LINE TESTING AND RECONFICE           | GURATION OF FIELD PROGRAMMABLE                     | F33615-98-C-1318                               |  |  |  |

| GATE ARRAYS (FPGAs) FOR FAUL            | T-TOLERANT (FT) APPLICATIONS IN                    | 5b. GRANT NUMBER                               |  |  |  |

| ADAPTIVE COMPUTING SYSTEMS              | (ACS)                                              | 5c. PROGRAM ELEMENT NUMBER                     |  |  |  |

|                                         |                                                    | 69199F                                         |  |  |  |

| 6. AUTHOR(S)                            |                                                    | 5d. PROJECT NUMBER                             |  |  |  |

| Miron Abramovici (Lucent Technologie    | es, Inc.)                                          | ARPI                                           |  |  |  |

| John M. Emmert (University of North O   | Carolina at Charlotte)                             | 5e. TASK NUMBER                                |  |  |  |

| Charles E. Stroud (University of North  | Carolina at Charlotte)                             | FT                                             |  |  |  |

| Charles 2. Survive (Chryelsky of Tyorki | Curonna at Charlotte)                              | 5f. WORK UNIT NUMBER                           |  |  |  |

|                                         |                                                    | 03                                             |  |  |  |

| 7. PERFORMING ORGANIZATION NAME         | 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) |                                                |  |  |  |

| Lucent Technologies, Inc.               | Department of Electrical & Computer                |                                                |  |  |  |

| Circuits & Systems Research Laborator   | y Engineering                                      |                                                |  |  |  |

| Agere Systems                           | University of North Carolina at Charlotte          | ;                                              |  |  |  |

| 600 Mountain Avenue                     | 9201 University City Blvd.                         |                                                |  |  |  |

| Murray Hill, NJ 07974                   | Charlotte, NC 28223                                |                                                |  |  |  |

| 9. SPONSORING/MONITORING AGENCY NAM     | IE(S) AND ADDRESS(ES)                              | 10. SPONSORING/MONITORING<br>AGENCY ACRONYM(S) |  |  |  |

| Information Directorate                 |                                                    | AFRL/IFTA                                      |  |  |  |

| Air Force Research Laboratory           |                                                    | AFKL/IF1A                                      |  |  |  |

| Air Force Materiel Command              |                                                    | 11. SPONSORING/MONITORING                      |  |  |  |

| Wright-Patterson Air Force Base, OH 4   | 5433-7334                                          | AGENCY REPORT NUMBER(S)                        |  |  |  |

|                                         |                                                    | AFRL-IF-WP-TR-2002-1505                        |  |  |  |

|                                         |                                                    |                                                |  |  |  |

#### 12. DISTRIBUTION/AVAILABILITY STATEMENT

Approved for public release; distribution is unlimited.

#### 13. SUPPLEMENTARY NOTES

Report contains color.

#### 14. ABSTRACT (Maximum 200 Words)

Adaptive computing systems (ACS) rely on reconfigurable hardware to adapt the system operation to changes in the external environment, and to extend mission capability by implementing new functions on the same hardware platform. This results in increased functional density and reduced power consumption – features very important in many domains, such as space missions or mobile devices. Field-programmable gate arrays (FPGAs) featuring incremental dynamic run-time reconfiguration (RTR) offer additional benefits by allowing the system to continue to execute uninterrupted, while portions of the FPGA are reconfigured for new logic functions. ACS are often deployed in harsh and/or hostile remote environments, and they are subject to strict high-reliability and high-availability requirements. Cosmic radiation may perturb the operation of a defect-free FPGA, and marginal defects not causing failures in manufacturing testing (such as a short initially having very high resistance) may become active with the aging of the device, or because of environmental factors. Since direct human intervention for maintenance and repair is impossible in such environments, fault-tolerant (FT) techniques resulting in graceful degradation must be used to achieve the desired mission life even in the presence of faults. However, traditional FT design, based on replicated modular redundancy and voting, is extremely expensive given the space, weight, and power constraints of ACS.

#### 15. SUBJECT TERMS

Formal Methods, FPGAs, Fault Tolerance, Adaptive Computing Systems, Reconfiguration, Run-Time, Testing, Diagnosis

| 16. SECURITY              | 6. SECURITY CLASSIFICATION OF:  |                              |                     | 18. NUMBER OF<br>PAGES | 19a. NAME OF RESPONSIBLE PERSON (Monitor)                                                 |

|---------------------------|---------------------------------|------------------------------|---------------------|------------------------|-------------------------------------------------------------------------------------------|

| a. REPORT<br>Unclassified | <b>b. ABSTRACT</b> Unclassified | c. THIS PAGE<br>Unclassified | OF ABSTRACT:<br>SAR | 84                     | 1st Lt. Jason Lawson<br>19b. TELEPHONE NUMBER (Include Area Code)<br>(937) 255-6548 x3586 |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std. Z39-18

# **Table of Contents**

| <b>Sectio</b> | <u>on</u>                                 | <u>Page</u> |

|---------------|-------------------------------------------|-------------|

| Table o       | of Contents                               | iii         |

| List of       | Figures                                   | iv          |

| List of       | Tables                                    | vi          |

| 1. Intro      | oduction                                  | 1           |

| 2. Mai        | n Contributions                           | 5           |

| <b>3.</b> The | Roving STARs                              | 7           |

| 3.1.          | The Test and Reconfiguration Controller   | 7           |

| 3.2.          | The Roving STARs Structure                | 7           |

| 3.3.          | The Roving Mechanism                      | 8           |

| 4. On-        | Line Testing and Diagnosis                | 11          |

|               | Basic BIST Structure                      |             |

| 4.2.          | Testing Programmable Logic Blocks         | 12          |

| 4.3.          | Divide-and-Conquer Adaptive Diagnosis     | 17          |

| 4.4.          | Locating Faulty PLBs Using BISTER Results | 19          |

| 4.5.          | Diagnosis within a Faulty PLB             | 26          |

| 4.6.          | Testing Interconnect                      | 29          |

| 4.7.          | Interconnect Diagnosis                    | 39          |

| 4.8.          | Fault Injection Emulation                 | 41          |

| 5. Faul       | t-Tolerant Techniques                     | 45          |

| 5.1.          | Basic Features                            | 45          |

| 5.2.          | Related Research                          | 46          |

|               | Multilevel Fault Tolerance Approach       |             |

| 5.4.          | Fault Tolerance for PLBs                  | 50          |

| 5.5.          | Fault Tolerance for Interconnect          | 55          |

| 5.6.          | Fault Tolerance Summary                   | 61          |

| 6. Sum        | mary and Conclusions                      | 63          |

| 7. Part       | icipants, Patents, and Publications       | 64          |

|               | rences                                    |             |

| List of       | Acronyms                                  | 73          |

# **List of Figures**

| <u>Figure</u> <u>I</u>                                                | <u>Page</u> |

|-----------------------------------------------------------------------|-------------|

| Figure 1. Roving Area Under Test Across the Chip                      | 1           |

| Figure 2. Horizontal and Vertical STARs                               |             |

| Figure 3. Roving Steps                                                |             |

| Figure 4. Basic BISTER Tile                                           |             |

| Figure 5. Integrated ORA/Scan cell                                    | 12          |

| Figure 6. Typical PLB Structure                                       |             |

| Figure 7. Configuration Multiplexer                                   | 13          |

| Figure 8. 3 by 2 BISTER Tile Rotations                                | 14          |

| Figure 9. 4 by 2 BISTER Tile Rotations                                |             |

| Figure 10. BISTER Tile Rotations (Two Faulty BUTs)                    | 15          |

| Figure 11. BISTER Tile Rotations (One Faulty BUT)                     | 15          |

| Figure 12. Layout of a BISTER Tile                                    |             |

| Figure 13. Example of Adaptive PLB Diagnosis                          | 18          |

| Figure 14. Example of Inconclusive Diagnosis                          | 18          |

| Figure 15. Combined test sessions a) 3 by 2 tile b) 4 by 2 tile       | 19          |

| Figure 16. Figure for Equation (1)                                    |             |

| Figure 17. Figure for Theorem 2                                       | 22          |

| Figure 18. Figure for Lemma 6                                         | 22          |

| Figure 19. Figure for Lemma 7                                         | 23          |

| Figure 20. Figure for Example 1                                       | 24          |

| Figure 21. Figure for Example 3                                       | 25          |

| Figure 22. Figure for Example 4                                       |             |

| Figure 23. Diagnosis of Actual Faulty PLB                             | 26          |

| Figure 24. ORA with Greater Diagnostic Resolution                     | 27          |

| Figure 25. PUB Diagnosis.                                             | 28          |

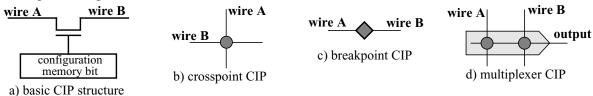

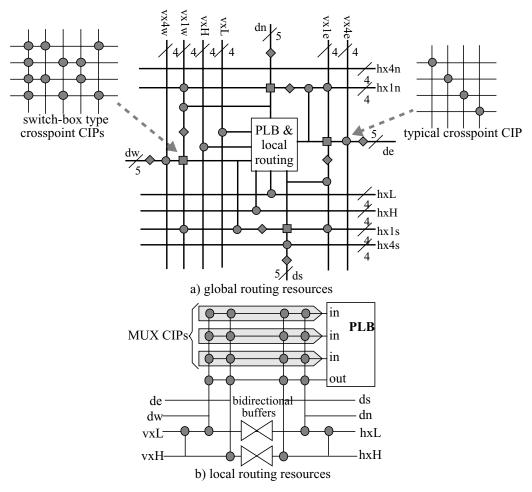

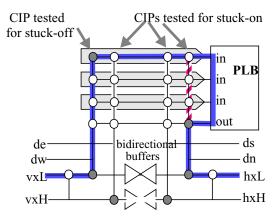

| Figure 26. CIP Structure and Types                                    |             |

| Figure 27. Single PLB View of Routing Resources                       |             |

| Figure 28. Basic BIST Structure for Interconnect                      | 32          |

| Figure 29. Bus Realignment                                            |             |

| Figure 30. Integrated ORA/scan cell                                   |             |

| Figure 31. Testing global crosspoint CIPs                             |             |

| Figure 32. Roving Order for Testing Interconnect                      |             |

| Figure 33. BISTER for Vertical Busses                                 |             |

| Figure 34. Example of Test Phases for Local Routing                   |             |

| Figure 35. Testing Crosspoint CIPs between Direct and Global Busses . |             |

| Figure 36. Example of MUX CIP Test Phases                             |             |

| Figure 37. Testing global crosspoint CIPs                             |             |

| Figure 38. Testing Results from Faulty ORCA 2C15s                     |             |

| Figure 39. Diagnostic Configurations                                  | 39          |

| Figure 40. Wire Segments and Faults                                   |             |

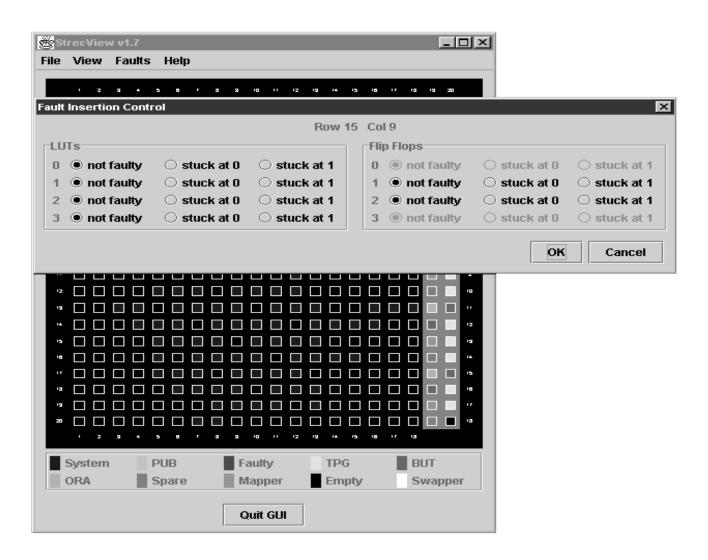

| Figure 41. TREC and fault injection emulations GUI                    |             |

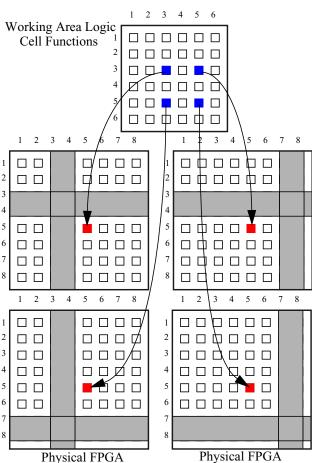

| Figure 42. Example of Four Logic Cells Time Sharing One PLB           | 50          |

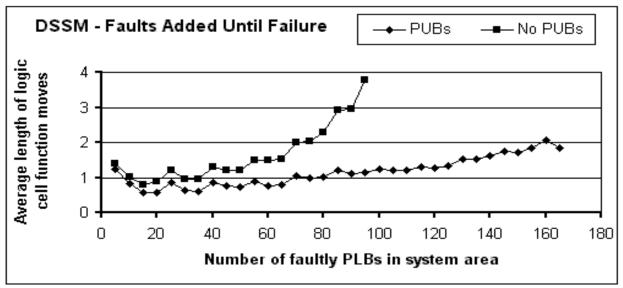

| Figure 43. | Number of Faults Tolerated with and without PUBs | 52 |

|------------|--------------------------------------------------|----|

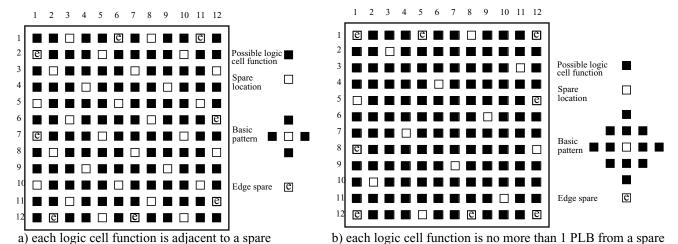

| Figure 44. | Spare Cell Allocation Patterns                   | 54 |

|            | Illustration for Fault Compatibility             |    |

| Figure 46. | Multiple Fault Interaction                       | 56 |

| Figure 47. | Compatible Multiple Fault                        | 56 |

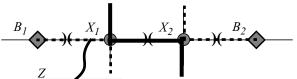

| Figure 48. | Where Is the Short?                              | 57 |

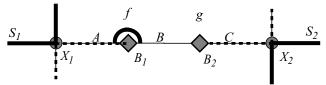

| Figure 49. | Signal Compatibility                             | 58 |

|            | Taking Advantage of an Open Segment              |    |

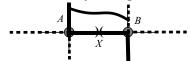

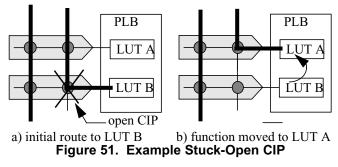

| Figure 51. | Example Stuck-Open CIP                           | 59 |

| Figure 52. | Bypassing an Open Segment                        | 60 |

| _          |                                                  |    |

# **List of Tables**

| <u>Table</u>                                                        | <b>Page</b> |

|---------------------------------------------------------------------|-------------|

| Table 1.Performance Penalty with STARs                              | 10          |

| Table 2:Summary of BIST Phases for ORCA 2C and 2CA Logic Blocks     | 16          |

| Table 3:Summary of Additional Diagnostic Phases for ORCA 2C and 2CA | 27          |

| Table 4:Summary of interconnect BIST test sessions                  | 34          |

| Table 5:Summary of interconnect BIST test sessions and phases       | 38          |

| Table 6:Summary of Interconnect BIST Test Results on Faulty Chips   | 38          |

| Table 7.Performance Penalty with Spare PLBs                         | 54          |

| Table 8.Single-Fault Compatibility Conditions                       | 56          |

|                                                                     |             |

#### 1. Introduction

Adaptive computing systems (ACS) rely on reconfigurable hardware to adapt the system operation to changes in the external environment, and to extend mission capability by implementing new functions on the same hardware platform. This results in increased functional density and reduced power consumption – features very important in many domains, such as space missions or mobile devices. Field-programmable gate arrays (FPGAs) featuring incremental dynamic runtime reconfiguration (RTR) offer additional benefits by allowing the system to continue to execute uninterrupted, while portions of the FPGA are reconfigured for new logic functions. ACS are often deployed in harsh and/or hostile remote environments, and they are subject to strict highreliability and high-availability requirements. Cosmic radiation may perturb the operation of a defect-free FPGA, and marginal defects not causing failures in manufacturing testing (such as a short initially having very high resistance) may become active with the aging of the device, or because of environmental factors. Since direct human intervention for maintenance and repair is impossible in such environments, fault-tolerant (FT) techniques resulting in graceful degradation must be used to achieve the desired mission life even in the presence of faults. However, traditional FT design, based on replicated modular redundancy and voting, is extremely expensive given the space, weight, and power constraints of ACS.

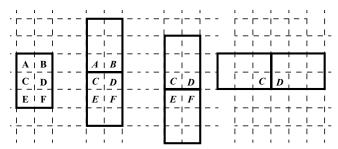

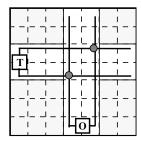

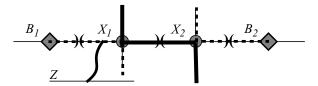

While FPGA testing has been the focus of many research and development efforts [2, 18, 20, 21, 25, 26, 27, 28, 33, 34, 41, 44, 45, 46, 52, 53, 55, 56, 57, 60], most of this previous work deals with off-line testing, which is not applicable in missions relying on continuous system operation. The only attempt at on-line FPGA testing has been the pioneering work of Shnidman et al. [48]. The main idea, originally proposed by Shombert and Siewiorek in the context of testing systolic arrays [49], is to have only a relatively small portion of the chip off-line and being tested, while the rest of the device is on-line and continues its normal operation. Testing of the entire FPGA is accomplished by repeatedly moving different sections of the system logic in the most recently tested part, thus allowing a new area of the chip to be tested. Figure 1 illustrates this process, called roving spares in [49] and fault scanning in [48]. For FPGAs, roving relies on RTR, which is the ability to dynamically reconfigure part of an FPGA without disturbing the operation performed in the rest of the device. Compared with on-line testing based on modular redundancy, this approach has much smaller overhead. Since a fault occurring in the working area will be detected the next time when the fault site will be under test, the fault latency (the interval between the occurrence of a fault and its detection) is bounded by the interval required to test the entire FPGA.

Despite these advantages, the method proposed in [48] has several serious limitations. Although today most FPGAs use dedicated wire segments for inter-block communication, this method can work only for bus-based FPGAs. Even with this limitation, it is not applicable to any existing

Figure 1. Roving Area Under Test Across the Chip

FPGA architecture, since it requires a modified design of the FPGA blocks. Moreover, these modifications introduce a substantial overhead, since the entire configuration memory is duplicated. This method does not address faults in the programmable interconnect network, which occupies most of the area of an FPGA, and it is also limited by the simplifying assumption that the configuration memory and flip-flops (FFs) are fault-free.

Most FT approaches for FPGAs target yield improvement by replacing faults detected in manufacturing test with spare resources to achieve a fully functional chip [7, 9, 10, 11, 12, 19, 22, 23, 24, 29, 31, 36, 40, 42, 47, 58]. But most of these methods are not applicable for on-line fault tolerance, because they can deal with only a limited number of faults, or only with specific faults, or use repair techniques not available in remote environments, or require excessive redundancy, or need excessive computation time to determine how to bypass faults. The method of Lach et al. [31] divides the FPGA into tiles, reserves a spare cell in every tile, and precomputes replacement configurations for every possible faulty cell in a tile. This removes the need for expensive on-line computations and enables fast bypassing of detected faults. However, this method cannot deal with more than one fault per tile. In [32], Lach et al. extend their method to consider interconnect faults. Similar to their method for handling logic faults, several replacement configurations are precomputed for programmable signals that do not extend beyond the tile, so that each configuration leaves some routing resources unused. Then when a fault occurs, they try to find a configuration that does not use the faulty resource; this method, however, is not able to tolerate all possible faults or a group of faults in the same tile. For signals that do extend between tiles, they propose two alternatives. In some cases the tile size can be enlarged to encompass the signals. This works well for hierarchical architectures like complex programmable logic devices (CPLDs) and for dedicated, linked interconnect paths like fast carries. For signals that are routed through interconnects that extend across several tiles, they leave a long segment vacant, to be used to replace any parallel segment in the same area. But after one faulty segment is replaced by the long spare, no additional faults can be tolerated in that region.

The embryonics approach, developed by Mange et al. [37, 38], applies evolutionary concepts from biology to achieve self-repair in a new type of fine-grained reconfigurable array. While their results are fascinating, this approach is not applicable to existing FPGAs.

All the FT methods discussed above are static, as the spare resources they provide – logic cells and/or interconnect – are preassigned in the FPGA. Too many spares cause a large overhead, while too few spares may result in not having sufficient resources available in areas affected by fault clusters. In contrast, the dynamic method proposed by Mahapatra and Dutt [36] allocates interconnect resources to bypass faults only after faults have been located. If the new required segments conflict with the current usage of the routing tracks, the layout is incrementally modified to make room for the new segments. However, this method is dynamic only with respect to the interconnect resources; spare cells are still statically allocated, which may result in long chains of layout changes between the fault sites and spare cells.

Our approach is specifically targeted toward faults that appear during the lifetime of the chip and affect the logic in a STAR when that area is under test. However, transient faults may affect the working area at any time. For transient faults, our system will use a low-overhead method such as concurrent error detection (CED) [62]. CED and roving STARs are complementary techniques, as CED does not address dormant faults and does not provide for diagnosis. At the system level, we

use a checkpointing and rollback strategy. A rollback restores the state of the system to the last state saved before the fault occurred (checkpoint), and it should be initiated whenever CED detects a fault. The STARs can continue roving during the rollback period, which is viewed as normal system activity. (Faster fault location can be achieved if the CED mechanism can indicate the unit likely to be faulty and roving starts within that unit.) However, when a fault is detected by a STAR, rollback is not needed because either it is already in progress (if CED has already encountered the same fault), or the fault has not affected the recent system operation and hence it must be a dormant one. If CED has detected a fault, but the next STAR roving round does not confirm its existence, the fault must have been a transient one from which the system has recovered by rollback.

THIS PAGE WAS INTENTIONALLY LEFT BLANK

#### 2. Main Contributions

We have developed the first integrated approach to on-line testing, diagnosis, and fault tolerance for FPGAs, where all three subjects are concurrently treated in an unified and consistent manner. Our approach inherits the basic feature of [49] and [48]; namely, we have self-testing areas (STARs) of the FPGA that are roving around the chip. However, our roving STARs approach provides many significant features not available in prior work. Our approach is applicable to any FPGA that supports RTR, and it does not require any modifications to the FPGA architecture.

To satisfy the high-reliability and high-availability requirements of ACS hardware, our approach guarantees complete testing of both logic and interconnect, and does not require any part of the chip to be fault free. Complete testing means that all the FPGA resources, including logic and interconnect currently not employed by the application logic, will be tested in every possible mode of operation. This strategy could be considered an overkill: why don't we test only the used resources, and only in their current mode of operation? The main reason is that during the normal operation of an adaptive system, the FPGA will be used with different configurations at different times, and our strategy makes certain that no segment of the FPGA will be assigned a function that may be incorrectly performed because of its dormant (not yet detected) faults. Also, the resources in the currently unused portions of the FPGA are spares to be used for fault tolerance. But since failures are as likely to affect the spares as the working area, there is no reason to assume that the spares will be fault free; thus the spares may also develop dormant faults, unless they are tested in the same way as the working area. Recently, it has been shown that on-line testing of dormant faults is essential in achieving high reliability in safety-critical applications [52].

Our approach is a type of built-in self-test (BIST), where both the test-pattern generation and the analysis of the output responses are done within the circuit under test. This is much more difficult than external testing, since we cannot assume that the FPGA resources used in test-pattern generators (TPGs) or in output response analyzers (ORAs) are fault free. Nevertheless, our logic BIST techniques will detect any single or multiple fault in a cell, and any possible combination of multiple faulty cells; our interconnect BIST techniques will detect any single or multiple fault affecting the interconnect network. By exhaustively testing both the programmable logic blocks (PLBs) and the programmable interconnect, our tests implicitly detect all possible stuck faults affecting the configuration memory.

We have developed diagnostic techniques that achieve the highest possible resolution, locating any group of faulty PLBs, any group of interconnect faults, and also identifying defective modules inside the faulty cells. (Note that one cannot distinguish between a configuration bit being stuck and the corresponding fault in the resource controlled by the stuck bit.) The diagnostic goal of conventional FT techniques for FPGAs is to identify faulty resources, which are then bypassed and replaced by spares. The high accuracy of our diagnosis allows us to introduce a new form of fault tolerance, based on reusing faulty resources whenever possible. A partially usable block (PUB) is a faulty PLB with identified failing mode(s) of operation. A PUB may be used as a fault-free cell in the working part of the system, provided that its faults do not affect its intended operation. Similarly, we allow the system logic to safely reuse faulty wire segments. Reusing defective hardware resources increases the effective spare capacity and leads to more graceful degradation and longer mission life.

In addition, our roving STARs approach has important advantages in FT applications. In most previous FT work, faults are detected in the working logic, and they must be located and bypassed very quickly to restart the normal operation as soon as possible. In contrast, in our approach the detected faults do not affect the working logic, so the system operation does not have to be interrupted for fault diagnosis and for computing fault-bypassing reconfigurations.

We also introduce the idea of an adaptive system clock. One side-effect of FT reconfigurations is a possible increase of the delays of some critical paths of the circuit. The conventional solution to this problem is to set the clock period with sufficient slack to work for any possible FT reconfiguration. But this cost in performance degradation is paid all the time, even if the worst-case faults will never occur. We use a programmable clock whose initial frequency is set to the maximum value allowed in the fault-free circuit, and we adjust it only when required as a result of FT reconfigurations [14]. In this way the ACS performance will be gracefully degraded, and only when needed in response to the occurrence of new faults.

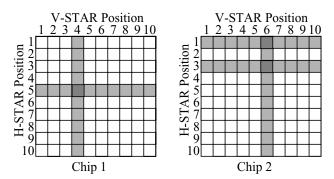

We have successfully implemented this approach using a commercially available FPGA – specifically, the ORCA 2C and 2CA series FPGA [16]. However, we emphasize that our approach is general, as it may be applied to any FPGA that uses segmented interconnect and features RTR. The remainder of this report is organized as follows. Section 3 presents the structure and the operation of the roving STARs. Section 4 describes the BIST and BIST-based diagnosis of logic and interconnect resources in the FPGA. Section 5 outlines the main concepts of our new FT techniques for faults in logic and in interconnect. Section 6 concludes the report. Section 7 lists the participants in the project, the patents obtained or applied for, and publications. Section 8 contains references.

# 3. The Roving STARs

## 3.1 The Test and Reconfiguration Controller

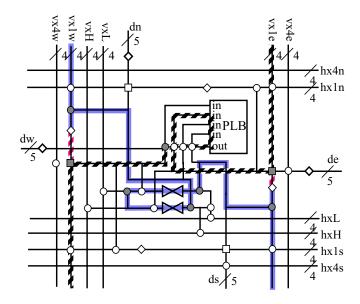

Since ACS normal system operation involves reconfiguring FPGAs for different functions, the reconfiguration process is controlled by a module external to FPGAs; typically, this is an embedded microprocessor having some memory to store configurations. We extend the tasks of this processor to also control the test, diagnosis, and FT functions, including their associated reconfigurations. We refer to this processor as the test and reconfiguration controller (TREC). TREC accesses an FPGA using its boundary-scan mechanism [51], so that this access is transparent to the normal function of the chip. TREC also employs the boundary-scan interface to partially reconfigure the FPGA, to control the BIST, and to retrieve the test results. TREC uses RTR to rove the STARs across the chip and to reconfigure them for different test and diagnosis operations. TREC also controls the system clock(s) and has the capability to stop the system operation for short intervals to allow for safe relocation of the system logic in the last tested area.

If faults are detected during BIST, TREC analyzes the results to locate the faults. If the faults could not be precisely diagnosed, TREC will run additional diagnostic configurations until the desired resolution is achieved. TREC also keeps track of the status of FPGA resources, and determines if the defective hardware located in the current STAR affects the operation of the next slice of the working area to be relocated over the STAR position. If the faults affect only spare resources, or if the faulty resources may be safely reused to implement the required function, TREC proceeds with the relocation. If the faulty resources may not be reused, then TREC determines configuration changes to the working area so that the defective resources are bypassed and replaced by fault-free ones. For faults affecting its own operation, TREC employs microprocessor-specific FT techniques that will not be discussed in this report.

# 3.2 The Roving STARs Structure

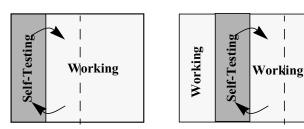

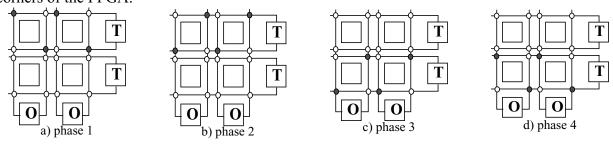

Figure 2 illustrates the floor plan of an FPGA at some stage of the roving process; the FPGA has a working area and a spare area consisting of a vertical STAR (V-STAR) with two columns and an horizontal STAR (H-STAR) with two rows. Depending on the positions of the two STARs, the working area may be contiguous or split in two of four regions. Most of the time only one STAR is active (testing) at any time. A STAR tests both the PLBs and the interconnect in its area. A PLB may use local interconnect to communicate with its adjacent cells, and global interconnect for

Figure 2. Horizontal and Vertical STARs

connections with other cells or input/output (I/O) blocks. The latter category includes long lines, that extend horizontally along an entire row or vertically along an entire column. While only one STAR would be sufficient to test all the PLBs in the FPGA, testing of both vertical and horizontal global busses and of the connections between them requires separate vertical and horizontal STARs. Having two roving STARs also provides additional benefits for diagnosis and fault tolerance that will be discussed in the next sections. Testing the entire FPGA takes one full horizontal sweep of V-STAR and one full vertical sweep of H-STAR. The direction of roving changes after every full sweep: left $\rightarrow$ right, up $\rightarrow$ down, right $\rightarrow$ left, and down $\rightarrow$ up. For an *NXN* FPGA, a full sweep of one STAR requires *N*/2 positions, thus the total number of STAR movements is *N*. An important consequence is that the fault latency increases linearly with the size of the FPGA.

To preclude the usage of the spare resources by the FPGA design tools, the spare PLBs in both STARs, the vertical routing tracks in V-STAR, and the horizontal routing tracks in H-STAR are designated as reserved. Connections among the working PLBs are allowed to use only horizontal wire segments through V-STAR, and only vertical segments through H-STAR; the same rule also applies to connections with the I/O blocks of the FPGA. For an NXN FPGA, the area overhead taken by the two STARs is  $OV(N) = 1 - (N-2)^2/N^2$ . The overhead decreases with N. For example, for N=20, OV is 19 percent, but for N=40, OV is only 10 percent. Another part of the overhead consists of routing resources for a four-wire bus around the perimeter of the array, needed for the links between the boundary-scan test access port (TAP) controller and BIST circuitry within the STARs.

## 3.3 The Roving Mechanism

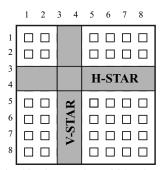

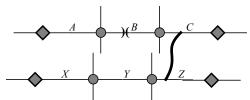

Once a STAR has been tested, the STAR roving process continues by relocating the working area adjacent to the STAR over the current STAR position, and by reconfiguring the just-released working area as a new STAR. Figure 3 illustrates several aspects of this procedure by following a section of one row during several steps. Figure 3a shows the initial state, where A, D, E, and F are working PLBs, separated by B and C which are part of V-STAR. Assume all test activity has stopped without detecting any faults, while the normal operation continues. TREC performs the following operations: (1) Configure B and C with the functions of D and E; (2) Stop the system clock; (3) If necessary, copy the state of D and E into B and C; (4) Reconfigure to disconnect the nets connected to D and E and connect them to B and C; (5) Restart the system clock; (6) Configure the new STAR and restart testing. The critical steps are (3) and (4), which must be as fast as possible to minimize the period when the system clock is suspended; these steps are explained next.

Step (3) – copying the state values from the old to the new locations of the relocated working PLBs – is not needed for PLBs that are used only as combinational functions. Otherwise, if the relocated functions include registers and/or RAM, the implementation of this step depends on the features of the target FPGA. For an FPGA that allows direct reading and writing of registers by treating them as addressable memory locations, the task is straightforward. Although a little more complicated, solutions based on partial configuration readback, available on ORCA series 3C [16], are also easy to implement. For FPGAs without such features, a general solution is to use an additional configuration that creates temporary transfer paths through the STAR from the source PLBs to the destination PLBs and issue a single clock (derived from the test clock *TCK*) to copy

Figure 3. Roving Steps

the values. Figure 3b illustrates a path *T* created to transfer values from D to B (we assumed that E implements a combinational function). In addition to a transfer path, copying RAM contents requires the creation of a transfer controller to sequence both the source and the destination RAMs concurrently through their address space and to issue the proper read and write signals for the desired transfer. The transfer controller can be placed in the STAR not involved in the current roving step (H-STAR in our example).

Step (4) maintains the correct interconnections among working PLBs; the results of this step can be seen in Figure 3c. Net Q, originally between F and D, has been extended to connect to B. In contrast, net R has been shrunk since now it connects adjacent PLBs. Net P, originally a direct connection between E and F, has been routed via two vertical segments and a horizontal one. Net S has been moved with the PLBs it connects.

These changes are done by an incremental rerouting of the affected area of the chip, using the same netlist, changing the placement of the relocated logic, marking the vertical tracks in the new STAR position as unusable, and saving the resulting incremental configurations. For a full horizontal swap we need to repeat this process N/2 times. We are using a standard router for this job. Since computing these roving configurations is not done on-line, but as a preprocessing step, the cost of the N incremental routing jobs is acceptable. A more efficient incremental routing procedure is described by Dutt et al. in [10], but this requires a special-purpose router.

Inserting a STAR in the working area introduces a delay overhead in the signals that now have to traverse the STAR, typically corresponding to a two-cell long wire segment. Although relatively small, this overhead must be compensated by a slack in the operating clock frequency. In the worst case, a signal in the application circuit's critical path may be split by one or two STAR widths. To investigate this performance penalty, we used seven benchmark circuits. First we mapped the circuit as a non-FT FPGA design using commercial computer-aided design (CAD) tools, with options set for performance optimization. Then we mapped the same set of circuits to the same FPGA with two inserted STARs. The results presented in Table 1 are based on implementing the seven benchmarks with ORCA 2C15A, and show the number of PLBs, the initial maximum delay, the maximum delay in the presence of STARs, and the percent increase. The

maximum delays were computed for the 10 positions of the V-STAR. For six circuits, the delay increase caused by the insertion of the STARs is between 0 and 16.3 percent.

**Table 1. Performance Penalty with STARs**

| Circuit                           | # PLBs | Initial<br>Delay (sec) | Delay w/<br>STARs (sec) | % diff |

|-----------------------------------|--------|------------------------|-------------------------|--------|

| Huffman                           | 40     | 87.5                   | 98.9                    | 11.5   |

| Fibonacci                         | 70     | 130.7                  | 130.8                   | 0.0    |

| Wallace tree multiplier           | 65     | 144.3                  | 149.7                   | 3.6    |

| Digital Single Sideband Modulator | 229    | 75.1                   | 76.6                    | 2.0    |

| Hilbert                           | 192    | 73.2                   | 87.5                    | 16.3   |

| Random number generator           | 134    | 49.4                   | 56.4                    | 11.5   |

| Mono-FFT                          | 62     | 117.8                  | 120.8                   | 2.5    |

# 4. On-Line Testing and Diagnosis

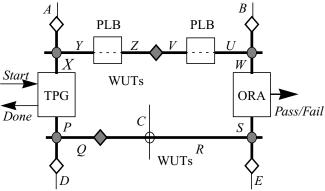

#### 4.1 Basic BIST Structure

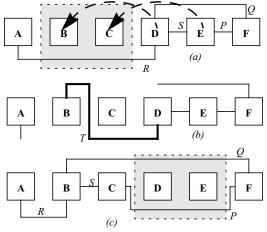

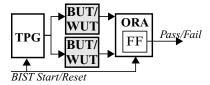

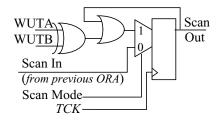

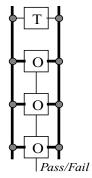

A STAR contains several disjoint tiles that are tested concurrently. Figure 4 shows the basic BIST structure used in a tile, called a BISTER, which inherits some of the concepts used in our off-line FPGA BIST methods for PLBs [56, 55, 2] and programmable interconnect [57]. A BISTER contains a TPG applying test patterns to two identically configured blocks under test (BUTs) in case of logic BIST, or two sets of wires under test (WUTs) in the case of routing BIST. The outputs of the BUTs or WUTs are compared by an ORA. The ORA latches and reports mismatches as test failures. Direct comparison avoids possible aliasing errors introduced by compressing responses into signatures [1]. BIST Start/Reset and Pass/Fail are two of the interface signals with the TREC via the boundary-scan access mechanism. Start/Reset is used to initiate the BIST sequence and to reset the TPG and ORA. The test result Pass/Fail is captured in a FF which is part of a scan register [18]. The other two inputs from the TREC/boundary-scan interface include TCK for clocking the BIST circuitry and a control input for scanning out the Pass/Fail results from each BISTER. The first configuration of a BISTER checks the proper operation of the scan register, inducing mismatches by comparing BUTs or WUTs with different configurations. This also protects against the case of all ORA FFs being stuck at the "Pass" value.

Figure 4. Basic BISTER

The TREC accesses an FPGA using its boundary-scan mechanism [51], so that this access is transparent to the normal function of the chip (most FPGAs support boundary scan). TREC employs the boundary-scan interface to reconfigure the STARs for different test and diagnosis operations, to initiate the BISTERs, and to scan out the test results. BISTERs work with the boundary-scan clock *TCK*, and the configuration clock is also derived from *TCK*. TREC also controls the system clock(s) and has the capability to stop the system operation for short intervals to allow for safe relocation of the system logic in the last tested area. If faults are detected, TREC starts the diagnosis process (to be discussed later).

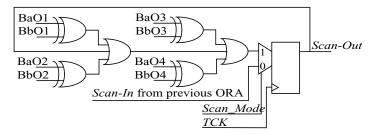

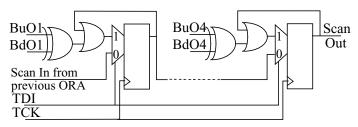

Figure 5 illustrates a typical ORA that compares four pairs of outputs coming from the two BUTs (or WUTs). The feedback latches the first mismatch into the FF. Higher diagnostic resolution could be obtained by constructing an independent ORA (comparison and latching FF) for each pair of outputs to be compared. However, this would increase the *Pass/Fail* result data to be retrieved by a factor of four. While higher diagnostic resolution is important for the FT techniques, there is a tradeoff between diagnostic resolution and the total testing time which, in turn, determines the fault latency. Therefore, to minimize fault latency, we break the fault detection and fault diagnosis into two separate processes when necessary. We apply diagnostics procedures only after we have detected faults in the STAR. Accordingly, we break our discussion of the fault

Figure 5. Integrated ORA/Scan cell

detection and diagnostic processes into the following separate subsections for both logic and interconnect.

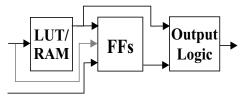

## 4.2 Testing Programmable Logic Blocks

Figure 6 shows a typical structure of a PLB, composed of a memory module, a register, and a combinational output module. This structure is found in most current RAM-based FPGAs. The memory block can implement combinational lookup tables (LUTs) or a RAM with various modes of operation (synchronous, asynchronous, single-port, dual-port, etc.). A PLB also contains special-purpose logic for arithmetic functions (counters, adders, multipliers, etc.) The register can be configured as FFs or latches with programmable clock-enable, preset/clear, and data selector functions.

Figure 6. Typical PLB Structure

The BUTs are repeatedly configured to be pseudoexhaustively tested in every mode of operation; this means that every module in a BUT is exhaustively tested [39]. The configuration of the TPG also changes when a new BUT configuration requires different patterns. For example, to test combinational functions implemented by a LUT with n inputs, the TPG is a counter that generates all possible  $2^n$  vectors, while to test the RAM, the TPG is a state machine generating standard RAM test sequences [59], which are known to be exhaustive for the fault models specific to RAMs, such as pattern-sensitive faults. The ORA needs to be reconfigured when the new mode of operation of BUT involves a different number of outputs.

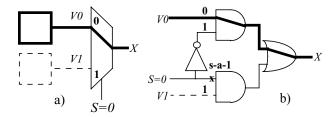

A configuration multiplexer (MUX) is a commonly used hardware mechanism that selects subcircuits for various modes of operation. A configuration MUX is controlled by configuration memory bits to select one input to be connected to its output. In Figure 7a, assume that we set the configuration bit S to 0 to connect V0 to X. Then the subcircuit producing V1 disappears from the circuit model seen by the user. This is correct from a design viewpoint, because the value V1 can no longer affect X in the current configuration. But from a testing viewpoint, in any test for the MUX, we need to set V0 and V1 to complementary values. In general, for a MUX with k inputs, if V is the value of the selected input, all the other k-1 inputs should be set to value  $\overline{V}$ .

Figure 7. Configuration Multiplexer

The problem arises because FPGA CAD tools generate the configuration bitstream based on the user model, which will never include the functionally inactive subcircuits (called invisible logic in [56]). Thus in Figure 7a, when S=0, V0 will be set to both 0 and 1, but V1 cannot change. Similarly, the user logic cannot control V0 in any configuration where S=1. The result is that the testing of the MUX may not be complete. For example, the s-a-1 fault in the gate-level MUX model in Figure 7b is detected only when S=0, V0=0, and V1=1. But this pattern may never be applied if V1 cannot be controlled when S=0.

Our solution relies on separately configuring the invisible logic so that it will generate the proper values needed for the inactive MUX inputs. Then we overlay the resulting configuration files over the main configuration file with the active logic, and we merge them without changing any MUX setting done in the main configuration. This process is conceptually simple, but its implementation requires knowledge of the FPGA configuration stream structure.

Note that in most previous work dealing with testing FPGAs, the problem of testing a configuration MUX is either not addressed or it is solved functionally, by connecting every input in turn to the output, and providing both 0 and 1 values to the selected input. However, the invisible logic driving the inactive inputs is completely ignored. Hence prior claims of complete testing may not be valid since the testing of every configuration MUX in the FPGA is likely to be incomplete. Methods that did provide complete tests for configuration multiplexers, such as [27, 55], used models that did not remove the invisible logic. But such models cannot be used with the existing FPGA CAD tools to generate configuration files.

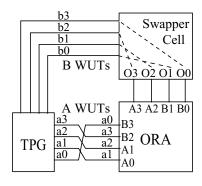

Since a BISTER provides complete testing only for its BUTs, we have to reconfigure every BISTER several times so that every PLB will be a BUT in at least one configuration. The BUTs are repeatedly configured to be tested in all their modes of operation. The modes of operation of a PLB may be determined only from the information available in the FPGA data book, without having a detailed knowledge of its implementation. The test time for a BISTER, and thus total roving time, is dominated by the reconfiguration time, which is much larger than the BIST time. Hence to reduce the latency of our procedure, we try to minimize the number of PLBs in a BISTER. The number of PLBs for an ORA and for a TPG depend on the target PLB architecture. Usually the number of outputs in a PLB is smaller than its number of inputs. Since a TPG must provide exhaustive patterns for BUTs, we will need more than one PLB to construct the TPG. For illustration purposes, we will assume that a TPG needs three PLBs and an ORA only one. (Our analysis, however, is independent of the number of PLBs used in implementation.)

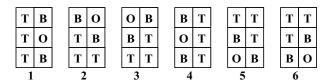

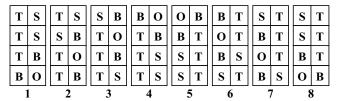

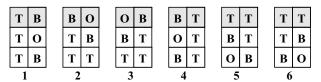

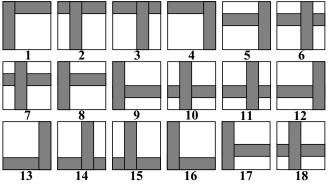

Figure 8. 3 by 2 BISTER Tile Rotations

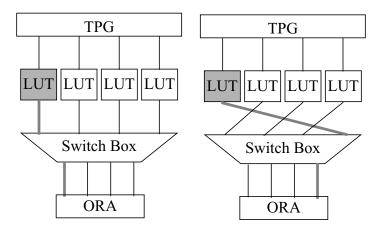

Figure 8 illustrates six floor plans of a 3 by 2 BISTER tile, where T, B, and O denote, respectively, a TPG cell, a BUT, and an ORA cell. The goal of the six configurations is to systematically rotate the functions of the PLBs, so that eventually every PLB in the tile is completely tested twice, each time being compared with a different BUT. This rotating strategy assures that every single faulty PLB and almost all combinations of multiple faulty PLBs (except for a few pathological cases described in [2]) are guaranteed to be detected. If the number of PLBs in a STAR is not a multiple of the number of PLBs in a tile, then the leftover PLBs that could not make up a BISTER will be grouped with some of the PLBs already tested in the adjacent tile, so that every PLB in the STAR will eventually be part of a BISTER.

Figure 9 illustrates the floor plan of the 4 by 2 BISTER tile used in our implementation with the ORCA 2C series FPGA and its associated eight test configurations (S indicates a spare PLB). The role of the spare cells is to provide additional routing resources to overcome routing congestion problems. We arrange the number of spare PLBs so that a tile will have an even number of PLBs, symmetrically distributed between the two columns of the V-STAR. Similar to the 3 by 2 BISTER tile, the eight configurations shown in Figure 9 systematically rotate the functions of the PLBs, so that every PLB in the tile is completely tested twice, each time being compared with a different BUT. To overcome routing congestion problems, spare PLBs may be incorporated into the BISTER tile to provide additional routing resources. While these are not pure rotations, since they maintain the 3 TPG cells in the same column, they do achieve the same property as the rotations of the 3X2 tile. This rotating strategy allows us to prove the following properties regarding the fault detection capability of a BISTER [4]:

Figure 9. 4 by 2 BISTER Tile Rotations

**Claim 1:** Any single faulty PLB is guaranteed to be detected in at least two BISTER configurations.

*Proof:* The faulty PLB is a BUT in two BISTER configurations, where its exhaustive inputs patterns are produced by a fault-free TPG, and its outputs are compared with a fault-free BUT by a fault-free ORA. Hence no fault (single or multiple) detected in the BUT can escape detection in these two configurations.

**Claim 2:** Except for a few pathological cases, any pair of faulty PLBs is guaranteed to be detected in at least one BISTER configuration.

*Proof:* Since any single faulty PLB is detected, we must have a circular masking relation [1], where one faulty PLB masks the detection of the faults in the other and vice versa. This masking should occur in any BISTER configuration where a single faulty PLB would be detected. First we note that any masking relation between the two faulty PLBs disappears whenever one of them becomes a spare. Because a TPG or an ORA containing a faulty PLB may still work correctly, we analyze only configurations when at least one of the faulty PLBs is a BUT and the other is not a spare.

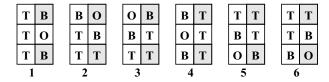

Case 1: Both faulty PLBs are BUTs in one BISTER configuration. Then the TPG and the ORA are fault-free, and the only way the faulty pair can escape detection is to have functionally equivalent faults, since then their identical outputs will not mismatch. Assume that the faulty PLBs are BUTs in the configuration 1 in Figure 10. Then in configurations 3 and 5, one of them is a BUT (compared with a fault-free BUT by a fault-free ORA), and the other is a TPG cell. The only way the faulty pair can escape detection is for the faulty TPG to skip exactly the patterns that detect the faulty BUT. We say that this is a pathological case, because it has an extremely low probability of occurrence: we need two faulty PLBs, and they must have functionally equivalent faults, and when a faulty PLB is part of the TPG, the TPG must skip those patterns that detect the faulty BUT.

Figure 10. BISTER Tile Rotations (Two Faulty BUTs)

Case 2: At most one faulty PLB is a BUT in any BISTER configuration. Assume, without loss of generality, that the faulty cells are in the first row of the BISTER, as shown in Figure 11. Let X be the faulty BUT and Y the faulty TPG cell in configuration 1. To have circular masking between X and Y, all of the following conditions must be true: 1) in configuration 1, the TPG must skip those patterns that detect X; 2) in configuration 4, the TPG must skip those patterns that detect Y; 3) in configuration 2, the ORA X must not record the mismatch between Y and the fault-free BUT; and 4) in configuration 3, the ORA Y must not record the mismatch between X and the fault-free BUT. Again, this is a pathological situation because we need the AND of four conditions, which are very unlikely by themselves.

Figure 11. BISTER Tile Rotations (One Faulty BUT)

Clearly, similar arguments can be made for more than two faulty PLBs. Hence we can conclude that:

**Claim 3:** In practice, any combination of faulty PLBs is detected in at least one BISTER configuration.

Table 2 summarizes the 14 test phases we have developed to completely test a PLB in our implementation of the roving STARs approach using the ORCA 2C and 2CA series FPGAs [16]. The last five phases apply only to the 2CA series PLB. The FF modes can be tested at the same time with five of the LUT modes to reduce fault latency (as illustrated in Table 2), or we can test them separately to enhance diagnostic resolution. We chose to minimize fault latency in our implementation at the expense of diagnostic resolution. Thus complete testing of a PLB requires 14 BISTER configurations. One additional BISTER configuration is added to each set of test phases to test the integrated ORA/scan chain for a total of 15 test phases per rotation of the BISTER.

Table 2: Summary of BIST Phases for ORCA 2C and 2CA Logic Blocks

| Phase |          | FF/Late      | ch Modes     | & Option        | IS             | LUT                   | No.  | Log | ic To | ested     |

|-------|----------|--------------|--------------|-----------------|----------------|-----------------------|------|-----|-------|-----------|

| No.   | FF/Latch | Set/Reset    | Clock        | Clock<br>Enable | FF Data        | Mode                  | Outs | LUT | FFs   | MUX       |

| 1     | -        | -            | -            | -               | -              | Asynchro-<br>nous RAM | 4    | √   |       | √         |

| 2     | -        | -            | -            | -               | -              | Adder/sub-<br>tracter | 5    | √   |       | √         |

| 3     | -        | -            | -            | -               | -              | 5-variable<br>MUX     | 4    | √   |       | <b>√</b>  |

| 4     | -        | -            | -            | -               | -              | 5-variable<br>XOR     | 4    | √   |       | √         |

| 5     | FF       | async. reset | falling edge | active low      | LUT output     | Count up              | 5    | 1   | 1     | V         |

| 6     | FF       | async. set   | falling edge | enabled         | PLB input      | Count up/<br>down     | 5    | √   | √     | $\sqrt{}$ |

| 7     | Latch    | sync. set    | active low   | active high     | LUT output     | Count down            | 5    | 1   | 1     | <b>√</b>  |

| 8     | FF       | sync. reset  | rising edge  |                 | PLB input      | 4-variable            | 4    | 1   | 1     | $\sqrt{}$ |

| 9     | Latch    | -            | active high  | active low      | dynamic select |                       | 4    |     | V     |           |

| 10    | -        | -            | -            | -               | -              | Multiplier            | 5    | 1   |       |           |

| 11    | -        | -            | -            | -               | -              | Greater/equal to Comp | 5    | √   |       |           |

| 12    | -        | -            | -            | -               | -              | Not equal to Comp     | 5    | √   |       |           |

| 13    | -        | -            | -            | -               | -              | Synchronous RAM       | 4    | √   |       |           |

| 14    | -        | -            | -            | -               | -              | Dual port<br>RAM      | 4    | √   |       |           |

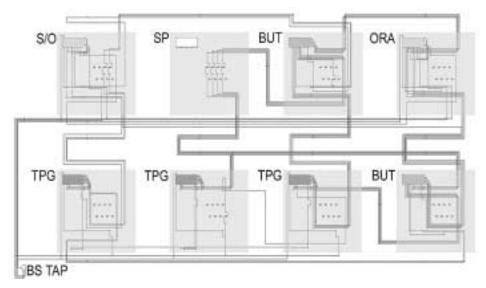

The operational modes of the PLBs require between 9 and 12 inputs be supplied with test patterns. Since a 4-bit counter can be easily implemented in a single PLB, we use three PLBs for a TPG. An ORA consisting of a 4-bit comparator and a FF to latch mismatches is implemented by a single PLB. Figure 12 shows the actual layout of a BISTER tile in the H-STAR. Two spare PLBs (denoted by S/O and SP), configured as identity functions, have been added to avoid the use of global vertical routing resources. The layout also shows the boundary-scan TAP controller (denoted by BS TAP), which is not part of the BISTER tile [18]. Since the tile has 8 PLBs, we will have 8 rotations of this layout (see Figure 9), and every BISTER will be reconfigured 15 times for a total of 120 configurations per STAR to completely test all of the PLBs within that STAR.

16

Figure 12. Layout of a BISTER Tile

Partial reconfiguration reduces the time required for downloading the BISTER tile configurations (and therefore the fault latency), and it also significantly reduces the amount of storage required for the BISTER tile configurations. For example, the complete configuration memory for the 2C15A consists of about 225 Kbits. Partial configuration of the complete STAR requires about 23 Kbits. However, by performing partial configuration for only those portions of the STAR that must be changed from one BISTER tile configuration to the next requires only between 3 Kbits and 10 Kbits, depending on how much of the STAR is being reconfigured; changing the mode of operation of the BUTs requires the smallest number of bits, while rotating the BISTER tile to begin testing a new set of BUTs requires the largest number of bits. As a result, only about 7 percent of the files are of the larger size (10 K), while 93 percent of the files are the smaller size (3 K), for a total of about 420 K bits of storage required for the PLB BIST configurations.

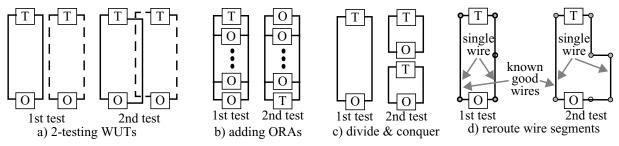

## 4.3 Divide-and-Conquer Adaptive Diagnosis

The goal of our original approach was to have a unique procedure able to locate any combination of multiple faulty PLBs in a BISTER without making any restrictive assumption about the multiplicity of the fault. We start by considering all the PLBs in a failing BISTER as suspects. Figure 13 illustrates this adaptive diagnosis procedure. The V-STAR has a failing BISTER with six suspected PLBs. First they are split in two sets  $-\{A,B\}$  and  $\{C,D,E,F\}$  — which are included in separate BISTERs whose other PLBs were shown to be fault free. Next we assume that the upper BISTER passes all its tests, while the lower one fails. The remaining suspects are again split in two sets  $-\{C,D\}$  and  $\{E,F\}$  — and included in separate BISTERs. Next we assume that the E and E are found to be fault free. But now the remaining suspects E and E are found to be included in separate BISTERs. To complete the diagnosis, we rove H-STAR to bring it over the row with E and E are found to be fault free. But now the remaining suspects E and E are found as a parate BISTERs. To complete the diagnosis, we rove H-STAR to bring it over the row with E and E and E and E are found as a parate BISTERs.

Figure 13. Example of Adaptive PLB Diagnosis

The time for the diagnosis procedure is determined by the number of partial reconfigurations needed to locate all the faulty PLBs. Even in the best case, when we have a single faulty PLB, we need at least three different STAR configurations, and for each one of them, the full set of six or eight rotations. In addition, several roving steps may be needed to bring the second STAR to cover the remaining suspected PLBs, where each roving step is done by another partial reconfiguration. Long run-time for diagnosis is not critical, because the normal system operation continues without interruption during this period [15]. However, it may result in delaying the detection of a new fault occurring during the execution of the diagnosis procedure.

A second problem with this procedure results from the need to group suspected PLBs with adjacent known-good ones. During the life of a fault-tolerant system, the set of fault-free spares gets gradually smaller as more faults occur, and fault-free PLBs may no longer exist in an area where they are needed to help in diagnosing suspects. In such a situation the procedure would be no longer applicable.

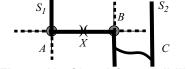

To illustrate a third shortcoming of the design-and-conquer technique, consider the situation shown in Figure 14, where we have the suspects A, B, C, and D. Recall that in [2] H-STAR and V-STAR move by two PLBs each roving step and thus each STAR can only be positioned in one of N/2 two-cell-wide positions in the FPGA. Then in V-STAR we can place  $\{A,B\}$  and  $\{C,D\}$  in separate BISTERs, and in H-STAR we can separate between  $\{A,C\}$  and  $\{B,D\}$ . But if all these four BISTERs fail, we cannot separate the suspects. Indeed both diagonal pairs of PLBs –  $\{A,D\}$  and  $\{B,C\}$  – would cause failures in all four BISTERs. Similarly, all sets of three faulty PLBs and the group of all four faulty PLBs in the 2 by 2 area located at the intersection of the V-STAR and H-STAR are indistinguishable. This problem could be solved by allowing STARs to have one-PLB-wide roving steps for diagnosis, but this solution would double the number of configurations to be stored by TREC, and significantly complicate the control programs.

Figure 14. Example of Inconclusive Diagnosis

## 4.4 Locating Faulty PLBs Using BISTER Results

In every test configuration, TREC records the set of failures obtained at the ORA outputs. Our improved diagnosis method consists of two stages. First, it tries to locate faulty PLBs based on analyzing the test results, and in many cases, this stage is sufficient to achieve maximum diagnostic resolution. The frequent case of a single faulty PLB falls in this category. For cases of multiple faulty cells not completely resolved by the first stage, a second stage employs the divide-and-conquer strategy based on additional reconfigurations [4, 3].

In any fault location procedure, maximum diagnostic resolution is achieved when faults are isolated within an equivalence class containing all the faults that produce the observed response. If every equivalence class has only one fault, we say that the fault is uniquely diagnosed, that is, there is no other fault which can produce the same response. In our case, a fault is one faulty PLB that may have several internal faults, and the response is the set of failing test configurations (also called test phases) detected at the outputs of the ORAs. We begin by assuming a single faulty PLB in the FPGA, then we analyze the case of multiple faulty PLBs, and we also discuss locating faults inside a defective PLB.

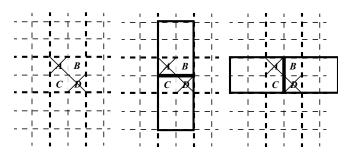

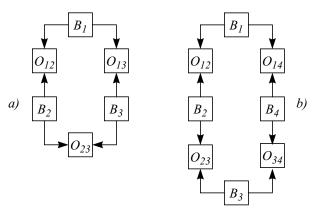

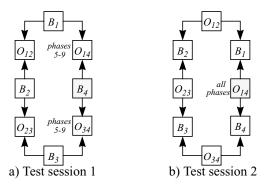

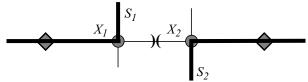

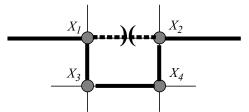

We can observe that the PLBs in a BISTER tile can be partitioned into two disjoint sets, so that every set contains the PLBs that are pairwise compared when configured as BUTs. For example, for the 3 by 2 tile, the BUTs in configurations 1, 3, and 5 are compared only among themselves and they are never compared to the BUTs in phases 2, 4, and 6. A similar partition exists for the 4 by 2 tile as well. We can represent the relations between BUTs that are pairwise compared and the ORAs that observe them by the graphs shown in Figure 15, where a BUT is denoted by a node  $B_i$ , and the ORA that observes BUTs  $B_i$  and  $B_j$  is denoted by  $O_{ij}$ . We can view such a graph as representing a combined test session, in which half of the BUTs in the tile are concurrently tested. Each tile is completely tested in two combined test sessions, where the BUTs in one session are ORAs in the other one, and vice versa.

## **Theorem 1:** Any single faulty PLB is guaranteed to be uniquely diagnosed.

*Proof:* When the faulty PLB is configured as a BUT, it is detected at its two adjacent ORAs, and no other BUT is detected at the same two ORAs. Note that when the faulty PLB is configured as a TPG cell, no error is generated even when the fault modifies the TPG patterns, because the two

Figure 15. Combined test sessions a) 3 by 2 tile b) 4 by 2 tile

BUTs still receive the same patterns. When configured as an ORA, the faulty PLB may generate an error, but this will be in addition to the failures observed in the combined session when it is a BUT, and these results are sufficient to distinguish it from any other single faulty PLB.

As a consistency check, we can verify that the sets of failures obtained at the two ORAs are identical.

The following results deal with the location of a group G of faulty PLBs that is detected in at least one test session. To uniquely diagnose G means to identify all its faulty blocks such that no other group (including subsets of G) can produce the same result. Although unique diagnosis is not always possible, there are many situations when it can be guaranteed.

We will analyze the interactions among faulty PLBs under the following assumptions:

Assumption 1: A TPG with faulty PLBs does not skip the patterns that detect faults in a BUT.

Assumption 2: A faulty PLB is not detected when it is configured as an ORA.

Based on these assumptions, the set of failing phases obtained at ORA  $O_{ij}$  is given by the following:

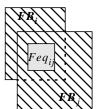

$$FO_{ii} = (FB_i \cup FB_i) - Feq_{ii} \tag{1}$$

where  $FB_k$  is the set of failing phases of BUT  $B_k$ , and  $Feq_{ij}$  is the set of failing phases of both  $B_i$  and  $B_j$  that have identical responses (and thus do not cause mismatches at  $O_{ij}$ ). In Figure 16, the area of  $FO_{ij}$  is marked by diagonal lines. Note that  $FO_{ij}$  is empty ( $\varnothing$ ) when both  $B_i$  and  $B_j$  are fault free, or when the faults in  $B_i$  and  $B_j$  are equivalent (since then  $FB_i = FB_j = Feq_{ij}$ ). Also note that there exists one situation when  $FO_{ij}$  is the same, no matter if only one or both of the BUTs observed at  $O_{ij}$  are faulty; this occurs if the two BUTs have the same sets of failing phases ( $FB_i = FB_j$ ), but their faulty responses are never the same ( $Feq_{ij} = \varnothing$ ).

Figure 16. Figure for Equation (1)

Knowing the set of failing phases observed at  $O_{ij}$  and the complete set of failing phases of one of the two faulty BUTs, we can determine the set of failing phases where the two BUTs have identical responses by the following:

$$Feq_{ij} = FB_i - FO_{ij} = FB_j - FO_{ij} \tag{2}$$

Based on  $FO_{ij}$  and one of the two sets, we can also compute a lower bound on the other set by

$$FB_i \supseteq (FO_{ij} - FB_i) \cup Feq_{ij} \tag{3}$$

or by

$$FB_{j} \supseteq (FO_{ij} - FB_{i}) \cup Feq_{ij} \tag{4}$$

Note that Equation (3) becomes an equality when  $FO_{ii}$  and  $FB_i$  are disjoint:

$$FB_i = FO_{ii} \cup Feq_{ii} \tag{5}$$

This occurs when  $FB_i \subseteq FB_i$  and  $Feq_{ij} = FB_i$ .

For the diagnosis procedure, we will make one more assumption:

Assumption 3: No more than two faulty BUTs have identical responses in the same failing phase.

To justify this assumption, recall that in every configuration the TPG applies exhaustive tests for that mode of operation. If Assumption 3 is not satisfied, it means that we would have three or more BUTs with equivalent faults for that mode of operation, which is quite an unlikely event.

The following results will be used by our diagnosis procedure.

**Lemma 1:** If none of the two ORAs observing BUT B fails in phase p, then B does not fail phase p.

*Proof:* Assume, by contradiction, that B fails phase p. Based on Assumption 1, the vectors detecting its faults are generated by the TPG. Then the other two BUTs observed by the two ORAs must have equivalent faults to the fault of B in phase p, because p is not reported by either of the two ORAs. But then we would have three BUTs with equivalent faults in the same phase, which contradicts Assumption 3. Therefore, B does not fail phase p.

**Lemma 2:** If the two ORAs observing the same BUT report no failures, then their common BUT is fault free.

*Proof:* Based on Lemma 1, the common BUT of the two ORAs does not fail any phase.

**Lemma 3:** Any BUT failure appears at least at two ORAs.

*Proof:* Assume, by contradiction, that phase p is reported only at one ORA. Let B be the BUT failing p, and O be the other ORA observing B. Since O does not report p as a failure, the other BUT (say C) observed by O must have identical response in p. But the other ORA observing C does not report p as a failure either, so we have more than two BUTs with equivalent faults in p, which contradicts Assumption 3. Therefore, p must appear at least two ORAs.

**Lemma 4:** If we have failures only at two ORAs, they must have identical failures.

*Proof:* Based on Lemma 3, any failure must appear at least twice, and in this case we have only two failing ORAs. Hence their failures must be identical.

**Theorem 2:** (For the 4 by 2 tile) If only two ORAs observing the same BUT report failure in phase p, their common BUT fails in phase p.

*Proof:* In Figure 17, without loss of generality, assume that  $O_{12}$  and  $O_{14}$  are the two failing ORAs reporting p as a failure. Assume, by contradiction, that their common BUT  $B_1$  does not fail phase p. Then both  $B_2$  and  $B_4$  must fail p. But since no other ORA reports p, then  $B_3$  must also fail in phase p, and its response must be identical to that of  $B_2$  and  $B_4$ . Hence we would have three BUTs with equivalent faults in phase p, which contradicts Assumption 3. Therefore, B must fail phase p.

Figure 17. Figure for Theorem 2

**Lemma 5:** If two ORAs observing the same BUT report no failures, then all three BUTs observed by them are fault free.

*Proof:* Based on Lemma 2, the common BUT of the two ORAs is fault free. So each one of the other BUTs is compared with a fault-free one by an assumed fault-free ORA, and no failure is reported. Hence the other two BUTs are also fault free.

**Lemma 6:** (For the 4 by 2 tile) If only two ORAs without a common BUT fail phase p, then at least one pair of BUTs between the two ORAs are faulty and have identical response in phase p.

*Proof:* In Figure 18, without loss of generality, assume that  $O_{12}$  and  $O_{34}$  are the two ORAs without a common BUT failing phase p. At  $O_{12}$ , p may be caused by  $B_1$  or  $B_2$ . Let us assume that  $B_1$  fails p. Because p is not observed at  $O_{14}$ ,  $B_4$  must also fail p with an identical response. Similarly, had we assumed that  $B_2$  fails p, we would have concluded that  $B_2$  and  $B_3$ , have equivalent faults in phase p. Note that all four BUTs may be faulty as well, but in this case the equivalent faults in the two pairs will be different.

Figure 18. Figure for Lemma 6

Note that under the condition of Lemma 6, we cannot reach a unique diagnosis. However, we can use the reduced set of suspects as a starting point for the divide-and-conquer technique to test some of the suspected PLBs in separate BISTER tiles. A subsequent example will show how the combined technique can uniquely diagnose the faulty PLBs.

**Lemma 7:** Assume that two out of three ORAs fail, such that the middle one has no failures, and the other two have disjoint failures. Then the two BUTs observed by the nonfailing ORA are fault free and the other two BUTs are faulty.

*Proof*: In Figure 19, without loss of generality, assume that  $O_{34}$  has no failures, while  $O_{14}$  and  $O_{23}$  have disjoint failures. Then we want to prove that  $B_3$  and  $B_4$  are fault free and  $B_1$  and  $B_2$  are faulty.

Figure 19. Figure for Lemma 7

Assume, by contradiction, that one of the two BUTs observed by the nonfailing ORA (say,  $B_3$ ) fails phase p. Since  $O_{34}$  reports no failures,  $B_4$  must have an equivalent fault in p. At most one of  $O_{14}$  and  $O_{23}$  may fail p, because their failures are disjoint. Then we have to analyze two cases:

Case 1: One of the failing ORAs (say,  $O_{23}$ ) shows p as a failure. Since p is not observed at  $O_{14}$ , while  $B_4$  fails p,  $B_1$  must also have an equivalent fault in p. In this case we would have three BUTs with equivalent faults in p, which would contradict Assumption 3.

Case 2: None of the failing ORAs reports p as a failure. But this would mean that both  $B_1$  and  $B_2$  must also have equivalent faults in p, since p does not appear at  $O_{14}$  or  $O_{23}$ . In this case we would have four BUTs with equivalent faults in p, which would contradict Assumption 3.

Therefore, both  $B_3$  and  $B_4$  are fault free. Then  $B_2$  is the source of the failures recorded at  $O_{23}$ , while those observed at  $O_{14}$  originate at  $B_1$ .

As a consistency check, we can verify that the failures recorded at the ORA between the faulty BUTs are the union of the disjoint sets of failures obtained at the other two failing ORAs (for the example above,  $FO_{12} = FO_{14} \cup FO_{23}$ ).

The following examples deal with the results of only one combined test session. Under the assumption that a faulty PLB is detected only when configured as a BUT, the two sessions can be independently analyzed, and a different group of faulty BUTs may be identified in each session.

**Example 1:** Figure 20 shows the set of failing phases obtained at the four ORAs in one combined test session for a 4 by 2 BISTER tile. Because failures in test phase 1 are reported only at  $O_{23}$  and  $O_{34}$ , then  $B_3$  is faulty and fails in phase 1 (by Theorem 2). In the same manner,  $B_4$  is identified as failing phase 5,  $B_1$  is identified as failing phase 9, and  $B_2$  is identified as failing phase 7. Since failing phase 8 is reported at three ORAs, Theorem 2 does not apply and we cannot determine which BUTs fail phase 8 (should be at least two). Note that we have identified all four BUTs as faulty.

Figure 20. Figure for Example 1

If our goal is also to identify the exact set of failing phases for every faulty PLB (to be able to reuse its fault-free modes of operation as a partially usable block), we can use the divide-and-conquer technique to obtain additional information. Let us assume that we test  $B_3$  in a separate BIS-TER with known fault-free PLBs and we find out that  $FB_3 = \{1,8\}$ . Then from Equation (2) we obtain  $Feq_{34} = \{1,8\} - \{1,5\} = \{8\}$ , and from Equation (4) we determine that  $B_4$  must also fail phase 8. At this point we still do not know whether  $B_1$  or  $B_2$  is causing  $O_{12}$  to report failure in phase 8, so we again use the divide-and-conquer technique and test  $B_1$  in a separate BISTER. Let us assume that we get  $FB_1 = \{9\}$ . Then from Equation (2) we obtain  $Feq_{12} = \emptyset$ , and from Equation (4) we determine that  $B_4$  must also fail phase 8. Now we know the exact sets of failing phases for every BUT.

Note that the original divide-and-conquer technique by itself cannot diagnose this quadruple fault, because no matter how the original tile is divided, any BISTER will contain one faulty PLB, and the initial set of eight suspected PLBs will never be reduced. In contrast, our analysis technique found all of the four faulty PLBs without any reconfiguration, and relied on the information provided by two steps of divide-and-conquer only to determine the exact sets of failures for the faulty PLBs.