# NAVAL POSTGRADUATE SCHOOL Monterey, California

# **THESIS**

USING COMMERCIAL OFF THE SHELF (COTS)

DIGITAL SIGNAL PROCESSORS (DSP) FOR RELIABLE

SPACE BASED DIGITAL SIGNAL PROCESSING

by

Matthew J. Wukitch

March 2001

Thesis Co-Advisor:

Herschel H. Loomis Alan A. Ross

Approved for public release; distribution is unlimited.

20010702 039

# REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503.

| AGENCY USE ONLY (Leave Blank)             | 2. REPORT DATE                    | 3. REPORT TYPE AND DATES CO           | WEREN                                    |

|-------------------------------------------|-----------------------------------|---------------------------------------|------------------------------------------|

|                                           | March 2001                        | Master's Thesis                       | OV LINED                                 |

| 4. TITLE AND SUBTITLE                     | Water 2001                        | Waster's Thesis                       |                                          |

|                                           | may 5' ', 1 a'   1 5              | (202) ( 2 2 1 1 2 2 2 1               | 5. FUNDING NUMBERS                       |

| Using Commercial off the shelf (CC        | OTS) Digital Signal Processors    | (DSP) for Reliable Space Based        |                                          |

| Digital Signal Processing                 |                                   |                                       |                                          |

| 6. AUTHOR(S)                              |                                   |                                       |                                          |

| Wukitch, Matthew J.                       |                                   |                                       |                                          |

|                                           |                                   |                                       |                                          |

| 7. PERFORMING ORGANIZATION NAME(S         | S) AND ADDRESS(ES)                |                                       | 8. PERFORMING ORGANIZATION REPORT NUMBER |

| Naval Postgraduate School                 |                                   |                                       | NEFORT NOMBER                            |

| Monterey, CA 93943-5000                   |                                   |                                       |                                          |

| 9. SPONSORING / MONITORING AGENCY         | NAME(S) AND ADDRESS(ES)           |                                       | 10. SPONSORING / MONITORING              |

|                                           |                                   |                                       | AGENCY REPORT NUMBER                     |

| 11. SUPPLEMENTARY NOTES                   |                                   |                                       |                                          |

| The views expressed in this thesis        | are those of the author and do    | not reflect the official policy of    | r nosition of the Department of          |

| Defense or the U.S. Government.           | are mose of the addict and ac     | not reflect the official policy of    | position of the Department of            |

| 12a. DISTRIBUTION / AVAILABILITY STATE    | MENT                              |                                       | 12b.DISTRIBUTION CODE                    |

| Approved for public release; distribution | ution is unlimited.               |                                       |                                          |

| 11                                        |                                   |                                       |                                          |

| 3. ABSTRACT (Maximum 200 words)           |                                   |                                       | 1                                        |

|                                           |                                   | Commercial-Off-the-Self Digital Si    |                                          |

| prove the concept of Triple Modular       | Redundant (TMR) processors in     | order to make a COTS DSP radia        | ation tolerant design. The system        |

| was designed to handle the effects of     |                                   |                                       |                                          |

| Two of the industry                       | y's leading programmable 32-bi    | t floating-point digital signal proce | essors were reviewed for this            |

| thesis, Analog Devices ADSP-21060         |                                   |                                       |                                          |

| based upon size, power, speed, and to     |                                   |                                       |                                          |

| processor's performance and characte      |                                   |                                       |                                          |

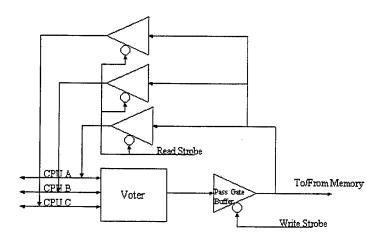

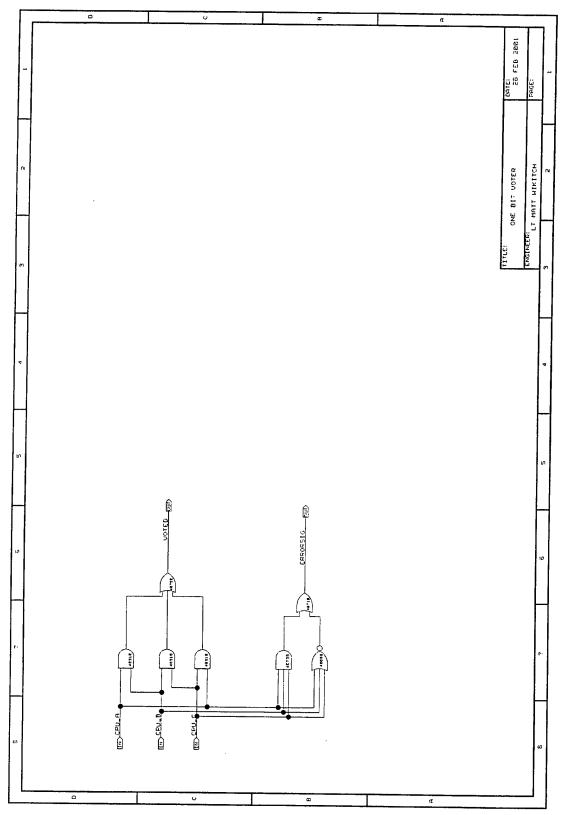

| The system emplo                          | ys a bit by bit voter that compa  | res the three processors' results a   | nd outputs the majority of the           |

| bits. All data, address, and control s    |                                   |                                       |                                          |

| significantly differs from previous T     |                                   |                                       |                                          |

| processor interrupts only when the e      | rrors accumulate to a critical le | vel. An external host processor co    | ontrols the processors' shared           |

NSN 7540-01-280-5500

Unclassified

17. SECURITY CLASSIFICATION

memory space.

14. SUBJECT TERMS

ADSP-21060

OF REPORT

Unclassified

Standard Form 298 (Rev. 2-89)

Fault-tolerant Computing, Digital Signal Processors, Texas Instruments TMS320C6701,

PAGE

Commercial-off-the-Shelf Technology, Radiation, Triple Modular Redundant, Analog Devices

18. SECURITY CLASSIFICATION OF THIS

Prescribed by ANSI Std. 239.18

UL

15. NUMBER OF PAGES

16. PRICE CODE

120

20. LIMITATION OF ABSTRACT

19. SECURITY CLASSIFICATION OF

Unclassified

THIS PAGE INTENTIONALLY LEFT BLANK

#### Approved for public release; distribution is unlimited

# USING COMMERCIAL OFF THE SHELF (COTS) DIGITAL SIGNAL PROCESSORS (DSP) FOR RELIABLE SPACE BASED DIGITAL SIGNAL PROCESSING

Matthew J. Wukitch Lieutenant, United States Navy B.S., U.S. Naval Academy, 1994

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL

March 2001

Author:

Matthew J. Wukitch

Approved by:

Herschel H. Loomis, Thesis Co-Advisor

n 4 Kass

Alan A. Ross, Thesis Co-Advisor

Jeffrey B. Knorr, Chairman

Department of Electrical and Computer Engineering

THIS PAGE INTENTIONALLY LEFT BLANK

## **ABSTRACT**

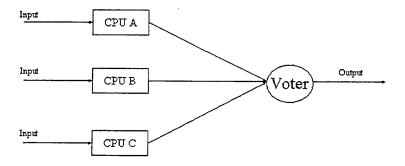

A radiation tolerant testbed was designed using a Commercial-Off-the-Self Digital Signal Processor and presented to prove the concept of Triple Modular Redundant (TMR) processors in order to make a COTS DSP radiation tolerant design. The system was designed to handle the effects of radiation associated with Single Event Upset only.

Two of the industry's leading programmable 32-bit floating-point digital signal processors were reviewed for this thesis, Analog Devices ADSP-21060 and the Texas Instruments TMS320C6701. The '6701 was the best processor for this design based upon size, power, speed, and tolerance to single event latchup, signal event burnout, and total ionization dose. A review of the processor's performance and characteristics is provided to ensure the proper operation of '6701 in a TMR design.

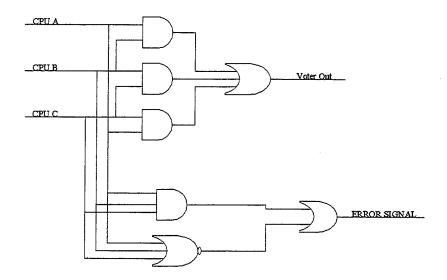

The system employs a bit by bit voter that compares the three processors' results and outputs the majority of the bits. All data, address, and control signals are monitored to determine that the system is operating properly. This system significantly differs from previous TMR designs, because only address errors cause immediate interrupts. Data errors cause processor interrupts only when the errors accumulate to a critical level. An external host processor controls the processors' shared memory space.

THIS PAGE INTENTIONALLY LEFT BLANK

## TABLE OF CONTENTS

| I.   | INT             | RODUCTION                                                    | 1  |

|------|-----------------|--------------------------------------------------------------|----|

|      | A.              | BACKGROUND                                                   | 1  |

|      | В.              | SPACE RADIATION ENVIROMENT                                   | 2  |

|      | C.              | SINGLE EVENT EFFECTS                                         | 4  |

|      |                 | 1. Single Event Upset                                        | 4  |

|      |                 | 2. Single Event Latchup (SEL)                                |    |

|      |                 | 3. Single Event Burnout (SEB)                                |    |

|      | D.              | PURPOSE                                                      |    |

|      | E.              | RADHARD VERSUS COTS                                          | 7  |

|      |                 | 1. Cost of Development of Radhard Devices                    |    |

|      |                 | 2. Benefits of Radhard                                       |    |

|      |                 | 3. Cost of Using COTS                                        |    |

|      |                 | 4. Benefits of COTS                                          |    |

|      | F.              | RELATED WORK                                                 | 11 |

|      | G.              | THESIS ORGANIZATION                                          |    |

| II.  | DD C            | OCESSOR SELECTION                                            | 12 |

| 11.  | A.              | CHARACTERISTICS                                              |    |

|      | В.              | GENERAL PURPOSE DIGITAL SIGNAL PROCESSOR VS                  | 13 |

|      | ъ.              | GENERAL PURPOSE MICROPROCESSORGENERAL PURPOSE MICROPROCESSOR | 12 |

|      | C.              |                                                              |    |

|      | D.              | SIZE, PINOUT, POWERON-CHIP MEMORY SIZE                       |    |

|      | <b>р.</b><br>Е. |                                                              |    |

|      | ь.<br>F.        | PROCESSOR REVIEW                                             | 10 |

|      | г.<br>G.        | CHARARACTERISTICS OF THE SELECTED PROCESSOR                  |    |

|      | G.              | 1. The CPU                                                   |    |

|      |                 | 2. Internal Program Control and Memory                       |    |

|      |                 | 3. Data Memory Controller and Memory                         |    |

|      |                 | 4. Direct Memory Access (DMA) Controller                     |    |

|      |                 | 5. Peripheral Bus Controller                                 |    |

|      |                 | 6. Timers                                                    |    |

|      |                 | 7. Interrupt Selector                                        |    |

|      |                 | 8. Multi-Channel Buffer Serial Ports (McBSP)                 |    |

|      |                 | 9. External Memory Interface Controller (EMIF)               |    |

|      |                 | 10. Host Port Interface (HPI)                                |    |

|      | I.              | SUMMARY                                                      |    |

|      |                 |                                                              |    |

| III. | DET             | ECTION AND CORRECTION OF SEU                                 |    |

|      | <b>A.</b>       | OVERVIEW                                                     | 31 |

|       | В.        | TRIPLE               | MODULAR REDUNDANCY (TMR)                           | 32         |

|-------|-----------|----------------------|----------------------------------------------------|------------|

|       |           |                      | oting Techniques                                   |            |

|       |           | 2. Ve                | oting Issues                                       | 35         |

|       | C.        | ANALYS               | SIS OF SEU ON TMS320C6701                          | 43         |

|       |           | 1. Er                | rror in Program RAM or Cache                       | 44         |

|       |           | 2. Er                | ror in Internal Data Memory                        | 44         |

|       |           | 3. SF                | EU Error Induced into Registers                    | 44         |

|       | D.        | SPECIAI              | L CONSIDERATIONS FOR DSP                           | 45         |

|       |           |                      | ldress Errors                                      |            |

|       |           |                      | ata Errors                                         |            |

|       |           |                      | ariable Pipe Length                                |            |

|       | E.        | SUMMA                | RY                                                 | 48         |

| IV.   | TMF       |                      | DESIGN                                             |            |

|       | <b>A.</b> |                      | EW                                                 |            |

|       | В.        | TRIPLE               | MODULAR REDUNDANT DIGITAL SIGNAL                   | 47         |

|       | _,        |                      | SOR                                                | 50         |

|       |           |                      | stbed Operation Summary                            |            |

|       |           | 2. TI                | TM TMS320C6701 Simulation                          | 33<br>57   |

|       | C.        |                      | 6320C6701 ADDRESS, BE, AND CE BUS INTERFACE        |            |

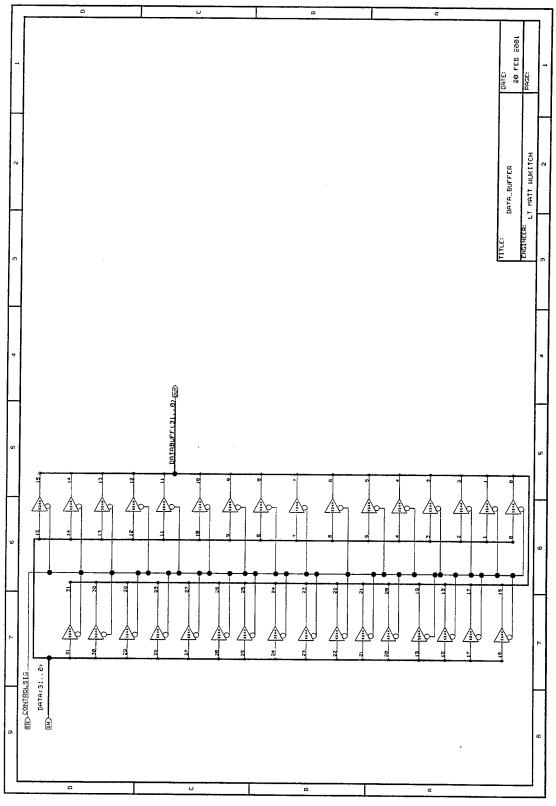

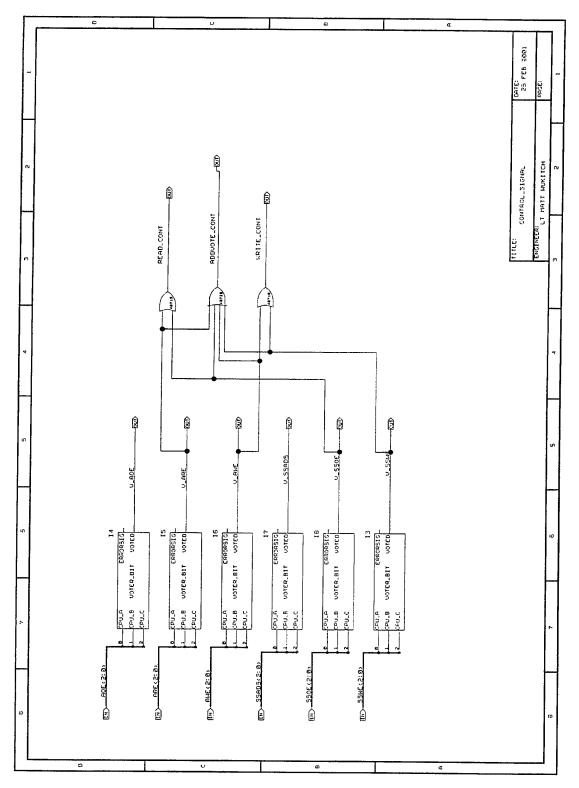

|       | D.        | TI <sup>TM</sup> TMS | 3320C6701 DATA BUS INTERFACE                       | . 30<br>61 |

|       |           |                      | emory Write Cycle                                  |            |

|       |           |                      | emory Read Cycle                                   |            |

|       |           |                      | dition Considerations for the Read/Write Cycle for | . 04       |

|       |           |                      | SRAM                                               | . 64       |

|       |           | 4. Fir               | st-in-First-Out (FIFO)                             | . 65       |

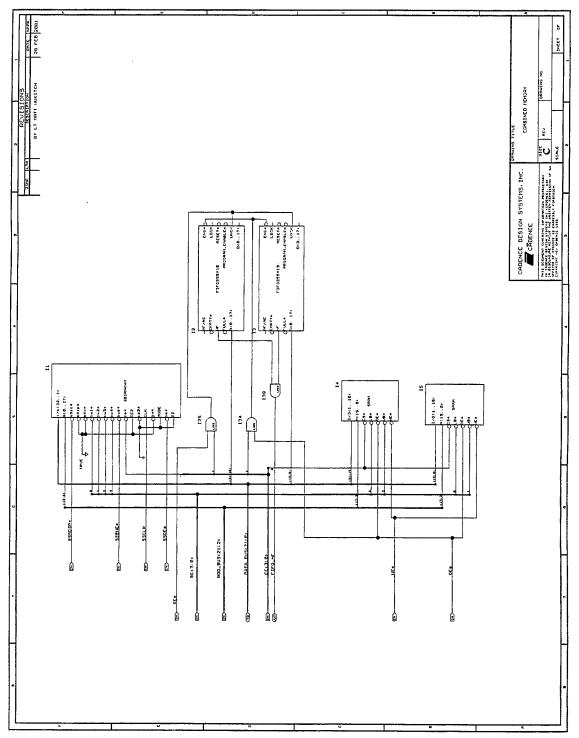

|       | E.        | TITM TMS             | 320C6701 HOST PROCESSOR INTERFACE (HPI)            | . 65       |

|       | F.        | <b>IMPACT</b>        | OF THE TMR SYSTEM                                  | . 66       |

|       | G.        |                      | RY                                                 |            |

| v.    | CON       |                      | AND FOLLOW-ON RESEARCH                             |            |

| •     | <b>A.</b> |                      | RY                                                 |            |

|       | B.        |                      | SIONS                                              |            |

|       | Č.        | FOLLOW               | -ON RESEARCH                                       | , UO<br>60 |

| A DDI |           |                      |                                                    |            |

| APPI  | ENDIX     | A. DE                | TAILED ANALYSIS OF SEU ON THE TMS320C6701          | . 71       |

| APPI  | ENDIX     | B. TH                | E SCHEMATIC OUT LINE OF THE TMR SYSTEM             | . 83       |

|       |           |                      | S                                                  |            |

|       |           |                      |                                                    |            |

| INIT  | 1A1. I)   | STRIKI TIC           | ON LIST                                            | ΛΛ         |

## LIST OF FIGURES

| Figure 1. 1 | Eight Point Radix-2 FFT [From: Ref. 1].                                    | 14 |

|-------------|----------------------------------------------------------------------------|----|

| Figure 2. 1 | Block Diagram TMS320C6701 [From: Ref. 12]                                  | 19 |

| Figure 3. 1 | Pipeline Stages [From: Ref. 12]                                            | 20 |

| Figure 4. 1 | Basic TMR Circuit Implementation [From: Ref. 2].                           | 32 |

| -           | Majority-Voter and Error Detection                                         |    |

|             | EMIF Control Register[From: Ref. 13].                                      |    |

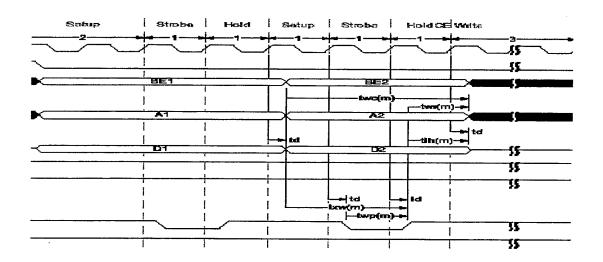

| -           | Asynchronous Write Cycle [From: Ref. 13]                                   |    |

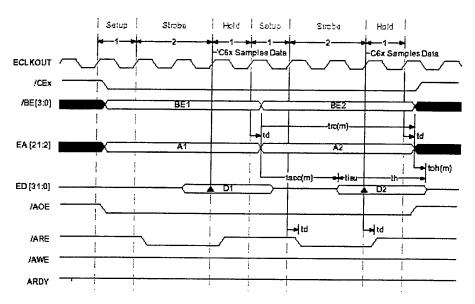

| _           | Asynchronous Read Cycle [From: Ref. 13]                                    |    |

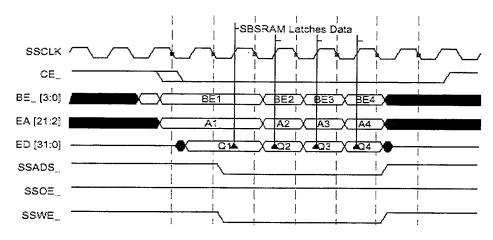

|             | SBSRAM Write cycle [From: Ref. 14]                                         |    |

| Figure 10.  | SBRAM Read Cycle [From: Ref. 14]                                           | 40 |

| Figure 11.  | '6701 SDRAM Read Clock Cycle [From: Ref. 16]                               | 41 |

|             | 6701 SDRAM Read Cycle [From: Ref. 16]                                      |    |

| _           | Simple '6701 Board Design.                                                 |    |

| Figure 14.  | TMR '6701 Board Design.                                                    | 51 |

| Figure 15.  | Interrupt Buffer Control Circuit.                                          | 52 |

| -           | Asynchronous SRAM Write Cycle with Voting Delay.                           |    |

| Figure 17.  | Synchronous Burst SRAM Read Cycle with Voting Delay                        | 60 |

|             | Simple Voter Control and Bypass Circuit                                    |    |

| Figure 19.  | Asynchronous SRAM Write Cycle with Delay of Voting                         | 62 |

| Figure 20.  | Synchronous Burst SRAM Write Cycle with Delay of Voting                    | 63 |

| Figure 21.  | Address Mode Register (Bits 31:26 Shaded).                                 | 71 |

| Figure 22.  | Address Mode Register (Bits 25:16 Shaded)                                  | 71 |

| Figure 23.  | Address Mode Register (Bits 15:0 Shaded).                                  | 72 |

| Figure 24.  | Control Status Register (Bits 31:16 Shaded).                               | 72 |

| Figure 25.  | Control Status Register (Bits 15:10 Shaded).                               | 72 |

|             | Control Status Register (Bit 9 Shaded).                                    |    |

| Figure 27.  | Control Status Register (Bit 8 Shaded).                                    | 73 |

| Figure 28.  | Control Status Register (Bits 7:2 Shaded).                                 | 73 |

| Figure 29.  | Control Status Register (Bits 1:0 Shaded).                                 | 74 |

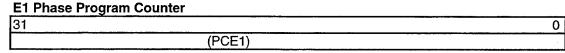

| Figure 30.  | Phase Program Counter (Bits 31:0 Shaded)                                   | 74 |

| Figure 31.  | Float-Point Adder Configuration Register (Bites 31:27, 15:11 Shaded)       | 75 |

| Figure 32.  | Float-Point Adder Configuration Register (Bites 26,25,10,9 Shaded)         | 75 |

|             | Float-Point Adder Configuration Register (Bites 24:16,8:0 Shaded)          |    |

| Figure 34.  | Floating-Point Auxiliary Configuration Register (Bits 31:27,15:11 Shaded). | 76 |

| Figure 35.  | Floating-Point Auxiliary Configuration Register (Bits 26:16,10:0 Shaded)   | 76 |

|             | Floating-Point Multiplier Configuration Register (Bits 31:27,15:11         |    |

| Sha         | ded)                                                                       | 76 |

| Figure 37.  | Floating-Point Multiplier Configuration Register (Bits 26,25,10,9 Shaded)  | 77 |

| Figure 38.  | Floating-Point Multiplier Configuration Register (Bits 24:16, 8:0 Shaded)  | 77 |

| Figure 30   | General Control Registers (Rits 31:20 Shaded)                              | 72 |

| Figure 40. | General Control Registers (Bits 28:1X Shaded).      | . 78 |

|------------|-----------------------------------------------------|------|

|            | General Control Registers (Bits X:X,1 Shaded).      |      |

|            | General Control Registers (Bit 0 Shaded)            |      |

|            | Interrupt Service Table Pointer (Bits 31:0 Shaded). |      |

| Figure 44. | Interrupt Enable Register (Bits 31:16,3,2 Shaded).  | . 80 |

| Figure 45. | Interrupt Enable Register (Bits 15:4,1 Shaded).     | . 80 |

| Figure 46. | Interrupt Set Register (Bits 31:16,3:0 Shaded).     | . 80 |

| Figure 47. | Interrupt Set Register (Bits 15:4 Shaded).          | 81   |

| Figure 48. | Interrupt Clear Register (Bits 31:16, 3:0 Shaded)   | 81   |

| Figure 49. | Interrupt Clear Register (Bits 15:4 Shaded).        | 81   |

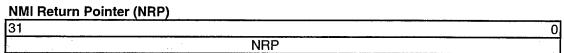

| Figure 50. | NMI Return Pointer (Bits 31:0 Shaded).              | 82   |

| Figure 51. | Interrupt Return Pointer (Bits 31:0 Shaded).        | 82   |

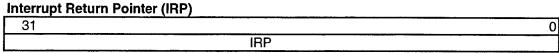

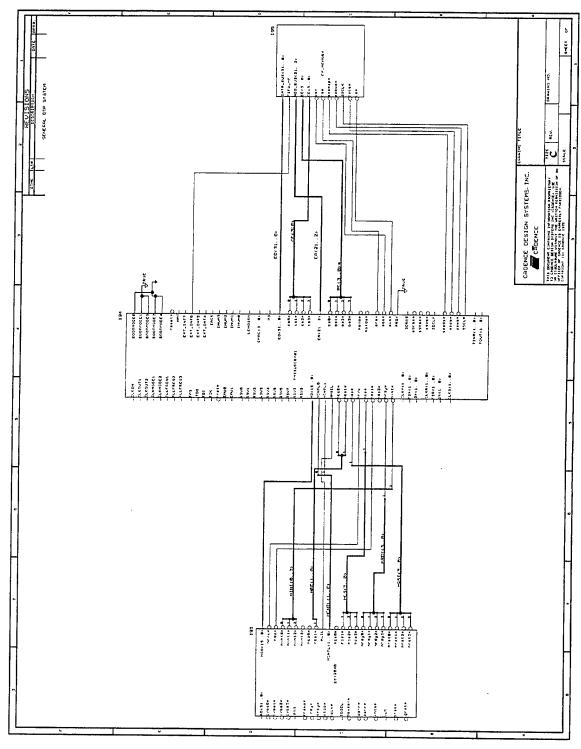

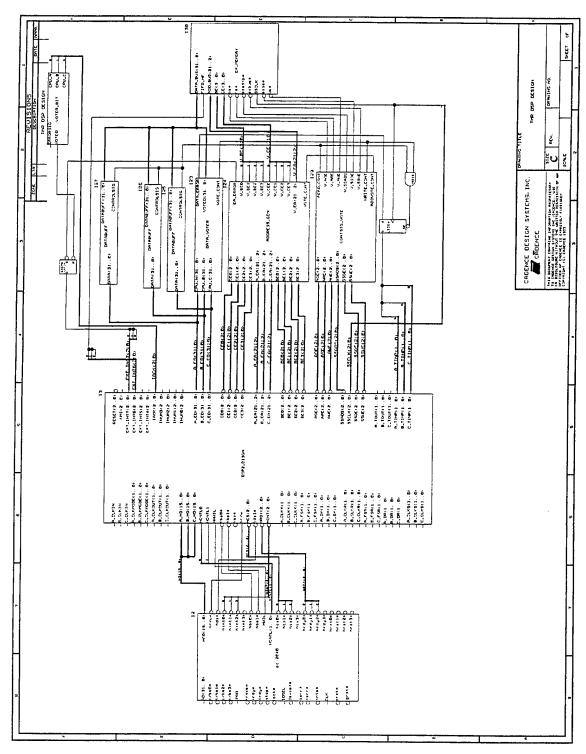

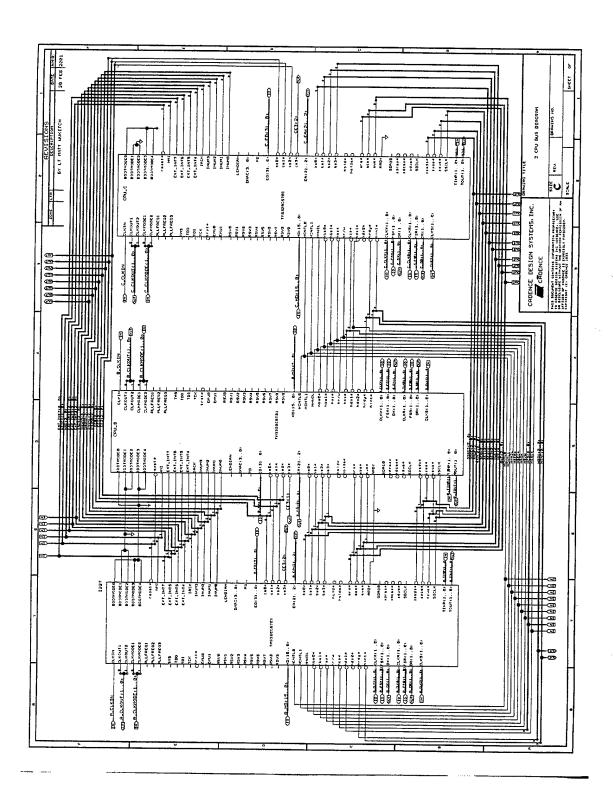

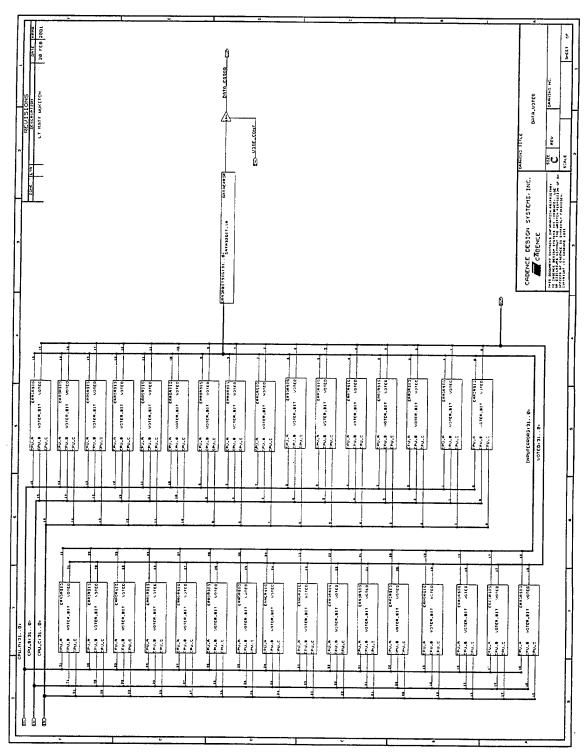

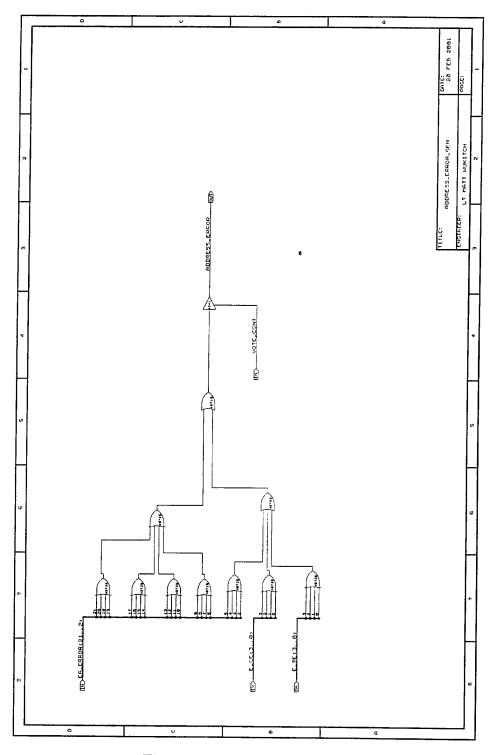

| Figure 52. | General TMS320C6701 Implementation.                 | 84   |

| Figure 53. | General Memory Architecture.                        | 85   |

| Figure 54. | '6701 TMR Design.                                   | 86   |

| Figure 55. | Schematic of Three '6701 Wired in Parallel          | 87   |

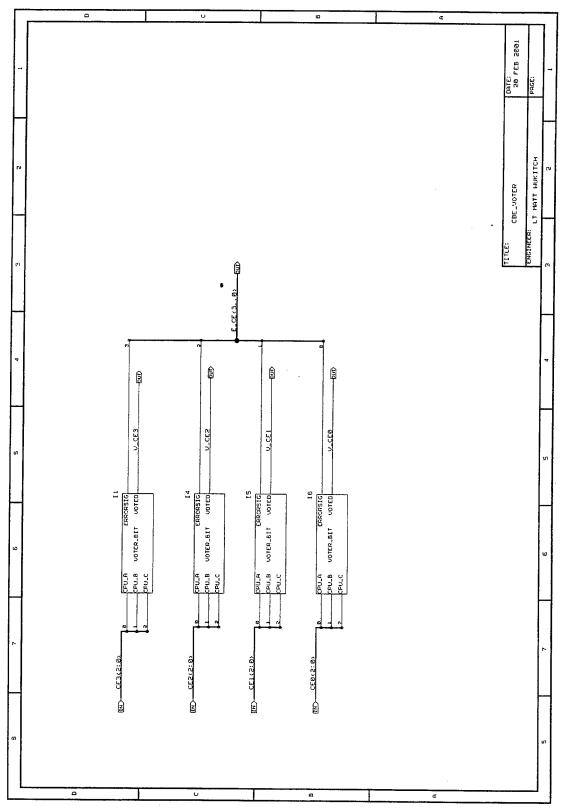

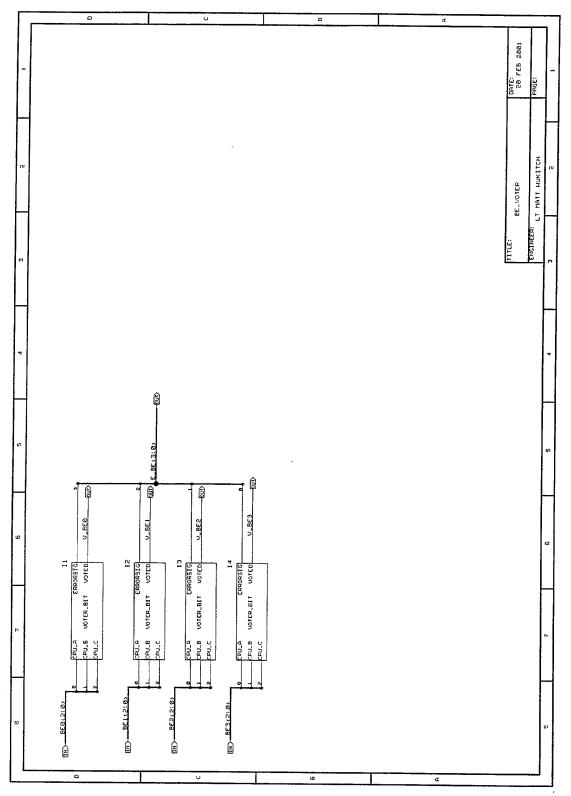

| Figure 56. | One-Bit Voter                                       | 88   |

|            | Data Buffer                                         |      |

| Figure 58. | Data Voter.                                         | 90   |

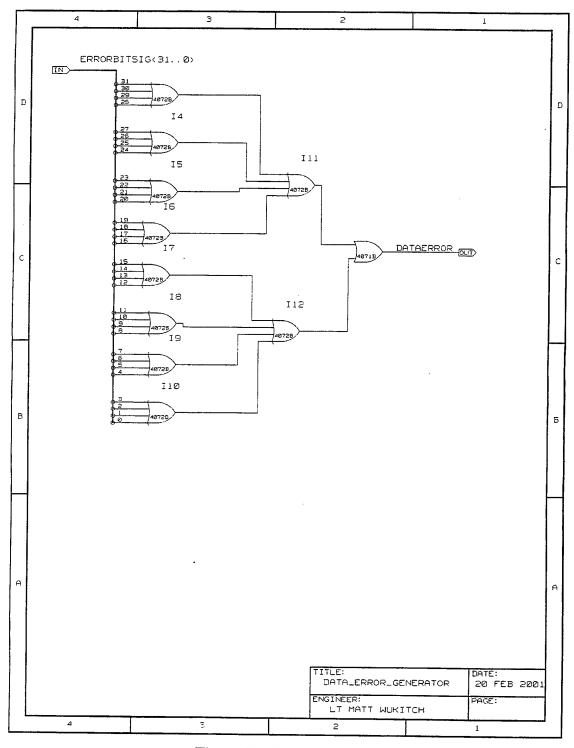

| Figure 59. | Data Error Generator                                | 91   |

| Figure 60. | Address Voter.                                      | 92   |

|            | CE Voter.                                           |      |

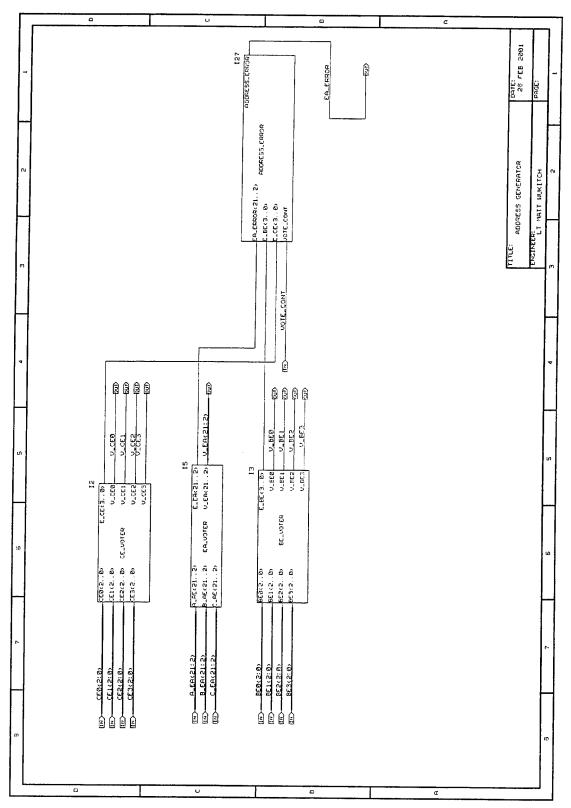

| Figure 62. | Address Error Generator.                            | 94   |

|            | BE Voter.                                           | 95   |

| Figure 64. | Control Signal Voter.                               | 96   |

# LIST OF TABLES

| Table 1. | Real additions and Multiplications Required to Perform an N Point FFT |    |

|----------|-----------------------------------------------------------------------|----|

| [F       | From: Ref. 1]                                                         | 14 |

|          | Digital Signal Processors.                                            |    |

|          | Function Units [From: Ref. 12]                                        |    |

|          | Interrupt Selection [From: Ref. 12]                                   |    |

THIS PAGE INTENTIONALLY LEFT BLANK

#### **ACKNOWLEDGMENTS**

First I would like to thank my mom and dad for always being there when I need them and Greg for always helping me out and taking trips to Canada. I would like to thank the following people for helping me to complete my thesis. Prof. Loomis and Prof. Ross for providing guidance. Jeff Weekley for editing and correcting my horrible grammar. I would like thank the following groups, Reel Big Fish, Less than Jake, Goldfinger, Catch 22, 311, Everclear, Third Eye Blind, Greenday, Blink 182 and all the other great bands that kept me sane will working on this project.

THIS PAGE INTENTIONALLY LEFT BLANK

#### **EXECUTIVE SUMMARY**

Radiation tolerant digital signal processors have not kept pace technologically with other digital signal processors that do not need to operate in the rigorous environment of space. The traditional approach of radiation hardening has not allowed for the inexpensive and quick development of designs suitable for space. This thesis offers one solution to the difficulties of the space deployment of digital signal processors, while providing for less expensive components and more flexibility in the end product application.

A radiation tolerant testbed was designed using a Commercial-Off-the-Self Digital Signal Processor and presented to prove the concept of Triple Modular Redundant (TMR) processors in order to make a COTS DSP radiation tolerant design. The system was designed to handle the effects of radiation associated with Single Event Upset only.

Two of the industry's leading programmable 32-bit floating-point digital signal processors were reviewed for this thesis, Analog Devices ADSP-21060 and the Texas Instruments TMS320C6701. The '6701 was the best processor for this design based upon size, power, speed, and tolerance to single event latchup, signal event burnout, and total ionization dose. A review of the processor's performance and characteristics is provided to ensure the proper operation of '6701 in a TMR design.

The system employs a bit by bit voter that compares the three processors' results and outputs the majority of the bits. All data, address, and control signals are monitored to determine that the system is operating properly. This system significantly differs from previous TMR designs, because only address errors cause immediate interrupts. Data errors

cause processor interrupts only when the errors accumulate to a critical level. An external host processor controls the processors' shared memory space.

#### I. INTRODUCTION

#### A. BACKGROUND

Digital signal processing is an area of study that has advanced rapidly over the past 30 years. The rapid development of very-large-scale integration (VLSI) of electronic circuits has spurred the development of more powerful, smaller, faster, and cheaper digital signal processors. Special purpose signal processors were introduced in the 1980s and advanced rapidly during the 1990s. The first processors were simple 8-bit fixed point processors that have advanced to today's 32-bit fixed or floating-point processors that can perform up to 1.1 billion instructions per second. The advantages of using digital signal processing over analog techniques include increased stability, reduced noise susceptibility, re-programmability, and high immunity to factors such as component aging, loss of precision, and temperature variations. These inexpensive and relatively fast processors have made it possible to build highly sophisticated digital systems capable of performing complex digital signal processing functions and tasks. Hence many of the signal processing tasks that were performed by analog circuits can now be done cheaper, more reliably and with decreased power requirements with a digital signal processor implementation. Therefore, it was natural to adapt these processors for space-based applications that range from signal processing, image processing, attitude control, and power management [Ref. 1].

#### B. SPACE RADIATION ENVIROMENT

The space environment requires a designer to take special precautions that are not required inside the earth's atmosphere. This environment poses a risk to all earth-orbiting satellites and missions to other planets in the form of electromagnetic radiation from the sun: not only visible light, but the entire range from radio to gamma rays. In addition to solar radiation, a satellite design has to deal with ionization particles of the sun and distant stars. Some of this is trapped within the earth's magnetic field forming the intense radiation of the Van Allen Belts [Ref. 2].

Radiation is the process of emitting radiant energy in the from of waves or particles. Most of the radiation in space near to Earth comes from the sun, as fusion in the sun shoots particles and radiates energy in the form of waves. The particles emitted by the sun become deflected or trapped by the Earth's magnetic field. The harmful high-energy waves are absorbed by particles in the upper atmosphere [Ref. 2].

Particles can come in a variety of forms classified in two groups, heavy and light ions. The light ion will be either a proton or a beta particle (electron). The proton is the simplest positive ion and is a fundamental particle with a small mass. The beta particle is the simplest negatively charged ion and also has a small mass. Stripping the two electrons from a helium atom creates the alpha particle. The classifications of ions as heavy or light is dependent on the atomic number of the element. All ions with two or more protons/neutrons are classified as heavy ions [Ref. 3].

Unlike particles emitted by the sun and other celestial objects the waves or photons emitted by them have neither mass nor charge. Gamma Rays are an example of photon radiation.

The sun dominates the sources of radiation in space near earth. Solar activity on the sun varies over an 11-year cycle, producing a variable average of solar particles.

Though solar activity is predictable on a macro scale, the sun still produces a wide variation in radiation intensity on a day-to-day basis [Ref. 3].

A second type of particle radiation is the Galactic Cosmic Ray (GCR), which consists of are particles that reach earth from sources outside the solar system. Cosmic rays are heavy ions produced from cosmic events such as exploding stars.

The largest contributor to a spacecraft's total dose is particles trapped by the earth's magnetic field. These particles come mainly from the sun but also from other celestial bodies. The particles create the region in space known as the Van Allen Belts. The belts are a fixed hazard to spacecraft and are distributed non-uniformly within the magnetosphere.

From these sources of radiation two factors, Total Ionization Dosage (TID) and Single Event Effects (SEE) are calculated to determine the survivability of spacecraft and their electronics. The Total Ionization Dosage (TID) is the total amount of radiation that can be absorbed during a spacecraft's lifetime before failure. TID creates bulk-oxide and interface-trap charge that reduces transistor gain and shifts the operating properties (e.g., threshold voltage) of semiconductor devices. TID accumulation will cause a device to fail in the following ways: the transistor threshold voltage shifts far enough to cause

circuit malfunction; the device fails to operate at the required frequency; or electrical isolation between devices is lost. All electronic devices experience the effects of TID, and these effects cannot be mitigated after the design and manufacturing process.

Therefore, we will focus on the second type of radiation effects, the single event effects.

Single Event Effects (SEE) consists of three different phenomena. They are single event upset (SEU), single event latchup (SEL) and the single event burnout (SEB). SEE are random events that occur when spacecraft are exposed to radiation. As the spacecraft orbit the earth, it is continuously exposed to radiation, some of which passes through their external shell and affect the spacecraft subsystems. When radiation interacts with microelectronic devices, it can cause behaviors that are unpredictable and potentially damaging. They are discussed in detail in the following sections.

#### C. SINGLE EVENT EFFECTS

SEEs occur when high-energy particles pass through microelectronic device and deposit enough energy to cause a transistor to change state. In most cases this is a transient effect occurring only long enough for the charge to be absorbed by the system. The transistor's state change can lead to latchup in parasitic transistors, high current state in a power transistor, or can be latched into a storage element. These three main types of SEE in complimentary Metal Oxide Semiconductors (CMOS) are discussed in the following sections [Ref. 3].

#### 1. Single Event Upset

An SEU is an unpredicted change of state or "bit flip" caused by a high-energy particle passing through a device. In a microprocessor a bit flip could cause a processor

to branch to an unexpected location in memory thus causing a program to crash. In microprocessors, SEUs are typically grouped into two types: program run errors and data errors. Program run errors are errors that occur in control logic, program counter, or any other register that determines the state of processor. Data errors are typically confined to data registers and cache. These two types of error are not necessarily exclusive. A data error could occur in a register that is later used as a program address. When the microprocessor reads the address held in that register it is going to run the wrong code located at that address or even an invalid address [Ref. 3].

#### 2. Single Event Latchup (SEL)

Integrated circuits are made by combining adjacent p-type and n-type regions into transistors. By the nature of the process, parasitic transistors are formed along alternate paths through the circuit. Normally, these parasitic transistors are biased off by the circuit design. Latchup occurs when the charge, such as that produced by a particle, activates one of these parasitic transistors, which forms into a circuit with large positive feedback. This creates a short circuit across the device, with two possible outcomes. The first is the current drawn through the parasitic transistor generates more heat than the device can dissipate and burns out. If the device is able to dissipate the heat, the large amount of current drawn through the parasitic transistor prevents the circuit from functioning correctly, which is a non-destructive SEL. The normal symptom of a non-destructive SEL is a hung system, which requires power to be cycled before proper operations can be restored [Ref. 3].

#### 3. Single Event Burnout (SEB)

SEB is another condition that can cause device destruction. It is caused by a single ion that induces a high current state in a MOSFET destroying the circuit [Ref. 3].

#### D. PURPOSE

One approach to building radiation tolerant electronics is to design and build them on an electrical insulator. The process of building on an electrically insulator is often called radiation hardening (Radhard). Another approach to fault tolerant computing is to design a fault tolerant architecture. The goal of this research is the testing and implementation of a fault tolerant computer system using a COTS programmable digital signal processor that is capable of operating in the presence of radiation induced SEUs.

This design does not take into account total dose radiation, which is a factor that usually limits the operational lifetime of spacecraft electronics. This factor is determined by the electrical properties of solid-state components exposed to radiation over a period of time. Ultimately the long exposure to radiation leads to changes in the component parameters outside of design specifications and causes the circuit to cease proper functioning. This factor must be addressed by spacecraft shielding, component selection and survivability, and not by system architecture. Other factors that must be addressed are SEL and SEB. These two phenomena can be limited by external power monitoring devices. Implementation of power monitoring devices will be left to follow-on studies.

Successful completion of this project will lead to numerous benefits for the space community. First, the adage of faster better cheaper can be utilized in the development of spacecraft. The spacecraft engineer will have a broader choice of devices and software to

choose from at a reduced cost. The spacecraft design will no longer be restricted to the use of radhard components.

Second, the fault tolerant system can be utilized as a testbed to analyze software fault tolerant programs. The fault tolerance hardware is able to detect the SEU and log the time and kind of an upset. The software can then be observed in the manner in which it handles the error. This testbed will allow the testing of software in a simulated space environment prior to use in orbit.

Last, the system can be utilized as a hybrid fault tolerant computer system. In this configuration, the processor is additionally monitored for SEU. Upon detecting an upset, the processor is restored to the state prior to the upset. The processor then continues execution from the point prior to the upset with little downtime and no loss of data. This is dramatically different from current operations where a processor is reset when an error occurs, resulting in downtime, loss of data and/or spacecraft availability. As shown, this is a major advance in the handling of spacecraft system failures.

#### E. RADHARD VERSUS COTS

The radiation effects discussed in the previous sections, with the exception of SEUs, are destructive in nature. The main way of reducing their effects is by utilizing radiation hardened (radhard) devices or by providing shielding. A radhard device is one that is specifically designed to be able to withstand higher amounts of radiation than standard commercial parts.

Determining the suitability of commercial-off-the-shelf (COTS) signal processor for space applications is a subject of ongoing research. To adapt COTS devices for space

a limited amount of radiation hardening is necessary to resist the effects of TID, SEL, and SEB. There are multiple reasons for utilizing a COTS device in the harsh environment of space. This section will present a few of the rationale leading to the use of COTS.

#### 1. Cost of Development of Radhard Devices

The small percentage of the overall market that requires radhard components puts severe economic constraints on the companies that produce these devices. The number of companies developing and marketing radhard devices is rapidly on the decline and the remaining companies are not developing new chip designs. For these reasons, the development of radhard devices is lagging behind state of the art technology by two or more generations. As an example, a spacecraft launched into space at present would have at best the equivalent of a Analog Devices ADSP-21020 25 MHz DSP that can execute 50 MFLOPS sustained performance compared to the current generation Texas Instrument (TITM) TMS320C6701 167 MHz processor that can execute sustained performance 668 MFLOPS. This entire order of magnitude difference in processor capability makes the COTS processor especially appealing [Ref. 8 and 9].

#### a. High development Cost of Radhard Devices

Low demand and little profit exist in the production of radhard devices, which has led to many manufacturers abandoning their production of radhard devices in favor of the more lucrative, higher volume consumer electronics. The limited availability of these devices then leads to an inflation of the cost. Part cost directly impacts the cost of the product. In a time of shrinking budgets, the spacecraft engineer is looking for a

cheaper suitable product. The best alternative is the development of hardware and software fault tolerant designs with non-radhard COTS [Ref. 3].

To produce the radhard ADSP-21020 (RH-21020) required 22 months from the beginning of the process to having a working prototype for delivery. This was a successful transfer of a commercial design to a radhard process. There was a tremendous amount of money and resources that were dedicated by the Air Force Research Laboratory (AFRL), Analog Devices and Lockheed Martin to jointly transfer the technology from standard silicon design to a radhard design. Though this was successful, it was very risky and had it not succeeded, all of those resources would have been wasted. Even with the backing of the AFRL the program for the technology transfer ran short of funding and a complete debugging of test programs and test patterns could not be completed [Ref. 8].

#### b. Cost for Software

Even the use of a commercial design for a radhard process does not guarantee that the software will be fully compatible. Advertised as a fully compatible family of processors, the earlier generations of ADSP-21xxx are actually of an older design, which have fewer functions without all the capabilities of the new processors in the normal 21xxx family. Therefore, modifications to the software will be required. Furthermore, the older design will require extensive testing, all of which adds to the cost of choosing a radhard design.

#### 2. Benefits of Radhard

With the use of a radhard device, a known error rate can be calculated and compared with COTS. One error every ten years is achievable in radiation tolerant designs. This compares to a COTS device that can have an error rate of anywhere between several an hour to several a day or more [Ref. 9]. Radhard devices are also designed for the rigorous space environment of wide temperature swings and high vibrations. COTS devices may have a much narrow window of tolerances.

#### 3. Cost of Using COTS

Since COTS devices are susceptible to radiation effects, a device will first need to be tested for its tolerance to destructive effects of radiation, such as TID, SEL and SEB.

Once a suitable commercial product is found, its implementation will still require protection from SEU. This can be achieved either through software redundancy, hardware redundancy or a combination of the two. It is notable that a software redundancy is not always a useful solution for microprocessors, because each instruction would have to be executed at least twice and then results compared. This effectively cuts the processor speed by a minimum of one-half. Hardware redundancy also has its drawbacks. It requires an increase in power, circuit size and weight.

#### 4. Benefits of COTS

The most apparent benefits of using COTS are lower cost of components, little or no need for special software, no restrictions on availability, faster processor speeds, and use of current design ICs. Because of the use of COTS we have eliminated the costly and

time consuming design phase of transferring a technology to a radhard design and replaced it with a cheaper and faster screening process of radiation testing of commercial devices. By using current generation processors, the COTS processor has better availability and fastest processing speeds than radhard processors. There will also be extensive technical support by the manufacture that is not always available in older radhard processor designs.

#### F. RELATED WORK

The investigation into use of COTS is an on going research project at the Naval Postgraduate School. There are many ways to mitigate the harmful affects of a SEU. Triple Modular Redundant (TMR) systems are an accepted means of dealing with the affects of SEU; a detailed discussion follows in this thesis. Prior work includes the following theses. LT John Payne, USN, this work included the initial proposal for a TMR system for a microprocessor, based upon the IDT<sup>TM</sup> R3081 [Ref. 2]. Capt. Dave Summer's, USMC, thesis continued upon John's work by implementing the design into programmable logic devices and completing the design [Ref. 4]. Capt. Summer's work finalized the layout of the system architecture and it was built for testing. Capt. Susan Groening, USMC and LT Kimberly Whitehouse, USN designed the operating system and interrupt handling routine necessary to operate a TMR R3081 [Ref. 5]. LT Damen Hofhienz, USN, followed the previous work by verifying the layout and tested the printed TMR circuit board [Ref. 3]. LT Hofhienz' work also included recommendations for a space-flight-ready design as a follow on. LTjg Huseyin Ekin, Turkish Navy, is conducting research into adapting a 64-bit microprocessor vice the 32-bit microprocessor

that was used in the previous TMR design. This thesis adapts the TMR design to a COTS 32-bit programmable digital signal processor.

#### G. THESIS ORGANIZATION

The organization of this thesis follows the design approach used in developing the system. Chapter I has been a brief introduction of the environment in which the system will be operating. Chapter II is a discussion on processor selection and justification.

Chapter III considers effect of SEU and architectural solutions to corruption of the processor's operation. Chapter IV will present the triple modular redundant testbed design. Chapter V presents the conclusions developed during this research and discusses topics for follow-on work.

#### II. PROCESSOR SELECTION

#### A. CHARACTERISTICS

The logical place to start to design a general-purpose digital signal processing system is to set some system parameters. Since this DSP system is to be used as a design test-bed, it is unknown how it ultimately will be implemented. Therefore, the design includes as many possible configurations to allow a following designer greater flexibility. As a rule for this project as many functions of the digital signal processor as possible will be implemented. Some other basic requirements are that it must have floating point capabilities and be programmable.

# B. GENERAL PURPOSE DIGITAL SIGNAL PROCESSOR VS GENERAL PURPOSE MICROPROCESSOR

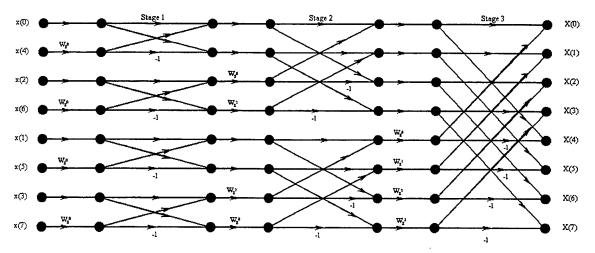

So, why use a general purpose DSP over an already proven general-purpose microprocessor? The answer to this question requires a review of how DSP is performed. The core of DSP relies upon the use of the Fast Fourier Transform (FFT) and filtering, both of which have very repetitive simple mathematics structures. A FFT is shown in Figure 1 [Ref.1].

Figure 1. Eight Point Radix-2 FFT [From: Ref. 1].

An important aspect of the FFT structure is the repetitive nature of the algorithm. A closer look at the example of an eight point FFT in Figure 1 reveals that in order to complete stage one, 8 real multiplies and 12 real adds are required, resulting in 8 complex numbers. Stage two and beyond require 16 real multiplies and 40 real adds, resulting in 8 complex numbers. Table 1 demonstrates how much computational power is required to do the basic FFTs. To maximize throughput, it is best to keep as many of the objects being operated on either in registers or on-chip memory.

| Real Multiplications |         |         | Real Additions |         |         |         |

|----------------------|---------|---------|----------------|---------|---------|---------|

| n                    | Radix 2 | Radix 4 | Radix 8        | Radix 2 | Radix 4 | Radix 8 |

| 16                   | 24      | 20      |                | 152     | 148     |         |

| 32                   | 88      |         |                | 408     |         |         |

| 64                   | 264     | 208     | 204            | 1032    | 976     | 972     |

| 128                  | 712     |         |                | 2504    |         |         |

| 256                  | 1800    | 1392    |                | 5896    | 5488    |         |

| 512                  | 4360    |         | 3204           | 13566   |         | 12420   |

| 1024                 | 10248   | 7856    |                | 30726   | 28336   |         |

Table 1. Real additions and Multiplications Required to Perform an N Point FFT [From: Ref. 1].

Since it is inevitable that results will need to be stored to memory, an efficient means of storage is necessary. With general-purpose processors, all addressing is either

linear direct addressing or linear indirect addressing. In the FFT it is desirable to store data in a circular buffer, stepped through by a constant value. A general-purpose digital signal processor allows for circular addressing and removes the required overhead needed to achieve the same results as a general-purpose microprocessor would.

#### C. SIZE, PINOUT, POWER

In a design for space applications, the size, pinout and power consumption are important factors affecting a spacecraft's cost. A spacecraft can cost between 50,000-70,000 dollars per kilogram when placed into orbit. A higher power requirement for any given device demands increased amounts of solar cells and batteries. Therefore, this adds to the overall weight of the design and thus increases the costs. Likewise, the more pins required directly effects the size of the device and therefore more space will be required, increasing the weight of the spacecraft. These three factors are important to a spacecraft's design consideration and cannot be ignored [Ref. 2].

#### D. ON-CHIP MEMORY SIZE

It is very common in DSP that a short section of program code will be executed many times over a large group of data. In order to help decrease the processing time, it is important to be able to have single-cycle-access-times to memory in order to avoid halting the CPU to wait for data. On-chip memory often has multiple busses that allow for multiple access to internal memory. With multiple busses to memory, two different functional units can access two different memory locations in one clock-cycle. This is something that cannot be achieved with a single 32-bit external-memory-bus.

#### E. SPEED

The speed of a processor is not strictly determined by the clock rate; it is a combination of on-chip memory access time, CPU speed, ability to transfer large blocks of data and the speed with which the processor interacts with external devices and memory. With higher CPU clock speeds, a more robust set of applications can be performed. In analyzing speed performance for a DSP system, it is more important to focus on number of clock cycles (time) to execute a radix-2 FFT than it is to focus on how many floating-point operations per second (FLOPS).

#### F. PROCESSOR REVIEW

As part of this research, several digital signal processors were analyzed based on the discussion in the preceding section. Table 2 contains the data concerning the two final DSP that were considered in developing the testbed [Ref. 6].

| Feature                          | TMS320C6701                                  | ADSP-21060                                   | Feature                                   | TMS320C6701                                                             | ADSP-21060                                               |

|----------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|

| IEEE Floating point support      | Yes                                          | Yes                                          | Accumulator Size                          | 80                                                                      | 80                                                       |

| Native 32 fixed point<br>support | Yes                                          | Yes                                          | 64 bit product                            | Yes                                                                     | Yes                                                      |

| Internal SRAM size               | 1 Mbit                                       | 4 Mbit                                       | Register file to memory bandwidth         | 128 bits/cycle                                                          | 64 bits/cycle                                            |

| Dual ported internal memory      | No                                           | Yes                                          | Software loops                            | Required to be non interruptible for                                    | Fully interruptible for                                  |

| Number of serial ports           | 2                                            | 2                                            | Complexity of hand-<br>optimized assembly | Highly complex,<br>must be written in<br>non-single<br>assignment form  | Algebraic<br>assembly<br>language, easy<br>to understand |

| Multiprocessing support          | Supported in 2<br>ways, cluster and<br>links | Supported in 2<br>ways, cluster and<br>links | Number of circular buffers supported      | 8 (only two<br>different lengths<br>allowed, has to be<br>power of two) | 32 (different<br>length for each<br>buffer allowed)      |

| DMA Channels                     | 4                                            | 10                                           | Conditional execution                     | Requires general purpose register                                       | All instructions are conditional                         |

| Zero overhead DMA                | No (there is cycle stealing from the         | Yes                                          | FIR filter code size                      | 100 instructions (assumed)                                              | 25 instructions                                          |

| Number of registers              | 32                                           | 16                                           | Typical power dissipation                 | Not Available                                                           | 1.5 W at 3.3V                                            |

| Package Size                     | 352 ball,<br>35mmX35mm                       | 225 ball, 23mm on<br>a side                  |                                           |                                                                         |                                                          |

Table 2. Digital Signal Processors.

The processor chosen was the TMS320C6701 general-purpose digital signal processor manufactured by Texas Instruments (TITM). The reasons for this selection were many. From the outset of this research project, the intent was to choose a COTS device for the TMR design. The '6701 is a COTS device, single chip, Harvard Architecture, with a 32-bit data bus and a 19-bit address bus. The processor has many glueless interfaces to external devices therefore minimizing the need for additional off chip control logic. This latter feature is also true of the Analog Devices ADSP-21060.

The determining factor was the failure of ADSP-21060 in a radiation environment [Ref. 10]. While the 6701 has not yet been tested, pending funds Dr. James Anderson of

Anderson of the Massachusetts Institute of Technology will test it. The outcome of those tests will determine how far this project can proceed, because TID, SEB or destructive SEL are a function of the processor's manufacture and cannot be corrected with extra hardware or software. However, it should be noted that some radiation effects could be diminished with shielding, as with a piece of aluminum.

#### G. CHARARACTERISTICS OF THE SELECTED PROCESSOR

The TMS320C6701 is intended to provide high-speed floating-point signal processing. It is a modified Harvard Architecture device. It has an instruction set that is similar to a reduced-instruction-set-computer (RISC), which employs load/store architecture. It operates on low voltage (3.3 V) and has power-down capabilities to conserve power. It also has many glueless architecture features built into the processor to reduce the number of off-chip components. This decreases the size and power requirements for external ICs which would be required to implement the design. Some of the features of TMS320C6701 include: [Ref. 9]

- 8.3 or, 6.7 ns Instruction Cycle Time (selectable)

- Eight 32-Bit Instructions/Cycle

- 1 GFLOPS

- Very Long Instruction Word (VLIW) 'C67x CPU Core

- Eight Highly Independent Functional Units:

- Four ALUs (Floating- and Fixed-Point)

- Two ALUs (Fixed-Point)

- Two Multipliers (Floating- and Fixed-Point)

- Load-Store Architecture With 32 32-bit general-purpose registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Hardware Support for IEEE Single-Precision Instructions Floating-Point

- Hardware Support for IEEE Double-Precision Instructions Floating-Point

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 512K-Bit Internal Program/Cache (16K 32-Bit Instructions)

- 512K-Bit Dual-Access Internal Data (64K Bytes)

- 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- 52M-Byte Addressable External Memory Space

- Four-Channel Bootloading

- Direct-Memory-Access (DMA) Controller with an Auxiliary Channel

- 16-Bit Host-Port Interface (HPI) with access to Entire Memory Map

- Two Multichannel Buffered Serial Ports (McBSPs)

- Up to 256 Channels Each

- Two 32-Bit General-Purpose Timers

- Flexible Phase-Locked-Loop (PLL) Clock Generator

- 352-Pin Ball Grid Array (BGA) Package (GJC Suffix)

- 0.18-mm/5-Level Metal Process

- CMOS Technology

- 3.3-V I/Os, 1.8-V Internal (120-, 150-MHz)

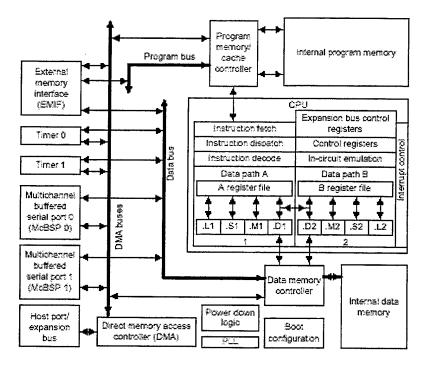

Figure 2 shows a block diagram of the TMS320C6701 DSP.

Figure 2. Block Diagram TMS320C6701 [From: Ref. 12].

### 1. The CPU

The CPU is a 32-bit RISC type floating/fix point execution engine, capable of executing one to eight instructions per clock cycle. It has a variable stage pipeline that can execute an instruction from a minimum of 7 stages to a maximum of 14 stages dependent upon the type of instruction. The CPU is divided into two execution paths, A and B. Each execution path contains functional units L, S, M, and D. It also includes 32 32-bit registers that are divided into two groups of 16 registers, one servicing data path A and the other servicing data path B [Ref. 12].

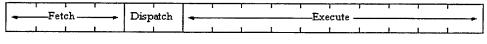

### a. Pipeline Structure

All instructions flow through the fetch, decode, and execute stages of the pipeline. The fetch stage of the pipeline has four phases for all instructions, and the decode stage has two phases for all instructions. The execute stage of the pipeline requires a varying number of clock cycles, depending on the type of instruction. The stages for '6701 are show in Figure 3.

Figure 3. Pipeline Stages [From: Ref. 10].

(1) Program Fetch. Program fetch occupies the first 4 cycles of the pipeline, and consists of program address generation, program address send, program access ready wait, program fetch packet receive. It is important to note that the processor fetches eight instructions each time a program fetch cycle is initiated, so all fetch

addresses end with two zeros. Therefore if a program branches to a location that ends in other than double zero it will read the instructions prior to the branch location and discard the unnecessary instructions [Ref. 10].

(2) Instruction Dispatch. The instruction dispatch phase of the pipeline consists of two stages: the instruction dispatch and instruction decode. When a program is compiled, the program is broken into execution packets. An execution packet is a set of instructions that can be executed in parallel. To distinguish instructions that can be executed in parallel, a "1" will be placed in the last digit of the instruction, and up to eight instructions can be executed at once. Instruction dispatch is responsible for assigning an instruction to an execution unit. Again, the unit to be used is predetermined at compile time [Ref. 10].

(3) Execution. The execution phase can range from one to ten clock cycles, depending on what type of instruction is being executed. Parallel instructions entering the execution stage of the pipeline may complete at different clock cycles. Due to the different number of cycles for each instruction, there are no pipeline interlocks, and therefore any interdependencies must be taken care of at compile time [Ref. 10].

### b. Register File

The general-purpose register file is broken into two groups, each with 16 32-bit registers. Group A registers service the A data path and B registers service the B data path. The '6701 general-purpose register files support data ranging in size from packed 16-bit data through 40-bit fixed-point and 64-bit floating-point data. Values

larger than 32 bits, such as 40-bit long and 64-bit float quantities, are stored in register pairs. In these the 32 LSBs of data are placed in an even-numbered register and the remaining 8 or 32 MSBs in the next upper register (which is always an odd-numbered register) [Ref. 10].

### c. Functional Units

The eight functional units in the '6701 data paths can be divided into two groups of four; each functional unit in one data path is almost identical to the corresponding unit in the other data path. The functional units are described in Table 3 [Ref. 10].

| Functional Unit         | Fixed-Point Operations                                                    | Floating-Point Operations                                                            |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| .L unit (.L1,           | 32/40-bit arithmetic and compare operations                               | Arithmetic operations                                                                |  |  |  |  |

| .L2)                    | 32-bit logical operations                                                 | DP SP, INT DP, INT SP                                                                |  |  |  |  |

|                         | Leftmost 1 or 0 counting for 32 bits                                      | conversion operations                                                                |  |  |  |  |

|                         | Normalization count for 32 and 40 bits                                    | İ                                                                                    |  |  |  |  |

|                         | Byte shifts                                                               |                                                                                      |  |  |  |  |

|                         | Data packing/unpacking                                                    | -                                                                                    |  |  |  |  |

|                         | 5-bit constant generation                                                 |                                                                                      |  |  |  |  |

|                         | Dual 16-bit arithmetic operations                                         | 1                                                                                    |  |  |  |  |

| ļ                       | Quad 8-bit arithmetic operations                                          |                                                                                      |  |  |  |  |

|                         | Dual 16-bit min/max operations                                            |                                                                                      |  |  |  |  |

|                         | Quad 8-bit min/max operations                                             |                                                                                      |  |  |  |  |

|                         |                                                                           |                                                                                      |  |  |  |  |

| .S unit (.S1, .S2)      | 32-bit arithmetic operations                                              | Compare                                                                              |  |  |  |  |

|                         | 32/40-bit shifts and 32-bit bit-field operations                          | SP DP conversion operations                                                          |  |  |  |  |

| in in the second        | 32-bit logical operations                                                 | Absolute value operations                                                            |  |  |  |  |

|                         | Branches                                                                  | Reciprocal and reciprocal square-                                                    |  |  |  |  |

|                         | Constant generation                                                       | operations                                                                           |  |  |  |  |

|                         | Register transfers to/from control file (.S2 only)                        |                                                                                      |  |  |  |  |

|                         | Byte shifts                                                               |                                                                                      |  |  |  |  |

|                         | Data packing/unpacking                                                    |                                                                                      |  |  |  |  |

|                         | Dual 16-bit compare operations                                            |                                                                                      |  |  |  |  |

|                         | Quad 8-bit compare operations                                             |                                                                                      |  |  |  |  |

|                         | Dual 16-bit shift operations  Dual 16-bit saturated arithmetic operations |                                                                                      |  |  |  |  |

|                         | Quad 8-bit saturated arithmetic operations                                |                                                                                      |  |  |  |  |

| M unit ( M1 M2          | 2) 16 x 16 multiply operations                                            | 32 X 32-bit fixed point multiply                                                     |  |  |  |  |

| (,                      | 16 x 32 multiply operations                                               | operations                                                                           |  |  |  |  |

|                         | Quad 8 x 8 multiply operations                                            | Floating-point multiply operations                                                   |  |  |  |  |

|                         | Dual 16 x 16 multiply with                                                | 1 Toating-point multiply operations                                                  |  |  |  |  |

|                         | add/subtract operations                                                   |                                                                                      |  |  |  |  |

|                         | Quad 8 x 8 multiply with add operation                                    |                                                                                      |  |  |  |  |

|                         | Bit expansion                                                             |                                                                                      |  |  |  |  |

|                         | Bit interleaving/de-interleaving                                          |                                                                                      |  |  |  |  |

|                         | Variable shift operations                                                 |                                                                                      |  |  |  |  |

|                         | Rotation                                                                  |                                                                                      |  |  |  |  |

|                         | Galois Field Multiply                                                     |                                                                                      |  |  |  |  |

| .D unit (.D1,           | 32-bit add, subtract, linear and circular                                 | Load doubleword with 5-bit offset                                                    |  |  |  |  |

| D2)                     | address calculation                                                       |                                                                                      |  |  |  |  |

|                         | Loads and stores with 5-bit constant offset                               |                                                                                      |  |  |  |  |

|                         | Loads and stores with 15-bit constant offset (D2 only)                    |                                                                                      |  |  |  |  |

|                         | Load and store double words with 5-constant                               |                                                                                      |  |  |  |  |

|                         | Load and store double and non-aligned words                               |                                                                                      |  |  |  |  |

|                         | 5-bit constant generation                                                 |                                                                                      |  |  |  |  |

|                         | 32-bit logical operations                                                 |                                                                                      |  |  |  |  |

| Company of the American |                                                                           | <ul> <li>Programme Anti-Programme Control (Programme Control (Programme))</li> </ul> |  |  |  |  |

Table 3. Function Units [From: Ref. 10].

## 2. Internal Program Control and Memory

The program memory controller, shown in Figure 2, provides the following functions: CPU and DMA requests to internal program memory and the required arbitration; CPU requests to external memory through the external memory interface (EMIF); and manages the internal program memory when it is configured as cache. The program memory/cache contains 64K bytes of RAM or, equivalently, 2K 256-bit fetch packets. The CPU, through the program memory controller, has a single-cycle throughput of 256-bit-wide connection to internal program memory. The memory/cache can be operated in four different modes, which are described in the paragraphs below.

### a. Mapped Mode

In mapped mode, the program fetches from the internal program-memory-addresses and returns the fetch packet from that address. In the other modes, CPU accesses to this address range return undefined data. Mapped mode is the default state of the internal program memory at reset. The CPU cannot access internal program memory through the data memory controller [Ref. 10].

### b. Cache Enabled

In cache-enabled mode, the first program fetch at an address causes a cache miss. In a cache miss, the fetch packet is loaded from the external memory interface (EMIF) and stored in the internal cache memory, one 32-bit instruction at a time. While the fetch packet is being loaded, the CPU is halted. Any subsequent read from a cached address causes a cache hit, and that fetch packet is sent to the CPU from the internal program memory without any wait states. Changing from mapped mode to cache enabled

mode flushes the program cache. This mode transition is the only means of invalidating the cache [Ref. 10].

### c. Cache Freeze

During a cache freeze, the cache retains its current state. A program read of a frozen cache is identical to a read of an enabled cache except that on a cache miss the data read from the external memory interface is not stored in the cache. Cache freeze ensures that critical program instructions are not overwritten in the cache [Ref. 10].

## d. Cache Bypass

When the cache is bypassed, any program read fetches data from external memory. The program instructions are not stored in the cache memory [Ref. 10].

## 3. Data Memory Controller and Memory

As shown in Figure 2, the data memory controller connects the CPU and the direct memory access (DMA) controller to the internal data memory and performs the necessary arbitration; the DMA connects the CPU to the External Memory Interface Controller (EMIF) and to the on-chip peripherals through the peripheral bus controller. The data memory is 64K bytes on-chip memory to store data for quick access by the CPU. There are no wait states incurred when accessing it. It cannot be operated in a cache mode. It functions strictly like any other memory. The on-chip memory is organized into two blocks of 32K bytes. The DMA and CPU can access on-chip memory simultaneously as long as they access different blocks of memory [Ref. 10].

## 4. Direct Memory Access (DMA) Controller

The direct memory access (DMA) controller transfers data between regions in the memory map without the intervention of the CPU. The DMA controller allows movement of data to and from internal memory, internal peripherals, or external devices to occur in the background of CPU operation. The DMA controller has four independent programmable channels, allowing four different contexts for DMA operation. In addition, a fifth (auxiliary) channel allows the DMA controller to service requests from the host port interface (HPI). It is important to note that the DMA can operate independently of the CPU once it has been setup. For example, the DMA can move blocks of data from a first-in-first-out (FIFO) initiated by an internal or external interrupt to internal or external memory and then reset once the data transfer is complete, all without the intervention of the CPU [Ref. 10].

#### 5. Peripheral Bus Controller

The peripherals are controlled by the CPU and the DMA controller through accesses of control registers. The CPU and the DMA controller access these registers through the peripheral data bus. The DMA controller directly accesses the peripheral bus controller, whereas the CPU accesses it through the data memory controller [Ref. 10].

#### 6. Timers

The device has two 32-bit general-purpose timers that can be used to:

- Time events

- Count events

- Generate pulses

- Interrupt the CPU

- Send synchronization events to the DMA

The timers have two signaling modes and can be clocked by an internal or an external source. The timers have an input pin and an output pin. The input and output pins, (TINP and TOUT) can function as timer clock input and clock output. They can also be configured for general-purpose input and output, respectively [Ref. 10].

# 7. Interrupt Selector

The '6701 peripheral set has up to 32 interrupt sources. The CPU however has only12 interrupts available for its use. The interrupt selector allows the designer to choose and prioritize which 12 of the 32 the system needs to use. The interrupt selector also allows one to effectively change the polarity of external interrupt inputs. Table 4 includes a list of possible interrupt source that can be used to halt the processor [Ref. 10].

| Interrupt<br>Selection Number | Interrupt Acronym | Acronym Interrupt Description   |

|-------------------------------|-------------------|---------------------------------|

| 00000b                        | DSPINT            | Host processor to DSP interrupt |

| 00001b                        | TINT0             | Timer 0 interrupt               |

| 00010b                        | TINT1             | Timer 1 interrupt               |

| 00011b                        | SD_INT            | EMIF SDRAM timer interrupt      |

| 00100b                        | EXT_INT4          | External interrupt pin 4        |

| 00101b                        | EXT_INT5          | External interrupt pin 5        |

| 00110b                        | EXT_INT6          | External interrupt pin 6        |

| 00111b                        | EXT_INT7          | External interrupt pin 7        |

| 01000b                        | DMA_INT0          | DMA channel 0 interrupt         |

| 01001b                        | DMA_INT1          | DMA channel 1 interrupt         |

| 01010b                        | DMA_INT2          | DMA channel 2 interrupt         |

| 01011b                        | DMA_INT3          | DMA channel 3 interrupt         |

| 01100b                        | XINT0             | McBSP 0 transmit interrupt      |

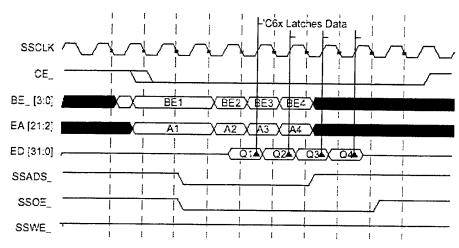

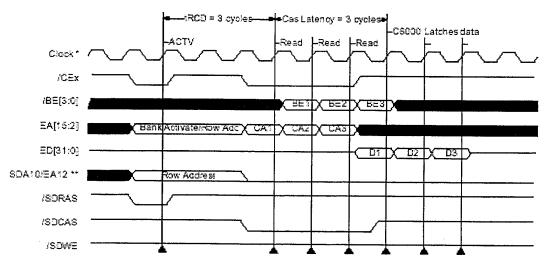

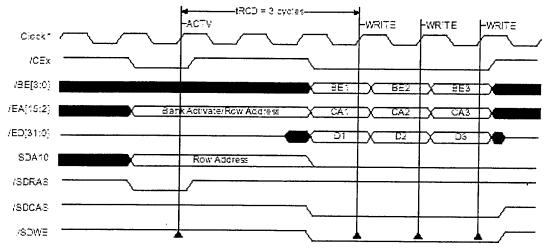

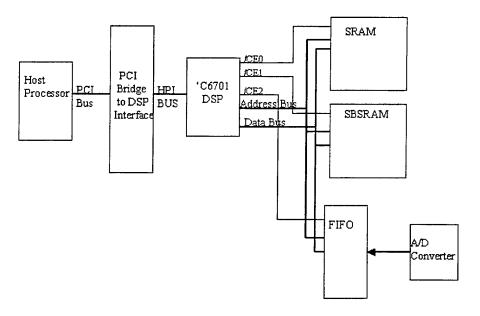

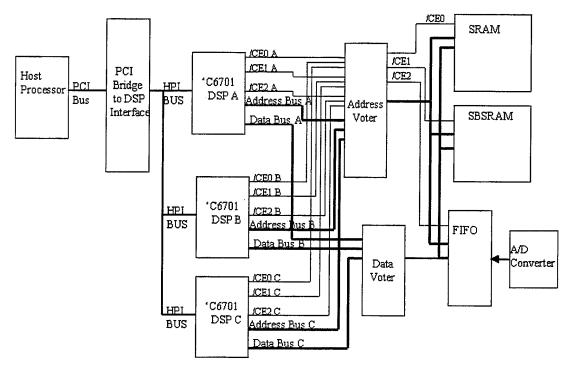

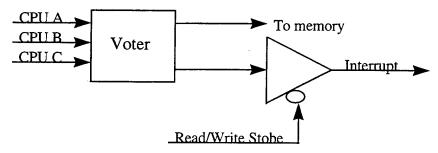

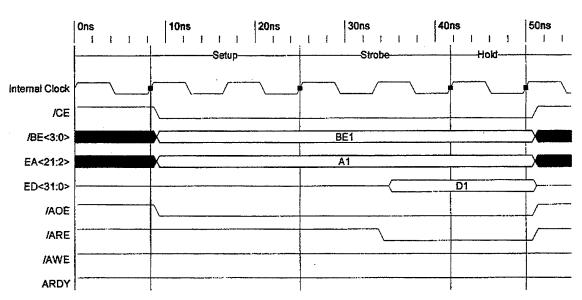

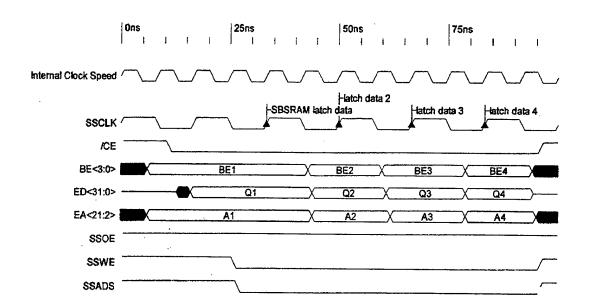

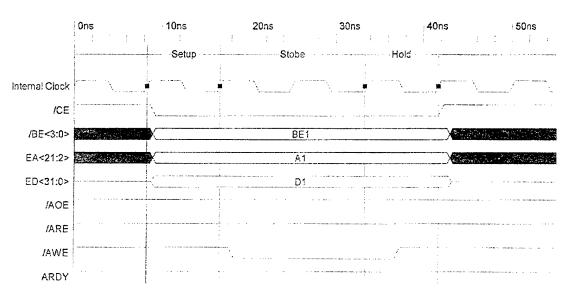

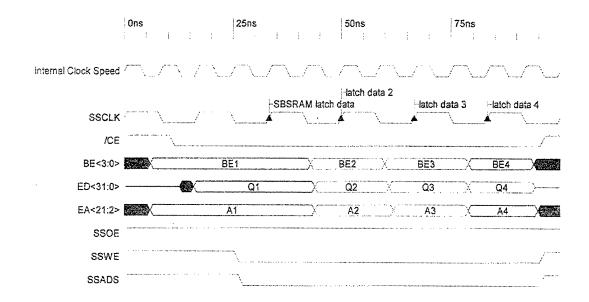

| 01101b                        | RINT0             | McBSP 0 receive interrupt       |