# NAVAL POSTGRADUATE SCHOOL Monterey, California

## **THESIS**

COMPLETION AND TESTING OF A TMR COMPUTING TESTBED AND RECOMMENDATIONS FOR A FLIGHT-READY FOLLOW-ON DESIGN

by

Damen O. Hofheinz

December 2000

Thesis Co-Advisors:

Alan A. Ross Herschel H. Loomis

Approved for public release; distribution is unlimited.

20010215 033

## REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.

| AGENCY USE ONLY (Leave blank)     Naval Postgraduate School                                      | 2. REPORT DATE December 2000             |                        | 3. REPORT TYPE AND DATES COVERED Master's Thesis       |  |

|--------------------------------------------------------------------------------------------------|------------------------------------------|------------------------|--------------------------------------------------------|--|

| 4. TITLE AND SUBTITLE Completion and Testing of a TMR Computing Tellow-on Design                 | 5. FUNDING NUMBERS                       |                        |                                                        |  |

| 6. AUTHOR(S)<br>Hofheinz, Damen O.                                                               |                                          |                        |                                                        |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND A<br>Naval Postgraduate School<br>Monterey, CA 93943-5000 | 8. PERFORMING ORGANIZATION REPORT NUMBER |                        |                                                        |  |

| 9. SPONSORING / MONITORING AGENCY NAME(                                                          | S) AND ADDRESS(ES)                       |                        | 10. SPONSORING /<br>MONITORING<br>AGENCY REPORT NUMBER |  |

| 11. SUPPLEMENTARY NOTES                                                                          |                                          |                        |                                                        |  |

| The views expressed in this thesis are those of t Defense or the U.S. Government.                | he author and do not reflect the offici- | al policy or pos       | sition of the Department of                            |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT                                                       |                                          | 12b. DISTRIBUTION CODE |                                                        |  |

| Approved for public release: distribution is unli                                                |                                          |                        |                                                        |  |

#### 13. ABSTRACT (maximum 200 words)

This thesis focuses on the completion and hardware testing of a fault tolerant computer system utilizing Triple Modular Redundancy (TMR). Due to the radiation environment in space, electronics in space applications must be designed to accommodate single event phenomena. While radiation hardened processors are available, they offer lower performance and higher cost than commercial off the shelf processors. In order to utilize non-hardened devices, a fault tolerance scheme such as TMR may be implemented to increase reliability in a radiation environment. The design that was completed in this effort is one such implementation.

The completion of the hardware design consisted of programming logic devices, implementing hardware design corrections, and the design of an overall system controller. The testing effort included basic power and ground verification checks to programming, executing, and evaluating programs in read only memory. During this phase, additional design changes were implemented to correct design flaws.

This thesis also evaluated the preliminary design changes required for a space implementation of this TMR design. This included design changes due to size, power, and weight restrictions. Additionally, a detailed analysis of component survivability was performed based on past radiation testing.

| 14. SUBJECT TERMS Fault Tolerant Computing, Triple Months Single Event Upsets (SEU) | 15. NUMBER OF PAGES                                         |                                                        |                                     |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|

|                                                                                     |                                                             |                                                        | 16. PRICE CODE                      |

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified                                  | 18. SECURITY CLASSIFICATION OF<br>THIS PAGE<br>Unclassified | 19. SECURITY CLASSIFI- CATION OF ABSTRACT Unclassified | 20. LIMITATION<br>OF ABSTRACT<br>UL |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited

# COMPLETION AND TESTING OF A TMR COMPUTING TESTBED AND RECOMMENDATIONS FOR A FLIGHT-READY FOLLOW-ON DESIGN

Damen O. Hofheinz Lieutenant, United States Navy B.S., Texas A&M University, 1994

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL December 2000

Damen O. Homen

Alan A. Ross, Thesis Co-Advisor-

Author:

Approved by:

Herschel H. Loomis, Thesis Co-Advisor

Jeffrey B. Knorr, Chairman

Department of Electrical and Computer Engineering

#### **ABSTRACT**

This thesis focuses on the completion and hardware testing of a fault tolerant computer system utilizing Triple Modular Redundancy (TMR). Due to the radiation environment in space, electronics in space applications must be designed to accommodate single event phenomena. While radiation hardened processors are available, they offer lower performance and higher cost than commercial off the shelf processors. In order to utilize non-hardened devices, a fault tolerance scheme such as TMR may be implemented to increase reliability in a radiation environment. The design that was completed in this effort is one such implementation.

The completion of the hardware design consisted of programming logic devices, implementing hardware design corrections, and the design of an overall system controller. The testing effort included basic power and ground verification checks to programming, executing, and evaluating programs in read only memory. During this phase, additional design changes were implemented to correct design flaws.

This thesis also evaluated the preliminary design changes required for a space implementation of this TMR design. This included design changes due to size, power, and weight restrictions. Additionally, a detailed analysis of component survivability was performed based on past radiation testing.

## TABLE OF CONTENTS

| I.   | INT                                          | INTRODUCTION                                             |    |  |  |  |  |  |  |

|------|----------------------------------------------|----------------------------------------------------------|----|--|--|--|--|--|--|

|      | A.                                           | A. THE SPACE ENVIRONMENT                                 |    |  |  |  |  |  |  |

|      |                                              | 1. Radiation                                             | 3  |  |  |  |  |  |  |

|      | В.                                           | SINGLE EVENT PHENOMENA (SEP)                             | 4  |  |  |  |  |  |  |

|      |                                              | 1. Single Event Upset (SEU)                              | 5  |  |  |  |  |  |  |

|      |                                              | 2. Single Event Latchup (SEL)                            | 5  |  |  |  |  |  |  |

|      |                                              | 3. Single Event Burnout (SEB)                            |    |  |  |  |  |  |  |

|      | C. COMMERCIAL-OFF-THE-SHELF VS. RADIATION HA |                                                          |    |  |  |  |  |  |  |

|      |                                              | DEVICES                                                  | 6  |  |  |  |  |  |  |

|      |                                              | 1. Forward-looking Technology                            | 7  |  |  |  |  |  |  |

|      |                                              | 2. Faster Design-to-Orbit Time                           | 7  |  |  |  |  |  |  |

|      |                                              | 3. Reduced Cost                                          |    |  |  |  |  |  |  |

|      | D.                                           | PURPOSE                                                  |    |  |  |  |  |  |  |

|      | <b>E.</b>                                    | THESIS ORGANIZATION                                      | 9  |  |  |  |  |  |  |

| II.  | BAC                                          | BACKGROUND                                               |    |  |  |  |  |  |  |

|      | A.                                           | FAULT TOLERANCE                                          |    |  |  |  |  |  |  |

|      | ~                                            | 1. Time Redundancy                                       |    |  |  |  |  |  |  |

|      |                                              | 2. Software Redundancy                                   |    |  |  |  |  |  |  |

|      |                                              | 3. Passive Redundancy                                    |    |  |  |  |  |  |  |

|      |                                              | 4. Hardware Redundancy                                   |    |  |  |  |  |  |  |

|      |                                              | a) Triple Modular Redundancy (TMR)                       |    |  |  |  |  |  |  |

|      | В.                                           | TMR MICROPROCESSOR DESIGN                                |    |  |  |  |  |  |  |

|      |                                              | 1. Hardware Design and Operation                         | 17 |  |  |  |  |  |  |

|      |                                              | 2. Fault Detection                                       | 18 |  |  |  |  |  |  |

|      | C.                                           | DESIGN IMPLEMENTATION                                    | 19 |  |  |  |  |  |  |

|      |                                              | 1. Design Hardware Changes                               | 20 |  |  |  |  |  |  |

|      |                                              | 2. Final Design                                          | 20 |  |  |  |  |  |  |

| III. | PRC                                          | OGRAMMABLE LOGIC DESIGN AND TESTING                      | 23 |  |  |  |  |  |  |

|      | A.                                           | PLD PROGRAMMING                                          |    |  |  |  |  |  |  |

|      |                                              | 1. Memory Controller PLD                                 |    |  |  |  |  |  |  |

|      |                                              | 2. Memory Enable PLD                                     |    |  |  |  |  |  |  |

|      | В.                                           | PLD TESTING                                              |    |  |  |  |  |  |  |

|      | C.                                           | FPGA PROGRAMMING                                         |    |  |  |  |  |  |  |

| TX7  | DEC                                          |                                                          |    |  |  |  |  |  |  |

| IV.  |                                              | DESIGN OF THE SYSTEM CONTROLLER FPGA                     |    |  |  |  |  |  |  |

|      | <b>A.</b>                                    | CUART STATE INIT MACHINE  1. State Machine Functionality |    |  |  |  |  |  |  |

|      | D                                            |                                                          |    |  |  |  |  |  |  |

|      | В.                                           | VOTE MACHINE                                             |    |  |  |  |  |  |  |

|      |                                              | 1. Voter Interrupt routine                               | 54 |  |  |  |  |  |  |

|      |                     |                 | <i>a</i> ) | INTRCNTR                    | 35     |  |  |  |  |

|------|---------------------|-----------------|------------|-----------------------------|--------|--|--|--|--|

|      |                     | 2.              | UAR        | RT Interrupt Routine        | 36     |  |  |  |  |

|      |                     | 3.              | State      | e Machine Design Constraint | 37     |  |  |  |  |

|      | C.                  | CON             |            | MODE STATE MACHINE          |        |  |  |  |  |

|      |                     | 1.              | Mod        | le Initialization           | 38     |  |  |  |  |

|      | D.                  | FIF             | O DATA     | A COLLECTION STATE MACHINE  | 40     |  |  |  |  |

|      |                     | 1.              | Data       | Collection                  | 40     |  |  |  |  |

|      | E.                  | TRA             |            | R STATE MACHINE             |        |  |  |  |  |

|      |                     | 1.              | XFE        | R State Machine             | 42     |  |  |  |  |

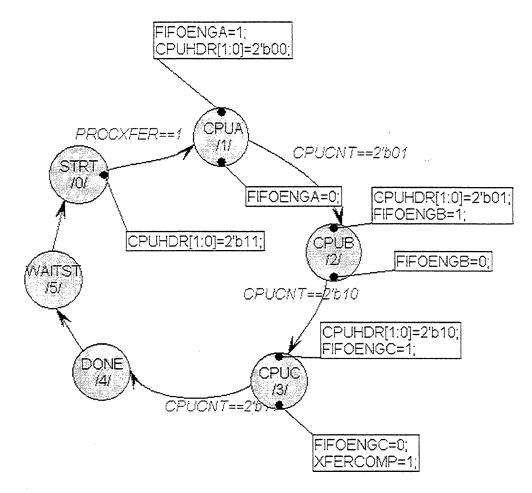

|      |                     | 2.              | CPU        | State Machine               | 43     |  |  |  |  |

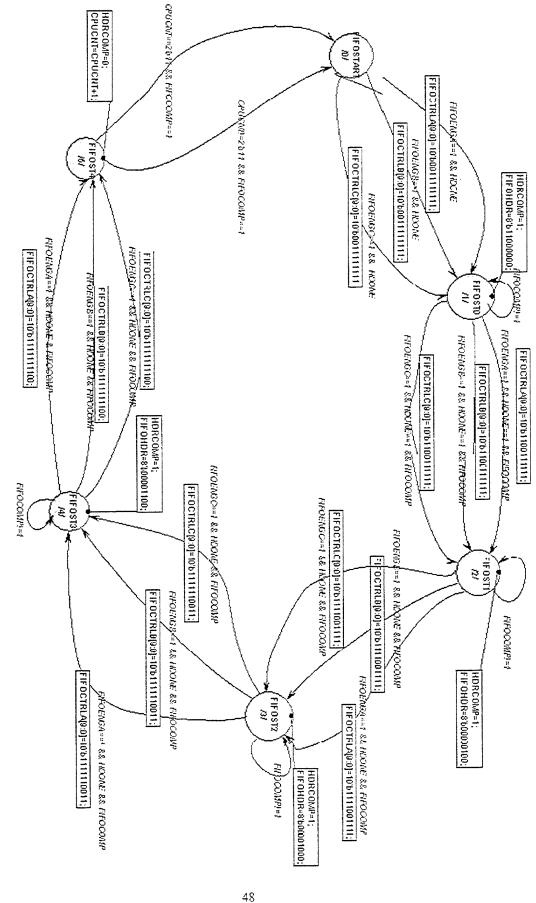

|      |                     | 3.              | FIFO       | OXFER Engine State Machine  | 45     |  |  |  |  |

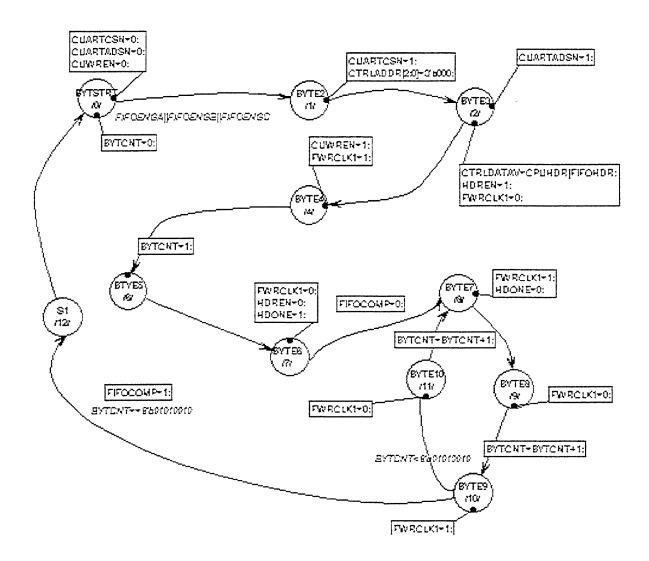

|      |                     | 4.              | BYT        | E Transfer Machine          | 49     |  |  |  |  |

| V.   | DESIGN COMPLETION53 |                 |            |                             |        |  |  |  |  |

|      | Α.                  | WH              | ITE W      | IRES                        | 53     |  |  |  |  |

|      | В.                  |                 |            | REGULATOR                   |        |  |  |  |  |

|      | ٠.                  | 1.              |            | age Regulator               |        |  |  |  |  |

|      |                     | 2.              |            | olt Bus                     |        |  |  |  |  |

|      |                     |                 |            |                             |        |  |  |  |  |

| VI.  |                     | SYSTEM TESTING5 |            |                             |        |  |  |  |  |

|      | A.                  |                 |            | HECKS                       |        |  |  |  |  |

|      |                     | 1.              |            | er Ground Testing           |        |  |  |  |  |

|      |                     | 2.              |            | k signal testing            |        |  |  |  |  |

|      | _                   | 3.              |            | et Signal                   |        |  |  |  |  |

|      | В.                  |                 |            | EVEL TESTING                |        |  |  |  |  |

|      |                     | 1.              |            | essor Initialization        |        |  |  |  |  |

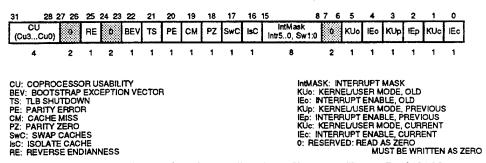

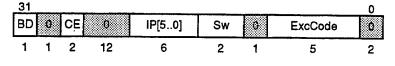

|      |                     |                 | <i>a</i> ) | Status Register             |        |  |  |  |  |

|      |                     |                 | <b>b</b> ) | The Cause Register          |        |  |  |  |  |

|      | ~                   |                 | <i>c)</i>  | Functional Testing          |        |  |  |  |  |

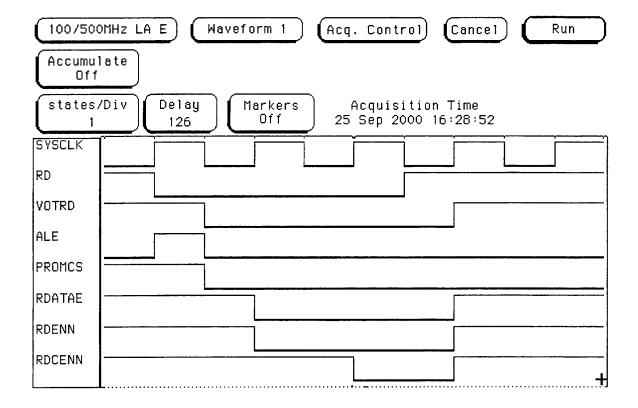

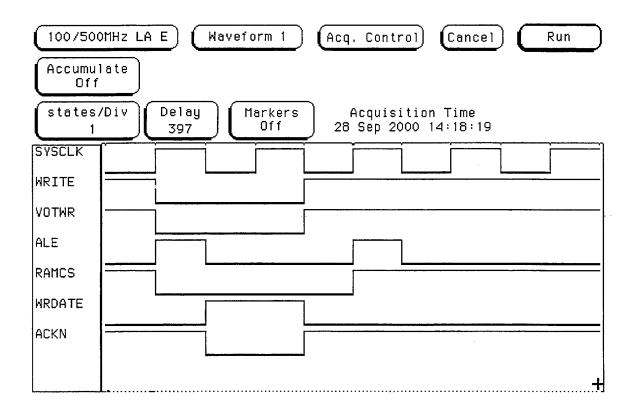

|      | C.                  |                 |            | A AND WAVEFORMS             |        |  |  |  |  |

|      |                     | 1.              |            | M Read                      |        |  |  |  |  |

|      |                     | 2.              |            | M Write                     |        |  |  |  |  |

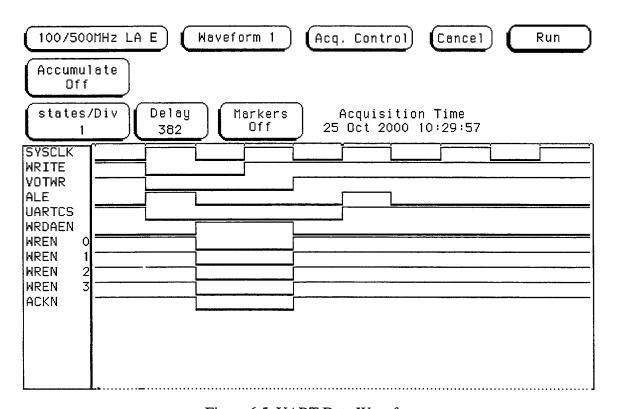

|      |                     | 3.              |            | RT DATA                     | ••• 10 |  |  |  |  |

|      |                     | 4.              | UAF        | RT INPUT/OUTPUT             | 76     |  |  |  |  |

| VII. | CON                 | VERS            | ION T      | O SPACE FLIGHT BOARD        | 79     |  |  |  |  |

|      | A.                  | CON             | NSTRA      | INTS AND TRADEOFFS          | 79     |  |  |  |  |

|      |                     | 1.              | Pow        | er                          | 79     |  |  |  |  |

|      |                     | 2.              | Size       |                             | 80     |  |  |  |  |

|      |                     | 3.              | Vibr       | ation Analysis              | 82     |  |  |  |  |

|      | В.                  | SPA             | CE FL      | IGHT PREPERATION            | 83     |  |  |  |  |

|      |                     | 1.              | Miss       | sion Parameters             | 83     |  |  |  |  |

|      |                     | 2.              | Radi       | iation Risk Assessment      | 84     |  |  |  |  |

|      |                     | 3.              | Miss       | sion Specific               |        |  |  |  |  |

|      |                     |                 | a)         | Microprocessor              | 87     |  |  |  |  |

|      |                     |                 | <b>b</b> ) | XILINX FPGA                 | 88     |  |  |  |  |

|       |       |       | c)           | Memory       | •••••             | •••••  | 89  |

|-------|-------|-------|--------------|--------------|-------------------|--------|-----|

|       |       |       | d)           |              | PROM              |        |     |

|       |       |       | e)           | FIFO         | •                 | •••••  | 91  |

|       |       |       | f)           | Assorted     | ••••••••••••••    |        | 92  |

|       | C.    | PAR   | T SEL        | ECTION       | ••••••            | •••••  | 92  |

| VIII. | CON   | CLUS  | IONS A       | ND FOLLO     | OW-ON RESEARC     | СН     | 95  |

|       | A.    | CON   | <b>ICLUS</b> | IONS         |                   | •••••  | 95  |

|       | В.    | FOL   | LOW-         | ON RESEA     | RCH               |        | 95  |

|       |       | 1.    | Com          | pletion of T | MR Implementation | n      | 96  |

|       |       | 2.    | Radi         | ation Testin | ıg                | ••••   | 96  |

| APPE  | NDIX  | A UPI | ATEL         | TMR PLD      | FILES             | •••••  | 97  |

| APPE  | NDIX  | в тм  | R SYS        | TEM CONT     | ROLLER FILES      | •••••• | 103 |

| APPE  | NDIX  | C PRO | )GRA         | M FILES      | •••••             | •••••  | 131 |

| APPE  | NDIX  | D PAF | RT SEI       | ECTION       | •••••             | •••••• | 145 |

| LIST  | OF RI | EFERE | NCES         | •••••        |                   | •••••  | 149 |

| BIBL  | IOGR. | APHY  |              | ••••••       | ••••••            | •••••• | 151 |

| INITI | AL DI | STRIF | RITIO        | NIJST        |                   |        | 153 |

### LIST OF FIGURES

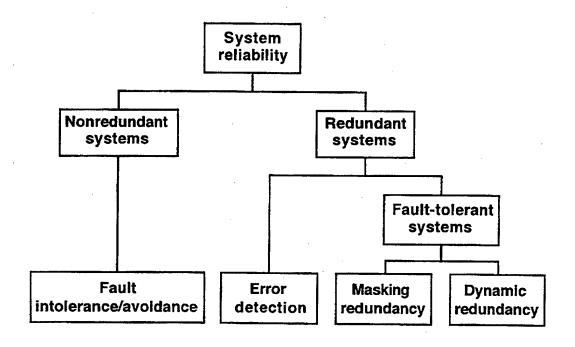

| Figure 2.1. Strategies in Designing a Reliable System. From Ref. [9]        | 12  |

|-----------------------------------------------------------------------------|-----|

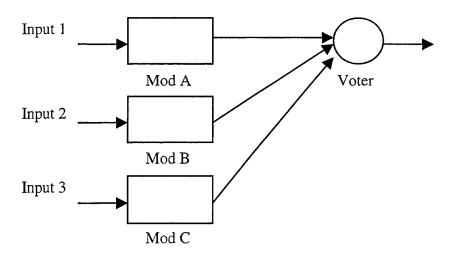

| Figure 2.2. Basic TMR Circuit Implementation. From Ref. [1]                 | 16  |

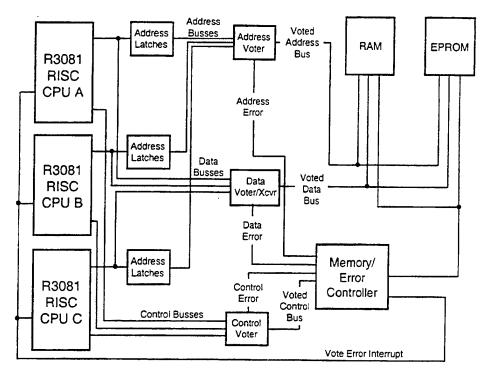

| Figure 2.5. TMR R3081 Block Diagram. After Ref. [2]                         | 21  |

| Figure 3.1. Programmable Logic Device Identifier. After Ref. [2]            | 23  |

| Figure 4.1. State Machine Hierarchy                                         | 30  |

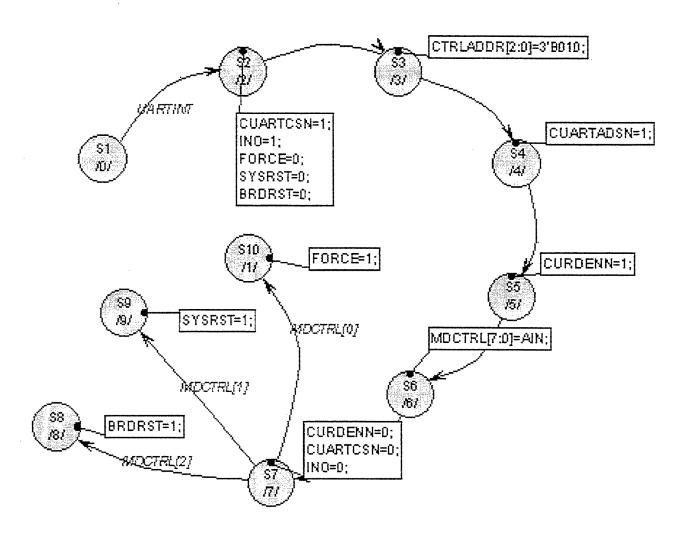

| Figure 4.2. UARTC State Machine                                             | 33  |

| Figure 4.3. VOTE State Machine                                              | 36  |

| Figure 4.4. MODECNTRL State Machine                                         | 39  |

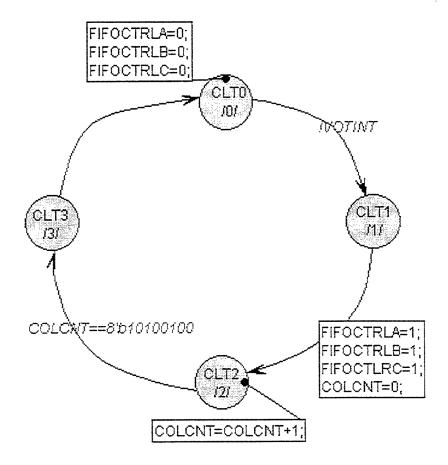

| Figure 4.5. COLLECT State Machine                                           | 41  |

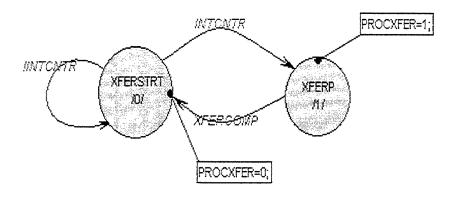

| Figure 4.6. XFER State Machine                                              | 43  |

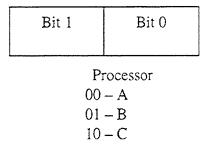

| Figure 4.7. CHDR Format                                                     | 44  |

| Figure 4.8. CPU State Machine                                               | 45  |

| Figure 4.9. FIFOCTRL Word                                                   |     |

| Figure 4.10. FIFOXFER State Machine                                         | 48  |

| Figure 4.11. BYTE Transfer State Machine                                    | 50  |

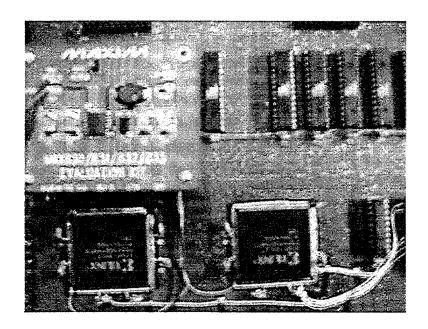

| Figure 5.1. MAXIM Voltage Regulator                                         | 57  |

| Figure 6.1. Status Register Format. From Ref. [12]                          | 64  |

| Figure 6.2. Cause Register Format. From Ref. [12]                           | 65  |

| Figure 6.3. ROM Data Waveform                                               |     |

| Figure 6.4. RAM Data Waveform                                               | 73  |

| Figure 6.5. UART Data Waveform                                              | 75  |

| Figure 7.1. Space Design Layout                                             | 82  |

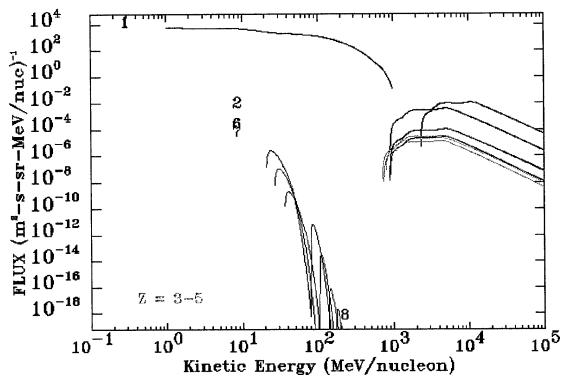

| Figure 7.2. Differential Flux of various elements vs. Kinetic Energy at the |     |

| external surface of the spacecraft Z=1 (protons) Z=8 (Oxygen)               | 86  |

| Figure A.1 MEMCONT PLD.                                                     |     |

| Figure A.2 MEMENABLE PLD                                                    | 102 |

## LIST OF TABLES

| Table 4.1. UART Control Register. From Ref. [12] | 32  |

|--------------------------------------------------|-----|

| Table 6.1.A. ROM Data List                       | 68  |

| Table 6.1.B. ROM Data List                       | 69  |

| Table 6.1.C. ROM Data List                       | 69  |

| Table 6.2.A. RAM Data List                       | 71  |

| Table 6.2.B. RAM Data List                       | 72  |

| Table 6.2.C. RAM Data List                       | 72  |

| Table 6.3.A. UART Data List                      | 74  |

| Table 6.3.B. UART Data List                      | 74  |

| Table 6.3.C. UART Data List                      | 75  |

| Table 6.3.D. UART Data List                      | 75  |

| Table 6.4.A. UART Receive Data                   | 77  |

| Table 6.4.B. UART Receive Data                   | 77  |

| Table 6.4.C. UART Receive Data                   | 77  |

| Table 6.5.A. UART Transmit Data                  | 78  |

| Table 6.5.B. UART Transmit Data                  | 78  |

| Table 6.5.C. UART Transmit Data                  | 78  |

| Table B.1. TMR Files                             | 103 |

| Table D.1. Radiation hardened Device List        | 146 |

| Table D.2. COTS Device List                      | 147 |

#### **EXECUTIVE SUMMARY**

Increased demands on satellite performance and a declining budget have forced engineers to search for cheaper and faster products. Past satellite designs were restricted to the utilization of radiation-hardened devices, today though the use of Commercial off the Shelf (COTS) devices is increasing. In order to utilize COTS devices in space though, the engineer must employ a method of increasing the reliability and redundancy of a system such as Triple Modular Redundancy.

A Triple Modular Redundancy design was previously fabricated to prove the implementation of this concept. The objectives of this research are the completion of the design and verification of proper operation. The research began with the completion and testing of the design files previously written for the programmable logic devices utilizing WINCUPL and Xilinx design software. During this phase, a design file for a PLD was modified to correct for an error. These design files were ultimately burned into the programmable logic devices.

The last step in completing the TMR board was the design and programming of the system controller FPGA. This FPGA is responsible for data input and output, board setup, and FIFO data collection. This design was accomplished utilizing the Xilinx foundation HDL and state machine tool.

With the completion of the programming and design phases, a thorough review of the design revealed a problem with the Field Programmable Array devices. The devices utilized in the design required 3.3 Voltage, while the board was designed with a 5V bus.

The addition of a voltage regulator into the board to provide the necessary voltage for the FPGAs was the final solution to this difficulty.

Upon completion of the system design corrections, initial testing of the design for proper operation consisted of basic power and ground verification checks to executing programs in read only memory. Numerous programs were written, compiled, linked, split and burned into ROM. A digital logic analyzer was used to capture program execution to verify proper read and write cycles to RAM and ROM. The captured data provided waveforms and data lists, which confirmed correct timing. The next program transmitted serial data from the 16550 UART to a PC. Initially difficulties in obtaining output led to the discovery of an incorrect device. After obtaining the new device, the correct output baud rate and data waveforms were present on the UART. The final design program captured transmitted data from the PC, added 32, and transmitted this data to the PC.

This work also focused on the preliminary design changes necessary for space implementation of the TMR design. This included design changes due to size, power, and weight restrictions. It also included a detailed analysis of component survivability based on past radiation testing.

The effort in this work completed the design and programming of the TMR logic devices and microprocessors. The waveforms and captured data supported the design implementation and predicted timing waveforms. The benefit of work on this design is the utilization of higher speed COTS microprocessors in space applications and a testbed for investigating software fault tolerant methods.

#### **ACKNOWLEDGMENTS**

The author would like to take this opportunity to thank all the people who provided the support and assistance that made this work possible.

To Captain David Summers: Your expertise provided great insight to the hardware/software interface requirements in this project. Additionally, your friendship provided the nucleus of a team that I am proud to follow in the footprints of.

To David Rigmaiden and Jim Horning: Your expertise and knowledge was appreciated in overcoming difficulties during the course of this project.

To Professor Alan Ross and Professor Herschel Loomis: Your guidance, patience and tutelage were instrumental in the completion of this portion of the project.

#### I. INTRODUCTION

Increasing the radiation tolerance of a spacecraft against the environment of space is the most important aspect in making it more survivable. Since the end of the 1980s, the Defense budget has seen a dramatic decrease in funding. This has in turn affected the research and development of radiation hardened devices by the commercial sector. Additionally, commercial companies such as Intel are reluctant to switch their foundries from production of normal microelectronics devices to radiation-hardened devices as a result of the loss in revenue. The result of this is a very limited availability of hardened devices at a high cost. Spacecraft Engineers working with lower budgets are therefore forced to look for alternative cheaper, faster and better performing methods of increasing the survivability of the Spacecraft. One alternative is the use of commercial-off-the-shelf (COTS) devices in place of radiation-hardened devices. COTS devices present spacecraft engineers with shorter design-to-launch times, lower parts costs, orders of magnitude better performance, and a wider range of available software than radiation hardened (radhard) devices. The major drawback to utilizing COTS devices in designing a spacecraft is their increased susceptibility to the effects of radiation, both total dose and single event upsets (SEUs) and system design techniques to protect them from this radiation such as increased shielding.

This thesis is a continuation of an ongoing multi-thesis project initiated by LT. Payne [Ref. 1], Capt. David Summers [Ref. 2] and Capt. Kim Whitehouse and LT. Susan Groening [Ref. 3]. It will present the concluding designs and testing of a fault tolerant

computer evaluation system including the design of the system controller. Additionally, it will also present the necessary changes for a space flight ready design.

The system is designed to perform two functions. First, it can act as a software testbed by enabling testing of fault tolerant software in the presence of radiation induced SEUs in a test chamber. This allows testing of the software algorithms in the environment they were designed to operate enabling detection and isolation of errors. Additionally, the design can be used as a combination software and hardware fault tolerant computer system. This is accomplished by utilizing the fault masking ability of the hardware with fault tolerant software. Both of these concepts will be discussed further in the body of the thesis.

#### A. THE SPACE ENVIRONMENT

As satellites become increasingly complex and versatile, the amount of electronic equipment in them grows. Care has to be taken to protect this equipment from both temporary and permanent damage from the environment. Designing equipment for space requires that the designers know the working environment. Like any environment, space dictates the characteristics of devices intended to operate there and imposes requirements on any equipment that would function there. This environment poses a risk to all earth orbiting satellites and missions to other planets in the form of electromagnetic radiation from the sun: not only visible light, but the entire range from radio to gamma rays. In addition, it is also filled with the corpuscular radiation of the sun, the solar wind. Some of this is trapped within the earth's magnetic field forming the intense radiation of the Van Allen Belts. [Ref. 1]

#### 1. Radiation

Radiation is the movement of energy through space by propagation of waves or particles. Most of the radiation in space near Earth comes from the sun, as fusion in the sun shoots particles through space. Around the planet's magnetic field, these particles become trapped or are deflected away from the planet. These particles pose a threat to the equipment of a spacecraft and can cause damage or disruptions in microelectronic devices. [Ref. 1]

These particles are either ions or photons. When an atom is hit by a fast-moving particle, an electron can be torn off producing an ion. There are two types of ions: light and heavy. The proton or light ion is the simplest positive ion and is a fundamental particle with low mass. The heavy ion or alpha particle is produced from the Helium atom. The helium atom contains two electrons, two protons, and neutrons. When the electrons are stripped away, the atom is ionized to HE++, which is known as an alpha particle. The classifications of ions as heavy or light is dependent on the atomic number of the element. All ions starting with the element Helium are classified as heavy ion. Unlike ions, photons have neither mass nor charge. X-rays are an example of photon radiation. [Ref. 4]

Multiple sources in space produce these radioactive particles. The first and largest source of radiation is the Sun, which produces solar flares and winds. Solar activity of the sun varies over an 11-year solar cycle, producing a variable average of solar particles. Though the solar activity is predictable on a macro scale, the sun still produces wide variations in radiation intensity on a day-to-day, hour-to-hour basis.

A second radiation type is Galactic Cosmic Ray or GCR, which are particles that reach near-earth from outside of the solar system. The cosmic ray consists of heavy ions produced by such events as exploding stars.

The last and largest contributor to a spacecraft's total dose is from particles trapped in the Earth's geomagnetic field, otherwise known as the Van Allen Belts. The belts are a fixed hazard to spacecraft and are distributed nonuniformly within the magnetosphere. Any satellite in orbit is subject to effects from the Van Allen Belts. [Ref. 5]

With this in mind, two factors are calculated to assist in determining the survivability of the spacecraft. The first is the total dosage, the total amount of radiation the spacecraft will be exposed to during its lifetime. The second is the dose rate effect, the amount of radiation the spacecraft is exposed to at a particular time. As the spacecraft orbits, radiation passes through it possibly affecting the spacecraft subsystems. When this radiation interacts with microelectronic devices, it can cause a malfunction known as a Single Event Phenomena, or SEP. Single event phenomena consist of three different effects, the single event upset (SEU), single-event latchup (SEL) and the single-event burnout (SEB), which are discussed in detail in the following section. [Ref. 6]

#### B. SINGLE EVENT PHENOMENA (SEP)

SEPs occur when a high-energy particle passes through the microelectronic device and deposits enough charge to cause a transistor to change state. In most cases, the transistor only changes state long enough for the charge to be absorbed back into the system and then resumes its original state. The transistor's state change can lead to latchup in parasitic transistors, high current state in a power transistor, or can be latched into a storage element. These three main types of SEP in Complimentary Metal Oxide Semiconductors (CMOS) are discussed in the following sections. [Ref. 6]

#### 1. Single Event Upset (SEU)

An SEU is an unpredicted change of state or "bit-flip" induced by an energetic particle such as a proton passing through a device. In a spacecraft computer; for example, a bit-flip could lead to a random change in critical data confusing the processor to the point it crashes. In microprocessors, SEUs are typically grouped into one of two error types: program run errors and data errors. Program run errors are errors that occur in the control logic, program counter (PC), or any other register that determines the state of the processor. Data errors are typically confined to the data registers and cache. These two types of errors are not necessarily exclusive. A data error could occur in a register that is later used as program address. When the microprocessor reads the address held in that register it is in the wrong location and begins to execute incorrect code. [Ref. 6]

#### 2. Single Event Latchup (SEL)

Integrated circuits are made by combining adjacent p-type and n-type regions into transistors. By the nature of the process, parasitic transistors are formed along alternate paths through the circuit. These parasitic transistors are biased off by the circuit design under normal circumstances. Latchup occurs when a charge, such as that produced by a particle, activates one of these parasitic transistors, which forms into a circuit with large positive feedback. This creates a short circuit across the device, with two possible outcomes. The first is the current drawn through the parasitic transistors generates more

heat than the device can dissipate and destroys it. If the device is able to dissipate the heat, the large amount of current drawn through the parasitic transistors prevents the circuit from working correctly, which is a non-destructive SEL. The normal symptom of a non-destructive SEL is of a hung system, which requires the system power to be cycled before proper operation is restored. [Ref. 6]

#### 3. Single Event Burnout (SEB)

Single Event Burnout is another condition that can cause device destruction. It is caused by a single ion, for example from a GCR, which induces a high current state in a MOSFET destroying the circuit. [Ref. 6]

## C. COMMERCIAL-OFF-THE-SHELF VS. RADIATION HARDENED DEVICES

The radiation effects discussed in the previous sections, with the exception of SEUs, are destructive in nature. The main way of reducing their effects is by utilizing radiation hardened (radhard) devices or providing shielding. A radhard device is one that is specifically designed to be able to withstand higher amounts of radiation than standard commercial parts.

Determining the suitability of commercial-off-the-shelf (COTS) microprocessor for space applications is a subject of ongoing research. There are multiple reasons for utilizing a COTS product within such a harsh environment as space. This section will present a few of the rationale leading to the use of COTS.

#### 1. Forward-looking Technology

As touched upon earlier in the introduction, the United States radiation hardened market is rapidly shrinking. The small percentage of the overall market that requires radhard components puts severe economic constraints on the companies that produce these devices. The number of companies developing and marketing radhard devices is rapidly on the decline and the remaining companies are not developing new chip designs. For these reasons, the development of radhard devices is lagging behind state of the art technology by two or more generations. As an example, a spacecraft launched in space at present would have at best the equivalent of a 486 66 MHz CPU radiation hardened microprocessor compared to the standard home computer with a modern 700 MHz Pentium III processor. This entire order of magnitude difference in processor capability makes the COTS processor especially appealing. [Ref. 7]

#### 2. Faster Design-to-Orbit Time

Parts availability is crucial in maintaining a development schedule. The limited availability of radhard devices offered by many manufacturers can lead to a delay in production schedule. By utilizing COTS devices, the production flow is maintained. The spacecraft engineer is given a wider selection of devices to utilize from multiple vendors. Additionally, the utilization of COTS allows for parts interchangeability in case of failure. This translates to less non-value-added time in the development schedule. Numerous companies are conducting radiation testing on devices, creating a growing database of devices suitable for space applications. [Refs. 7 and 8]

#### 3. Reduced Cost

Low demand and little profit exist in the production of radhard devices, which has led to many manufactures abandoning their production of radhard devices in favor of the more lucrative, higher volume consumer electronics. The limited availability of these devices then leads to an inflation of the cost. Part cost directly impacts the cost of the product. In a time of shrinking budgets, the spacecraft engineer is looking for a cheaper suitable product. The best alternative is the development of hardware and software fault tolerant designs with non-radhard COTS. [Ref. 7]

#### D. PURPOSE

The goal of this research is the testing and implementation of a fault tolerant computer system using COTS microprocessors that is capable of operating in the presence of radiation induced SEUs. This thesis specifically concentrates on the programming and initial testing of a design previously fabricated in the work reported in Reference 2.

This design did not take into account total dose radiation, which is a factor that usually limits the operational lifetime of spacecraft electronics. This factor is determined by the electrical properties of solid-state components exposed to radiation over a period of time. Ultimately the long exposure to radiation leads to changes in the component parameters outside of design specifications and causes the circuit to cease proper functioning. This factor is less stringent in the design because of spacecraft shielding, component selection and survivability.

Successful completion of this project will lead to numerous benefits for the space community. First, the adage of faster better cheaper can be utilized in the development of spacecraft. The spacecraft engineer will have a broader choice of devices and software to choose from at a reduced cost. The spacecraft design will no longer be restricted to the use of radhard components.

Second, the fault tolerant system can be utilized as a testbed to analyze software fault tolerant programs. The fault tolerance hardware is able to detect the SEU and log the time and kind of an upset. The software can then be observed in the manner in which it handles the error. This testbed will allow the testing of software in a simulated space environment prior to use in orbit.

Last, the system can be utilized as a hybrid fault tolerant computer system. In this configuration, the processor is additionally monitored for SEU. Upon detecting an upset, the processor is restored to the state prior to the upset. The processor then continues execution from the point prior to the upset with little downtime and no loss of data. This is dramatically different from current operations where a processor is reset when an error occurs, resulting in downtime, loss of data and spacecraft availability. As shown, this is a major advance in the handling of spacecraft system failures.

#### E. THESIS ORGANIZATION

The organization of this thesis follows the design approach used in developing the system. Chapter I has been a brief introduction of the environment in which the system will be operating. Chapter II is background material on research that has led to the foundation and fabrication of this design. Chapter III contains the programming, testing,

and implementation of the programmable elements of the system. Chapter IV presents the design and programming of the system controller. Chapter V presents the final steps in design completion. Chapter VI presents the steps that were taken in testing the design after manufacture. Chapter VII presents steps required to transition the current test bed design to a flight ready design. Chapter VIII presents the conclusions developed during this research and discusses topics for follow-on work.

#### II. BACKGROUND

Fault tolerance has been implemented in computers for many years. A digital system, though very reliable, does not operate fault free. When a system experiences a fault, it has to be detected and corrected. The technology of computer systems has progressed at a rapid rate and many fault tolerance requirements have been dropped in order to improve speed or performance. However, the Department of Defense requires the use of fault tolerant designs in systems that perform critical tasks, such as the control system of the F-117 stealth aircraft. A minor fault in the computer during flight would mean disaster for the aircraft. This level of performance has maintained the practice of fault tolerance methods at the forefront many of designs. [Ref. 8]

The purpose of this chapter is to provide the reader with a brief background of this project. The chapter starts by outlining the general concept of fault tolerance and focuses in on the design and implementation of this system.

#### A. FAULT TOLERANCE

There are two approaches to increase the survivability or reliability of electronics in a spacecraft, which are radiation hardening and the use fault tolerance. Figure 2.1 provides a flow diagram for the design of a reliable system. The first method, radiation hardening of devices, is simply constructing devices in such a way as to increase the total dose survivability and reduce the possibility of an SEP. Four basic ways to harden a device are with junction isolation, dielectric isolation, silicon-on-sapphire devices, and silicon-on-insulator devices. This method would relate to the left-hand side path

designing a system with fault avoidance by utilizing parts with a high reliability. This system design has increased radiation tolerance, but offers little or no redundancy.

The second method, fault tolerance, follows the right side of the figure and is simply the ability of the spacecraft to functionally operate in the presence of a fault. Fault tolerance is usually achieved by increasing the redundancy of onboard systems. Reliability is determined by the design of the system, the parts utilized, and the operating environment. One method of increasing reliability is by employing the worst-case design, using high quality components, which in turn adds cost. An alternative method of improving spacecraft reliability is to use a fault-tolerant design. Fault tolerance can be accomplished in either software or hardware. This section will discuss the redundancy methods that are relevant to this design, which are time, software, passive, and hardware redundancy. [Refs. 9 and 10]

Figure 2.1. Strategies in Designing a Reliable System. From Ref. [9]

#### 1. Time Redundancy

Time redundancy is one of the easiest methods to implement; it involves the restoration of a system to the point immediately after experiencing a fault. This fault is detected by placing checkpoints and with a timeout mechanism. If the system fails to perform a task within a certain amount of time, a fault is detected. The restoration of the system is accomplished by rollback of instructions, segments of programs or entire programs to the last checkpoint. The problem with this method is that it can be time consuming, which is determined by the size of the program and memory that is restored. Additionally, there is a loss of information to the point that the system last saved data. [Ref. 10]

An alternative method of time redundancy is the performance of a calculation numerous times for accuracy. This requires the system to save the state before the calculation, perform the calculation and save it, make a context switch back to the beginning of the calculation, perform it again, and then compare the results of the two different calculations. This results in a large computational drain on the system and two-fold increase in calculation time. [Ref. 10]

#### 2. Software Redundancy

No matter how capable the programmer, almost all software contains faults. A way to achieve some level of protection from these faults is the implementation of a software redundancy method. One such method is N-version programming, which is the addition of software modules to provide checks. For example, five individual programs

are designed for the same function. They are all executed, and their outputs are voted upon. Additional methods of software redundancy are consistency checks of the data against known correct values and capability checks to ensure those functional programs are operating correctly. [Ref. 10]

A subset of software redundancy is error-correcting codes. These codes can be utilized to provide automatic fault detection. One of the best-known codes, the Hamming single error correcting code, is used to increase reliability of information transmitted or stored in memories. [Ref. 10]

#### 3. Passive Redundancy

Passive redundancy employs multiple units, some of which are not continuously operating and are command selectable. In this configuration, redundant items act in response to a specific failure or anomaly. The detection of a fault is achieved by conducting periodic tests, self-checking circuits, or watchdog timers. Passive redundancy allows mission operations to continue in the presence of one or more failures. [Ref. 10]

#### 4. Hardware Redundancy

The most widely accepted view of hardware redundancy is the addition of components. Hardware redundancy can be broken into two subcategories: static and dynamic. Static redundancy, also known as masking redundancy, is the addition of extra component to mask out a fault near instantaneously. One of the major methods utilized to accomplish this is Triple Modular Redundancy or TMR. Dynamic Redundancy is implemented by monitoring the operation of the numerous devices for a fault. In this

system, only one module or device is operating at a time. If a fault is detected in this operational device, it is switched and replaced by another device. [Ref. 10]

The design described in the following chapters of the paper and employed in this system is Triple Modular Redundancy, a hardware redundancy technique. The TMR concept is implemented by utilizing three identical modules that feed their output to a voting unit. This voting unit then compares the outputs and passes the majority vote to the output, essentially masking out any single fault.

#### a) Triple Modular Redundancy (TMR)

As stated before, TMR is implemented by the replication of the devices and performing a majority vote to determine the output of the system. For example, if Module A becomes faulty, the two remaining module's outputs mask the fault when the majority vote is performed. The inputs and outputs of a module do not have to be single bytes. A word can be inputted into a module to produce a word output. This word has to then be inputted into parallel voting units to vote. The basic concept of the TMR circuit is shown below in Figure 2.1

The concept of TMR can be expanded to include multiple voting modules to produce an N-modular redundant system. As N gets larger, the logic required to realize the circuit and the added levels of delay get excessive. The typical range for N is from three to five. [Ref. 10]

Figure 2.2. Basic TMR Circuit Implementation. From Ref. [1]

The TMR system does have drawbacks, the primary being that the voter is a single point of failure. If the voter fails for some reason, the system will crash or propagate errors. A method to prevent this problem is the use of triplicated voters. [Ref. 10]

#### B. TMR MICROPROCESSOR DESIGN

The framework for the system in this design was first developed and simulated using Verilog by Lieutenant John C. Payne, Jr., USN, as a Fault Tolerant Computing Testbed [Ref. 1]. Following this Captain David Summers, USMC implemented and fabricated the design [Ref. 2]. The remainder of this section is a brief synopsis of the TMR Testbed Design.

#### 1. Hardware Design and Operation

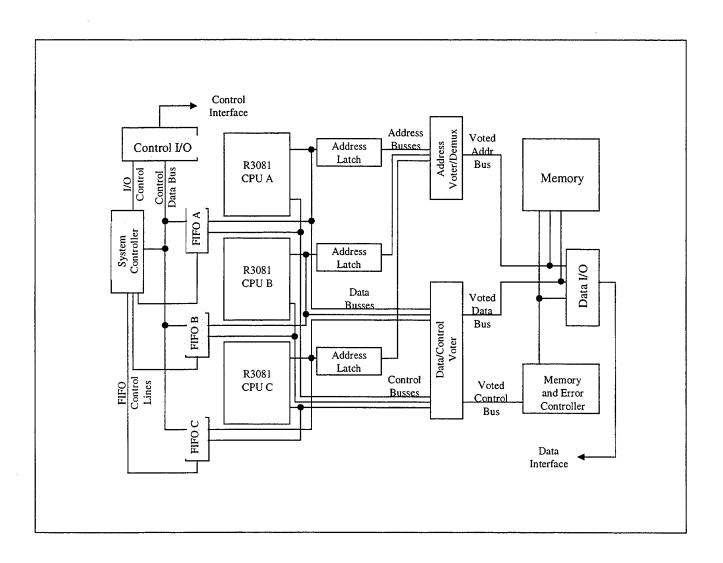

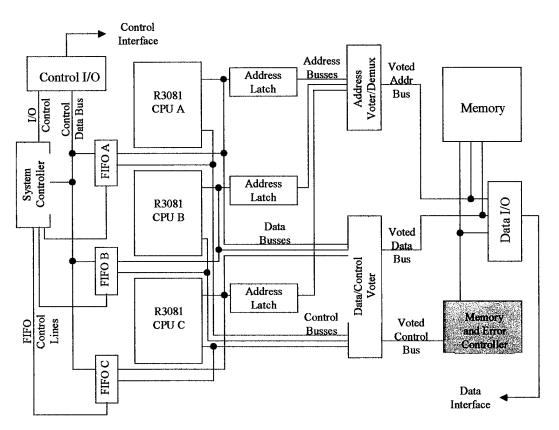

The first step in the design process was the integration of the system components. As stated previously, TMR is implemented by on the replication of three modules. This design was first focused on the 3081 as a single system and then triplicated. Figure 2.3 demonstrates the implementation of this concept. The TMR implementation has relatively few changes from the single processor design. The major additions to the design were the data, address, and control voter components.

As shown in Figure 2.3, the three system processors are connected in parallel. The system acts as if only one processor is present in the system. The processors perform functions in a lock step manner from initial boot up by executing the same instructions. The processors then route address, data, and control information through busses to their respective voters. The voters perform a majority vote on the signals and pass them on to the Memory Space and Memory Controller as in a single processor system. If an error is detected in a voter, the Memory Controller generates an interrupt.

Figure 2.3. TMR R3081 Board Design. From Ref. [1]

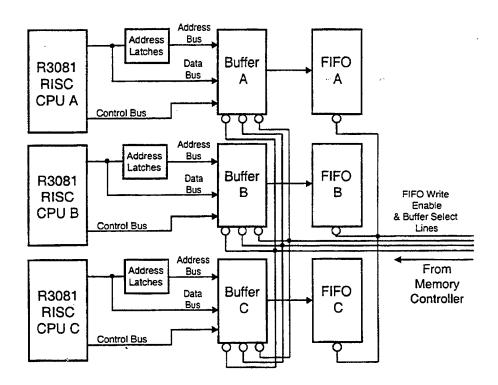

### 2. Fault Detection

Though the voters mask out the fault generated in the data going to memory, the problem remains of detecting which processor was at fault and where. In order to accomplish this, the internal registers of each processor have to be stored and examined. The information (address, data, and control) is captured prior to being voted by placing First-In-First-Out (FIFO) Registers on the address, control, and data busses between the processors and voters. If an error is detected, by any of the voters, the current bus cycle completes and an interrupt is generated. The processors are then restored to the state prior to the fault and resume operation. The arrangement is shown below in Figure 2.4.

This design protects only the processor operation and the processor output. The reliability of the data stored in the memory is not improved. This issue is discussed in Chapter VI as a part of the required preparations for a space flight design.

Figure 2.4. TMR FIFO Interface. From Ref. [2]

# C. DESIGN IMPLEMENTATION

Lt. Payne's design and simulations were the framework for the concept of the TMR system. His design product was software verification in Verilog of this implementation of TMR. The thesis presented by Capt. David Summers [Ref. 2] describes the implementation of the TMR design in hardware and the required changes. The following sections will provide a brief overview of these design changes and further information regarding them can be found in Reference 9.

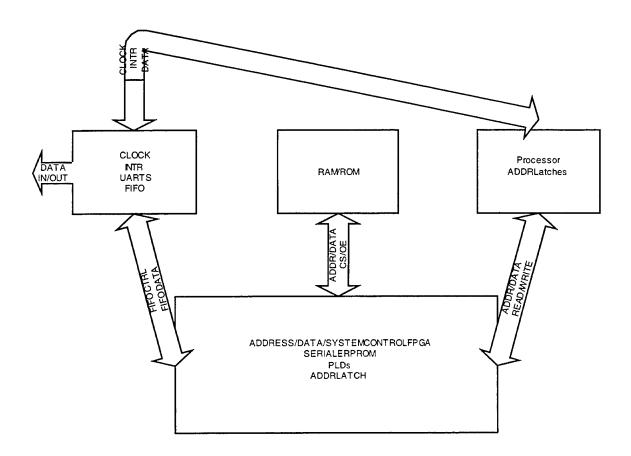

## 1. Design Hardware Changes

The process in the design of any system is driven by many factors including part availability and compatibly. Capt. Summers was required to implement design changes in order to provide a working board for future test and space applications. The three major changes implemented were the addition of a system controller FPGA and I/O interface ports. The system controller FPGA was added to replace some of the functionality provided by the computer in the Verilog design. The I/O interface was added to provide a method to upload programs and control the board during testing. The design and implementation of the system controller FPGA is covered in this thesis. Additional support elements such as oscillators, buffers, and a reset circuit were also added to the design. These design changes are highlighted and shown in Figure 2.5.

### 2. Final Design

The design and manufacture of the TMR board were completed by Capt. Summers, but he was unable to complete the programming, test, and verification of the design. This thesis continues the preparation of the board for eventual cyclotron testing and spacebased applications. This author began work on the TMR design with Capt. Summers on the design of the PLDs, FPGAs programs and the detailed timing analysis. This joint effort was presented in Capt. Summer's thesis as Chapter IV. Chapter III presents the continuation of this initial effort with the programming and testing of the Programmable Logic Devices (PLD).

Figure 2.5. TMR R3081 Block Diagram. After Ref. [2]

THIS PAGE INTENTIONALLY LEFT BLANK

# III. PROGRAMMABLE LOGIC DESIGN AND TESTING

Designers are continuously challenged to add more logic to system while using the same amount of board space. In order to incorporate this in the TMR design, the Memory Controller and Memory Enable functions were implemented in Programmable Logic Devices (PLDs), and Field Programmable gates arrays (FPGAs) were used to implement the data, control, and address voting logic. The programmable logic components of the design are identified as shaded blocks in Figure 3.1.

Figure 3.1. Programmable Logic Device Identifier. After Ref. [2]

### A. PLD PROGRAMMING

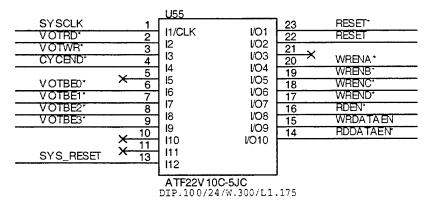

The final system design shown in Figure 3.1 utilized four user-defined modules, which are the address/voter demux, data/control voter, system controller and the memory and error controller. The first three modules were implemented utilizing Xilinx FPGAs are discussed in later sections. The memory and error controller modules were implemented in the TMR design utilizing two Atmel ATF22V10C-7PC PLDs. Detailed information regarding device selection and program logic is found in Reference 2 Chapter IV. This chapter will describe the steps taken in the programming and testing of these devices.

The software program utilized to construct files for download to the PLD is a program called WinCUPL, which is a Windows version of Universal Compiler for Programmable Logic (CUPL). CUPL is a HDL (Hardware Description Language) comparable to ABEL used to program logic devices. The input to WinCUPL is a user created Programmable Logic Device (PLD) file and the output is a standard JEDEC file used to program the device. After compiling, the JEDEC file is downloaded to a programming unit to program the device fuses. The program device utilized in the design of this system is the ALLPRO 96 256 Pin programming system by Logical Devices, Inc. After the file is downloaded, it is programmed into the device and the logic output of device is compared against test vectors. The following sections give a brief synopsis of the purpose of the devices and the testing and verification procedures.

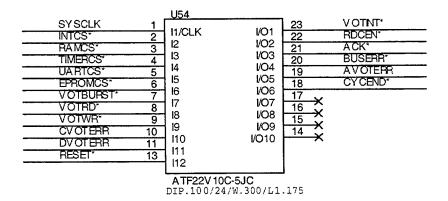

# 1. Memory Controller PLD

The main function of the memory controller is to provide all of the signals necessary for memory access during bus cycles. The memory controller inputs consist of the chip select signal for all peripheral devices such as RAM, ROM, timer, UART, and voter interrupt. Additionally, the voted signal such as read, write, data, address, and control vote errors are inputted to the memory controller. These inputs are utilized to generate the vote interrupt, read/write cycle enable, acknowledge, bus error, and cycle end signals. Appendix A gives a detailed pin out of the Memory Controller PLD.

# 2. Memory Enable PLD

The Memory Enable PLD assists the Memory Control PLD during bus transactions. It accomplishes this by producing the read and write enable strobes for the memory system, read and write data enable signals to control the drivers on chips between the busses, and a positive and negative logic synchronous reset. Inputs to the PLD consist of the voted read/write and voted byte enable signal. Utilizing these inputs, the PLD outputs the write and read enable signals for the peripheral devices.

# B. PLD TESTING

Test vectors allow the designer to verify, test and debug a PLD design for proper functionality before it is used in the system. Though the test vectors can pass when tested on the CUPL functional simulation, the same vectors may fail when tested on the PLD programmer. This is the case with the memory controller PLD that had two vectors fail. Two reasons that this could occur are improper test vector usage and a result of the programmer's hardware characteristics. The programming hardware dictates the

sequence in which inputs in a given vector are applied to the device. Analysis of device output and logic equations is the only manner by which to analyze and correct this. Analysis of the device output led to the conclusion that the PLD was unable to latch the counter causing the vector failures. The PLD program file was modified to correct this error and passed both the simulation and programmer tests. The impact of the change to the PLD functionality is that the bus error and cycle end signal will assert on one clock earlier. This is no manner affects the function of the TMR system. After completing the program changes, the file was compiled and downloaded into the programmer. Programming of the PLD passed all test vectors successfully. An updated design file is given in Appendix A.

## C. FPGA PROGRAMMING

The field programmable device chosen for this system is the Xilinx XL4013XLA. These devices are utilized to implement address voter\demux, data\control voter, and the system controller shown in Figure 3.1. Reference 2 Chapter IV gives a detailed discussion on the selection of this device and the design of the programs. The software used to develop the program for the devices was Xilinx Foundation Software. The FPGA design is a 3-step process that consists of the following stages. First, design entry, in this stage of the design flow the design is created either in schematic editor or hardware descriptor language (HDL). Second, design implementation by mapping the file to a specific Xilinx architecture, and placing and routing the design, the design file created in the first step is mapped into a physical file format. The physical information contained in this file is then used to create a bit stream file for programming in a programmable

device. The final stage of the process is completed when the bit stream file is formatted by a PROM formatter into a configuration file for the FPGA device that can be stored in a PROM. This is accomplished by converting the BIT file into one of four PROM formats: MCS-86 (Intel), EXORMAX (Motorola), TEKHEX (Tektronix) or straight HEX format.

In a joint effort with Capt. Summers, the first two steps of this process were executed. [Ref. 2] While executing the third step, it was discovered that the PROM code formatter in this software is targeted for Xilinx parts and the Serial EEPROM utilized in this design was an ATMEL AT17C512. Further research into the impact of utilizing this file in the device was conducted by contacting Xilinx and Atmel. After numerous conversations with the two companies, it was concluded that the Xilinx software program uses the device selection in determining the allowable size of the prom file only. Therefore, the difference in device was acceptable and would have no impact. Completing the process the file was formatted into MCS-86 and TEKHEX, then downloaded to the ALLPRO 96 programmer for programming into the Serial EEPROM.

In order to accomplish programming of a device, the ALLRPO has to first recognize the device type. The device programmer was unable to recognize the ATMEL devices for programming and thus unable to program the serial PROM. Research into possible causes for this failure led to a notice on the ATMEL website [Ref. 11]. This notice stated that some ATMEL serial EEPROMs failed to accept device encoding during manufacture and listed steps to overcome this failure. The instructions detailed methods of switching off the programmers' device recognition function. After completing the procedure detailed in the notice, the device programmer was still unable to program the

device. An ATMEL FPGA engineer, who assisted with the information for the programmer was aware of the difficulties experienced in programming the devices and offered assistance with programming the devices. The devices were returned after programming for installation in the system. Verification of successful programming is only indicated by the programmer's comparison of the contents of the programmer memory to the device contents.

The programming of the Memory Controller PLDs and the Voter FPGAs allow the system to function as a stand-alone computer system able to detect and correct single bit errors occurring in any of the processors. The design of the system controller FPGA though mentioned in the start of this chapter was not discussed. The design and programming of this programmable device completes the TMR design and is discussed in detail in following chapter.

## IV. DESIGN OF THE SYSTEM CONTROLLER FPGA

As stated earlier, programmable logic offers flexibility to the system designer and is essential to performing controlling functions in the TMR 3081 design. The Data Voter and Control voter were previously implemented and programmed using the schematic editor in the Xilinx software. The System controller FPGA presents a more difficult design problem because the logic implemented by this controller cannot easily be modeled as a combinatorial design. Therefore, it was decided to use Xilinx Foundation HDL editor and State Machine tool to design the controller. The system controller performs numerous functions in the TMR system. It initializes the Control UART, enables the interrupts for the 3081 microprocessor after resets, transfers and collects FIFO data, and defines the mode in which the TMR system functions. In examining all of these tasks, there are three distinct possibilities of data flow. These are:

- The FPGA outputs data to the UART

- The FPGA enables the FIFO to output data to the UART

- The FPGA accepts input from the UART

Each of these events is mutually exclusive: that is, no two events can ever occur at the same instant in time. It is the function of the system controller to define, which one of these events listed above is presently in progress. The detailed subsystem programs of the system controller FPGA are listed in Appendix B. The following sections discuss the state machines for each subsystem of the system controller FPGA. Figure 4.1 provides an overview of the flow of the state machines discussed in the following sections.

Figure 4.1. State Machine Hierarchy

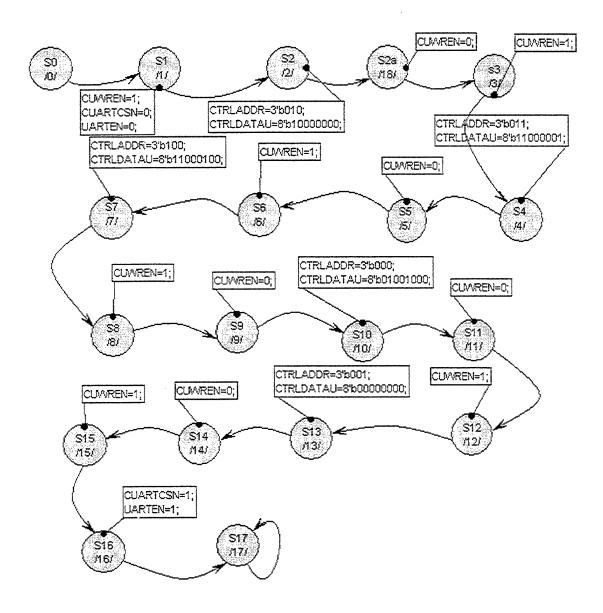

## A. CUART STATE INIT MACHINE

The Control UART Initialization state machine is the uppermost in the state machine hierarchy. It automatically initializes the UART to the proper mode of operation when the system controller FPGA is powered on or reset. The following sections present the operation of the UARTINT state machine.

## 1. State Machine Functionality

The CUARTIN state machine initializes the control UART to communicate with the HCI. This is accomplished by a sequence of UART register writes. The first register initialized by this sequence is the FIFO control register, which is a write only register. The register enables the FIFO by asserting the first bit. The next register in the sequence is the Line control register. The line control register controls the format of the data communication. The first two bit in the register are set to '11' setting the serial character word length to 8 bits. The last six bits in the register set the parity and number of stop bits. The Human Control Interface design by Capt. Kim Whitehouse and LT. Susan Groening [Ref. 3] currently has no parameters set for these modes. The default initialization sequence therefore sets the modes for no parity and one stop bit. The Modem control register is next in the sequence and controls an interface with a modem. The assertion of the first two bits and the sixth bit in the register enable the autoflow control mode of the UART. The final registers in the setup sequence are the Divisor Latch (LSB) and Divisor Latch (MSB). These registers are utilized to control the programmable baud generator for the UART. The divisor written into the registers is 72. This divisor sets the baud rate of the UART to 9600. The final state of the UART initialization sequence disable the data lines and deasserts the chip select line. Completion of UART setup enables communication with the HCI and allows the state machine to proceed to the next state machine, VOTE.

The CUARTINT state machine initiates in state S0 and immediately transitions to the next state, S1. The state machine shown in Figure 3.1 contains no conditions for transitioning from state to state. Therefore, once the state machine is initialized it does not depend on any outside input for completion of the control UART initialization process. Continuing in state S1, the FSM asserts UART Enable (UARTEN) and Control UART Chip Select (CUARTCSN). The assertion of these signals enables the UART to

drive the bi-directional bus and read status information from a register. In the next state, S2, the FSM first asserts the Control Address bus (CTRLADDR) with the register selection address. The UART has twelve internal registers, only, six of which are utilized during the initialization process discussed in this section. The table below details the register selection dependent on the address placed on the CTRLADDR bus.

| DLABT | <b>A</b> 2 | A1 | A0                                                          | REGISTER                                      |  |

|-------|------------|----|-------------------------------------------------------------|-----------------------------------------------|--|

| 0 L L |            | L  | Receiver buffer (read), transmitter holding register (write |                                               |  |

| 0     | L          | L  | Н                                                           | Interrupt enable register                     |  |

| X     | L          | Н  | L                                                           | Interrupt identification register (read only) |  |

| Х     | L          | Н  | L                                                           | FIFO control register (write)                 |  |

| X     | L          | Н  | Н                                                           | Line control register                         |  |

| Х     | Н          | L  | L                                                           | Modern control register                       |  |

| Х     | Н          | L  | H                                                           | Line status register                          |  |

| Х     | Н          | Н  | L                                                           | Modern status register                        |  |

| X     | Н          | Н  | Н                                                           | Scratch register                              |  |

| 1     | L          | L  | L                                                           | Divisor latch (LSB)                           |  |

| 1     | L          | Ŀ  | Н                                                           | Divisor latch (MSB)                           |  |

Table 4.1. UART Control Register. From Ref. [12]

In addition to asserting the control address, state S2 places the setup data on the Control Data UART (CTRLDATU) bus that is tied to the bi-directional Control Data (CTRLDATA) bus. This data is written into the selected register and latched in by state S2b with the assertion of the Control UART Write (CUWREN). The next state S3 deasserts CUWREN, which enables the next state, S4, to change the address and data lines without effecting the UART. This process is repeated to setup remaining registers.

Figure 4.2. UARTC State Machine

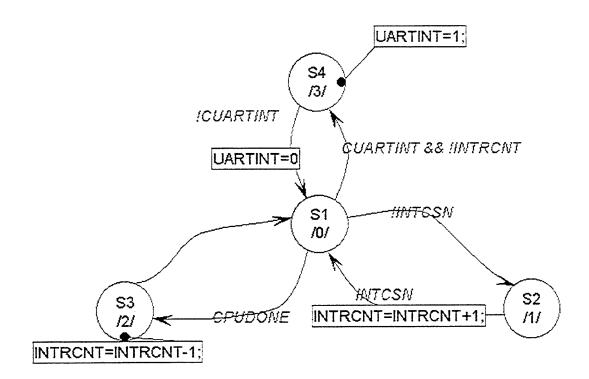

## B. VOTE MACHINE

The vote state machine is the primary state machine of the system controller FPGA. This state machine has two primary purposes. The first is to detect a voter interrupt from the microprocessor and start the collect/transfer state machines. The second is to detect a Control UART Interrupt (CUARTINT) assertion from the HCI. The

state machine is broken into three functions to ensure control over what state machine is driving the data bus. The following sections discuss the operation of this state machine based on these two functions.

## 1. Voter Interrupt routine

The main function of the system controller FPGA is to monitor the TMR board for a vote interrupt to collect and transfer the data. This important function is implemented and started with the voter interrupt routine. This state machine detects a voter interrupt and increments an interrupt counter. The incrementing of this interrupt counter is a signal to the collect and transfer state machines to begin the process of collecting the data from the FIFOs and transferring the data to the UART.

The state machine waits in state S1 and monitors the Interrupt Chip Select (INTCSN) signal for indication of a voter interrupt. When, the INTCSN signal is asserted, the state machine transitions to state S2. The state machine then waits for the deassertion of this signal indicating that a voter interrupt has been serviced. The state machine then transitions back to state S1 incrementing the Interrupt Counter (INTRCNT) register, which starts the Transfer state machine discussed in a later section.

The state machine resides in this state until assertion of the CPUDONE signal by the Transfer state machine. Assertion of this signal indicates that the Transfer state machine has completed the transfer of the CPUs FIFO array contents to the HCI. The state machine transitions to state S3 decrements the interrupt counter and then transitions back to state S1 awaiting another interrupt signal. This completes the detection and start of the interrupt service routine.

# a) INTRCNTR

The interrupt counter register is implemented in the design to enable the system to contend with numerous consecutive interrupts. The processors will have dumped and restored their internal registers before the system controller FPGA is finished transferring the FIFO data. The state machine controls this by incrementing for each transition of INTCSN signifying to the state machine that an additional interrupt has been serviced. This in turn will ensure seamless operation of the Transfer state machine during multiple interrupts. Additionally, it is important to note that INTRCNTR is a 4-bit register and therefore the maximum number of interrupts counted by this machine is 32. Since the collect and transfer sequences for the FIFO are occurring simultaneously, only an extreme error condition producing consecutive voter interrupts would lead the state machine exceeding this design limit.

Figure 4.3. VOTE State Machine

# 2. UART Interrupt Routine

Since the vote state machine is the highest in the hierarchy, it was necessary to implement the detection of a request from the HCI to input data to the system controller FPGA here. The HCI inputs data through the UART to the system controller to implement three functions, which are a board level reset, a system level reset, or to set the mode of operation of the board to one or three processors. The system controller detects this request for input and starts the CONTROL MODE state machine.

An alternate transition path from state S1 to state S4 is caused by the assertion of the Control UART Interrupt (CUARTINT) signal with the INTRCNT register equal to zero. The CUARTINT signal originates from the UART and is asserted by the HCI

placing data in the UART. Transitioning to state S4 causes the assertion of the UARTINT signal that starts the CONTROL MODE state machine. This state machine is discussed in the following section.

## 3. State Machine Design Constraint

An important factor in this state machine design is the imposed constraint that a transition to state S4 from state S1 is inhibited during a voter interrupt service. This was accomplished by the ANDing of the signal CUARTINT and !INTCNTR. This constraint was placed on the design to protect against switching the mode of operation during an interrupt handling routine. An example of this is switching from TMR processor mode to one processor mode during a voter interrupt service. If the processors are currently dumping their registers to the FIFO, the transfer process is asserting and deasserting the CTRLDATA bus. A switch in mode would require that the Read Machine drive the CTRLDATA bus breaking the current FIFO data dump. Therefore, it was decided to block this function from occurring until completion of the service routine.

This basic principle is also implemented in the design of the HCI. During a voter interrupt routine, the HCI is receiving FIFO data and the user is unable to halt the process. The next section discusses the operation of the Control Mode state machine, which the HCI utilizes to setup the TMR system.

### C. CONTROL MODE STATE MACHINE

The vote state machine initiates the control mode state machine. This state machine reads in the control word from the UART inputted by the HCI. The state machine next utilizes the control word by checking what bits are set to decide which of

the three functions previously mentioned to perform. This operation of this state machine flow is discussed in the following sections.

#### 1. Mode Initialization

This FSM initializes in state S1 and transitions to state S2 upon assertion of the UARTINT signal by the VOTE state machine discussed previously. State S2 asserts the signals FORCE, mode enable (MODEEN), and CUARTCSN setting the default mode of the TMR design to single processor and enabling the FSM to drive the bi-directional CTRLDATA bus for input. The selection of the default mode of the design to single processor mode is to allow the user to setup the system design and conduct initial tests before transitioning to the TMR mode. This selection can be changed in future designs. The assertion of the final signal CUARTCSN indicates to the UART to activate the asynchronous communications element for data transfer. The FSM next transitions to state S3, asserting the CTRLADDR bus with '000' selecting the holding register (write) of the UART. A transition to state S4 asserts the chip select signal, CUARTADSN, which allows the selection of the control register in the UART. The state machine next transitions to state S5, asserting Control UART Write Enable (CUWREN) and writing the control word onto the data lines. Next, state S6 reads in the data on the input bus AIN tied to the CTRLDATA bus and places the contents into a temporary register MDCTRL. The FSM transitions to state S7 deasserting CUWRENN, CUARTCSN, and MODEEN allowing the other state machines to drive the bi-directional data bus CTRLDATA. State S7 has three possible transition paths that are dependent upon the data in MDCTRL register. The transition paths each contain an 'IF' conditional that checks a bit in the control word which in turn selects the transition path. State S10 causes a change in design mode from single to TMR processor mode. State S8 and S9 are responsible for a board and system reset. The Control Mode state machine is shown in figures 4.4 and the control mode word is given in Appendix B.

Figure 4.4. MODECNTRL State Machine

### D. FIFO DATA COLLECTION STATE MACHINE