# Partial Order Reduction for Verification of Timed Systems

Marius Minea December 1999 CMU-CS-00-102

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

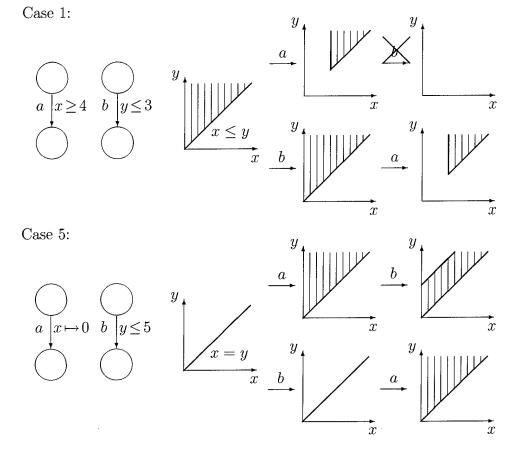

#### Thesis Committee

Edmund M. Clarke, Chair Randal E. Bryant Jeannette M. Wing Doron Peled, Bell Laboratories

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

©1999 Marius Minea

This research is sponsored by the Semiconductor Research Corporation (SRC) under agreements through Contract No. 99-TJ-684, the National Science Foundation (NSF) under Grant Nos. CCR-9505472 and CCR-9803774, and the Defense Advanced Research Projects Agency (DARPA) under Contract No. DABT63-96-C-0071. Any opinions, findings, conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of SRC, NSF, DARPA, or the United States Government.

DISTRIBUTION STATEMENT A

Approved for Public Release Distribution Unlimited

20000509 111

**Keywords:** formal verification, model checking, partial order reduction, timed systems

## **School of Computer Science**

# DOCTORAL THESIS in the field of COMPUTER SCIENCE

# Partial Order Reduction for Verification of Timed Systems

## **MARIUS MINEA**

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

| ACCEPTED:                      |              |      |

|--------------------------------|--------------|------|

| Edmel M. Clarke                | Da 17, 1999  |      |

| THESIS COMMITTEE CHAIR         | 10           | DATE |

| Markel & Bry & DEPARTMENT HEAD | Jan 21, 2000 | DATE |

| APPROVED://)                   |              |      |

| Mens                           | 1/27/00      |      |

| DEAN                           | ·            | DATE |

#### Abstract

This dissertation presents solutions for the application of partial order methods to the verification of timed systems, with the purpose of reducing the size of the explored state space.

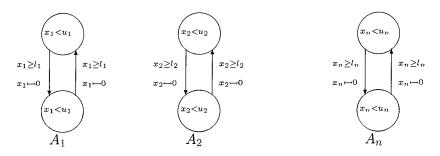

Timed systems, which rely on timing information to operate correctly, pose special difficulties for automatic verification. Not only does the size of their state space grow exponentially with the number of components, as in any concurrent system, but some of the history of past transitions becomes part of the timed state. This hinders the use of partial order reduction, a technique which is applicable if different transition interleavings lead to the same state. We have given a partial order reduction algorithm for systems described as networks of timed automata, which preserves formulas in a timed extension of linear temporal logic. The algorithm is based on a modified local-time semantics, which allows individual automata to execute independently except for synchronization transitions.

More generally, we have investigated the application of partial order reduction in a continuous-time model whose semantics is defined in terms of timed traces. We show how to separate the causal dependence of transitions from their time ordering due to concurrency and how this leads to the application of partial order reduction. As particular instances of this framework we obtain improved algorithms for timed event/level structures and time Petri nets, as well as our algorithm for timed automata.

We have evaluated the performance of our partial order reduction approach on several timed automata benchmarks. The resulting reduction in state space stems from two sources: the local-time model reduces the number of generated time regions, while the partial order techniques applied from the domain of untimed systems reduce the explored control state space.

#### Acknowledgements

I was fortunate and privileged to have Ed Clarke as my advisor. He shaped my path to research by guiding me with his extensive knowledge, and at the same time opened up doors so I could gain from the expertise of others. He has shown enthusiasm for my progress and support when I was struggling, and it was Ed who suggested this thesis topic, at a time when I had long been searching for one.

I owe a lot of gratitude to my thesis committee for their advice and patient reading of my thesis. Doron Peled provided me with a lot of detailed research expertise, and friendly but sternly brought me back on track when I was losing focus. Jeannette Wing gave me insightful critical advice, both in overview and in detail; meetings with her were always extremely stimulating. Randy Bryant has been a model for solid, successful research, and it was always reassuring to hear from him that I was on the right track.

This work would not have been possible without the environment in CMU's Computer Science department, with stimulating top-notch research, and at the same time an atmosphere that I can hardly imagine friendlier. Thanks to everyone, from Sharon to facilities, for doing everything in their power so we would feel well here and give our best. And thanks to the virtual community of zephyr++.

My introduction to partial order methods came at Bell Laboratories where I had a very productive summer working with Bob Kurshan, Vladimir Levin, Doron Peled and Hüsnü Yenigün. I was kindly invited to Uppsala by Wang Yi, where I benefitted from talks with Bengt Jonsson and Johan Bengtsson, among others. At VERIMAG Grenoble I had insightful discussions with Joseph Sifakis, Stavros Tripakis and Sergio Yovine.

Over the years, I've enjoyed working with many members of the model checking group: Somesh, Xudong, Will, Vicky, Sergey and Yuan. I've had some of the best time working with Sérgio Campos: it is with him that I started to work on real-time systems, and both work and friendship have continued after his graduation.

Thanks to all my friends who shared my life away from work during these years. To Dan, forever joyful and supportive, for everything. To Mihai and Raluca, for the wonderful musical evenings at their place, and also, together with Ciprian, Ion and Cristi, for making me feel closer to home. To my longtime officemates, Bruce and Ralph, and later C.K., for making life between the concrete windowless walls of Wean Hall not only endurable, but enjoyable. To Andrei and Dave, for the joy of climbing, and to the volleyball group for a welcome weekly respite and for friends like Darrell, Dushyanth and Edwin.

Finally, and most importantly, thanks to my parents, to whom I owe what I am, who encouraged and supported me all these years, and who accepted the hardships of being far away so that I could see this through.

# Contents

| 1 | Intr | roduction 3                                       |

|---|------|---------------------------------------------------|

|   | 1.1  | Motivation                                        |

|   | 1.2  | Thesis Approach and Contributions                 |

|   | 1.3  | Related Work                                      |

|   |      | 1.3.1 Continuous and Discrete Time 6              |

|   |      | 1.3.2 Other Partial Order Approaches 8            |

|   |      | 1.3.3 Other Approaches to State Space Explosion 9 |

|   | 1.4  | Outline                                           |

| 2 | Par  | tial Order Reduction 13                           |

|   | 2.1  | Introduction                                      |

|   | 2.2  | Basic Notions                                     |

|   | 2.3  | Principles of Partial Order Reduction             |

|   | 2.4  | Conditions for Partial Order Reduction            |

|   | 2.5  | A Proof for Partial Order Reduction               |

|   | 2.6  | Calculating Ample Sets                            |

|   | 2.7  | Other Partial Order Reduction Methods             |

|   | 2.8  | Static Partial Order Reduction                    |

|   |      | 2.8.1 A Modified Cycle Closing Condition          |

|   |      | 2.8.2 Determining Sticky Transitions              |

|   |      | 2.8.3 Experimental Evaluation                     |

| 3 | Par  | tial Order Reduction for Timed Automata 43        |

|   | 3.1  | Introduction                                      |

|   | 3.2  | Timed Automata                                    |

|   |      | 3.2.1 Definition                                  |

|   |      | 3.2.2 Semantics                                   |

|   | 3.3  | The model checking problem                        |

|   | 6.3               | Case Studies of Timed Systems                          |            |

|---|-------------------|--------------------------------------------------------|------------|

|   | 0.2               |                                                        |            |

|   | 6.2               | Parameterized Benchmarks                               | ~~         |

| - | 6.1               | Implementation                                         | 103        |

| 6 | Exp               | erimental Results 1                                    | 03         |

|   | 5.5               | Discussion                                             | LUU        |

|   | 5.4               | Partial Order Reduction                                | 99         |

|   |                   | 5.3.4 Exploration based on timed regions               | 98         |

|   |                   | 5.3.3 Enforcing timing conditions                      | 96         |

|   |                   | 5.3.2 Traces with relaxed timing                       | 93         |

|   |                   | 5.3.1 Preliminaries                                    | 91         |

|   | 5.3               | A Relaxed Timing Semantics                             | 91         |

|   | 5.2               | Timed Structures and Traces                            | 90         |

|   | 5.1               | Background and Motivation                              | 88         |

| 5 | ΑР                | artial Order Reduction Framework for Timed Systems     | 88         |

|   |                   | 4.2.3 An Improved Algorithm for TEL Structures         | 83         |

|   |                   | 4.2.2 State Space Exploration Using POSETs             | 78         |

|   |                   | 4.2.1 Timed Event/Level Structures                     | 77         |

|   | 1.4               | for Timed Event/Level Structures                       | 77         |

|   | 4.2               | Partial Order Reduction                                |            |

| 4 | 4.1               | Partial Order Reduction for the Region Graph Automaton | 73         |

| 4 | Rod               | uction for Other Timed Models                          | <b>7</b> 3 |

|   | 3.10              | Summary                                                | 72         |

|   | 3.9               | Partial order reduction                                | 70         |

|   | 3.8               | Building a finite model                                | 68         |

|   | 3.7               | Preservation of LTL $_{\Delta}$ formulas               | 63         |

|   | 5.0               | 3.6.1 Representation of local-time zones               | 59         |

|   | 3.6               | The local-time zone automaton                          | 58         |

|   | $\frac{3.4}{3.5}$ | A local time model                                     |            |

|   | 3.4               | 3.3.1 Effect of transition interleavings               |            |

|   |                   | 3.3.1 Effect of transition interleavings               | 50         |

# Chapter 1

## Introduction

#### 1.1 Motivation

A significant part of today's computer-related systems are time-critical. They may rely on timing information to operate correctly, or their specifications may require that certain actions be executed within given time limits. Examples of such systems are timed asynchronous circuits, network or communication protocols, and industrial controllers. Failure to satisfy these properties may result in malfunction, system shutdown, significant financial costs, or even risk to humans. It is therefore imperative that correctness of these applications is guaranteed under all possible circumstances.

Moreover, the development of techniques that assist this correctness goal can stimulate the use of designs that offer increased efficiency, but whose behavior is more difficult to analyze. Such is the case, for example, with asynchronous circuits which can achieve significant performance gains while dispensing with some of the limitations of designs based on a synchronous clock.

At the same time, timed systems often lack in robustness (a small change in timing can result in a significant change in behavior), and their analysis can be very complex, since they have a large family of possible executions. The latter reason makes traditional methods such as testing and simulation even less likely to deliver exhaustive correctness results than in the case of untimed systems. In fact, with a dense view of time, the family of behaviors for a timed system can be infinite.

Formal verification techniques approach the correctness problem by proving using mathematical formalisms that a system model satisfies its specification under all possible circumstances. Within this category, model checking [CE81] has emerged as a very successful technique, with the benefit that it is completely automatic. However, its application to even larger and more complex systems is limited by the so-called *state space explosion* problem: for many types of systems, the number of possible states grows exponentially with the number of component parts. This quickly leads to models whose size exceeds the current capabilities of verification tools. For real-time systems, the space explosion problem is even more limiting, and is caused by two different factors: complexity in the control space and complexity due to the timing associated with the system.

To illustrate more precisely the causes of state space explosion in the case of timed systems, consider a typical state exploration algorithm. A complete state space search has to consider all transitions which could be executed first from a given state, in order to generate all possible interleavings. In an untimed concurrent system, this leads to a number of interleavings (and explored states) which is exponential in the number of concurrent components. In a timed system, the firing times of transitions become part of the state space, since the future behavior of the system typically depends on the relationship between them. This has two consequences. First, more information is usually needed to describe a timed state, resulting in a higher amount of memory used. Second, two transitions leading to the same state in the underlying untimed control structure will generally lead to different timed states, since the ordering of transitions is incorporated in the timed space.

Partial order reduction (e.g., [God90, Pel93, Val90]) is a well-established method to reduce the complexity of state space exploration in systems consisting of several parallel components. It explores a restricted number of interleavings for independent concurrent transitions, while preserving the verified property in the reduced model. This aspect makes it a very good candidate for containing the state space explosion in timed systems. However, partial order reduction considers two transition interleavings to be equivalent only if they lead to the same state. Thus, for timed systems, the encoding of transition ordering as part of the state, besides being one of the main causes of complexity also prohibits the direct application of partial order reduction. It is precisely this issue that we propose to address.

### 1.2 Thesis Approach and Contributions

This dissertation presents solutions for the application of partial order methods to the verification of various models of timed systems, with the purpose of reducing the size of the explored state space.

The general approach followed is to define an alternate semantics for the timed model under investigation, in which causal dependence of transitions is separated from time ordering due to concurrency. This relaxed timing semantics is characterized by a richer set of behaviors. Whereas the standard semantics requires successive transitions to occur in a sequence of monotonically increasing timepoints, in the new semantics some transitions can be explored in an order which may be different from the original ordering of their execution times. However, the behaviors of the new model are restricted in such a way as to preserve the truth value of the specification. We chiefly work in the context of specifications expressed in timed extensions of next-time free linear temporal logic.

Performing the state space search using the modified semantics instead of the original one can be advantageous because the relaxed time ordering condition on transitions leads to the generation of fewer timed states. A timed state no longer needs to encode the total order of transitions leading to it, but merely a partial order representing causality. At the same time, the commutativity of transitions which are independent in the underlying untimed system is restored. This allows partial order reduction to be applied, potentially leading to a yet smaller system model, this time due to a decrease in the number of control states.

The main contributions presented in this dissertation are:

- A method for the application of partial order reduction to networks of timed automata, based on a local-time model. In particular, we show how to effectively search the state space of the system using a local-time model, how to perform verification for a timed extension of linear temporal logic, and we give conditions for the selection of a reduced set of transitions during exploration. Our experimental results show that using a local-time model for exploration leads to a significant reduction in the number of timed regions, while partial order reduction results in a further reduction of the control state space.

- A general formalism for the application of partial order reduction for a class of continuous-time systems. We define a general timed model,

and a semantics based on execution traces which separates the issues of transition causality from the ordering of their timestamps. We then show how our semantics naturally allows the application of partial order reduction and present an algorithm that performs a reduced state space search on a model based on timed regions.

- An algorithm that applies partial order reduction to the exploration

of timed event/level structures, used in the modeling of asynchronous

circuits. Compared to the original algorithm which focuses on exploring

fewer timing regions, the new algorithm also reduces the number of

control states.

- A technique to apply partial order reduction statically at the time of model construction. This represents joint work, presented in [KLM<sup>+</sup>98]. The method permits reduction to be separated from the model checking algorithm and combined with other verification techniques, in particular with symbolic model checking.

- A proof for the correctness of partial order reduction with ample sets using a weaker condition for independence between transitions.

#### 1.3 Related Work

We present a brief selective overview of relevant related research in the verification of timed systems, first discussing various models, and then previous work on applying partial order reduction to this domain.

#### 1.3.1 Continuous and Discrete Time

To formalize the notion of time, two main directions have been pursued in the literature. One of them considers a dense (continuous) model of time, equating time with the set of real numbers  $\mathbb{R}$ . In this model, an event (or a transition) can occur at an arbitrary time point on the real scale. On the other hand, the discrete model of time allows transitions to occur only at discrete time quantums, modeling time using the set of integer numbers  $\mathbb{Z}$ . Throughout the history of verification for timed systems, the relative merits of the two approaches have been compared and debated [AH91, HMP92].

A comparison of the two models can be made in terms of both expressivity and efficiency. The continuous time model is strictly more expressive than the one employing discrete time. Intuitively, continuous time can model delays that are arbitrarily small. When modeling a system using the dense time paradigm, one does not have to assume that the granularity of the clock is appropriate for modeling all system behaviors. Furthermore, when composing two discrete-time systems, one has to match the granularity of the two clocks, an issue which does not occur with continuous time.

However, for some classes of timed systems, certain properties are preserved by discretization. Henzinger, Manna and Pnueli [HMP92] discuss timed transition systems, i.e., state-transition graphs augmented with upper and lower integer time bounds on transitions. They show that all qualitative (or time-independent) properties, and some common quantitative properties such as time-bounded invariance and time-bounded response are preserved by a discrete-time semantics. Furthermore, if a property expressed in a certain timed logic holds in the continuous-time semantics, a weaker, derived property is guaranteed to hold in discrete time.

On the other hand, there exist systems and properties which are not preserved if a discrete-time model is used instead of continuous time. An analysis for combinational circuits is given in [AMP98]. Again, the timing constraints are expressed as bounded delays which are imposed on the output of each gate. It is shown that for acyclic circuits, a discretization quantum can be found such that qualitative behavior (i.e., event ordering) is preserved. In these cases, a time quantum of 1/n, where n is the number of signals in the circuit, is sufficient. However, there exist cyclic circuits whose continuous-time qualitative behavior is not preserved by any discretization.

From an efficiency point of view, both discrete- and continuous-time models have their individual advantages and disadvantages, although in general, practical results for discrete-time models have been better, as reported for instance in [BMT99]. Discrete-time techniques allow efficient representation techniques from the untimed domain to be used, such as binary decision diagrams [Bry86]. However, discrete time does not constitute an unconditional improvement. Modeling a system in discrete time can already result in a more complex model than by using a continuous-time semantics. Moreover, discrete-time techniques tend to be more sensitive to the size of the constants appearing in the model descriptions, and large constants can result in state space explosion.

#### 1.3.2 Other Partial Order Approaches

We discuss three of the most common models that have been used for the description and verification of timed systems: timed automata, time Petri nets and timed event/level structures, and the related work that has been carried out to apply partial order reduction to these models.

The first partial order reduction procedure for a timed model seems to have been presented in the context of time Petri nets by Yoneda, Schlingloff et al. [YSSC93, YS97]. Their model is an extension of Petri nets in which upper and lower time bounds may be placed on transitions MF76. Because of their restricted timing conditions, time Petri nets are less expressive than timed automata. On the other hand, converting a Petri net into a timed automaton can potentially involve an exponential increase in the size of the model. Hence, verification algorithms for time Petri nets are not subsumed directly by those for timed automata. Yoneda and Schlingloff prove a partial order reduction algorithm that preserves properties in a timed extension of next-time free LTL. The fundamental idea of their approach is that only transitions from the reduced set chosen for exploration need to be interleaved in all possible time orderings. In Chapter 5 we show how this idea can be generalized, and the required condition can be weakened. Sloan and Buy [SB96, SB97] give a procedure similar to [YS97] for a more restrictive model of simple time Petri nets, in which each transition has a static delay. Lilius [Lil98] suggests an improvement that does not store the firing sequence of transitions as part of a timed state, but can only applied to analyzing reachability of place markings.

Timed automata [AD90, ACD90] are finite-state automata augmented with a set of real-valued clocks that evolve at the same rate. Their transitions are guarded by constraints on clocks or their differences. Combining a natural description formalism with high expressive power, they have been extensively studied in the literature (see [AD94] for a comprehensive survey).

The model checking problem for timed automata has been investigated for powerful timed logics such as timed computation tree logic (TCTL) [ACD90] and timed modal  $\mu$ -calculus [HNSY92]. The worst-case complexity of model checking is exponential in the number of clocks and the size of the maximal time constant in the model. However, model checking tools such as Kronos [NSY92] and UPPAAL [LPW95] have implemented efficient search and representation techniques together with various optimizations that have enabled the verification of a number of real-world examples.

The first approach to the application of partial order reduction for systems composed of communicating timed automata is due to Pagani [Pag96, Pag97]. Her analysis shows however that the dependencies between the passage of time and transitions that cause a state change reduce the independence of transitions significantly compared to the untimed case and thus make the application of partial order reduction difficult. An improvement which identifies additional cases where reduction can be applied is presented in [DGKK98].

Bengtsson et al. [BJLW98] were the first to suggest a modified semantics that allows the component automata of a network to execute individually, synchronizing their local time scales only on synchronization transitions. Our results for timed automata are based on their work. However, the only preservation result proved for the new semantics was for local reachability. Moreover, they did not present a concrete verification algorithm, since the new model lacked an effective condition to decide the equality of two timed regions (i.e., a stopping condition in the state space search). As our main result, we show in Chapter 3 how to use this local-time model to perform model checking for a timed extension of linear temporal logic.

Timed event/level structures [BM97] are a specification formalism tailored to the description of asynchronous circuits, derived from the timed event/rule structures of [Mye95]. A rule describes a causal relation between two events, together with a separation interval (integer upper and lower time bounds) between them. They are in essence similar to Petri nets but in addition allow rules to depend on the value of signals. Belluomini and Myers [BM98] present an algorithm that stores only partial ordering relations between events and thus reduces the number of timed states generated during system exploration. However, the term "partial order" here does not imply the exploration of a reduced set of event or rule interleavings. In Chapter 4 we present how partial order reduction (in the sense of exploring a restricted set of events) can be added to their algorithm to also reduce the set of explored control states.

#### 1.3.3 Other Approaches to State Space Explosion

Partial order reduction attempts to alleviate the state explosion problem for timed systems by addressing one specific cause, the redundant exploration of multiple transition interleavings. A wide variety of other methods have been used to contain state space explosion by addressing orthogonal issues. We mention some of the most relevant techniques, since many of them can be used in a model checker together with partial order reduction. For timed automata, one of the reasons for the large size of the state space is the fact that during state space exploration, all pairs of clocks are related to each other by clock constraints. However, not all clocks are used at every point during the execution of the system. If a clock is not used in any constraint prior to the next point when it is reset, its relation to other clocks is irrelevant, and it can be removed from the representation of the current state. This method, called clock activity reduction, was introduced first by Daws and Yovine [DY96] and can significantly reduce the amount of memory that is necessary to store a timed state.

Another approach that reduces the complexity related to timing is based on the observation that not all the timing information in the description of a timed system is usually needed to guarantee the satisfaction of a given property. An approximation scheme which uses upper and lower bounds on the set of reachable states is described in the Ph.D. thesis of Wong-Toi [Won94]. Approximations have also been studied by Balarin [Bal96], and are incorporated in the model checked RT-Cospan [AK95]. In the latter situation, the underlying untimed description of the system is composed with an automaton representing the time bounds. Only the bounds that are necessary to verify the given property are successively introduced in the composition.

Time-abstracting bisimulations, which hide the quantitative aspects of time, are discussed in the Ph.D. thesis of Tripakis [Tri98]. If a system's quotient is computed with respect to a time-abstracting bisimulation, efficient methods from the untimed domain, such as minimization of the resulting transition system, can be applied for verification. Methods for abstraction of timed systems are also discussed in the thesis of Taşıran [Taş97].

Symbolic techniques based on BDDs have been investigated with great interest in the domain of timed systems, due to their success in the untimed and discrete-time case. Wong-Toi [Won94] reports successful use of BDDs to encode control states that share the same timing information, especially when used together with approximations. Balarin [Bal96] takes a different approach and uses BDDs to encode the difference bound matrices which represent time zones. Bozga, Maler et al. [BM97, BMT99] show that in several cases, BDDs together with discretization enable the verification of systems with more components than using a standard difference bound matrix (DBM) representation and continuous-time semantics. Belluomini [Bel99] uses BDDs for the storage of the reached state sets, but converts to an explicit DBM representation for the exploration algorithm. This modification makes the exploration slower, but enables the verification of larger models.

In previous joint work [CCM+94, CCM97], later extended in the Ph.D. thesis of Campos [Cam96], we have taken a different approach to the verification of timed systems, by focusing on a discrete-time model with unit transitions. Although very simple, this model is applicable in many situations, and has proved especially useful for systems whose components are naturally scheduled to execute in discrete time intervals. Since the model only needs to handle unit-time transitions, symbolic representation and analysis techniques based on BDDs from the domain of untimed systems are directly applicable, and show the same efficiency in practice. As a significant advantage, the approach allows not only the verification of specifications in temporal logics with or without explicit timing, but also the computation of quantitative properties about the system behavior. These include precise lower and upper bounds on execution times or on times spent in states that satisfy certain conditions, and can be used for detailed assessment of system properties.

The fundamental difference between the above approach and the work presented in this thesis lies in the application domain, and has consequences for modeling and efficiency. Most of the examples analyzed with the approach of [CCM+94] are composed of interacting processes executing on a single processor, or represent hardware and embedded systems where signals are discretely sampled. For these, the unit-time model is very appealing, and provides an efficiency that can likely not be matched for a continuous-time model with multiple clocks. Our thesis presents a general approach to reduction that is targeted mostly at asynchronous timed systems in which discretization may not preserve the system behavior, or lead to state space explosion.

More recently, two data structures have been defined that are specifically tailored to the representation of difference constraints that appear in time zones. In both cases, one of the goals is to efficiently represent unions of time zones in the reached state space, rather than having to represent each time zone separately. Clock difference diagrams [BLP+99] are multiway decision diagrams, in which levels are indexed by clock pairs (i.e., clock differences), and each lower-level node corresponds to an interval on the real time scale for the corresponding clock difference. In difference decision diagrams [MLAH99], the decision is binary and is given by the truth value of an atomic clock constraint. In addition, DDDs are the first data structure that makes possible model checking of timed automata in a fully symbolic fashion.

#### 1.4 Outline

Chapter 2 starts by presenting the basic principles underlying partial order reduction. We give a proof for the correctness of partial order reduction using a weaker notion of independence. Next, we present a static approach to reduction, in which the reduced model is generated at compile-time. The next three chapters present our results concerning the application of reduction to timed systems. In Chapter 3, after introducing the local-time model for networks of timed automata, we show how to apply partial order reduction to the model checking of a timed extension of LTL. Chapter 4 presents a different reduction method, also for timed automata, but this time based on the region graph construction. Then, we show how partial order reduction can be incorporated into an exploration algorithm for timed event/level structures.

Chapter 5 presents our most general result. We identify the principles underlying the reduction techniques presented so far and apply them to a model of timed systems that can be particularized to either timed automata, time Petri nets or TEL structures. Chapter 6 presents a performance evaluation of the reduction method from Chapter 3 on systems modeled as timed automata, the most expressive of the timed models analyzed so far with partial order reduction. Finally, our conclusions and some directions for future work can be found in Chapter 7.

# Chapter 2

## Partial Order Reduction

#### 2.1 Introduction

The main obstacle for automatic verification methods based on state space exploration is the fact that the systems to be verified often have prohibitively many states for an exhaustive traversal. The state space of a system made up of several components is the product of the state spaces of the individual parts, and its size is therefore exponential in the number of components. Thus, the size of the global system quickly becomes unmanageable, even if each individual component is of relatively small size. This has been called the *state space explosion problem*.

A wide array of techniques has been developed to alleviate this problem. Methods based on compositional reasoning verify the system behavior based on properties of the individual components, without having to construct the global state space. Other methods are relatively independent of the modular system structure. Abstraction techniques create smaller, high-level models that approximate the original one, by removing irrelevant detail. On-the-fly and local model checking techniques restrict exploration to only those parts of the system state space which are relevant for the verified property. Symbolic techniques use an implicit representation of the state space, which does not bear a direct relationship to the number of states and can be significantly smaller.

Partial order reduction is a technique that constructs a smaller state space by addressing a specific reason behind the state space explosion, namely the existence of many potentially equivalent execution traces. This method is typically applied to asynchronous systems, which are described using an interleaving model of computation. Concurrent events are modeled by allowing their execution in all possible orders relative to each other. This serialization creates a large number of possible states and paths. However, not all different interleavings can be generally distinguished by a specification. Partial order reduction techniques take advantage of this by generating and exploring a model with only a reduced set of interleavings, and thus fewer states. At the same time, the reduced model is guaranteed to contains at least one representative from each class of equivalent behaviors, thus preserving the truth value of the specification.

In this chapter, we first present the basic principles behind the partial order reduction method. Next, we prove that a relaxed independence relation between transitions is sufficient to ensure the correctness of the ample set method for partial order reduction. Finally, we present a variant called static partial order reduction, which incorporates reduction into the model in a preprocessing step and is thus independent of the model checking algorithm. In particular, this method can be combined with symbolic state space exploration techniques.

Several approaches that use the commutativity between selected transitions to reduce the state space of a system have been suggested in the literature. The first such method seems to have been suggested by Overman [Ove81] in his Ph.D. thesis. However, it was restricted to models whose state space did not contain loops. Later on, Katz and Peled [KP88] described a proof system for concurrent systems that took advantage of commutativity between transitions. This deduction system used as its core a set of proof rules that asserted properties of sequences that are generated by exploring certain subsets of successors from each state.

Over the last decade, several methods have been developed that apply partial order reduction to model checking of finite-state systems. The common characteristic of all these methods is that they explore only a certain subset of transitions from each state. They differ in the conditions imposed on the reduced transition set in order to guarantee correctness. Such techniques are the *stubborn set* method of Valmari [Val90], the *persistent set* method of Godefroid and Wolper [GW91, God96], and the *ample set* method of Peled [Pel93]. We will focus here on the ample set method, occasionally borrowing ideas from the stubborn set technique.

The name partial order reduction reflects the fact that the initial versions of this method used an explicit partial order semantics. Generally speaking,

a partially ordered execution is represented by a set of events and a causality relation between them. The causality relation indicates which events have to precede others in any system execution, whereas the remainder of the events that are not restricted by this relation are independent and can occur in any order. This view of the system is in contrast to a total ordering on events, in which all events are serialized, i.e., any event either precedes or follows any other event. There are versions of partial order reduction that are explicitly based on the fact that the generated reduced state space includes at least one completion into a total order for each partially ordered execution. However, most current methods are no longer based on explicitly maintaining this relation.

#### 2.2 Basic Notions

We analyze systems that are modeled as state transition graphs. Let S be the set of system states. A transition is identified with a particular action that the system can execute and is given by a relation  $\alpha \subseteq S \times S$ , which defines the pairs of states between which the action can be executed. A state transition graph is a tuple  $M = (S, S_0, T, L)$ , where  $S_0 \subseteq S$  is a set of initial states, T is a set of transitions  $\alpha \subseteq S \times S$ , and  $L: S \to \mathcal{P}(AP)$  is a labeling function that assigns to each state a subset of the set AP of atomic propositions.

A transition  $\alpha \in T$  is enabled in a state s if there exists a state s' such that  $(s,s') \in \alpha$ . Otherwise,  $\alpha$  is said to be disabled at s. A transition is deterministic if for any state  $s \in S$  there exists at most one state  $s' \in S$  such that  $(s,s') \in \alpha$ . In this case,  $\alpha$  is in fact a partial function on S, and we will use the notation  $s' = \alpha(s)$  instead of  $(s,s') \in \alpha$ . In the following, we will restrict ourselves to systems with deterministic transitions. It is still possible to model nondeterminism in such systems, since in general there can be more than one transition enabled at a given state.

An execution sequence  $\sigma$  of a state transition graph is an infinite sequence  $\sigma = s_0 \xrightarrow{\alpha_0} s_1 \xrightarrow{\alpha_1} \dots$  such that for all  $i, s_{i+1} = \alpha_i(s_i)$ . We denote by  $\sigma_i$  the suffix of  $\sigma$  that starts at state  $s_i$ , i.e.,  $\sigma_i = s_i \xrightarrow{\alpha_i} s_{i+1} \xrightarrow{\alpha_{i+1}} s_{i+2} \xrightarrow{\alpha_{i+2}} \dots$ . An execution sequence  $\sigma$  is an *initial execution sequence* if  $s_0$ , the first state in the sequence, belongs to the set of initial states  $S_0$  of M.

In an asynchronous system, an execution trace serializes transitions regardless whether they occur sequentially in the same component or concur-

rently in different components. Therefore, the number of transitions separating two events has no direct relationship to the time delay between them. Moreover, a transition which does not change the state labeling (also called a *stuttering step*) and is concurrent with an observable event will be necessarily serialized either before or after it. However, given the concurrent semantics of the system, the serialization order should not affect the specification. These observations argue (cf. [Lam83]) for a specification which cannot distinguish between sequences of identically labelled states on an execution path of the system.

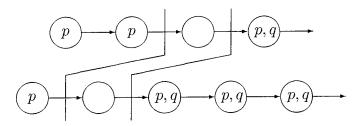

Two infinite execution sequences are stuttering equivalent (Figure 2.1) if they reduce to identical sequences of state labelings after in each of them, any finite sequence of identically labeled states is collapsed to a single state. In other words, two infinite paths  $\sigma = s_0 \xrightarrow{\alpha_0} s_1 \xrightarrow{\alpha_1} \dots$  and  $\rho = r_0 \xrightarrow{\beta_0} r_1 \xrightarrow{\beta_1} \dots$  are stuttering equivalent if one can define two infinite sequences of integers  $0 = i_0 < i_1 < \dots$  and  $0 = j_0 < j_1 < \dots$  such that  $\forall k \geq 0, L(s_{i_k}) = L(s_{i_k+1}) = \dots = L(s_{i_{k+1}-1}) = L(r_{j_k}) = L(r_{j_k+1}) = \dots = L(r_{j_{k+1}-1})$ . The indices  $i_k$  and  $j_k$  are the starting points of identically labeled subsequences of states in the two paths, respectively. The stuttering equivalence relation between  $\sigma$  and  $\rho$  is denoted by  $\sigma \sim_{\text{st}} \rho$ .

Figure 2.1: Stuttering equivalent paths

For assertions about the behavior of a program, we use the temporal logic LTL [GPSS80]. Given a finite set of propositions AP, the formulas of LTL are defined inductively as follows:

- p is a formula, for every  $p \in AP$

- if  $\varphi$  and  $\psi$  are formulas, then so are  $\neg \varphi$ ,  $\varphi \wedge \psi$ ,  $\mathbf{X} \varphi$  and  $\varphi \mathbf{U} \psi$ .

An execution sequence  $\sigma = s_0 \xrightarrow{\alpha_0} s_1 \xrightarrow{\alpha_1} \dots$  is said to satisfy an LTL formula  $\phi$  (denoted by  $\sigma \models \phi$ ) under the following conditions:

- $\sigma \models p \text{ iff } p \in L(s_0), \text{ for } p \in AP,$

- $\sigma \models \neg \varphi$  iff not  $\sigma \models \varphi$ ,

- $\sigma \models \varphi \land \psi$  iff  $\sigma \models \varphi$  and  $\sigma \models \psi$ ,

- $\sigma \models \mathbf{X} \varphi \text{ iff } \sigma_1 \models \varphi$ ,

- $\sigma \models \varphi \cup \psi$  iff  $\exists i \geq 0$  such that  $\sigma_i \models \psi$  and  $\forall j \cdot 0 \leq j < i \Rightarrow \sigma_j \models \varphi$ .

Let false stand as an abbreviation for  $p \wedge \neg p$ , and true be an abbreviation for  $\neg false$ . We also use the following abbreviations:  $\varphi \vee \psi = \neg((\neg \varphi) \wedge (\neg \psi))$ ,  $\mathbf{F} \varphi = true \mathbf{U} \varphi$ ,  $\mathbf{G} \varphi = \neg \mathbf{F} \neg \varphi$ .

For a given state transition graph M and LTL formula  $\varphi$ , the model checking problem for M and  $\varphi$  is to verify that for every initial state  $s_0 \in S_0$  and every path  $\sigma$  starting in  $s_0$ , it is true that  $\sigma \models \varphi$ . We write  $M \models \varphi$  to denote that the formula  $\varphi$  is true in model M.

An LTL formula  $\varphi$  is invariant under stuttering if for any two paths  $\sigma$  and  $\sigma'$  such that  $\sigma \sim_{st} \sigma'$ , we have  $\sigma \models \varphi$  iff  $\sigma' \models \varphi$ .

Recall that we have argued for the use of specifications that cannot distinguish between stuttering equivalent sequences. In general, an LTL formula is sensitive to stuttering if it contains the next-time operator  $\mathbf{X}$ . Denote by LTL\_X the subset of logic LTL that does not make use of the next-time operator. It has been shown by Peled and Wilke [PW97] that an LTL property is invariant under stuttering precisely if it can be expressed in LTL\_X.

The notion of stuttering equivalence can be naturally extended from paths to state transition graphs. Two state transition graphs M and M' labeled with the same set of atomic propositions are stuttering equivalent if a correspondence relation can be established covering all their execution sequences, such that corresponding execution sequences are stuttering equivalent. Specifically,

- for each initial execution sequence  $\sigma$  of M there exists an initial execution sequence  $\sigma'$  of M' such that  $\sigma \sim_{st} \sigma'$ .

- for each initial execution sequence  $\sigma'$  of M' there exists an initial execution sequence  $\sigma$  of M such that  $\sigma' \sim_{st} \sigma$ .

The fact that  $LTL_{-X}$  formulas are stuttering invariant together with the definition of stuttering equivalence of state transition graphs imply the following result:

If M and M' are stuttering equivalent state transition graphs, then for any  $LTL_{-X}$  formula  $\varphi$ ,  $M \models \varphi$  iff  $M' \models \varphi$ .

This is the main result which justifies the use of partial order reduction, since this method generates a reduced model that is stuttering equivalent to the original one. In the next section, we describe the general principles that stand behind the reduced state space generation.

## 2.3 Principles of Partial Order Reduction

The results about stuttering presented in the previous section imply that when model checking a concurrent asynchronous system with respect to a stuttering-invariant specification, one does not need to explore all behaviors of the model. If the execution sequences are divided into equivalence classes with respect to stuttering equivalence, it is sufficient to select just one behavior from each class as part of the reduced model in order to guarantee correctness.

Consider an example that illustrates the importance of reduction. Assume that the system to be verified is composed of n concurrent processes,  $P_1, P_2, \dots, P_n$ . Each process  $P_i$  has a transition  $\alpha_i$  enabled in some local state  $s_i$ , such that  $\alpha_i(s_i) = s_i'$ . The concurrent transitions  $\alpha_i$  can be ordered in n! possible ways, resulting in the exploration of  $2^n$  different states. However, it is possible that the specification is a property that relates the initial global state  $(s_1, \dots, s_n)$  with the resulting global state  $(s_1', \dots, s_n')$ , without depending on intermediate states, and the path taken between these. Thus, it is much more efficient to consider only one particular ordering and the corresponding n+1 states.

In most variants of partial order reduction, the reduced model of the system is built by performing a modified depth-first search on an explicit-state representation of the system. This is followed by a separate model checking phase performed on the reduced state-transition graph. Another option is to construct the reduced model on the fly, during model checking. This has the advantage that the state space construction can be guided taking into account the specification, and the size of the constructed model can be reduced further. Another variant, described in detail later in this chapter involves the use of breadth-first search, which has the potential of combining partial order reduction with a symbolic representation. The essential aspect

common to all these approaches is that the reduced model is built directly, without first constructing the full state graph of the original system. This is a natural requirement, since the full model is typically too large to be constructed in the first place, and an indirect approach would defeat the purpose of the reduction.

The selection of representative behaviors is made by following from each state only a subset of the enabled transitions, as opposed to an ordinary search which would explore all of them. We denote by  $ample(s) \subseteq enabled(s)$  the set of transitions which are explored from state s in the case of partial order reduction.

The key to applying partial order reduction is a procedure that calculates at each state s a suitable set ample(s) of transitions to be explored. On one hand, this set should be small (significantly smaller than the set of all enabled transitions), in order to effectively reduce the searched state space. On the other hand, the correctness of the verification result has to be preserved, by including in the reduced state graph at least one equivalent execution sequence for each execution of the original model. Finally, the overhead for computing an ample set should be sufficiently small such that the verification time is not increased compared to full state space search, offsetting the benefits of the reduction.

In order to obtain such a procedure for selecting transitions, one has to formalize the notion of transitions that can be reordered. Two key concepts play a role in this process: the notion of transition *independence* relates to the interaction between the execution of transitions in the model, whereas transition *visibility* is determined by the properties examined by the specification.

Two transitions  $\alpha, \beta \in T$  are independent in a state  $s \in S$  if they satisfy the following two conditions:

- Enabledness: If  $\alpha, \beta \in enabled(s)$ , then  $\alpha \in enabled(\beta(s))$  and symmetrically  $\beta \in enabled(\alpha(s))$ .

- Commutativity: If  $\alpha, \beta \in enabled(s)$  then  $\alpha(\beta(s)) = \beta(\alpha(s))$ .

The enabledness condition expresses the fact that two independent transitions that are enabled at a given state cannot disable each other. The commutativity condition states that the execution of two independent transitions in any order (which is guaranteed to be possible by the enabledness condition) leads to the same state. Two transitions that are independent at

each state  $s \in S$  are called *globally independent*. In the following, "independent" implicitly stands for "globally independent", unless a specific state is mentioned. Two transitions are called *dependent* (at a particular state or globally) if they are not *independent*.

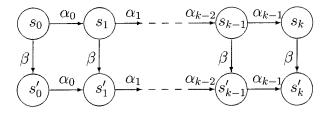

Figure 2.2: Independent transitions

The independence relation can be pictorially represented using a diagram such as the one in Figure 2.2, which depicts a simple fragment of a state transition graph. Transitions  $\alpha$  and  $\beta$  are independent in state s. A possible reduction would consider only the execution sequence  $s \xrightarrow{\alpha} s_1 \xrightarrow{\beta} s'$ , eliminating the path  $s \xrightarrow{\beta} s_2 \xrightarrow{\alpha} s'$ . However, this reduction is only correct if the checked property cannot distinguish between the intermediate states  $s_1$  and  $s_2$ . (Additional conditions for the correctness of the reduction are needed, and they will be described in the next subsection. For instance, eliminating one of these states may prevent the exploration of its successors, which may be significant for verification.)

The definition of independence given here requires independent transitions not to disable one another. However, the execution of a transition can enable the execution of another one, while maintaining independence. The partial order reduction literature often uses a more restrictive version of the enabledness condition that requires independent transitions to neither disable or enable one another. Specifically, the more restrictive condition requires that if  $\alpha \in enabled(s)$ , then  $\beta \in enabled(s)$  iff  $\beta \in enabled(\alpha(s))$ , together with the symmetric condition with  $\alpha$  and  $\beta$  reversed (the commutativity condition remains the same). In the stubborn set approach of Valmari [Val90] the less restrictive condition is consistently used, whereas the persistent set method of Godefroid et al. [God96] is defined using the more restrictive condition. The papers describing the approach of Peled generally use the more restrictive condition) and [HP94]. In both of the latter cases, reference to proofs

made using the more restrictive condition is made. In the following we use the less restrictive condition and prove that it is sufficient for handling  $LTL_{-X}$ .

To examine what it means for a specification to distinguish between two states, we introduce a second key notion, that of transition visibility. Recall that one of the elements of the state transition graph is the labeling function  $L: S \to \mathcal{P}(AP)$  which assigns to each state a set of atomic propositions. The specification may not observe all atomic propositions in AP; let  $AP' \subseteq AP$  be the subset of atomic propositions which are actually used in the formula. A transition  $\alpha$  is called invisible with respect to  $AP' \subseteq AP$  if its execution between any two states does not change the labeling with atomic propositions from AP'. Formally, the transition  $\alpha \in T$  is invisible with respect to AP' if for any two states  $s, s' \in S$  with  $s' = \alpha(s)$  we have  $L(s) \cap AP' = L(s') \cap AP'$ . A transition is called visible if it is not invisible. Since the set of atomic propositions with respect to which we consider visibility is typically given by the specification, in the following we will use the terms "visible" and "invisible" without referring specifically to a set of atomic propositions AP'.

#### 2.4 Conditions for Partial Order Reduction

The notions of independence and visibility of transitions are the fundamental properties taken into account when selecting a reduced set of transitions to explore at a given state. The selected subset of transitions should be small, in order to facilitate reduction. However, if at some state a reduced set of transitions cannot be found, the search algorithm is safe in exploring all enabled transitions. In this case, if ample(s) = enabled(s), the state is said to be  $fully\ expanded$ .

In order to describe the most general reduction conditions, and at the same time facilitate a natural proof of correctness, the reduced sets of transitions at each state are not described operationally by means of an algorithm to select them. Rather, a set of conditions is given that these transitions must satisfy [Pel93]. Following these conditions, algorithms and heuristics can be devised that actually construct an ample set for each state. Such algorithms are reviewed in a later section.

The first trivial condition has to ensure that at each step some new state can be explored in the reduced model if this is possible in the original model:

C0 (Emptiness)  $ample(s) = \emptyset$  iff  $enabled(s) = \emptyset$ .

The next constraint ensures that any path of the original state graph can

be transformed into a path of the reduced model by commuting independent transitions. This is a first step to guarantee that the reduced model will contain a representative for each path in the full state space.

C1 (Faithful decomposition) For any execution sequence  $s_0 \xrightarrow{\alpha_0} s_1 \xrightarrow{\alpha_1} \dots$  of M, and for any  $k \in \mathbb{N}$ , if  $\alpha_i \notin ample(s_0)$  for  $0 \le i \le k$ , then  $\alpha_i$  is independent of any transition  $\beta \in ample(s_0)$  for  $0 \le i \le k$ .

In other words, on any execution sequence of the original model starting at some state s, no transition which is dependent on a transition from ample(s) can occur before some transition from ample(s) is executed. Since any transition in  $enabled(s) \setminus ample(s)$  can be executed from s in the original model, this implies immediately that any transition which is not in ample(s) is independent from any transition in ample(s). This property has been named "faithful decomposition" in [KP88], since the set of enabled transitions at any state s is partitioned into two sets, ample(s) and its complement, and neither of the transitions in one of the two sets can affect the execution of a transition in the other set.

Condition C1 is used to show that for any execution sequence  $\sigma$  starting at some state  $s_0$  in the original model, some transition in  $ample(s_0)$  can be taken without disabling any of the transitions in the given sequence. This in turn, can be used as an inductive argument to construct an execution sequence in the reduced state model from each execution sequence in the original model (a complete proof is given in a subsequent section). We explain informally why this condition holds and give a complete proof in a later section. If the first transition is an ample transition,  $\alpha_0 \in ample(s_0)$ , the property is trivially true. The following two cases remain:

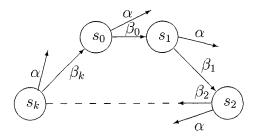

Figure 2.3: Reordering of transitions based on commutativity

(a)  $\sigma$  contains some transition from  $ample(s_0)$ . Let the first such transition be  $\beta = \alpha_k$ , with  $k \geq 1$ . By condition  $\mathbf{C1}$ ,  $\alpha_k \in ample(s_0)$  is independent of  $\alpha_0, \ldots, \alpha_{k-1}$  and commutes with all these transitions.

Thus, the transition sequence  $\alpha_k \alpha_0 \alpha_1 \dots \alpha_{k-1}$  can be executed in  $s_0$ , leads to the same state as the transition sequence  $\alpha_0 \alpha_1 \dots \alpha_k$ , and can be followed from this state by the remaining suffix  $\sigma_k$  of  $\sigma$ .

(b)  $\sigma$  does not contain any transition from  $ample(s_0)$ . Let  $\beta \in ample(s_0)$  be an arbitrary transition. By condition C1,  $\beta$  is independent from all transitions in  $\sigma$ . Therefore, if  $s'_1 = \beta(s_0)$ , then  $\alpha_0 \in enabled(s'_1)$ , and inductively if follows that the entire transition sequence  $\alpha_0\alpha_1\ldots$  can be executed from  $s'_1$ .

However, the fact that each path in the full state space can be transformed into a path which includes the same transitions and has a prefix which belongs to the reduced model is not sufficient in itself. One has to guarantee that the specification is not affected, by ensuring that the generated path is stuttering equivalent to the original one. This aspect is handled by the following condition:

C2 (Visibility) If ample(s) contains a visible transition, then the state s is fully expanded, i.e., ample(s) = enabled(s).

We explain the effect of this condition based on the cases (a) and (b) presented for condition C1. In case (a), since  $\alpha_0 \notin ample(s_0)$ , it follows that state  $s_0$  is not fully expanded and thus all transitions from it must be invisible. If we denote  $s_i' = \alpha_k(s_i)$ , for  $0 \le i \le k$  (cf. Fig. 2.3 for  $\beta = \alpha_k$ ), then we have  $L(s_i) = L(s_i')$ . Thus the two state sequences  $s_0s_1 \dots s_ks_k'$  and  $s_0s_0's_1'\dots s_{k-1}'s_k'$  are stuttering equivalent, since a one-to-one correspondence of labelings exists after collapsing  $s_k$  with  $s_k'$  in the first sequence and  $s_0$  with  $s_0'$  in the second. A similar argument holds in case (b). Here too,  $\beta$  must be invisible, and after collapsing  $s_0$  and  $s_0'$ , the prefixes  $s_0s_1 \dots s_k$  and  $s_0s_0's_1'\dots s_k'$  are stuttering equivalent for any k.

Note that one of the possible transformation cases described for condition C1 (specifically, the second) does not consume any transition from  $\sigma$  while generating an alternate execution sequence in the reduced state model. Instead, a supplementary transition from the ample set of the current state is inserted. It is possible for this step to be repeated sufficiently often, so that the inserted ample transitions closes a cycle in the state space of the reduced (and original) model (see Figure 2.4). Then, a stuttering-equivalent path for  $\sigma$  will not be generated, since the transition  $\alpha_0$  will never be explored, despite remaining continually enabled while executing the ample transitions. This can affect the truth value of the specification, since  $\alpha_0$  may be visible

or lead to parts of the state space which are not explored otherwise. The following condition guarantees that no transition is ignored and the above case does not occur:

Figure 2.4: Cycle-closing condition

C3 (Cycle closing) A transition which is enabled in every state of a cycle in the reduced state space belongs to the ample set of some state on the cycle.

The conditions for partial order reduction can be simplified if model checking is done under fairness assumptions. Typically, the verified system consists of multiple processes, and the usual notion of fairness states that each process has to execute infinitely often. Noting that two transitions enabled at the same local state of a process are dependent, this notion of fairness implies the following condition [Pel94, Pel96a]:

**F** If a transition  $\alpha$  is enabled in the starting state s of an execution sequence  $\sigma$ , then  $\sigma$  must contain either  $\alpha$  or a transition dependent on  $\alpha$ .

The fairness condition  $\mathbf{F}$  ensures precisely that case (b) discussed above cannot happen. Indeed, if  $\mathbf{F}$  is applied to  $\alpha \in ample(s)$ , then  $\sigma$  must contain either  $\alpha$  or some transition  $\beta$  dependent on it. In the latter case,  $\mathbf{C1}$  states that some transition in ample(s) must appear in  $\sigma$  before  $\beta$ . In either case,  $\sigma$  contains a transition from ample(s). In [Pel96a], the visibility condition  $\mathbf{C2}$  is handled by including visible transitions in the dependence relation. Since  $\mathbf{C1}$  implies that an ample transition is independent of all transitions outside the ample set, it follows that an ample set that contains one visible transition has to contain all of them. Thus, condition  $\mathbf{C1}$  subsumes  $\mathbf{C2}$  in this case.

This completes the presentation of the conditions which characterize ample sets. It can be shown that under these conditions, the constructed reduced model is stuttering equivalent to the original one. In the next section, we give a new proof that this result holds even if we use the less restrictive notion for transition independence discussed in Section 2.3.

### 2.5 A Proof for Partial Order Reduction

The correctness proofs for the ample set given in the literature employ a restricted definition of transition independence, which requires that two independent transitions neither disable or enable one another at any state. However, the stubborn set method of Valmari uses the less restrictive version presented in Section 2.3, which considers two transitions independent even if one of them enables the other. Godefroid [God96] presents his persistent set approach using the more restrictive independence condition, but does not mention in his comparison to ample sets and stubborn sets whether this difference is relevant or not.

A clear statement regarding the two different conditions is important, since the weaker version allows the selection of potentially smaller ample sets. Moreover, the weak version also forms the basis for existing criteria and heuristics for ample set selection such as those used in the SPIN model checker [HP94]. In the following, we prove the the correctness of ample set reduction for  $LTL_{-X}$  model checking using the weaker independence condition. An alternative, independent proof of this result is given in [CGP99].

We prove that for every transition sequence  $\sigma$  in the original state transition graph we can construct a stuttering equivalent sequence  $\sigma'$  in the reduced model. Let  $\sigma = s_0 \stackrel{\alpha_0}{\to} s_1 \stackrel{\alpha_1}{\to} \cdots s_n \stackrel{\alpha_n}{\to} \cdots$  be an arbitrary transition sequence. Given  $\sigma$  and a natural number i, we denote by  $\sigma_{\leq i}$  the prefix of  $\sigma$  formed by taking the first i transitions, and by  $\sigma_{\geq i}$  the remaining suffix of the transition sequence. We prove by induction on i that for prefixes of  $\sigma$  with length  $i \geq 0$  we can construct a sequence  $\sigma'_{\leq j}$  of length  $j \geq 0$  which is stuttering equivalent to  $\sigma_{\leq i}$ . Moreover,  $\forall k < j \cdot \alpha'_k \in ample(s'_k)$ , i.e.,  $\sigma'_{\leq j}$  is a finite sequence of transitions which can be taken in the reduced model. In the course of the induction proof, we will refer to i and j as the current points in  $\sigma$  and  $\sigma'$ , respectively. At each point,  $\sigma'_{\leq j}$  will contain all transitions of  $\sigma_{\leq i}$  (in some order), with two possible types of transitions added:

- (i) Ample transitions after the current point in  $\sigma$  may be executed earlier (before the current point) in  $\sigma'$ . The finite ordered set (sequence)  $I \subseteq \mathbb{N}$  contains the indices of transitions beyond the current point i in  $\sigma$  that have been already included in  $\sigma'$ . We call such transitions marked.

- (ii) Additional ample transitions may be inserted in  $\sigma'$  in order to ensure that it is a legal transition sequence in the reduced model. We denote the sequence of all such inserted transitions by  $\delta$ .

**Notation:** If  $I \subseteq \mathbb{N}$  is a finite increasingly ordered set of indices, we denote by  $\sigma|_I$  the transition sequence obtained by selecting from  $\sigma$  the transitions with indexes in I (in the given order). Similarly, we denote by  $\sigma|_{\bar{I}}$  the sequence obtained by deleting from  $\sigma$  the transitions whose indices are in I (here the ordering of I is irrelevant).

Our induction invariant relates  $\sigma, i, \sigma', j, I$ , and  $\delta$  as follows:

- (a) The transition sequence  $\sigma'_{\leq j}$  is stuttering equivalent to  $\sigma_{\leq i}$ . In particular,  $L(s_i) = L(s'_i)$ .

- (b) If  $k \in I$ , then  $k \geq i$  and  $\alpha_k$  is invisible and independent of  $\alpha_l$ , for all  $l \notin I, i \leq l < k$ . (A marked transition is invisible and independent of all unmarked transitions past the current point in  $\sigma$  but preceding it.)

- (c) The transition sequence  $(\alpha_k)|k \geq i, k \notin I$ , obtained from the suffix  $\sigma_{\geq i}$  by removing marked transitions, is enabled in  $s'_i$  in the original model.

- (d) Each transition in  $\delta$  is invisible and independent of all transitions  $\alpha_k$ ,  $\forall k \geq i, k \notin I$  (all unmarked transitions past the current point in  $\sigma$ ).

- (e)  $s_i \stackrel{\sigma|_I\delta}{\longrightarrow} s_j'$ . That is, the marked transitions (comprising  $\sigma|_I$ ) together with the inserted transitions (comprising  $\delta$ ) are exactly those that belong to  $\sigma'_{\leq j}$  but not to  $\sigma_{\leq i}$ . Their sequence is enabled in  $s_i$  and takes this state to  $s_j'$ .

For the base case, choose j=i=0,  $s_0'=s_0$ ,  $I=\emptyset$  and  $\delta=\epsilon$  (the empty sequence). All parts of the invariant are trivially satisfied: (a) is true because both transition sequences consist of just the same initial state, (b) is vacuously true, since I is empty, (c) is true since  $\sigma$  is enabled in  $s_0$ , (d) is vacuously true since  $\delta$  is empty, and (e) is true since both  $\sigma|_{I}=\delta=\epsilon$  and  $s_0=s_0'$ .

For the induction step, we consider the following cases:

1.  $i \in I$ . (The next transition in  $\sigma$  is marked.) Let i' = i + 1 and  $I' = I \setminus \{i\}$ . That is, we advance the current point in  $\sigma$  and delete  $\alpha_i$  from the set of marked transitions, since it is now before the current point. Since  $\alpha_i$  is invisible according to (b), we have  $L(s_{i+1}) = L(s_i) = L(s'_j)$ , which maintains (a). Part (b) still holds since no transitions are added to I, and  $\alpha_i$  is no longer relevant for the independence condition (since

- i'=i+1). For parts (c) and (d) the unmarked sequence of transitions after the current point in  $\sigma$  remains the same ( $\alpha_i$  is no longer marked, but it is now before the current point), and  $\delta$  does not change either. Finally,  $i=\min I$ , so  $\alpha_i$  is the first transition in  $\sigma|_I$ , therefore (e) can be written as  $s_i \stackrel{\alpha_i}{\longrightarrow} s_{i+1} \stackrel{\sigma|_{I'}\delta}{\longrightarrow} s'_j$ , the last part of which is exactly (e) after this step.

- 2.  $i \notin I$  and  $\alpha_i \in ample(s'_j)$ , so  $\alpha_i$  is a legal transition in the reduced model. We include  $\alpha_i$  in  $\sigma'$ , advance both counters (i' = i + 1, j' = j + 1) and set  $s'_{j+1} = \alpha_i(s'_j)$ . By (b) and (d),  $\alpha_i$  is independent of all transitions in  $\sigma|_I$  and  $\delta$  and therefore commutes with them. Since  $s_i \stackrel{\sigma|_I\delta}{\to} s'_j \stackrel{\alpha_i}{\to} s'_{j+1}$ , it follows that  $s_i \stackrel{\alpha_i}{\to} s_{i+1} \stackrel{\sigma|_I\delta}{\to} s'_{j+1}$ , which proves (e). Moreover,  $L(s_{i+1}) = L(s_{j+1})$ , so (a) is preserved. Part (b) is preserved since I is the same (i' = i + 1) but  $\alpha_i \notin I$ , and  $\alpha_i$  no longer appears in the independence condition. The transition sequence in part (c) is of the form  $\alpha_i\beta$  (with  $\beta$  some transition string). If  $\alpha_i\beta$  is enabled in  $s'_j$ , then  $\beta$  is enabled in  $\alpha_i(s'_j) = s'_{j+1}$ . Finally, part (d) is weakened since  $\alpha_i$  no longer appears.

- 3.  $i \notin I$ ,  $\alpha_i \notin ample(s_i)$ , and  $\exists k > i, k \notin I$ , such that  $\alpha_k \in ample(s_i)$ . That is,  $\alpha_i$  is neither marked nor ample, but there is an ample unmarked transition  $\alpha_k$  later in the sequence. Let k be the smallest such index. We mark transition  $\alpha_k$  and append it to  $\sigma'$ , i.e.,  $I' = I \cup k$ , j' = j+1 and  $s'_{j+1} = \alpha_k(s'_j)$ . Because  $\alpha_k$  is ample,  $\sigma'_{\leq j'}$  is a legal transition sequence in the reduced model. Since  $\alpha_i \notin ample(s'_j)$ ,  $s'_j$  is not fully expanded, and  $\alpha_k$  is invisible by C2. Thus  $L(s'_{i+1}) = L(s'_i) = L(s_i)$ , and (a) still holds. By condition C1, all transitions preceding  $\alpha_k$  in  $\sigma_{\geq i}|_{\bar{I}}$  (i.e.,  $\alpha_l$ with  $i \leq l < k, l \notin I$ ) have to be independent of  $\alpha_k$ , so (b) is preserved. Independence implies commutativity, so  $\alpha_k$  can be executed as first transition of  $\sigma_{\geq i}|_{\bar{I}}$  in  $s'_{i}$ , and the remainder of this sequence remains enabled in  $s'_{i+1}$ , which proves (c). Part (d) still holds since  $\delta$  is the same, and there is one less unmarked transition. By substituting  $\alpha_k$ for  $\alpha_l$  in (b), we obtain that  $\alpha_k$  commutes with all marked transitions which occur later in  $\sigma$ , and because of (d) it also commutes with the transitions in  $\delta$ . Therefore, since  $I' = I \cup k$ ,  $s_i \stackrel{\sigma|_I\delta}{\to} s'_i \stackrel{\alpha_k}{\to} s'_{i+1}$  implies  $s_i \stackrel{\sigma|_{I'}\delta}{\longrightarrow} s'_{j+1}$  (with  $\alpha_k$  inserted to preserve the increasing ordering of I') and the final part of the invariant is proved.

4.  $i \notin I$ , and  $\forall k \geq i, k \notin I$ ,  $\alpha_k \notin ample(s'_j)$ . That is, there is no remaining unmarked transition which belongs to  $ample(s'_j)$ . We need to insert an ample transition so  $\sigma'$  remains a legal transition sequence in the reduced model. Select an arbitrary transition  $\beta \in ample(s'_j)$  and let  $j' = j+1, s'_{j+1} = \beta(s'_j)$ . We also append  $\beta$  to the sequence of transitions inserted so far,  $\delta' = \delta \beta$ . Again, since  $s'_j$  is not fully expanded,  $\beta$  has to be invisible, so  $L(s'_{j+1}) = L(s'_j) = L(s_i)$ , and (a) still holds. None of the variables involved in (b) changes. Since  $\beta$  is independent of all transitions in  $\sigma_{\geq i}|_{\bar{I}}$ , (c) remains valid as well, and  $\beta$  can also be appended to  $\delta$  without violating (d). Finally,  $s_i \xrightarrow{\sigma|_I \delta} s'_j \xrightarrow{\beta} s'_{j+1}$ , therefore  $s_i \xrightarrow{\sigma|_I \delta'} s'_{j+1}$ , which proves (e).

To conclude the induction proof, we note that only a finite number of steps of type (3) or (4) (for which the current point in  $\sigma$  is not advanced) can be taken without performing either (1) or (2). Otherwise, the transition sequence  $\sigma'_{\geq j}$  eventually closes a cycle on which transition  $\alpha_i$  is always enabled without ever belonging to an ample set, which contradicts **C3**. Therefore, after a finite number of steps either (1) or (2) must be performed, which advances the current point in  $\sigma$  by 1, i' = i + 1. The above four cases therefore guarantee a finite procedure that constructs in the reduced model a stuttering equivalent prefix for  $\sigma_{\leq i+1}$  starting from a similar prefix for  $\sigma_{\leq i}$ . We also note that since every transition in  $\sigma_{\leq i}$  is included in  $\sigma' \leq_j$ , we have  $i \leq j$ , which ensures that j grows unbounded as i does. By induction, a stuttering equivalent sequence  $\sigma'$  exists in the reduced model for the entire transition sequence  $\sigma$ , q.e.d.

## 2.6 Calculating Ample Sets

The established conditions for ample set reduction do not directly provide an operational procedure that effectively determines an ample set of transitions at each state. To apply partial order reduction in practice, a procedure which computes ample sets has to be devised. On one hand, this procedure must generate ample sets that are small enough so that the resulting state space is significantly smaller than the original one. On the other hand, the algorithm must be sufficiently simple so that it can be implemented easily, without introducing significant overhead and slowing down verification. This section

reviews some selection criteria which are typically employed to ensure that each of the given conditions is satisfied.

It is trivial to verify that the ample set is nonempty (condition C0). Likewise, the visibility of a transition is immediately determined, and thus for condition C2 it suffices to examine each transition in turn. In fact, in order to obtain small ample sets, a single invisible transition is the ideal case.

In general, it is much more difficult however to check condition C1. First, this condition describes a property of ample sets in terms of the execution sequences of the full state-transition graph, and the principal aim of the reduction technique is to avoid constructing this graph in the first place. Furthermore, the execution sequences on which C1 would have to be checked can extend arbitrarily far into the future, up to the occurrence of the first ample transition. In general, checking condition C1 is at least as hard as checking reachability for the full state transition graph, as has been shown in [CGP99].

In practice, using an expensive algorithm that can verify condition C1 for an arbitrarily chosen set of ample transitions could be quite expensive. Instead, partial order verifiers take advantage of the specific system structure to generate ample sets of transitions for which C1 can be easily guaranteed to hold. In particular, the ample set selection becomes much easier in the typical case when the system is described as a composition of concurrent processes. We present practical conditions that can be used for concurrent processes with synchronous communication, a model which also forms the underlying control structure for timed automata, and discuss how the introduction of global data variables affects these conditions.

A system consists in this case of a set of *processes*, which are modeled as state-transition graphs. Each process may also have a set of *local variables* that can be changed only by transitions performed by that process. Control states and local variables form the *local state* of the process, and the product of the local states forms the *global state* of the system. A transition that only changes the control state and local variables of a process is called an *internal* transition.

In the synchronous communication model, the sender and the receiver coordinate, and the sending and receiving transitions occur simultaneously. This is the case, for example, in Communicating Sequential Processes [Hoa95] and in the rendezvous model of ADA. The sending and receiving transitions can therefore be considered as a common transition shared by the two processes. We call such a transition a communication transition. Simultaneous