| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                       |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Form Approved<br>OMB No. 0704-0188                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| List and the mark think the state condent a                                                                                                                                                                                                                                                                                     | an - manting and the wave of the destinger to | The state the state of the stat | end instructions, searching existing data sources,<br>in this builden estimate or line lither aspect of this<br>constron (Denations and Reports, 1215 Jefferson<br>(264-0188) Washerson (2010)                                                                                                                    |  |

| 1. AGENCY USE ONLY (Leave Dia                                                                                                                                                                                                                                                                                                   |                                               | 3. REPORT TYPE AND O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                   |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                           | ······································        | 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FUNDING NUMBERS                                                                                                                                                                                                                                                                                                   |  |

| Analyzing Safety Pro                                                                                                                                                                                                                                                                                                            | perties of Requirement                        | .s Gr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ant F496209310034                                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                 |                                               | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F49620-93-1-0034                                                                                                                                                                                                                                                                                                  |  |

| 5. AUTHOR(S)<br>Joanne Atlee, Marsha                                                                                                                                                                                                                                                                                            | a Chechik, and John Gar                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11620-9.5-1-0034                                                                                                                                                                                                                                                                                                  |  |

| 7. PERFORMING ORGANIZATION I                                                                                                                                                                                                                                                                                                    |                                               | 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PERFORMING ORGANIZATION                                                                                                                                                                                                                                                                                           |  |

| University of Maryla<br>Department of Comput                                                                                                                                                                                                                                                                                    |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NEPORT NUMBER                                                                                                                                                                                                                                                                                                     |  |

| College Park, MD 20                                                                                                                                                                                                                                                                                                             |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                 | GENCY NAME(S) AND ADDRESS(ES                  | ) 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . SPONSORING / MONITORING<br>AGENCY REPORT NUMBER                                                                                                                                                                                                                                                                 |  |

| AFOSR/NM<br>110 Duncan Avenue Ro                                                                                                                                                                                                                                                                                                | oom B115                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

| Bolling AFB DC 2033                                                                                                                                                                                                                                                                                                             |                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /                                                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                 |                                               | IMMII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 204 190 —                                                                                                                                                                                                                                                                                                         |  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                         |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                         | ' STATEMENT                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25. DISTRIBUTION CODE                                                                                                                                                                                                                                                                                             |  |

| 12a. DISTRIBUTION / AVAILABILITY<br>Approved for public                                                                                                                                                                                                                                                                         | release;                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

| 12a. DISTRIBUTION / AVAILABILITY                                                                                                                                                                                                                                                                                                | release;                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

| 12a. DISTRIBUTION / AVAILABILITY<br>Approved for public                                                                                                                                                                                                                                                                         | release;<br>ited.                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |  |

| <ul> <li>Approved for public distribution unlim</li> <li>Abstract (Maximum 200 wor)</li> <li>ABSTRACT (Maximum 200 wor)</li> <li>Precise notation that all cases of a such notation, we early stages of the stechnique because is report describes models of these software a models of the prop</li> </ul>                     | e release;<br>ited.                           | cify unambiguous require<br>re considered and docum<br>automatically analyze so<br>e. We use model checking<br>can check properties of l<br>es our efforts to use it t<br>ements model system sai<br>from requirements by cr<br>cking to determine if th<br>om a case study in whic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ements, and ensure<br>nented. Using one<br>oftware artifacts at<br>g as our verification<br>large systems. This<br>to analyze software<br>fety properties and<br>reating abstractions<br>ne abstractions are                                                                                                      |  |

| <ul> <li>Approved for public distribution unlim</li> <li>Abstract (Maximum 200 wor)</li> <li>ABSTRACT (Maximum 200 wor)</li> <li>Precise notation that all cases of a such notation, we early stages of the stechnique because is report describes models of these software a models of the prop</li> </ul>                     | e release;<br>ited.                           | cify unambiguous require<br>re considered and docum<br>automatically analyze so<br>e. We use model checking<br>can check properties of l<br>es our efforts to use it t<br>ements model system sai<br>from requirements by cr<br>cking to determine if th<br>om a case study in whic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ements, and ensure<br>nented. Using one<br>oftware artifacts at<br>g as our verification<br>large systems. This<br>to analyze software<br>fety properties and<br>reating abstractions<br>ne abstractions are<br>ch we analyzed the                                                                                |  |

| <ul> <li>Approved for public distribution unlim</li> <li>Abstract (Maximum 200 wor)</li> <li>ABSTRACT (Maximum 200 wor)</li> <li>Precise notation that all cases of a such notation, we early stages of the stechnique because is report describes models of these software a models of the prop</li> </ul>                     | e release;<br>ited.                           | cify unambiguous require<br>re considered and docum<br>automatically analyze so<br>e. We use model checking<br>can check properties of l<br>es our efforts to use it t<br>ements model system sat<br>from requirements by cr<br>ecking to determine if th<br>om a case study in whic<br>ystem.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ements, and ensure<br>nented. Using one<br>oftware artifacts at<br>g as our verification<br>large systems. This<br>to analyze software<br>fety properties and<br>reating abstractions<br>ne abstractions are<br>ch we analyzed the                                                                                |  |

| Approved for public<br>distribution unlim<br>13. ABSTRACT (Maximum 200 wor<br>Precise notation<br>that all cases of a<br>such notation, we<br>early stages of the<br>technique because is<br>report describes m<br>requirements and of<br>that designs model<br>of these software a<br>models of the prop<br>requirements and d | e release;<br>ited.                           | cify unambiguous require<br>re considered and docum<br>automatically analyze so<br>e. We use model checking<br>can check properties of l<br>es our efforts to use it t<br>ements model system sat<br>from requirements by cr<br>tecking to determine if th<br>om a case study in whice<br>ystem.<br>DTIC QUALITY INS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ements, and ensure<br>nented. Using one<br>oftware artifacts at<br>g as our verification<br>large systems. This<br>to analyze software<br>fety properties and<br>reating abstractions<br>are abstractions are<br>ch we analyzed the<br>IPECTERD C                                                                 |  |

| Approved for public<br>distribution unlim<br>13. ABSTRACT (Maximum 200 wor<br>Precise notation<br>that all cases of a<br>such notation, we<br>early stages of the<br>technique because is<br>report describes m<br>requirements and of<br>that designs model<br>of these software a<br>models of the prop<br>requirements and d | e release;<br>ited.                           | cify unambiguous require<br>re considered and docum<br>automatically analyze so<br>e. We use model checking<br>can check properties of l<br>es our efforts to use it t<br>ements model system sat<br>from requirements by cr<br>tecking to determine if th<br>om a case study in whice<br>ystem.<br>DTIC QUALITY INS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ements, and ensure<br>nented. Using one<br>oftware artifacts at<br>g as our verification<br>large systems. This<br>to analyze software<br>fety properties and<br>reating abstractions<br>ne abstractions<br>ne abstractions are<br>ch we analyzed the<br>EPECTED C<br>15. NUMBER OF PAGES<br>34<br>16. PRICE CODE |  |

.

.\*

.

# Analyzing Safety Properties of Requirements

. .

| Joanne Atlee              | Marsha Chechik            | John Gannon                  |

|---------------------------|---------------------------|------------------------------|

| Dept. of Computer Science | Dept. of Computer Science | Dept. of Computer Science    |

| University of Waterloo    | University of Toronto     | University of Maryland       |

| Waterloo, Ontario N2L 3G1 | Toronto, Ontario, M5S 1A4 | College Park, Maryland 20742 |

# 1 Introduction

Precise documentation of software requirements has several potential benefits[31]: designers know what they are to build; reviewers can check that customers' intentions are met; testers can formulate test cases independently from the system's implementation; and maintainers can use the original requirements to learn about the system before making their changes. Several formal requirements notations (e.g., the Software Cost Reduction (SCR) notation[3, 21, 23], the Requirements State Machine Language[27], and Statecharts[19]) have been used to specify the requirements of large, real-world avionics applications (the A-7E aircraft, the FAA's Traffic Collision and Avoidance System, and the Lavi fighter's avionics system, respectively). These requirements notations describe systems as sets of concurrently executing state machines which respond to events in their environments.

The keys to winning acceptance for employing precise documentation during system development include demonstrating that its use improves software quality, amortizing the cost of its creation across several different analysis activities, and reducing the cost of analysis through automation. Our research has focused on developing techniques that use formal methods to enable automatic analysis of program artifacts at early stages of the software development life cycle[5, 7, 6, 14, 15].

In this report, we summarize our work to analyze program requirements and designs. We use model checking[17] because it can be fully automated and can check properties of large systems. Developers are more likely to understand a proof technique like model checking, which is based on search and which produces counter examples when proofs fail, than a technique based inductive theorem proving. Model checking has been successfully applied to verifying and debugging hardware designs (e.g., [10, 8, 16]). More recently it has been used to analyze software artifacts. Model checking has been used to detect design flaws in software architecture designs[2] and Z specifications[26], and to prove properties of cache coherence protocols[35] and concurrent Ada programs[11]. The key to success in these endeavors is creating an appropriate abstraction of a system so that results obtained from analyzing the abstraction also apply to the system.

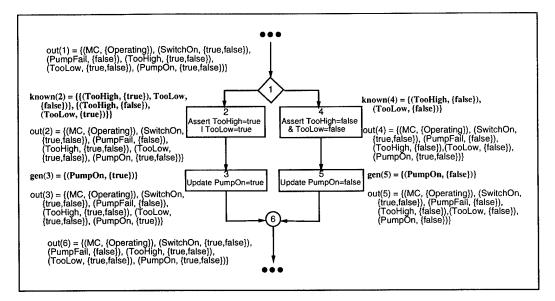

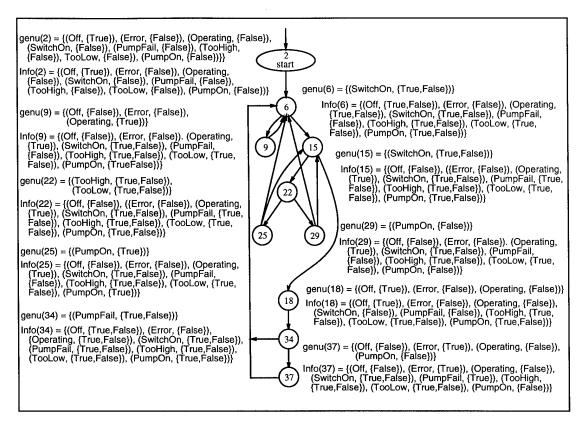

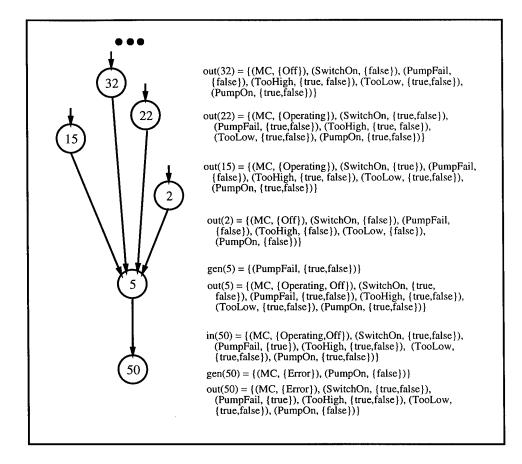

We analyze safety properties of software requirements and designs by creating models from such artifacts and using model checking techniques to determine if the safety properties are true for the model. We have developed automated techniques to translate requirements into a logical model. We represent a system's safety assertions as logical formulas in a branching-time temporal logic, Computation Tree Logic[18] (CTL), and use existing CTL model checkers[10, 28] to check our models.

Analyzing the safety properties of system's requirements, however, fails to tell us whether or

not its implementation preserves these properties. To verify that a system design is consistent with its requirements, we would like to ensure that the design's state transitions are enabled by the same events as those of the requirements, and the requirement's safety properties also hold in the design. To judge global properties like these, we need to determine the possible system states which exist at different program points. The detailed bookkeeping necessary to do this exceeds the capabilities of human reviewers for all but small implementations. We present a language for specifying detailed designs and an analysis technique to create a model of a design through abstract interpretation of the language constructs. We also show how to use requirements information to automatically generate properties which ensure that required state transitions appear in the design and systems goals hold, and how these properties are checked against the design model.

. .

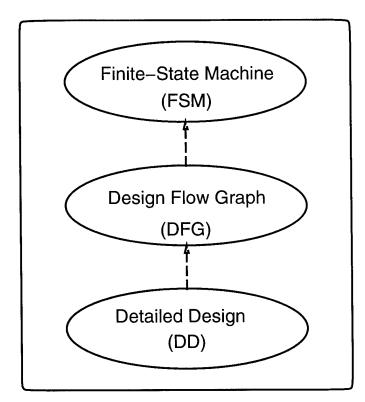

The rest of the report is organized as follows: Section 2 introduces the SCR requirements specification format. Section 3 explains basic principles behind model checking. In Section 4 we show how to create a logic-model semantics that precisely models the operational semantics of SCR modes and mode transitions, so that system goals can be translated into temporal logic formulas and model checking techniques used to verify that these formulas hold in the requirements. Section 6 presents our techniques for verifying designs: how to generate first-order logic properties from SCR tables, how build finite-state abstractions of designs, and how to check the properties using a special-purpose model checker. Section 10 describes a case study in which we analyzed the requirements and design of a Water-Level Monitoring System[33]. We present our conclusions in Section 11.

# 2 SCR Requirements

The SCR requirements notation was developed by a research group at the Naval Research Laboratory as part of the Software Cost Reduction project [3, 23]. A complete SCR requirements specification contains behavioral, functional, precision, and timing requirements of a software system as well as assumptions about the environment in which the system will operate. In SCR requirements, environmental variables are monitored, and their values are translated to input data values for a a set of finite state machines (FSMs). The FSMs record the system's states and set the values of output data items. The values of output data items control variables in the system's environment[29, 33].

### 2.1 Behavioral Requirements

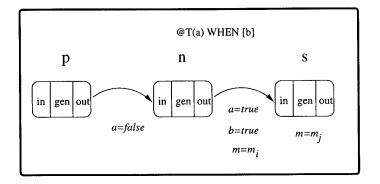

The input language of each machine is a set of *conditioned events*. A *condition* is a predicate on monitored or mode class variables, an *event* when the value of a condition changes. Let condition SwitchOn represent predicate [On/Off switch = On], and condition PumpFail represent predicate [Pump failure = true]. Primitive events @T(SwitchOn) and @F(SwitchOn) represent condition SwitchOn becoming true and becoming false, respectively. Conditioned event

### @T(SwitchOn) WHEN [~ PumpFail]

describes the event SwitchOn becomes true while PumpFail remains false. Formally, conditioned event @T(SwitchOn) WHEN [PumpFail] occurs at time t if and only if primitive event @T(SwitchOn) occurs at time t and condition PumpFail is true for some non-zero interval of time leading up to and including time t [3]. SwitchOn is called the *triggering event* and Pump-Fail is called the event's WHEN condition.

A state of the monitored environment is defined by the current values of the conditions, and the state space is the set of possible combinations of values of conditions. However, the behavior of the system is rarely affected by the values of all the conditions at once. A *mode class* defines a set of states, called *modes*, that partition the monitored environment's state space. One mode is designated as the *initial mode*. Assumptions about the initial state of the environment are specified with the initial mode. Transitions between pairs of modes are activated by conditioned events. If a conditioned event can trigger two or more transitions from the same mode, then the mode class is non-deterministic.

An SCR requirements document contains the specification of one or more mode classes. At all times, the system is in exactly one mode of each mode class. Each mode class specifies one aspect of the system's behavior, and the system's global behavior is defined to be the composition of the specification's mode classes.

Table 1 shows a mode transition table for a Simplified Water-Level Monitoring System (SWLMS). A switch controls whether the system is on or off. If the system is on and its sensors detect too much (too little) water, a pump is turned on for a fixed period to remove (add) some water. If the sensor or the pump fails, the system enters an error state. This simplified version of the system has no error recovery, so there are no transitions from the error state. This system has one mode class MC with modes Off, Operating, and Error; four monitored variables SwitchOn, PumpFail, TooHigh, and TooLow; and a single controlled variable PumpOn. Below the mode transition table is the specification of the system's initial mode. Mode class MC starts in mode Off, and all monitored variables are initially false. The specification of a mode class's transition relation has a tabular format. Each row in the table specifies a conditioned event that activates a transition from the mode on the left to the mode on the right. For example, a table entry of "@T" (or "@F") under a column represents a triggering event for the condition represented by the variable labelling the column, a table entry of "t" (or "f") represents a WHEN condition for the condition. If the value of a condition does not affect the occurrence of a conditioned event, then the table entry is marked with a hyphen ("-"). If during time interval  $[t - \epsilon, t]$  the system is in mode Off, the switch is in the Off position and the pump is operating; and if at time t the switch is moved to the On position while the pump continues to operate; then the system is in mode Operating at time t.

| Current Mode | SwitchOn | PumpFail | New Mode  |

|--------------|----------|----------|-----------|

| Off          | @T       | f        | Operating |

|              | —        | @T       | Error     |

| Operating    | @F       | f        | Off       |

|              | _        | @T       | Error     |

Initial: Off (~SwitchOn & ~PumpFail & ~TooHigh & ~TooLow) Assumptions: TooLow->>~TooHigh

Table 1: Mode transition table for SWLMS.

Values of controlled variables change in response to events when the system is in particular

modes. Table 2 shows an event table for the controlled variable PumpOn, which represents the pump being turned on or off. This variable starts with value false and becomes true when the system is in mode Operating and either event @T(TooHigh) or @T(TooLow) occurs.

| Mode      | Triggering Event |              |

|-----------|------------------|--------------|

| Operating | @T(TooHigh)      |              |

|           | @T(TooLow)       | -            |

|           | _                | @F(TooHigh)  |

|           |                  | @F(TooLow)   |

|           | —                | @T(PumpFail) |

| Off       | _                | @T(PumpFail) |

| PumpOn =  | True             | False        |

Initial: False

Table 2: Event table for controlled variable PumpOn.

### 2.2 Environmental Assumptions

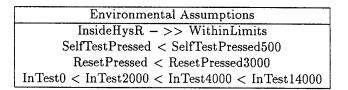

An SCR requirements document also specifies assumptions of the behavior of the environment. Similar to the *NAT* relation in Parnas's 4-variable model of system requirements [29], an *as*sumption specifies constraints on the values of conditions, imposed either by laws of nature or by other mode classes in the system. As such, assumptions are invariant constraints that must hold in all system states.

The syntax and semantics of assumption specifications are described in [4]; for the purposes of this report, symbol "|" denotes exclusive-or, "->" denotes implication, "->>" denotes strict implication, and "<" denotes an ordering on the lengths of time that conditions are true<sup>1</sup>. The assumptions specified in Figure 1 state that the water level cannot be too high and too low at the same time.

#### 2.3 System Goals

Finally, an SCR requirements specification often includes a set of *goals* that the system is required to meet. These goals are not additional constraints on the required behavior; it is expected that the SCR tabular specification enforces these goals. Specified goals are redundant information that are included in the specification because the reader might not deduce these properties from the tabular specifications. Most of the goals specified in the SWLMS example are mode invariants:

• If the system is in mode Off, then conditions SwitchOn and PumpFail are false.

Other goals express global behavioral requirements on the occurrence of an event:

• If event @T(SwitchOn) occurs, the system cannot remain in mode Off.

<sup>&</sup>lt;sup>1</sup>In  $a \to b$  the state space in which a is true is a strict subset of the state space in which b is true. As with implication, whenever a is true, b must also be true. Because of the relationship between their state spaces, b must be true whenever a is changing value, and a must be false whenever b changes value.

Temporal requirements on state changes can also be specified.

• When the water level becomes too high while the system is in mode Operating, the pump will immediately be turned on.

. .

# 3 Model Checking