## NIST SPECIAL PUBLICATION 400-97

#### U.S. DEPARTMENT OF COMMERCE/Technology Administration National Institute of Standards and Technology

Semiconduction Wieasine menustechnolo

Test Springeme Implementational Document.

DC Parametric Lest Spanetices and Test Medical stores and Test Medical stores.

O Pasabisia

19961008 035

# DISCLAIMER NOTICE

THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

Maria and and

he National Institute of Standards and Technology was established in 1988 by Congress to "assist industry in the development of technology . . . needed to improve product quality, to modernize manufacturing processes, to ensure product reliability . . . and to facilitate rapid commercialization . . . of products based on new scientific discoveries."

NIST, originally founded as the National Bureau of Standards in 1901, works to strengthen U.S. industry's competitiveness; advance science and engineering; and improve public health, safety, and the environment. One of the agency's basic functions is to develop, maintain, and retain custody of the national standards of measurement, and provide the means and methods for comparing standards used in science, engineering, manufacturing, commerce, industry, and education with the standards adopted or recognized by the Federal Government.

As an agency of the U.S. Commerce Department's Technology Administration, NIST conducts basic and applied research in the physical sciences and engineering, and develops measurement techniques, test methods, standards, and related services. The Institute does generic and precompetitive work on new and advanced technologies. NIST's research facilities are located at Gaithersburg, MD 20899, and at Boulder, CO 80303. Major technical operating units and their principal activities are listed below. For more information contact the Public Inquiries Desk, 301-975-3058.

#### Office of the Director

- · Advanced Technology Program

- Quality Programs

- · International and Academic Affairs

#### **Technology Services**

- · Manufacturing Extension Partnership

- · Standards Services

- · Technology Commercialization

- Measurement Services

- · Technology Evaluation and Assessment

- · Information Services

## Materials Science and Engineering Laboratory

- · Intelligent Processing of Materials

- Ceramics

- Materials Reliability1

- · Polymers

- · Metallurgy

- · Reactor Radiation

## Chemical Science and Technology Laboratory

- · Biotechnology

- · Chemical Kinetics and Thermodynamics

- · Analytical Chemical Research

- Process Measurements

- · Surface and Microanalysis Science

- Thermophysics<sup>2</sup>

#### **Physics Laboratory**

- · Electron and Optical Physics

- Atomic Physics

- · Molecular Physics

- · Radiometric Physics

- · Quantum Metrology

- · Ionizing Radiation

- Time and Frequency<sup>1</sup>

- Quantum Physics<sup>1</sup>

#### **Manufacturing Engineering Laboratory**

- Precision Engineering

- · Automated Production Technology

- Intelligent Systems

- · Manufacturing Systems Integration

- · Fabrication Technology

## **Electronics and Electrical Engineering Laboratory**

- Microelectronics

- · Law Enforcement Standards

- Electricity

- Semiconductor Electronics

- Electromagnetic Fields1

- Electromagnetic Technology<sup>1</sup>

- Optoelectronics<sup>1</sup>

#### **Building and Fire Research Laboratory**

- Structures

- · Building Materials

- Building Environment

- · Fire Safety

- · Fire Science

#### **Computer Systems Laboratory**

- Office of Enterprise Integration

- · Information Systems Engineering

- · Systems and Software Technology

- Computer Security

- · Systems and Network Architecture

- Advanced Systems

## **Computing and Applied Mathematics Laboratory**

- Applied and Computational Mathematics<sup>2</sup>

- Statistical Engineering<sup>2</sup>

- Scientific Computing Environments<sup>2</sup>

- Computer Services

- Computer Systems and Communications<sup>2</sup>

- Information Systems

<sup>&</sup>lt;sup>1</sup>At Boulder, CO 80303.

<sup>&</sup>lt;sup>2</sup>Some elements at Boulder, CO 80303.

### Semiconductor Measurement Technology:

## Test Structure Implementation Document: DC Parametric Test Structures and Test Methods for Monolithic Microwave Integrated Circuits (MMICs)

#### C. E. Schuster

Semiconductor Electronics Division Electronics and Electrical Engineering Laboratory National Institute of Standards and Technology Gaithersburg, MD 20899-0001

#### Sponsored by:

Defense Advanced Research Projects Agency Arlington, VA 22209-2308 and U.S. Air Force Wright Laboratory Wright-Patterson AFB, OH 45433-6543

September 1995

National Institute of Standards and Technology Special Publication 400–97 Natl. Inst. Stand. Technol. Spec. Publ. 400–97, 85 pages (September 1995) CODEN: NSPUE2

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1995

#### TABLE OF CONTENTS

|              |                 |                                                        | Page |

|--------------|-----------------|--------------------------------------------------------|------|

| ΑB           | STRACT          |                                                        | 1    |

|              |                 |                                                        |      |

| EX           | ECUTIVE SU      | JMMARY                                                 | 2    |

| 1.           | INTRODUC        | TION                                                   | 5    |

| 1.1.         |                 |                                                        |      |

| 1.2.         | -               |                                                        |      |

| 1.2.         | 1.2.1.          | NISTGAAS Form and Function                             |      |

|              | 1.2.2.          |                                                        |      |

| 2.           |                 | TATION CONSIDERATIONS                                  |      |

| 2.<br>2.1.   |                 |                                                        |      |

| 2.1.<br>2.2. | -               | Test Structures                                        |      |

|              | _               | ng a Test Vehicle                                      |      |

| 2.3.         | _               | the Testing Environment                                |      |

| 2.4.         | -               | ng Data Analysis Capabilities                          |      |

| 3.           |                 | R-AIDED DESIGN (CAD) CELL LIBRARY                      |      |

| 3.1.         | Overview        | 7                                                      | 9    |

| 3.2.         | Process L       | ayers                                                  | 10   |

| 3.3.         |                 | rs and Patterns                                        |      |

| 3.4.         | Cell Nam        | ing Conventions                                        |      |

|              | 3.4.1.          | Test Structure Names                                   |      |

|              | 3.4.2.          | Layer Names                                            |      |

|              | 3.4.3.          | Dimensions                                             |      |

| 3.5.         |                 | wing Hierarchy                                         |      |

| 3.6.         | Obtaining       | g the NISTGAAS Cell Library                            | 13   |

| 4.           | <b>ACKNOWLE</b> | EDGMENTS                                               | 14   |

| 5.           | REFERENC        | ES                                                     | 14   |

|              | APPENDICE       | ES .                                                   |      |

|              |                 | x A - NISTGAAS Cell Library Contents                   | 15   |

|              | A.1             | List of Test Structures                                |      |

|              | A.2             | Library Hierarchy                                      |      |

|              | A.3             | Process Layer Designators                              | 17   |

|              | A.4             | Cell Contents                                          | 17   |

|              | Appendi         | x B - NISTGAAS Test Structure Specification            |      |

|              | B.1             | Kelvin-Cross Interfacial Contact Resistor (Four-Pad)   |      |

|              | B.2             | Kelvin-Cross Interfacial Contact Resistor (Shared-Pad) |      |

|              | B.3             | Nanometer-Resolution Electrical Alignment Structure    |      |

|              | B.4             | Mesa/Channel van der Pauw Sheet Resistor               |      |

|              | B.5             | Step Coverage/Interconnect Meander                     |      |

|              | B.6             | Interconnect Resistor                                  |      |

|              | B.7             | Cross-Bridge Resistor                                  |      |

|              | B.8             | MIMIC-Standard 200 µm FET                              |      |

|              | Appenai         | c C - NISTGAAS Test Structure Sideviews                | /9   |

#### LIST OF FIGURES

|              |                                                                  | Page        |

|--------------|------------------------------------------------------------------|-------------|

| Figure 1.    | Selecting Test Structures and Test Vehicles                      | 7           |

| Figure 2.    | Fabrication Process Steps                                        | 11          |

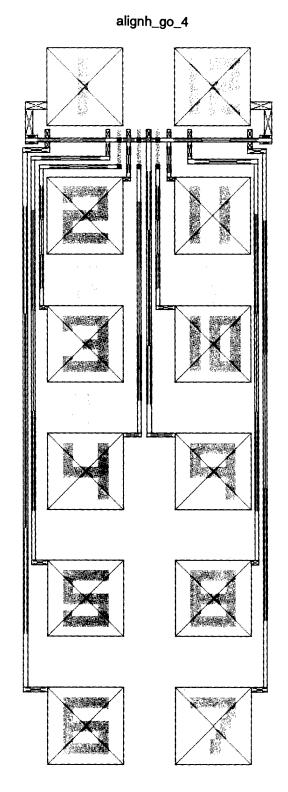

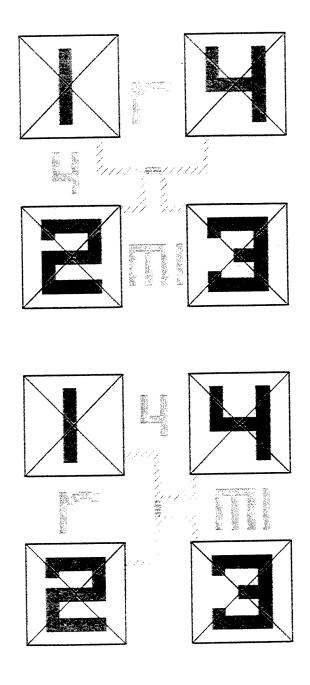

| Figure A-1.  | NISTGAAS Top-Level CAD Drawing                                   | 20          |

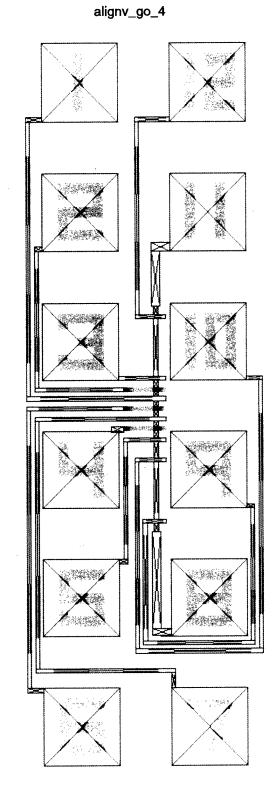

| Figure A-2.  | NISTGAAS 2nd-Level CAD Drawing                                   | 21          |

| Figure C-1.  | Sideview: Kelvin-Cross Interfacial Contact Resistor (Four-Pad)   | 81          |

| Figure C-2.  | Sideview: Kelvin-Cross Interfacial Contact Resistor (Shared-Pad) | 82          |

| Figure C-3.  | Sideview: Nanometer-Resolution Alignment Structure               | 83          |

| Figure C-4.  | Sideview: Mesa/Channel van der Pauw Sheet Resistor               | 84          |

| Figure C-5.  | Sideview: Step Coverage/Interconnect Meander                     | 85          |

| Figure C-6.  | Sideview: Interconnect Resistor                                  |             |

| Figure C-7.  | Sideview: Cross-Bridge Resistor                                  |             |

| Figure C-8.  | Sideview: MIMIC-Standard 200 μm FET                              | 88          |

|              | LIST OF TABLES                                                   | Page        |

|              |                                                                  | O .         |

| Table 1.     | NISTGAAS Cell Types and Their Application                        | 3           |

| Table 2.     | NISTGAAS Design Rules                                            | 10          |

| Table A-1.   | NISTGAAS Test Structures and CAD File Locations (Page 1 of 2)    | 18          |

| Table A-2.   | Mapping of Color/Pattern to Process Layer                        | 22          |

|              | LIST OF SCHEMATICS                                               | Page        |

|              |                                                                  | · ·         |

| Figure B-1.  | Kelvin-Cross Interfacial Contact Resistor (Four-Pad)             | 29          |

| Figure B-2.  | Kelvin-Cross Interfacial Contact Resistor (Shared-Pad)           | 34          |

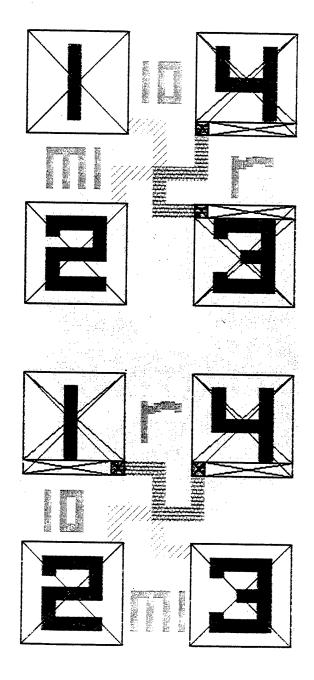

| Figure B-3.  | Nanometer-Resolution Electrical Alignment Structure (Horizontal) | 43          |

| Figure B-4.  | Nanometer-Resolution Electrical Alignment Structure (Vertical)   | 44          |

| Figure B-5.  | Mesa/Channel van der Pauw Sheet Resistor                         |             |

| Figure B-6.  | Step Coverage/Interconnect Meander                               | 58          |

| Figure B-7.  | Interconnect Resistor                                            | 62          |

| Figure B-8.  | Cross-Bridge Resistor                                            | 66          |

| Figure B-9.  | MIMIC-Standard 200 μm FET (Horizontal)                           |             |

| Figure B-10. | MIMIC-Standard 200 µm FET (Vertical)                             | <b>.7</b> 3 |

Semiconductor Measurement Technology:

Test Structure Implementation Document: DC Parametric Test Structures and Test Methods for Monolithic Microwave Integrated Circuits (MMICs)

C. E. Schuster

Semiconductor Electronics Division National Institute of Standards and Technology Gaithersburg, MD 20899

#### **ABSTRACT**

This document describes a set of microelectronic test structure designs for manufacturers of GaAs MMIC devices. These designs enable the dc measurement of process and device parameters that can be used to diagnose, monitor, compare, and predict the performance of the fabrication process or the devices produced. The test structure designs are embodied in a computer-aided design library known as NISTGAAS, which contains 8 types of test structures, implemented in 125 combinations of process layer and size, and based on a 2 x 6 probe-pad array. Any design, once fabricated on a wafer, can be probed using commonly available commercial parametric test system equipment. This document specifies how to implement and test each type of test structure and how to analyze the results. It also provides guidance on how to apply the set of test structures at the wafer level. Although NISTGAAS was designed for the process described in this document, it was also designed and demonstrated to be adaptable for other MMIC processes. Since NISTGAAS contains cell designs rather than a chip design, it provides a flexible test structure methodology that also provides the MMIC community with a common reference point for assessing process and device performance.

**Key Words:** CAD cell library; GaAs; integrated circuit; MMIC; parametric test method; process control; test structure

#### **DISCLAIMERS**

Certain commercial and public-domain products are identified to specify the procedures described in this document. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the products identified are necessarily the best available for the purpose.

The NISTGAAS cell library was produced by the National Institute of Standards and Technology, an agency of the U.S. Government, and by statute is not subject to copyright in the United States. Recipients of this software assume all responsibility associated with its operation, modification, maintenance, and subsequent re-distribution.

#### **EXECUTIVE SUMMARY**

The NISTGAAS computer-aided design (CAD) cell library was initially developed as part of the Defense Advanced Research Projects Agency (DARPA)/Tri-Service effort known as the Microwave/Millimeter Wave Monolithic Integrated Circuits (MIMIC) Program. The NISTGAAS library includes designs developed by NIST and the U.S. Air Force, Wright Laboratory (WL). The NISTGAAS development and validation were funded in part by WL MIPR Nos. FY1123-90-N9514, FY1175-91-N9518, FY1123-92-N9520, and FY1175-93-N9519.

Under the MIMIC Program, DARPA sponsored contracts for processes, products, and services to develop high-performance, affordable, and available microwave and millimeter-wave technology for manufacturing electronic systems. One aspect of this program was the Materials/Devices Correlation task (MIMIC Phase 1, Task 4.E), to investigate and quantify GaAs process performance through the use of test structures.

Six contractor foundries participated in Task 4.E, using test structures provided by WL. A common test chip, replicated about 200 times on each 3-inch wafer, was used by each contractor to produce high-density test structure data for 6 lots of 4 wafers each. Test structure data from the contractors and WL were analyzed by WL, with NIST assistance. Most test structures performed adequately for most process lots and lines. Some observations about performance variations provided guidance for improved test structure designs, test procedures, and test procedure specifications [1].

A second-generation wafer-level test vehicle, known as the High-Density Test Reticle (HDTR), was designed (partly) to investigate new test structure designs intended to improve and extend the performance of particular Task 4.E test structures and of the general test structure methodology. The HDTR test structures were designed by WL and NIST, fabricated by WL, and tested by WL and NIST [2, 3]. The HDTR test structures and other NIST test structure designs are contained in the NISTGAAS library, which includes the eight test structure types shown in Table 1. These types are implemented in 125 layer and size combinations, where each combination is a cell in the NISTGAAS library.

The NISTGAAS library and this implementation document provide the GaAs-based microwave community with a readily available, thoroughly documented, and flexible implementation method to use as a common reference point for assessing process and device performance.

Table 1. NISTGAAS Cell Types and Their Application

| TEST STRUCTURE TYPES                                      | APPLICATION                                                                                                                        |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Kelvin-Cross Interfacial<br>Contact Resistor (Four-Pad)   | Determine interfacial contact resistances to assess quality of a contact type                                                      |

| Kelvin-Cross Interfacial<br>Contact Resistor (Shared-Pad) | Determine interfacial contact resistances to assess quality of a contact type                                                      |

| Nanometer-Resolution<br>Electrical Alignment Structure    | Determine placement of a feature relative to<br>two reference features to assess the<br>performance of lithography processes/tools |

| Mesa/Channel van der Pauw<br>Sheet Resistor               | Determine sheet resistance of mesa and channel, thickness of channel to assess potential FET performance                           |

| Step Coverage/Interconnect<br>Meander                     | Determine current continuity to assess step coverage for two conducting layers                                                     |

| Interconnect Resistor                                     | Determine load resistance of a contact type to provide circuit design parameter                                                    |

| Cross-Bridge Resistor                                     | Determine sheet resistance and linewidth to assess the quality of a conducting layer                                               |

| MIMIC-Standard 200 μm FET                                 | Determine dc FET parameters to assess FET performance                                                                              |

#### 1. INTRODUCTION

#### 1.1. Purpose

This document describes how to implement the test structures included in the NISTGAAS cell library. It specifies each test structure design, how to test it, and how to analyze the results. It also addresses how to apply the set of NISTGAAS test structures at the wafer level.

#### 1.2. Scope

#### 1.2.1. NISTGAAS Form and Function

The NISTGAAS cell library contains dc parametric test structures designed for a MMIC process that has design rules typical for fabricating 1  $\mu$ m, low-noise, depletion-mode devices. The library can be used with other MMIC processes, as it is designed so the test structures can be easily customized for processes with similar but different design rules and mask layers. The CAD software used to create NISTGAAS is the (public-domain) Magic graphic layout editor [4], so the mask-level layout information for the test structure designs is transferable in either Caltech Intermediate Form (CIF) or Calma Stream format. Each test structure design can be tested using a dc parametric test system with a probe card that can access a 2 x 6 probe-pad array, where the probe pads are 75  $\mu$ m x 75  $\mu$ m each and have a 125  $\mu$ m pitch.

Since the NISTGAAS library provides individual test structure designs (cells), rather than a test chip, only the designs useful for a particular application need be implemented. This enables the user to develop a flexible monitoring capability without sacrificing area (to non-applicable parts of a test chip), when such area might be better used for product or for design development.

#### 1.2.2. Documentation

Each test structure type is specified in terms of its purpose, application, design variations, CAD, layout constraints, measurement method, computation and interpretation of results, and historical references. These specifications are found in Appendix B, while the remaining document provides information needed to understand and effectively use Appendix B.

This document is organized to provide adequate information for various types of users but to minimize the effort each needs to find details of interest or reproduce working-level aids.

Potential users include program managers, process engineers, CAD personnel, tester code developers, and data analysts. Generally applicable background information is in section 2 (general perspective on test structure implementation) and in section 3 (specific rationale, assumptions, and conventions used in designing the NISTGAAS cell library). Appendix A (library configuration) will be the most useful to CAD personnel. Appendix B (the test structure specifications) is intended mainly for coders and analysts, but can also be useful to program managers and process engineers in assessing the process-related aspects of test structure design and implementation. Process engineers may also find Appendix C (process sideviews) a useful extension to the Appendix B checkplots.

#### 2. IMPLEMENTATION CONSIDERATIONS

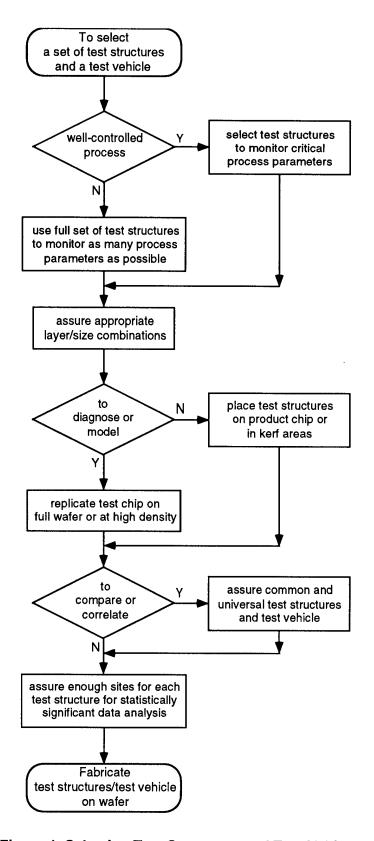

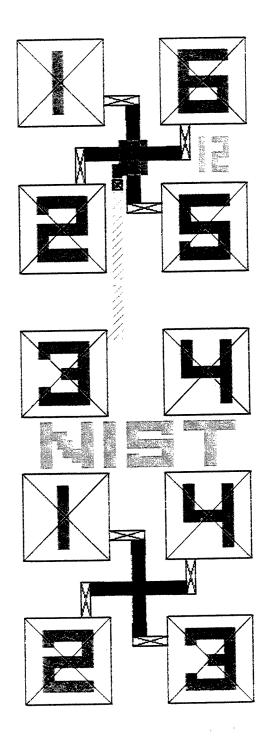

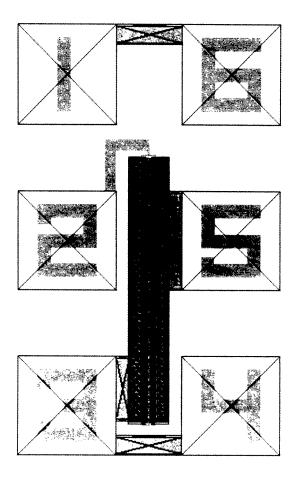

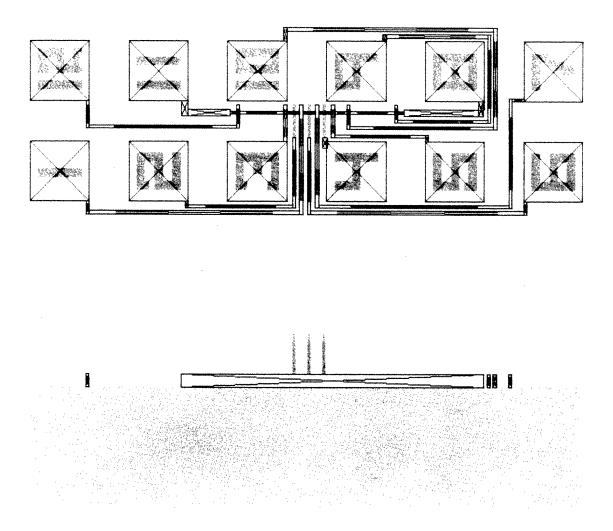

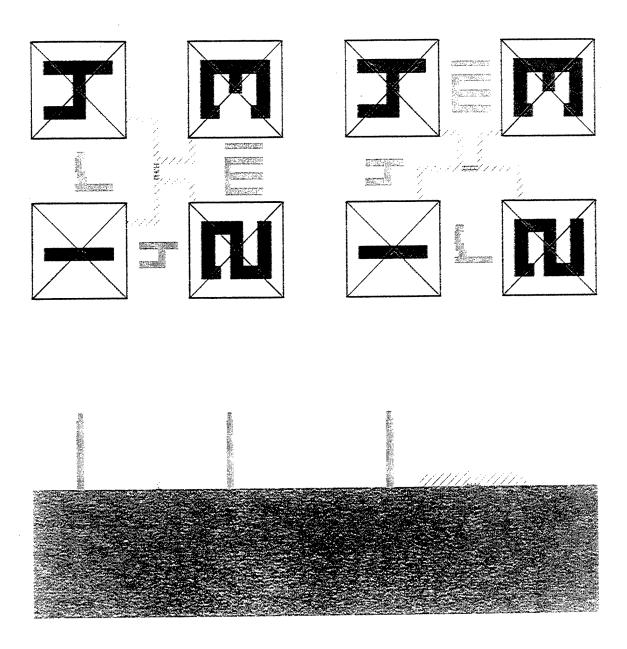

To gain the maximum benefit from using test structures, users need to be conscientious not only in applying the specifications in Appendix B, but also in several other areas: selecting test structures, developing an appropriate test vehicle, assuring the testing environment, and developing data analysis capabilities. These areas are discussed in detail elsewhere [5] and here within the context of MMIC manufacturing environments and the NISTGAAS cell library. The sections on selecting test structures and test vehicles are summarized in figure 1.

#### 2.1. Selecting Test Structures

As the first step in the test structure implementation process, the user should determine why test structures are needed – both broadly and specifically. In doing this, the expertise of process and design engineers is valuable. The reasons for using test structures affect the data needed and the test structures and test vehicle design to be used. The major consideration involves whether the test structures will be used to monitor a well-controlled production environment, to diagnose a new process, to develop process models, or to provide data for comparison to data from other process lines.

In a well-controlled process, the physics and the yield goals of the process and products are understood, so the critical parameters needed to monitor the process are well known and limited. In the other process environments and applications, many more parameters may be needed to develop correlations between process parameters or between process parameters and device parameters or to compare the capabilities of different process lines. These considerations affect not only which test structure types are needed, but also what layer/size combinations are needed.

In comparing data from different process lines, a common set of test structures, appropriate for all processes, is needed. If one of the common test structures has not previously been used on a process line, a line-specific test structure providing similar parameters should be retained to correlate process conditions based on previous history.

The layer/size combinations selected should be those actually used in the device or process step for which the test structure parameter is needed. If devices require features larger than the minimum size, designs with the same size features should be included. For example, to assess a FET with a 10  $\mu m$  channel width, the mesa/channel van der Pauw is implemented with a 10  $\mu m$  vs 4  $\mu m$  linewidth. In determining a load resistance for the source or drain of a FET, a corresponding-size, ohmic-to-mesa interconnect resistor is used.

Further, particular process sensitivities may affect the choice of the NISTGAAS cell to be used. For example, if ohmic sheet resistance is adequately controlled but does vary, test structures with ohmic runs long enough to be susceptible to such variations should not be used. For the alignment structure, such a sensitivity could be minimized by using the OG vs GO cell.

Another consideration in selecting test structures involves how a mask set will be developed and used. By including designs with linewidths smaller than the process currently supports,

Figure 1. Selecting Test Structures and Test Vehicles.

the design limits of the process may be assessed and a new mask set is not needed for the next generation of the process. Such decisions are a trade-off with other factors such as test vehicle size and the cost, time, and needs associated with a new mask set.

#### 2.2. Developing a Test Vehicle

Once the necessary test structure types and layer/size combinations are identified, the test vehicle implementation and layout can be developed. As in choosing test structures, a major consideration in test vehicle design is its application, e.g., to monitor, diagnose, model, or compare. Again, process and product design expertise is needed.

For process diagnosis and modeling, a full-wafer or other high-density test vehicle is needed to provide robust statistics for correlation and wafer-mapping analyses. Frequently, all of the test structures are included on a test chip that is replicated on an entire wafer or at a high density and uniformly distributed with product-related chips on a wafer. For monitoring a well-controlled and well-characterized process, reduced implementations that fit on the product chip or wafer or in the kerf area are usually adequate. Possible implementations are usually strip-like and known by such terms as test strip, coupon, pellet, or plug-bar.

Regardless of the test vehicle type, several layout factors are important. Most important is that the test structures should be located near the MMIC they are to characterize. Thus, a test chip implementation should either contain on-chip MMIC devices or have the salient test structures near the edge of the test chip that will be adjacent to the edge of a product chip with a near-by device. Similarly, test strips should have their test structures arranged to be near the related device. For example, if gate-to-ohmic alignment is critical for a FET, the gate-to-ohmic alignment structure should be located near a sample of the FET.

Another layout consideration is whether correlation between the test structure parameters is needed. The user must then decide which test structures need to be placed near each other and assure that their relation to near-by device needs are maintained.

Each test structure design should be replicated at sites that are uniformly distributed on the wafer. This provides some indication of parameter uniformity, the sites needed to perform the preliminary validation procedures included in some of the test structure specifications, and the sites needed to demonstrate data reproducibility. Although five sites are often used, this is about half the sites usually needed to provide a robust statistical basis for data analysis [6].

If comparisons between process lines are needed, a standard test vehicle with moderate to high density is usually needed. In addition to the above factors, this test vehicle must be designed to be accommodated by all the process lines. Process lines should consider retaining previously used process-specific test vehicles to correlate new parameters to previous history.

If adequate space is not available for the initially identified set of test structure designs, the set must be prioritized according to which designs provided the most useful information. This exercise should consider not only test structure type but also layer and size choices. For example, in assessing the quality of the different contacts in the process, having 3 vs 5 linewidths for all types of contacts may be preferable to having 5 linewidths for fewer types.

#### 2.3. Assuring the Testing Environment

Before collecting data that will be analyzed for significant purposes, the hardware and software in the testing environment must be thoroughly validated. Instruments should be calibrated, the switching matrix and probe card connections verified, and other tester diagnostics performed. Software function and correct data logging should be demonstrated using known artifacts or benchmarks. This should verify that correct currents or voltages are forced or measured and that sufficient settling times are allowed to produce realistic results that are accurately stored in the intended locations in a database.

These activities are simply good engineering practice. Other assurances that relate more to specific measurement procedures for MMIC environments and NISTGAAS test structures are discussed in the introductory notes in Appendix B.

#### 2.4. Developing Data Analysis Capabilities

Automated techniques with analyst-friendly interfaces should be developed to assure consistency in analyzing test structure data of more than minimal volume. The first step of such automation should include an algorithm to assure that measurements are reproducible. If the measurements are not reproducible, the cause needs to be determined, the problem resolved, and the measurements repeated. If measurements are reproducible, the next step should include a robust outlier exclusion algorithm, such as in reference [7], to remove data points that will skew further statistical analysis. Once reproducibility is demonstrated and outliers are excluded, the integrity of the data is sufficient to support further analysis. Some mechanism should also exist so that analysts can easily distinguish the original data from data that have successfully completed these evaluations.

#### 3. COMPUTER-AIDED DESIGN (CAD) CELL LIBRARY

#### 3.1. Overview

The NISTGAAS cell library was designed using the Magic CAD layout editor (version 6.3 on a Sun SPARCsystem 300 with SunOS 4.1.2 and Open Windows 2.0). The library layout and its associated technology file are designed in a hierarchical manner. The test structures are designed with constraints intended to assure portability and immunity to yield-limiting defects. These features enable the library to be customized easily for different mask layers and design rules. Because the library is hierarchical by test structure type and a cell naming convention is used, test structure designs are easily located and the framework for adding customized designs is available and obvious.

For most test structure types, a number of design variations are provided. The variations for a given test structure type result from different combinations of process layers and dimensions, producing a set of unique designs for that test structure type. Each design variation is a "cell" in the NISTGAAS library and is stored as a separate file within the library file hierarchy.

All the design variations for each test structure type are listed in Appendix A and are referenced in the specification for each test structure type in Appendix B. Although each specification shows the drawing for only one of the available cells, all cells referenced in the specification are found in the electronic version of NISTGAAS. To understand the NISTGAAS cell designs, some background process- and library-related information is needed.

#### 3.2. Process Layers

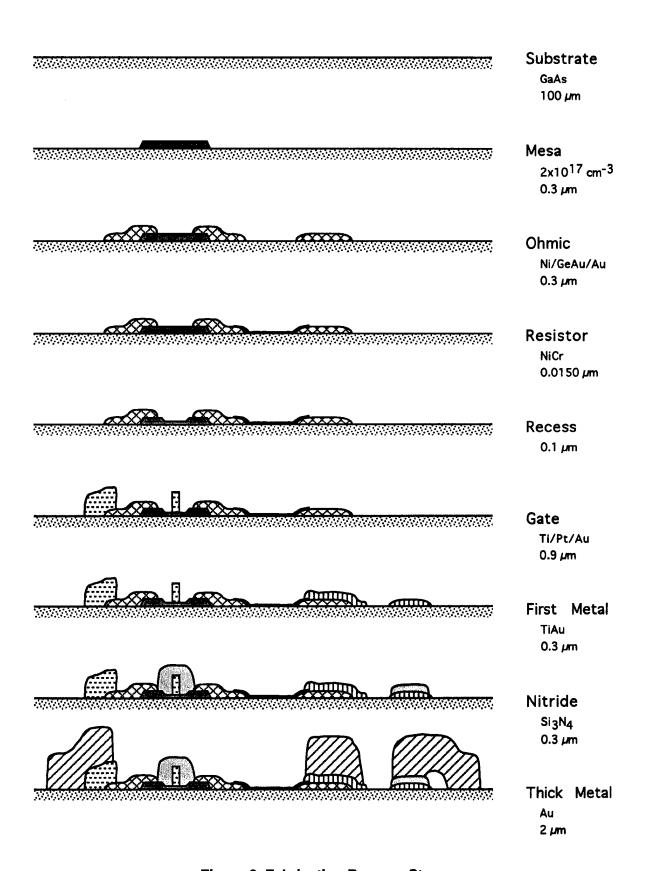

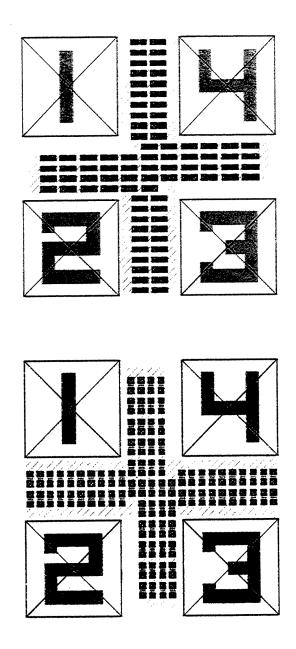

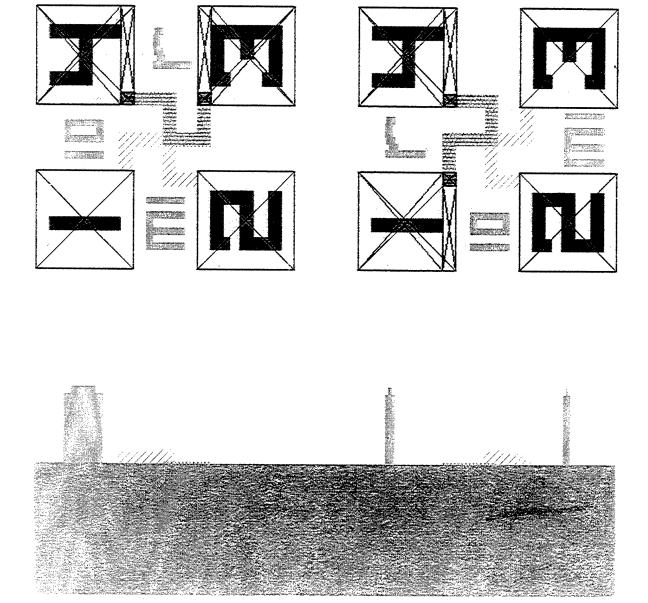

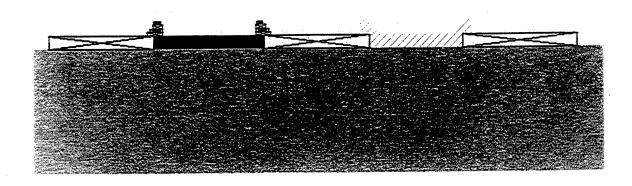

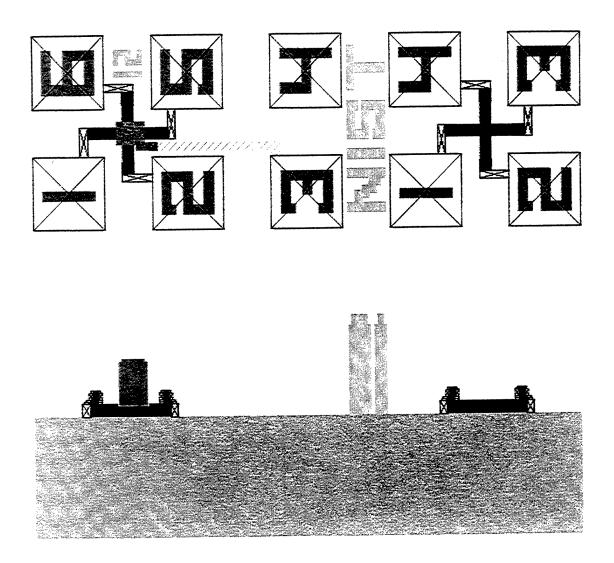

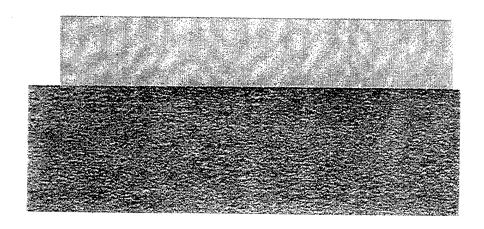

The NISTGAAS technology file represents a common Metal-Semiconductor Field Effect Transistor (MESFET) process, where the design rules and processing steps support a planar process fabricating 1  $\mu$ m, low-noise, depletion-mode devices. The design rules are summarized in table 2, and the processing steps are summarized in figure 2.

Table 2. NISTGAAS Design Rules

|                       | М | 0 | R | G | M1 | DI | AIR | T |

|-----------------------|---|---|---|---|----|----|-----|---|

| Minimum<br>width (μm) | 4 | 4 | 4 | 1 | 1  | 4  | 4   | 4 |

| Minimum<br>space (μm) | 5 | 4 | 4 | 2 | 2  | 4  | 4   | 4 |

#### where:

M = mesa

$\mathbf{O}$  = ohmic

R = resistor

G = gate

M1 = first metal

**DI** = dielectric (nitride)

**AIR** = air bridge

**T** = thick metal

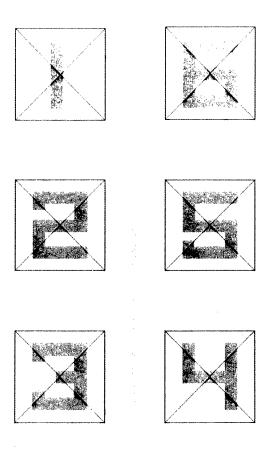

#### 3.3. Plot Colors and Patterns

Each process layer or construct in a cell is represented as a color, in the electronic format of NISTGAAS, and as a black and white pattern in the drawings in Appendix B. In the electronic version, a legend shows each layer name and the associated color. When the NISTGAAS cells are viewed on a Sun system or in black and white, the colors and patterns equate to the process layers and constructs as indicated in Appendix A.

#### 3.4. Cell Naming Conventions

Cell names consist of two or three fields concatenated with the character "\_" between each. The three fields include test structure name, layer name, and dimension. A description of each field follows, along with its valid entries.

Figure 2. Fabrication Process Steps.

#### 3.4.1. Test Structure Names

The test structure name field is an abbreviation of the full test structure name:

- 1. CONRES Kelvin-Cross Interfacial Contact Resistor (Four-Pad)

- 2. CONRESSH Kelvin-Cross Interfacial Contact Resistor (Shared-Pad)

- 3. ALIGNH and ALIGNV Nanometer-Resolution Electrical Alignment Structure; names denote different designs for horizontal and vertical orientations

- 4. VPAUW Mesa/Channel van der Pauw Sheet Resistor

- 5. MEANDER Step Coverage/Interconnect Meander

- 6. INTRES Interconnect Resistor

- 7. CROSSBR Cross-Bridge Resistor

- 8. RFFETH and RFFETV MIMIC-Standard 200 μm FET; names denote different horizontal and vertical designs based on the Task 4.E MESFET designs with the same names.

#### 3.4.2. Layer Names

The layer name field identifies the process layer(s) in the test structure design. In most cases, a layer is indicated by its first letter, and multi-character layer names indicate two layers, with the upper layer occurring first in the layer name. The exceptions are: M1; AIR; and names noted as "in CONRESSH," where the name indicates which layer in the two sets of layers in the test structure is shared at pads used by both designs. The NISTGAAS layer names are:

- 1. M mesa

- 2. O ohmic; in CONRESSH: layer shared by OM and M1O designs

- 3. R resistor; in CONRESSH: layer shared by RO and M1R designs

- 4. G gate

- 5. M1 first metal; in CONRESSH: layer shared by M1G and TM1 designs

- 6. T thick metal; in CONRESSH: layer shared by TO and TG designs

- 7. AIR air bridge (thick metal-dielectric-first metal)

- 8. OM ohmic-to-mesa

- 9. RO resistor-to-ohmic

- 10. GO gate-to-ohmic

- 11. M1O first metal-to-ohmic

- 12. TO thick metal-to-ohmic

- 13. M1R first metal-to-resistor

- M1G first metal-to-gate

- 15. TG thick metal-gate

- 16. TM1 thick metal-to-first metal

#### 3.4.3. Dimensions

These represent dimensions in the test structure design, in micrometers: the width of a square contact or a bridge, or the dimensions of a FET gate. The NISTGAAS dimensions include:

- 1. 1

- 2. 2

- 3. 3

- 4. 4

- 5. 6

- 6. 8

- 7. 10

- 8. 12

- 9. 1x200

Thus, some typical cell names are VPAUW\_M\_4, CONRES\_M1R\_12, MEANDER\_AIR, and RFFETH\_1x200. For a complete list of the cell names for all of the NISTGAAS designs, see Appendix A.

#### 3.5. CAD Drawing Hierarchy

The NISTGAAS cell library is hierarchical, with like cells grouped together. The library configuration is shown in Appendix A, which also describes how to navigate through the hierarchy to any test structure design.

#### 3.6. Obtaining the NISTGAAS Cell Library

To obtain the NISTGAAS cell library and its associated technology file, or for more information, please contact:

C. E. Schuster NIST Bldg 225/Rm B360 Gaithersburg, MD USA 20899-0001

Phone: 1-301-975-2241

e-mail: schuster@sed.eeel.nist.gov

#### 4. ACKNOWLEDGMENTS

The efforts of these individuals are notable in developing the NISTGAAS cell library and are appreciated: P. Roitman for guidance on designing the CAD library; R. A. Allen, for guidance on designing and testing the electrical alignment test structure; J. C. Marshall for developing the Magic technology file; C. H. Ellenwood for digitizing and managing the CAD library; and L. W. Linholm for many helpful comments. The NIST team also thanks WL personnel for their contributions: M. Mah for providing process information; D. Via for digitizing the MIMIC-Standard 200  $\mu$ m FET; J. K. Gillespie and S. E. Cummins for providing test information for the MIMIC-Standard 200  $\mu$ m FET, as well as many other helpful technical discussions; and, especially, R. T. Kemerley for encouraging and supporting the concept of a CAD cell library for MMIC test structures.

#### 5. REFERENCES

- [1] Schuster, C. E., Linholm, L. W., and Gillespie, J. K., High-Density Test Structures for Assessing Microwave/Millimeter Wave Monolithic Integrated Circuit (MIMIC) Performance, Digest of Papers, 1991 Government Microcircuit Applications Conference, Orlando, FL, November 5-7, 1991, Vol. XVII, pp. 335-338 (1991).

- [2] Gillespie, J., Bozada, C., Kehias, L., Quach, T., Mah, M., Worley, R., Cummins, S., and Eppers, C., High Density Test Reticle, U.S. Air Force Wright Laboratory Interim Report WL-TR-93-5011 (February 1993).

- [3] Schuster, C. E., and Linholm, L. W., Semiconductor Measurement Technology: Test Structure Assessment Document: DC Parametric Test Structures and Test Methods for Monolithic Microwave Integrated Circuits (MMICs), NIST Special Publication (to be published).

- [4] Mayo, R. N., Arnold, M. H., Scott, W. S., Stark, D., and Hamachi, G., 1990 DECWRL/Livermore Magic Release, Regents of the University of California, Lawrence Livermore National Labs, Stanford University, and Digital Equipment Corp. (September 1990).

- [5] Kopanski, J. J., and Schuster, C. E., Review of Semiconductor Microelectronic Test Structures with Applications to Infrared Detector Materials and Processes, *Semicond. Sci. Technol.* **8**, 892-894 (July 1993).

- [6] Suehle, J. S., Linholm, L. W., and Kafadar, K., A Method for Selecting a Minimum Test Chip Sample Size to Characterize Microelectronic Process Parameters, Proc. 1983 Custom Integrated Circuits Conf., Rochester, NY, May 23-25, 1983, pp. 308-312 (1983).

- [7] Rosner, B., Percentage Points for a Generalized ESD Many-Outlier Procedure, *Technometrics* **25** (2), 165-172 (1983).

Appendix A - NISTGAAS Cell Library Contents

#### **Appendix A - NISTGAAS Cell Library Contents**

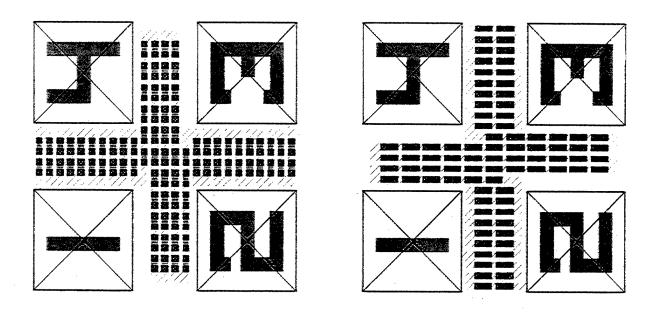

This section describes how to navigate through the CAD drawing hierarchy to a particular test structure design and how to understand the checkplots found in Appendix B. In the following text, references to process layers or constructs are made in terms of color and pattern. The colors pertain to what is seen when viewing the CIF format of NISTGAAS, while the patterns (in black and white) pertain to the Appendix B checkplots.

#### A.1 List of Test Structures

For each test structure type, a number of design variations related to process layers and size are included. Table A-1 shows the available design variations and associated cell names. The cell name is a concatenation of the test structure type, process layer, and size. In the cell name, the notation "{2,3,4,6,8,10,12}" indicates that seven separate cells actually exist, with the last character of their names being "2", "3", ... "12", respectively. The information in the Layout Label column relates to the library cell hierarchy as follows.

#### A.2 Library Hierarchy

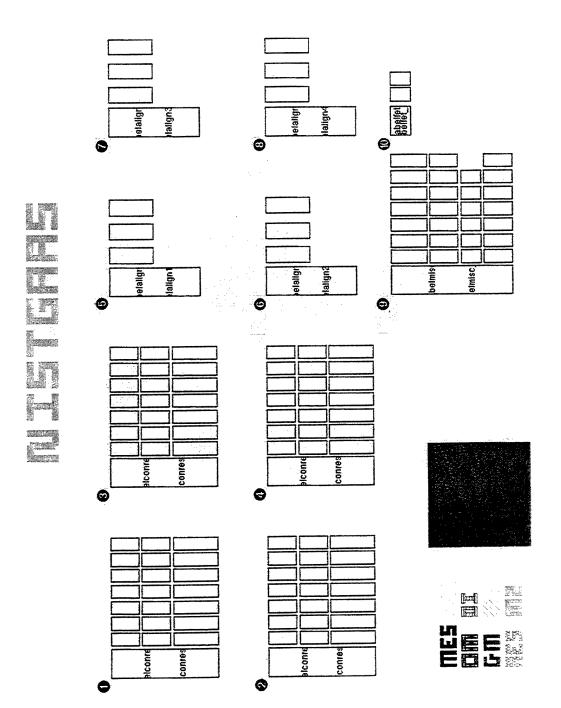

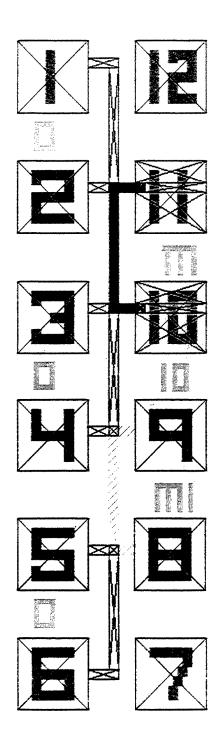

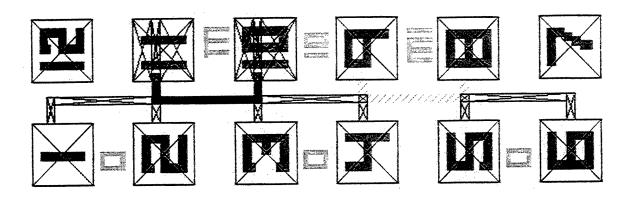

When the NISTGAAS file is viewed, the top-level drawing, shown in figure A-1, has blocks whose labels show only partially. The numbers to the left of each set of blocks are keyed to table A-1, to indicate the content of the layout label blocks at the next lower level of the drawing hierarchy. When a block at the lower level is viewed, as shown in figure A-2, the layout label in table A-1 is clearly seen in the large full-length block on the left. Each block to the right contains one test structure design variation (i.e., one cell), whose cell name corresponds to an entry in table A-1.

#### A.3 Process Layer Designators

Upon viewing a cell, a checkplot of the test structure design is seen. Checkplots for each test structure type are included in the specifications in Appendix B. The meaning of the colors and patterns is defined in the top-level drawing (figure A-1), in the legend found in the lower left corner, where the process layer names are partially spelled out in their corresponding color or pattern. For convenience when viewing a design on the screen and in Appendix B, the mapping of process layer to color and pattern is shown in table A-2. As an aid in identifying the design when the fabricated test structure is viewed under a microscope or on a CAD monitor, most designs include a layer designator, formed in thick metal and placed adjacent to a run of the layer.

#### A.4 Cell Contents

Most cells include two independent sets of probe pads to accommodate either a horizontal-vertical or a  $0^{\circ}$ - $90^{\circ}$  combination of orientation variations. The convention used is: the upper set of pads is the horizontal or  $0^{\circ}$  orientation and the lower set of pads is the vertical or  $90^{\circ}$  orientation. Both sets of pads can be probed with one touchdown of a  $2 \times 6$  probe card.

Table A-1. NISTGAAS Test Structures and CAD File Locations (Page 1 of 2)

| TEST STRUCTURE           | PROCESS LAYER              | CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CAD File Location             |

|--------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| TYPE                     | COMBINATION                | Layout Label                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cell Name                     |

| Kelvin-Cross Interfacial | ohmic-to-mesa              | • labelconres1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | conres_om_{2,3,4,6,8,10,12}   |

| Contact Resistor         | first metal-to-ohmic       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conres_m1o_{2,3,4,6,8,10,12}  |

| (Four-Pad → conres,      |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conressh_o_{2,3,4,6,8,10,12}  |

| Shared-Pad → conressh)   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

|                          | resistor-to-ohmic          | Q labelconres2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | conres_ro_{2,3,4,6,8,10,12}   |

|                          | first metal-to-resistor    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conres_m1r_{2,3,4,6,8,10,12}  |

|                          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conressh_r_{2,3,4,6,8,10,12}  |

|                          | first metal-to-gate        | 8 labelconres3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | conres_m1g_{2,3,4,6,8,10,12}  |

|                          | thick metal-to-first metal |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conres_tm1_{2,3,4,6,8,10,12}  |

|                          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conressh_m1_{2,3,4,6,8,10,12} |

|                          | thick metal-to-gate        | 4 labelconres4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | conres_tg_{2,3,4,6,8,10,12}   |

|                          | thick metal-to-ohmic       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conres_to_{2,3,4,6,8,10,12}   |

|                          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | conressh_t_{2,3,4,6,8,10,12}  |