# AFIT/GCS/ENG/87D-10

# A DIGITAL LOGIC SIMULATOR WITH

CONCURRENT PROGRAMMING CONSIDERATIONS

THESIS

Wayne C. DeLoria Captain, USA

AFIT/GCS/ENG/87D-10

Approved for public release; distribution unlimited

AFIT/GCS/ENG/87D-10

# A DIGITAL LOGIC SIMULATOR WITH CONCURRENT PROGRAMMING CONSIDERATIONS

### THESIS

Presented to the Faculty of the School of Engineering of the Air Force Institute of Technology,

Air University,

In Partial Fulfillment of the

Requirements for the Degree of

Master of Science in Computer Systems

| Acces               | sion For       |  |  |

|---------------------|----------------|--|--|

| NTIS                | GRA&I          |  |  |

| DTIC                | ГАВ 🚹          |  |  |

| Unann               | ounced 🗌       |  |  |

| Justi               | fication       |  |  |

| By<br>Distribution/ |                |  |  |

|                     |                |  |  |

| Avai                | lability Codes |  |  |

| •                   | Avail and/or   |  |  |

| Dist                | Special        |  |  |

| A-/                 |                |  |  |

Wayne C. DeLoria

Captain, USA

December 1987

Approved for public release; distribution unlimited

### Acknowledgments

Perhaps one of the greatest lessons learned from an intensive period of research and study, such as this thesis effort, is the realization that such undertakings can never come to fruition without the assistance and understanding of others. We all hope for self-sufficiency, but reality proves that we are all gregarious. Many colleagues and friends were helpful throughout this effort, but some really stand out as lifesavers.

Of course, I could not have accomplished any amount of success without the guidance and assistance of my advisor, CPT N.J. Davis. The other members of my advisory committee were equally important --CPT Bruce George, whose bright disposition kept us all going, and CPT Wade Shaw, whose inspiration was responsible for this whole thing. Dr. Frank Brown, who oversaw the original version of the simulator, also supplied some direction.

Various sections of this report would never have gone to press were it not for classmates and colleagues. CPT Edward Poore saved my life (and perhaps my sanity) with his undying patience and indispensable knowledge of statistics and their applications. LT Bill Hodges' intimate familiarity with the iPSC Hypercube saved uncounted hours in the pursuit of many

i i

elusive bugs which kept popping up in concurrent applications.

My two partners in the development of the integrated digital design tool (IDIET) were also instrumental in whatever success was realized by this project. Although they were working toward different goals, without the productive interaction with CPT Charles Adams and LT Steven Wagner, I might very well still be at the drawing board.

And last, but certainly not least, my most heartfelt thanks and love go out to my wife Sheryl, without whose support, and sometimes tearful understanding, this thesis would never have been completed.

i i i

# Table of Contents

| r a                                                                                                                                                                                       | iye                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Acknowledgments                                                                                                                                                                           | i i                              |

| List of #igures                                                                                                                                                                           | vi                               |

| List of Tables                                                                                                                                                                            | i i                              |

| Abstract                                                                                                                                                                                  | i x                              |

| CHAPTER 1 - THESIS OVERVIEW AND ORGANIZATION                                                                                                                                              | 1                                |

| <pre>1.1 Overview</pre>                                                                                                                                                                   | 1<br>3                           |

| CHAPTER 2 - INTRODUCTION AND OBJECTIVES                                                                                                                                                   | 5                                |

| <pre>2.1 Introduction</pre>                                                                                                                                                               | 5<br>1Ø<br>12                    |

| CHAPTER 3 - LOGSIM                                                                                                                                                                        | 13                               |

| 3.1 Background                                                                                                                                                                            | 13<br>17                         |

| 3.2.1 Overview                                                                                                                                                                            | 17<br>18<br>22                   |

| 3.3 Summary                                                                                                                                                                               | 24                               |

| CHAPTER 4 - SOFTWARE DEVELOPMENT                                                                                                                                                          | 25                               |

| 4.1 Re-engineering Overview<br>4.2 Analysis - LOGSIM, version 5.5<br>4.3 Design - LOGSIM248<br>4.4 Coding - LOGSIM248<br>4.5 IDIET Integration<br>4.6 Testing and Debugging - LOGSIM248 . | 25<br>25<br>31<br>35<br>39<br>40 |

| CHAPTER 5 - CONCURRENT LOGSIM                                                                                                                                                             | 43                               |

| 5.1 Overview                                                                                                                                                                              | 43<br>46<br>47<br>49             |

|              |                          |        |       |        |      |      |       |        | Page   |

|--------------|--------------------------|--------|-------|--------|------|------|-------|--------|--------|

| CHAPTER 6 -  | DISCUSSION               | • •    | • •   | • • •  | •••  | ••   | ••    | ••     | . 51   |

|              | 6.1 Compar               | ing Pe | erfor | mance  | - LO | GSIM | v5.   | 5      |        |

|              | vs. LO                   |        |       |        |      |      |       |        |        |

|              | 6.2 Concur               |        |       |        |      |      |       |        |        |

|              | 6.3 Using                | LOGSI  | 1248  | Indepe | nden | tly  |       | • •    | . 59   |

|              | 6.4 LOGSIM               |        |       |        |      |      |       |        |        |

|              | 6.5 Future               |        |       |        |      |      |       |        |        |

| Bibliography |                          |        | • •   | • • •  | • •  | • •  |       | ••     | . 66   |

| Appendix A:  | Source Cod               | e - L( | OGSIM | 248.   |      |      |       |        | . 68   |

|              |                          |        |       |        |      |      |       | •••    |        |

| Appendix B:  |                          |        |       |        |      |      |       |        |        |

|              | Decomposit               | ion.   | • •   | • • •  | ••   | • •  | • •   | ••     | . 130  |

| Appendix C:  | Statistica               | l Infe | ormat | ion .  | ••   | • •  | • •   | ••     | . 148  |

| Appendix D:  |                          |        |       |        |      |      |       |        |        |

|              | Graphic In               | terfa  | ce Im | ages   | ••   | • •  | ••    | •••    | . 162  |

| Appendix E:  | LOGSIM248                | Manua  | l for | Indep  | ende | nt   |       |        |        |

|              | Operation                |        |       |        |      |      | ••    | •••    | . 175  |

|              | E.l Overvi               | ew .   | • •   | • • •  | • •  |      |       | • •    | . E-1  |

|              | E.1 Overvi<br>E.2 What I | s LOG  | SIM24 | 8? .   |      |      |       |        | . E-2  |

|              | E.3 Materi               | als R  | eauir | ed.    |      |      |       |        | • E-3  |

|              | E.4 LOGSIM               | 248 F  | ile I | nterfa | Ce   | ••   | • •   | •••    | • E~5  |

|              |                          | E.4.1  | Circ  | uit Co | nfia | urat | ion   | Inni   | 1+     |

|              |                          |        | File  | - TEM  | P.CK | т.   |       |        | . E-6  |

|              |                          | E.4.2  |       | ut Spe |      |      |       | •••    | • • •  |

|              |                          |        |       | - TEM  |      |      |       |        | . E-9  |

|              |                          | E 4 R  |       | t Data |      |      |       |        |        |

|              |                          |        |       | t Port |      |      | LEFIE | • 1 (4 | • E-9  |

|              |                          |        |       | - TEM  |      |      |       |        | . E-10 |

|              |                          |        |       |        |      |      |       |        |        |

|              | E.5 Invoki               | ng The | e Sim | ulator | •    | • •  | • •   | • •    | . E-11 |

|              | E.6 Summar               |        |       |        |      |      |       |        |        |

|              | ANNEX A: L<br>ANNEX A. E |        |       |        |      |      |       | ••     | . E-13 |

|              |                          |        |       | • • •  |      |      |       | • •    | . E-15 |

| Vita         | • • • • •                |        | • •   | • • •  | • •  | • •  |       | • •    | . 193  |

×

# List of Figures

1.2.2.2.2.2.

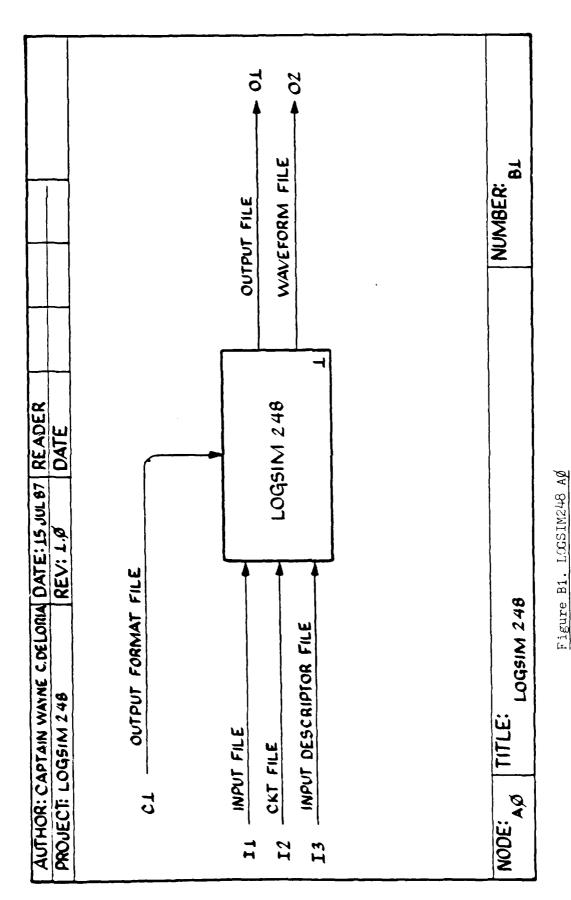

| Bl.  | LOGSIM248 A0                                    | Page<br>B-1 |

|------|-------------------------------------------------|-------------|

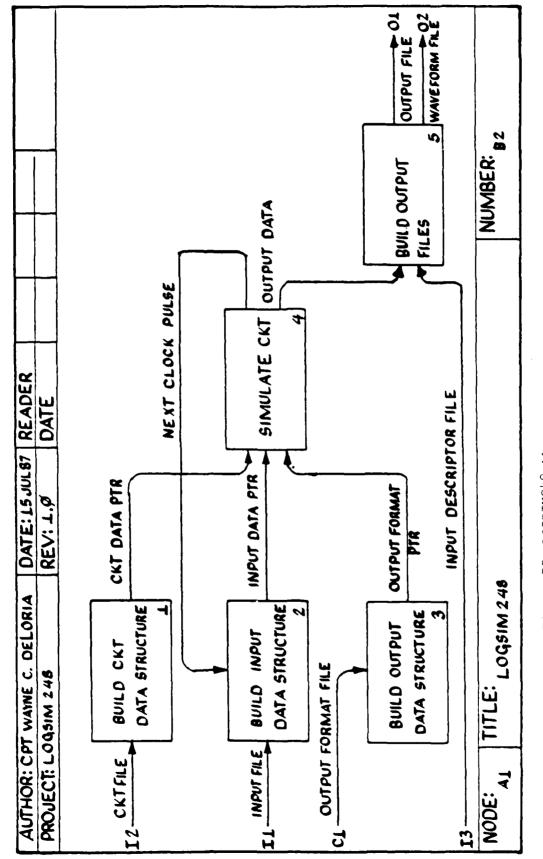

| в2.  | LOGSIM248 Al                                    | B-2         |

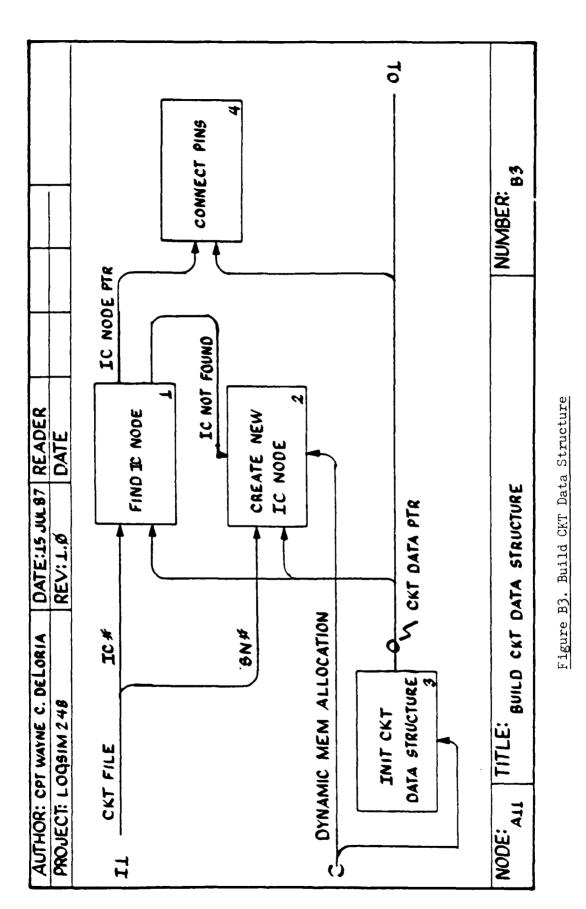

| вз.  | Build Ckt Data Structure                        | B-3         |

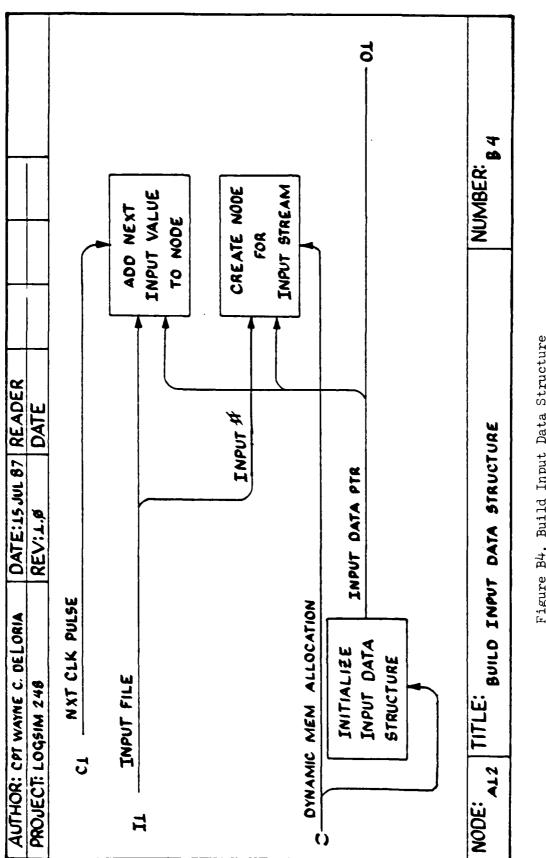

| в4.  | Build Input Data Structure                      | B-4         |

| в5.  | Build Output Data Structure                     | B-5         |

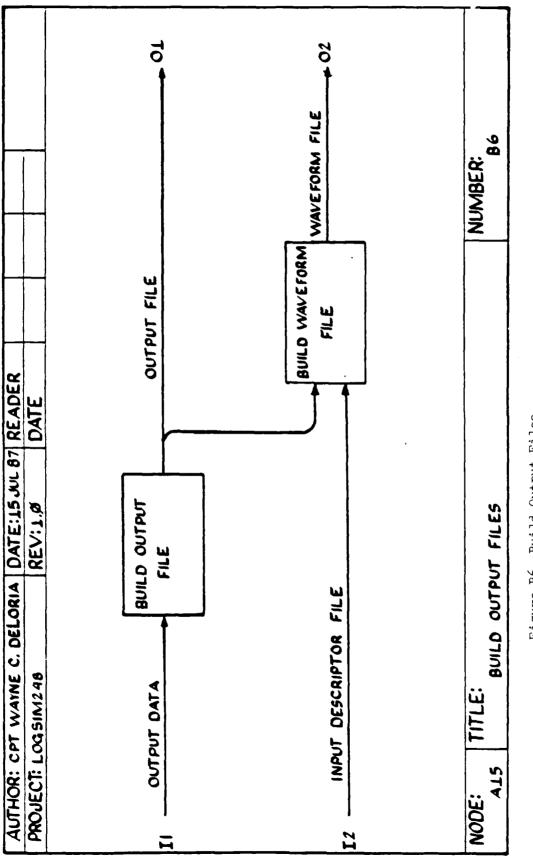

| B6.  | Build Output Files                              | B-6         |

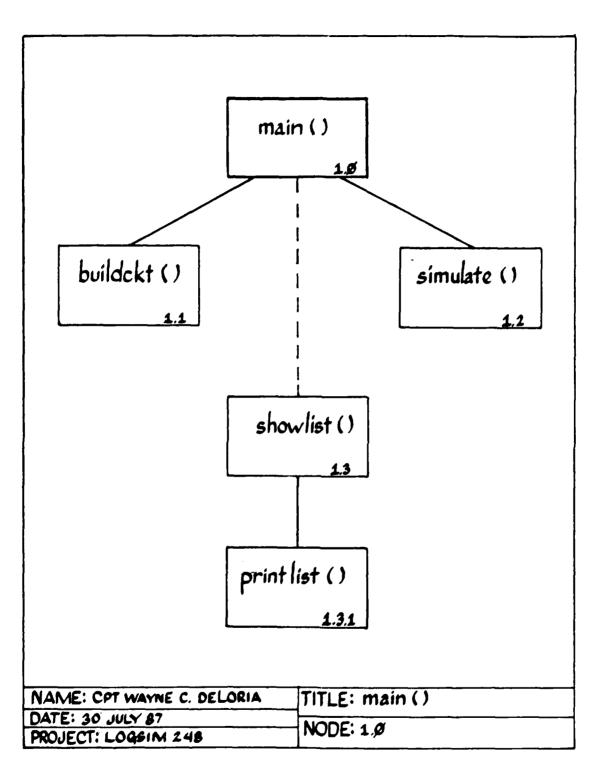

| в7.  | main()                                          | B-7         |

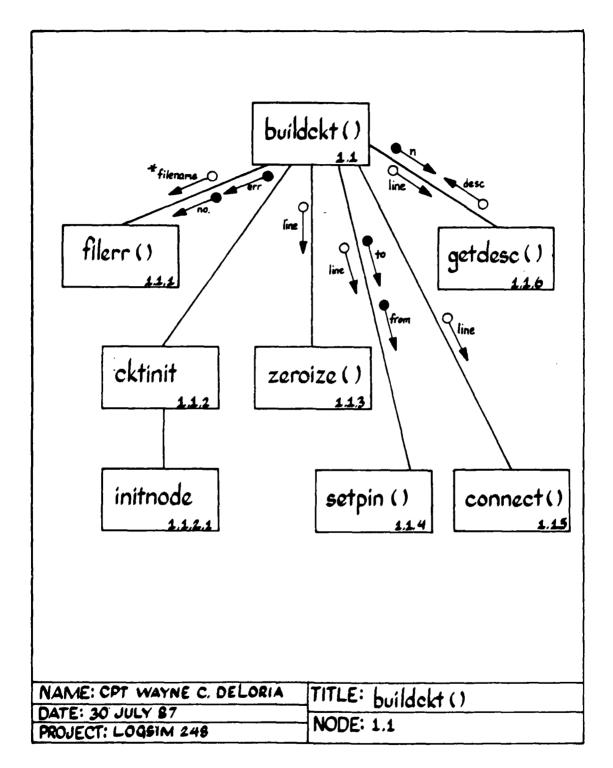

| в8.  | <pre>buildckt(), cktinit()</pre>                | B-8         |

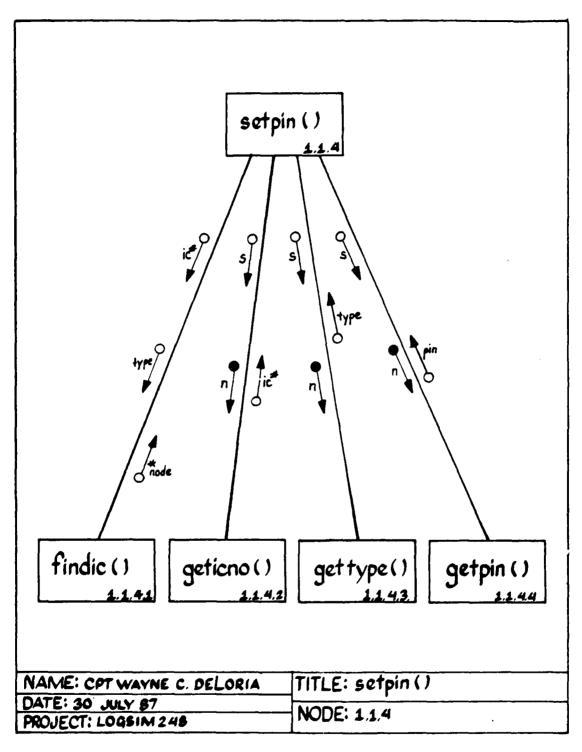

| в9.  | setpin()                                        | B-9         |

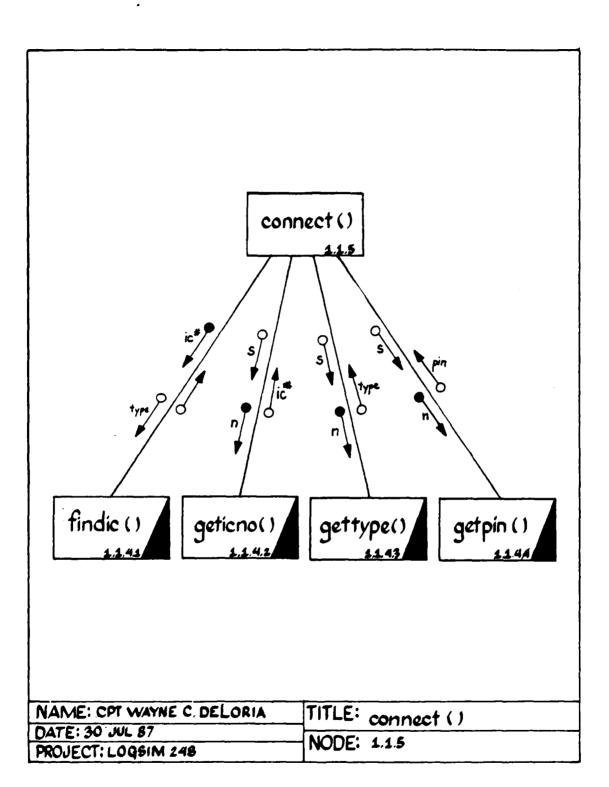

| B10. | connect()                                       | B-10        |

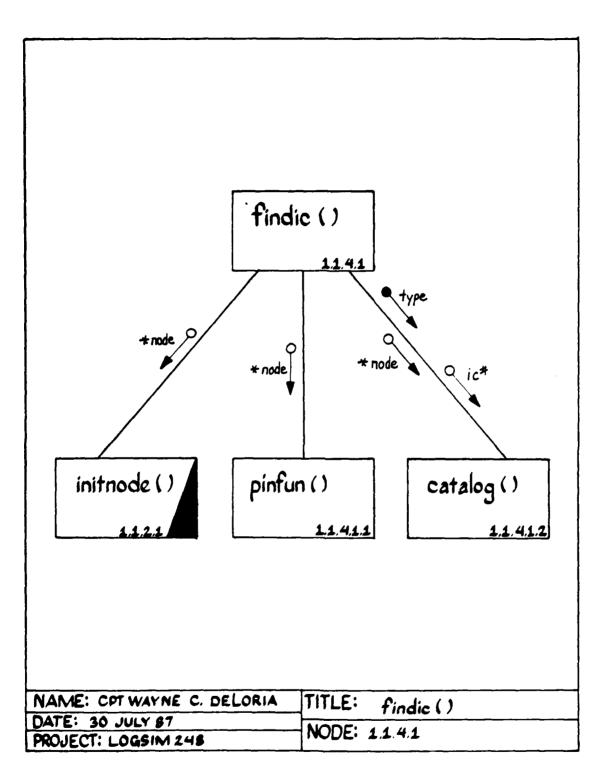

| B11. | findic()                                        | B-11        |

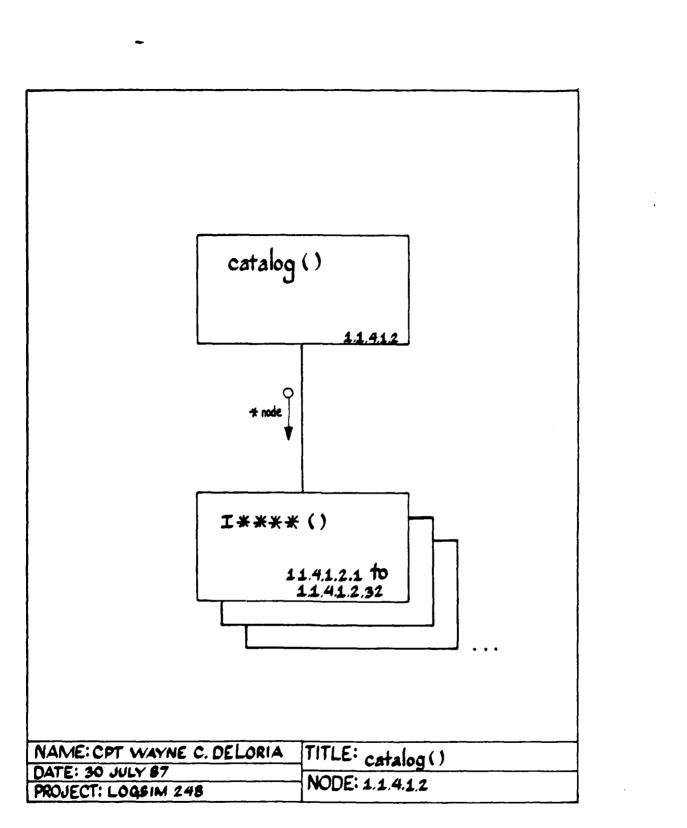

| в12. | catalog()                                       | B-12        |

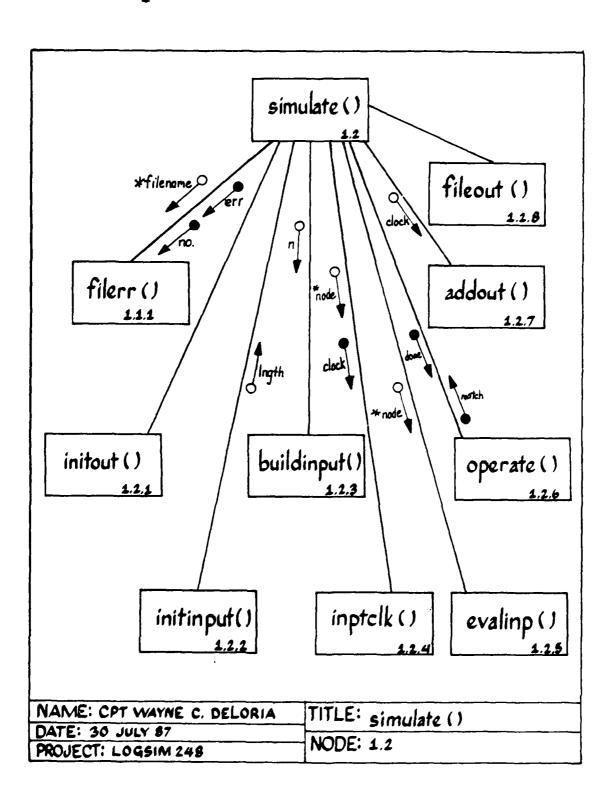

| в13. | simulate()                                      | B-13        |

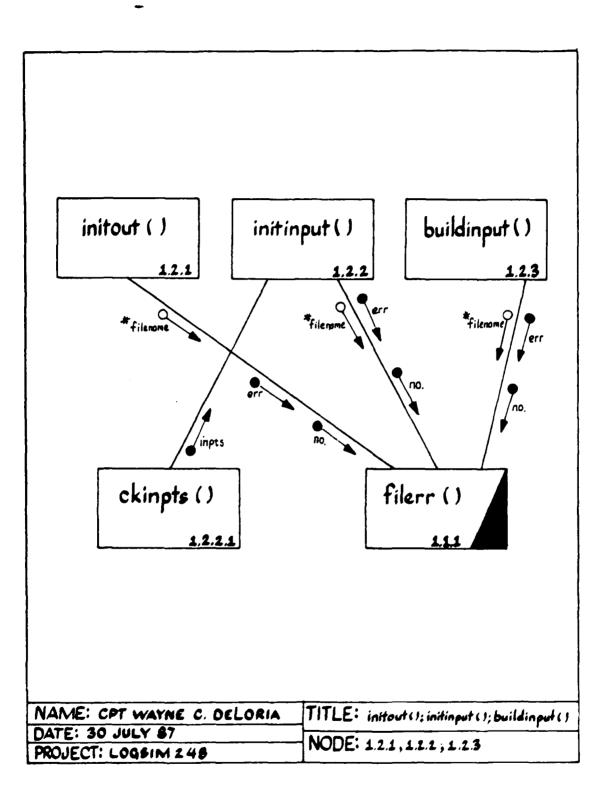

| B14. | <pre>initout(), initinput(), buildinput()</pre> | B-14        |

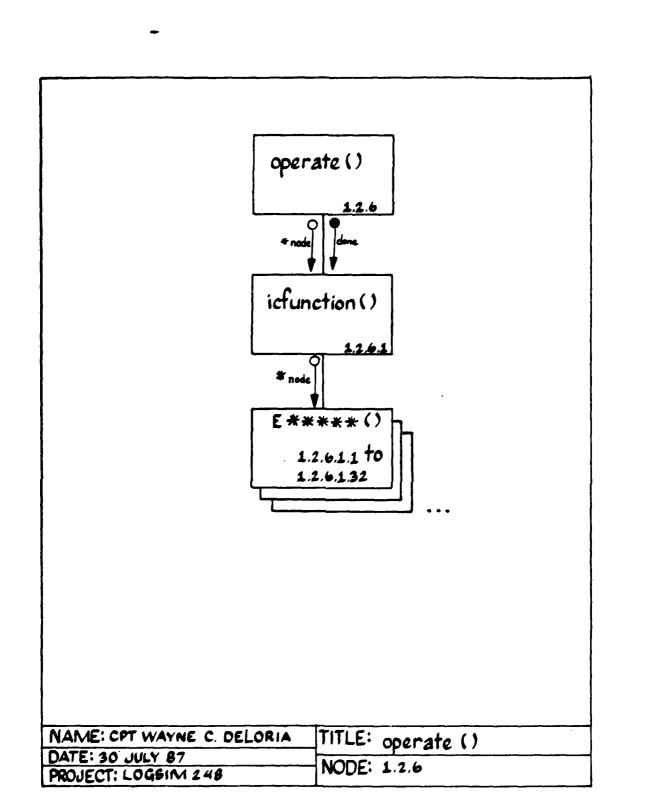

| B15. | operate()                                       | B-15        |

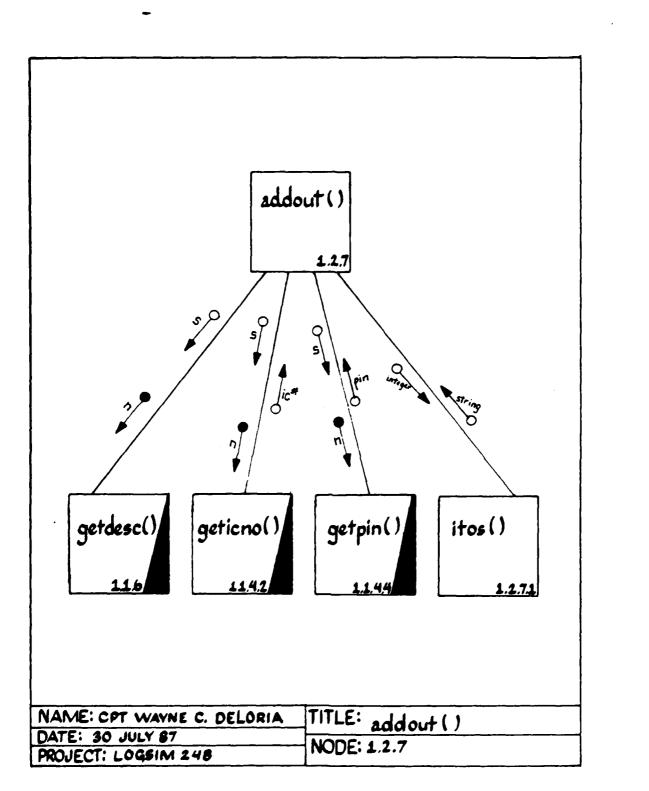

| в16. | addout()                                        | B-16        |

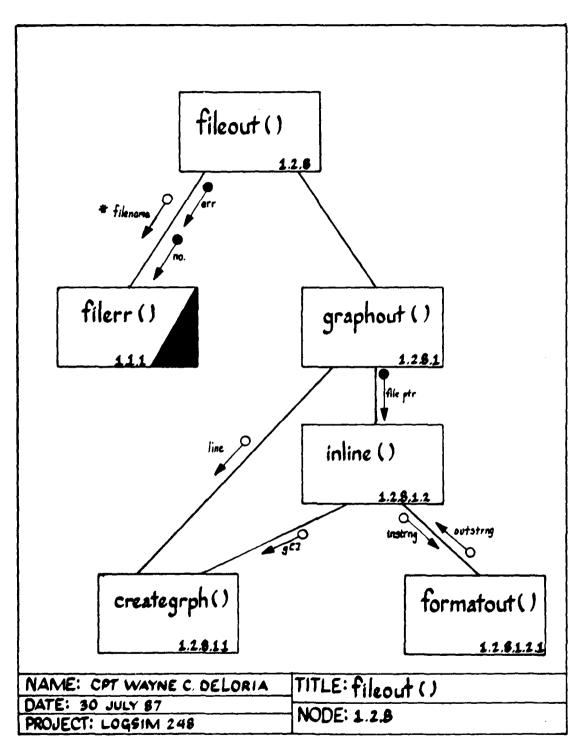

| в17. | fileout()                                       | B-17        |

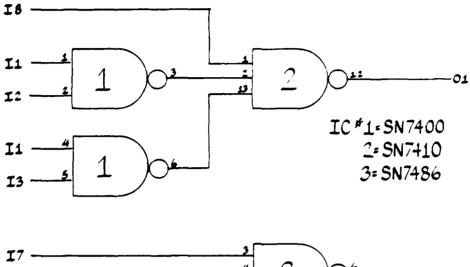

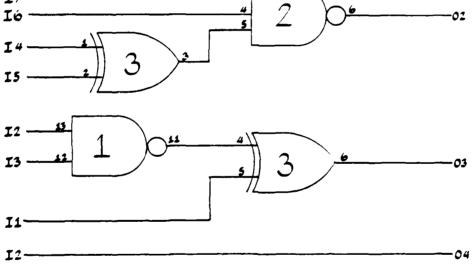

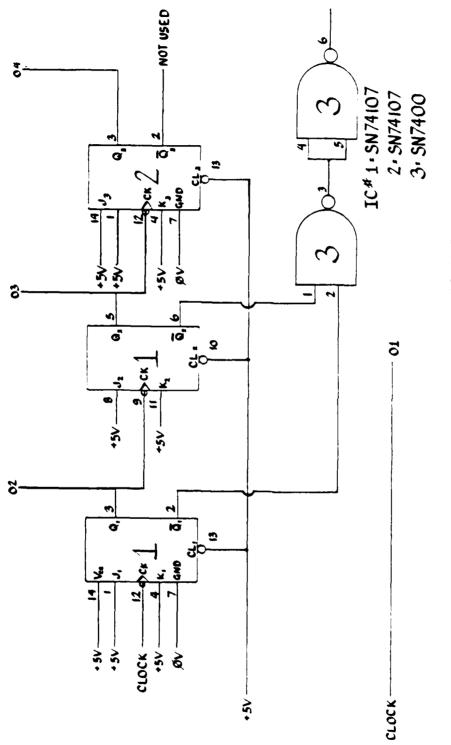

| D1.  | Schematic Diagram for BCD.CKT                   | D-1         |

| D2.  | Inputs for BCD.CKT                              | D-2         |

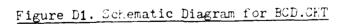

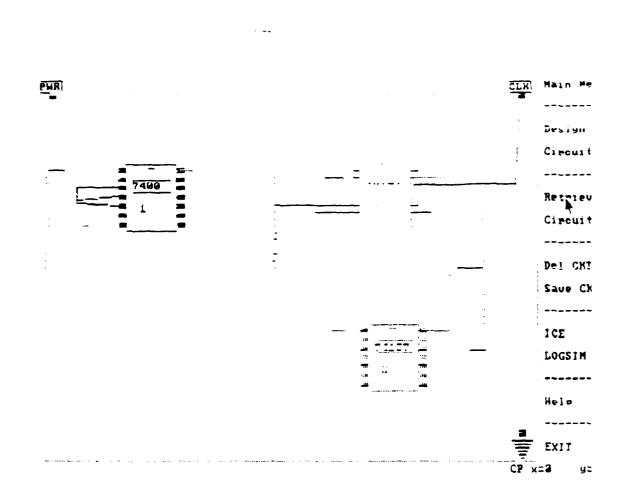

| D3.  | Graphic Circuit Image for BCD.CKT               | D-2         |

| D4.  | Binary Output Image for BCD.CKT                 | D-3         |

| D5.  | Waveform Output for BCD.CKT                     | D-3         |

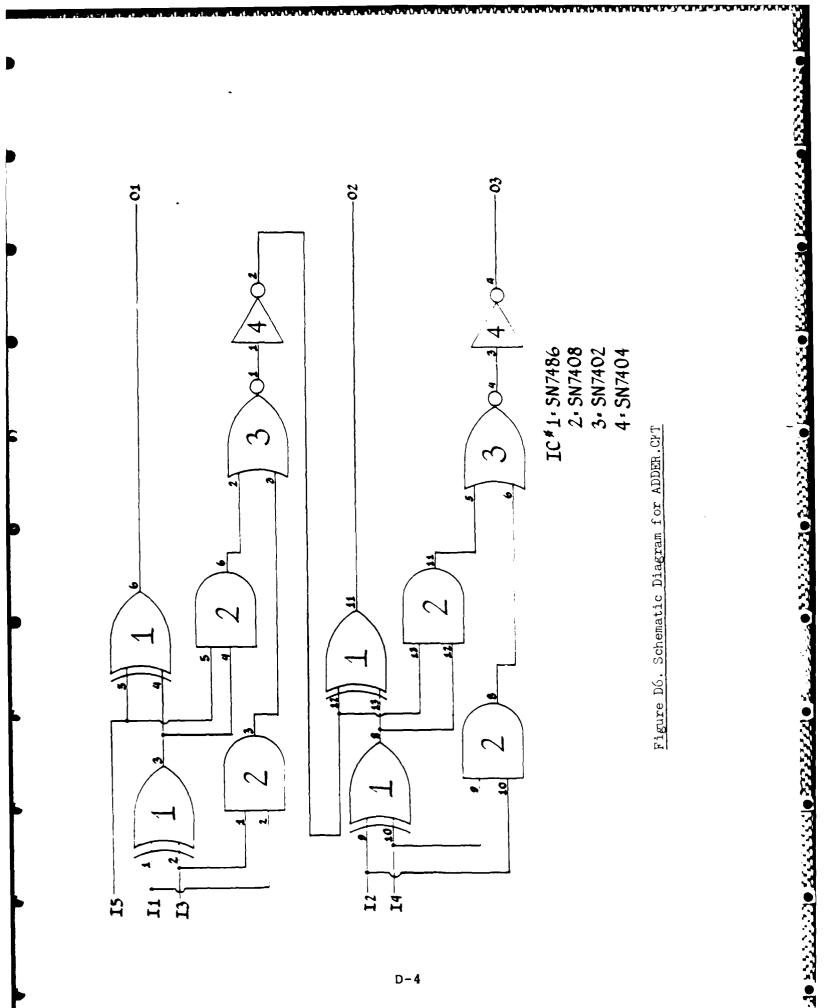

| D6.  | Schematic Diagram for ADDER.CKT                 | D-4         |

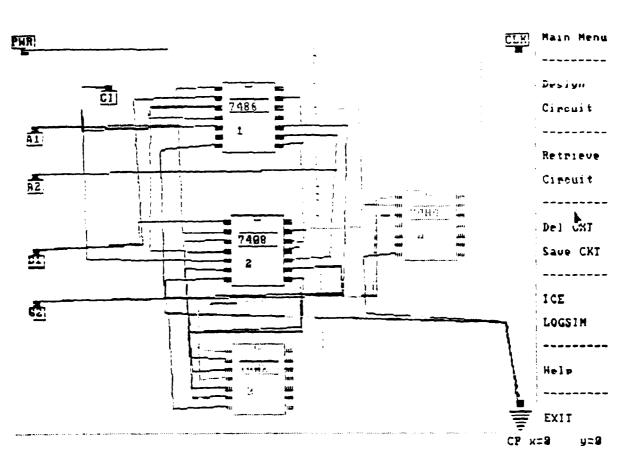

| D7.  | Page<br>Graphic Circuit Image for ADDER.CKT                    |

|------|----------------------------------------------------------------|

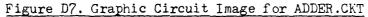

| D8.  | Inputs for ADDER.CKT                                           |

| D9.  | Binary Output Image for ADDER.CKT D-6                          |

| D10. | Waveform Output Image for ADDER.CKT D-6                        |

| D11. | Schematic Diagram for BCR3S.CKT D-7                            |

| D12. | Graphic Circuit Image for BRC3S.CKT D-8                        |

| D13. | Binary Output for BRC3S.CKT D-9                                |

| D14. | Waveform Output for BRC3S.CKT                                  |

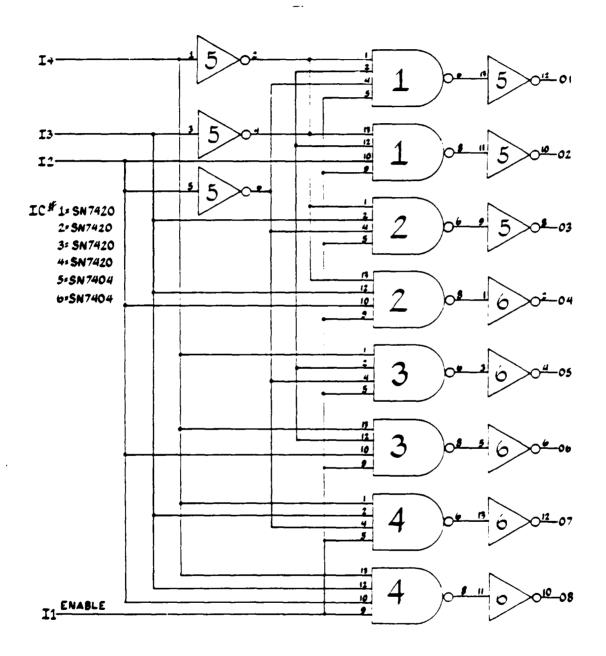

| D15. | Schematic Diagram for DECODER.CKT D-10                         |

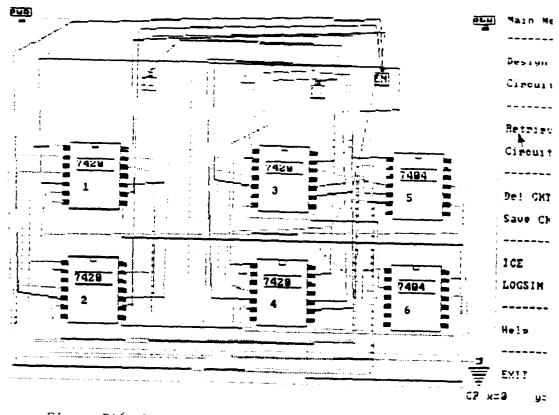

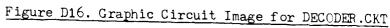

| D16. | Graphic Circuit Image for DECODER.CKT D-11                     |

| D17. | Inputs for DECODER.CKT                                         |

| D18. | Binary Output for DECODER.CKT D-12                             |

| D19. | Waveform Output for DECODER.CKT                                |

| El.  | LOGSIM248 TTL IC Library                                       |

| E2.  | Schematic For TEMP.CKT - Binary Coded Decimal<br>Encoder E-B-2 |

| E3.  | Circuit Configuration Input File - TEMP.CKT E-B-2              |

| E4.  | Output Monitor File - TEMP.DIS E-B-2                           |

| E5.  | Input Data File - TEMP.IN                                      |

| E6.  | Input Port Label FIle                                          |

| Ε7.  | Binary Output File - TEMP.OUT                                  |

| E8.  | Waveform Output File - TEMP.WAV E-B-3                          |

<u>Čečelo zerostalo žerostalo žerostalo zerostalo zerostalo zerostalo zerostalo kerestalo zerestalo zerestalo zerostal</u>

# List of Tables

| 1.  | Data File Formats                                         | Page<br>21 |

|-----|-----------------------------------------------------------|------------|

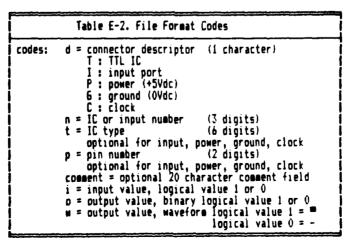

| 2.  | File Format Codes                                         | 21         |

| 3.  | Simulation Run Time Comparison                            | 55         |

| 4.  | Mean Run Time Comparison for Concurrent<br>Implementation | 57         |

| El. | Data File Formats                                         | E-7        |

| Е2. | File Format Codes                                         | E-7        |

## Abstract

The digital logic simulator, LOGSIM248, a re-engineered version of LOGSIM, version 5.5, has been implemented as a component of the digital design environment, IDIET (Integrated DIgital Engineering Tool). This new design expands the capabilities of the older version by improving run time performance, maintainability, and compatibility. Written in the C programming language, LOGSIM248 boasts looser coupling between functional modules while exhibiting greater functional cohesion within these modules. As an integral part of IDIET, the simulator overcomes difficulties created by the complicated user interface of earlier versions.

With greater run time performance as a goal, this new simulator was studied and adapted to produce a concurrent implementation. Here, several roadblocks were encountered which essentially showed this algorithm and data structure implementation to be difficult to "parallelize" at best. Due to communication constraints on the host computer, data structures used to simulate circuits caused large delays due to the requirment to disassemble and re-assemble them at the

i x

various processing nodes. This program handicap coupled with communication transmission delays between processors resulted in time complexity problems.

Essentially a software engineering project, the re-design of LOGSIM, version 5.5, was necessitated by various shortcomings associated with the older version. The new implementation conforms to the proposed ANSI standard for the C programming language by utilizing only standard library functions and source code which complies with the original Kernighan and Ritchie model. This re-hosting has improved system portability allowing LOGSIM248 to run on all MS/DOS micro-computers available to the designer.

# A DIGITAL LOGIC SIMULATOR WITH CONCURRENT PROGRAMMING CONSIDERATIONS

# CHAPTER 1 - THESIS OVERVIEW AND ORGANIZATION

1.1 Overview

Recently, a great deal of attention has been directed toward methods which enhance efforts to design and build efficient and functional digital circuits with minimum cost and maximum performance. The primary products resulting from these efforts are a plethora of computer aided design (CAD) tools appearing on today's computer software market. These tools aid the user in circuit design, circuit board layout, and, in some cases, circuit simulation. Although not all CAD tools include simulation as a part of their working environment, simulation of digital circuits is an integral part of the design process and should be considered when building such tools.

In this thesis effort, the simulation of digital circuits is explored with the production of a logic simulator as a functional by-product. This study improves on an existing simulator called LOGSIM which was developed at the University of Kentucky and enhanced by students at the Air Force Institute of Technology (1). This design tool

simulates digital circuit designs at the integrated circuit (IC) level, allowing chip and pin level circuit descriptions to be tested for functionality and performance. Various problem areas were still present within the enhanced version produced at AFIT - particularly simulation run time for large circuit designs, and software engineering inadequacies which could hamper maintenance and future upgrades.

This thesis effort centers around two main areas of investigation. First, LOGSIM is re-engineered for inclusion as an integral part of a digital design tool which offers a graphic user interface, a circuit connectivity expert system, and the logic simulator. Secondly, methods are explored to re-host LOGSIM on a parallel processing computer in an effort to realize faster simulation run times.

The first part of this effort has been accomplished with the associated efforts of two other thesis projects. The first of these is the design and implementation of a graphic user interface which provides the user with a pictorial representation of the circuit design (2). The second project employs an expert system which studies the circuit design and reports problems in IC inter-connectivity, missing or improper connections, and possible oscillation/race conditions (3). All three of these projects have been integrated to produce a comprehensive digital design tool which is expected to be employed in the academic arena.

The second part of this thesis deals with a concurrent construction of the simulator to enhance run time

performance. A parallel model has been engineered and compiled with some improvements noted and directions for future efforts realized. This part of the project utilized the simulator developed for the integrated effort and exploited the natural parallelism contained therein to develop a "first-cut" compilation for the initial analysis.

# 1.2 Organization

The remainder of this thesis report provides a detailed review of all implementation efforts and analysis of results for those goals outlined in the previous section. It is followed by five appendices which contain supporting data referenced throughout the report.

Chapter 2 contains the thesis introduction and presents an overview of the research goals toward which this project is aimed. In Chapter 3, early work with LOGSIM is discussed, problem areas identified, and re-engineering efforts as related to the integrated design tool implementation discussed. Chapter 4 contains results of work performed towards meeting the requirements of the digital design tool. Methods are discussed and results presented. Chapter 5 discusses the parallel implementation, method of attack, and comparative results. Finally, Chapter 6 offers a discussion of the effort as a whole, lessons learned, and resulting contributions to the computing arena.

Appendix A contains a complete listing of the source code for LOGSIM248, the simulator implemented for this project. Appendix B is comprised of all data flow and functional decomposition block diagrams used during the design phase of the project. Statistical information which compares an older version of the simulator to the new version is contained in Appendix C. Test case documentation is contained in Appendix D. A manual for independent use of the new simulator is included as Appendix E.

#### CHAPTER 2 - INTRODUCTION AND OBJECTIVES

# 2.1 Introduction

The development process for any end item is most effective when the item produced performs those functions described by the applicable requirements while conserving resources such as time, money, and materials. Design engineers are successful during the research phase of product development when functional prototypes perform in accordance with requirements. Productive engineering practices must be employed during all phases of the development cycle in order to satisfy these goals.

It would be most effective to build prototypes which are already known to function properly. This way, only those resources necessary to build the minimum number of required prototypes will be expended and delays or cost overruns due to extended research can be avoided. Trial and error methods not only waste time, but are expensive and may expend costly and scarce materials.

Computer simulation of functional end items is a method through which engineers may confirm or expand the operational capabilities of the end product without first building expensive prototypes. Simulators can be used for fault isolation and detection, optimization of design, and confirmation of component interaction in complex designs.

After simulation results have shown that the product performs in accordance with requirements, the prototype may be built with greater assurance of functional success (4:118).

One research area where simulation is most appropriate is in digital circuit design. Here, especially for large, complicated circuits, the design engineer could spend a great deal of time debugging physical prototypes without the aid of computer simulation.

Research and academic environments are two areas where simulations of basic digital designs would aid in the development process. The effects of simulation tools in the research environment was noted earlier in this section.

In the academic world, materials are a precious commodity and simulations which guarantee the proper functioning of digital circuits prior to building prototypes would be beneficial. Additionally, laboratory resources (space, time, etc.) are difficult to schedule on most campuses. The time/space required for building and testing digital circuits can be lessened by using simulation techniques prior to prototype construction. This would free crowded laboratories and allow greater flexibility in academic scheduling practices.

Effective digital circuit simulation tools should be composed of three distinct sub-functions. The first is the user interface. Here the user describes the circuit elements and interconnections. The input streams, output specifications and circuit layout may also be described.

Graphical representation of the circuit is a helpful aid for future conversion to physical prototypes and also allows the user a pictorial view of the circuit. This view can aid in circuit debugging and may later be included as a integral part of a larger circuit.

The second area to be considered in a digital design simulation tool is assuring that the input circuit is correct and consistent. Such problems as input pin to output pin connections, ground to electrical high, disconnected power, and improper fan-out are examples of errors in the design which must be isolated before proper simulation can take place. A routine which checks the circuit design for these problems should be incorporated into the simulation tool to insure proper functionality. Debugging a design prior to simulation allows the user to better understand simulation results. Incorrect or unexpected results may stem from two areas. The circuit may be incorrectly designed, or a connection error may have been made during the construction of the graphic representation of the circuit. The user can be alerted to many design errors through the use of such a connectivity checker, giving a greater assurance of circuit correctness.

Finally, the heart of the design tool is that routine (or group of routines) which actually performs the functional simulation of the circuit. Using the circuit design, input

stream, and output specifications, this routine may perform either logic or timing (or both) simulations by following the circuit path from inputs to outputs and returning output values for a designated series of clock cycles. Logic simulators are used to verify the functioning of a given circuit while timing simulators are used to confirm time relationships between various signals within the circuit.

Various constraints must be realized before designing and implementing a digital design simulation tool. The first and perhaps foremost consideration should be the target audience. A large number of Computer Aided Design (CAD) tools presently exist --each configured for a specific purpose. Tools used to simulate simple circuits designed in an academic setting, by nature of their requirements, differ from those used to simulate Very Large Scale Integration (VLSI) designs used in complex production environments.

The host computer, i.e., the computer on which the simulation tool will be run, is also a major consideration. The screen size, resolution, and underlying graphics hardware affect the graphical representation created by the user interface. The simulation designer must be concerned with expected circuit size, layout, and complexity. Circuit designs may be limited in these areas due to screen, memory, and processing speed constraints. Computer memory could limit circuit size and the necessity to utilize large, complicated, data structures, while the processing speed of the computer could affect the simulator's ability to produce

results in an acceptable time period. Large complicated designs may be impractical to run on small, slow machines.

The user must have at his disposal a wide range of electrical and/or digital components to use in designing circuits. How these components are represented within the simulation program is a major consideration for the programmer. Hardcoded representations of component descriptions and/or operation may improve the speed of the simulation but hamper easy addition of new components to the simulators library. Component libraries stored on disk in retrievable data base format may slow the simulation but are easily updated and may be used universally by all modules of the simulation tool.

Logic simulations of circuits with only a few components may produce results using sequential algorithms relatively quickly. However, the combinatorial explosion apparent in simulations of circuits employing a large number of integrated circuit (IC) packages or electronic components may make sequential simulation routines impractical. Parallel processing computers now being introduced into the computing community may hold the solution to this problem of the Von Neuman "bottleneck."

Methods by which simulation routines are "parallelized" is a research area gaining a great deal of attention. Because digital circuits are inherently parallel in their design it would seem apparent that simulators which capitalize on this parallelism must improve performance and

produce results more quickly. The question gaining researcher's attention deals with the most efficient and practica! method to employ in working towards this end.

### 2.2 Research Objectives

This thesis effort is divided into two separate, but related, objectives. The first objective is the reengineering and re-design of an existing digital logic simulator for inclusion into an integrated design tool which combines the three sub-functions referred to earlier -- the user interface, the circuit connectivity checker, and the circuit simulator. The user interface and connectivity checker are being implemented through associated thesis efforts. The user interface is being designed as a graphic oriented interface employing the EGA graphics standard (2). The connectivity checker (3) is being designed as an expert system which utilizes Micro Data Base System's GURU expert system tool (5).

The host computer for this integrated design tool (and ultimately for the logic simulator) is an Intel 80286 based Zenith 248 micro-computer utilizing the MS/DOS operating system. However, it is desirable to insure the functionality of both the simulator and the entire design tool on as many compatible (MS/DOS) computers as possible.

The digital design tool is envisioned to be used primarily in an academic environment to design, test, and simulate

basic digital circuit designs which employ TTL IC packages. This tool will allow the student to work a level of abstraction higher than that of most digital design tools. Other available digital CAD systems usually require design work at the gate level. In this project the designer will work with those TTL components commonly found in digital design laboratories. Specifically, the 7400 family of IC packages is used as an initial library of available circuit components. A modest collection of 32 separate packages was identified for the initial IC library. This insured that designs of a general nature could be simulated by the tool while permitting the designers more time to develop system capabilities and optimize the algorithms involved.

The user interface is being implemented as a graphic oriented, menu driven system through which the user creates a pictorial representation of the circuit design using IC graphic icons and interconnecting lines. The design is produced interactively with the aid of a mouse and keyboard input to system produced prompts. After completing the design, the user may invoke either the connectivity checker or the logic simulator through one of the interactive menu: (2).

The connectivity checker consists of an expert system which inspects subject circuits for possible illegal or erroneous connections. Connections which are suspect but not necessarily illegal are annotated and presented to the user as 'questionable.' Absent connections are labeled as

'missing.' The results of both this effort and the simulator are presented to the user on separate screens. This expert system and the logic simulator have been designed to function independently or as an inclusion to the integrated design tool (3).

The second objective of this thesis deals with exploration into methods by which this re-designed simulation program may be "parallelized" in order to improve run time performance. The host computer for this effort is a 32 node Intel iPSC hypercube parallel processor in which all or groups of the 32 processors may be used during simulation.

### 2.3 Summary

Simulation of digital circuits is not a new venture. Many CAD systems exist for the design and simulation of digital circuits. Academicians and researchers are continuously exploring methods to improve digital design and shorten the development cycle. This thesis effort provides a digital logic simulator as part of an integrated design tool which will aid design students in first year college design courses. The design tool will incorporate three functional systems -- a graphic user interface, connectivity checker, and logic simulator. These three sub-systems provide the user with a robust tool which allows the user to produce correct, functional circuits prior to prototype development.

CHAPTER 3 - LOGSIM

# 3.1 Background

LOGSIM, version 5.5 (6), is a digital design logic simulation program which has been used in the design of simple circuits employing a very limited library of integrated circuit (IC) packages. LOGSIM is unique in that all simulations are performed on circuit designs represented at the IC level. This approach differs from most digital logic simulators which perform simulations of circuits represented at the gate level. This higher level of abstraction allows the user to visualize circuit layout, economize on pin and chip count, and become familiar with commercially available IC packages.

The original program was created at the University of Kentucky by Samuel A. Smith, under the auspices of Frank M. Brown, PhD. This program, though functional, was poorly documented, confusing to use, and difficult to maintain. "The code is an excellent example of a very clever program that was obviously difficult to write but it is equally difficult to read. The original code had only 138 comments out of approximately 2800 lines of code (2:2)." It was implemented in Sheffield Pascal and initially hosted on a PRIME S850 computer (2:2).

In late 1985, CPT Mark C. Rowe from the Air Force Institute of Technology, re-hosted LOGSIM onto a 16-bit microcomputer utilizing the MS/DOS operating system and onto the VAX 11/780 utilizing UNIX. He wrote these new versions in TURBO Pascal (7) for the microcomputer and Berkely Pascal (8) for the VAX, re-engineering the entire project. The end result of CPT Rowe's effort is a more thoroughly documented simulator which is markedly easier to use and maintain. This re-engineered version of LOGSIM (version 5.5), although a usable tool, still contains many problem features making it unattractive to inexperienced users.

First, the user interface is very cumbersome, requiring the circuit designer to traverse a large number of menus to completely specify the circuit. For larger circuits, this process must be interrupted to store sections of the design on disk. Circuit connections are specified on a pin-by-pin basis wherein the user is prompted by IC and pin number and responds with the IC and pin number of the connected component. The user has no means of visualizing this and must complete a detailed design by hand prior to simulation.

Secondly, because of the manner in which pin-to-pin connections are referenced within the program, the number of IC's which may be included in any one circuit design is limited to only 32 of the more basic packages. Specific chip/pin relationships are represented by a five digit integer. This integer identifies the IC and pin number of

the source. The first three positions of this integer indicate the pin number while position four and five depict the IC number. This representation allows the use of modulo arithmetic and integer division to extract IC and pin numbers for inter-package connections. Because of the integer overflow problem with integers greater than 32767, only 32 packages may be included in any one circuit design.

A third problem deals with the limited number of IC's available for inclusion in the design. All IC's used in design simulation within LOGSIM must be contained in the present IC library of 32 standard TTL packages. If the designer wishes to incorporate an IC into the circuit design which is not present in this library, LOGSIM cannot be used. No automated capability presently exists for the user to specify parameters for a new IC or to add new IC's to the existing library. Any additions to the library would have to hardcoded into the program. The program must then be recompiled, forming a new executable version of the simulator.

Another problem lies in the area of proper connectivity. Upon completion of the design and prior to running the simulation, the circuit is not checked by the program for design defects, such as incorrect or incompatible pin connections, missing inputs/outputs, improper inputs/outputs, etc.. If problems of this sort do exist, the simulation will run with the erroneous circuit configuration, possibly generating incorrect results. Because the simulation may run to conclusion, the user has no way of knowing if the results

are incorrect due to design defects or improper circuit connections specified within LOGSIM.

If the circuit to be simulated has no external inputs, (i.e., the only connections to IC inputs pins are power, ground, and clock) LOGSIM, version 5.5, cannot be used. At least one input stream must be specified for every simulation run. Additionally, it is not possible to monitor power, ground, or clock for output display purposes. Only the values at the IC pins and user supplied input values may be monitored. If power, ground, or clock are connected to an input pin and this pin is monitored, only zeros (logical low) will be displayed for that pin. The actual values of these pins are assumed by the attribute of the pin descriptor field in the circuit node data structure. These descriptors are bound during configuration of the circuit and remain static for the duration of the simulation. This problem limits the user to circuits which have external inputs and prevents the user from displaying all results which may be required for proper analysis of the circuit.

The current version of LOGSIM is a sequential program, designed and written in TURBO Pascal and implemented on MS/DOS (Intel 8086/8088-based) compatible micro-computers. Digital circuits, by nature of their construction, may contain many sections which perform operations concurrently. Large complicated designs, if forced to execute sequentially, may require long periods of time to perform the desired simulation and produce usable results. LOGSIM, version 5.5,

16

operates relatively quickly for small, simple designs which utilize only a few IC's. However, as the size of the input circuit grows, simulation time appears to increase exponentially.

Finally, LOGSIM, version 5.5, does not run on all MS/DOS compatible micro-computers. Because of memory constaints inherent in the TURBO Pascal (version 3.0) compiler, overaly files were required to allow the execution of the entire simulator. The methods used to compile the implementation of these overlay files cause segmentation errors in Intel 80286based computers. It is an expressed objective of this project to re-host LOGSIM onto a Zenith 248 which, due to these segmentation problem, does not support the present version of LOGSIM. Re-engineering the simulator with this and other design considerations will vastly enhance capabilities and performance.

#### 3.2 LOGSIM248 Implementation

# 3.2.1 Overview

LOGSIM248 is a digital design logic simulation program, developed for this thesis effort, which is a new implementation based on LOGSIM, version 5.5. The original source code was written in the C programming language and developed using the Borland International TURBO C integrated development environment (9). TURBO C conforms to the

proposed ANSI standard for C compilers and also contains additional function libraries which enhance it's capabilities. LOGSIM248, however, does not incorporate any TURBO C specific library functions. Portability of LOGSIM248 source code is, therefore, not compromised. This simulation program may be run independently or as an integral part of the larger digital design tool, IDIET (Interactive DIgital Engineering Tool). If run independently, all files normally created by IDIET's graphic user interface must be created by the user as ASCII files. Because LOGSIM248 performs no checking of input file correctness, all files created as input for the simulator must be formatted in accordance with predefined interface

DECENTRY DESCRIPTION DESCRIPTION DESCRIPTION

independently, all files normally created by IDIET's graphic user interface must be created by the user as ASCII files. Because LOGSIM248 performs no checking of input file correctness, all files created as input for the simulator must be formatted in accordance with predefined interface specifications (see Appendix E). When run as an integral part of IDIET, LOGSIM248 is invoked through the graphic user interface. All input files are created by the user interface prior to simulation run and are supplied to LOGSIM248 properly formatted.

# 3.2.2 Data Structures

LOGSIM248 operates on three main data structures; the circuit configuration list, the input data list, and the output display list. Each of these is implemented as a circular linked list with a dummy header node. This configuration is useful when complete list traversals are

required as the index is left pointing to the head of the list after completion of the traversal.

The circuit configuration list consists of linked nodes, each representing one IC package of the input circuit design. These nodes are modeled after similar data structures in LOGSIM, version 5.5, and contain fields for IC type, IC number, pin types, initial and subsequent pin TTL values, and pin-to-pin connection descriptors.

The input data list consists of nodes which correspond to input source descriptions. These nodes contain two fields -the input number and the input value of the current clocked input from that source.

The output display list consists of nodes corresponding to user requested output monitor points. Each node is represented by a string of two parts. The first 32 elements of the string consist of a description of the monitor point. The remainder of the string consists of output values derived from the simulation which correspond to the clocked input values.

Four associated data files are required for proper functioning of the simulation program. These files communicate the circuit configuration, input data stream, input port labels, and output monitor points to the requesting LOGSIM248 modules (see Table 1).

(1) TEMP.CKT contains all connections required to complete the circuit design.

(2) TEMP.IN contains input numbers and their corresponding input streams.

(3) TEMP.IND contains the user supplied, two character, input port labels used to identify corresponding input streams.

(4) TEMP.DIS contains a listing of all user requested monitor points to be used in constructing the output file.

LOGSIM248 creates two output data files. These files contain simulation results in two separate formats:

(1) TEMP.OUT contains a description of the requested monitor points in a usable format (different from that of TEMP.DIS) followed by the corresponding output stream of ones and zeros.

(2) TEMP.WAV is divided into two parts. The first is a listing of the input ports (again in a usable format, with user assigned port labels) followed by the input data stream. The second part consists of the output monitor points and associated data streams as described for TEMP.OUT above. The data streams for this file, however, are made up of graphic characters which give the waveform equivalent of the binary data.

|                                               | Table 1. Data<br>(see Table 2.                                    | File Formats<br>for format codes)                   |                                           |

|-----------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|

| tesp.ckt_                                     | circuit i<br>format Ednantttttp<br>example:                       | nput file<br>p comment:dnnntttttp                   | p comment)                                |

| P000                                          | power +5Vdc                                                       | :T001 740014 pow                                    | er Vcc                                    |

|                                               | output so<br>format: [dnnnttttt<br>examples:                      | nitor file<br>pp comment:]                          |                                           |

|                                               | 003 output pin #3<br>input #3                                     | :                                                   |                                           |

| -                                             | format: [nnn:iiiii<br>example:                                    |                                                     |                                           |

| 001:1010                                      | 101010101010110101010                                             |                                                     | ··                                        |

|                                               | format: [[C #nnn (S<br>[Input nnn<br>[Clock<br>[Power<br>[Ground  | utput file<br>Nnnnn) PIN #nn                        | :000]<br>:000]<br>:000]<br>:000]<br>:000] |

| IC # 1<br>Input 0<br>Clock<br>Power<br>Ground | examples:<br>(SN 7400) PIN #13<br>03                              | :0110111001111000<br>:1001100001110011<br>:01010101 | 0001101<br>0101010<br>1111111             |

| tesp.nev                                      | waveform                                                          | output file                                         |                                           |

|                                               | input stream descr<br>format: [Input #n<br>output stream desc     | nn Port cc<br>ription                               | :iiiI                                     |

|                                               | [Input nn<br>[Clock<br>[Pow <b>er</b><br>[Ground                  | (SNnnnn) PIN ‡nn<br>7                               | :WNW]<br>:WNW]<br>:WWW]<br>:WWW]<br>:WWW] |

| Input fil                                     | example:<br>le contents:<br>1001 Port Al                          | ·                                                   | <b>Fill</b> S                             |

| IC # 1<br>IC # 13<br>Input<br>Clock<br>Power  | ita streams:<br>L (SN 7400) PIN #13<br>3 (SN74181) PIN #13<br>003 |                                                     |                                           |

| 6r ound                                       |                                                                   |                                                     |                                           |

\*\*\*\*\*\*

| Table 2. File Format Codes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| codes:                     | <pre>d = connector descriptor (1 character)     T : TTL IC     I : input port     P : power (+5Vdc)     G : ground (0Vdc)     C : clock n = IC or input number (3 digits)     t = IC type (6 digits)     optional for input, power, ground, clock p = pin number (2 digits)     optional for input, power, ground, clock comment = optional 20 character comment field i = input value, logical value 1 or 0 o = output value, binary logical value 1 or 0</pre> |  |  |  |

| ļ                          | w = output value, wavefors logical value 1 = •<br>logical value 0 = -                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

3.2.3 Operation

LOGSIM248 first opens the circuit configuration file (TEMP.CKT) and reads the circuit connection list one entry at a time. Each entry represents a two ended connection. This may be pin-to-pin, input-to-pin, power-to-pin, etc.. Circuit configuration nodes are initialized and added to the circuit configuration list for each new IC number encountered. Initialization of these nodes includes dynamic allocation of storage for the node, linking of the node to the front of the circuit configuration list, and assigning initial values to all fields of the node data structure. After this initialization has been accomplished, connections are annotated by assigning IC/pin numbers, power or ground indicators, or input port numbers to the appropriate field of the node. If new IC numbers are encountered for the next connection, only the connection field of the already existent IC nodes are updated.

The next step is to initialize the input data list by creating a linked list header, opening the input data file (TEMP.IN), and dynamically allocating storage for each input node indicated by a input number and associated data stream from the input data file. As each input node is created, the input number corresponding to the next entry of the input data file is assigned to the input number field of the node.

As the simulation progresses through the associated data streams the data field of the input node is updated for each clock pulse until all data is exhausted.

Two coded functions are required for each IC type (i.e., SN7400, SN7402, etc.). The first of these functions is used when initializing circuit configuration nodes. This function contains initial values for certain fields of the data structure. These include IC type, pin types, and some initial pin values and connections. All fields not initialized by this function are assumed general in nature and are initialized by a general initialization function.

The second function required for each IC type deals with the operation of the IC. This function is used during the simulation to equate output pin values to existing input values using functional descriptions obtained from TTL data manuals. During each clock pulse of the simulation and immediately following the assignment of all new input values, the operation function related to each IC of the configuration circuit list is called in turn and the new values of the output pins assigned to the corresponding fields of the appropriate circuit nodes. This is repeated until two consecutive operations of the circuit produce the same output values. At this point the clock can be advanced and the next data set evaluated. Failure to produce two consecutive constant output pin value sets after a specified

number of iterations causes termination of the simulation. The user is notified that the circuit is in an oscillation condition and is presented with the clock pulse containing the errant data set.

The final function of the simulator is to produce the two output files discussed in section 3.2.2. After each set of input values (for a particular clock pulse) is simulated, and prior to moving on to the next set, the circuit configuration list is searched for those pins identified in TEMP.DIS. These are the pins which the user identified as monitor points for inclusion in the output files. After locating these points the corresponding values are appended to the appropriate output stream in the output display list. After the last set of input values has been simulated, the output display list is used to create TEMP.OUT and TEMP.WAV.

#### 3.3 Summary

Although a usable tool, LOGSIM, version 5.5, was in need of a major overhaul. Problems in software design, portability, and performance limited its' use and impaired its' maintainability. LOGSIM248, as will be seen in the next chapters, has overcome these problems, and presents a more efficient and usable tool. Re-designed data structures and a new data interface have allowed the integration of LOGSIM248 into a total digital design tool while improving maintainability.

# CHAPTER 4 - SOFTWARE DEVELOPMENT

# 4.1 Re-engineering Overview

The re-engineering effort which resulted in the design and implementation of LOGSIM248 proceeded in five distinct phases;

- (1) analysis of LOGSIM version 5.5

- (2) design, LOGSIM248

- (3) coding, LOGSIM248

- (4) integration of LOGSIM248 into IDIET

- (5) testing and debugging, LOGSIM248 and IDIET

#### 4.2 Analysis - LOGSIM, version 5.5

The analysis of LOGSIM, version 5.5 was divided into two separate parts. The first part consisted of a "hands-on" approach which was necessary to become familiar with user interaction and program performance. Several small digital circuits were used to accomplish this objective. These circuits consisted of one or two IC's which performed very basic functions and are of no consequence here.

The second part of the analysis involved an in-depth study of the simulation source code and accompanying documents. This proved to be a time consuming effort due to the length of the source code and those software engineering shortcomings discussed in Chapter 3.

During the "hands-on" familiarization with LOGSIM, version 5.5, most problems encountered pertained to "ease of use." These problems included mastering the menu driven user interface, visualizing the overall circuit layout, dealing with input inadequacies, and interpreting output data. A short discussion of each of these problems follows.

In order to build the circuit, specify input data and output format, and run the simulation, the user is required to navigate through a myriad of menus which offer options pertaining to these operations. After spending some time working with the program it becomes apparent that these menus are related in a tree-like manner. Movement through the menus consists of no more than moving up and down this tree. Although it is easy to get lost, upward movement (i.e., repeatedly exiting the present menu) will eventually return the user to the root where circuit manipulation and simulation may be started again. After running a number of simulations, the user should be able to learn this menu mechanism well enough to accomplish his objective. However, the primary audience envisioned for LOGSIM248 is the academic (collegiate) arena. Here students will be expected to

quickly master the various tools of the laboratory and may not have the necessary time to become thoroughly familiar with the complexities of this intricate menu system.

Another difficulty noted during the "hands-on" phase was the inability to visualize the circuit during construction. The user is first prompted for an IC package type and identification number, after which, more prompts for all connections to this package are presented, pin by pin. After entering data for a particular chip, the user may start over at the first pin of the present chip or request chip data previously entered. Here he may either check or correct circuit data. This accomplishes the objective of configuring the circuit, but makes it difficult to visualize the circuit as it is created. If the user were able to see a graphic image of the circuit design as it was being created, comparisons could be made directly to design support material to insure correct entry of circuit data and to visualize IC layout and pin orientation.

Simulation output also has a presentation problem. All requested output data are presented in columnar fashion. Each clocked output data set appears on consecutive rows in the display, resembling a truth table. These data sets may include input streams, output streams, and/or any other pin values, all of which may be viewed at the same time for a particular clock pulse.

For some circuit designs, the individual input/output data streams are better viewed with the data presented from

left to right. This is especially true when performing various waveform analyses. Some sort of waveform display option would give the user the ability to see input/output relationships in a different, and, perhaps, more usable format.

It was during this phase of the analysis that circuit input limitations were discovered. After designing a three stage binary ripple counter which only requires power, ground, and clock values as input to the circuit, LOGSIM, version 5.5, would not allow the simulation to proceed because no external input streams had been supplied. Additionally, the program provided no apparent means of presenting power, ground, or clock values as part of the output display. This problem, discussed in Chapter 3, prevents the user from comparing output values with the system supplied clock, and requires some sort of external input even for those circuits which do not require it.

This "hands-on" phase of the LOGSIM, version 5.5 analysis showed the simulator to be a useful, but sometimes confusing tool which presents simulation output in a manner that could prove difficult to analyze by the less experienced designer (i.e., first year design students).

The second part of the LOGSIM, version 5.5 analysis consisted of the inspection and analysis of the source code produced by Captain Rowe (6). Although some documentation did exist, a great deal of time was required to organize,

analyze and understand the various modules which comprised the simulator program.

The following are the major software engineering deficiencies discovered during this phase:

- (1) A 15 page report and 12 pages of block diagrams are all the design documentation that accompanies over 4,500 lines of code. Although each procedure and function contains a header block listing a small amount of information about the function of that procedure, little to no comments can be found in the code.

- (2) Some procedures contain as many as 500 lines.

- (3) Block indentation is inconsistent creating confusion in source code structure.

- (4) Global coupling is prolific throughout the program. This type of coupling requires a large amount of globally declared variables and wasted memory space.

- (5) Because TURBO Pascal, version 3.0, allows executable files to occupy no more than 64 Kbytes of storage (due to 16-bit addressing limitations), and because of the size of the simulation program, overlay files were needed to allow the entire program to be compiled and run within the 64 Kbyte limit.

Because of these deficiencies, maintenance, modifications, and/or upgrades to this source code would certainly be difficult. The need for re-engineering was apparent, in spite of the requirement to integrate a reengineered simulator into IDIET. Toward this end, all user interface modules needed to be stripped from the existing code, data structures rebuilt to accommodate the IDIET interface, all modules translated into the C programming language, and a great deal of documentation supplied.

The C programming language was chosen for a number of reasons. The user interface to IDIET is also written in C in order to use the underlying graphics package. For uniformity and future maintenance/upgrade reasons, C was also chosen for LOGSIM248. As stated earlier, the Pascal version of LOGSIM was not entirely compatible, i.e., this version was not supported by Intel 80286 micro-computers (Zenith 248, IBM AT, etc.). By using the C programming language (in particular TURBO C) compatibility among more computers was expected. In addition, the Intel iPSC Hypercube does not support any version of Pascal, but does support the C programming language. In order to complete the concurrent version of LOGSIM on this computer system, re-hosting the simulator in C was necessary.

4.3 Design - LOGSIM248

LOGSIM248 easily decomposes into four distinct functional areas:

- (1) circuit configuration

- (2) input data structure configuration

- (3) circuit simulation

- (4) output file construction.

LOGSIM248 has been designed with these four functional areas as the initial decomposition. Four input files (see section 3.2.2) are created by the user interface module of IDIET and are used to communicate data between the user interface and the simulator. These four files are the only input or control structures required by LOGSIM248. Output consists solely of two output data files. These two files are supplied to the user interface for screen presentation. Data flow diagrams and functional decomposition block diagrams illustrating the design methodology for LOGSIM248 are contained in Appendix B. The data flow diagrams (SADT diagrams) depict information flow and the transformations that are applied as data moves from input to output (10:99). These diagrams decompose the simulator into the various activities which occur during program execution. The functional decomposition block diagrams show the actual decomposition used while writing the source code. Data flow

diagrams help to visualize those transformations that input data undergoes during program execution. These diagrams are immediately translatable into the functional decomposition.

As discussed in Chapter 3, three data structures are the primary objects used by the simulator. Each of these is a circularly linked list configured with a dummy header node. These data structures are used to store and maintain the circuit configuration data, input data, and output data. The linked lists used in LOGSIM248 differ from the corresponding data structures used in LOGSIM, version 5.5, in three ways:

- (1) All three list are circular. Resetting an index to the beginning of the list is not required for iterative processes that repeatedly traverse the entire list. The index is properly positioned at the beginning of the linked list after completion of each iteration. LOGSIM, version 5.5, uses nil terminated lists that required re-initialization after each traversal. This may not be time effective -- especially for those procedures that must traverse the linked lists repeatedly.

- (2) LOGSIM, version 5.5, is designed to build an input linked list early in the simulation which contains the entire input stream for all inputs specified by the user. This requires the use of a

great deal of memory (especially for those simulations which required large amounts of input data) due to the manner in which TURBO Pascal allocates dynamic memory. If the input data streams are large, and the circuit configuration linked list (already created) is also large, internal memory could easily be exhausted before all data structures are completed. If memory does become exhausted, LOGSIM, version 5.5, contains a routine which stores incomplete data structures on disk. When the simulation is run, this incomplete information must be swapped in and out of memory, as needed. This system does work, however, it is obvious that a time penalty for this file I/O will be incurred.

LOGSIM248 uses a different strategy for input data. As the simulation progresses only the dataset required for the clock pulse currently being simulated is stored in memory. This input data linked list is updated with new data for each clock pulse of the simulation. Here, less memory is used and the traversal of the present input data set linked list requires less time.

(3) The output data list in LOGSIM248 is also a linked list which contains the output monitoring points (as specified for TEMP.DIS in Table 1)

followed by the output data stream. This data stream is built one element at a time as the simulation progresses through each clock pulse of the input data list. After the simulation is complete, the monitor points are reformatted (as shown for TEMP.OUT and TEMP.WAV in Table 1) and the reformatted output points are written to both TEMP.WAV and TEMP.OUT followed by the output data stream (in waveform and binary format, respectively).

LOGSIM, version 5.5, writes each output data set to the requested I/O device (disk, screen, printer) as it is created. A large time penalty is incurred, especially when writing output data to a disk, due to disk spin-up and seek time.

All coupling between functional modules has been improved. Most modules are simply data coupled. The problem of global (or common) coupling, discussed earlier has been almost completely eradicated. Only three global variables are used, each of which is a pointer to the three data structures explained above. These global variables are available for manipulation by any module in the program.

Another problem of LOGSIM, version 5.5, noted above, is the length of the procedures. Many of these procedures exhibit cohesion problems. Too many functions are

accomplished within one procedure making it difficult to understand the purpose of each module. All of the functions defined by the decomposition for LOGSIM248 are designed as single-function modules. This functional form of cohesion enhances understanding of each module and improves maintainability.

These improvements in both coupling and cohesion are evidenced in the functional decomposition illustrated in Appendix B. Excepting the three global variables which are used throughout the program to point to the three linked lists, all data required for each module is passed when that module is called. The arrows associated with links between blocks illustrate both control (solid head arrows) and informational data which is passed between functional modules. This is indicative of good data coupling. As can be seen, all modules present this form of coupling, or (in the case of no passed data) no coupling at all. The improvements in functional cohesion (i.e., each module performs one function) is indicated by the module names, but is better seen in the source code itself (Appendix A).

4.4 Coding ~ LOGSIM248

All source code for LOGSIM248 is contained in six separate files (see Appendix A). These files can be directly correlated to the decomposition referred to in the previous section and are organized in a functionally cohesive manner.

- logsim.h: This is a header file which contains all constant declarations and data structure type declarations used in the program modules.

- simlib.c: This file contains low level functions used throughout the program to perform parsing, data type conversions, random number generation, etc..

- exec.c: This file contains the function main() and all debugging functions. This file also contains the error handler used throughout the program.

- makeckt.c: This file contains all functions associated with the construction of the circuit configuration linked list. Here the TEMP.CKT file is read, all circuit connections parsed from this file, and all circuit information plus initial pin values stored in the circuit configuration list.

- simio.c: This file contains those functions associated with the initialization and maintenance of all input and output data structures. Additionally, those functions used to construct the output files, TEMP.OUT and TEMP.WAV, are contained in this file.

This file contains the heart of the srun.c: simulator program. Here pin values of those IC packages contained in the circuit configuration linked list are updated for each clocked input data set, after which each IC is "operated" to produce new output values at the output pins. Oscillating circuit conditions are also detected here. - configic.c: This file contains all chip configuration functions and an executive function which chooses the appropriate configuration function. These functions are called by the makeckt.c module upon initialization of a new node in the circuit configuration linked list. These nodes represent a single IC package in the present circuit design. After adding the node to the list, each field of the structure is bound to initial values for the corresponding IC by functions in this file.

- opic.c: This file contains all those functions required to operate the IC packages used in the circuit configuration list. These functions perform the appropriate boolean, arithmetic, and other assorted TTL operations for those IC's presently contained in the simulator IC library.

All modules included in the above source code files (with the exception of configic.c and opic.c) contain an average of nine functional statements apiece. Because these modules are functionally cohesive they are designed and coded to perform one function. The modules used for IC configuration and operation also perform a single function. However, due to the requirement for functional completeness, some of these are substantially longer.

Optimization of source code was attempted, wherever possible. Register variables were used for counters and loop indices to insure rapid incrementing. Increment and decrement operators (++ and --), and pointer arithmetic were used wherever possible to speed up these operations. To insure greater maintainability, a great deal of modularization was achieved. This was expected to detract from the overall speed of operation due to the stacking operations of local variables at each function call. Statistical analysis of the comparative speed of LOGSIM248 to LOGSIM, version 5.5, however, does not bear this out (see section 6.1).

#### 4.5 IDIET Integration

After successful compilation and limited testing of LOGSIM248, integration of the simulator into the digital design tool, IDIET (Integrated Digital Engineering Tool)

became the next goal. Here, not only were design and code considerations important, but insuring a productive working environment for all project designers became the dominant theme. Prior to the start of the individual component projects, the three project designers (graphic user interface, connectivity checker expert system, and simulator program designers) agreed on a set of specifications for all interface requirements. Due to unforeseen difficulties during each individual's design and coding phases, these specifications sustained a small amount of modification. Through good communication of modified requirements, all interface changes were effected painlessly. The resulting specifications are contained in the file formats for those files listed in Table 1.

At this point it was decided that the production of a waveform output (TEMP.WAV) would be more easily accomplished by the simulation program and the required additions to LOGSIM248 were incorporated into the source code file containing all I/O modules (simio.c). Additionally, due to memory constraint problems with the host computer, it was not possible for all three programs to remain resident at the same time. Therefore, a small executive program was created to run the graphic interface and simulation components independently of the expert system.

4.6 Testing and Debugging - LOGSIM248

As with any software engineering project, finding test cases which test the proper conditions and provide results which can be used to evaluate program performance was a difficult task. The test cases used were grouped into three separate classes.

The first class consisted of circuit designs used during the development phase of the project. These designs needed to be simple enough so that time was not wasted implementing them but large enough to insure some measure of proper performance.

The second class of test cases consisted of those circuit designs implemented during the testing phase of the integrated design tool, IDIET. These cases consisted of circuit designs which taxed the power of the simulator and provided measurable performance indicators used for debugging and performance enhancement.

The third class of test cases consists of circuit designs created by those students of the Air Force Institute of Technology chosen to field-test the digital design tool as a whole. These circuit designs, along with the inexperience of the users, were expected to provide a myriad of insights into software design flaws for all aspect of the design tool.

Because of the combinatoric explosion involved with testing circuits which use all IC's contained in the IC library, more emphasis was placed on the execution of those

modules involved in circuit configuration, input/output specification, and simulation execution. All functional modules (excepting those modules contained in configic.c and opic.c) were completely tested using dummy stubs at each stage of the coding phase.

Because of limitations of the graphic user interface, circuits comprised of more than 10-12 IC packages are difficult to create with IDIET. The size of the screen prohibits larger circuits with many connections. As the circuit grows, the screen takes on the appearance of a "rat's nest" and becomes impossible to sort out connections for debugging or modification. Subsequently, the four test cases used during the IDIET testing phase contain 3-6 IC packages with 20-75 connections between packages. This proved to be a manageable circuit size through which productive program debugging could be accomplished.

The four test cases used are (1) a binary coded decimal encoder, (2) a two-bit full adder, (3) a three stage binary ripple counter, and (4) a 3 by 8 decoder. Schematics and graphic screen images of these circuits are contained in Appendix D.

The Digital Circuit Design class of the Air Force Institute of Technology was chosen to perform user "hands-on" testing of IDIET. Their first assignment included the design of a Binary Coded Decimal to Excess 13 encoder. All students

easily mastered the design tool, producing results which either confirmed their designs or indicated circuit flaws. No appreciable negative comments were made with regards to LOGSIM248. More user testing is forthcoming and will be used to upgrade and/or maintain the system.

#### CHAPTER 5 - CONCURRENT LOGSIM

#### 5.1 Overview

Although applying concurrent processing techniques to a digital circuit simulator like LOGSIM248 would appear to be advantageous in producing improved performance, other factors peculiar to this implementation need to be considered. The most practical way to produce LOGSIM248 test cases which can be verified as correct is to use the integrated design tool, IDIET. After configuring and simulating a digital circuit, all relevant files (containing circuit configuration and input/output data) used during the simulation may be saved for further study. These files contain all data required to recreate the circuit, provide input and output specifications, and simulate circuit performance (see Chapter 3). It would be impractical to compare the performance of the LOGSIM248, divorced from IDIET, to a "parallelized" version designed on a concurrent processor due to those difficulties involved with independent use of LOGSIM248 (see Chapter 6).

IDIET, however, presents some limitations which may devalue the implementation of a concurrent LOGSIM248. The most obvious of these limitations is the inability to produce circuits (using IDIET) large enough to tax the speed of the

host computer -- the Zenith 248 (see section 6.1). Test cases designed with IDIET, which were constructed from only six IC packages, began to clutter the graphic design area of the screen. With careful planning, and judicious use of the graphic design area, circuits consisting of nine or ten separate IC packages represent the upper limit of workable circuit size using IDIET. However, based on the statistics produced for test cases used during program implementation (see section 6.1), it is not envisioned that circuits of this size would produce time delays of any consequence. It is obvious from those statistics, however, that simulation speed is inversely proportional to circuit design size. Thus far, circuits designed using IDIET have not slowed the system. So, how slow is <u>too</u> slow?

The primary purpose of concurrent processing is to reduce the time complexity limitations of sequential computers for large, CPU intensive problems by employing multiple CPU's, all working concurrently on decomposed areas of a compound problem. As stated in Chapter 2, digital circuits are, by their very nature, parallel constructs that would appear to conveniently lend themselves to concurrent applications. However, the trade-off between time savings and computing cost must be considered, especially if no inconvenience is perceived by a sequential implementation. At this writing, IDIET stands as an integrated system whose capabilities are limited in such a way as to present no such time inconvenience.