ARO 18790.17-EL

APR 3 0 1986

E

86

# TOPOLOGICAL PROPERTIES OF INTERCONNECTION NETWORKS FOR PARALLEL PROCESSORS

Ph.D. Thesis by: Robert R. Seban

Faculty Advisor: Howard Jay Siegel

Appendix E for

Distributed Computing for Signal Processing: Modeling of Asynchronous Parallel Computation Final Report

> U.S. Army Research Office Contract No. DAAG29-82-K-0101\*

\*Chapters 1 through 8 supported by this contract.

This decement has been approved for public release and sale; He distribution is unlimited.

### TOPOLOGICAL PROPERTIES OF INTERCONNECTION

### NETWORKS FOR PARALLEL PROCESSORS

- A UNIFIED APPROACH

A Thesis

Submitted to the Faculty

of

**Purdue University**

by

Robert R. Seban

In Partial Fulfillment of the

**Requirements for the Degree**

of

Doctor of Philosophy

December 1985

This document has been approved for public release and sale; its distribution is multiclied.

### ACKNOWLEDGMENTS

I would like to thank my major advisor Professor H. J. Siegel and my committee members Professor E. J. Coyle, Professor S. E. Hambrusch, and Professor D. G. Meyer for their time and effort.

Chapters 4 and 5 were supported in parts by the U.S. Army Research Office, Department of the Army, under contract number DAAG29-82-K-0101. Chapters 6, 7, and 8 were supported in parts by a David Ross Grant 1984-1985, under contract number 0857-56-12855, and by the U.S. Army Research Office, Department of the Army, under contract number DAAG29-82-K-0101. Chapter 9 was supported by IBM Federal Systems Division, under contract number 289662B-YD. Chapter 10 was supported in parts by National Science Foundation Grant under contract number ECS-8120896.

### TABLE OF CONTENTS

Page

## ABSTRACT 2 4.7 Systems and Subsystems ......40

### iii

iv

5.2 Overview

63

5.3 Problem Statement

64

5.4 Previous Work

65

5.5 Basic Concepts

65

5.6 Quasimorphism

77

5.7 Emulation of Systems

94

5.8 Conclusions

102

Page

##

| <b>6.2</b> Overview                           |  |

|-----------------------------------------------|--|

| 6.3 Problem Statement                         |  |

| 6.4 Previous Work                             |  |

| 6.5 Basic Concepts                            |  |

| 6.6 Composition and Decomposition of Networks |  |

| 6.7 Partitionability Algorithm                |  |

| 6.8 Conclusions                               |  |

## 7 SINGLE STAGE PARTITIONABLE NETWORKS - SYNTHESIS......134

|   | 7.1 | Introduction                                     | 135 |

|---|-----|--------------------------------------------------|-----|

|   |     | Overview                                         |     |

|   |     | Problem Statement                                |     |

|   | 7.4 | Previous Work                                    |     |

|   |     | Basic Concepts                                   |     |

|   |     | Synthesis of Single Stage Partitionable Networks |     |

|   |     | Conclusions                                      |     |

| 8 | MU  | LTISTAGE NETWORKS - ANALYSIS                     | 152 |

|   | 8.1 | Introduction                                     | 153 |

|   | 8.2 | Overview                                         |     |

|   | 8.3 | Problem Statement                                |     |

|   |     | Previous Work                                    |     |

|   |     | Basic Concepts                                   |     |

|   |     | Multistage Network Model and Applications        |     |

|   |     | Conclusions                                      |     |

|   |     |                                                  |     |

| Pa<br>9.3 Problem Definition                                                                                    | Basic Concepts                                                                                                                     |     |                              | Page |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|------|

| 9.5 DMA - Direct Memory Access1879.6 Architecture of the Fault Tolerant Crossbar1939.7 Network Architectures203 | DMA - Direct Memory Access187Architecture of the Fault Tolerant Crossbar193Network Architectures203Fault Detection and Recovery211 | 9.3 | Problem Definition           |      |

| 9.5 DMA - Direct Memory Access1879.6 Architecture of the Fault Tolerant Crossbar1939.7 Network Architectures203 | DMA - Direct Memory Access187Architecture of the Fault Tolerant Crossbar193Network Architectures203Fault Detection and Recovery211 | 9.4 | Basic Concepts               |      |

| 9.6 Architecture of the Fault Tolerant Crossbar                                                                 | Architecture of the Fault Tolerant Crossbar                                                                                        |     |                              |      |

|                                                                                                                 | Fault Detection and Recovery                                                                                                       |     |                              |      |

|                                                                                                                 | •                                                                                                                                  | 9.7 | Network Architectures        | 203  |

| 9.8 Fault Detection and Recovery                                                                                | Conclusions                                                                                                                        | 9.8 | Fault Detection and Recovery |      |

| 9.9 Conclusions                                                                                                 |                                                                                                                                    | 9.9 | Conclusions                  |      |

C SCOLLER

R.

## 10

| 10.1 Introduction                      |     |

|----------------------------------------|-----|

| 10.2 Overview                          |     |

| 10.3 SIMD Machines                     |     |

| 10.4 The Interconnection Networks      |     |

| 10.5 Shuffling with the PM2I Network   |     |

| 10.6 Shuffling with the Illiac Network |     |

| 10.7 Conclusions                       |     |

| 11 CONCLUSIONS                         | 242 |

| LIST OF REFERENCES                     | 251 |

| VITA                                   |     |

•

200

22.22.22 22.22.22

## LIST OF TABLES

| e                                                           | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comparison of efficiency<br>of different types of emulation | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The multiplication table                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| for $\langle C, \gamma \rangle$ , Example 7.6.10            | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The multiplication table                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| for $\langle C, \gamma \rangle$ , Example 7.6.11            | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The idea underlying the                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| algorithm for the PM2I to perform                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| the shuffle, shown for $N = 8$                              | 229                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of the algorithm for performing the                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • • • •                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\bullet$ , $-$                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                             | 232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                             | Comparison of efficiency<br>of different types of emulation<br>The multiplication table<br>for $\langle C, \gamma \rangle$ , Example 7.6.10<br>The multiplication table<br>for $\langle C, \gamma \rangle$ , Example 7.6.11<br>The idea underlying the<br>algorithm for the PM2I to perform<br>the shuffle, shown for N = 8<br>Example of the algorithm for performing the<br>shuffle using the PM2I when N = 8.<br>It is assumed that initially the DTR of PE P<br>contains the integer P, $0 \leq P < 8$ .<br>The dotted line shows the movement of the data |

## LIST OF FIGURES

| Figu          | re                                                                                                     | Page |

|---------------|--------------------------------------------------------------------------------------------------------|------|

| 4.1:          | An example of a topologically arbitrary network                                                        | 33   |

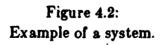

| 4.2:          | Example of a system                                                                                    | 44   |

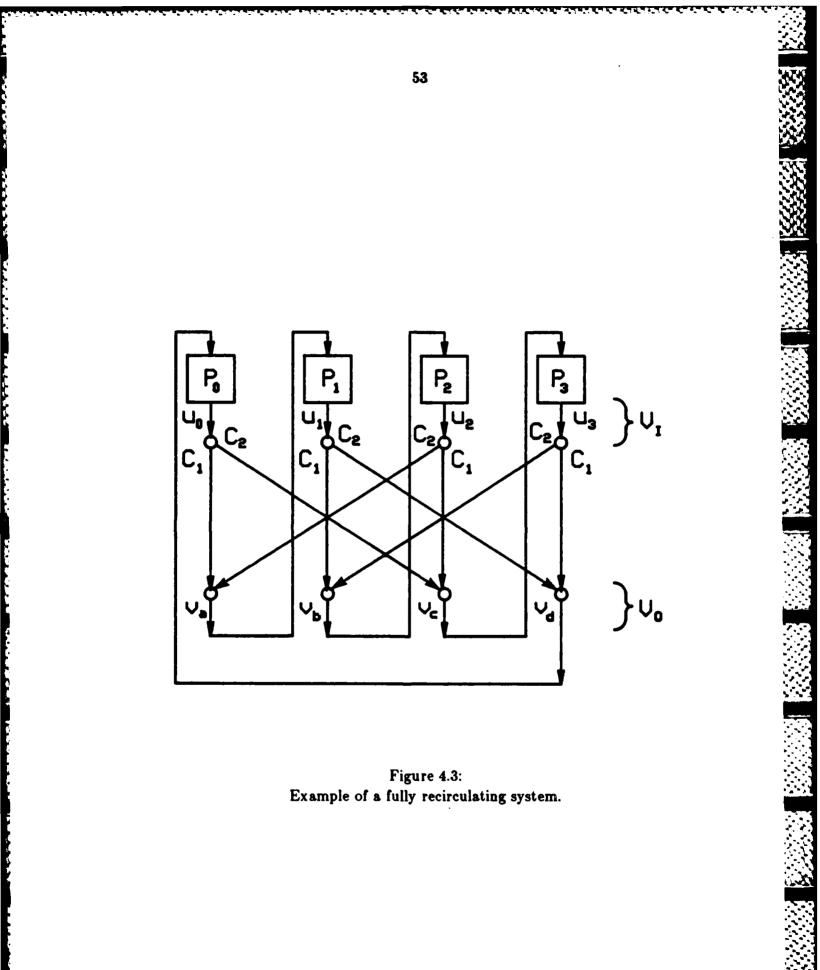

| 4.3:          | Example of a fully recirculating system                                                                | 53   |

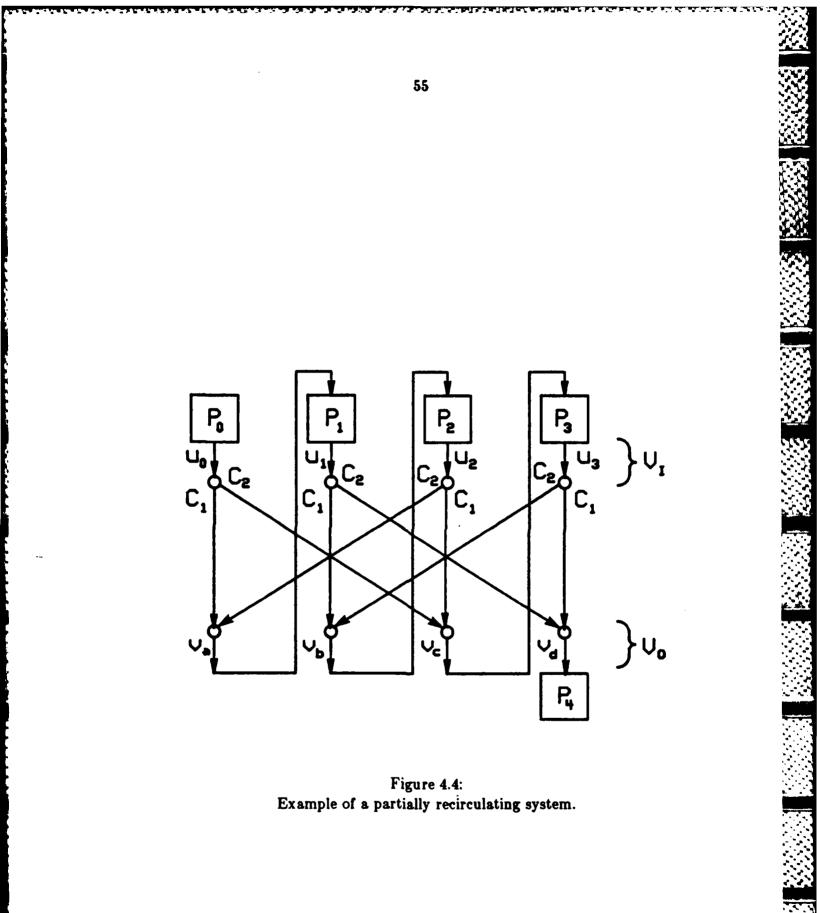

| 4.4:          | Example of a partially recirculating system                                                            | 55   |

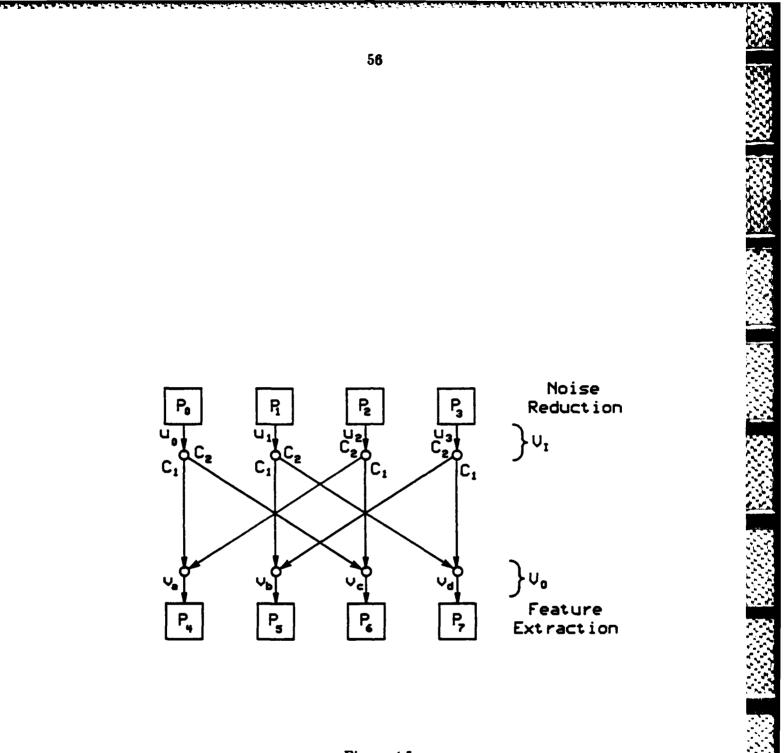

| 4.5:          | Example of a nonrecirculating system.                                                                  | 56   |

| 5.1:          | Genealogy of the maps and correspondences.                                                             | 67   |

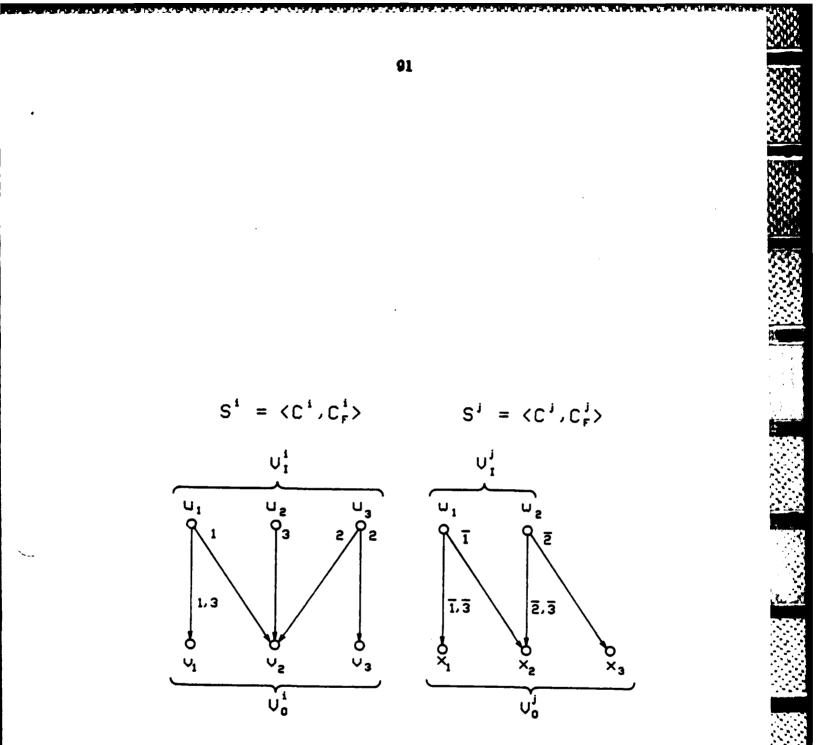

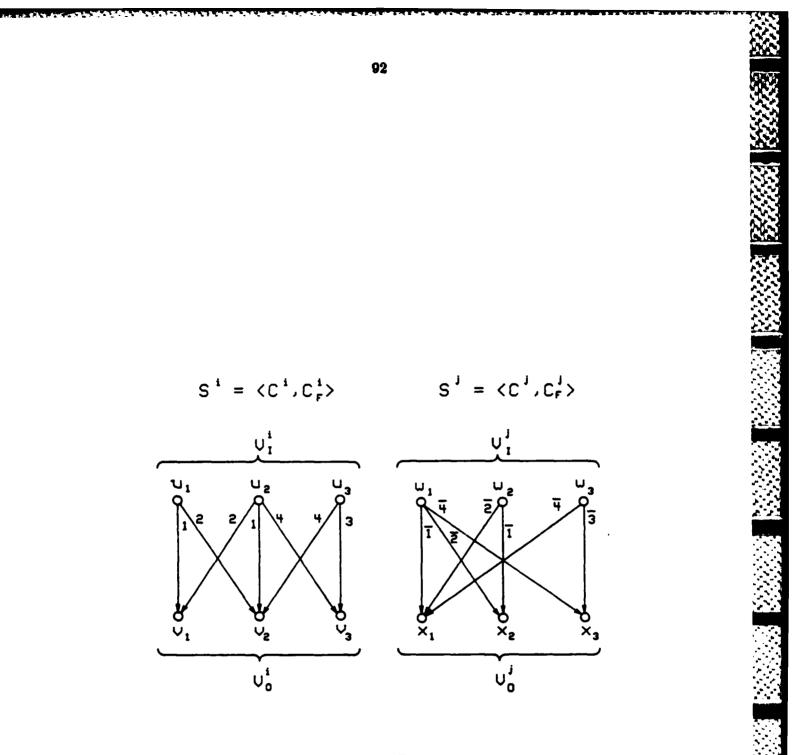

| 5. <b>2</b> : | Systems $S^i = \langle C^i, C_F^i \rangle$ , $S^j = \langle C^j, C_F^i \rangle$<br>for Example 5.6.12. | 91   |

| 5. <b>3</b> : | Systems $S^i = \langle C^i, C_F^i \rangle$ , $S^j = \langle C^j, C_F^i \rangle$<br>for Example 5.6.13  | 92   |

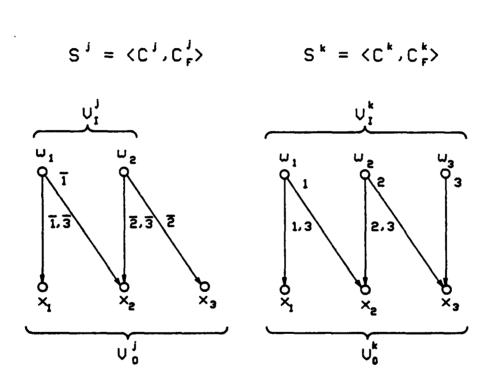

| 5.4:          | Systems $S^j = \langle C^j, C_F^i \rangle$ , $S^k = \langle C^k, C_F^k \rangle$<br>for Example 5.7.3.  | 98   |

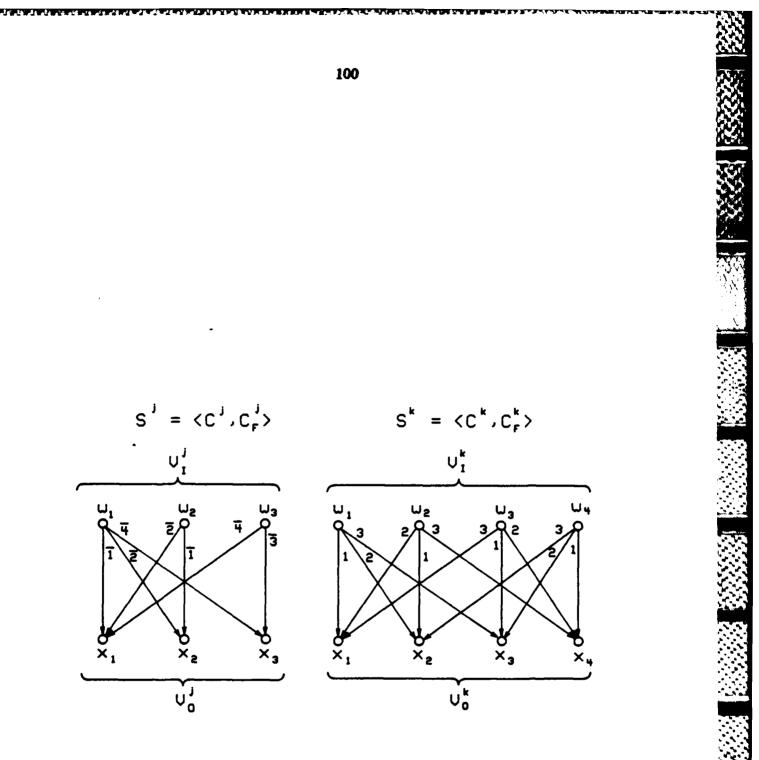

| 5.5:          | Systems $S^j = \langle C^j, C_F^i \rangle$ , $S^k = \langle C^k, C_F^k \rangle$<br>for Example 5.7.4.  | .100 |

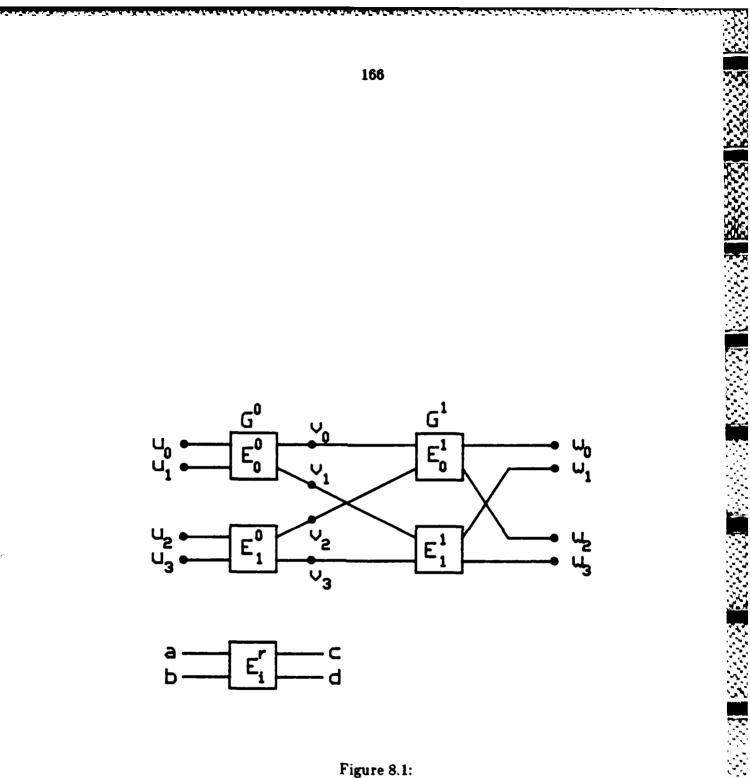

| 8.1:          | Multistage network for Example 8.6.2.                                                                  | 166  |

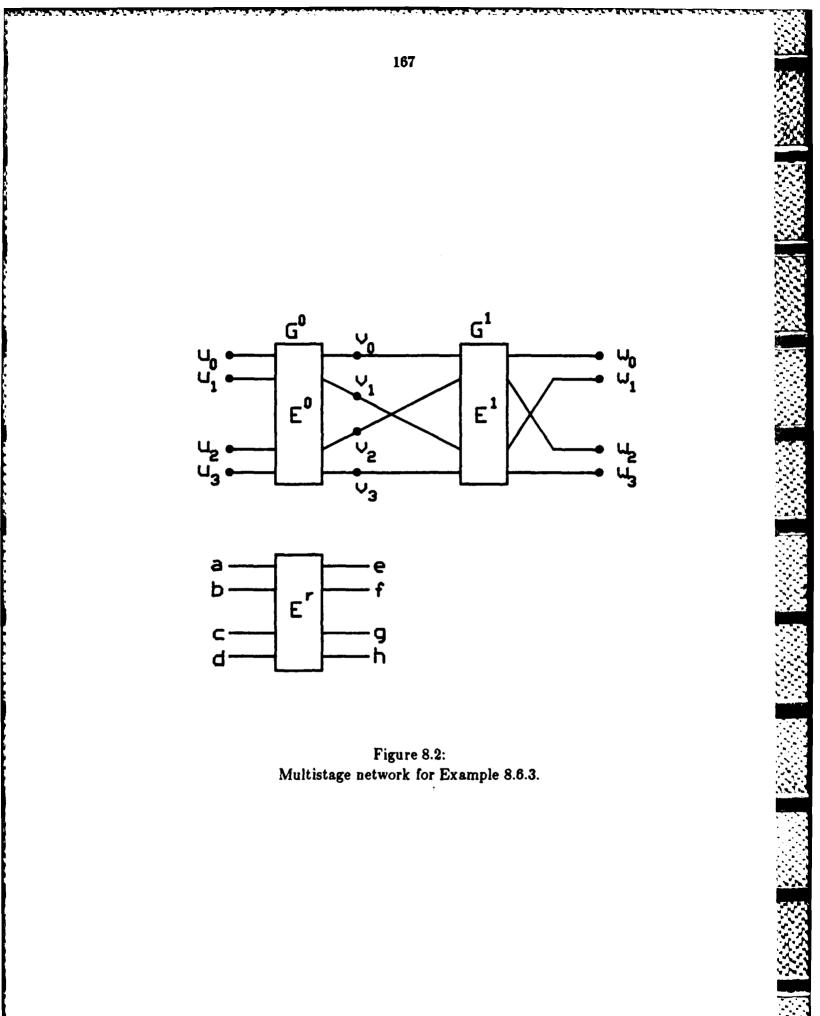

| 8.2:          | Multistage network for Example 8.6.3.                                                                  | .167 |

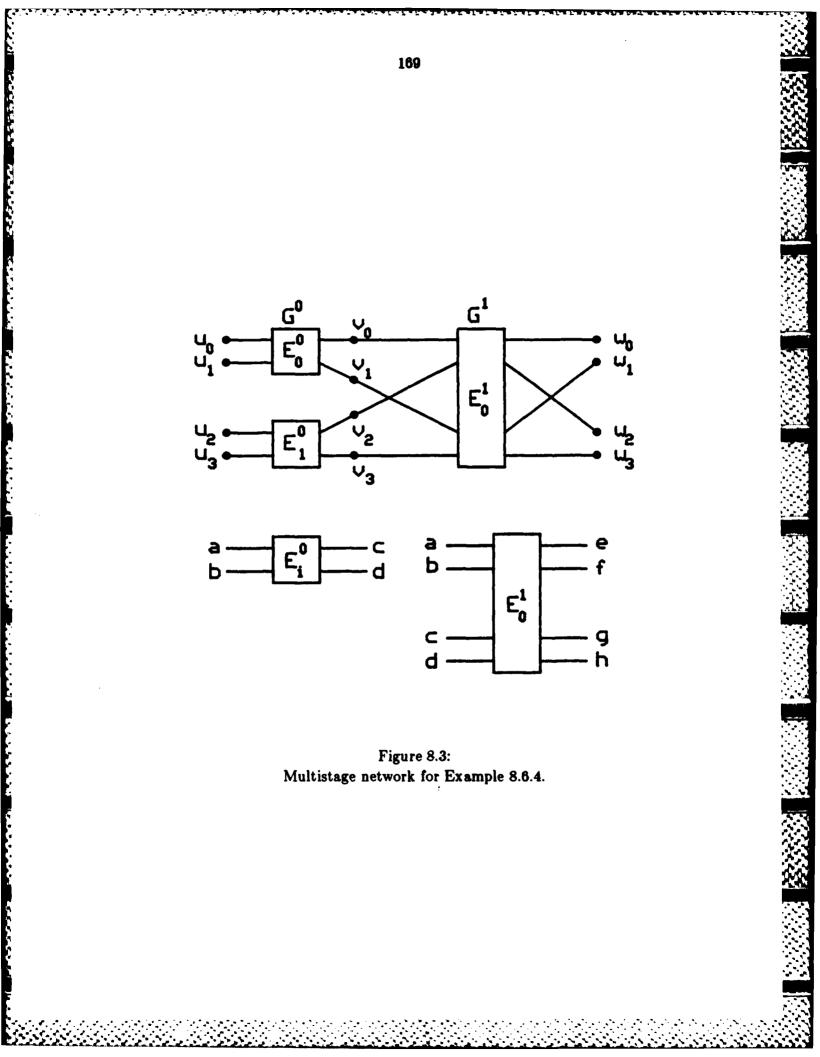

| 8.3:          | Multistage network for Example 8.6.4.                                                                  | .169 |

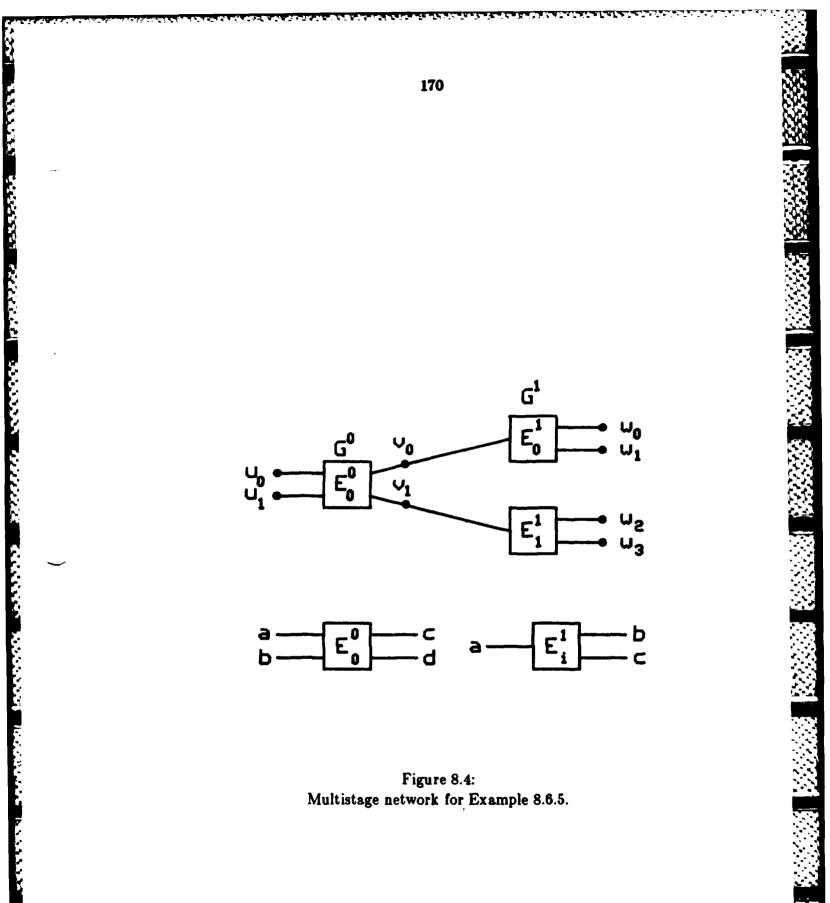

| 8.4:          | Multistage network for Example 8.6.5.                                                                  | .170 |

viii

| Figure<br>9.1: Signal data transfer parameters for                                                                                                                             | e |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| three iterations of an evolutionary distributed<br>processing system                                                                                                           |   |

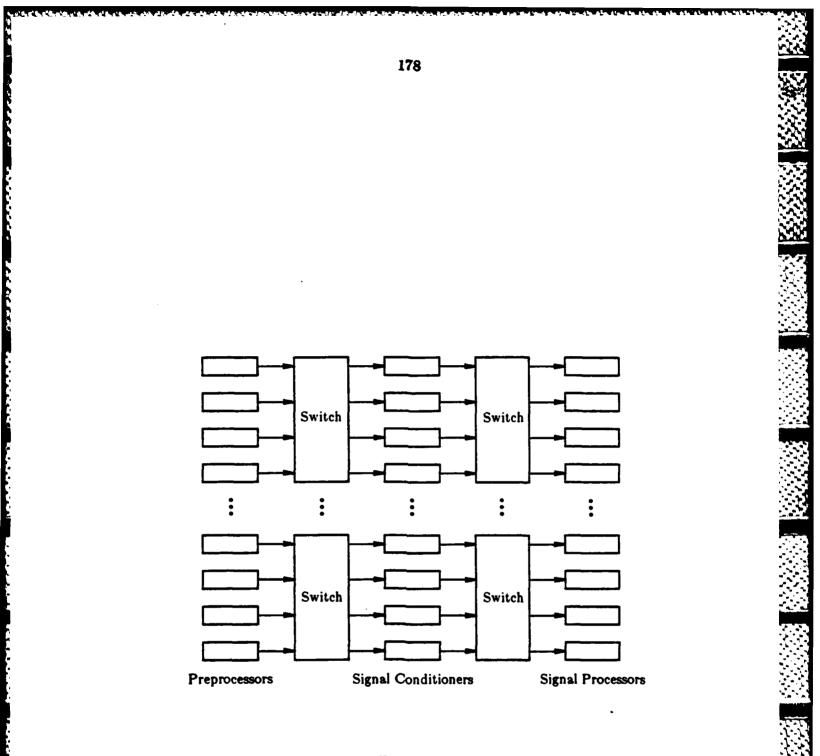

| 9.2: A signal data switching configuration<br>for front end PEs                                                                                                                |   |

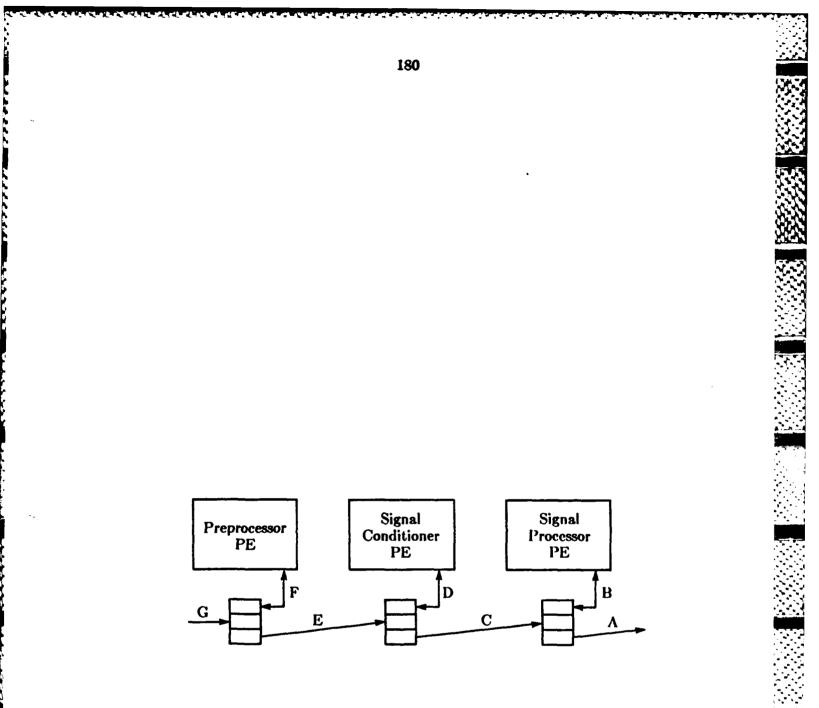

| 9.3: PEs and their associated swinging<br>buffered memories                                                                                                                    |   |

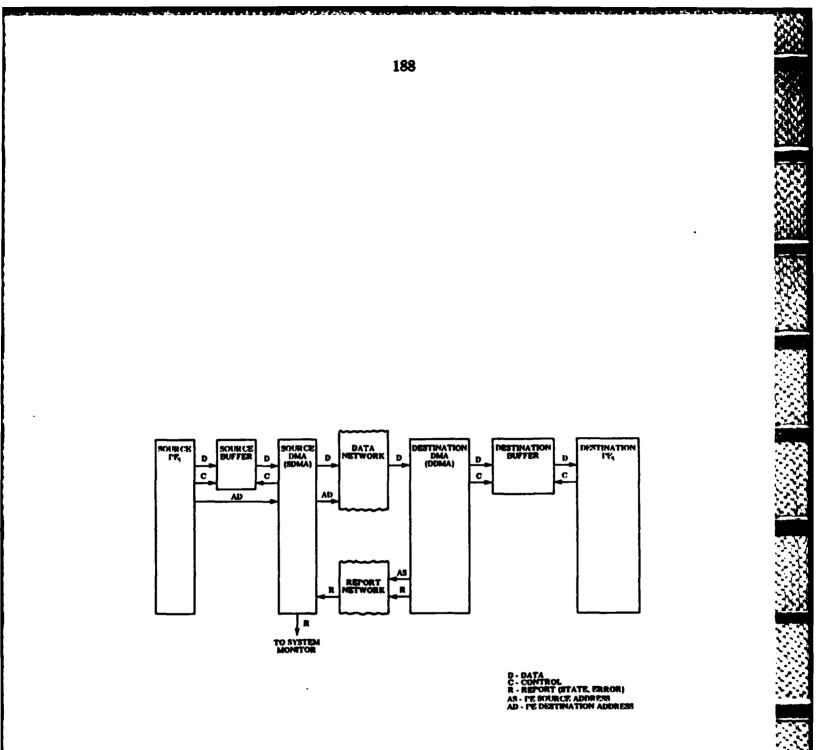

| <ul> <li>9.4: The architecture of the communication system:</li> <li>D - data, C - control, R - report,</li> <li>AS - PE source address, AD - PE destination address</li></ul> |   |

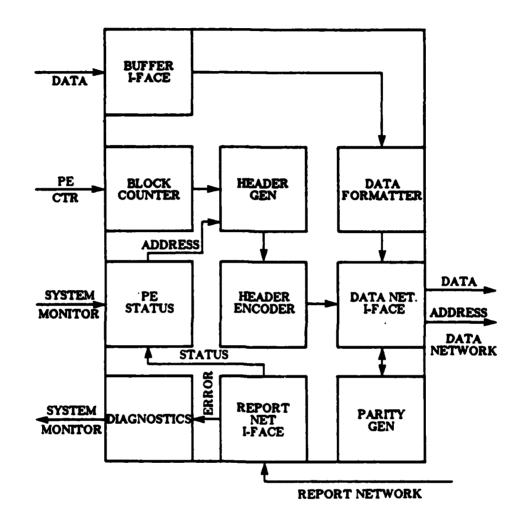

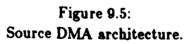

| 9.5: Source DMA architecture                                                                                                                                                   |   |

| 9.6: Destination DMA architecture                                                                                                                                              |   |

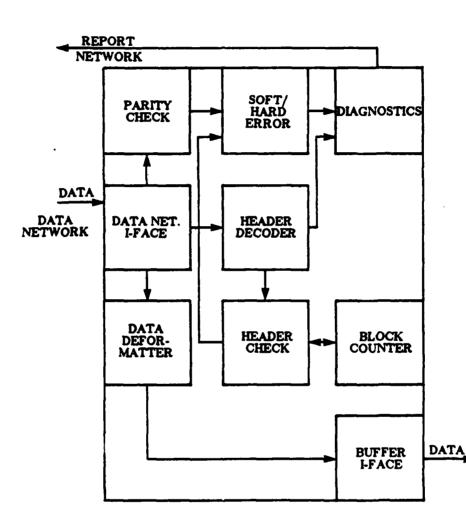

| 9.7: Implementation of a 4×4×8<br>crossbar using bit slicing                                                                                                                   |   |

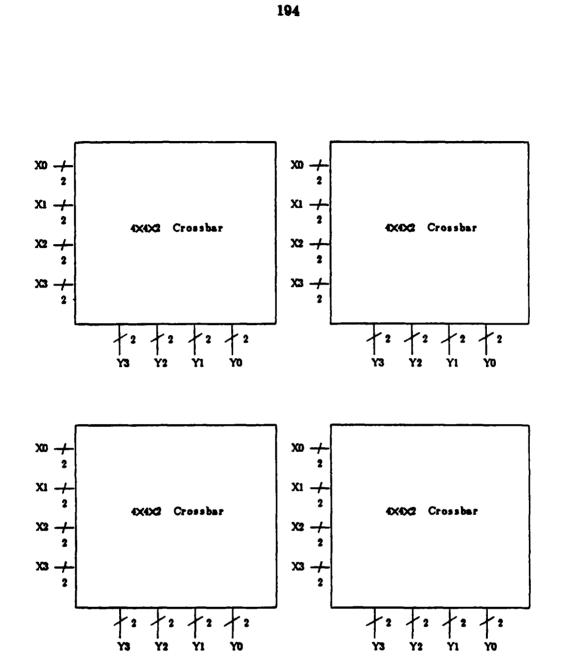

| 9.8: Implementation of a 4×4×8<br>crossbar using cascading                                                                                                                     |   |

| 9.9: Block diagram of a type I chip197                                                                                                                                         |   |

| 9.10: The data path for output port i (DO i)200                                                                                                                                |   |

| 9.11: Block diagram of a type II chip202                                                                                                                                       |   |

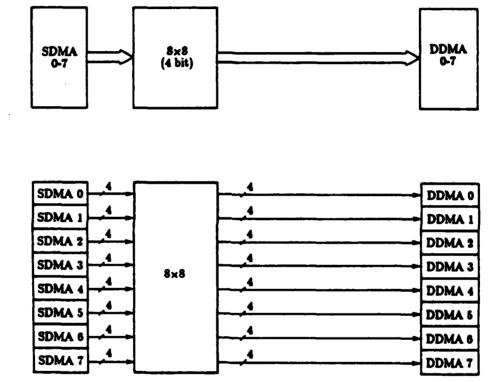

| 9.12: Network architecture scheme 1                                                                                                                                            |   |

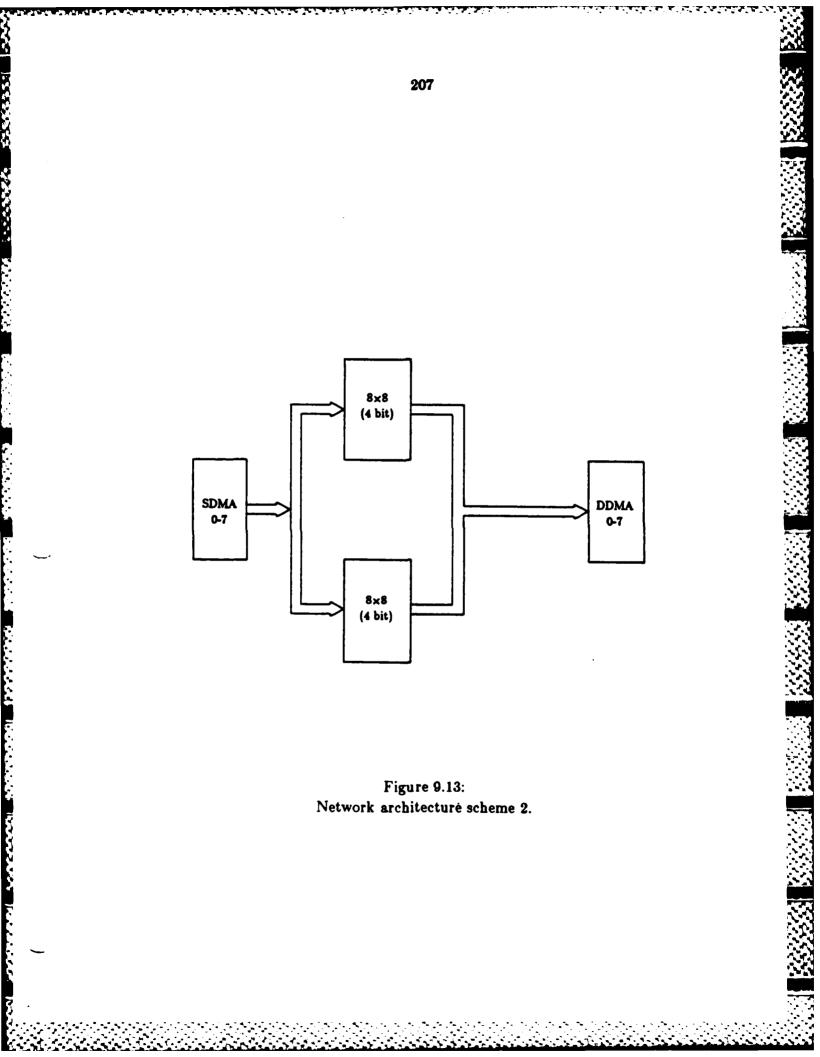

| 9.13: Network architecture scheme 2207                                                                                                                                         |   |

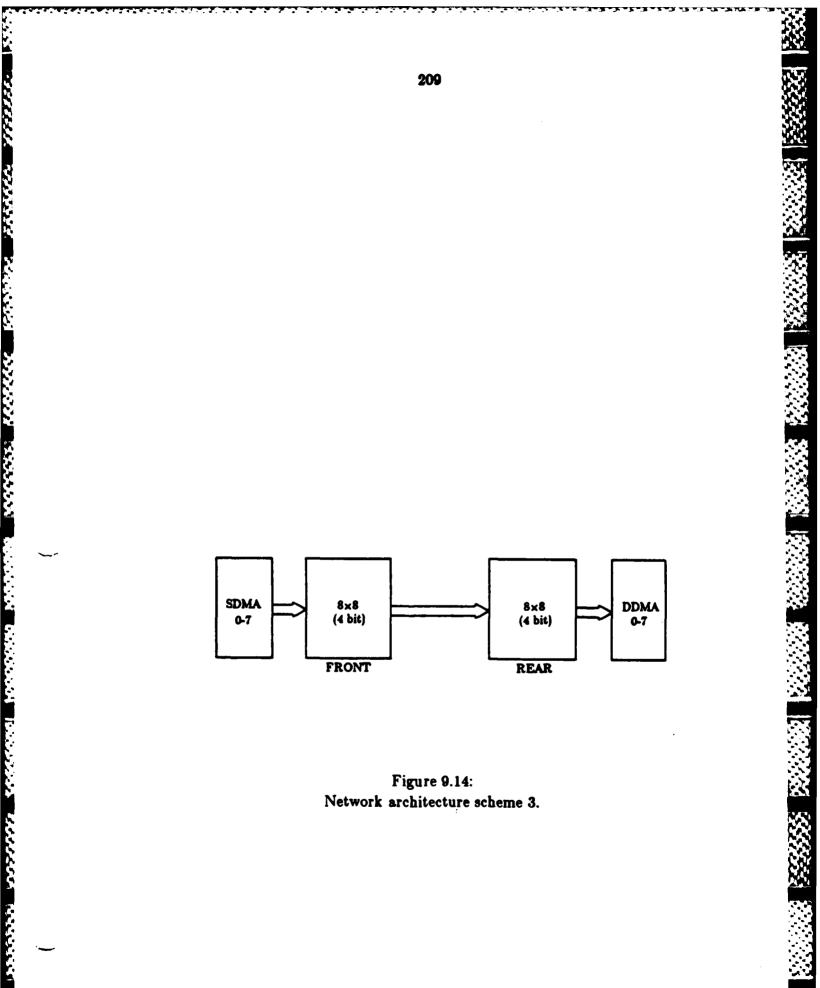

| 9.14: Network architecture scheme 3209                                                                                                                                         |   |

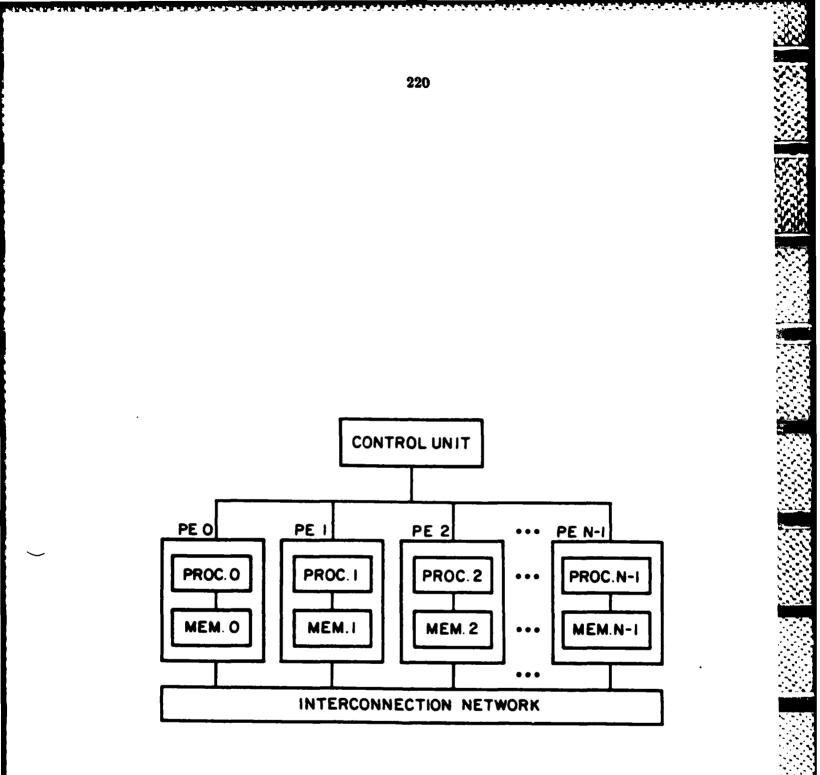

| 10.1: PE-to-PE SIMD machine configuration, with N PEs                                                                                                                          |   |

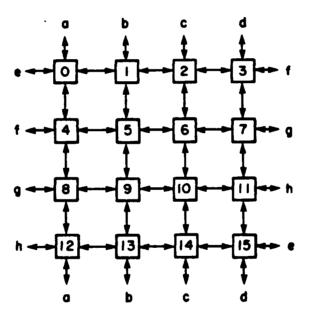

| 10.2: Illiac network for N = 16.<br>(The actual Illiac IV SIMD machine had N = 64).<br>Vertical lines are $+\sqrt{N}$ and $-\sqrt{N}$ .<br>Horizontal lines are $+1$ and $-1$  |   |

| Figure                                                                                                                                                                                                          | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

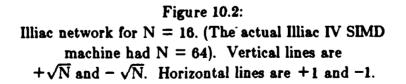

| <ul> <li>10.3: PM2I network for N = 8.</li> <li>(a) PM2<sub>+0</sub> connections. (b) PM2<sub>+1</sub> connections.</li> <li>(c) PM2<sub>+2</sub> connections. For the PM2<sub>-i</sub> connections,</li> </ul> |      |

| $0 \le i \le 2$ , reverse the direction of the arrows.                                                                                                                                                          | 224  |

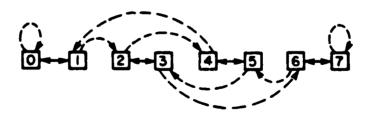

| 10.4. Shuffle Exchange network for $N = 8$                                                                                                                                                                      |      |

#### ABSTRACT

Ph.D.. Purdue University. 1985. Seban. Robert R. December TOPOLOGICAL PROPERTIES OF INTERCONNECTION NETWORKS FOR PARALLEL PROCESSORS -UNIFIED APPROACH. Major Professor: Howard Jay Siegel.

Two methods are used to speed up the execution of a computational task. One is new technology development and the other is the exploitation of parallelism in the computation. To take an advantage of the parallelism in a task requires the utilization of parallel computer architectures. At a certain high level of abstraction a parallel computer system is represented as a graph where the nodes represent processors, memories, or other devices, and the edges represent the communication links.

In this research the following problems of parallel processing are studied. First is a theoretical study of topological properties of interconnection networks. Second is a case study of a network design for a real-time system. Luciy, the use of SIMD networks for performing "shuffles."

A general model that can be used to describe networks and systems with arbitrary topologies is developed. Based upon the of morphism of groups, the concept of morphism of systems is developed. The morphism of systems is called quasimorphism and allows a method of comparison between topologically arbitrary parallel computer systems. The quasimorphism is used to study the emulation of one system by another.

The composition, decomposition, and partitionability of single stage networks are studied. Informally, the partitionability property means that the network can be divided into several parts each with a degree of independence. The synthesis of single stage partitionable interconnection networks is examined. The applications of the model to multistage networks is discussed.

A case study of the design of a network for a real-time signal processing system is performed. A network and network interfaces are designed for a distributed digital signal processing system subject to high throughput, extendibility, fault tolerance, and other constraints.

The data permuting ability of single stage SIMD networks are studied. Specifically, algorithms for the PM2I and Illiac networks to perform the "shuffle" data permutations are developed.

Two methods are used to speed up the execution of a computational task. One is new technology development and the other is the exploitation of parallelism in the computation. To take advantage of the parallelism in the task requires the utilization of parallel computer architecture [KuL78, ThW75]. There are two major classes of parallel computer system architectures, loosely coupled, where the information transfer is infrequent, and tightly coupled, where information transfer is frequent, perhaps every operation cycle. In this research the primary concern is the class of tightly coupled parallel computer systems.

At a certain high level of abstraction a parallel computer system is represented as a graph where the nodes represent processors, memories, or other devices and the edges represent the communication links. This representation is frequently used by researchers and is based upon the belief that one of the salient features of a parallel computer system is the topology of the interconnection network and the way the processors and other devices are connected to it. Although the graph depiction of the system contains large amount of information, it does not convey the dynamic structure of a reconfigurable network. Our model developed in this research embodies that information.

Much research has been devoted to study several topologically regular interconnection networks. Amongst the best known networks are Illiac [BoD72], Shuffle [LaS76], Omega [Law75], multistage Cube [AdS82b], STARAN [Bat76], ADM [McS82], k-connected mesh [NaS80], and PM2I [SeS84b]. The researcher usually proceeded as follows: he devised a model for the network of interest and derived analytical results based on that model. This approach has

the drawback that the results are network specific since the model is network specific and sometimes implementation dependent.

Our research differs from the past work in several aspects. First, a unified approach to the analysis of interconnection networks that is valid for large classes of interconnection networks was developed. Second, several algorithms that allow systematic analysis and design of networks with the desired property of partitionability will be developed. In more detail, the following related topics of topological properties of parallel computer systems will be studied.

AND ADDRESS AND AND ADDRESS ADDR

BARADAN BARADARA INGGARAD RAYANNA BARADARA ING

In Chapter 3, the background of parallel computer architecture is presented. Numerous parallel computer systems have been discussed in the literature and proposed, and several have been built. Parallel systems are divided into two major classes, tightly coupled and loosely coupled. The subject of analysis here is the tightly coupled parallel systems group which can be divided into several categories.

L is shown that each type of parallel computer architecture requires one or more interconnection networks. Some systems use networks dedicated to the communication between particular subsystems, some other systems use a single network multiplexed for communication among different parts of the system. In an ensemble parallel system the network is used by the control unit to broadcast instructions and data [ThW75]. In a pipelined system the interconnection network is used to provide data communication among the computational units (segments) of the pipeline [Bae80]. In vector and array parallel system one network is used for interprocessor communication and a usually separate network is used by the control unit to broadcast data, instructions, and control information to the processors [BaB68]. In a systolic system the network is used to propagate the wave of partial results from a set of processors to the next set of processors [KuL78]. In an associative system the control unit uses the network to broadcast selected data fields to the processors for comparison, and in some cases another network is used for interprocessor communications [Bat74]. Reconfigurable systems have a network that allows the system to be statically or dynamically restructured into multiple machines of different sizes [SiS84]. A data flow system consisting of multiple rings needs a communication network to move data among rings [WaG82].

In Chapter 4 a general model of single stage interconnection networks is developed [SeS84a]. This model is sufficiently general so that it can be used to model networks with an arbitrary topology, including both regular and irregular topologies. The model is independent of the method of implementation of the network. This is necessary because properties of networks such as similarity relationships, emulation, and partitionability of networks are implementation independent.

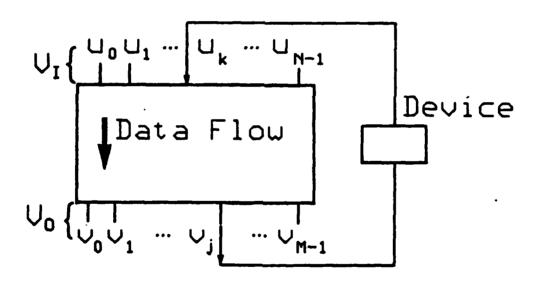

The model together with additional information is then used to construct a model for parallel computer systems. A system, informally, consists of a set of devices, an interconnection network, and a method for use of the network. Each device is assumed to have two logical ports, an input port and an output port, possibly implemented physically as the same set of I/O pins. Some examples of devices are processors, memories, or processor/memory pairs. Based upon the use of the network, three types of systems, recirculating, nonrecirculating, and partially recirculating, are defined. Relationships between systems such as equality and three types of subsystems are rigidly defined and their properties explored.

In Chapter 5 a technique is developed to measure the similarity of two systems. This generalizes the past work on similarity used by many researchers which classifies the relationships between two networks into two kinds only, (a) the networks are isomorphic or (b) the networks are not isomorphic. The measure has a number of uses and is applied in this chapter to the analysis of emulation. Our definition of emulation is a generalized case of the one described in [FiF82].

Previous work, related to our research developed here, can be found in the classification of groups in the field of abstract algebra and group theory [Han68, Her75]. The theory of group classification is based upon the concept of morphism. Morphism measures the similarity of behavior between group operations of two groups. This measure ignores the labeling of the elements of the groups and is concerned strictly with the structure which is determined by the group operation.

Based upon the idea of morphism of groups, the concept of morphism of systems is developed [SeS84a]. In the domain of parallel computer systems the structure of interest is the structure of the correspondences of the system's network in the graph theoretical sense. The morphism of systems is called quasimorphism and allows a method of comparison between topologically arbitrary parallel computer systems. The quasimorphism facilitates the analysis of following problems in parallel processing: system emulation, multiple mapping of a problem into a system for increased reliability, and partitioning of systems. The quasimorphism is analyzed with respect to properties similar to the properties of reflexivity, symmetry, and transitivity.

Also in this chapter the problem of emulation of one system by another is discussed. Three different types of emulation are considered. Several efficiency

measures of the emulation were defined and the three types of emulation were evaluated using these criteria.

In Chapter 6 the composition, decomposition, and partitionability of single stage networks are studied [SeS85]. Informally, the partitionability property means that the network can be divided into several parts each of which has certain degree of independence. The type of partitionability analyzed in this chapter has three subtypes.

The partitionability property of interconnection networks in the context of parallel computer systems has the following advantages, besides being interesting from the theoretical point of view.

- (1) If the network is partitionable then the resource allocation of only a subset of the total resources is possible. This can be used as follows.

- (a) A user can utilize only a small part of the machine for program development phase.

- (b) In a multiple user environment the partitioning provides a natural protection among users.

- (c) In a multitasking environment the partitioning provides a protection among independent tasks.

- If the network is partitionable, the fault tolerance of the system increases as follows.

- (a) A method of graceful degradation is possible by separating the faulty section from the correctly operating ones.

- (b) If in addition to being a partitionable network, the sections are isomorphic, then an increase of reliability may be realized by multiple mappings of the same task onto the multiple sections and tandem

cross checking of partial results.

- (c) It is possible to construct a link and switching element fault tolerant network using a partitionable network as a core.

- (3) If the network is partitionable, then there is an efficient implementation in terms of hardware and control. The network can be implemented as a set of network components each with its own set of inputs and outputs. Consequently the data path layout and in some instances the control lines layout on VLSI chip or on a printed circuit board can be simplified.

An algorithm to classify partitionability of interconnection networks is developed which will output one of the following:

- (1) The network is not partitionable.

- (2) The network is partitionable into subnetworks with common control signals and the combination of the of the subnetworks will exactly generate all interconnection patterns of the original network.

- (3) The network is partitionable into subnetworks with separate control signals and the combination of the subnetworks will exactly generate all interconnection patterns of the original network.

- (4) The network is partitionable into subnetworks with separate control signals and the combination of the subnetworks will generate a superset of interconnection patterns of the original network.

The algorithm is general in the sense that it will accept as an input a topologically arbitrary interconnection network.

In Chapter 7 the synthesis of single stage interconnection networks with the partitionability property is studied. Several different techniques are developed, each of which can be used to construct a large class of single stage partitionable networks. The algorithms are presented for a simplified case, but they can be easily generalized in a number of different ways.

In the first part, of this chapter an algorithm to generate a large class of partitionable networks is developed and proven correct. This algorithm is based upon the results of the analysis presented in Chapter 6.

The second part of this chapter discusses the problem of synthesis of a special case of partitionable networks. This special class of networks consists of those networks that are isomorphic to a direct product of groups [Han68, Her75]. Since these groups have been studied in the abstract algebra extensively, techniques are known to determine the possibility of decomposition of a given group into a direct product of groups.

In Chapter 8 the analysis of multistage networks will be addressed. This extends the work done in Chapter 6 into the domain of multistage interconnection networks.

First a method of composition of single stage networks is presented and its properties studied. Using the composition of single stage networks, the multistage model is defined. This approach has the advantage that some results of analysis of single stage networks can be applied to the study of the multistage networks. The model is very general since each stage consists of the general single stage model presented earlier. Several examples of an application of the multistage model are presented.

In Chapter 9 a case study of a communication system for a real-time, distributed digital signal processing system. Network and network interfaces are designed subject to number of system constraints such as very high throughput, system extendibility, and fault tolerance requirements. For this

application, and given the current and near future technology, a crossbar based interconnection network was selected for the task under consideration. Two different fault tolerant chip architectures are presented. Four network architectures are designed and their characteristics are discussed. Several fault detection and recovery techniques on the system level are developed.

In Chapter 10, a study of shuffle interconnection function emulation by PM2I and Illiac SIMD networks is performed. It was previously shown that a lower bound on the number of transfers needed for the PM2I network to perform the shuffle is  $\log_2 N$ . The algorithm described here is near optimal and requires only  $(\log_2 N) + 1$  transfers. Also, an algorithm for the case where there is a machine with a PM2I network and it is desired to emulate a shuffle that is of smaller size than the host network is presented. Using the PM2I algorithm as a basis, an algorithm for the Illiac to emulate the shuffle is given. It requires  $2\sqrt{N} - 1$  transfers, which is only three transfers more than lower bound of  $2\sqrt{N} - 4$  shown previously.

In Chapter 3 an overview of several classes of tightly coupled parallel computer architectures will be given. First the defining features of each class will be presented, and then an example of the class will be discussed in detail. All the examples consist of existing systems or systems in research or design stages which have been described in the literature.

In Chapter 4 the network model is presented. The model together with additional information is then used to define the model of a parallel computer system. Three types of systems based upon the method of use of the network are defined and examples of each category given.

In Chapter 5 a measure of similarity of systems with arbitrary labeling and topology is introduced. The measure is called quasimorphism and is used in this chapter to analyze emulation of one system by another.

In Chapter 6 the horizontal composition and decomposition of interconnection networks are formally defined and analyzed. Using the compositions, three types of partitionable single stage networks are recognized. An algorithm is presented that accepts as an input a topologically arbitrary interconnection network and outputs one of following four outcomes: the network is not partitionable, or the network is partitionable in one of the three types.

In Chapter 7 the synthesis of single stage partitionable networks is studied. An algorithm is presented to synthesize a large class of partitionable networks. In addition, a special class of partitionable interconnection networks that are isomorphic to a direct product of groups is described.

In Chapter 8 the analysis of multistage networks is discussed. Basic definitions such as vertical composition of networks is presented and its properties analyzed. Using composition of single stage networks, the multistage network model is defined and some applications are shown.

In Chapter 9 a network and network interfaces are designed for a realtime, distributed digital signal processing system. The design is subject to number of system constraints such as very high throughput, system extendibility, and fault tolerance requirements. Several fault detection and recovery techniques on the system level are studied, since fault tolerance is a salient issue of this system.

In Chapter 10 the ability of the PM2I and Illiac type single stage SIMD machine interconnection networks to perform the shuffle interconnection was examined. Two algorithms were developed, one for the case of a PM2I of same size as the shuffle and one for the case of a PM2I of a larger size than the shuffle. Both algorithms are near optimal in the number of network transfers. In addition, using the PM2I algorithm as a basis, an algorithm for the Illiac to emulate the shuffle is developed.

.

Y

#### **3.1 Introduction**

One method of speeding up the execution of computational tasks is to use parallel computer architectures which exploit the parallelism in the execution phase of the task. Numerous parallel computer systems have been discussed in the literature and proposed, and several have been built. Parallel systems are divided into two major classes, tightly coupled and loosely coupled. The subject of analysis here is the tightly coupled parallel systems group which can be divided into several categories.

As will be shown, each type of parallel computer architecture requires one or more interconnection networks. Some systems use networks dedicated to the communication between particular subsystems, some other systems use a single network multiplexed for communication among different parts of the system. In an ensemble parallel system the network is used by the control unit to broadcast instructions and data. In a pipelined system the interconnection network is used to provide data communication among the computational units (segments) of the pipeline. In vector and array parallel system one network is used for interprocessor communication and a usually separate network is used by the control unit to broadcast data, instructions, and control information to the processors. In a systolic system the network is used to propagate the wave of the partial results from a set of processors to the next set of processors. In an associative system the control unit uses the network to broadcast the selected data fields to the processors for comparison, and in some cases another network is used for the interprocessor communications. Reconfigurable systems use a network for interprocessor communication and perhaps a different

network for fetching/storing data in the memories. Data flow system consisting of multiple rings needs a communication network to move data among rings.

#### 3.2 Overview

In this chapter an overview of different classes of tightly coupled parallel computer architectures will be given. Each class will be presented as follows. First the defining features of the class will be presented, and then a representative system of the class will be discussed. All the examples consist of existing systems or systems in research or design stages described in the literature. For a good survey of systems see [HaL82] and of interconnection networks see [Sie85].

### 3.3 Problem Statement

Several categories of parallel computer architectures will be defined. This will be followed by a detailed description of an example of architecture in each category. The description of the system will demonstrate that each category of parallel computer architecture described uses one or more interconnection

### **3.4 Parallel Computer Architecture Classes**

The Ensemble Processors achieve the speedup of execution of computational task by utilizing many processing elements each of which is operating on an independent data stream. The system does not use an interprocessor interconnection network, however, the control unit uses an interconnection network to transfer data and instructions to the processors.

A representative of this group is the Parallel Element Processing Ensemble (PEPE) [ThW75, ViC78], whose design can support up to 288 processors. PEPE was developed to handle the tracking of multiple targets and as such it must compute identical operations on large number of independent data streams. These data streams are radar signal returns of possibly multiple objects entering the radar's surveillance volume. PEPE also uses an associative operation to locate the file of a target given its new data coordinates. This operation is implemented by broadcasting of the new data from the control unit to the processors using the interconnection network. If a correlation is found between new data and a file in a processor then the new information is added to the file, otherwise an idle processor will be allocated for a new target. The pipelined processors (MISD mode) achieve speedup of computation by (a) breaking the instruction into a sequence of smaller operations and (b) executing concurrently the smaller operations using several computational units. The flow of data is such that unit  $u_i$  executes its subtask and passes the data to unit  $u_{i+1}$ , hence the term pipeline. Some systems that fall into this category are TI ASC [Bae80, Sto80, The74], CRAY 1 [KoT80], and CYBER 205 [Bae80, KoT80].

The TI Advanced Scientific Computer (ASC) consists of an instruction unit and from one to four processing units. The instruction unit is constructed as a four stage pipeline and the stages are: instruction fetch, instruction decode, effective address calculation, and register operand fetch. All processing units are identical and each consists of eight stages, however, using a dynamic reconfiguration (via a network) a custom pipeline can be constructed from the basic eight elements. The stages of the processing unit are: input, exponent subtractor, prenormalizer, multiplier, adder, normalizer, accumulator, and output.

The vector and array processors (SIMD Mode) achieve speedup of computation by using a large number of computational elements. Examples of their applications include the image processing, such as filtering and convolution, and in matrix operations for the weather prediction or simulation. Some examples of these systems are Illiac IV [BaB68, BoD72], MPP [Bat80], Cartesian Moment Computer (CMC) [ReS82, Seb82], and BSP [KoT80]. Two examples will be discussed, the MPP and the BSP.

The Massive Parallel Processor (MPP) consists of  $128 \times 128 = 16384$  simple processing elements. Each element processes data one bit wide (bit serial). Each processor communicates with other processors in the array using

the four nearest neighbor interconnection network. The processing array uses staging memories to reorder the data received from a satellite into a form where each processor receives all the bits of the grey value of one pixel in the image.

Burroughs Scientific Processor (BSP) consists of 16 arithmetic units, each capable of operating on 48 bit words. There is an input alignment network to move data from the 17 memory units to the 16 arithmetic units and an output alignment network to move the data from the 16 arithmetic units to the 17 memory units. The alignment network allows a 16×16 matrix to be stored in the 17 memories in such manner that row, column, diagonal, and many other substructures of the matrix can be fetched/stored without an accessing conflict [BuK71].

The systolic arrays or wavefront processors [KuL78, Kun82] receive the name from their mode of operation which can be described as follows. The systolic arrays are usually organized as one or two dimensional arrays of simple processors, each connected to its neighbors in some regular way (two, three, four, or six nearest neighbors). Each processor repeatedly executes the same operation on data as it is pipelined through the systolic array, creating partial results. Each partial result is passed to a neighboring processor which will use the partial result and additional (partial) results to create a more complete result until finally at the output edge of the array the final result is outputted.

The associative processors achieve the speedup by operating in parallel on a large number of records that are selected based on the value of a field in the record. Examples in this category are STARAN [Bat74, FeF74, RoP77], OMEN [Hig72], and ALAP [YaF77]. The ALAP will be described here.

The Associative Linear Array Processor (ALAP) consists of a linearly connected array of processors that receive common data and commands from the control unit. Their matching line outputs are "or"ed together to notify the control unit if there is a match to the input data. A VLSI system consisting of 13 processors was constructed and tested. A bus is used to input individual as well as common data into the processors, therefore it would become a bottleneck if a large number of processors were used.

The reconfigurable systems consist of a large number of processors which communicate through a reconfigurable interconnection network. Some examples of this category are PASM [SiS79, SiS81, SiS84], TRAC [KaP80, SeU80], and CHIP [Sny82]. The PASM system will be described here.

The partitionable SIMD/MIMD (PASM) system is currently under development in Purdue University, School of Electrical Engineering. The system includes  $Q = 2^q$  Micro Controllers (MCs), and the Parallel Computation Unit (PCU) which is comprised of N =  $2^n$  processors, N memory modules, and an interconnection network.

The system's strength lies in its ability to allocate a subset of its N processors to a particular task. For details on the allocation strategies see [TuS83]. It is intended to be used in image processing and pattern recognition applications. The collection of resources consisting of RN/Q processors,  $(R = 2^r, 0 \le r \le q)$  together with R Micro Controllers and RN/Q memories is called a virtual machine. The actual processors selected for a given virtual machine depend upon the type of partitionability of the system and the partition selected. The type of partitionability is a function of the interprocessor interconnection network. The virtual machines are independent of each other, consequently different machines can execute different jobs

concurrently. The current status of PASM is the logic design phase and building of a small prototype of 16 processors and four MC's using off shelf logic devices.

Data flow system achieves computational speedup by exploiting the parallelism at the instruction level [WaG82]. Conceptually, each instruction is translated into a template consisting of an operation and data slots. An instruction gets executed if its data are available and a processor is available.

Data flow computers are usually implemented as rings, each ring consisting of at least the following blocks: a token queue, a matching store, and a processing unit. The "token queue" saves results generated by the processing unit. The "matching store" tries to match incoming tokens from the token queue with the slots of templates currently residing in the matching store. The "processing unit" accepts the instruction template with all its fields resolved and executes the operation, passing the results to the token queue. Since multiple rings each consisting of a token queue, a matching store, and a processing unit are used for speedup of the execution, a token generated in one ring may be needed as a data in a template residing in the matching store of another ring. In order for the token to move from one ring to another an interconnection network must be used to connect the data paths of different rings.

### 3.5 Conclusions

In this chapter an overview of several major classes of tightly coupled parallel computer systems was presented. Each category of parallel computer system was described in sufficient details to show that an essential part of each system is one or more interconnection network. The usage of the interconnection network varies from system to system. Some systems use networks dedicated to the communication between particular subsystems, some other systems use a single network multiplexed for communication among different parts of the system. In an ensemble parallel system the network is used by the control unit to broadcast instructions and data. In a pipelined system the interconnection network is used to provide data communication among the computational units (segments) of the pipeline. In a vector and array parallel system one network is used for interprocessor communication and a usually separate network is used by the control unit to broadcast data. instructions, and control information to the processors. In a systolic system the network is used to propagate the wave of the partial results from a set of processors to the next set of processors. In an associative system the control unit uses the network to broadcast the selected data fields to the processors for comparison, and in some cases another network is used for interprocessor communications. Reconfigurable system uses a network for interprocessor communication and perhaps a different network for fetching/storing data in the memories. Data flow system consisting of multiple rings needs a communication network to move data among rings.

When a designer is facing the problem of selecting a parallel computer system for a particular task or a class of tasks, then several properties of the network becomes of interest. These properties are heavily dependent upon the topology of the network and therefore the study of the topological properties of networks is an important method of evaluation and classification of parallel computer systems.

# 4 MODELING OF NETWORKS AND SYSTEMS

#### 4.1 Introduction

Most current analytical techniques for interconnection networks and modeling techniques of networks are concentrated on the analysis of topologically regular interconnection networks. Examples of such networks are Illiac [BoD72], Shuffle [LaS76, SeS84b], multistage Cube [AdS82b], STARAN [Bat74], ADM [McS82], k-connected mesh [NaS80], and PM2I [SeS84b]. The past research usually proceeded on the following lines. A network specific model is defined and then analytical results are derived using this model. The problem with this approach is that the results developed are problem specific, that is to say, the results are valid only for the small class of networks that the model represents. One way to generalize the results of the analysis is to develop a general model describing the topology of the network.

In this chapter, the following problems are discussed. A general problem of modeling networks with arbitrary topology is developed [SeS84a]. This model is sufficiently general so that it can be used to model networks with arbitrary including regular and irregular topology. The model is independent of the method of implementation of the network. This is necessary because properties of networks such as similarity measures, emulation and partitionability of networks are implementation independent. The similarity measures between two networks is classified into several classes. This is a refinment of the old system which classified the similarity measure between two networks into two classes only, isomorphic and nonisomorphic. The model of network together with additional information is then used to construct a model for parallel computer systems. A system, informally, consists of a set of devices, interconnection network, and a method of use of the network. Each device is assumed to have two logical ports, an input port and an output port, possibly implemented as the physically same set of I/O pins. Some examples of devices are processors, memories, or processor/memory pairs. Based upon the use of the network, three types of systems, recirculating, nonrecirculating, and partially recirculating are defined. Relationships between systems such as equality and three types of subsystems are rigidly defined and their properties explored.

## 4.2 Overview

This chapter is organized as follows. In section 4.3 definitions of the problems addressed in this chapter are given. In section 4.4 the previous related work is briefly described. In section 4.5 the basic concepts are defined. In section 4.6 the network model is presented, several major relationships between networks described, their properties given and some examples of applications presented. In section 4.7 the concept of a parallel computer system is formally introduced. Three types of systems based upon the method of use of the network are defined and examples of each category given. Several similarity measures between two systems are defined and examples presented. In section 4.8 the conclusion and summary of the chapter is given.

# 4.3 Problem Statement

In this section, an informal description of the work presented in this chapter is given. The descriptions will be informal only, as the basic mathematical concepts have not been defined yet and will be introduced later in this chapter. The following problems of analysis of interconnection networks are addressed in this chapter. In order to analyze the topological properties of interconnection networks a model must be developed. In this chapter, a general model of topologically arbitrary interconnection networks is presented which will be used through most of this research [SeS84b]. This model is implementation independent, which is desired since the topological properties of networks are implementation independent, moreover if the model were implementation dependent that would reduce its scope of applicability to the class of networks having that implementation. Next, several important relationships between networks such as equality and two types of subnetworks are defined and their properties shown. In the next section the model for a parallel computer system is defined. A system, informally consists of a set of devices, an interconnection network, and a use of the network. Each device (processor, memory or processor/memory pair) is assumed to have two logical ports, one input port and one output port. Based upon the method of use of the network, three types of systems, recirculating, nonrecirculating, and partially recirculating are defined. Relationships between systems such as equality and three types of subsystems are rigidly defined and their properties explored.

### 4.4 Previous Work

In this section, the previous work is briefly described. Previous work on modeling of interconnection networks in [Gok76, GoL73, LiM82, Upp81] was used to describe the class of SW Banyans networks. The model is based on graph theory and is sufficiently general to describe the class of SW Banyans, however it is implementation dependent, which narrows down the the scope of its applicability. Some issues discussed using the model were mapping methods of simple regular interconnection networks such as ring or a tree onto the Banyan networks. Additional work on modeling of regular networks, such as mesh, shuffle, Cube and PM2I was done in [FiF82], and was network specific. In [FiF82] a specific class of networks called quotient networks was discussed. Informally, a quotient network is a network that is homomorphic to the same type of network of a smaller size in terms of processors. A class specific model was developed in [RaF83] for the evaluation of a class of linear array-processor systems for VLSI implementation. A general model was developed for the analysis of time space tradeoff ci interconnection network in [MaM81b]. A good overview of interconnection networks can be found in [Sie85, WuF84].

#### 4.5 Basic Concepts

In this section, basic definitions and notation needed as the background for the rest of the paper are introduced. Some of the definitions can be found in books on basic abstract algebra [Han68, Her75] and graph theory [BoM76, Har69], however are included here for completeness. The purpose of these definitions is to develop a formal notation that will be used to discuss more complex concepts such as networks and systems. To relate these definitions to the subject at hand, some examples are given in the end of this section.

Let the set of input labels of a graph/algebraic structure be denoted by  $V_{I}$  and the set of output labels of the structure be denoted by  $V_{O}$ . All graph/algebraic structures defined in this paper over  $V_{I} \times V_{O}$  will assume that  $V_{I} \cap V_{O} = \emptyset, V_{I} \neq \emptyset, V_{O} \neq \emptyset$ , where  $\emptyset$  is the *empty set* and  $V_{I} \times V_{O} = \{\langle v_{a}, v_{b} \rangle | v_{a} \in V_{I}, v_{b} \in V_{O}\}.$

The following notation will be used throughout this paper. The symbols are enclosed in a pair of double quotation marks.

" $\{","\}$ " - delimiters for set. "(",")" - function application and grouping of operations. "<",">" - delimiters for n-tuple.

"[","]" - used as defined in context.

Definition 4.5.1:

Let A be a set, then  $P[A] \triangleq \{B \mid B \subseteq A\}$  is the power set of A.

Definition 4.5.2:

Let  $C_m \in P[V_1 \times V_0]$ , then  $C_m$  is an I/O correspondence over  $V_I \times V_O$ . Definition 4.5.3:

Let  $C_m \in P[V_I \times V_O]$  such that  $\langle v_a, v_b \rangle$ ,  $\langle v_c, v_d \rangle \in C_m \rightarrow v_b \neq v_d$ , then the  $C_m$  is a nondestructive I/O correspondence over  $V_I \times V_O$ . (Physically,  $C_m$  represents one state of a reconfigurable network).

Definition 4.5.4:

Let  $C[V_I \times V_O] \triangleq \{C_m \in P[V_I \times V_O] \mid C_m \text{ is nondestructive}\}$ . Then  $C[V_I \times V_O]$  is called the *C*-set over  $V_I \times V_O$ .

The definitions 4.5.5 to 4.5.8 discuss the connectivity or accessibility aspects of the I/O correspondences.

Definition 4.5.5:

Let  $C_m \in C[V_I \times V_O]$ , then  $s(C_m) \triangleq \{v_a | < v_a, v_b > \in C_m\}$  is the source set of  $C_m$ .

Definition 4.5.6:

Let  $C_m \in C[V_I \times V_O]$ , then  $d(C_m) \triangleq \{v_b | < v_a, v_b > \in C_m\}$  is the destination set of  $C_m$ .

Definition 4.5.7:

Let  $C = \{C_m \mid m=1,2,...n\} \subseteq C[V_I \times V_O]$ , then  $s(C) \triangleq \bigcup_m s(C_m)$  is the source set of C.

Definition 4.5.8:

Let

$$C = \{C_m \mid m=1,2,...n\} \subseteq C[V_I \times V_O]$$

, then  $d(C) \triangleq \bigcup_m d(C_m)$  is the

destination set of C.

Example 4.5.9:

Let  $V_I = \{v_0, v_1\}$ , and set  $V_0 = \{u_0, u_1, u_2, u_3\}$ . Consider the set  $A = \{\langle v_0, u_0 \rangle, \langle v_0, v_2 \rangle, \langle v_1, u_3 \rangle\}$ . What type of correspondence it is.

Solution:

- (a): Clearly  $A \subseteq P[V_I \times V_0]$ , therefore A is an I/O correspondence over  $V_I \times V_0$ .

- (b):  $\langle v_0, u_0 \rangle, \langle v_0, u_2 \rangle \in A$ , and  $u_0 \neq u_2$ .  $\langle v_0, u_2 \rangle, \langle v_1, u_3 \rangle \in A$ , and  $u_2 \neq u_3$ .  $\langle v_0, u_0 \rangle, \langle v_1, u_3 \rangle \in A$ , and  $u_0 \neq u_3$ . Therefore A is a nondestructive I/O correspondence over  $V_I \times V_O$ .

(c): The source set of A is  $\{v_0, v_1\} = V_1$ .

(d): The destination set of A is  $\{u_0, u_2, u_3\} \subset V_0$ .

Example 4.5.10:

Let  $V_I$  and  $V_O$  be two sets,  $V_I = \{v_0, v_1\}, V_0 = \{u_0, u_1, u_2, u_3\}$ . Consider the set  $B = \{\langle v_0, u_0 \rangle, \langle v_0, u_2 \rangle, \langle v_1, u_2 \rangle\}$ . What type of correspondence it is.

Solution:

(a): Clearly  $B \subseteq P[V_I \times V_O]$  therefore B is an I/O correspondence over  $V_I \times V_O$ . (b):  $\langle v_0, u_2 \rangle, \langle v_1, u_2 \rangle \in B$  and  $u_2 = u_2$ . Therefore B is not nondestructive I/O correspondence over  $V_I \times V_O$ , and B could not represent a state of a reconfigurable network.

## 4.6 Interconnection Network Model

In this section, a formal graph/algebraic model of an interconnection network is presented. Graph models for analyzing networks have been used by other researchers. For example, in [Gok76, GoL73, LiM82, Upp81] they are used to analyze regular SW Banyan networks, and in [FiF82] they are used to study the partitioning of regular networks. The model presented here differs from [Gok76, GoL73, LiM82, Upp81] and [FiF82] by being completely general so that it can be used to describe an arbitrary, topologically regular and irregular, interconnection network.

Certain relationships between networks that are of interest to the computer system designer are presented here in a rigid mathematical fashion. In particular, the relationships subnetworks and equality are defined and their properties described. In the end of the section, some examples of applications are presented and an example is generalized into a theorem. Let  $K = \langle C \rangle$  be such that:

- (1)  $C \subseteq C[V_I \times V_0].$

- (2)  $V_I = s(C)$ .

- $(3) V_{O} = d(C).$

- $(3) |C| \geq 2.$

Then  $K = \langle C \rangle$  is an I/O representation of a reconfigurable network over  $V_I \times V_O$

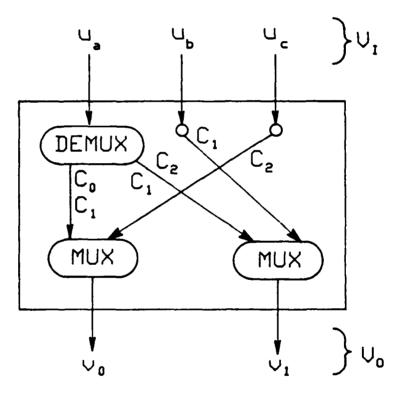

Physical implications:  $\langle v_a, v_b \rangle \in C_m$ ,  $C_m \in C$  represents the network moving data from input  $v_a$  to output  $v_b$  when the state of the network is  $C_m$ . C represents the set of all possible states of the reconfigurable network. For an example of a topologically arbitrary interconnection network see Figure 4.1. The example has the following parameters:

$$\begin{split} \mathbf{V}_{I} &= \{\mathbf{u}_{a}, \mathbf{u}_{b}, \mathbf{u}_{c}\}, \ \mathbf{V}_{O} &= \{\mathbf{v}_{0}, \mathbf{v}_{1}\}, \\ \mathbf{C}_{0} &= \{<\mathbf{u}_{a}, \mathbf{v}_{0} > < \mathbf{u}_{a}, \mathbf{v}_{1} > \}, \\ \mathbf{C}_{1} &= \{<\mathbf{u}_{a}, \mathbf{v}_{0} >, < \mathbf{u}_{b}, \mathbf{v}_{1} > \}, \\ \mathbf{C}_{2} &= \{<\mathbf{u}_{a}, \mathbf{v}_{1} >, < \mathbf{u}_{c}, \mathbf{v}_{0} > \}, \\ \mathbf{C} &= \{\mathbf{C}_{0}, \mathbf{C}_{1}, \mathbf{C}_{2}\}. \ \mathbf{K} &= <\{\mathbf{C}_{0}, \mathbf{C}_{1}, \mathbf{C}_{2}\} >. \end{split}$$

Definition 4.6.2:

Let  $K[V_I \times V_O] \triangleq \{K \mid K = \langle C \rangle$  is a network over  $V_I \times V_O\}$ . Then  $K[V_I \times V_O]$  is called the *K*-set over  $V_I \times V_O$ .

The Definitions 4.8.3 to 4.8.5 are used to classify formally the measure of similarity between two networks. The classes are presented here in the order of increasing strictness. Note that these relationships provide a refined scale of

Figure 4.1: An example of a topologically arbitrary network.

LS7.5.5000

the measure of similarity between two networks compared to the more customary classification of isomorphic/nonisomorphic which was used in the past. Several examples illustrating the application of these measures are given after the definitions are presented. The examples are generalized into a theorem relating the PM2I and k-dimensional Illiac networks.

Definition 4.6.3:

Let  $K[V_I^1 \times V_O^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K[V_I^2 \times V_O^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks such that:

- (1)  $V_I^1 \subseteq V_I^2, V_0^1 \subseteq V_0^2.$

- (2)  $\forall C_m^1 \in C^1 \exists C_n^2 \in C^2 \ni : C_m^1 \subseteq C_n^2$ .

Then  $K^1$  is subnetwork of type b of  $K^2$ . Notation:  $K^1 \subseteq b K^2$ .

Definition 4.6.4:

Let  $K^1 \in K[V_I^1 \times V_0^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K^2 \in K[V_I^2 \times V_0^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks such that:

- (1)  $V_I^1 \subseteq V_I^2, V_0^1 \subseteq V_0^2$ .

- (2)  $\forall C_m^1 \in C^1 \quad \exists C_n^2 \in C^2 \ni : C_m^1 = C_n^2.$

Then  $K^1$  is subnetwork of type c of  $K^2$ . Notation:  $K^1 \subseteq c K^2$ .

Note: The reason for referring to these subnetworks as types b and c is to make this notation consistent with the definitions of subsystems in Section 4.7, where the three types of subsystems type a, b, and c are described.

Definition 4.6.5:

Let  $K^1 \in K[V_I^1 \times V_O^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K^2 \in K[V_I^2 \times V_O^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks such that:

- (1)  $V_{f}^{1} = V_{f}^{2}, V_{O}^{1} = V_{O}^{2}.$

- (2)  $C^1 = C^2$ .

- Then  $K^1$  is equal to  $K^2$ . Notation:  $K^1 = K^2$ .

The Theorems 4.6.6 to 4.6.8 describe the sufficient conditions for the relationships of the different types to exist.

#### Theorem 4.6.6:

Let  $K^1 \in K[V_I^1 \times V_O^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K^2 \in K[V_I^2 \times V_O^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks. If  $\forall C_m^1 \in C^1 \exists C_n^2 \in C^2 \ni : C_m^1 \subseteq C_n^2$ , then  $K^1 \subseteq b K^2$ .

Proof:

- (1): Show  $V_{I}^{1} \subseteq V_{I}^{2}$ .  $(\forall C_{m}^{1} \in C^{1}), \quad (\exists C_{n}^{2} \in C^{2}) \Rightarrow (C_{m}^{1} \subseteq C_{n}^{2})$   $\rightarrow (\forall C_{m}^{1} \in C^{1}, C_{m}^{1} \subseteq C_{g(m)}^{2}))$   $\rightarrow (\forall C_{m}^{1} \in C^{1}, s(C_{m}^{1}) \subseteq s(C_{g(m)}^{2})))$   $\rightarrow (\bigcup_{m} s(C_{m}^{1}) \subseteq \bigcup_{m} s(C_{g(m)}^{2})))$  $\rightarrow (\bigcup_{m} s(C_{m}^{1}) \subseteq \bigcup_{n} s(C_{g(m)}^{2})) \rightarrow V_{I}^{1} \subseteq V_{I}^{2}.$

- (2): Show  $V_0^1 \subseteq V_0^2$ .

Similar to (1) except replace the s set by the d set.

Theorem 4.6.7:

Let  $K^1 \in K[V_I^1 \times V_0^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K^2 \in K[V_I^2 \times V_0^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks. If  $\forall C_m^1 \in C^1 \exists C_n^2 \in C^2 \ni : C_m^1 = C_n^2$ , then  $K^1 \subseteq c K^2$ . Show

$$V_I^1 \subseteq V_I^2$$

and  $V_O^1 \subseteq V_O^2$ .

The proofs are similar to proof of Theorem 4.6.6.

Theorem 4.6.8:

Let  $K^1 \in K[V_I^1 \times V_O^1]$ ,  $K^1 = \langle C^1 \rangle$ , and  $K^2 \in K[V_I^2 \times V_O^2]$ ,  $K^2 = \langle C^2 \rangle$ , be two networks. If  $C^1 = C^2$  then  $K^1 = K^2$ .

Proof:

- (1): Show  $V_I^1 = V_I^2$ .  $C^1 = C^2 \rightarrow s(C^1) = s(C^2) \rightarrow V_I^1 = V_I^2$ .

- (2): Show  $V_0^1 = V_0^2$ .  $C^1 = C^2 \rightarrow d(C^1) = d(C^2) \rightarrow V_0^1 = V_0^2$ .

The following examples show an application of the similarity measure between two networks. Note the increasing similarity between the PM2I and k-dimensional Illiac as the dimension k increases. The examples are generalized into a theorem showing what happens at the limit of k as k increases to maximum.

**Example 4.6.9**:

Consider the Illiac network with N = 64 processors. The network can be modeled as follows.

$$V_{I}^{1} = \{u_{j} | j=0,1,...63\}, V_{O}^{1} = \{v_{k} | k=0,1,...63\}.$$

$$C^{1} = \{C_{0}^{1}, C_{1}^{1}, C_{2}^{1}, C_{3}^{1}\}.$$

Let  $\oplus$  denote addition modulo 64 and  $\ominus$  subtraction modulo 64.

$$C_0^{1} = \{ \langle u_j, v_{j \oplus 1} \rangle | j = 0, 1, \dots 63 \},$$

$$C_1^{1} = \{ \langle u_j, v_{j \oplus 1} \rangle | j = 0, 1, \dots 63 \},$$

$$C_2^{1} = \{ \langle u_j, v_{j \oplus 8} \rangle | j = 0, 1, \dots 63 \},$$

$$C_3^{1} = \{ \langle u_j, v_{j \oplus 8} \rangle | j = 0, 1, \dots 63 \}.$$

Then  $K^1 = \langle C^1 \rangle$  describes the network.

Consider the single stage PM2I network with N = 64 processors. The network can be described as follows.

$$V_{I}^{2} = \{u_{j} | j=0,1,...63\}, V_{O}^{2} = \{v_{k} | k=0,1,...63\}.$$

$$C^{2} = \{C_{0}^{2}, C_{1}^{2}, ... C_{11}^{2}\},$$

$$C^{2}_{s} = \{\langle u_{j}, v_{j \oplus 2^{s}} \rangle | s = 0,1,...5; j = 0,1,...63\}.$$

$$C^{2}_{6+t} = \{\langle u_{j}, v_{j \oplus 2^{s}} \rangle | t = 0,1,...5; j = 0,1,...63\}.$$

Then  $K^{2} = \langle C^{2} \rangle$  describes the network.

What is the relationship between the networks.

Solution:

- (a):  $V_I^1 \subseteq V_I^2, V_0^1 \subseteq V_0^2,$

- (b):  $\forall C_p^1 \in C^1 \quad \exists C_n^2 \in C^2 \ni$ :  $C_p^1 = C_n^2$ . By Theorem 4.6.7 K<sup>1</sup> is a subnetwork of type c of K<sup>2</sup>, denoted by K<sup>1</sup>  $\subseteq$  c K<sup>2</sup>. Since  $C_1^2 \notin C^1$ , therefore K<sup>1</sup>  $\neq$  K<sup>2</sup>. In the special case of N = 4 the Illiac is equal to the PM2I.

Example 4.6.10:

Consider the generalized three dimensional Illiac system with 64 processors, arranged as a  $4 \times 4 \times 4$  matrix. This network can be modeled as follows.

$$V_{I}^{1} = \{u_{i} | i=0,1,...63\}, V_{O}^{1} = \{v_{k} | k=0,1,...63\}.$$

$C^{1} = \{C^{1}_{0}, C^{1}_{1}, C^{1}_{2}, C^{1}_{3}, C^{1}_{4}, C^{1}_{5}\}.$ Let  $\oplus$  denote addition modulo 64 and  $\Theta$  subtraction modulo 64.  $C_{a}^{1} = \{\langle u_{j}, v_{j \oplus 4^{a}} \rangle | a = 0, 1, 2; j = 0, 1, ...63\},$  $C^{1}_{3+b} = \{\langle u_{j}, v_{j \oplus 4^{b}} \rangle | b = 0, 1, 2; j = 0, 1, ...63\}.$ Then  $K^{1} = \langle C^{1} \rangle$  describes the network. Let  $K^{2} = \langle C^{2} \rangle$  be the PM2I network with N = 64 as in Example 4.6.9.

What is the relationship between the networks.

Solution:

- $(a): \quad V_I^{\ 1} \subseteq V_I^{\ 2}, \ V_0^{\ 1} \subseteq V_0^{\ 2},$

- (b):  $\forall C_p^{-1} \in C^1 \quad \exists C_n^{-2} \in C^2 \ni : C_p^{-1} = C_n^{-2}$ . By Theorem 4.6.7 K<sup>1</sup> is a subnetwork of type c of K<sup>2</sup>, denoted by K<sup>1</sup>  $\subseteq$  c K<sup>2</sup>. Since  $C_1^{-2} \notin C^1$ , therefore K<sup>1</sup>  $\neq$  K<sup>2</sup>.

# Example 4.6.11:

Consider the generalized six dimensional Illiac system with 64 processors, arranged as a  $2 \times 2 \times 2 \times 2 \times 2 \times 2 \times 2$  matrix. This network can be modeled as follows.

$$V_{I}^{1} = \{u_{j} | j=0,1,...63\}, V_{O}^{1} = \{v_{k} | k=0,1,...63\}.$$

$$C_{a}^{1} = \{C_{0}^{1}, C_{1}^{1}, ..., C_{11}^{1}\}.$$

Let  $\oplus$  denote addition modulo 64 and  $\Theta$  subtraction modulo 64.

$$C_{a}^{1} = \{ \langle u_{j}, v_{j \oplus 2^{a}} \rangle | a = 0, 1, 2, 3, 4, 5; j = 0, 1, ...63 \},$$

$$C_{6+b}^{1} = \{ \langle u_{j}, v_{j \oplus 2^{b}} \rangle | b = 0, 1, 2, 3, 4, 5; j = 0, 1, ...63 \}.$$

Then  $K^1 = \langle C^1 \rangle$  describes the network.

Let  $K^2 = \langle C^2 \rangle$  be the PM2I network with N = 64 as in Example 4.6.9.

What is the relationship between the networks.

Solution:

$C^1 = C^2$ , and Theorem 4.6.8 imply  $K^1 = K^2$ .

Theorem 4.6.12:

Let there be  $K^1 = \langle C^1 \rangle$  a PM2I network with  $N = 2^m$  processors, then there exist  $K^2 = \langle C^2 \rangle$  a generalized Illiac network in k dimensions, such that  $K^1 \subseteq c K^2$ ; moreover there exists k = mdimension such that  $K^1 = K^2$ . Consequently PM2I can be viewed as a limiting case of a k-dimensional Illiac network.

Proof:

(1): Consider the generalized k-dimensional Illiac system with 64 processors, arranged as  $2 \times 2 \times 2 \times 2 \times 2 \times 2 \times 2$  matrix. This network can be modeled as follows.

$$V_{I}^{1} = \{u_{j} | j=0,1,...63\}, V_{O}^{1} = \{v_{k} | k=0,1,...63\}.$$

$$C_{a}^{1} = \{C_{0}^{1}, C_{1}^{1}, \cdots C_{11}^{1}\}.$$

Let  $\oplus$  denote addition modulo 64 and  $\ominus$  subtraction modulo 64. Let  $d=N^{\frac{1}{k}}$ ,  $C_a^{1} = \{ \langle u_j, v_{j \oplus d^a} \rangle | a = 0, 1, ..., k - 1; j = 0, 1, ..., N - 1 \},$  $C_{b+b}^{1} = \{ \langle u_j, v_{j \oplus d^b} \rangle | b = 0, 1, ..., k = 1; j = 0, 1, ..., N - 1 \}.$

Then  $K^1 = \langle C^1 \rangle$  describes the network.

Consider the single stage PM2I network with N processors. The network can be described as follows.

$$V_{I}^{2} = \{u_{j} | j=0,1,...N-1\}, V_{O}^{2} = \{v_{k} | k=0,1,...N-1\}.$$

$C^{2} = \{C_{0}^{2}, C_{1}^{2},...C_{2m-1}^{2}\}.$

$$C_0^2 = \{ \langle u_j, v_{j \oplus 2^0} \rangle | s = 0, 1, ... 2m - 1; j = 0, 1, ... N - 1 \}.$$

$$C_{m+t}^2 = \{ \langle u_j, v_{j \oplus 2^0} \rangle$$

$$| t = m, m + 1, ... 2m - 1; j = 0, 1, ... N - 1 \}.$$

Then  $K^2 = \langle C^2 \rangle$  describes the network.

(2):

$$N = 2^{m}$$

and  $N = d^{k} \rightarrow 2^{m} = d^{k} \rightarrow d = 2^{\frac{m}{k}}$ ,

$\rightarrow \frac{m}{1} = 1, 2, \dots m \rightarrow d = 2^{\frac{m}{k}} \rightarrow d = 2, 4, \dots N.$

(3): (1), (2)

$$\rightarrow$$

$C_a^1 \subseteq C_s^2$ .

$C_a^1 \subseteq C_s^2$  and  $C_b^1 \subseteq C_t^2 \rightarrow \forall C_p^{-1} \in C^1 \quad \exists C_n^{-2} \in C^2 \ni$ :

$C_p^{-1} = C_n^{-2}$ .

By Theorem 4.6.7 K<sup>1</sup>  $\subset$  c K<sup>2</sup>.

(4): (1), (2), and

$$d = 2 \rightarrow C_a^1 = C_s^2$$

.

$C_a^1 = C_s^2$  and  $C_b^1 = C_t^2 \rightarrow C^1 = C^2$ .

$C^1 = C^2$  and Theorem 4.6.8 imply  $K^1 = K^2$ .

#### 4.7 Systems and Subsystems