MICROCOPY RESOLUTION TEST CHART

# NAVAL POSTGRADUATE SCHOOL Monterey, California

# THESIS

APPLICATION OF A SILICON COMPILER TO VLSI DESIGN OF DIGITAL PIPELINED MULTIPLIERS

by

Dennis J. Carlson

June 1984

DTIC FILE COPY

Thesis Advisor:D. E. KirkApproved for public release; distribution unlimited

84 09 28 041

0CT 03

|                                                                                                                                      | PORT DOCUMENTATION                                                                                                                                                   | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                         |                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| 1. REPORT NUMBER                                                                                                                     |                                                                                                                                                                      | A146828                                                                                                             | 3. RECIPIENT'S CATALOG NUMBER                                      |  |  |  |

|                                                                                                                                      | on of a Silicon Com                                                                                                                                                  | mpiler to                                                                                                           | 5. TYPE OF REPORT & PERIOD COVERED<br>Master's Thesis<br>June 1984 |  |  |  |

| VLSI Desig<br>Digital Pi                                                                                                             | n of<br>ipelined Multiplie                                                                                                                                           | rs                                                                                                                  | 6. PERFORMING ORG. REPORT NUMBER                                   |  |  |  |

| 7. AUTHOR(*)<br>Dennis J.                                                                                                            | Carlson                                                                                                                                                              |                                                                                                                     | 6. CONTRACT OR GRANT NUMBER(#)                                     |  |  |  |

| <b>`</b>                                                                                                                             | ANIZATION NAME AND ADDRESS                                                                                                                                           |                                                                                                                     | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS     |  |  |  |

|                                                                                                                                      | tgraduate School<br>California 9394                                                                                                                                  | 3                                                                                                                   |                                                                    |  |  |  |

| 11. CONTROLLING OF                                                                                                                   | FFICE NAME AND ADDRESS                                                                                                                                               |                                                                                                                     | 12. REPORT DATE                                                    |  |  |  |

|                                                                                                                                      | tgraduate School<br>California 9394                                                                                                                                  | 3                                                                                                                   | June 1984<br>13. NUMBER OF PAGES                                   |  |  |  |

|                                                                                                                                      | ENCY NAME & ADDRESS(II dilleren                                                                                                                                      |                                                                                                                     | 15. SECURITY CLASS. (of this report)                               |  |  |  |

|                                                                                                                                      |                                                                                                                                                                      |                                                                                                                     | Unclassified<br>154. DECLASSIFICATION/ DOWNGRADING<br>SCHEDULE     |  |  |  |

| 6. DISTRIBUTION ST                                                                                                                   | ATEMENT (of this Report)                                                                                                                                             |                                                                                                                     | <b>.</b>                                                           |  |  |  |

| 17. DISTRIBUTION ST                                                                                                                  | ATEMENT (of the abstract entered                                                                                                                                     | in Block 20, il different fr                                                                                        | an Report)                                                         |  |  |  |

|                                                                                                                                      | Y NOTES                                                                                                                                                              |                                                                                                                     | <u></u>                                                            |  |  |  |

| 18. SUPPLEMENTARY                                                                                                                    |                                                                                                                                                                      |                                                                                                                     |                                                                    |  |  |  |

| 18. SUPPLEMENTAR'                                                                                                                    |                                                                                                                                                                      |                                                                                                                     |                                                                    |  |  |  |

| 9. KEY WORDS (Cont                                                                                                                   |                                                                                                                                                                      |                                                                                                                     | iers, Silicon Compiler,                                            |  |  |  |

| 9. KEY WORDS (Cont<br>VLSI Desi<br>CAD Tools<br>CAD Tools<br>The concept<br>The process<br>an 8-bit pi<br>sulting des<br>bugging the | gn, MacPitts, Pipe<br>nue on reverse elde l'inscessery and<br>and application of<br>of employing the<br>pelined digital mu<br>ign is evaluated.<br>MacPitts compiler | lined Multipl<br>defined Multipl<br>f silicon con<br>MacPitts sili<br>ultiplier is p<br>The process<br>and the Caes | iers, Silicon Compiler,                                            |  |  |  |

-

.

Arrroved for public release; distribution unlimited.

Application of a Silicon Compiler to VLSI Design of Digital Pipelined Hultipliers

by

Cennis J. Carlson Lieutenant Commander, United States Navy E.S., Rensselaer Polytechnic Institute, 1969

Submitted in partial fulfillment of the requirements for the degree of

HASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

NAVAI POSTGRADUATE SCHOOL June 1984

bon

Author:

Approved by:

Thesis Advisor

sound

Second Reader

Chairman, Department of Electrical and Computer Engineering

An Dur

Dean of Science and Engineering

### ABSTRACT

The concept and application of silicon compilers is described. The process of employing the MacPitts silicon compiler to design an 8-bit pipelined digital multiplier is presented, and the resulting design is evaluated. The process of installing and debugging the MacPitts Compiler and the Caesar VLSI graphics editor on the VAX-11/780 computing facilities at NPS is documented in appendices.

| Acces       | sion For  |          |          |          |

|-------------|-----------|----------|----------|----------|

| NTIS        | GRA&I     | M        |          |          |

| DTIC        | TAB       | <b>A</b> |          |          |

| Unann       | ounced    | Ē        |          | DIIG     |

| Justi       | fication  |          | $\Delta$ | arre /   |

|             |           |          | -+-      | BOPY     |

| By          |           |          | Ŋ        |          |

| Distr       | ibution/  |          |          | $\smile$ |

| Avai        | lability  | Codes    |          |          |

|             | Avail and | i/or     |          |          |

| Dist        | Special   | L        |          |          |

|             |           |          |          | İ        |

| A .         |           |          |          |          |

| <b>H</b> -/ |           |          |          |          |

|             | L         |          |          |          |

## IABLE OF CONTENTS

| I.   | IEIE | CDUC  | T ION:  | • •   | •     | • •   | •    | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 11 |

|------|------|-------|---------|-------|-------|-------|------|-------|------|------|-----|-----|-------------|-----|-----|-----|---|---|---|----|

|      | 1.   | BAC   | K GR O  | UNC   | ٠     | • . • | •    | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 11 |

|      | E.   | CUE   | R EN T  | RES   | SEAR  | СН    | G01  | LS    | •    | •    | •   | •   | •           | •   | •   | •   | • | • | • | 12 |

| II.  | AFFI | RCACE | IES T   | o si  | LIC   | O N   | CCI  | IPI   | LAT  | 101  | 9   | •   | •           | •   | •   | •   | • | • | • | 15 |

|      | λ.   | VL S  | SI DE   | SIG   | N AC  | T IV  | IT:  | IES   | DO   | MA : | I N | •   | •           | •   | •   | •   | • | • | • | 15 |

|      | E.   | EV)   | L DA T  | ICN   | CAV   | EAT   | . 1  | •     | • •  | •    | •   | •   | •           | •   | •   | •   | • | • | • | 17 |

|      | c.   | LIN   | II TE D | SFI   | ectr  | 08    | COL  | IPI   | l er | S    | (Te | AN  | ISI         | LAI | :0B | S)  |   | • | • | 18 |

|      | D.   | BRC   | ) A C-S | P EC! | CR DM | 51    | LIC  | CON   | CO   | MPJ  | LE  | ERS | 5           | •   | •   | •   | • | • | • | 19 |

|      |      | 1.    | Floo    | r Pl  | lann  | ers   | 3.   | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 19 |

|      |      | 2.    | Beha    | vici  | al    | Sp€   | ci   | fica  | ati  | on   | Co  | mī  | <b>ji</b> ] | ler | s   | •   | • | • | • | 21 |

| III. | USII | IG MI | CPIT    | TS.   | • •   | • •   | •    | •     | • •  | •    | •   | •   | •           | •   | •   | •   | • | • | • | 30 |

|      | λ.   | TH P  | INP     | 07 I  | PILE? |       | •    | •     | • •  | •    | •   | •   | •           | •   | •   | •   | • | • | • | 30 |

|      |      | 1.    | Fund    | asei  | ntal  | s     | of t | the   | Ma   | CPj  | itt | s   | La          | ang | jua | ıg€ | 9 | • | • | 30 |

|      |      | 2.    | Two     | Mult  | tipl  | ie    | : Es | ra sj | ple  | s    | •   | •   | •           | •   | •   | •   | • | • | • | 36 |

|      | Β.   | INV   | OCAT    | ICN   | OPT   | 101   | IS   | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 42 |

|      | c.   | USI   | e of    | TEE   | MAC   | PI    | TS   | IN:   | r er | PRI  | ETE | R   | •           | •   | •   | •   | • | • | • | 46 |

|      | C.   | EV C  | LUTI    | ON C  | )F T  | HE    | 8 1  | BIT   | PI   | PEI  | LIN | IEC | )           |     |     |     |   |   |   |    |

|      |      | HO 1  | LTIPL   | IES   | •     | • •   | •    | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 49 |

|      |      | 1.    | Desi    | gn 1  | loti  | val   | tic  | n ai  | nd   | Coi  | ıst | :Ia | ir          | its | 5   | •   | • | • | • | 49 |

|      |      | 2.    | Firs    | t De  | esig  | n:    | 3    | Sta   | age  | s,   | 8   | Bj  | lts         | 5 C | n   | Or  | e |   |   |    |

|      |      |       | Chip    | • •   | • •   | • •   | •    | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 50 |

|      |      | 3.    | Firs    | t Fa  | arti  | tic   | ni   | ng:   | 2    | B    | its | 5,  | 1           | St  | ag  | je  |   |   |   |    |

|      |      |       | Pipe    | lire  | ε.    | • •   | •    | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 51 |

|      |      | 4.    | Seco    | nd l  | Part  | iti   | ioni | ing   | :    | 4 1  | Bit | :s, | 2           | 2 5 | Sta | Ige | 9 |   |   |    |

|      |      |       | Pipe    | line  | €.    | • •   | •    | •     | • •  | •    | •   | •   | •           | •   | •   | •   | • | • | • | 54 |

|      |      | 5.    | Thir    | d Fa  | arti  | tic   |      | ng:   | 2    | Bi   | Lts | 5,  | 4           | St  | ag  | e   |   |   |   |    |

|      |      |       | Pipe    | line  | э.    | • •   |      | •     |      | •    | •   | •   | •           | •   | •   | •   | • | • | • | 57 |

| E             | DES            | IGN V  | ALID      | ATIC  | DN .           | • •          | • •   |        | •            | • •   | •  | • | • | • | 60 |

|---------------|----------------|--------|-----------|-------|----------------|--------------|-------|--------|--------------|-------|----|---|---|---|----|

|               | 1.             | Funct  | icna      | 1 S i | i <b>mul</b> a | a ți o       | n.    | • •    | •            | • •   | •  | • | • | • | 60 |

|               | 2.             | Desig  | n Ru      | le C  | :hec           | king         | • •   | • •    | •            | • •   | •  | • | • | • | 63 |

|               | 3.             | Node   | Extr      | act i | ion a          | and 1        | Even  | t Si   | muJ          | lati  | מכ | • | • | • | 66 |

| F             | . SUM          | M AR Y | OF A      | CTI V | ITI            | ES I         | N THI | E MA   | CPI          | TTS   |    |   |   |   |    |

|               | DES            | IGN C  | ICLE      | •     | • •            | • •          | • •   | • •    | •            | • •   | •  | • | ٠ | • | 68 |

| IV. MAG       | CPITTS         | PERF   | ORMA      | NC E  | • •            | • •          | • •   | • •    | •            | • •   | •  | • | • | • | 72 |

| 1             |                | OUT E  | REOR      | S A B | ID I           | NEFF:        | ICIEI | ICIE   | S            | • •   | •  | • | • | • | 72 |

|               | 1.             | Ineff  | icie      | ncie  | es.            | • •          | • •   | • •    | •            | • •   | •  | • | • | • | 72 |

|               | 2.             | Error  | ε.        | • •   | • •            | • •          | • •   | • •    | •            |       | •  | • | • | • | 75 |

| B.            | ORG            | A NELL | ES V      | s. s  | STAN           | DARD         | CELI  | LS.    | •            | • •   | •  | • | • | • | 77 |

| C.            | SO F           | TWARE  | INC       | ompi  | TIB            | ILIT:        | IES   | • •    | •            | • •   | •  | • | • | • | 78 |

| <b>v.</b> cci | NCLUSI         | ON .   | • •       |       | • •            | • •          |       |        | •            | • •   | •  | • | • | • | 79 |

| λ.            | . SUM          | M AR Y | • •       | • •   |                |              |       |        | •            |       | •  | • | • | • | 79 |

| E.            | REC            | CMMEN  | ITATI     | ONS   |                | • •          |       | • •    | •            |       | •  | • |   | • | 80 |

| APPENDIX A    | <b>↓</b> • т № | 57177  | 1770      |       | , M 7          | <u>ጉ</u> ወተም | TC 01 | ג דר ד | <b>v</b> _ 1 | 1 /7  | 20 |   |   |   |    |

| ALL DUVIA 1   |                | DER U  |           |       |                |              |       |        |              | •     |    |   |   |   | 01 |

| A.            |                | TALLA  |           |       |                |              |       |        |              |       | •  | • | • | • | 01 |

| <b>2</b> 0    | SIS            |        | 1200      |       |                |              | •••   |        |              |       |    |   |   |   | 81 |

| E.            |                | T ALLA | <br>תחדתא |       |                |              |       |        |              |       | •  | • | • | • | 01 |

| 2             |                | t en   |           |       |                |              |       |        |              |       | -  | _ | _ | _ | 85 |

|               |                |        |           |       |                |              |       |        |              |       |    | • | • | • | 00 |

| APPENCIX 1    |                |        |           |       |                |              |       |        |              |       |    |   |   |   |    |

|               |                | der u  |           |       |                |              |       |        |              |       |    |   |   |   |    |

| -             |                | TALLA  |           |       |                |              |       |        | -            |       | -  | - | • | ٠ | 88 |

| E.            | . INS          |        | TICN      | UNI   | ER !           | THE          | UNIX  | 4.2    | 01           | PERA! |    | - |   |   | _  |

|               | SYS            | t en   | • •       | • •   | • •            | • •          | • •   | • •    | •            | • •   | •  | • | • | ٠ | 89 |

| APPENDIX      | C: MA          | NUAL   | FAGE      | S PC  | CR B           | ERKE:        | LEY   | desi   | GN           | TOO   | LS | • | • | • | 91 |

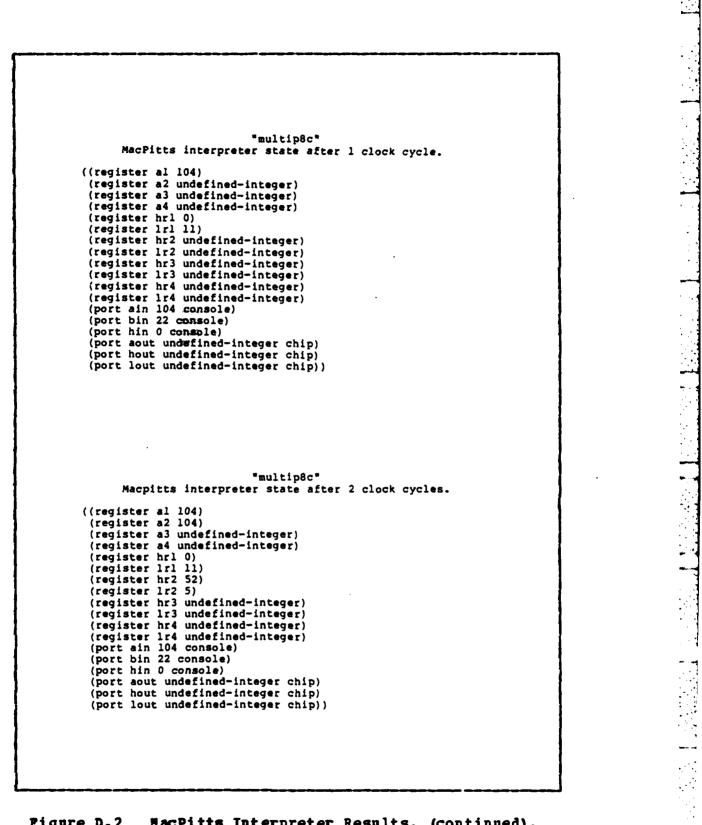

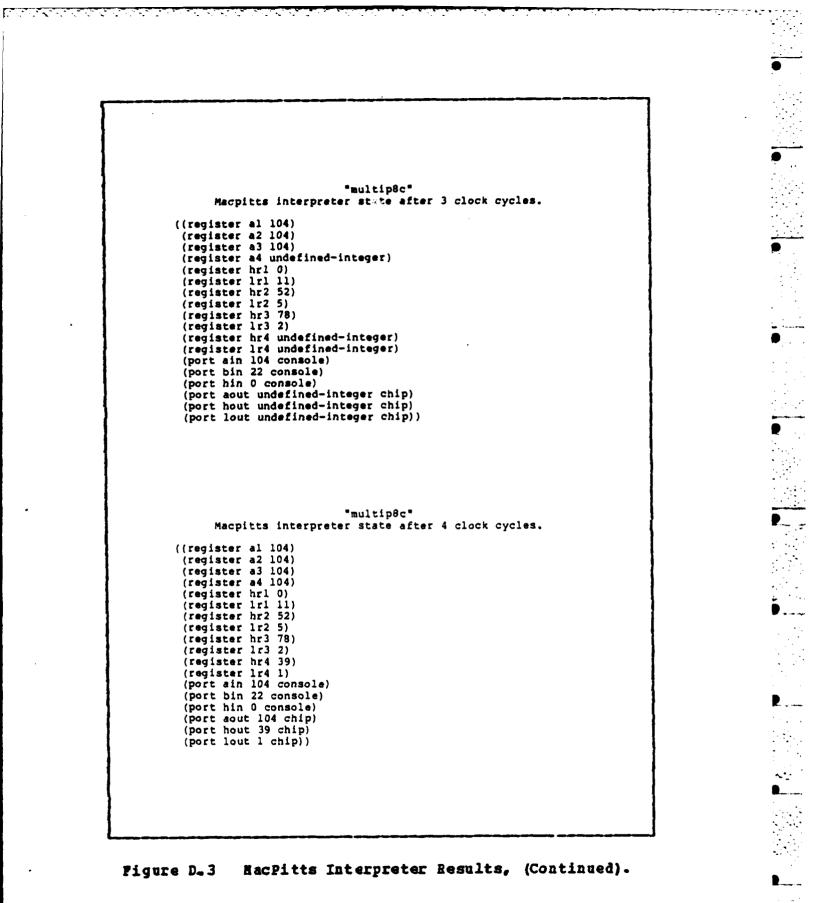

| APPENCIX      | D: SI          | MULAT  | ICN       | RESU  | JLTS           | FOR          | MUL   | CIP8   | С            |       |    |   |   |   |    |

|               | MU             | lti pl | IER       | • •   | • •            | • •          | • •   | • •    | •            | • •   | •  | • | • | 1 | 22 |

| APPENLIX E: LAYCUT FHOTOGRAPHS | 131 |

|--------------------------------|-----|

| LIST OF REFERENCES             | 137 |

| BIBLICGBAPHY                   | 139 |

| INITIAL CISTRIBUTION LIST      | 140 |

Sector Contractor

# LIST OF TABLES

| I.  | Statistic | s For  | Mac  | Pitt | s i | Uu. | lt | ip: | lie | BL | CI | 1) | ₽ |   |   |   |   |   |    |

|-----|-----------|--------|------|------|-----|-----|----|-----|-----|----|----|----|---|---|---|---|---|---|----|

|     | Designs   |        | • •  | • •  | •   | •   | •  | •   | •   | •  | •  | •  | ٠ | • | • | • | • | • | 61 |

| II. | MacPitts  | Source | e Fi | les  | . • | ٠   | •  | •   | •   | •  | •  | •  | • | • | • | • | • | • | 82 |

**?**.

£...

L

Ĩ

.

::

# LIST OF FIGURES

| 2.1  | VISI Design Activities Spectrum 16                  |

|------|-----------------------------------------------------|

| 2.2  | Typical floor plan produced by the                  |

|      | F.I.R.S.T. Silicon Compiler                         |

| 2.3  | Flcor Plan cf the MacPitts Target                   |

|      | <b>Architecture</b>                                 |

| 2.4  | MacPitts Register Circuit and Timing Diagram 25     |

| 2.5  | MacPitts Program Data Flow                          |

| 3.1  | Multic.mac Scurce File                              |

| 3.2  | Example of the Multic Behavioral                    |

|      | Specification                                       |

| 3.3  | Multip.mac Scurce file                              |

| 3.4  | Compiler Statistics for multip                      |

| 3.5  | A MacPitts Interpreter Session for multip 48        |

| 3.6  | Multip8.mac Source File                             |

| 3.7  | Multip8.mac Source File (Continued)                 |

| 3.8  | <b>Use of Ports and Registers in multip8.mac 54</b> |

| 3.9  | Data Path Architecture of Multip8 Chip 55           |

| 3.10 | Blcck Diagram of First Partitioning                 |

| 3.11 | Multip8a.mac Source File                            |

| 3.12 | Multip8t.mac Source File                            |

| 3.13 | Multip8c.mac Source File                            |

| 3.14 | Values: Program to Compute Hultip8c Output 64       |

| 3.15 | Mextra .log File for Mul8c.cif 66                   |

| 3.16 | Two Macro Driver Files for Event Simulation 67      |

| 4.1  | Data Path Ourut Routing                             |

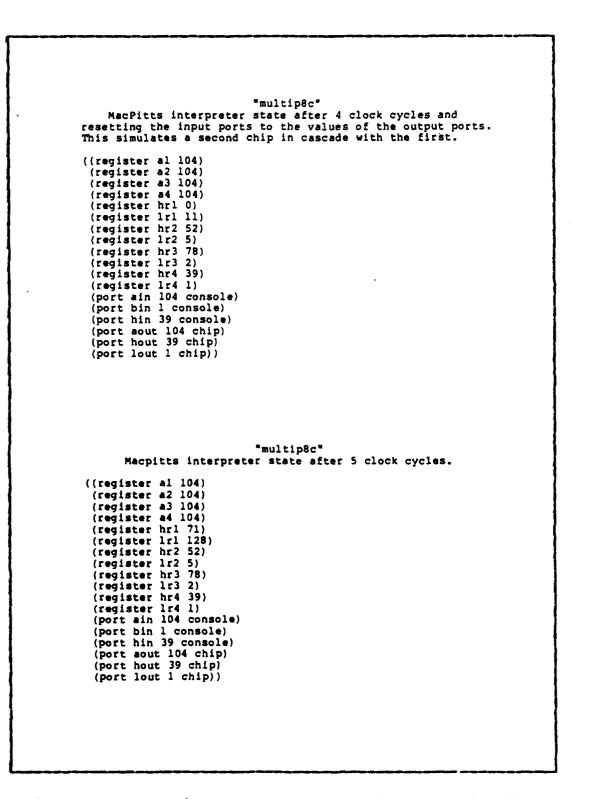

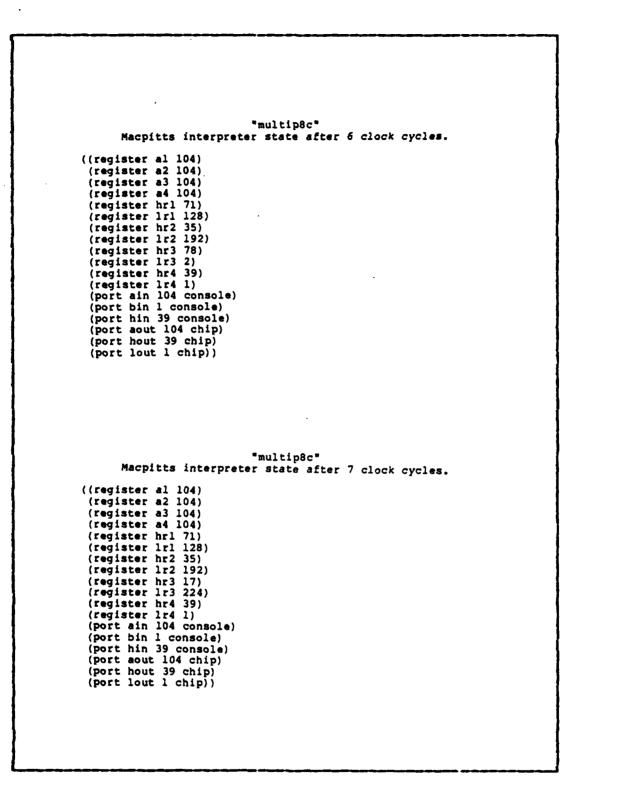

| D.1  | Macpitts Interpreter Results                        |

| D.2  | MacPitts Interpreter Results, (continued) 123       |

| D.3  | MacPitts Interpreter Results, (Continued) 124       |

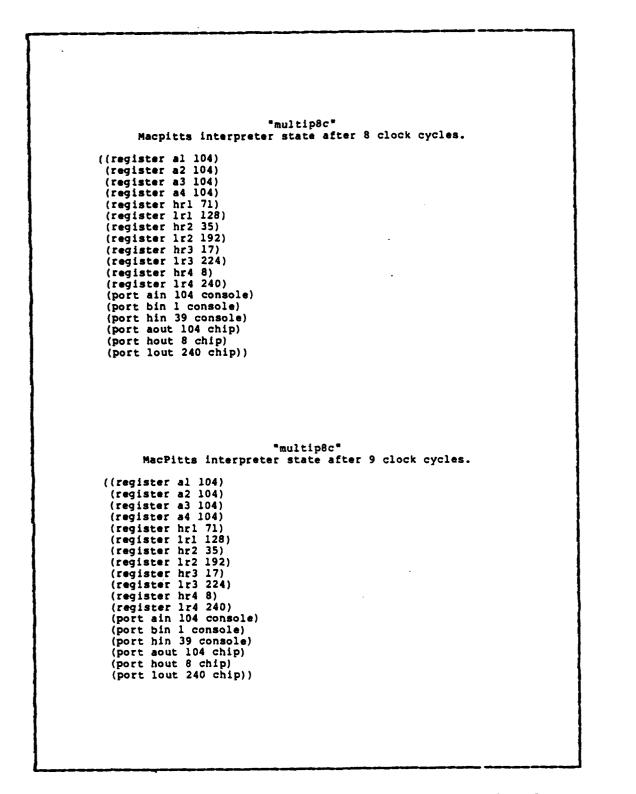

| D-4         | MacPitts Interpreter Results, (Continued) 125    |

|-------------|--------------------------------------------------|

| <b>D.5</b>  | MacPitts Interpreter Results, (Continued) 126    |

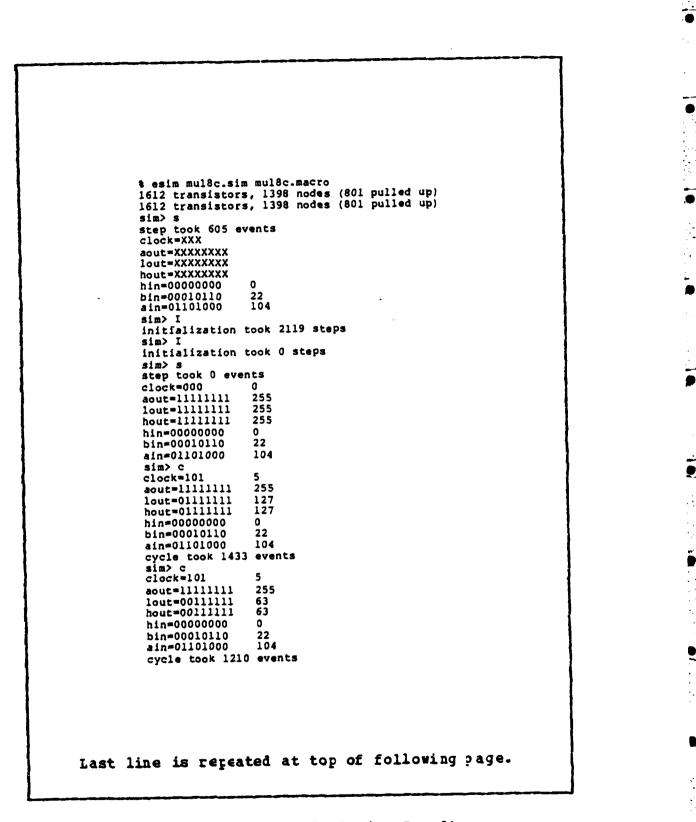

| <b>D</b> -6 | NacPitts Interpreter Besults, (Continued) 127    |

| D.7         | Event Simulation Results                         |

| D.8         | <b>Event Simulation Results, (Continued)</b> 129 |

| D.9         | Event Simulation Results, (Continued) 130        |

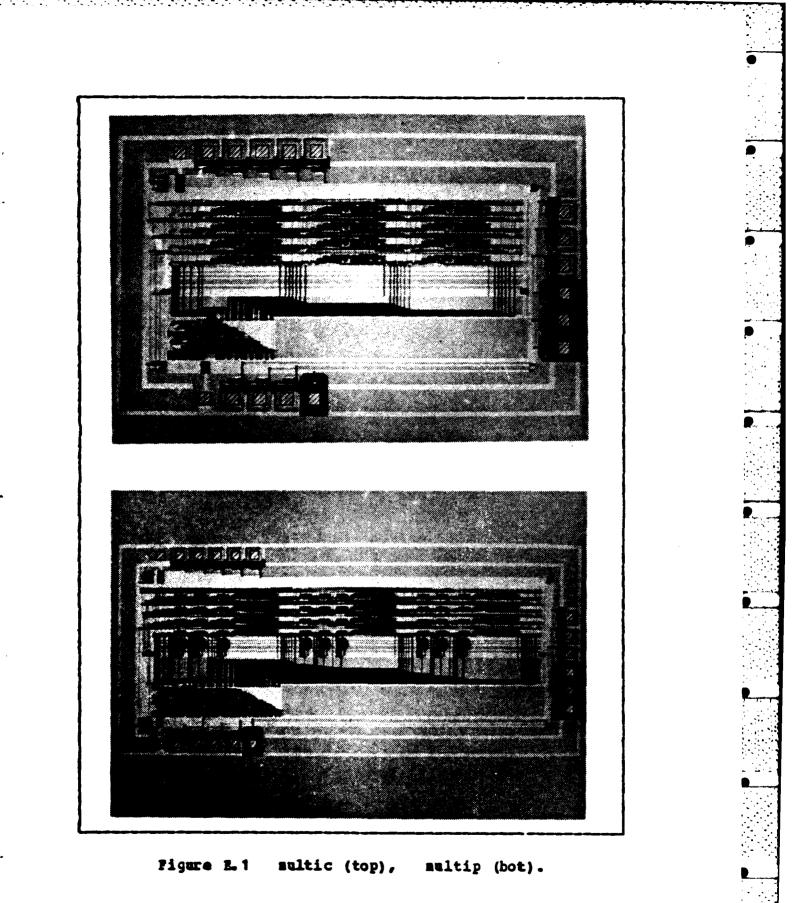

| E. 1        | multic (top), multip (bot) 132                   |

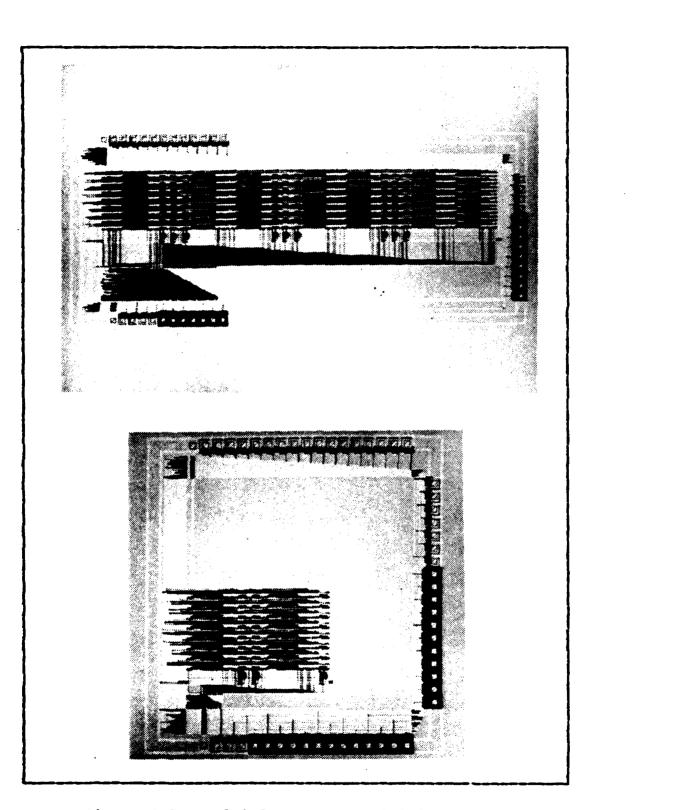

| E.2         | multip8 (top), multip8a (bot) 133                |

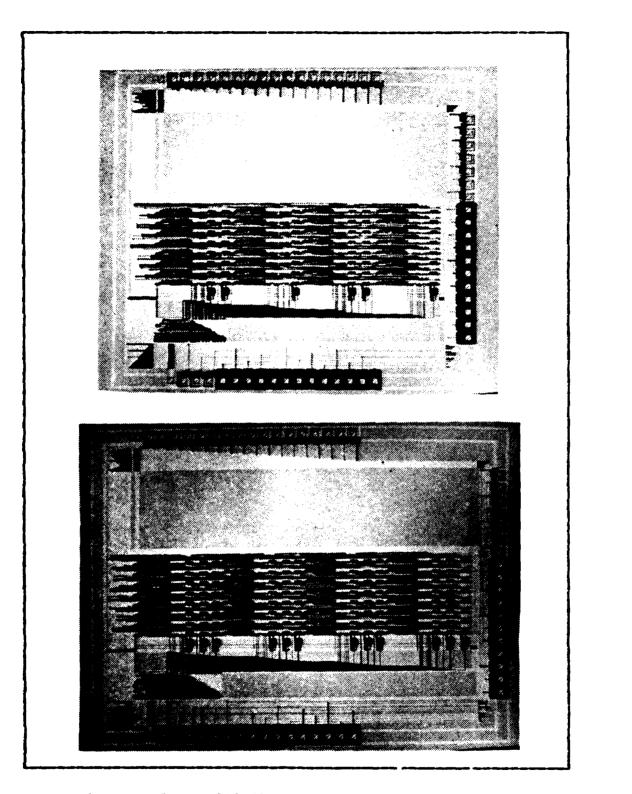

| E.3         | multip8b (top), multip8c5 (bot) 134              |

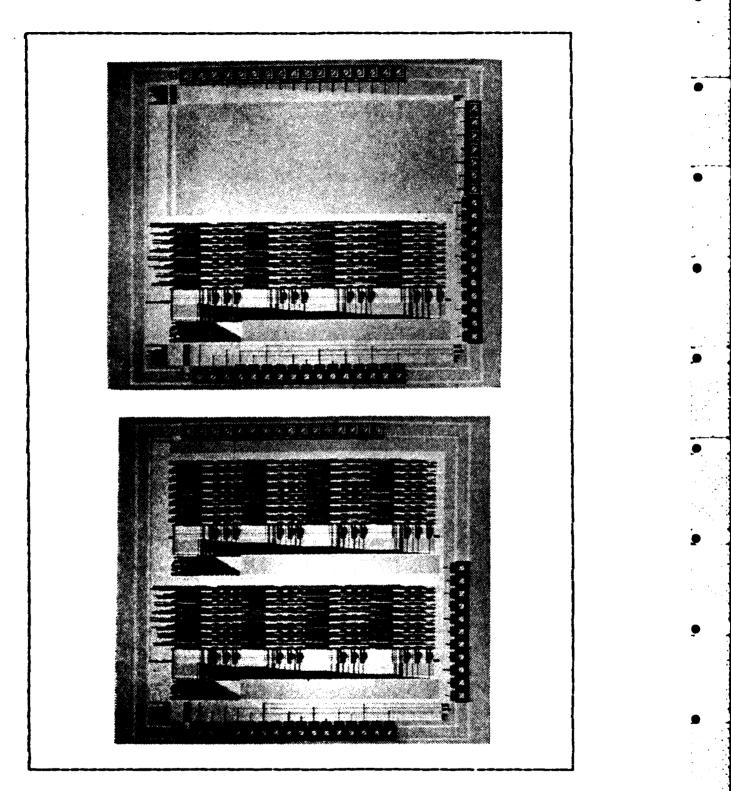

| E.4         | multip8c4 (top), multip8c4d (bot) 135            |

| E. 5        | Layout Errors in kchip2 136                      |

#### ACKNOWLEDGEMENTS

I would like to thank the following individuals for their assistance in the completion of this thesis: Naval Postgraduate School Dr. Donald Rick Prcf. Robert Strum Dr. Herschel Loomis Mr. Al Wong Massachusetts Institute of Technology Linceln Laboratery Mr. Kenneth W. Crouch Dr. Antun Demic University of California at Berkeley Dr. John K. Custerhout Dr. Keith Sklover Stanford University Dr. Robert Mathews Hs. Susan Taylor University of Ransas Dr. Gerry L. Kelly

#### I. INTRODUCTION

#### A. BACKGRCUND

The initial work done on the design of very large scale integrated circuits (VLSI) at the Naval Postgraduate School (NPS) used a set of software tools which require designer interaction at all levels of the design process. These tools and their use is described in a recent thesis by Conradi and Hauenstein [Ref. 1].

Their design approach centers around the use of: (1) machine-generated programmable logic arrays (PLA's) specified in a language which translates boolean equations into circuit layouts, and (2) a library of standard cell layouts from which other required circuit primitives are selected. The designer arranges the PLA's and standard cells cn a "floorflan" designed by heuristic methods, and interconnects them with a network of individual wires devised by the designer and encoded as a "wirelist." The floorplan layout and addition of interconnecting wires must be done manually, typically on graph paper at the drawing board. The results are manually encoded in an input file format readable by a layout language program ("cll" in the case of the cited research) which merges the designer's floorplan and wirelist (1) the selected library cell layout descriptions and with: (2) the FLA layout descriptions produced by the separate FLA generation program. The circuit layout program then produces a description of the total design in another standard file interchange format, the Caltech Intermediate Form, (CIF) described by Mead and Conway [Ref. 2: pp. 115-127]. The CIF file can then be used as a source for extracting design validation information, as well for producing the photographic masks used for circuit fabrication.

The design process outlined has the advantage of giving the designer thorough control over the architecture of the circuit. The human ability to evaluate alternatives, recognize patterns and grasp complex multi-dimensional relationships between individual elements and the whole design exceeds that of any current machine algorithm.

Cn the other hand, this process absorbs large ancunts of the designer's time in performing the drudgery of planning and encoding the laycut details. There are at least four things wrong with involving the designer at this level:

(1) It is repetitious work, and therefore error-prone.

(2) It is slow. (Southard [Ref. 3] and others have noted that design costs far outweigh production costs for custom VLSI.)

(3) Preccupation with mechanical details restricts a designer's freedom to explore high-level architectural issues such as bus structure, degree of pipelining, and speed-complexity tradeoffs.

(4) Major modifications to the layout are very expensive to make if they come late in the design cycle, i.e. after cell interconnection.

#### E. CUBBENT RESEARCH GOALS

With this background for motivation, it was decided to investigate additional VLSI computer-aided design tools which would reduce time-to-design, minimize the occurrence of human error in layout, and make it possible to explore design alternatives with greater ease.

The major tool available in the VLSI research community for this purpose is MacPitts. MacPitts (the name is derived from two early researchers, McCulloch and Pitts who studied neurological systems from a mathematical and logic standpoint) is a silicon compiler developed at the Massachusetts

Institute of Technology's Lincoln Laboratories in 1981-1982 [Ref. 4]. A silicon compiler, according to one recent definition [Bef. 5] which captures current usage of this cften **Eisunderstood term**, is "a program that, given a description of what a circuit is supposed to do, will produce a chip layout that implements that function in silicon." There is enough latitude to allow fundamentally different approaches to silicon compilation to coexist under this definition, as will be demonstrated in the following chapter. In any case, however, the term compiler is apt. Like software compilers, these programs take high-level source code descriptions which are human-readable (and perhaps, but not necessarily, algorithmic) and "convert" them into low-level object code (a CIF file) which is directly readable by a machine. In the case of a silicon compiler, however, the machine is not a general-rurpose computer, but a photo-resist mask generator at a silicon foundry facility that fabricates integrated circuits.

Another function that the most advanced silicon compilers perform is resource allocation. Software compilers free the programmer from making decisions on where in available memory space to store a particular machine code Silicon compilers, at their best, free the designer word. from deciding where cn available silicon area to place a particular circuit element. Resource allocation is a onedimensional job in scitware compilers, but a two-dimensional job in silicon compilers. The constraints on efficient resource allocation in silicon are severe--compactness is almost always one gcal, as is speed of operation (minimum propagation delay.) In <u>memory</u> allocation, compactness is not essential, unless one is using a sequential access memory.

Installation of MacPitts on the NPS VAX-11/780 computer facility was expected to be a "turn-key" operation. This was in fact not the case. A large amount of effort was

spent in researching and performing the modifications to the host computer environment which enable it to run the MacPitts system, as well as in troubleshooting the distributed MacPitts source code itself. The installation process is described in Appendix A.

MacPitts has no progressive breakpoint facilities to allow a designer freedom to observe or alter the layout Once invoked, process at any point during execution. MacPitts produces a final interconnected layout, complete with bending pads, or no layout at all. Therefore, it was considered worthwhile to implement the color graphics designed by editor, Caesar, John Ousterhout at the University of California at Berkeley [Ref. 6]. This tool allows the chip laycut to be examined in detail on a color CRT menitor, and permits editing of the layout. Caesar represents the layout internally as a hierarchy of  $c \in Ils$ , which yields insight into the ways that MacPitts partitions the layout process.

The installation of Caesar, while not as difficult as MacPitts, involved setting some site-dependent parameters as well as finding and correcting a bug in the distributed source code. These activities are described in Appendix B. Appendix C contains a copy of the on-line manual pages for Caesar and other Berkeley tools used in this research.

## II. APPROACHES TO SILICON COMPILATION

#### A. VISI DESIGN ACTIVITIES DOMAIN

When trying to understand how silicon compilers work it is instructive to think of two design problems in the order in which they must be attacked. The first is translation of a brief behavioral cr functional description into a mcre precise intermediate description that is still independent of the specific implementation technology. The second is the automatic generation of a chip layout in a target semiconductor medium, using the intermediate description as a guide. It is important to separate the second activity from the first when one is designing a silicon compiler because of the speed at which the target semiconductor technologies are evolving. That is, complementary metal oxide semiconductor (CMOS) processes are rapidly overtaking N-channel metal oxide semiconductor (NMOS) processes. Multiple-layer metalization is also becoming more common, and minimum circuit feature sizes are shrinking as better control over the manufacturing processes is achieved. Computer architectures and functions evolve more slowly, by comparison.

These two problems may be further subdivided. Werner [Ref. 7] has contributed the idea that a spectrum of VISI design activities exists with corresponding media for the exchange of information by the computer-aided design tools employed at each band in the spectrum. (See figure 2.1.) Silicon compilers try to span the whole spectrum, an ambitious undertaking.

Geometric (Mask-Level) 'Silicon'' Description Symbolic Layout without Compaction Symbolic Representation without Compaction (Conventional) Automatic Layout Tools (Placement and Routing) VLSI Design Activities Spectrum [Ref. 7]. (Conventional) Symbolic Layout with Compaction Structural Information Textual Description of Assembly of Symbolic (Data Path Gen.) Model Compuers (PLAWeinberger, etc.) Intermediate Level Descriptions Representation (with Compaction) Silicon Assembler Logic Diag/ Network Description -----Boolean Description Functional/Logical Information 🗢 "Ideal" suicon compiler (for an anive chip) **Figure 2.1** Register/ Transter Level Description Logic Synthesis High-Level Behevioral/ Functional Desc. of a System

-

----

## E. EVALUATION CAVEAT

It should be recognized that all silicon compilers designed to date have to some extent traded performance of the ultimate VLSI design (as measured by operating speed and area efficiency) for reduced design time for the chip (and for the silicon compiler itself.) Gross [Ref. 8] quotes estimates for reduced design costs (time) by use of broad spectrum silicon compilers to be a factor of 20. But Wallich, in a recent survey of silicon compiler efforts [Ref. 5], states that designs produced by silicon compilers available today tend to range from 15 to 200 percent larger than equivalent hand-crafted designs.

Still, silicon compilers have been misunderstood by Some, without fully underresearchers as noted by Gross. standing the dimensionality of the VLSI design process, believe that the design problem can be almost completely solved by the application of current software methods and Others, seeing the obvious limitations of contempotools. rary silicon compilers and not grasping the potential contributions to VISI from computer science technology transfer, believe that efficient VLSI designs will always be essentially manual. Murphy of Bell Laboratories, quoted by Werner [Ref. 7], states that "total automation is inappropriate--either now or in the foreseeable future--in anything where you have a competitive need for performance." Hevertheless, Bell Labs is conducting research of its own into silicon compilers. Their "Plex" project reported in a more recent paper [Ref. 9] produces layouts of microcomputers given, as input, the program (in assembly or C language) that the microcomputer is to execute.

According to Wallich, the ultimate silicon compiler, now just a dream, will not only be able to take a behavioral description and produce a geometrical description of the

chip suitable for input to a Bask Making Machine, but will for any kind of chip--microprocessor, do sc signal or even analog-digital hybrid for which the FROCESSOF, design rules are far more complex. The subtle process of architectural optimization (i. e. selecting a best floor plan from the myriad possibilities.) which occurs in the middle of the design activities spectrum, has so far not been captured in an algoriths. То achieve some breadth without keing overwhelmed by complexity, silicon compilers have tended to contain built-in assumptions about a "target architecture." They are optimized for producing a certain circuits--mostly microprocessors--and class of produce layouts of reasonable area and speed only for applications test suited to their target architecture.

#### C. LINITED SPECTRUM COMPILERS (TRANSLATORS)

For completeness, it is necessary to mention these VISI design tools in current use which fall short of covering the design spectrum. They are:

- Randcm logic/Standard-cell place-and-route systems,

- Nodule compilers to implement boolean logic, including:

Gate array compilers,

- PLA generators,

- Regular expression compilers for

- finite-state machines,

- Layout Languages,

- Interactive graphical layout editors.

## D. BROAD-SPECTROM SILICON COMPILERS

### 1. Flocr Planners

#### a. Common Properties

The first broad spectrum translators of interest are the floor planners. They all employ a structural specification language in which the specification always corresponds extremely closely to a description of the designer's mental model of how the chip should be laid out. They produce, as an initial output, a skeleton of the layout Subsequently, similar to an architect's floor plan. flcor planners fill the "rooms" with cells from a standard library. Some floor planners, of which Johannsen's Bristle Blocks is a pioneering example [Ref. 10], can linearly stretch cells to match up the interconnections of abutting cells (so-called "pitch matching.")

### Ł. F.I.R.S.1.

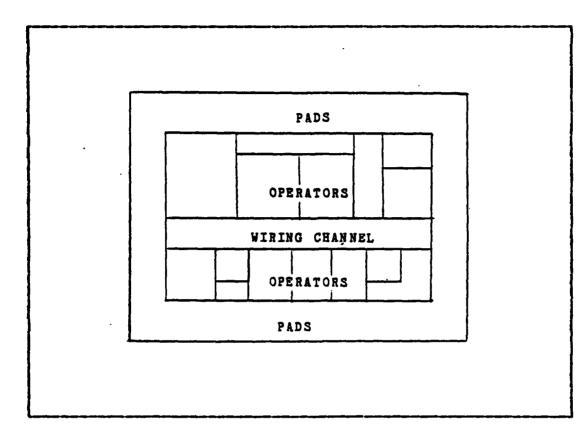

The current state of the art in floor planners is represented by the F.I.R.S.T. (Fast Implementation of Beal-Time Signal Transforms) silicon compiler developed at Edinburgh University [Ref. 11]. The F.I.R.S.T. compiler produces layouts of digital signal processing systems implemented as hard-wired networks of pipelined bit-serial crera-The floor plan of F.I.B.S.T. chips (see figure 2.2) tors. consists of a central wiring channel with operators arranged as function blocks around the "waterfront." Each bit-serial operator is implemented as a separate function block which in turn is assembled from a library of hand-designed cells. The function blocks are arranged, in the order of their high-level specification by the designer, in two rows along either side of the wiring channel which accommodates all interconnections between the blocks. This uncomplicated and

### Figure 2.2 Typical floor plan produced by the F.I.B.S.T. Silicon Compiler.

novel layout methodolcgy results in the non-use of about 20% of the total chip area (because the blocks may have varied heights.) At present, F.I.R.S.T. supports only the N-channel metal oxide semiconductor (NMOS) technology.

The F.I.R.S.T. software consists of a small suite of programs which provides the designer with a complete specialized design environment. At the top level is a language compiler that accepts a structural description of the circuit in terms of a net list of bit-serial operators. The F.I.R.S.T. system contains a library of primitive operators, (such as MOLTIPLY, ADD, SORT, BIT DELAY, ETC.) as well as a number of more complex procedural definitions (such as Biquad, Lattice, Butterfly, etc.) that enable a

range of signal processing architectures. The language compiler produces an intermediate level format file as output. This file is used by both a layout program, which produces the mask geometry, and a simulator. The simulator is event driven, which means that the voltage values on circuit nodes are modeled as discrete bits of data occurring at discrete time intervals. The functioning of individual operators is simulated on a word-by-word basis in response to a file of input commands. It is asserted that the simulator has the ability to uncover timing bugs in the data stream.

A unique and useful aspect of F.I.R.S.T. is incorporation of a translator program to convert the simulator's output into a form suitable for use with an automatic test fattern generator system.

## 2. <u>Eehavioral Specification Compilers</u>

a. Common Properties

In contrast to the floor planners, which accept <u>structural</u> specifications at the top level, are the <u>behav-</u> <u>ioral</u> specification compilers, which do not require the designer to possess a prior mental model of the architecture to be designed. These systems attempt to translate a highlevel behavioral description of the circuit into a geometric mask description. This step is a significant one over floor flanners.

L. Ayres' Work

Ayres is the first to have written a book-length treatment of silicon compilation [Ref. 12]. Ayres' compiler approach starts with a synchronous logic specification of the chir behavior. Then follows a decomposition of this specification repeatedly into a hierarchy of implementing

BHOS FLA's which beccme successively more area-efficient as they become smaller. The system includes heuristics to manage and optimize cn-chip routing among the PLA's generated. Ayres' compiler is potentially applicable to a broader class of circuits than F.I.R.S.T., but is still not efficient for a general range of problems. The sccre of applications vas restricted intentionally to control complexity. The very use of PLA's as the sole tasic building block restricts the area efficiency of this system. Even though the PLA's themselves become more area-efficient as they become smaller, the difficulty of managing their interconnections limits the ultimate efficiency of the layout.

c. MacPitts

MacPitts is the only broad spectrum silicon compiler with which this author has had any first-hand experience. It is also the most widely known and most ambitious behavioral specification compiler in operation.

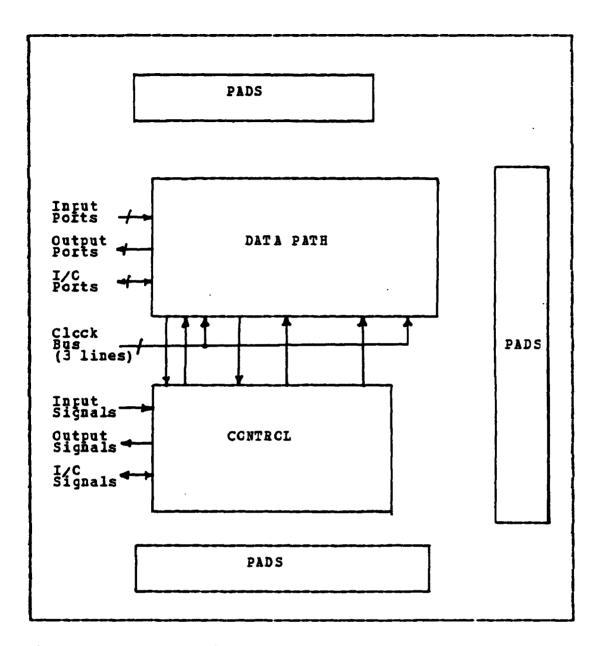

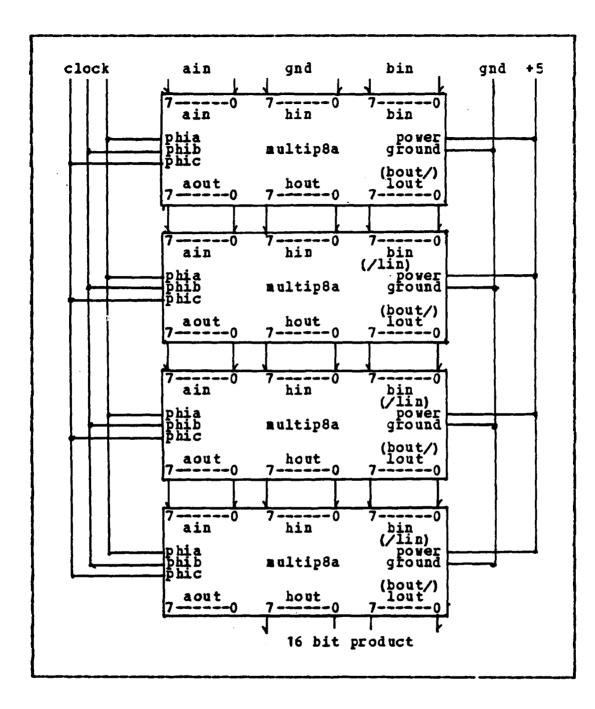

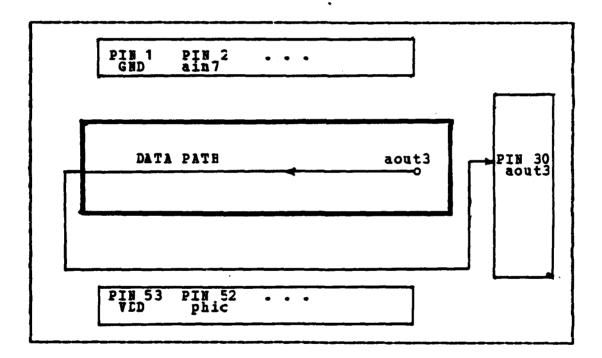

The hardware specification generated by MacPitts is in the form of an MMOS technology CIP file. To cope with the ccarlexity of this project the designers restricted the target architectures to microprocessors consisting of a data path and a controller (see figure 2.3.) Other restrictions include fixing the width of the data path to one value throughout the design, and requiring the designer to specify control and paralleliss explicitly. The latter is not actually a restriction in one sense, however, because it affords greater generality in designs. Except for making pin assignments, the MacFitts user has no explicit control over the floor glan of his design. The MacPitts target architecture results in the same basic floor plan for all designs, although this particular architecture is applicable to a greater variety of digital problems than any other scheme presently available.

The data rath portion of the layout consists of a rectangular array of units called "organelles." An organelle is a hit-wise functional unit. A standard library of functions--adder, subtracter, shifters, incrementers, comparators, etc.--is provided. Also, if the algorithmic behavior specification calls for conditional data flow or looping, the data path may also include multiplexers which have connections for control signals. This multiplexer organelle is not a litrary cell but is built into MacPitts. Data storage registers, implemented as master-slave flipflops, are also "built-in organelles." These are instantiated in the data rath if their use is implied by the algorithmic specification.

The vertical dimension of the data path outline in figure 2.3 corresponds to the number of bits in the data word. Longer word-lengths produce a taller chip. The various organelles are cascaded along the horizontal dimension of the data path outline.

The control portion of the layout acts OD various signals, either derived from the data rath OT outside the chip, and implements whatever boolean logic is necessary (as inferred from the algorithmic specification) to generate controls signals to drive the multiplexers in The result is an implementation of a finite the data path. state machine, (FSM) as described in Mead and Conway [Ref. 2]. The control unit does not use PLA's, but rather structural NOR gate arrays called "Weinberger Arrays" which implement arbitrary combinational logic functions. can Weinberger [Ref. 15] demonstrates that his logic arrays have three features which contribute to efficiency in an automated circuit layout scheme.

- They simplify the formation of interconnection patterns within the framework of a standardized layout.

- They significantly reduce the required area (by eliminating unused inputs and separate interconnection areas.)

- They eliminate crossing of signal nets (by using single level wiring.)

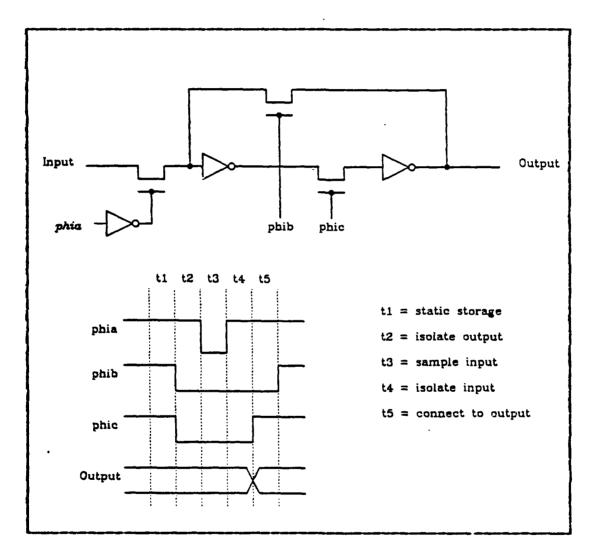

State timing is controlled not by a two-phase non-cverlapping clock, which is somewhat standard in NMOS VLSI, but by a three-phase clock which drives the register circuit shown in figure 2.4. This clocking scheme apparently allows a more compact layout of the register crganelle, but requires an extra pin in the package.

Figure 2.4 HacPitts Register Circuit and Timing Diagram.

One of the authors of MacPitts, Siskind guoted in [Ref. 7], admits that optimizing chip performance was not a primary design gcal. Circuit densities reported were 80-100 transistors per square millimeter in 5 micron feature size NMOS--approximately 2 orders of magnitude lower than the state of the art layouts reported in Gross [Ref. 8]. Southard contends that the cells he helped design for MacPitts could fairly easily have been made 20 per cent smaller than they are [Ref. 5].

MacPitts cnly produces NMOS output in CIF, but the user has a chcice of either 4 or 5 micron minimum feature size, which the compiler handles by linearly scaling all features except the pads. The latter are contained in two separate libraries for 4 micron and 5 micron designs.

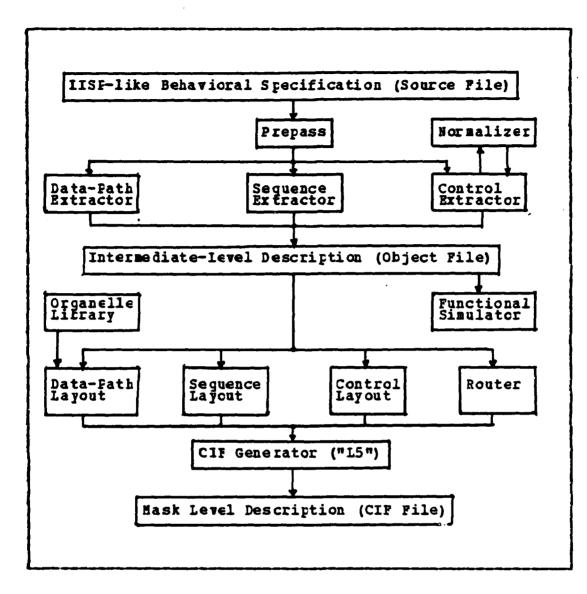

From the programming viewpoint, MacPitts is a very complex system. It consists of a binary executable module of over 1.5 megabytes which was built up as a LISP programming environment and then dumped, as described in the Franz Lisp manual [Ref. 13]. A synopsis of the functional elements which make up this LISP environment is shown in figure 2.5. Unlike F.I.R.S.T., these programs (except the functional simulator or "interpreter" as its authors call it) are not individually accessible. MacPitts runs automatically from beginning to end with no possibility for operator intervention. The only control available at the console when the compiler is running is the standard UNIX system abort signal.

The authors of MacPitts were careful to separate all the processing into technology independent (front-end) and technology dependent (back-end) portions, with the intermediate-level description being the point of division. This intermediate-level description is available to the user as an "object file" in human readable form. It is possible, although not very fractical, to write an object file

Figure 2.5 HacPitts Program Data Flow.

directly for input to the back end of MacPitts. The object file is a long list containing 5 elements, each element being itself a list. The 5 elements are: definitions, flags, data path, control, and pins. This list is, of course, in a form readable by the layout programs.

The layout programs produce only NMOS technology. As mentioned above, two bonding pad libraries are

the Stanford standard cell library pads includ∈d: for 5 and the MOSIS ARPA community pads for 4 micron designs, micron designs. The "layout language" and CIF generation program, L5, which is embedded in MacPitts, was written especially for the project by Crouch [Ref. 14]. It has built-in facilities to handle both NMOS and CMOS technology Therefore, expanding MacPitts to produce CMOS CIF layouts. would not entail a complete rewrite of the back end programs.

An important feature of the MacPitts software is the functional simulator or interpreter. A MacPitts program is not only an IC specification, it is also an algorithmic The interpreter executes the specification specification. program as a general-furpose computer using an interactive, screen-oriented input/output style. By invoking this option of MacFitts the user can exercise his design, thereby validating (to whatever extent the exercise is complete) its functional fidelity. Once the functional simulation is done to satisfaction, MacFitts can be restarted without setting the interpreter opticn. This produces a finished layout and corresponding CIF file. By using the same language to drive both the interpreter and the integrated circuit compiler, human error is reduced.

MacPitts lacks some features. It has none of the capabilities of F.I.R.S.T. to produce a test pattern to exercise the chip. It also lacks any built-in mechanism to identify worst-case path delays or to predict the maximum clock frequency of the finished chip. It does keep account of conductivity information, however, which it uses to predict chip power consumption.

MacPitts uses a "correct by construction" doctrine in the laycut process. By denying the user the means to specify the layout details of the chip, this approach also denies the user the opportunity to commit

design rule errors or to translate the specification program into a non-corresponding layout. But can MacPitts itself make design rule errors?

The following chapters examine how to use MacPitts to produce an integrated circuit layout, how to validate the design, and where to look for ways to improve chip performance.

## 111. USING MACPITTS

A. IEE INPUT FILE

## 1. Fundamentals of the MacPitts Language

"MacPitts," the system for generating a custom integrated circuit, is also "MacPitts," the language in which the algorithm is specified. In this section the second meaning is the one implied. All of the information which specifies what functional behavior is required of a VLSI circuit is communicated to MacPitts in a single text file. This file, which must have the extension ".mac", is written using syntax which closely resembles that of the LISP programming language. Because the MacPitts compiler is implemented in LISP, it is reasonable to expect the syntax of the MacFitts design language to follow the LISP parenthesized notation. This choice was made by the authors of HacPitts because it eliminates the need for a separate parser.

LISE is a list processing language. Its data elements are "symbolic expressions" made up of "atoms" (fundamental word-like objects separated by spaces), lists of atcms, lists of lists of atoms and so on. One of the strengths of LISP is the ability to concatenate atcms or lists into new lists, and to perform other operations on a list cr a hierarchy of lists to produce new lists modified LISP has many built in functional definiin useful ways. tions which are an "environment" of specifications for the operations to be performed on lists. These definitions are all contained in The Franz Lisp Manual [Ref. 13]. In addition to using these definitions, the LISP user is free to extend the LISP environment by defining new functions which

specify other operations on lists. The types of operations may be simple manipulations of the atoms by partitioning or permutation, or, if the atoms which comprise the list happen to be numbers, arithmetic operations may be performed. Ihe definitions of the operations themselves may also be assemtled from lists of more primitive operational atoms. This functional extension of operations is what the authors of BacPitts have done in creating the MacPitts Lisp environment.

The design of a VLSI circuit can be thought of as a list-building process in which the lists are electrical rorts, registers, interconnection nets, data testing operaand ultimately a string of words which define a tions, unique patterning of silicon in the mask level descriptive These lists are built according to rules language, CIF. contained in another list--the algorithmic specification source file. Although the MacPitts design language resenbles IISF syntactically, its semantics is different and much more limited. A powerful feature of LISP is, for example, recursive definition. This feature is absent in the MacPitts design language. A description of the MacPitts grammar in Eackus normal form is given in [Ref. 4].

In its most general form, a MacPitts "program" to specify a circuit's behavior consists of a set of "processes," each of which executes sequentially, but all of The states of each process are which run in parallel. fundamentally disjoint from those of the other processes. This allows the hardware for each process to run independently of the other processes, if desired, and concurrently with the states of the other processes, in any case. The operations performed by a given process in a given state are specified by a "form." Each form corresponds to a single machine state, and is executed in one clock cycle. A state say be given a name by preceding the form with a label.

Normally execution proceeds sequentially from one state to the following state in the .mac file at each clock cycle. A "go" form can be used, however, to deviate from this sequential flow by causing the named state to be executed next instead of the syntactically following state.

Lata is communicated between the data path and the external world through "ports" which have the same bit width as the data path. Cnly a single data path width definition is allowed per program. A port may be declared "input," "output," "tri-state cutput," or "i/o." Ports may also be declared as "internal," in which case they simply cascade the output of one data path operation to the input of another. The data rath may also be specified to contain The difference between internal ports and regisregisters. ters is that registers can store data indefinitely after it has been clocked in, whereas ports are only electrical nodes in the data path and therefore do not store data. Ports simply are arrays of named terminals for conducting data from one point to another.

Control of operations performed on the data by the data path crganelles is governed by the Weinberger array control unit. Control outputs from the control unit to the data path may determine, by means of their control over sultiplexer organelles within the data path, which crerations cccurring within the data path will affect downstream Status outputs from the data path returning to organelles. the control unit allow the sequence of operations performed by the control unit to vary depending on the data present either in the registers or at any other point in the data rath. The control unit functions may also be made to depend upon external inputs. The control unit communicates with the outside world using "signals," which are analogous to the "forts" used by the data path except that each signal appears on a single wire. Signals may be declared as "input," "output," "tri-state output," "i/o" or "internal."

Operations performed by the data path during a given state are specified by the IISP "setq" form. The seta causes the data gath to evaluate a sequence of operations on either input port data, internal port data or register data. (The setg may also be used with signals.) The result of these specified operations is then conducted to another named port or loaded into a data path register during the The compiler includes enough copies of next clock cycle. each operator in the data path so that separate processes, intended to run in parallel, do not conflict over the attempted shared use of a single resource. The data path can cascade several crerations together in a single form. This allows forms such as the following example, which computes a=b-c using 2's complement arithmetic, to execute in one clock cycle:

## (setg a (+ b (1+ (not c))) .

The list consisting of everything on the preceding line is a single form. There are three operators in this expression: "+," which specifies use of an adder, "1+" which specifies an incrementer, and "not" which specifies an inverter. Each operator is followed by its operands listed in <u>symbolic</u> notation. Therefore, the single operand of 1+ is the integer that results from <u>evaluating</u> the expression "(not c)." Note that there is not a default hierarchy of operations within a form. As with LISP, the order of operations in MacPitts must be specified explicitly by the use of nested parentheses.

Sequences of setq forms normally operate sequentially, each being executed on a separate clock cycle. By enclosing the forms within another "parallelizing form," of which "par" is an example, several forms can be made to run in parallel, gaining speed over sequential operation at the cost of more hardware and hence more area in silicon. The par form is used as follows:

#### (par form1 form2 form3...)

Of course the results obtained by running setq forms in parallel may be quite different from those obtained by running them all sequentially within one process. Consider the following example where "a" and "b" have already been declared registers (i.e. master-slave flip flops):

(par (setg a b)

(setg b a)) .

This expression will result in exchanging the contents of "a" with contents of "b." The exchange will be done in one MacPitts clock cycle. This action is made possible by the input isolation which occurs during the flip-flop operating cycle. All such data storage elements are read before they are written. On the other hand, sequential operation of the same setg's is implied in the following process:

(process load1 (setg a b)

(setq b a)) .

This precess will lead both b and a with the criginal contents of b, and require two cycles to do it. (Here "load1" merely furnishes a process name, as demanded by the MacPitts grammar.) We have used two lines and indented format only for the sake of clarity. All the functional information meeded by MacPitts is denoted by the ordering of forms within the nests of parentheses.

The "cond" form allows the conditional execution of cther forms it contains during a given state. It consists of a list of guards, only one of which is to be executed. Each guard begins with a "condition" which determines whether the remaining forms in the guard are to be executed. The first guard whose condition is true enables the execution of the forms following the condition in that guard. This is illustrated by the following example adapted from [Ref. 4].

This example is heavily nested. Nevertheless, close examination reveals that the outermost "(cond..." has only two guards in its list, each of which contains other "(cond..." forms. The two guards are:

and

(condition4 (cond (condition5 form7 form8))

(cond (condition6 form9))

form10) .

If condition1 is false and condition4 is true then form10 is executed. If condition5 is true then form7 and form8 are executed along with form10. Likewise if condition6 is true then form9 is executed in parallel as well.

The semantics of the cond statement is inherently parallel. The conditions of the alternate guards are checked in parallel. Likewise, all forms within the guards are executed simultaneously in one clock cycle. The compiler makes the conditions of different guards in one cond form mutually exclusive, and implements them using combinational logic in the control unit as described above. This logic is used to enable or inhibit the execution of forms controlled by that guard in parallel.

Note that the form:

## (cond (t form1 form2 form3 ...))

is used to enable parallel execution of several forms during one clock cycle without being dependent on <u>any</u> condition. (The "t" stands for "true.") The "(par..." form already encountered is actually just a shorthand macro expression for the "(cond (t..." form.

In a MacPitts layout, the conditions are formed in the control unit, which is a Weinberger array of NOR gates [Ref. 15]. Therefore, they are not limited to cnly the sun-cf-products notation used by PLA-based finite state machine comrilers. The conditions are derived from either signals arriving on an input pin, signals from the data cath. or signals arriving from other processes. More complex conditions can be constructed from these signals using the logical operators "and," "or" and "not" to build arbitrary Boolean expressions. These operators are part of the MacPitts library cf functions. Thus, the cond statement is cne cf the most powerful features for providing high performance designs.

With this brief and somewhat condensed description of the features available in the MacPitts algorithmic language, the way is prepared to to understand an example of some code which will produce a complete integrated circuit chip. A full detailed description of all the facilities of MacPitts is found in a report authored by its creators [Ref. 16], which also serves as a fairly complete users' manual.

#### 2. Ivo Multiplier Examples

Consider, line by line, figure 3.1 which is a listing of the file multic.mac. This example and the one which follows it are inspired by similar ones in [Ref. 16]. It contains all of the design information needed by MacPitts to produce a 4 bit combinational multiplier. On any line,

; multiplier, no state combinational (program multic 4 (def 1 ground) 3 (def ain port input (2 3 4 5)) (def bin port input (6 7 8 9)) (def res port output (10 11 12 13)); result (def r0 port internal) 6 7 8 (def rl port internal) 9 (def r2 port internal) (def 14 phia) 10 (def 15 phib) 11 12 (def 16 phic) (def 17 power) 13 14 (always (cond ((bit 0 bin) (setq r0 (>> (bit 0 ain) ain))) 15 16 17 (t (setq r0 0))) (cond ((bit 1 bin) (setq r1 (>> (bit 0 (+ r0 ain)) (+ r0 ain)))) 18 (t (setq r1 (>> (bit 0 r0) r0)))) 19 (cond ((bit 2 bin) (setq r2 (>> (bit 0 (+ rl ain)) (+ rl ain))))

(t (setq r2 (>> (bit 0 rl) rl)))) 20 21 (cond ((bit 3 bin) (setq res (>> (bit 0 (+ r2 ain)) (+ r2 ain)))) 22 (t (setq res (>> (bit 0 r2) r2)))))

Figure 3.1 Multic.mac Source File.

text following a semicolon is treated as a comment, which the ccapiler ignores. Line 2 tells the compiler that a "program" (which is another way of saying, "circuit design") called "multic" starts here, and that the data rath is 4 tits wide. Because the data path is only 4 bits, this simple multiplier will only be able to output numbers from 0 to 15. Even though the input ports are also four bits wide, we must restrict input numbers to only those whose product falls in the range of values from 0 to 15. Furthermore, if this algorithm is to give correct results for all multipliers, without overflow, the leading bit of the multiplicand must be zero. No provision is made to output a flag if the dynamic range of the multiplier is exceeded.

Lines 3 through 13 declare the various signals and integer data words input to, output from and existing within the multiplier. Line 3 assigns the ground connection to pin 1 which is always in the upper left corner of the layout; subsequent pin numbers proceed clockwise from this point around the layout perimeter. Line 4 assigns pins 2-5 to an input port labeled "ain." This input is the multiplicand. By MacPitts convention, the most significant bit (MSB) of ain is read from the first pin on the list, pin 2, and the least significant bit (LSB) from the last pin on the list, Line 5 similarly defines the multiplier input port, cin 5. "bin." Line 6 assigns an output port labeled "res" (for result) to another block of 4 pins. This port also serves as the accumulator for the fourth and final partial product. Lines 7 through 9 define 3 internal ports (necessarily of width 4 tits) labeled r0, r1 and r2. These serve to cascade the three stages of a standard shift and add algorithm. Each port contains one of the first three partial products, each being the result of operations conditioned on cne of the sultipler bits. Lines 10 through 12 assign pins to the three phase clock, whether that clock is used by the circuit In multic.mac the clock is not used. or not. Line 13 defines the + 5 volt direct current power, Vdd, connected to cin 17.

Line 14 signifies that the functions which follow, up to the matching right parenthesis on line 22, are to execute on every clock cycle. The "(always..." form is really the "(process..." form, reduced to a single state. Moreover in this case, given the (always... form, <u>and</u> given that the data path contains only ports and not registers, the inputs will affect the result after an interval governed only by the sum of the physical gate delays in the data path and control unit. There is no controlled latency in the data path, because there are no registers in this design in which to store data.

Lines 15 through 23 contain the shift and add scheme. In lines 15 and 16 the controller is told to examine bit 0 (the LSB) of bin. If it is high (true) the r0

rort takes on the value of the ain port rotated right by one bit, i.e. r0 is actually connected by means of a multiplexer organelle tc a right rotated version of ain. The shiftright-one-bit form, ">>," takes two arguments. The second argument specifies what data word is being shifted, and the first tells what to put in the MSB of that data word. Thus. a rotate is also within the capabilities of the shift form. as it is applied in this case. If bit 0 of bin is not high, then, by line 16, the r0 port--all 4 bits--is connected to In lines 17 and 18 the controller is told to around. If it is high, then r1, the next examine bit 1 of bin. internal port in the data path, is connected to a rightrotated version of the sum of r0 and ain. The adder orgamelle in MacPitts performs this summation as a standard ripple carry full addition. Note again that the expression:

(bit 0 (+ r0 ain))

in line 17 turns the single shift operator into a right rotate operator by making the MSB of r1 contain the same value as bit 0 of the sum of r0 and ain. If bit 1 of bin is low, on the other hand, line 18 instructs the controller to connect r1 to simply a right-rotated version of r0. Note that no rotations are being performed by any of these operations in the sense that a shift register would perform them. It is only the interconnections between organalles that are being set up variously by the controller to give an appearance of forwarding a rotated version down the data rath. Also note that even though the addition form appears twice in line 17, logically only one adder need be instantiated, since the operands are identical in both occurrences. HacPitts, tco, can recognize this, and will not waste space creating more adders than the minimum necessary. In lines 19 and 20 the controller examines bit 2 of bin. If it is high, port r2 is connected to a right-rotated version cf the sum of r1 and ain. If bit 2 of bin is low, r2 is connected

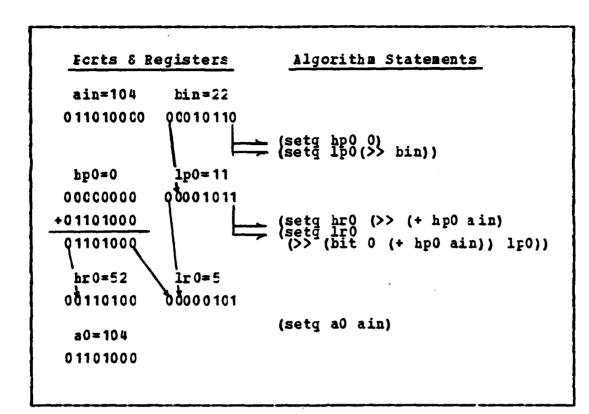

to a right-rotated version of r1. In lines 21 and 22 the controller finally examines the MSB, bit 3, of bin. If it is high, the output port, res, is connected to a rightrotated version of the sum of r2 and ain. If bit 3 of bin is low, res is connected to a right rotated version of r2. For concreteness, a schematic trace of this algorithm in action on the problem "4x3=12" is presented in figure 3.2.

Figure 3.2 Example of the Multic Behavioral Specification.

For comparison, consider now another design. This one is specified by the file multip.mac shown in figure 3.3 This is a four bit pipelined multiplier in which the product does not appear at the result port until the third clock cycle after values have been applied to the inputs, ain and bin. Changing the combinational design to a pipelined design can most easily be accomplished in two steps. First,

1 ; multiplier, with pipelining 2 (program multip 4 3 (def 1 ground) (def ain port input (2 3 4 5)) 5 (def a0 register) (def al register) (def a2 register) 6 7 8 (def bin port input (6 7 8 9)) (def b0 register) 9 10 (def bl register) 11 (def b2 register) (def res port output (10 11 12 13)) 12 (def r0 register) 13 14 (def rl register) (def r2 register) (def 14 phia) 15 16 (def 15 phib) 17 18 19 (def 16 phic) (def reset signal input 17) 20 (def 18 power) (always 21 22 (cond ((bit 0 bin) (setq r0 (>> (bit 0 ain) ain))) 23 (t (setq r0 0))) (cond ((bit 1 b0) (setg r1 (>> (bit 0 (+ r0 a0)) (+ r0 a0))))

(t (setg r1 (>> (bit 0 r0) r0)))) 24 25 (cond ((bit 2 bl) (setq r2 (>> (bit 0 (+ r1 al)) (+ r1 al))) (t (setq r2 (>> (bit 0 r1) r1)))) (cond ((bit 3 b2) (setq res (>> (bit 0 (+ r2 a2)) (+ r2 a2)))) 26 27 28 29 (t (setq res (>> (bit 0 r2) r2)))) 30 (cond (reset (setq a0 0) 31 (setq b0 0) 32 (setq al 0) 33 (setq bl 0) 34 (setq a2 0) 35 36 (setq b2 0)) (t (setq a0 ain) 37 (setq b0 bin) 38 (setq al a0) 39 (setq bl b0) 40 (setq a2 a1) 41 (setq b2 b1)))))

Figure 3.3 Hultip.mac Source file.

the three internal ports of multic, r0, r1 and r2, are all redefined as registers. Then six other new registers, a0-a2 and 10-12 are defined to send successive values of the inputs ain and bin down the pipe in step with their corresponding partial products. The ease with which this is done (from a user's point of view) is evidence of the power of HacPitts to create custom designs.

Referring to figure 3.3 we see that the shift and add algorithm. lines 22-29, is identical to that of multic.mac. In line 19 pin 17 is defined as a "reset" signal input. The reset signal is required for any MacPitts design which uses one or more "process" forms in order that the frogram counters for all processes can always be reset to the same known state. This is obviously vital when two or more processes on the same chip must be synchronized. In the multip design, however, which uses the "(always..." form, the reset signal performs no such built in automatic function. The reset signal is available, however, for userspecified functions as well, and in this case is used only to signal a setg of all internal multiplier and multiplicand instead of passing the values one more registers to zero, step down the pipeline. Therefore, the reset is not essential to the pipeline multiplier operation here but only acts to allow the pipeline to be exptied out and to inhibit any new input data from propagating to completion, for what that may be worth in whatever the intended application. It is included here for illustration only. Recall that propagation of all input data in the pipeline (lines 30-35 or, if reset is false, lines 36-41) occurs in a single clock cycle as well, because these setq's are enclosed in the "(cond..." form, which causes them to be executed in parallel.

### B. INVCCATION OPTIONS

Equipped with one or more .mac files written to reflect the desired behavior of a circuit, the user is ready to run macpitts.<sup>1</sup> The form of the command line invocation from the UNIX shell is simply

% macpitts <program\_name> <optic a>>

<sup>1</sup>The name assigned to the executable binary file on the UNIX crerating system which embodies the MacPitts system is "macpitts." where <program\_name> would be either multic or multip, in the case of the previous examples, and <options> is any or none of the words from the list:

.

.

?• .

-----

| stat*  | nostat*      |

|--------|--------------|

| herald | noherald*    |

| cif*   | nocif        |

| obj*   | ncobj        |

| int    | noint*       |

| opt-d* | noopt-d      |

| opt-c* | noopt-c      |

| 4 u    | 5 <b>u</b> * |

|        |              |

where the \* options are the defaults and the left and right columns are mutually exclusive.

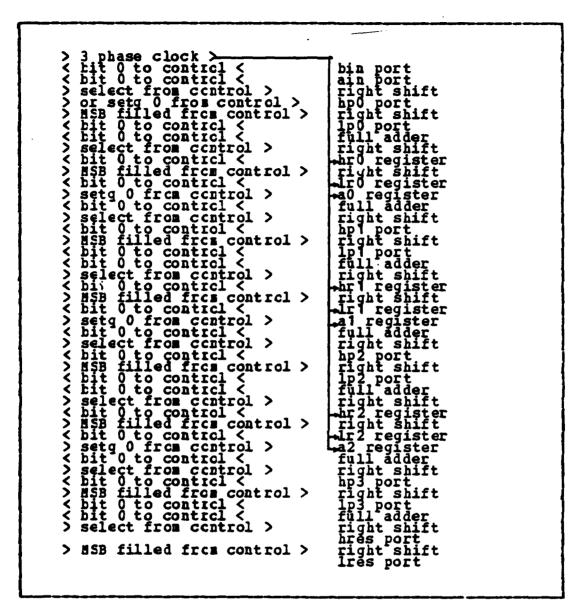

The "stat" cption tells macritts to output statistics about the chir design to the standard output device (terminal screen, normally) as various parameters are calculated. Figure 3.4 shows the statistics generated for the multip

1 Statistic - for project multip Statistic - options: (\5u herald opt-d opt-c stat obj cif) 2 Statistic - Maximum control depth is 4 Statistic - Number of gates is 60 Statistic - Data-path has 25 Units 5 6 Statistic - Control has 69 columns Statistic - Circuit has 1129 transistors 8 Statistic - Control has 17 tracks Statistic - Power consumption is 0.172120 Watts 10 Statistic - Data-path internal bus uses 5 tracks Statistic - Dimensions are 6.320000 mm by 2.847500 mm Statistic - Memory used - 526K 11 12 Statistic - Compilation took 30.432777 CPU minutes

Statistic - Garbage collection took 18.520277 CPU minutes

Statistic - For a total of 796 garbage collections 13

Figure 3.4 Compiler Statistics for multip.

chip. The meaning of these statistics is as follows. Line 1 simply echoes the program name which was given at the beginning of the multip.mac source file. Line 2 summarizes the invocation options in effect either by user selection or default.

Line 3 gives the worst-case number of logic levels between any input and any output in the control unit.

Line 4 gives the total number of NOR gates needed in the control unit.

Line 5 is the number of data rath "organelle units," where an organelle unit is a word-length assembly of organelle bits. This number is the same as the number of elements in the data path list of the multip.obj file.

Line 6 is the number of vertical metal columns in the control array, excluding the ground columns.

Line 7 is the total number of transistors in the circuit, including the data path, control unit, and all bonding pads. Line 8 is the stack beight of horizontally running polysilicon lines used to intraconnect the control unit.

Line 9 is an estimate of the worst-case static power consumption of the chip obtained using the layout topology, heuristic values of undetermined origin for the conductivity of each electrical feature, and a 5 wolt power supply.

Line 10 is the maximum stack height of horizontally placed polysilicon lines, per bit in the data path, needed to interconnect the organelles.

Line 11 is the overall outline size of the chip layout. Line 12 is the peak storage allocation demanded by macritts during the run.

Line 13 is the CPU time required for compilation and layout, which is always less than the apparent running time by an amount which depends on the average system usage rate.

Lines 14 and 15 reflect a function of Franz Lisp wherein past used storage locations are reclaimed for the available memory list. The last three statistics were probably included because macritts can be very demanding of computing resources.

The "herald" option outputs messages to the terminal screen at each milestone in the sometimes lengthy compilation process. These reassure the user that macritts is still running. In addition to heralding what point in the design process macritts is currently working on, information on current accumulated CPU time and CPU garbage collection time is printed at the beginning of each herald line in units of sixtieths of a second.

"cif" option keys the compiler to output a mask Ibe level description .cif file in the Caltech Intermediate The cif option is normally not deselected unless the FORE. available disk storage space is limited and the user is only interested in reading the statistics for his compiled (The cif file for a relatively simple design, design. sultip.cif, is over 158 kilobytes long.) If no cif is produced on a given macpitts run, the entire lay ut process must be repeated to subsequently obtain a cif file. This is done most expeditiously by running macpitts with the nocbj cption.

The "nocbj" option tells macpitts to start with a previously created object file (the output of the macpitts "front end,") rather than a source file. MacPitts will then effectively start at the "back end," doing the layout and outputing statistics and cif, assuming these are included in the options list.

"Int" tells macpitts to use the interpreter mode, which allows functional simulation of the chip without actually performing the layout and generating a .cif file.

"Cpt-c" and "opt-d" invoke optimization routines for normalization of the combinatorial logic of the control unit. Investigation of the four possible combinations of these two options reveals that they do not affect the overall dimensions of the final 8 bit multiplier design (to te described later.) This is probably because the rins,

data path layout and bus wiring dominate the chip area, not the control unit, which is comparatively small for this chip. The compilation time required, however, was approximately 20 percent greater when opt-c and opt-d were used than when they were not used. Using opt-c and opt-d does reduce the complexity of the control unit, and therefore will reduce signal delays, to the benefit of operating speed.

The "4u" option sets the minimum feature size for the layout to 4 microns, and accordingly lambda, the commonly used parameter which represents the half line width dimension, is set to 200 centimicrons.

Another option, logo, was available in the original macpitts, but is not supported at NPS because suitable font files are not currently available.

#### C. USE OF THE RACPITIS INTERPRETER

Invoking macpitts with the int option should be the first step in every Macpitts design cycle. Macpitts has good facilities for catching grammatical errors in the user's .mac source code which operate whether or not the interpreter is invoked. After the .mac file passes grammar checks, the interpreter allows the extracted algorithmic description to be exercised with arbitrary inputs. The results are displayed on the screen to provide an indication that the design is functionally correct. Assuming the user's path list is set up in the .login file to include the directory, /vlsi/macpit, the following command can be issued:

### % macpitts multip int herald