# INTEGRATED CIRCUITS LABORATORY

STANFORD ELECTRONICS LABORATORIES

DEPARTMENT OF ELECTRICAL ENGINEERING

STANFORD UNIVERSITY · STANFORD, CA 94305

TR-DXG501-82-1

ICL-17-79

COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUIT FABRICATION PROCESSES FOR VLSI DEVICES

prepared by

J.D. Plummer

R.W. Dutton

J.F. Gibbons

C.R. Helms

I.D. Meindl

W.A. Tiller

C.P. Ho

K.C. Saraswat

B.E. Deal

INTEGRATED CIRCUITS LABORATORY STANFORD UNIVERSITY Stanford, Ca. 94305

June 1983

JUL 7 1983

Semi-Annual Report for Period 1 April 1982 · 30 September 1982

Distribution Statement Approved for public release; distribution unlimited

Prepared for: ADVANCED RESEARCH PROJECTS AGENCY 1400 Wilson Boulevard Arlington, Va. 22209

US Army Electronics Technology & Devices Laboratory

83 07 6

134

| 5. TYPE OF REPORT & Semi-Annual Rel April 1982-30 6. PERFORMING ORG. 2-DX6501 8. CONTRACT OR GRAMMDA903-79-C-02 | REPORT NUMBER  ANT NUMBER(s)               |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Semi-Annual Re April 1982-30  6. PERFORMING ORG. 2-DXG501 8. CONTRACT OR GRA MDA903-79-C-02                     | REPORT NUMBER  ANT NUMBER(s)  257          |

| 2-DXG501<br>8. CONTRACT OR GRA<br>MDA903-79-C-02                                                                | ANT NUMBER(s)                              |

| MDA903-79-C-02                                                                                                  | 257                                        |

| 10. PROGRAM ELEMEN                                                                                              |                                            |

| AREA & WORK UN                                                                                                  | NT, PROJECT, TASK<br>NIT NUMBERS           |

|                                                                                                                 | ecours oraces                              |

| June 1983                                                                                                       | 13. NO. OF PAGES                           |

| 15. SECURITY CLASS. (of this report) Unclassified                                                               |                                            |

| 15a. DECLASSIFICATION / DOWNGRADING SCHEDULE                                                                    |                                            |

|                                                                                                                 | June 1983 15. SECURITY CLASS. Unclassified |

16. DISTRIBUTION STATEMENT (of this report)

Approved for public release; distribution unlimited.

17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from report)

18. SUPPLEMENTARY NOTES

This contract is awarded under Basic Agreement MDA903-79-C-0257, issued by Defense Supply Service-Washington. This research is sponsored by Defense Advanced Research

Projects Agency (DARPA).

19. KEY WORDS (Continue on reverse side if necessary and identify by block number)

Modeling Semiconductor Devices, Semiconductor Processing, Computer-Aided Device Design, Computer-Aided Process Design, Ion Implantation, Thermal Oxidation, Chemical Vapor Deposition, Device Simulation

20. ABSTRACT (Continue on reverse side if necessary and identify by block number)

Efficient design of high performance VLSI processes requires accurate models for the physical processes used for fabrication. This is particularly true as device geometries shrink and fabrication technologies become inherently 2D. First order models for thermal oxidation, ion implantation, diffusion, chemical vapor deposition and other processes cannot accurately predict device structures from modern IC technologies. ) over

DD 1 JAN 73 T4 EDITION OF 1 NOV 65 IS OBSOLETE

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

# UNCLASSIFIED

| SECURITY CLASSIFICATION OF THIS PAGE (WIND DATA ENTIRED)                          |

|-----------------------------------------------------------------------------------|

| 19. KEY WORDS (Continued)                                                         |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| •                                                                                 |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| 1                                                                                 |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| 20 ABSTRACT (Continued)                                                           |

|                                                                                   |

| The Sundamental objection of this program is to devalue assumets and physically   |

| The fundamental objective of this program is to develop accurate and physically   |

| correct models for these processes which are general enough to incorporate in a   |

| general purpose, user-oriented computer simulation tool - SUPREM. This program    |

| accepts process schedules as inputs and provides predicted device structures as   |

|                                                                                   |

| outputs. It is meant to be capable of accurately simulating both bipolar and MOS  |

| VLSI structures. SUPREM is specifically designed to couple with device simulation |

| tools so that it forms the cornerstone of a hierarchy of VLSI process, device,    |

| circuit and system design aids.                                                   |

| Circuit and system design aids.                                                   |

| . \                                                                               |

|                                                                                   |

| \                                                                                 |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| 7 AUTHOR(s) (Continued)                                                           |

|                                                                                   |

| •                                                                                 |

| K. Saraswat, F. C. Shone, M. Taubenblatt, Y. Thathachari, W. Tiller, E. Young.    |

| R. Sarashas, T. S. Shohe, T. Tausenstast, T. Machaellari, H. Titter, E. Tourig.   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| <b>(</b>                                                                          |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| FORM S A STOCK                                                                    |

DD1 JAN 73 1473 (BACK) EDITION OF 1 NOV 65 IS OBSOLETE SEMI-ANNUAL REPORT

ON

COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUIT

FABRICATION PROCESSES FOR VLSI DEVICES

APRIL 1, 1982 - SEPTEMBER 30, 1982

This work was supported by a contract from the

DEFENSE ADVANCED RESEARCH

PROJECTS AGENCY

MDA903-79-C-0257 ARPA Order No. 3709

Approved for public release

Distribution unlimited

James D. Plummer

Stanford Electronics Laboratory

Stanford University

Stanford, California

Accession For

ETIS CRA&I

DTIC TAB

Universation

Diministration

Availability Codes

Availability Codes

Availability Codes

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the U. S. Government.

# TABLE OF CONTENTS

|         |                                                                                                                                               | Page |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| SUMMARY |                                                                                                                                               |      |  |  |

| 1.      | OXIDATION AND POINT DEFECTS                                                                                                                   | . 7  |  |  |

| 2.      | THIN OXIDE GROWTH KINETICS IN DRY OXYGEN                                                                                                      | . 16 |  |  |

| 3.      | ATMOSPHERIC AND HIGH PRESSURE OXIDATION OF POLYCRYSTALLINE SILICON                                                                            | . 20 |  |  |

| 4.      | OXIDATION ENHANCEMENT STUDIES                                                                                                                 | . 28 |  |  |

| 5.      | Si/SiO <sub>2</sub> INTERFACE CHARGES                                                                                                         | . 42 |  |  |

| 6.      | MEASUREMENT AND CHARACTERIZATION OF THIN OXIDES ON POLYSILICON                                                                                | . 57 |  |  |

| 7.      | ION IMPLANTATION AND RANGE STATISTICS                                                                                                         | . 70 |  |  |

| 8.      | SILICIDE/SILICON CONTACTS                                                                                                                     | . 77 |  |  |

| 9.      | GETTERING AND TRANSIENT PROCESS CHARACTERIZATION                                                                                              | . 79 |  |  |

| 10.     | Si WAFER SURFACE PROPERTIES: SURFACE COMPOSITION AND THE EFFECT OF CLEANING PROCEDURE STUDIED BY ELLIPSOMETRY AND AUGER ELECTRON SPECTROSCOPY | . 85 |  |  |

| 11.     | STUDIES OF OXYGEN DIFFUSION THROUGH SiO <sub>2</sub>                                                                                          | . 89 |  |  |

| 12.     | PHOSPHORUS DIFFUSION IN SILICON                                                                                                               | . 92 |  |  |

# COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUIT

#### FABRICATION PROCESSES FOR VLSI DEVICES

#### SUMMARY

The work described here builds upon an established program which over the past five years has resulted in the development of three generations of computer-aided process modeling programs - SUPREM I, II and III. The second generation version - SUPREM II - is currently in use at more than 150 industrial firms and university research groups and is generally regarded as the preminent tool of its type available today. A significant number of published papers from groups all over the world reference this computer program, and in fact, many papers include simulated results obtained from SUPREM. It has found widespread application in the design of state-of-theart MOS and bipolar fabrication processes.

The principal highlight of the program during the present reporting period has been the release of SUPREM III. This is a completely new, greatly improved version of the program with substantially improved capabilities. SUPREM III can simulate structures with up to five material layers. Built in models for Si,  $SiO_2$ , Polysilicon and  $Si_3N_4$  are included and other materials can easily be added with user defined parameters. A large number of new and/or improved physical models for oxidation, diffusion, epitaxy and ion

implantation are included in SUPREM III, these have, for the most part, come from experimental and theoretical work under this program over the past five years. These new models should greatly expand the range of applicability and the accuracy of the program.

At the present time approximately 25 copies of the new program have been licensed from the University by U. S. semiconductor manufacturers and defense contractors. We expect that over the lifetime of the program the distribution will eventually exceed that of SUPREM II. Initial feedback from industry users is beginning to come in to us, and it is clear already that the new program capabilities will make SUPREM III a much more valuable tool than its predecessors. We expect over the next two years to release updated versions of the program as new materials models become available. Much of the work which is aimed at this objective is described in the remainder of this report.

The specific goals of this research have been and continue to be the formulation of basic physical and mathematical models of integrated circuit fabrication processes which can accurately predict the structure of small geometry VLSI devices (and other arbitrary device structures) which will result from a given fabrication sequence, and to implement these models in a comprehensive process modeling computer program. Such a program, it was believed at the outset of this work, would significantly reduce costly and time consuming iterative, experimental approaches to developing or optimizing silicon technologies. This has, in fact, occurred. SUPREM III represents a major step along the path toward improved simulation tools.

It is clear that the historical trends in integrated circuit technology over the past two decades towards increased complexity and smaller active device dimensions will continue. Modern device structures employ lateral

device dimensions on the order of 2-3  $\mu$  and vertical dimensions well below 1  $\mu$ m. There are no basic physical mechanisms which will prevent a reduction in each of these dimensions by an additional order of magnitude over the next two decades. Practically accomplishing this continued scaling, however, depends upon our ability to physically understand and quantitatively model the fabrication techniques which will be used in the construction of such devices.

For devices with relatively large geometries (>5  $\mu$ ) and loose processing tolerances, relatively simple models suffice for prediction of vertical device structures resulting from a given fabrication sequence. As device dimensions shripk, however, it becomes essential to employ more robust process models and to consider the interaction both laterally and vertically of various processing steps, if accurate simulation of structures is to be obtained. This is important even with today's 2-3  $\mu$ m device geometries; it will become essential for smaller devices.

Large geometry devices can be successfully modeled as one-dimensional structures. This is true for both process models and electrical models. Devices with lateral dimensions below a few microns, however, require two-dimensional models for accurate simulation. This need has stimulated a large body of work in recent years on two-dimensional electrical models of device current-voltage characteristics. One example of this type of work is the 2D program GEMINI, developed under this program. Work of this type has resulted in remarkable advances in our understanding of small geometry device physics.

Progress has not been as rapid, however, in two-dimensional process modeling. While some basic 2D process modeling programs have been developed at Stanford (SUPRA for example) and elsewhere, these programs do not

incorporate robust 2D kinetic models which can accurately predict doping profiles and device geometries under a wide range of conditions. This is a direct result of our need for improved physical models of oxidation, ion implantation, diffusion, and CVD. It is quite clear that these processes are not one dimensional. Recent experimental evidence has clearly indicated that oxidation or impurity diffusion in a localized region of a silicon substrate can substantially affect oxidation or diffusion rates in laterally or vertically adjacent regions of the substrate. There is no clear agreement at the present time on the basic physical mechanisms responsible for such results, although much has been learned in the past several years. It is clear, however, that we must quantitatively understand such phenomena if we are to accurately model small device s'ructures.

A specific goal of this program is to understand and model these two-dimensional effects. We have made substantial progress in this regard in the past six months. It appears now that the basic physical phenomena underlying these interactions are the roles of points defects—silicon vacancies and interstitials—in impurity diffusion, thermal oxidation, and other processes. The generation and consumption of these point defects during high temperature fabrication steps appear to be the unifying physical effects which can explain many of the phenomena which have been regarded as anomalous to date. We have used such models to quantitatively understand a variety of process phenomena and have incorporated some of these models in SUPREM II.

More such models are in SUPREM III. The unifying role of these mechanisms is a cornerstone of the work described in this progress report. We regard such models as absolutely essential to accurate modeling of two-dimensional effects in small devices.

Simply stated, the long-range objective of this research is the development of a 2D process modeling program which contains physically correct 2D kinetic models. Most of the effort under this program is aimed at experimental and theoretical work to uncover the basic physical mechanisms which govern 2D oxidation kinetics, 2D diffusion, etc. This is a major problem area with very difficult materials problems. It will become clear in the technical discussions later in this report that 2D process modeling involves much more than solving 1D equations in two dimensions. Basic physical laws and understanding are lacking at present. Effects such as lateral OED, oxidation under masking Si<sub>3</sub>N<sub>4</sub> layers, lateral and vertical effects of high dopant concentrations on diffusion coefficients, and a host of other known experimental effects cannot be explained by a simple extrapolation of known 1D physical laws to 2D structures. This program is aimed at generating the physical understanding needed to develop 2D kinetic models.

An essential part of this is to develop models for bulk point defect (interstitial and vacancy) generation, recombination and diffusion, since it is clear that the <u>local</u> concentrations of these defects determine <u>local</u> diffusion coefficients, oxidation rates, etc. In fact, an alternative statement of the overall objective of this program would be to develop techniques for calculating <u>local</u> (i.e. time and position dependent) process parameters suitable for process simulation. Such process parameters will of necessity be <u>geometry dependent</u> which means that diffusion coefficients and oxidation rate constants, for example, will depend on the presence or absence of nearby heavily doped regions or oxidizing interfaces. This will imply a tight coupling between surface geometry and resulting impurity profiles in small devices.

In this context, the overall objectives of this program are:

- (1) To develop accurate physical models for the basic technologies used in the fabrication of silicon integrated circuits--oxidation, ion implanatation, diffusion, and chemical vapor deposition (CVD).

- (2) To develop accurate physical models for the interaction of these processes, for example, the enhancement of diffusion coefficients in an oxidizing ambient.

- (3) To develop accurate physical models based upon silicon point defects for two-dimensional process phenomena in small geometry devi-

- (4) To develop high resolution analytic tools for the experiment characterization of small device structures.

- (5) To implement improved process models in updated versions of .... EM

III so that this program is capable of accurately simulating small

devices and multi-layer structures.

- (6) To aim toward a robust 2D process modeling program (SUPREM IV) which would combine outputs from this program with numerical techniques developed under other support.

- (7) To disseminate the results to the semiconductor and defense industries.

The remainder of this report describes the specific research activities during the six month period covered by this report. Each of the subsequent sections includes a discussion of the problems under investigation, the results to date and plans for the future. The unifying themes of all of the work to be described are the development of new or improved models for SUPREM III and the investigation of 2D materials phenomena required to develop SUPREM IV.

# 1. OXIDATION AND POINT DEFECTS

# S. DUNHAM, J. PLUMMER

The existence of interactions between silicon oxidation and the diffusion of impurities (OED and ORD) and growth/shrinkage of stacking faults (OISF) has been well established [1-12]. Both effects are attributed to the creation of interstitialcies at the oxidizing interface in order to relieve the stress created there [13-15]. Many of these studies have examined the relationship between oxidation rate  $\frac{dX}{dt}$  and interstitialcy density resulting in fits to the equation:

$$C_{I} = \left(\frac{dX_{o}}{dt}\right)^{n} \tag{1}$$

Unfortunately, the value of n must be calculated empirically and reported values have ranged from less than 0.3 [4] to more than 1.0 [12]. Our ongoing work then, is an attempt to physically account for the relationship between oxidation rate and point defect densities and thus to develop quantitative models for OED, ORD and other phenomena suitable for 2D process modeling in SUPREM IV.

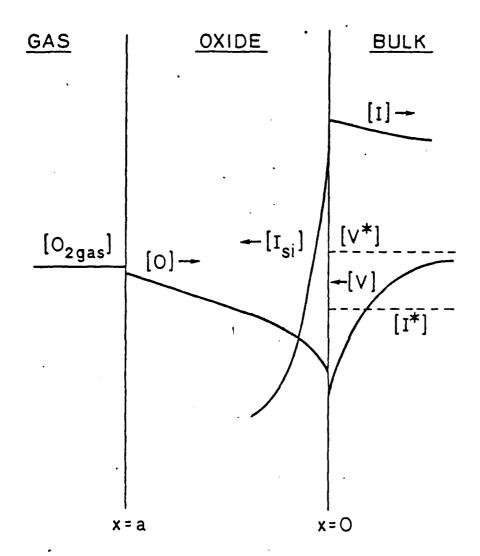

It has been observed that in lightly-doped silicon, oxidation is more than 99% complete [16], so virtually all of the silicon interstitialcies created by oxidation must diffuse into the oxide where they react with incoming oxygen to complete the process. Therefore, the fluxes within the

oxide (Figure 1) determine the interstitialcy density at the interface. We can write the continuity equations for oxygen and silicon interstialcies as:

$$\frac{\partial C_0}{\partial t} = D_0 \frac{\partial^2 C_0}{\partial x^2} - k_I C_I C_0$$

(2)

$$\frac{\partial C_{I}}{\partial t} = D_{I} \frac{\partial^{2} C_{I}}{\partial x^{2}} - k_{I} C_{I} C_{o}$$

(3)

In steady state, as for relatively long oxidations, the time derivatives are zero so combining (2) and (3) and integrating twice we get:

$$C_{O} = \gamma C_{I} + a + bx \tag{4}$$

where  $\gamma = (D_I/D_00)$ .

Tracer experiments [17-19] have shown that oxidation takes place very close to the oxide-bulk interface so there is no flux of interstitials through the oxide. Therefore, we can conclude that:

$$\left(\frac{dC_{I}}{dx}\right)_{X=0}=0\tag{5}$$

and

$$C_1(0) = 0$$

(6)

By Henry's Law:

$$C_0(0) = Kp_{0_2}$$

(7)

so combining with (4) and (6):

$$a = Kp_{0_2}$$

(8)

The rate of oxide growth is proportional to the flux of oxygen at the gasoxide interface:

$$D_{o}\left(\frac{dC_{o}}{dx}\right)_{x \doteq o} = -\frac{1}{\Omega} \frac{dX_{o}}{dt}$$

(9)

where  $X_0$  is oxide thickness and  $\Omega$  is the molecular volume of  $SiO_2$ . Combining this with (4) and (5):

$$b = - (D_0 \Omega)^{-1} \left( \frac{dX_0}{dt} \right)$$

(10)

We can now rewrite equation (4) as:

$$C_{o} = \gamma C_{I} + \kappa \rho_{o_{2}} - (D_{o} \Omega)^{-1} \left(\frac{dX_{o}}{dt}\right) X$$

(11)

The second of th

For conditions where the partial pressure dependence of the oxidation rate is linear (wet or high temperature dry), at the interface the rate of oxidation, which is equal to the oxygen flux, is proportional to the density of oxygen:

$$D_{o}\left(\frac{dC_{o}}{dx}\right)_{x = x_{o}} = k_{o}C_{o}X_{o}$$

(12)

Due to volume constraints, a certain percentage ( $\alpha$ ) of interface reactions must result in point defect interactions. Ho and Plummer's results [20,21] show that vacancy mechanisms are negligible in intrinsin silicon so:

$$D_{I} \left( \frac{dC_{I}}{dx} \right)_{x = x_{o}} = - \alpha D_{o} \left( \frac{dC_{o}}{dx} \right)_{x = x_{o}}$$

(13)

Substituting the derivative of (11) and rearranging:

$$\left(\frac{dC_{I}}{dx}\right)_{x = x_{O}} = \frac{\alpha}{1+\alpha} (\delta D_{O} \Omega)^{-1} \left(\frac{dX_{O}}{dt}\right)$$

(14)

Combining this result with (12) and the experimental support for the Deal-Grove model [22] that says:

$$X_{o} = \frac{B}{2} \left( \frac{dX_{0}}{dt} \right) - \frac{A}{2}$$

(15)

then solving for the density of interstitialcies at the oxide-bulk interface we get:

$$C_{I}(X_{o}) = K_{1} \frac{dx_{o}}{dt} + K_{2}$$

(16)

$$K_1 = \frac{1}{\delta \Omega} \left[ \frac{1}{k_0 (1+\alpha)} - \frac{A}{2D_0} \right]$$

(17)

$$K_2 = \frac{1}{\delta} \left[ \frac{B}{2D_0} - Kp_{0_2} \right]$$

(18)

We can see that depending on the magnitudes of  $K_1$  and  $K_2$ , which will change with temperature and partial pressure, any power law relationship relating  $C_1$  and  $dx_0/dt$  between 0 and 1 can be approximated.

Looking first at stacking fault growth:

$$L = \int_{0}^{t} (\kappa_{I} c_{I} - \kappa_{V} c_{V} - \kappa_{R}) dt$$

(19)

Assuming steady-state recombination of point defects, then  $c_V = (c_V^* c_I^*)/c_I$ ,

so using (16) and looking only at parabolic oxidations where  $\frac{dL}{dt} = \left(\frac{B}{2t}\right)^{1/2}$ ,

we can integrate to get:

$$L = \left(K_{1}K_{1}B^{1/2}\right)t^{1/2} + \left(K_{2} - K_{r} - \frac{2K_{V}C_{1}^{*}C_{V}^{*}}{K_{2}}\right)t + \frac{K_{1}B^{1/2}}{2K_{2}} \ln\left(1 + \frac{2K_{2}}{K_{1}B^{1/2}} t^{1/2}\right)$$

(20)

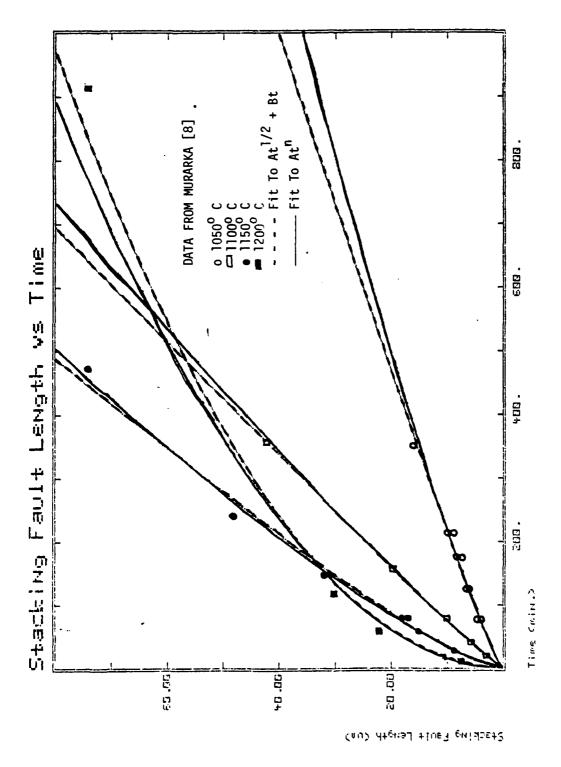

Ignoring the final term which should be small since  $C_1>> C_1^*$ , this expression gives a stacking fault length time dependence of between 0.5 and 1.0 which fits well with reported dependences [3,7-11]. In fact, fits to  $L = A_1 t^{1/2} + A_2 t$  are virtually indistinguishable from the accepted practice of fitting to  $L = At^n$  (Figure 2). Since the constants  $A_1$  and  $A_2$  will change with oxidizing conditions, we can see how different apparent power relationships should result.

Most impurities diffuse via point defect mechanisms which in the most general case gives:

$$D_{i} = C_{I}D_{I} + C_{V}D_{V}$$

(21)

As for stacking faults, except for impurities that diffuse only with vacancies (ORD), the second term is usually negligible so calculating the time-averaged diffusion constant gives:

$$\langle D_{i} \rangle = D_{I}K_{1} \langle \frac{dx_{0}}{dt} \rangle + D_{I}K_{2}$$

(22)

which can apear as any power dependence between 0 and 1. Most experimental work has involved changing either temperature or partial pressure so no direct comparison with experiment has been done to this point.

In conclusion, this work gives a physical basis for the observed dependence of impurity diffusion and stacking fault growth/regrowth on oxidation conditions. There appears to be great potential in unifying the many seemingly contradictory results that have shown up in this area. Such a model would enable prediction of the effect of oxidation on the resulting bulk properties and perhaps point out how to most effectively make use of these interactions.

#### References

- [1] D.A. Antoniadis, A.G. Gonzales, and R.W. Dutton, <u>J. Electrochem. Soc.</u>, 27, 813 (1978).

- [2] R. Francis and P.S. Dobson, J. Appl. Phys., 50(1), 280 (1979).

- [3] S.M. Hu, J. Appl. Phys., 45, 1567 (1974).

- [4] K. Taniguchi, K. Kurosawa, and M. Kashiwagi, J. Electrochem. Soc., 127, 2243 (1980).

- [5] A.M. Lin, D.A. Antoniadis, and R.W. Dutton, <u>J. Electrochem. Soc.</u>, <u>128</u>, 1131 (1981).

- [6] S. Mizuo and H. Higuchi, Jap. J. Appl. Phys., 20, 739 (1981)

- [7] R.B. Fair, J. Electrochem. Soc., 128, 1360 (1981).

- [8] S.P. Murarka, J. Appl. Phys., 48, 5020 (1977).

- [9] A.M. Lin, R.W. Dutton, D.A. Antoniodis, and W.A. Tiller, J. Electrochem. Soc., 128, 1121 (1981).

- [10] S.P. Murarka, Physical Review B, 16, 1849 (1977).

- [11] S.M. Hu, J. Appl. Phys., 51, 3666 (1980).

- [12] Y. Ishikawa, Y. Sakina, H. Tanaka, S. Matsumoto, and T. Numi, <u>J. Electrochem. Soc.</u>, <u>129</u>, 644 (1982).

- [13] W.A. Tiller, J. Electrochem. Soc., 127, 619 (1980).

- [14] W.A. Tiller, J. Electrochem. Soc., 127, 625 (1980).

- [15] W.A. Tiller, J. Electrochem. Soc., 128, 689 (1981).

- [16] B.E. Deal, <u>J. Electrochem. Soc.</u>, <u>110</u>, 527 (1963).

- [17] M.M. Atalla, in <u>Properties of Elemental and Compound Semiconductors</u>, 1960, ed. by H. Gatos, Interscience, 163 (1960).

- [18] J.R. Ligenza and W.G. Spitzer, <u>J. Phys. Chem. Solids</u>, <u>14</u>, 131 (1960).

- [19] P.J. Jorgensen, <u>J. Chem. Phys.</u>, <u>37</u>, 874, (1962).

- [20] C.P. Ho and J.D. Plummer, J. Electrochem. Soc., 126, 1516 (1979).

- [21] C.P. Ho and J.D. Plummer, <u>J. Electrochem. Soc.</u>, <u>126</u>, 1523 (1979).

- [22] B.E. Deal and A.S. Grove, <u>J. Appl. Phys.</u>, <u>36</u>, 3770 (1965).

FIGURE 1: Densities and fluxes of reactants in oxidizing silicon.

FIGURE 2: Comparison of modeling based upon equation 20 and experimental data.

# 2. THIN OXIDE GROWTH KINETICS IN DRY OXYGEN

H. MASSOUD, C. HO, J. PLUMMER

Very thin layers of thermal  $SiO_2$  were grown in dry oxygen in the thickness range 0 - 500 Å as described in earlier reports. These oxidations were carried out on single crystal silicon of different orientations (100), (111) and (110) , for different phosphorous substrate doping densities  $(1 \times 10^{15} \text{cm}^{-3})$ ,  $(2 \times 10^{20} \text{cm}^{-3})$  and  $(3.2 \times 10^{20} \text{cm}^{-3})$  , in different oxygen partial pressures in argon (1 atm, 0.1 atm and 0.01 atm), in the temperature range 800°C to 1000°C. The growth was monitored by an in-situ automated high-temperature ellipsometer which is well-suited for data collection in the initial stages of oxidation where the growth rate is enhanced. The experimental work was done in cooperation with IBM.

The data were analyzed in the context of the Deal-Grove linear-parabolic model where the oxidation rate is expressed as:

$$\frac{dX_{OX}}{dt} = \frac{B}{2X_{OX} + A} \tag{1}$$

where B and (B/A) are the parabolic and linear oxidation rate constants respectively. These rate constants describe the oxidation kinetics beyond the fast initial regime. The rate constants were obtained using the optimum  $X_1$  method. The oxidation rate enhancement in the thin regime can be expressed as an excess or as a ratio term:

$$\frac{dX_{ox}}{dt} = \frac{B}{2X_{ox} + A} + \Delta_{e}(X_{ox}, t)$$

(2)

or

$$\frac{dX_{OX}}{dt} = \frac{B}{2X_{OX} + A} \left[ 1 + \Delta_r(X_{OX}, t) \right]$$

(3)

where  $\Delta_{\bf e}$  and  $\Delta_{\bf r}$  are the excess or ratio enhancement terms which vanish with the onset of the linear parabolic kinetics. For all the orientations studied in 100% pure oxygen, it was found that these excess terms could be fitted to the following expressions:

$$\frac{dX_{ox}}{dt} = \frac{B}{2X_{ox} + A} + C_1 e^{-X_{ox}/L_1} + C_2 e^{-X_{ox}/L_2}$$

(4)

or

$$\frac{dX_{ox}}{dt} = \frac{B}{2X_{ox} + A} \left( 1 + K_1^* e^{-t/\tau_1} + K_2^* e^{-t/\tau_2} \right)$$

(5)

The dependence of the oxidation excess enhancement term  $\Delta_e$  on oxide-thickness is defined by two terms exponentially decaying with thickness. Both terms contribute to  $\Delta_e$  up to ~ 50Å, where the term  $(C_1,L_1)$  vanishes. From ~ 50Å to to the onset of linear-parabolic kinetics (~ 300Å), only the term  $(C_2,L_2)$  is responsible for the rate enhancement:  $L_1$  is of the order of 7 - 17Å, and is a weak function of temperature.  $L_2$  is of the order of 60 - 80Å, is temperature independent and is only a function of substrate orientation.

The oxidation rate enhancement studied as a ratio term was best fitted to an expression like that of equation (5). In this analysis  $K_1^*$  and  $K_2^*$  are orientation dependent constants that are temperature independent. This analysis is most consistent with the assumption that the concentration of oxygen species in the oxide during the initial stages of the oxidation is enhanced above what is inferred from permeation studies. The most frequently quoted values for the solubility of oxygen and water modules in  $SiO_2$  are  $5 \times 10^{16} cm^{-3}$  and  $5 \times 10^{19} cm^{-3}$  respectively. This corresponds to an average spacing between the oxidant species of 270Å and 27Å for oxygen and steam respectively.

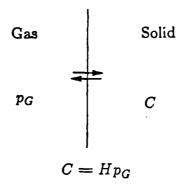

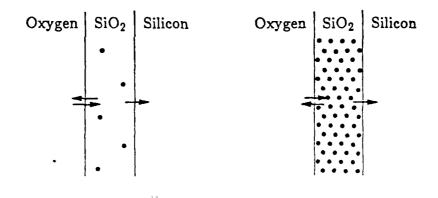

It is easily seen that the concept of an average bulk solubility is questionable in the case where the average spacing between the solute molecules is larger than the thickness of the film considered. This is illustrated in Figure 1. The same conclusion is arrived at when we consider the validity of application of Henry's Law to the kinetics of oxidation in the initial stages. Henry's Law assumes that the solubility C of a gas in equilibrium with a solid is related to the gas pressure  $p_{\rm G}$  by the Henry's Law constant H:

$$C = Hp_{G}$$

(6)

This assumes a semi-infinite solid. This assumption is needed to establish the equilibrium between the flux of gas molecules entering the solid and the flux of gas molecules leaving the solid. In equilibrium, these two fluxes are equal. In the case of a thin layer of  $\mathrm{SiO}_2$  (as shown in Figure 1), it is seen that in the case of dry oxygen, the flux of oxygen molecules consumed in the oxidation reaction at the  $\mathrm{Si-SiO}_2$  inteface may directly affect the equilibrium established at the outside surface of the  $\mathrm{SiO}_2$  layer. In the case of steam, the effects of the flux of water molecules consumed at the  $\mathrm{Si-SiO}_2$  interface are screened by the higher solubility of water in  $\mathrm{SiO}_2$ . This is in agreement with the absence of a fast initial oxidation stage in the case of steam.

Analysis of the oxidation data at lower partial pressures of oxygen will help elucidate the importance of the role oxygen solubility plays in the non-steady state period present in the case of oxidation in dry oxygen. It may also suggest other physical mechanisms that play a role in fast initial oxidation as well.

# HENRY'S LAW

Dry Wet  $C^{\bullet} = 5 \times 10^{16} \text{ cm}^{-3}$   $C^{\bullet} = 5 \times 10^{19} \text{ cm}^{-3}$

FIGURE 1: Physical arguments which may explain why  $0_2$  solubility is higher than the equilibrium value during the initial oxidation stage (see text).

# 3. ATMOSPHERIC AND HIGH PRESSURE OXIDATION OF POLYCRYSTALLINE SILICON B. CAIRNS, L. LIE

High pressure oxidation runs for polycrystalline silicon kinetic studies were not made during this time period because a problem of accurate temperature control developed in the high pressure oxidation system when it was converted from a 3-inch to 4-inch wafer capability for other internal Fairchild programs. A new tube and thermal control system which will correct this problem have been ordered and high pressure runs should resume in the late October to early December time frame.

# 3.1 Resistivity of Oxidized Polycrystalline Silicon

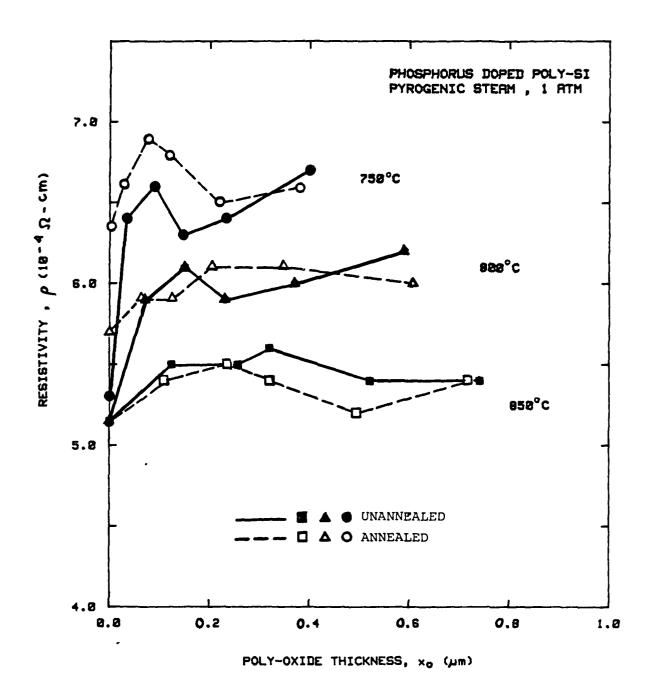

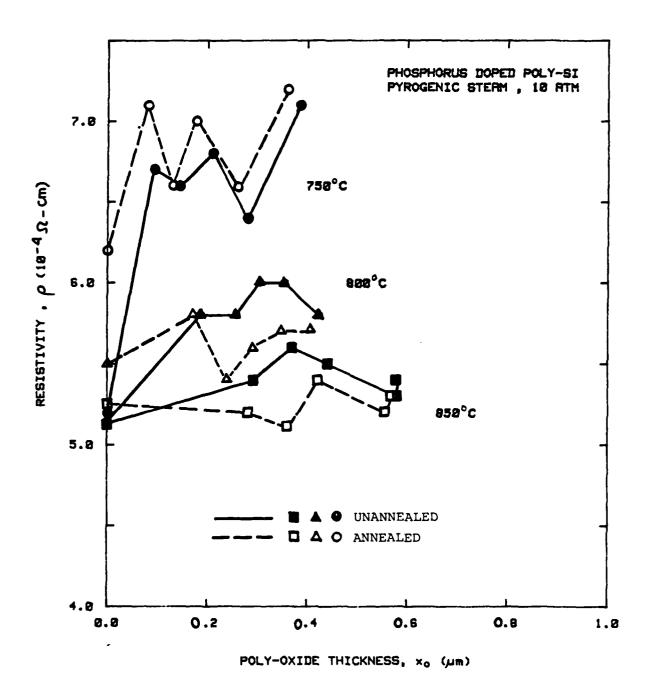

Measurements of polycrystalline silicon film resistivities following pyrogenic steam were completed. The phosphorous doped polycrystalline silicon films were oxidized in 1, 5 and 10 atm pyrogenic  $\rm H_2O$  at 750°, 800°, and 850°C. Results show that the resistivity is dependent on oxidation temperature and is fairly constant as the oxidation proceeds at a given temperature (Figures 1 and 2). As expected, the higher oxidation temperatures yielded lower film resistivities. In all cases, we did not oxidize more than 50% of the poly-Si films. Results reported by Saraswat of Stanford show a substantial increase in resistivity when more than 60% of the films are oxidized. The polycrystalline silicon films which did not receive a pre-oxidation anneal show a very rapid increase in the film resistivity for all temperatures and pressures to the values for the annealed films. This is not surprising for oxidation temperatures below the 950°C at which these films were doped. Reduced dopant solubility within the polycrystalline silicon grains after oxidation could be the main factor for this rapid increase in the resistivity. We could not

determine a time constant for the process, but it is complete in about 10 minutes. It was also noted that pressure effects appear negligible on the variation of film resistivities following oxidations up to 10 atm at these temperatures. The slight differences between 1 atm and 20 atm seen between Figures 1 and 2 are within the range of data scattering.

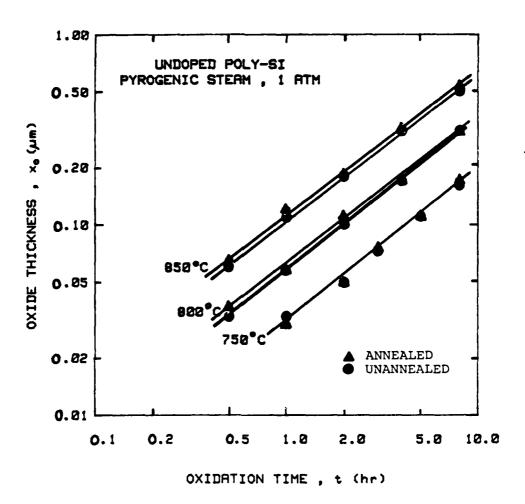

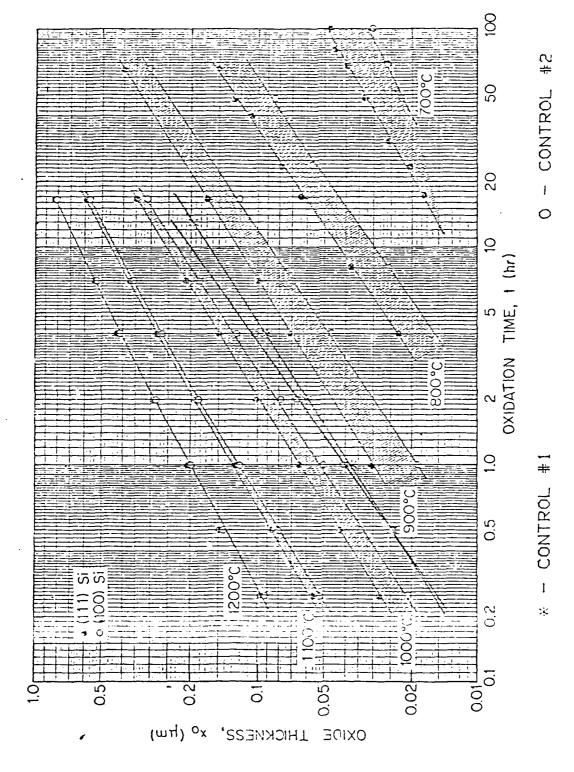

# 3.2 Atmospheric Oxidation of Polycrystalline Silicon

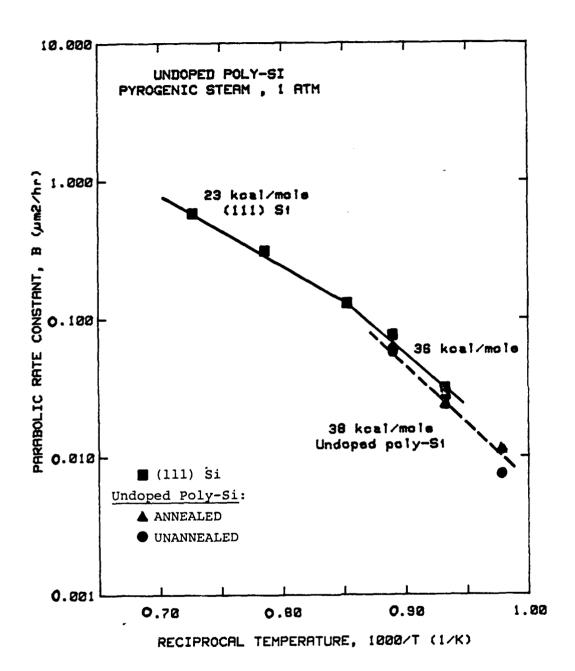

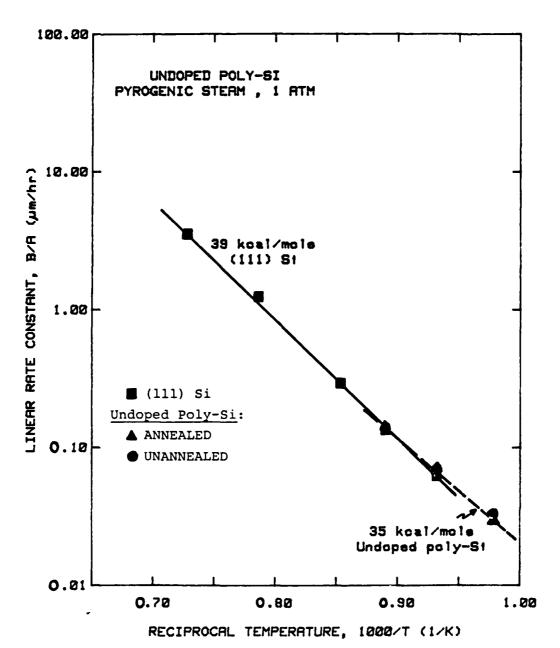

The oxidations of undoped polycrystalline silicon films in 1 atm pyrogenic steam at 750°, 800°, and 850°C have been completed. Half of the samples received a pre-oxidation anneal in nitrogen at the oxidation temperature. The plot of log oxide thickness versus log oxidation time is shown in Figure 3. For undoped polycrystalline silicon the differences observed in the oxidation rates between unannealed and pre-oxidation annealed samples are mostly within the accuracy of the oxide thickness measurements. This is not unexpected because x-ray diffraction analysis of the undoped polycrystalline silicon film as deposited by LPCVD at 615°C shows a predominant grain orientation of (110) and little changes are observed in the structure of polycrystalline silicon after annealing at temperatures up to 1000°C [1]. Analysis of the oxide growth data indicates that the oxidation kinetics of the film resembles that of (110) oriented single crystal siicon. The parabolic rate constant B was found to be slightly lower, by approximately 25%, than that of the (111) single crystal silicon; while the linear rate constant B/A was quite similar to that of the (111) single crystal silicon. These results are in agreement with available data comparing (111) and (110) lightly doped single crystal silicon oxidation kinetics [2,3]. The activation energies for B (38 kcal/mole) and B/A (35 kcal/mole) are the same, within the experimental accuracy, as for the B and B/A respectively, of the lightly doped

(111) single crystal silicon in this lower temperature range. The graphs of log B and log B/A versus reciprocal tempeature are shown in Figures 4 and 5, respectively.

The oxidation of doped and undoped polycrystalline silicon films in 1 atm dry  $0_2$  ambient at  $800^\circ$ ,  $900^\circ$ , and  $1000^\circ$ C have also been completed. Annealed and unannealed samples were included. All wafers were pulled in argon after each oxidation run. This completes the runs of the atmospheric part of the program. Analysis of the oxidation kinetics of these samples and comparison with respect to single crystal silicon oxidation in dry  $0_2$  are underway.

## 3.3 Structural Evaluation

Several samples of doped polycrystalline silicon oxidized in pyrogenic steam at 1 atm and 10 atm have been submitted for cross-section TEM evaluation. Samples were chosen to evaluate the effects of pressure, temperature, and annealing on oxides of the same thickness range (2000-2500 Å) as well as various thicknesses under constant temperature and pressure conditions.

#### References

- [1] T.I. Kanins, M.M. Mandurah and K.C. Saraswat, <u>J. Electrochem. Soc.</u>, <u>125</u>, 927 (1978).

- [2] Y. Kamigaki and Y. Itoh, J. Appl. Phys., 48, 2891 (1977).

- [3] E.A. Irene, <u>J. Electrochem. Soc.</u>, <u>121</u>, 1613 (1974).

FIGURE 1: Residual poly-silicon film resistivity versus poly-silicon oxide thickness grown in 1 atm pyrogenic steam at  $750^{\rm O}$ ,  $800^{\rm O}$ , and  $850^{\rm O}$  C. Results for annealed and unannealed phosphorus doped poly-silicon film are shown.

FIGURE 2: Residual poly-silicon film resistivity versus poly-silicon oxide thickness grown in 10 atm pyrogenic steam at  $750^{\circ}$ ,  $800^{\circ}$ , and  $850^{\circ}$  C. Results for annealed and unannealed phosphorus doped poly-silicon film are shown.

FIGURE 3: Oxide thickness versus oxidation time for annealed and unannealed undoped poly-silicon films oxidized in pyrogenic steam at 1 atm and  $750^{\circ}$  -  $850^{\circ}$  C.

FIGURE 4: Parabolic rate constant B versus 1000/T for annealed and unannealed undoped poly-silicon films oxidized in pyrogenic  $\rm H_2O$  at 1 atm and  $750^{\rm O}$  -  $850^{\rm O}$  C. Parabolic rate constants of (111) Si are shown for comparison.

FIGURE 5: Linear rate constant B/A versus 1000/T for annealed and unannealed undoped poly-silicon films oxidized in pyrogenic  $\rm H_2O$  at 1 atm and  $750^{\rm O}$  -  $850^{\rm O}$  C. Linear rate constants of (111) Si are shown for comparison.

## 4. OXIDATION ENHANCEMENT STUDIES

W. A. TILLER, Y. T. THATHACHARI, W. E. DIBBLE, JR., D. N. MODLIN and E. M. YOUNG

# 4.1 Field Enhancement

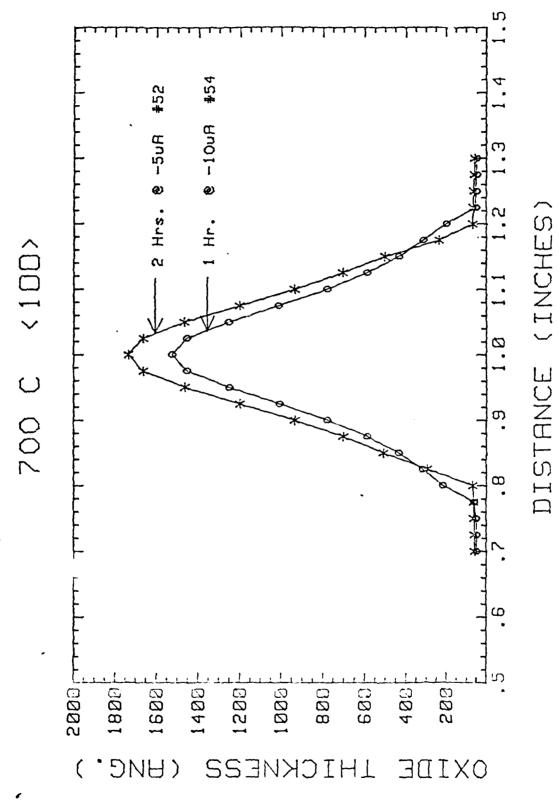

In the field-enhanced oxidation studies, the native oxide thickness,  $X_N$  is much less than the total oxide thickness,  $X_B$ , at t=700° C with a <100> substrate and I ~ -  $5\mu$ A. Thus, we decided to check to see if the experimental data satisfied a constant current-time product since this is what is expected theoretically; i.e.,

$$\frac{\chi_{B}}{\chi_{B}} - \chi_{N} = \frac{It}{qN_{O}}$$

(1)

where  $X_B$  is the average enhanced oxide thickness. The question is, does this also happen for the peak oxide thickness, i.e., do we have

$$X_{B} - X_{N} \alpha It$$

(2)

In Figure 1, we see the superposed results of an  $I=-5\mu A$  and t=2.0 hr experiment with one at  $I=-10\mu A$  and t=1.0 hr. Although the profiles are quite similar, the  $-10\mu A$  curve is wider at its base and has a lower peak height. Thus, although eq. 1 holds, eq. 2 does not hold exactly. This situation is readily explained. In the point to plane discharge, increasing I leads to enhanced natural repulsion betwen the ions so that the ion beam widens because the axial electric field is not increased in proportion to the increased space charge. Thus, the current density at the center of the beam must decrease because the integral of the total beam intensity is equal to the beam current.

The oxygen partial pressure dependence,  $P_{0_2}$ , was investigated with the negative ion beam at 700° C using an admixture of oxygen in argon. The values of  $X_B$  for t = 1 hr at I =  $-10\mu A$  with 10%, 50%, 80%, and 100%  $0_2$  in argon are given in Figure 2. We note that, as  $P_{0_2}$  is reduced by a factor of 10,  $X_B$  decreases by only = 18%. The explanation for this result is thought to depend upon the electron attachment probability to 0 and  $0_2$ .

As  $P_{0_2}$  decreases, the concentration of unattached electrons entering the oxide increases. We expect that the concentration of free electrons,  $\eta$ , will be given by

$$\eta = K_1 e_{\chi}p(-\epsilon_1/kT) + K_2 e_{\chi}p(-\epsilon_2/kT)$$

(3)

where K is a constant and  $\varepsilon$  is the binding energy of an electron to an 0 or  $0_2$  (electron affinity). In eq. 3, K will decrease as  $P_{0_2}$  increases and will depend upon the relative population of 0 and  $0_2$ . If the concentration of 0 stays relatively constant even though the concentration of  $0_2$  decreases, since  $\varepsilon_0 > \varepsilon_{0_2}$ , one might expect  $X_B$  to be only slightly dependent upon  $P_{0_2}$ . Because of eq. 3, at higher T for a given t and I, we should expect  $X_B$  to fall off. This is observed experimentally.

In these studies, a series of baseline control experiments were conducted The Si wafer rested on a quartz plate at a distance of 0.5 cm below the platinum needle and no external potential was applied to the system. However, directly beneath the needle, the oxide growth was enhanced. This was later found to be due to (i) a small remnant positive polarization potential in the quartz plate and sapphire standoffs of the apparatus and (ii) to a lesser extent the presence of platinum in the system.

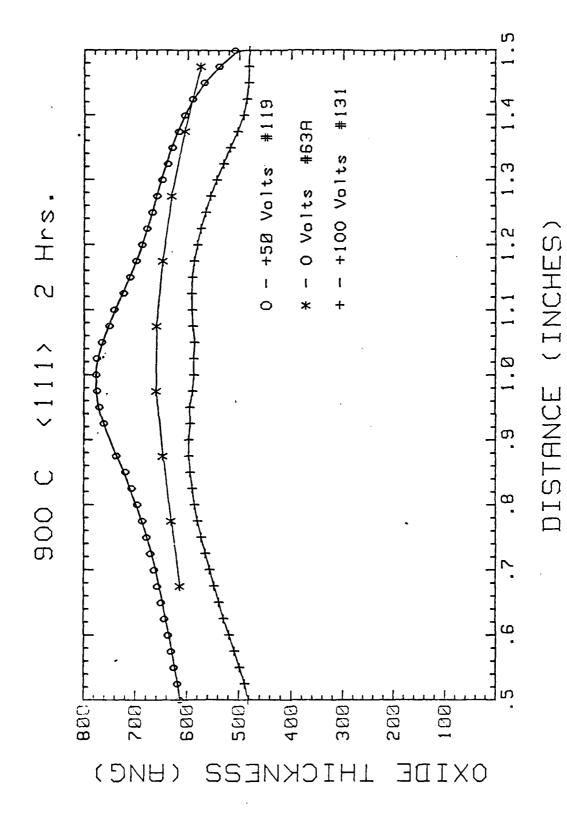

In Figure 3, two sets of control experiments at 900° C with Si <111> subtrates with zero applied potential are shown. The first set, which were performed near the beginning of the experimental work, reveal an enhanced peak oxidation rate compared to that expected in a standard oxidation furnace. The second set, conducted some months later with no changes in the experimental apparatus, reveal an even greater enhanced peak oxidation rate compared to the first set. It was anticipated that these unwanted electrical effects were associated with (i) electrical polarization in the apparatus due to the flow of current I and (ii) work function differences between dissimilar materials; i.e., the equivalent voltage for the system,  $V_{eq}$ , is given by

$$V_{eq} = V_{pol} + V_{WF}$$

(4)

We expect that  $V_{pol} >> V_{WF}$  and that the difference between set 1 and set 2 of Figure 3 is due to changes in  $V_{pol}$ . The measured volume conductivity at 900°C is  $\sigma_{V} \approx 10^{-9} \, \text{ohm}^{-1} \, \text{cm}^{-1}$  while the DC resistance for a fully polarized quartz plate in the apparatus is  $\approx 1.4 \times 10^7$  ohms which leads to an IR drop of  $\approx 70$  volts across the quartz plate. Thus, if internal polarization completely cancels this voltage drop during a run, the remnant field left in the system system will be  $\approx 70$  volts.

Figure 4 shows three oxide thickness profiles for Si  $\langle iii \rangle$  substrates at 900° C with t = 2 hrs. Experiment #63 was an open-circuit control while #119 and #131 had +50V and +100V, respectively, applied to the needle. As #63 was the first experiment performed, the oxidation enhancement is indicative of the remnant polarization present in the quartz plate at that time. Experiment

#119 was conducted shortly thereafter and, because the +50V is applied in series with  $V_{pol}$ , the resulting thickness profile is further enhanced. On the other hand, experiment #131 was performed after a number of experiments utilizing a beam current of  $I = +5 \mu A$ . We see that, for an applied voltage of +100V, substantially less enhancement is obtained than that found in experiment #119. This is because  $V_{pol}$  changed both magnitude and sign because of the positive ion current forced through the sample and the quartz plate.

Assuming a linear relationship between the percentage peak enhancement and the resultant voltage on the needle, one can estimate the voltage due to remnant polarization. Experiments #63 and #119 show 37% and 62% enhancement, respectively, which would lead to a  $V_{pol} = +74V$  which agrees quite well with the estimate of 70 volts obtained earlier.

# 4.2 Photo Enhancement

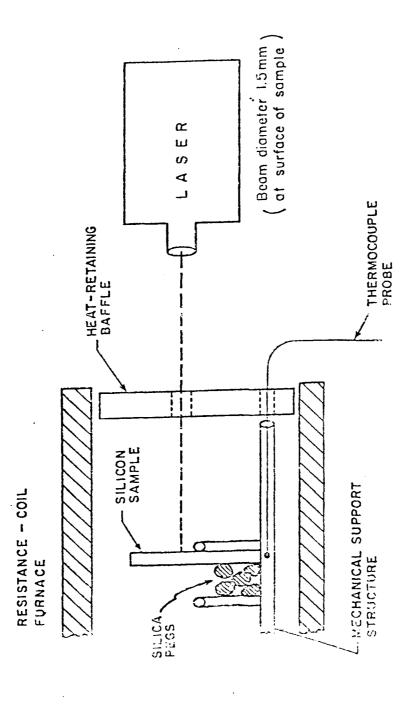

The purpose of the present work was to examine the extent to which a true photonic or optically induced enhancement mechanism is at work in silicon versus enhancement caused by local excess heating of the surface at the laser beam spot. In our study, a Lexel argon-ion laser was used to generate a photon flux of selectable energy and adjustable intensity. In the continuous beam, only one wavelength of the five most powerful lasing wavelengths was used at a time; i.e., 2.4 eV, 2.5 eV, 2.54 eV, 2.6 eV or 2.7 eV. The beam was directed into a thermal oxidation furnace so as to hit the center surface of a vertical sample of silicon (see Figure 5) at a few degrees off of the normal to avoid multiple-reflection measurement errors of the beam spot power density. The silicon sample was otherwise exposed to typical thermal oxidation processing.

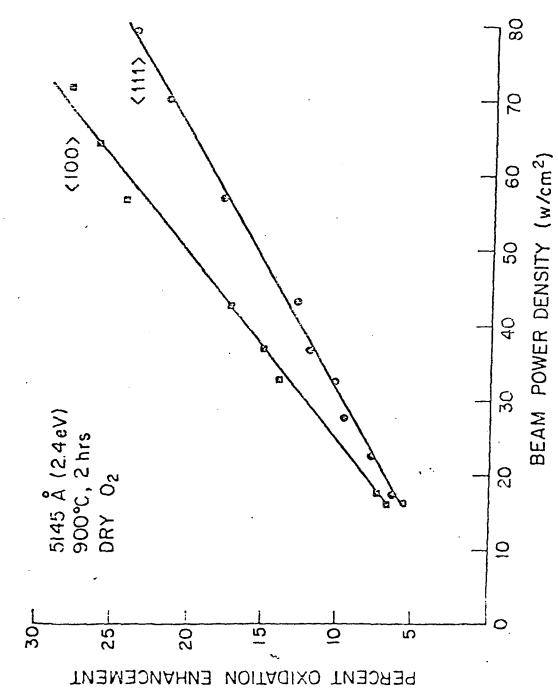

Typical oxidation conditions were two hours at 900° C in dry  $0_2$  which resulted in control oxides of  $\approx$  450 A and  $\approx$  300 A for the <111> and <100> orientations, respectively. The peak oxidation enhancement, measured via ellipsometry, varied linearly with beam power density and was in the 3% to 30% range, as ilustrated in Figure 6. We note that the enhancement is greater for the <100> than for the <111> Si which is opposite to that expected for a purely thermal result.

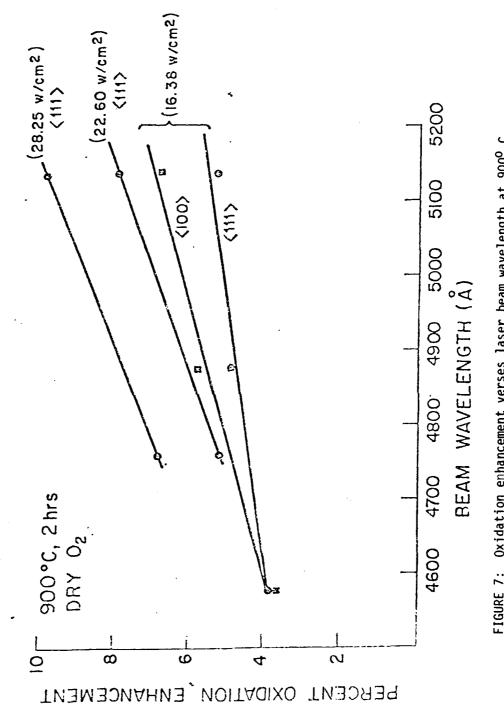

Experiments were also carried out at low but constant beam power density while the photon flux was varied with the photon energy in the range 2.4 eV to 2.7 eV. At constant beam power  $P_0$  the photon flux F is directly proportional to the optical wavelength  $\lambda$  according to

$$F = \left(\frac{P_0}{hc}\right) \quad \lambda \tag{5}$$

where c is the speed of light and h is Planck's constant. Thus, at long wavelengths, more photons arrive at, and interact with, the active silicon surface than do so at shorter wavelengths. Figure 7 illustrates typical results for both <111> and <100> silicon and shows the percent oxidation enhancement to increase linearly with beam wavelength and thus with photon flux.

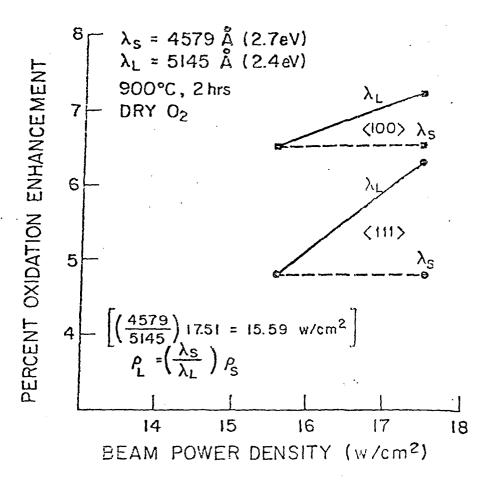

A variation of these two experiments was performed to conclusively demonstrate the nature of the photonic mechanism. Here, the power of the longer wavelength beam  $P_L$  was lowered to reduce  $F_L$  to the same value as that from a shorter wavelength beam operating at  $P_S$ ; i.e., we require that

$$\frac{P_{L}}{P_{S}} = \frac{\lambda_{S}}{\lambda_{L}} \tag{6}$$

If a photonic mechanism of oxidation enhancement is indeed operative, the amount of enhancement produced by both wavelengths should now be identical. The results shown in Figure 8 confirm this hypothesis.

A great deal of care must be exercised over the course of a typical 2 hour oxidation experiment both in measuring, and in maintaining constant, the power density of the laser beam. This is a prerequisite to observing the photonic effect with the precision of the experiments becoming more critical as the wavelength difference,  $\Delta\lambda = |\lambda_i - \lambda_j|$ , decreases. In addition, as the beam power density increases, more heating of the silicon surface is likely to occur, eventually washing out the photonic effect. Preliminary experiments show that, as the beam power density increases for fixed  $\Delta\lambda$ , this is indeed the case.

FIGURE 1: Oxide thickness vs position on wafer for  $700^{\rm O}$  C oxidations.

FIGURE 2: Dependence of oxide thickness on oxygen partial pressure for 700<sup>0</sup> C, 60' oxidations. #20 1 F 88 \* #57 -10 uA 60 #58 40 700 C 20 1600 2000 1800 1400 1200 1000 200 800 600 400 (HNC. **LHICKNE22** OXIDE

\* OXYGEN (ARGON ADMIXTURE)

Relationship of enhanced oxidation kinetic results to "normal" oxidation data. FIGURE 3:

FIGURE 4: Oxide thickness profiles for  $900^{0}$  C, <111>, 2 hr oxidations.

FIGURE 5: Experimental set-up for laser enhanced oxidation studies.

FIGURE 6. Oxidation enhancement verses laser beam power density at  $900^{

m O}$  C.

FIGURE 7: Oxidation enhancement verses laser beam wavelength at  $900^{\rm O}$  C.

FIGURE 8: Oxidation enhancement verses laser beam power density for two laser wavelengths.

## 5. Si/SiO<sub>2</sub> INTERFACE CHARGES

## A. AKINWANDE, C. HO, J. PLUMMER

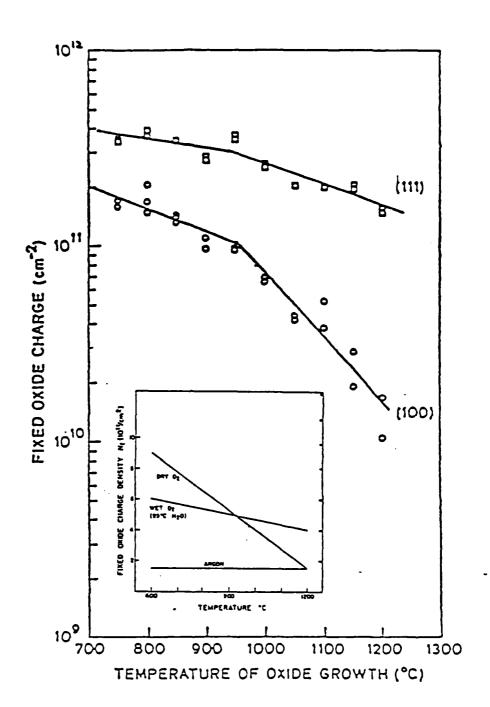

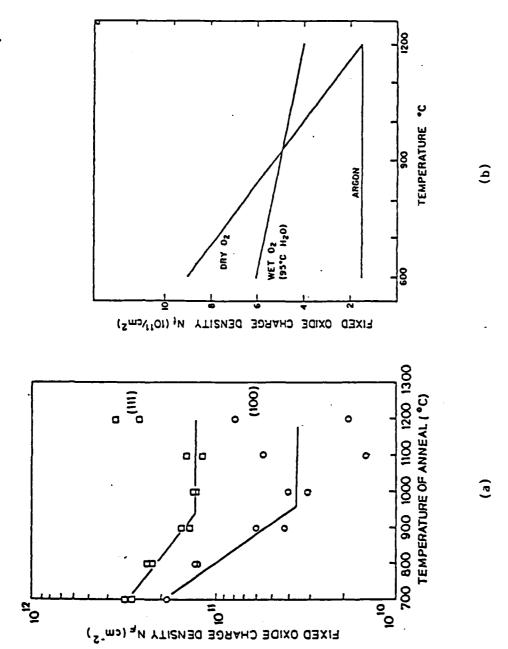

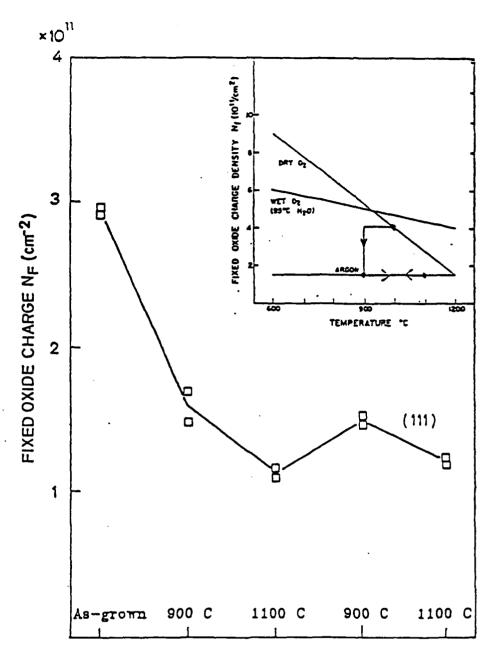

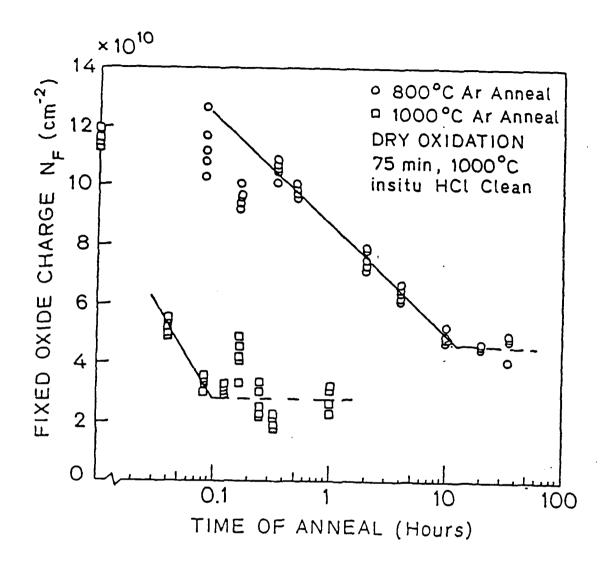

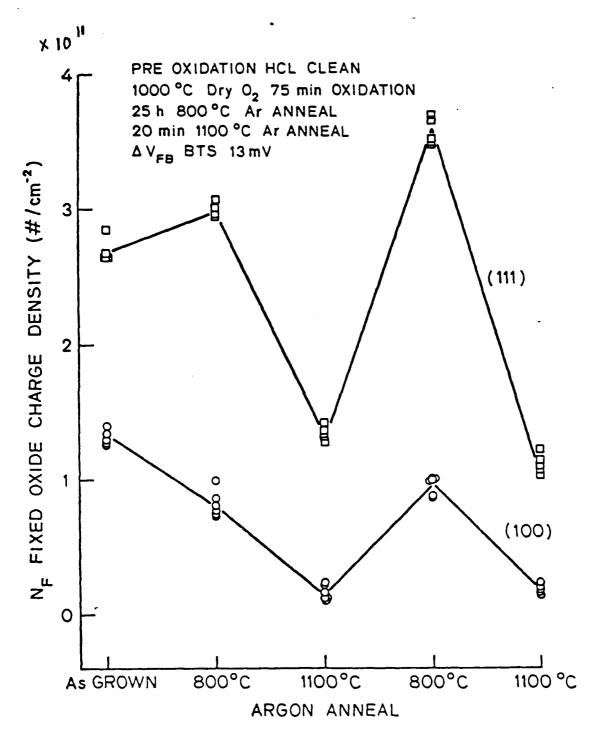

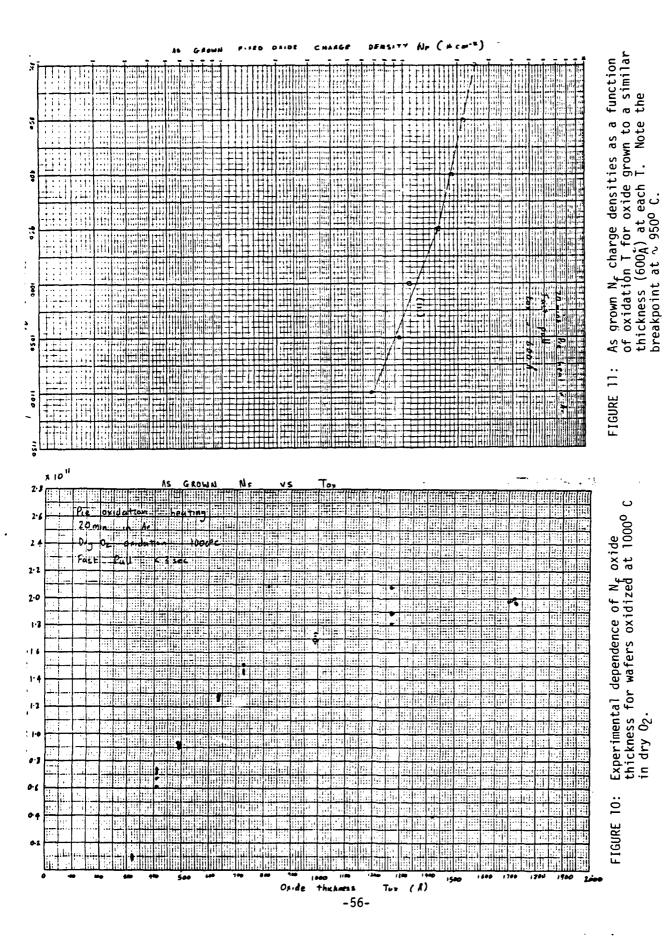

In the last annual report, it was demonstrated: (a) as grown charges follow the Deal  $N_{\rm F}$  triangle qualitatively but a careful examination of the results indicate a breakpoint at a temp of about 950° C. This led us to suggest that there may be a viscoelastic relaxation process occurring at the interface at the same time as charge generation during the oxidation process (Figure 1); (b) annealed charges appear not to show the temperature independence that the bottom part of the  $N_{\rm F}$  triangle would suggest. There seems to be a break point at about 950° C also. This led us to suggest that the anneal process may be a viscoelastic decay process (Figure 2); (c) As confirmation of the fact that the annealed charges are not independent of temperature, thermal cycling experiments were carried out on (111) Si wafers oxidized in dry  $0_2$  at  $1000^{\circ}$  C for 75 minutes. These wafers were later annealed in argon (< 2 ppm  $H_20$ ) and cycled between  $900^{\circ}$  C and  $1100^{\circ}$  C. The results did show that oxide charges do thermally cycle under the conditions given (Figure 3).

Since the above summarized experiments, numerous experiments have been carried out to answer some of the questions raised and attempts have also been made to develop theoretical tools to model the processes. The major accomplishments over the last few months are itemized below:

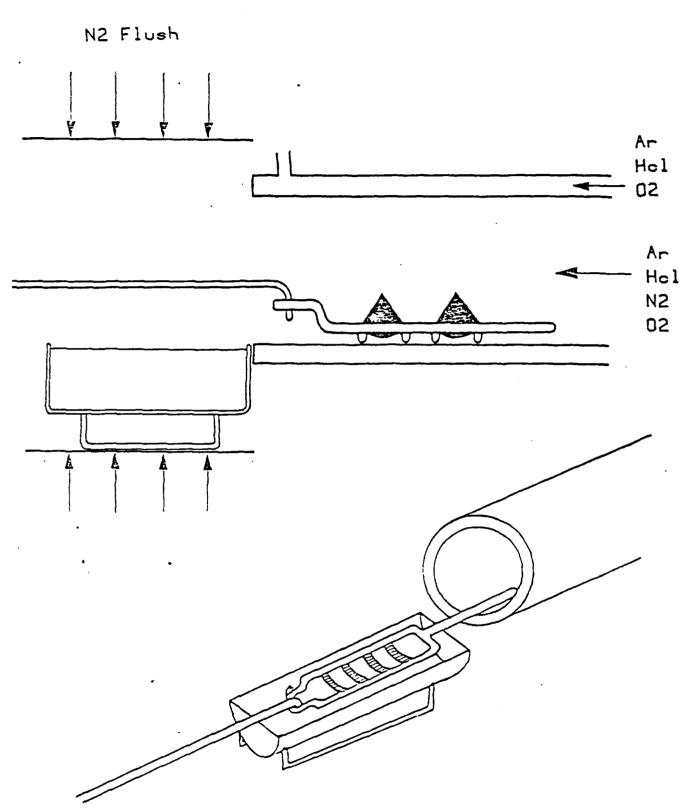

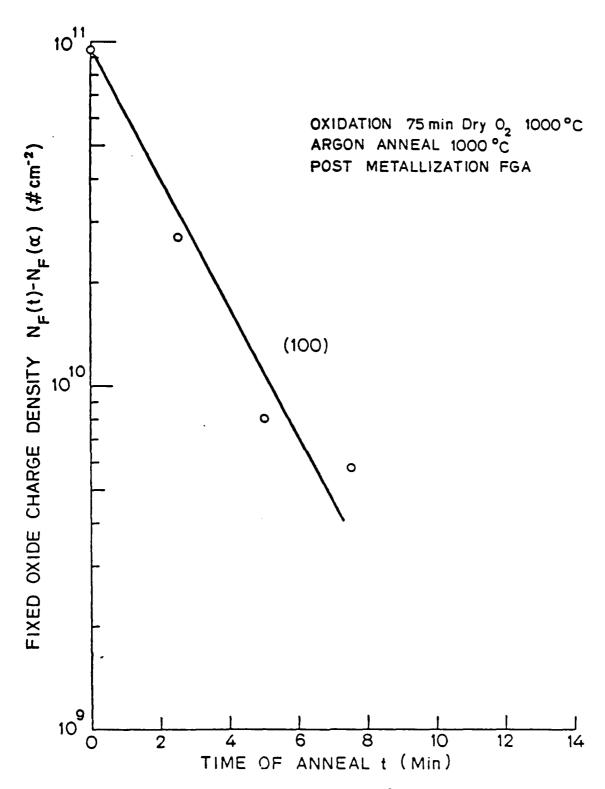

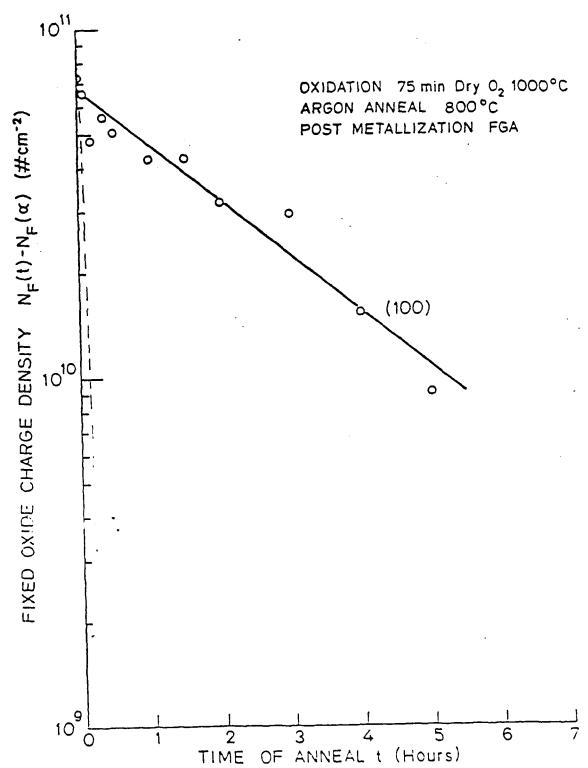

(1) A fast pull technique was developed to enable a quench of Si wafers from processing temperature to room temperature. This set up is shown in Figure 4. Quench durations of < 3 secs have generally been achieved. (2) In the first set of experiments using the new experimental set-up, in oxides were grown at  $1000^{\circ}$  C in dry  $0_2$  for 75 mins and were fast pulled ( $\sim$  2 sec pull). They were subsequently annealed at various temperatures ( $800^{\circ}$  C,  $900^{\circ}$  C and  $1000^{\circ}$  C) in argon which has < 1 ppm  $H_2O$ . The results are as shown in Figures 5, 6 and 7. From these results, the anneal process appears to be exponential with a time constant which decreases with temperature. The anneal process saturates to a final value which also decreases with temperature. Finally, this has led to a suggestion that the anneal kinetics may be described by:

$$N_{f}(t) = (N_{f}(0) - N_{fe}(T)) \exp(-t/\tau(T)) + N_{fe}(T)$$

(1)

where

$$\tau(T) = K \exp(Ea/kT) \tag{2}$$

In order to explain this behavior, we favor a model which invokes a maxwellian viscoelastic relaxation process at the  $\mathrm{Si/Si0}_2$  interface. This process relieves the strain/stress at the interface. This implies that we must make an a priori assumption that strain/stress generated by the lack of free volume during the oxidation process is the origin of oxide charges. It must be reiterated though that this is just one of many possible models and careful further experimentation is required.

We have also investigated a situation in which the viscoelastic process is not maxwellian. This would result in a situation where the fictive "growth" temperature of the oxide is different from the anneal temperature [1]. It is expected under such circumstances that the anneal time constant would be a function of the processing

- history of the  $\mathrm{Si}/\mathrm{SiO}_2$  wafers. Preliminary experiments are being carried out to test this effect.

- (3) The second set of recent experiments were to reproduce the thermal cycling of oxide charges under different anneal conditions (i.e., temperature). Oxides were grown on (111) and (100) Si Cz wafers at  $1000^{\circ}$  C in dry  $0_2$  for 75 mins. They were subjected to 20 min pre heat in Argon prior to oxidation, 20 min 1% HC1/Ar etch + 20 min purge in Argon at  $1000^{\circ}$  C. The wafers were fast pulled from the oxidizing ambient (≈ 2 sec) and were subsequently given anneals in argon and cycled between 800° C and 1100° C. As the results shown in Figure 8 indicate, the charges do thermally cycle in argon on both orientations. It should be noted that the annealed charges at 800° C for (111) wafers are greater than the as grown values at 1000° C. This observation coupled with the fact that the charges reproduce under thermal cycling has led to the suggestion that there may be a reversible reaction going on at the interface between Si and  $SiO_2$ , that results in an equilibrium value of oxide charges for a particular temperature. Attempts have been made to formulate this problem mathematically and results thus far indicate that more careful studies are required.

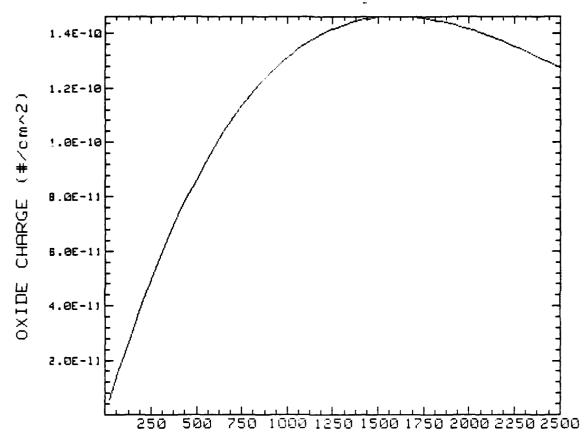

- (4) The third set of new experiments were to study the as-grown charge kinetics. As we suggested earlier, it has been suggested in the literature [2] there may be a possibility that during an oxidation process, there is simultaneous generation and annihilation (anneal) of oxide charges at the Si/SiO<sub>2</sub> interface. The problem was formulated mathematically under the assumptions that: (a) there is a

distribution of oxide charges in the oxide with the highest value at the interface; (b) charges are generated as the interface moves past the point in question in the oxide; (c) charges are rather immobile; (d) charges at a point in the oxide anneal with an exponential decay starting from the time of generation, i.e., the time the interface moved past the point in question. The time constant would be what is expected from a viscoelastic relaxation

$$t = \frac{\eta(T)}{G} \tag{3}$$

and, (e) a weighted sum of the charges is taken. The dependence this model would predict on oxide thickness is as shown in Figure 9. Preliminary experiments have been carried out and the results for (111) Si wafers are shown in Figure 10. It is our belief that by extension of the domain of the experiment, either by growing thicker oxides or growing oxides at higher temperature where T would be shorter, the peak predicted by the model would be observed. Experimentation is in progress.

(5) The fourth set of experiments were to investigate the as grown charges as a function of oxidation temperature at constant oxide thickness (600A). As shown in Figure 11, we reproduce earlier results in which we observe a breakpoint at a temperature of about 950°C.

In order to conclude this report, it can be seen that many more questions have been raised than have been answered. We have thus set the following priorities:

- (a) Repeat the thermal cycling experiments using both CZ and FZ Si wafers. This would eliminate any questions as to the effect of dissolved oxygen on Si on the  $Si/SiO_2$  interface.

- (b) Study the anneal kinetics from the point of view of a reversible process.

- (c) Complete the study of the effect of thermal history (i.e., oxidation) on the anneal process.

- (d) Determine if the anneal process which seems to be limited by a bond breaking/thermal mechanism can be aided by an external source of energy such as UV light at low temperature to shorten the decay time constant.

- (e) Complete the experiments on the generation mechanisms.

#### References

- [1] G. Hetherinton, K.H. Jack and J.C. Kennedy, "The Viscosity of Viterous Silica", Physics and Chemistry of Glasses, Vol 5, No. 5, p. 130, Oct. 1964.

- [2] M. Hamasaki, "Generation Kinetics of Oxide Charges and Surface States During OXidation of Silicon"

FIGURE 1: As-grown (fast pulled) fixed oxide charge density  $N_{\rm f}$  vs. growth temperature for (111) and (100) wafers. While the general behavior expected from the  $N_{\rm f}$  triangle is observed, a distinct break also occurs at  ${\sim}950^{\circ}$  C.

Fixed oxide charge density  $N_{\rm f}$  vs. anneal temperature in argon for (lll) and (100) wafers. (a) Expt. (b)  $N_{\rm f}$  triangle. The times were adjusted at each temperature to reach an equilibrium value. FIGURE 2:

ARGON ANNEAL

FIGURE 3: Fixed oxide charge density  $N_{\rm f}$  vs. Argon anneal cycle for (111) wafers thermally cycled between  $900^{\rm O}$  C and  $1100^{\rm O}$  C in Ar. This illustrates that the bottom part of the  $N_{\rm f}$  triangle is not flat.

FIGURE 4: Schematic representation of fast pull apparatus designed to permit < 3 sec quench times from oxidation temperature to room temperature.

FIGURE 5: Example of anneal kinetics of oxide charges for (100) wafers in Argon at  $800^{\rm O}$  C and  $1000^{\rm O}$  C. Note that both decay time constants and the final annealed values are different at the two temperatures.

FIGURE 6: Anneal kinetics of N at  $1000^{\rm O}$  C in Ar, for wafers oxidized at  $1000^{\rm O}$  C in dry  $0_2$ .

FIGURE 7: Anneal kinetics of N  $_{\rm f}$  at  $800^{\rm O}$  C in Ar, for wafers oxidized at  $1000^{\rm O}$  C in dry  $0_2$  .

FIGURE 8: Thermal cycling of final Ar annealed value of  $\rm N_f$  as the annealing temperature is charged from  $800^{\rm O}$  C to 11000 C.

OXIDE THICKNESS (Ana)

FIGURE 9: Predicted dependence of  $N_f$  on oxide thickness based upon the model described in the text, and a viscoelastic relaxation time of 4 hours.

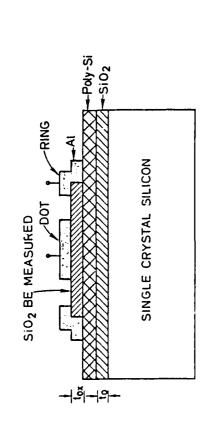

# 6. MEASUREMENT AND CHARACTERIZATION OF THIN OXIDES ON POLYSILICON E. KUTLU, K. SARASWAT, J. PLUMMER

Our first experiments on the oxidation of plysilicon showed that the oxidation kinetics of poly are different from the oxidation kinetics of single crystal silicon mostly during the linear regime [1]. It is, therefore, necessary to work with thin oxides in order to understand the oxidation kinetics, of polysilicon. Although several measurement techniques are available for the measurement of thin oxides on single crystal silicon, they are not generally useful for the measurement of thin oxides on poly.

The sensitivity of alpha step measurements to variations of the oxide thickness on the wafer makes the accuracy of the measurements questionable. The measurements give  $\pm$  20% thickness variations for oxides thinner than 1000 Å. Epplipsometry measurements would not be meaningful because of the multiple reflections coming from the multiple layer structure. The spectrophotometer technique would also fail, since short wavelengths, which are necessary for the measurement of thin films, would be absorbed by the silicon.

An alternative technique, which we are investigating, uses C-V measurements. When the oxide capaticance is known, oxide thickness can be obtained from the relationship

$$t_{ox} = \frac{\epsilon_o^K ox^A}{C_{ox}} \tag{1}$$

where  $t_{OX}$  is the oxide thickness,  $\epsilon_{O}$  is the permittivity of free space,  $K_{OX}$  is the dielectric constant of the oxide and  $C_{OX}$  is the oxide capacitance.

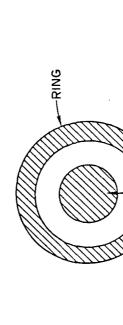

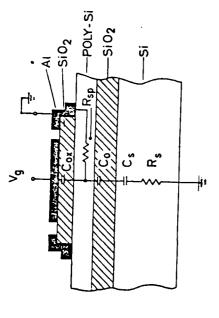

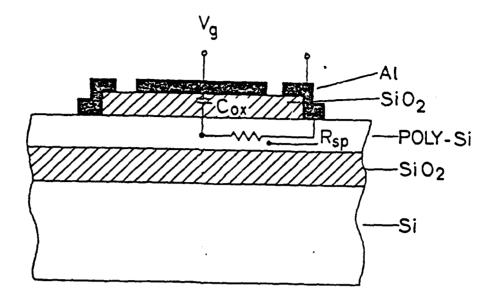

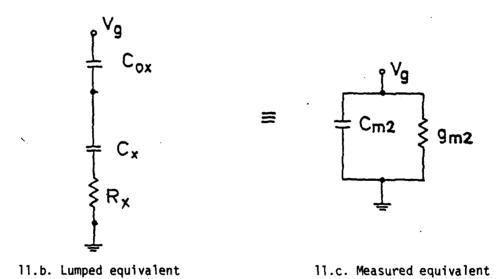

The capacitor structure prepared for these measurements is shown in Figure 1. In the following sections analyses of the different measurements on this structure will be discussed, and a set of experiments which are in progress will be described. Although the structure is distributed in nature, the equivalent circuit elements will be treated as lumped circuit elements.

## 6.1 Analysis of the Measurements

With the structure shown in Figure 1, three different measurements seem possible: substrate-ring shorted; substrate floating, and a 2-step measurement which will be described later.

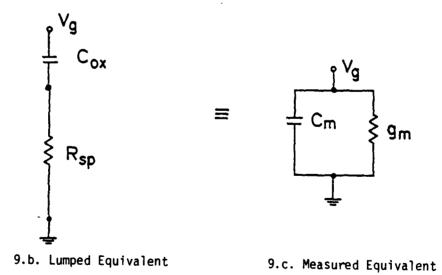

## 1. Substrate-Ring Shorted

The structure, its lump equivalent and measured equivalent circuits are shown in Figures 2a, 2b, 2c respectively. In these figures:  $C_{\text{OX}}$  is the capacitance of the oxide layer on the silicon,  $C_{\text{S}}$  is the depletion or inversion layer capacitance of the substrate,  $R_{\text{Sp}}$  the spreading resistance of the poly.  $R_{\text{S}}$  is the substrate resistance of the silicon and  $C_{\text{m}}$  and  $g_{\text{m}}$  are the measured equivalent capacitance and conductance of the system repectively.

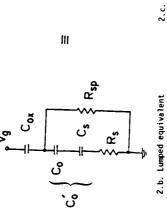

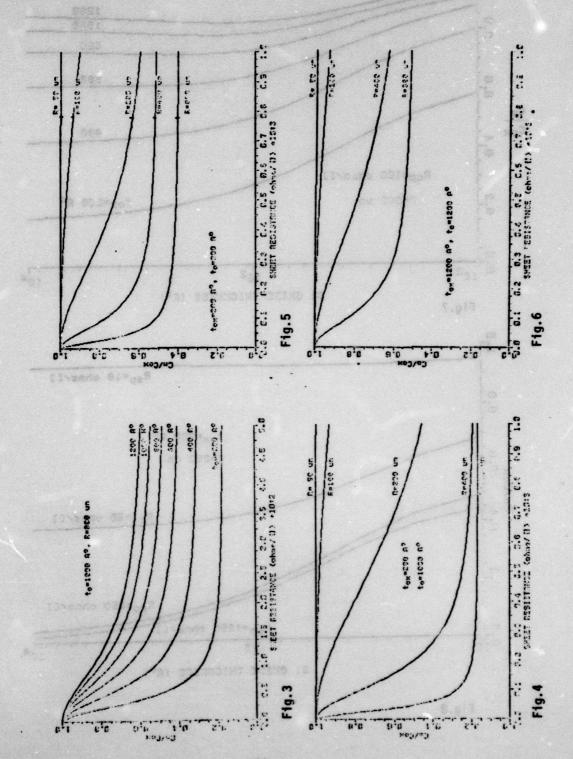

As can be seen from Figure 2, the measured capacitance is in general different from the oxide capacitance  $C_{OX}$ , depending on the values of the parasitic elements. If some of those such as  $R_S$ ,  $C_S$  and  $C_O$  are known,  $C_{OX}$  and  $R_{SP}$  can be found from  $C_m$  and  $g_m$  uniquely for the given structure. The resultant expressions are rather complicated, however, the dependence of  $C_m/C_{OX}$  on  $R_{SP}$ ,  $t_O$  and R which is the radius of the dot are given in Figures 3-6. In these figures it is assumed that  $R_S$  =  $50\Omega$  and  $C_S$  is negligible.

As can be seen from Figure 3 and Figure 2b, there are two limiting cases corresponding to highly and lightly doped poly:

a)

$$\lim_{R_{sp} \to 0} C_m = C_{ox}$$

(2)

which means that for highly doped samples, the substrate parasitic elements  $t_0$ ,  $R_S$ ,  $C_S$  do not have an effect on the measurements.

b)

$$\lim_{m \to \infty} C_m = \frac{C_{ox}^{\prime}}{1 + \omega^2 C_{ox}^2 R_s^2}$$

(3)

where

$$\frac{1}{C'_{OX}} = \frac{1}{C'_{O}} + \frac{1}{C_{OX}}$$

;  $\frac{1}{C'_{O}} = \frac{1}{C_{O}} + \frac{1}{C_{S}}$  (4)

which means that depending on the oxide thickness on the substrate, the measured capacitance will differ from the true oxide capacitance.

Neglecting the effect of the depletion capacitance i.e.  $C_0'\simeq C_0$ , three special thicknesses are distinguishable.

b1.

$$t_0 = t_{ox}$$

In this case, under the condition  $\omega^2 C_{0x}^{\prime} R_s^2 << 1 C_m = \frac{C_{0x}}{2}$

For two different thicknesses, this case is shown in Figure 5 and Figure 6.

b2.

$$t_0 \gg t_{0x}$$

which means  $C_0 << C_{OX}$ . In this case, since  $C_0$  will dominate, we will measure  $C_0$ , rather than  $C_{OX}$ .

b3.

$$t_o \ll t_{ox}$$

or  $C_{\rm OX}$  <<  $C_{\rm O}$ . Since we will measure the oxide capacitance directly, this is the condition we have to consider when we want to measure thin oxides on lightly doped samples. The effect of  $t_{\rm O}$  on the measured capacitance for lightly doped poly is shown in Figures 7-8.

Now, the question is, in the case of lightly doped poly, how thin can the oxide layer on the substrate be made in order to get the correct oxide thickness on poly? We cannot avoid having an oxide layer on the Si substrate, since this would totally change the polysilicon oxidation kinetics. Furthermore, if we make  $t_0$  thinner than 200Å, then its thickness becomes comparable with that of the depletion layer and we can no longer neglect the depletion capacitance. Therefore, with this measurement technique, especially for the lightly and moderately doped poly, we cannot avoid the effects of parasitic elements on the measurement.

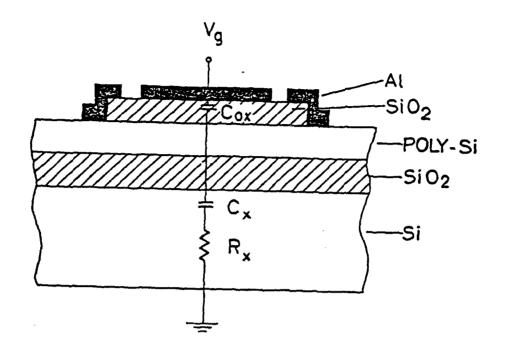

#### 2. Floating Substrate

Another possible measurement which can be done between the ring and dot by letting the substrate float, seems to avoid the parasitic elements of the structure. The structure, and as a first approximation its equivalent circuit are shown in Figures 9a-9b respectively. Figure 9c illustrates the measured equivalent. As is seen from the figures the calculation of the oxide capacitance  $C_{\text{OX}}$ , requires a simple unique conversion from the measured capacitance  $C_{\text{m}}$  and the conductance  $C_{\text{m}}$ .

$$C_{\text{ox}} = C_{\text{m}} \left(1 + \frac{1}{K_1^2}\right)$$

,  $R_{\text{sp}} = \frac{1}{g_{\text{m}}(1 + K_1^2)}$  where  $K_1^2 = \frac{\omega^2 C_{\text{m}}^2}{g_{\text{m}}^2}$  (5)

Although this technique looks simple, in the case of leakage from the poly to the substrate, the problems of the first technique would still exist here. Furthermore, since the whole structure is distributed, a first order lumped circuit approximation might not be adequate.

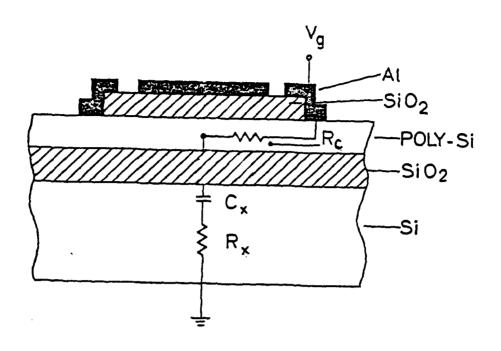

#### 2-Step Measurement

This technique utilizes a 2-step measurement, one between the gate and the substrate, and the other between the ring and the substrate. The advantage of this measurement is that it provides knowledge of the parasitics of the system. The second measurement will give directly the parasitics of the system, and by using this information in the first measurement, we will be able to extract the oxide capacitance. The measurement structures and their equivalent circuits are shown in Figures 10-11. In these figures:  $C_X$  is the total parasitic capacitance of the system,  $R_X$  is the total parasitic resistance of the system,  $R_C$  is the contact resistance between the A1 and the poly, and  $C_{OX}$  is the oxide capacitance.  $C_{m1}$ ,  $g_{m1}$  and  $C_{m2}$  are the measured equivalent capacitances and conductances of the 2-step measurement. From Figures 10-11, it can be shown that the above parameters can be calculated in terms of the measured capacitances and conductances as follows:

$$R_c = \frac{1}{g_{m2}(1 + \kappa_2^2)}$$

;  $R_x = \frac{1}{g_{m1}(1 + \kappa_1^2)} - R_c$

$$c_x = c_{m2}(1 + \frac{1}{\kappa_1^2})$$

;  $c = \left[\frac{1}{c_{m2}} \left(\frac{\kappa_2^2}{1 + \kappa_2^2}\right) - \frac{1}{c_x}\right]$  (6)

where:

$$K_1^2 = \frac{\omega^2 C_{m1}^2}{g_{m1}^2}$$

;  $K_2^2 = \frac{\omega^2 C_{m2}^2}{g_{m2}^2}$  (7)

### **Experiments**

In order to verify the above analysis, the experiments should reflect the effects of the parasitic elements of the structure. So, the experiments should be done on both highly and lightly doped samples which have thin and thick oxide layers on the substrte. The substrate should be highly doped in order to reduce the ffect of  $R_S$  and  $C_S$ . The measurements should also be done for different thicknesses of oxide grown on the poly. Given the above considerations, the following samples were prepared.

- 1. Four 2",  $\langle 111 \rangle$ , B doped wafers with 0.01  $_{\rm QCM}$  resistivity were used as substrates.

- 2. Two of these wafers were oxidized in dry  $0_2$  at 850°C for 15 min giving an average oxide thickness of 250Å. The other two wafers were oxidized in dry  $0_2$  at 1100°C for 70 min giving an average oxide thickness of 1450Å.

- 3. Poly was deposited on all of the wafers with LPCVD. The average thickness was  $0.5 \mu m$ .

- 4. The halves of the first and second group of wafers were implanted with P with a dose of  $10^{15} \rm cm^{-2}$ , whereas the other halves were implanted with a dose of  $10^{16} \rm cm^{-2}$ .

- 5. All of the samples were annealed in Ar at 1000°C for 70 min, in order to allow the dopant to redistribute.

- 6. One-half wafer from each group with  $10^{15}$  doping was oxidized at 850°C for 15 min. Both of these oxidation conditions should give 200% average oxide thickness on the poly. The rest of the samples were oxidized in dry  $0_2$  at

1100°C for 70 min. This last oxidation should give 1500A average oxide thickness on the poly. Measurements are underway at the present time to characterize these samples. When all the measurements are completed, we would expect to see the following results.

- With the floating substrate and the 2-step mesurements we would expect to measure the capacitance of the oxide on all of the samples, regardless of their preparation.

- With the shorted substrate measurement, for highly doped samples we would expect to measure the correct oxide capacitance. However, for lightly doped samples, depending on the oxide thicknesses both on the substrate and on poly we should observe differences on the measured values.

The development of this technique for measuring thin oxides on polysilicon should allow us to characterize the growth kinetics of  $\mathrm{SiO}_2$  on this film (and also on silicides and other thin films) and hence should provide better data and models for incorporation in SUPREM III.

Fig. 1. The ring-dot structure for C-V measurements.

Fig.2.a. The structure for shorted substrate measurement

. g

2.c. Measured equivalent

Fig.8

Fig.9.a. The structure for floating substrate measurement

Fig.10.a. The structure for the first step measurement

Fig.11.a.The structure for the second step measurement

## 7. ION IMPLANTATION AND RANGE STATISTICS

M. GILES, L. CHRISTEL, J. GIBBONS

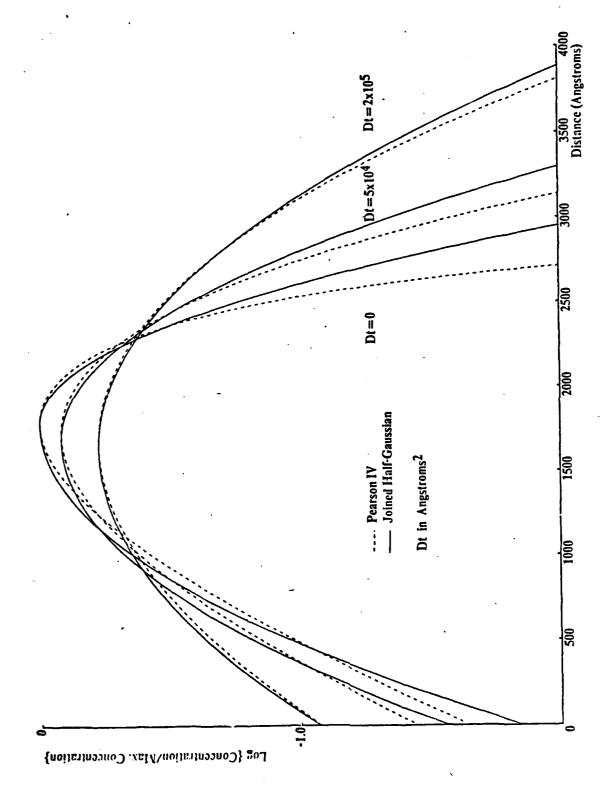

During this period the main emphasis of our work has been the application of the Boltzmann transport equation to the calculation of ion implantation profiles for light ions and at low energies. As devices shrink to sub-micron dimensions the thickness of overlying films, such as oxides, must be correspondingly reduced. This will in time require implantation energies to be lowered. It is, therefore, necessary to develop methods of calculating implanted ion profiles at these low energies. Some time has also been spent in developing a very simple model of the diffusion of implanted ions based on a joined half-gaussian profile, suitable for hand calculation or as a rapid approximation in the early stages of process development.

## 7.1 Low Energy Light Ion Implantation

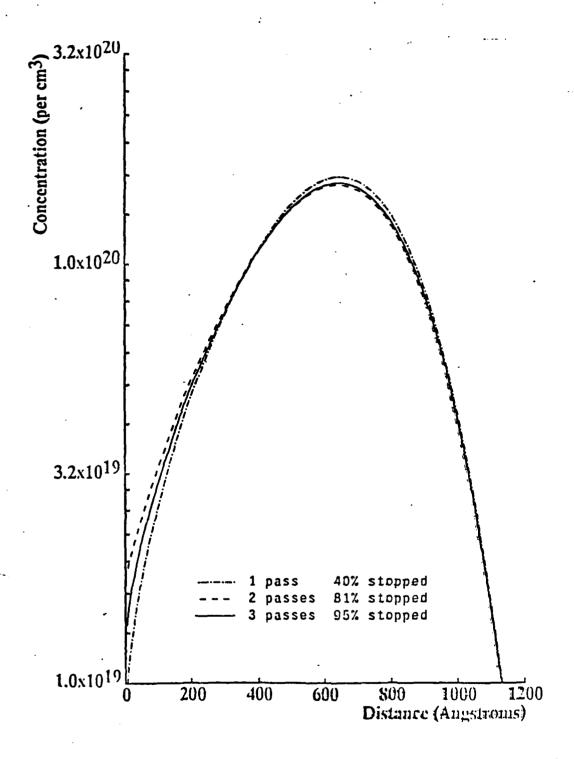

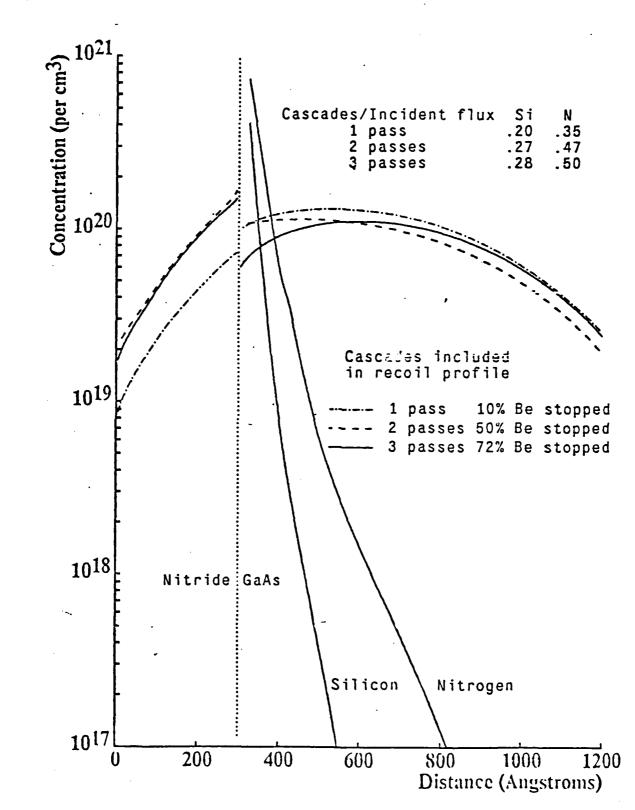

The Boltzmann transport equation approach [1] has been successfully applied to many ion implantation problems, predicting range and damage distributions, recoil distributions [2] and stoichiometric disturbances in compound semiconductors [3]. In this approach, numerical integration of the transport equation proceeds stepwise into the target. At each step the state is described by a matrix in which the value of an element corresponds to the number of ions with a certain energy E; moving at an angle  $\Theta_j$  to the surface normal. During each step scattering redistributes ions in the energy-angle matrix. Ions which are scattered to angles greater than 90° are called backscattered and were previously considered stopped at the scattering point. However, when the incident ion is much lighter than the target atoms, a large fraction of the incident ions are backscattered. To follow the motion of these ions a multiple pass approach has been developed, where each pass follows the motion of ions backscattered during the previous pass.

In the present calculations, backscattered ions are removed from the matrix and their energy and angular distribution is stored for future use. At the end of the first pass, we then have a concentration profile as before, together with a set of matrices of backscattered ions for each step into the target. The second pass is made from inside the target towards the surface, which is the direction of motion of the previously backscattered ions. At the beginning of each step the stored backscatter distribution for the depth is added to the continuing distribution of ions still moving from the previous step. Ions backscattered during the step are again stored in preparation for a third pass, and so on until all of the ions have stopped.

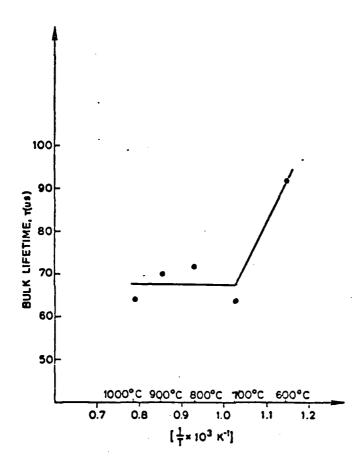

The calculated profile for Boron implanted into Silicon at 15 keV is shown in Figure 1, where the target/ion mass ratio is 2.55. Here we observe that, even though 60% of the incident Boron ions are backscattered during the first pass, there is little change in the final profile. This is because most of the backscattered ions are moving almost perpendicular to the surface so are likely to be stopped or backscattered again with only a small change. Similar results are obtained with higher beam energies, leading to the conclusion that single pass Boltzmann or LSS [4] techniques will give satisfactory profile descriptions for these cases.