| AD-A128 608<br>UNCLASSIFIED | OF CUSTOM L<br>ENGINEERING | E-ART ASSESSM<br>SI/VLSI(U)<br>GROUP M A B<br>2-04)-1-VOL-6 | AEROSPACI<br>REUER ET | E CORP<br>AL. DO | EL SEG<br>CT 82 | UNDO CA | ۱. | 1/1 | <br>i. |

|-----------------------------|----------------------------|-------------------------------------------------------------|-----------------------|------------------|-----------------|---------|----|-----|--------|

|                             |                            |                                                             |                       |                  |                 |         |    |     |        |

|                             |                            |                                                             |                       |                  |                 |         |    |     |        |

|                             |                            |                                                             |                       |                  |                 |         |    |     |        |

|                             |                            |                                                             |                       |                  |                 |         |    |     |        |

|                             |                            |                                                             |                       |                  | END             |         |    |     |        |

|                             |                            |                                                             |                       |                  | 6-83            |         |    |     |        |

MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARES-1963-A

**REPORT SD-TR-83-20**

608

8

A 12

**B**

**UTC** FILE COPY

# State-of-the-Art Assessment of Testing and Testability of Custom LSI/VLSI Circuits

9.

n

Volume VI: Redundancy, Testing Circuits, and Codes

# M. A. BREUER & ASSOCIATES Encino, Calif. 91436

and

A. J. CARLAN Technical Study Director

October 1982

Engineering Group THE AEROSPACE CORPORATION El Segundo, Calif. 90245

Prepared for

SPACE DIVISION AIR FORCE SYSTEMS COMMAND Los Angeles Air Force Station P.O. Box 92960, Worldway Postal Center Los Angeles, Calif. 90009

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED This final report was submitted by the Aerospace Corporation, El Segundo, CA 90245 under Contract No. F04701-82-C-0083 with the Space Division, Deputy for Logistics and Acquisitions, P.O. Box 92960, Worldway Postal Center, Los Angeles, CA 90009. It was reviewed and approved for The Aerospace Corporation by J. R. Coge, Electronics and Optics Division, Engineering Group. Al Carlan was the project engineer.

This report has been reviewed by the Office of Information and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nationals.

This technical report has been reviewed and is approved for publication. Publication of this report does not constit. Air Force approval of the report's findings or conclusions. It is published only for the exchange and stimulation of ideas.

FOR THE COMMANDER

APPROVED

STEPHEN A. HUNTER, LT COL, USAF Director, Speciality Engineering and Test

| REPORT DOCUMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TION PAGE                                                                                                                                                                                                                                                                                                                                                                           | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                     | 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                                                                                       |

| SD-TR-83-20                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AD-H128608                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                     |

| TITLE (and Subtitle)                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                     | S. TYPE OF REPORT & PERIOD COVERED                                                                                                                                                                                                                                                  |

| State-of-the-Art Assessment                                                                                                                                                                                                                                                                                                                                                                                                                                        | of Testing and                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                     |

| Sestability of Custom LSI/VL                                                                                                                                                                                                                                                                                                                                                                                                                                       | SI Circuits                                                                                                                                                                                                                                                                                                                                                                         | Interim                                                                                                                                                                                                                                                                             |

| Vol VI: Redundancy, Testing                                                                                                                                                                                                                                                                                                                                                                                                                                        | Circuits and Codes                                                                                                                                                                                                                                                                                                                                                                  | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                     | TR-0083(3902-04)-1                                                                                                                                                                                                                                                                  |

| AUTHOR(+)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                     | 8. CONTRACT OR GRANT NUMBER(.)                                                                                                                                                                                                                                                      |

| M.A. Breuer & Associates                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                     | F04701-80-C-0081                                                                                                                                                                                                                                                                    |

| and                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                     | F04701-81-C-0082<br>F04701-82-C-0083                                                                                                                                                                                                                                                |

| ALJ. Carlan, Aerospace Techn<br>PERFORMING ORGANIZATION NAME AND A                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DDRESS                                                                                                                                                                                                                                                                                                                                                                              | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                                                                                                                                                      |

| M.A. Breuer & Associates                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| 16857 Bosque Dr.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| Encino, CA 91436                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                     | 12. REPORT DATE                                                                                                                                                                                                                                                                     |

| CONTROLLING OFFICE NAME AND ADDRE<br>Space Division                                                                                                                                                                                                                                                                                                                                                                                                                | .33                                                                                                                                                                                                                                                                                                                                                                                 | October 1982                                                                                                                                                                                                                                                                        |

| Air Force Systems Command                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                     | 13. NUMBER OF PAGES                                                                                                                                                                                                                                                                 |

| Los Angeles, Calif. 90245                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                     | 91                                                                                                                                                                                                                                                                                  |

| MONITORING AGENCY NAME & ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                   | f different from Controlling Office)                                                                                                                                                                                                                                                                                                                                                | 15. SECURITY CLASS. (of this report)                                                                                                                                                                                                                                                |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| The Aerospace Corporation                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                     | Unclassified                                                                                                                                                                                                                                                                        |

| El Segundo, Calif. 90245                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                     | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                     | SCHEDULE                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| Approved for public release;<br>DISTRIBUTION STATEMENT (of the ebetrace<br>SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| DISTRIBUTION STATEMENT (of the abetreci                                                                                                                                                                                                                                                                                                                                                                                                                            | t entered in Block 20, if different fro<br>possery and identify by block number)<br>Exponential failure 1<br>Quadding<br>Hybrid redundancy                                                                                                                                                                                                                                          | a Report)<br>.aw SIFT computer<br>PRIME computer<br>Hamming code                                                                                                                                                                                                                    |

| DISTRIBUTION STATEMENT (of the abetrect<br>SUPPLEMENTARY NOTES<br>KEY WORDS (Continue on reverse elde if neo<br>Redundancy constructs<br>Simplex structure<br>Self checking<br>Fault-tolerant architecture<br>Reliability                                                                                                                                                                                                                                          | entered in Block 20, if different fro<br>becary and identify by block number)<br>Exponential failure 1<br>Quadding<br>Hybrid redundancy<br>Triple modular redund<br>STAR computer                                                                                                                                                                                                   | a Report)<br>.aw SIFT computer<br>PRIME computer<br>Hamming code                                                                                                                                                                                                                    |

| DISTRIBUTION STATEMENT (of the ebetrect<br>SUPPLEMENTARY NOTES<br>KEY WORDS (Continue on reverse elde if neck<br>Redundancy constructs<br>Simplex structure<br>Self checking<br>Fault-tolerant architecture                                                                                                                                                                                                                                                        | entered in Block 20, if different fro<br>every and identify by block number)<br>Exponential failure I<br>Quadding<br>Hybrid redundancy<br>Triple modular redund<br>STAR computer<br>every and identify by block number)<br>reliability and self of<br>put new emphasis on th<br>reliel, triple modular<br>computers employing or<br>e, software and time 1<br>interrelated. Mathema | aw SIFT computer<br>PRIME computer<br>PRIME computer<br>Hamming code<br>lancy<br>thecking required by the new<br>are use of redundant circuits.<br>Tredundancy, Quadd, standby,<br>are or more of these types are<br>redundancy required for error<br>atical modeling, when applied |

| DISTRIBUTION STATEMENT (of the abstract<br>SUPPLEMENTARY NOTES<br>KEY WORDS (Continue on reverse side if nece<br>Redundancy constructs<br>Simplex structure<br>Self checking<br>Fault-tolerant architecture<br>Reliability<br>ABSTRACT (Continue on reverse side if nece<br>e demands for higher system<br>ult tolerant computers have<br>pes of redundancy include pa<br>brid and software. Various<br>scussed. Generally, hardwar<br>tection and correction, are | entered in Block 20, if different fro<br>every and identify by block number)<br>Exponential failure I<br>Quadding<br>Hybrid redundancy<br>Triple modular redund<br>STAR computer<br>every and identify by block number)<br>reliability and self of<br>put new emphasis on th<br>reliel, triple modular<br>computers employing or<br>e, software and time 1<br>interrelated. Mathema | aw SIFT computer<br>PRIME computer<br>PRIME computer<br>Hamming code<br>lancy<br>thecking required by the new<br>are use of redundant circuits.<br>Tredundancy, Quadd, standby,<br>are or more of these types are<br>redundancy required for error<br>atical modeling, when applied |

| DISTRIBUTION STATEMENT (of the abstract<br>SUPPLEMENTARY NOTES<br>KEY WORDS (Continue on reverse side if nece<br>Redundancy constructs<br>Simplex structure<br>Self checking<br>Fault-tolerant architecture<br>Reliability<br>ABSTRACT (Continue on reverse side if nece<br>e demands for higher system<br>ult tolerant computers have<br>pes of redundancy include pa<br>brid and software. Various<br>scussed. Generally, hardwar<br>tection and correction, are | entered in Block 20, if different fro<br>every and identify by block number)<br>Exponential failure I<br>Quadding<br>Hybrid redundancy<br>Triple modular redund<br>STAR computer<br>every and identify by block number)<br>reliability and self of<br>put new emphasis on th<br>reliel, triple modular<br>computers employing or<br>e, software and time 1<br>interrelated. Mathema | aw SIFT computer<br>PRIME computer<br>PRIME computer<br>Hamming code<br>lancy<br>thecking required by the new<br>are use of redundant circuits.<br>Tredundancy, Quadd, standby,<br>are or more of these types are<br>redundancy required for error<br>atical modeling, when applied |

# TABLE OF CONTENTS

|      |       |       | P                                                      | 'age |

|------|-------|-------|--------------------------------------------------------|------|

| EXEC | UTIVI | SUMMA | RY                                                     | 5    |

|      | PAR   | r I   | REDUNDANCY AND FAULT TOLERANT<br>COMPUTER ARCHITECTURE | 5    |

|      | PAR   | 11    | SELF-CHECKING CIRCUITS                                 | 6    |

|      | PAR   | 111   | CODING TECHNIQUES                                      | 7    |

| PART | I     |       | ANCY AND FAULT TOLERANT COMPUTER<br>ECTURE             | 9    |

|      |       | 1.0   | Introduction                                           | 9    |

|      |       | 1.1   | Some Fundamental Principles                            | 11   |

|      |       | 1.2   | Mathematical Theory of Reliability                     | 12   |

|      |       | 1.2.1 | Failure Rate                                           | 13   |

|      |       | 1.2.2 | Exponential Failure Law                                | 13   |

|      |       | 2.0   | Principal Redundancy Structures and<br>Their Models    | 14   |

|      |       | 2.1   | Series Reliability                                     | 14   |

|      |       | 2.2   | Parallel Reliability                                   | 15   |

|      |       | 2.3   | Triple Modular Redundancy (TMR)                        | 15   |

|      |       | 2.4   | Quadd Redundancy                                       | 16   |

|      |       | 2.5   | Standby Replacement Redundancy                         | 16   |

|      |       | 2.6   | Hybrid Redundancy                                      | 18   |

|      |       | 2.7   | K-out-of-N Redundant Architecture                      | 20   |

|      |       | 3.0   | Partitioned and Balanced Fault-Tolerance               | 25   |

|      |       | 4.0   | Case Histories                                         | 26   |

|      |       | 4.1   | Quadding and the OAC-PPDS                              | 26   |

1

# 88 05 26.076

16 St. 18

|         |        | I                                                                                                                                                                               | age?                                   |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|         | 4.2    | TMR and the Saturn V LVDC                                                                                                                                                       | 27                                     |

|         | 4.3    | Standby-Sparing and the JPL-STAR Computer                                                                                                                                       | 29                                     |

|         | 5.0    | Standby Redundancy versus Autonomous<br>Redundancy                                                                                                                              | 31                                     |

|         | 6.0    | Protective Architecture for the "Hard-Core"                                                                                                                                     | 33                                     |

|         | 6.1    | Implementation of the V-D-S Unit                                                                                                                                                | 34                                     |

|         | 7.0    | Recent Trends in Fault-Tolerant Architectures                                                                                                                                   | 37                                     |

|         | 7.1    | The SIFT Computer                                                                                                                                                               | 38                                     |

|         | 7.2    | The PRIME Computer                                                                                                                                                              | 40                                     |

|         | 8.0    | Automation of Reliability Measurement<br>Processes                                                                                                                              | 41                                     |

|         | 8.1    | Unifying Notation                                                                                                                                                               | 42                                     |

|         | 8.2    | Existing Reliability Programs                                                                                                                                                   | 44                                     |

|         | 8.3    | CARE's Repository of Equations                                                                                                                                                  | 45                                     |

|         | 9.0    | References                                                                                                                                                                      | 46                                     |

|         |        | A. General References. B. Quadding. C. Saturn V LVCD and the OAO PPDS. D. Raytheon's RAYDAC. E. The JPL-STAR. F. Hybrid Redundancy. G. SIFT. H. PRIME. I. Reliability Programs. | 46<br>47<br>48<br>48<br>48<br>49<br>50 |

| PART II | SELF-C | HECKING CIRCUITS                                                                                                                                                                | 51                                     |

|         | 1.0    | Introduction                                                                                                                                                                    | 51                                     |

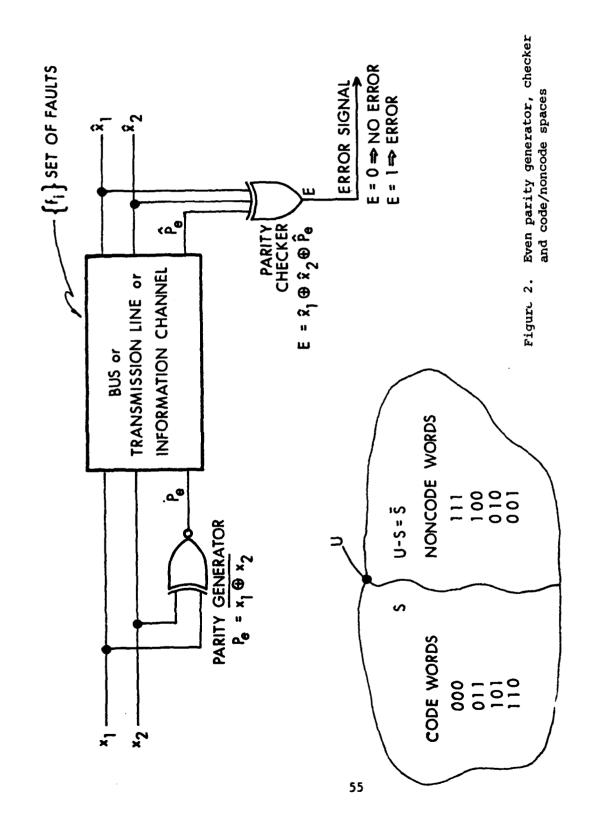

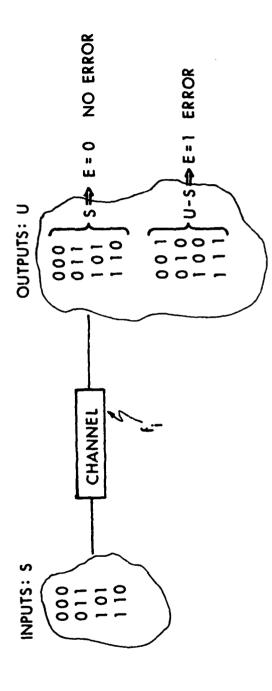

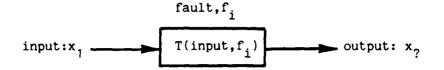

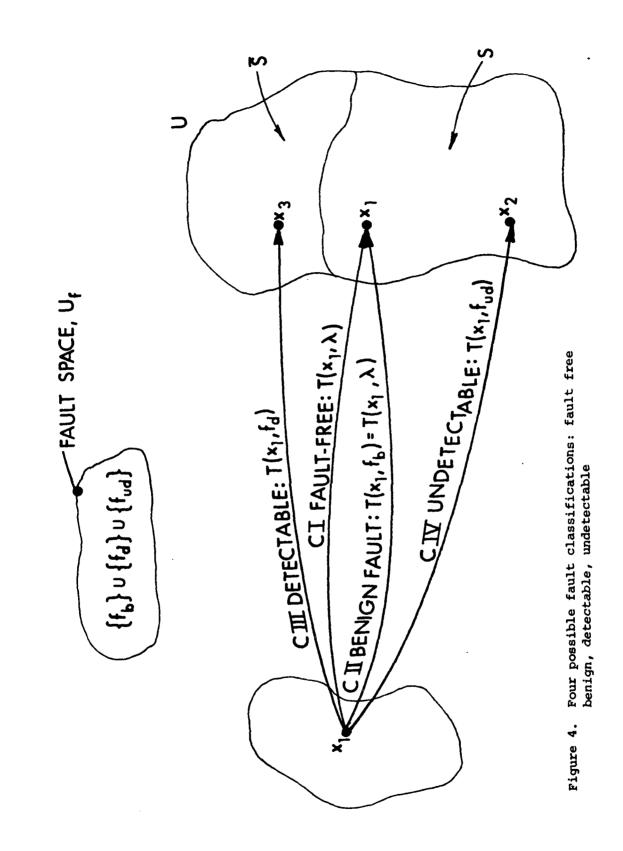

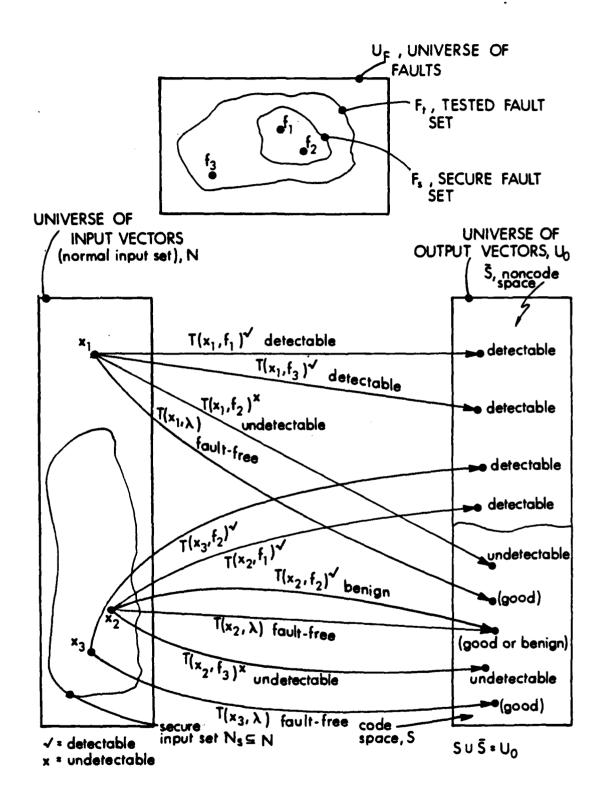

|         | 2.0    | Basic Concepts of Code Space and<br>Detectable Errors                                                                                                                           | 51                                     |

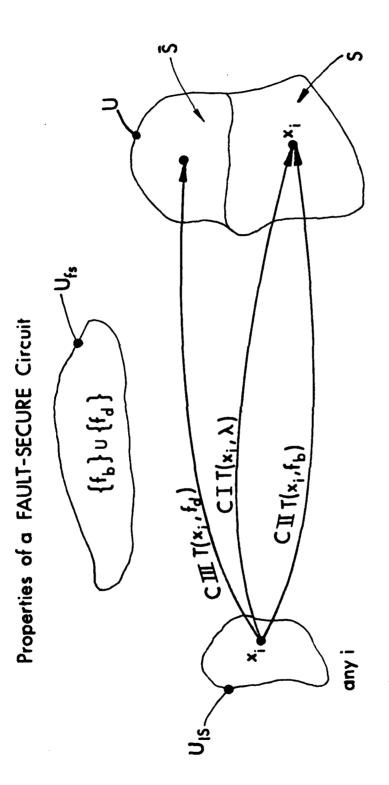

|         | 3.0    | Fault-Secure Circuits                                                                                                                                                           | 57                                     |

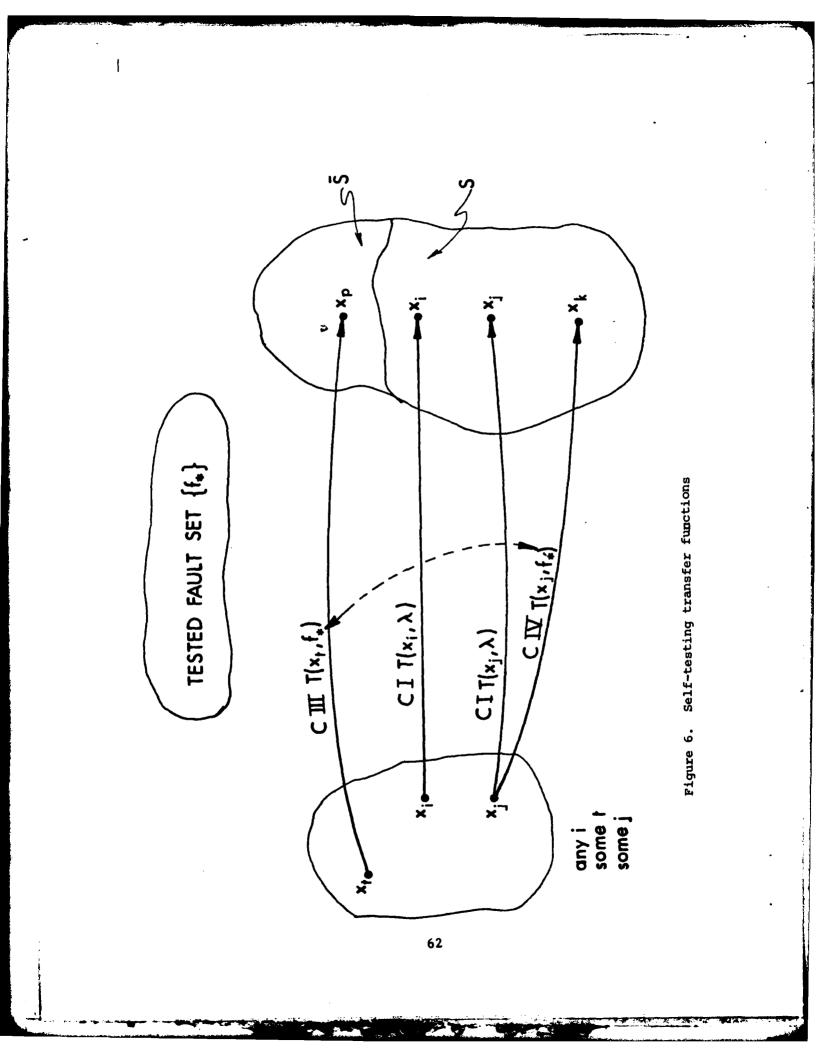

|         | 4.0    | Self-Testing Circuits                                                                                                                                                           | 60                                     |

2

5

|      |     |        | P                                                                               | age        |

|------|-----|--------|---------------------------------------------------------------------------------|------------|

|      |     | 5.0    | Totally Self-Checking Networks                                                  | 64         |

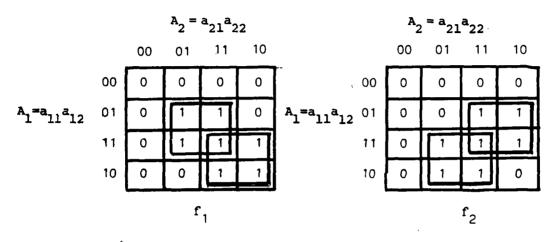

|      |     | 6.0    | Morphic Boolean Functions and their<br>Implementation as Self-Checking Circuits | 65         |

|      |     | 7.0    | Conclusion                                                                      | 69         |

|      |     | 8.0    | References                                                                      | 69         |

| PART | III | CODING | TECHNIQUES                                                                      | 71         |

|      |     | 1.0    | Introduction                                                                    | 71         |

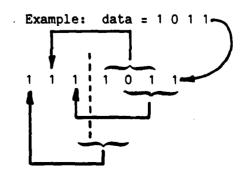

|      |     | 2.0    | Transmission Codes                                                              | 72         |

|      |     | 2.1    | Parity Bits                                                                     | 72         |

|      |     | 2.2    | Hamming Codes                                                                   | 74         |

|      |     | 2.3    | Cyclic Codes                                                                    | 77         |

|      |     | 2.4    | Codes for Asymmetric Errors                                                     | 7 <b>9</b> |

|      | -   | 2.5    | Fixed Weight Codes                                                              | 79         |

|      |     | 3.0    | Arithmetic Codes                                                                | 7 <b>9</b> |

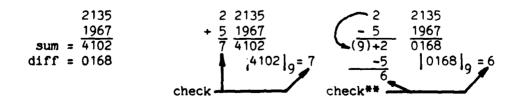

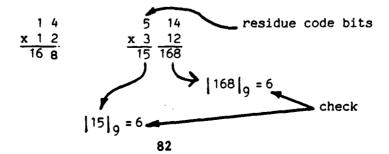

|      |     | 3.1    | Residue Operations                                                              | 80         |

|      |     | 8.2    | The Use of Residues for Arithmetic<br>Error Detection                           | 81         |

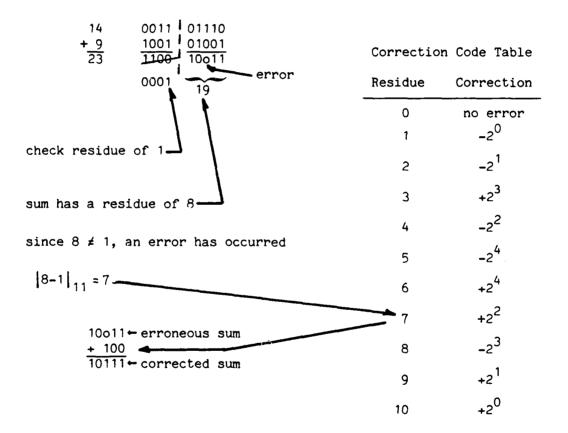

|      |     | 3.3    | The Use of Residues for Error<br>Correction                                     | 83         |

|      |     | 3.4    | The AN Product Codes                                                            | 84         |

|      |     | 3.5    | The AN+B Codes                                                                  | 85         |

|      |     | 3.6    | Sum Codes                                                                       | 87         |

|      |     | 4.0    | Other Considerations and Conclusions                                            | 87         |

|      |     | 4.1    | A Summary of Code Technology                                                    | 87         |

|      |     | 4.2    | Fault Propagation                                                               | 88         |

|      |     | 4.3    | Further Studies                                                                 | 88         |

|      |     | 5.0    | References                                                                      | 88         |

\*

#### EXECUTIVE SUMMARY

#### PART I REDUNDANCY AND FAULT TOLERANT COMPUTER ARCHITECTURE

Part I of this chapter deals with redundancy and its framework. The framework of redundancy consists of (i) modeling and evaluation of the redundancy constructs, and (ii) the embodying of the constructs in faulttolerant computer architecture.

Mathematical modeling of redundancy constructs permits their quantitative evaluation and provides a numeric basis for critical comparison.

Case histories of fault-tolerant computer architecture illustrate, by the design selection of particular redundancy constructs from the repertoire of constructs, the relative significance that the designer placed on specific redundancy constructs in relation to their functional environment in the architecture.

In general, a system if designed in such a manner that only the absolute minimum amounts of hardware is utilized to implement its function is said to be *non-redundant* or is said to have a *simplex structure*. If even after utilizing the finest components available the desired system reliability is not achieved or if failure-tolerance is desired as a system capability then *redundancy* as a design procedure is restored too, i.e., more system elements are used than were absolutely necessary to realize all the system's functions (excepting for the attributes of reliability and fault-tolerance). The additional system elements, referred to as the redundant elements, need not all necessarily be hardware elements but may also be additional software (software redundancy), additional time (time redundancy) and additional information (information redundancy). Examples of the latter are the application of errordetection and correction codes.

Naturally, the hardware, software, and time redundancy are often interrelated. Additional software requires additional memory storage and additional time is used to execute the added software. The term *protective redundancy* is often used to characterize that redundancy which has an overall beneficial effect on the system attributes since redundancy alone without proper application may well become a liability. Protective redundancy is utilized to realize

fault-tolerant digital systems and self-repairing systems by such means as triple or N-tuple modular redundancy (TMR, NMR), quadded redundancy, standbyreplacement redundancy, hybrid redundancy, software redundancy and the application of error-detection and correction codes.

Redundancy as a procedure, for designing more reliable system than allowed by the intrinsic reliability of the constituting components, is as old as the discipline of engineering itself. Examples of the use of redundancy in ancient times is provided in the civil engineering construction where more than the absolutely minimum redundancy were used as insurance against (i) the lack of accurate knowledge of underlying phenomena, and (ii) the lack of confidence in the available data on materials used. Redundancy as a procedure is even more basic. This is evidenced by the testimony of evolutionaly processes of life which make abundant use of it (e.g., in the human body there are two kidneys, two lungs, two cerebral hemispheres, etc.).

For the computer age, redundancy has been used at all levels of technology, from that of VLSI devices, circuitry, logic, subsystems, computers, and even to entire networks of digital systems.

Part I of this chapter spans the general area of fault-tolerant systems. The utilization of the various protective redundant structures as basic building blocks for fault-tolerant digital computing systems have been described and evaluated comparatively. A unifying notation for characterizing the most commonly used protective redundancy schemes has been presented. It has also been demonstrated that the k-out-of-N redundant model subsumes either directly or by composition a great number of other redundant structures.

By employing reliability analysis to these fault-tolerant systems, their overall reliability can be measured and compared.

#### PART II SELF-CHECKING CIRCUITS

Self-checking circuits by definition pertain to circuits whose outputs are encoded in an error-detecting code. In Part II of this chapter the underlying theory based on code spaces is developed to present the notions of selfchecking circuits, partially self-checking circuits, totally self-checking circuits, and totally self-checking networks. An introduction to Morphic Boolean logic is also presented which is an aid to the design of self-checking checkers. These are presented with examples and illustrations.

#### PART III CODING TECHNIQUES

Part III of this chapter deals with coding techniques used to achieve concurrent diagnosis in digital computing systems. Coding theory is the body of knowledge dealing with the science of redundantly encoding data so that errors can be detected and with further encoding even corrected.

The fundamental principles underlying transmission codes as well as arithmetic codes are developed and illustrated by the use of short simple examples. Both error detection as well as error correction properties are treated and the tradeoffs between these are explained.

The use of residue codes for protecting instruction words in the JPL-STAR computer is given as a real example.

Coding theory is a very rich and by far the most developed branch of fault-tolerant computing. The theoretical basis, the functional limits of reliable communication for a given channel, and the mathematical tools and classification schemes are well established. This section does not attempt to be an exhaustive evaluation, the emphasis taken is to highlight the essential principles by means of short examples. For the more interested practitioner pointers are provided to the literature.

#### PART I REDUNDANCY AND FAULT TOLERANT COMPUTER ARCHITECTURE

### 1.0 INTRODUCTION

A fault-tolerant computer is a computer organized and structured such that it can perform its design specified functions even in the presence of hardware failures.

By the sheer force of necessity an important attribute in computer architecture is reliability and fault-tolerance. Historically, the early days of computers, because of the unreliability of thermonic devices, were extremely innovative and productive of fault-tolerance techniques, many of which we take for granted these days, e.g., parity checking, retrying of operations, duplexing of processors, etc. Then, with the advent of semiconductors and their greater inherent reliability fault-tolerance was no longer a pressing issue, and undiverted effort was allocated to the enhancement of computational architectures. Subsequently, the space age and computer-oriented national defense needs again shifted the equilibrium between intrinsic component reliabilities on the one hand and the sheer size and complexity and hazardous application environments of the fabricated structures on the other. These demands on reliability, continuous service, and hardware integrity spawned a new breed of computer architecture entitled "fault-tolerant computers."

This chapter surveys the various techniques employed in faulttolerant architectures from the point of view of the protective redundancy structures utilized, and points out the significant features unique to the implementation of fault-tolerance in either hardware, microprogramming, or software.

The domain of reliability engineering involves considerations of all aspects of design, development and fabrication, so as to minimize the chance of equipment breakdown. Neglect of reliability considerations can prove to be very costly, from the loss of consumer accptance of the product to missions such as rocket launching of spacecrafts which depend heavily on reliability engineering. Failure of a single component could result in the total loss of the system.

٩

PRECEDING PAGE MLANK-NOT FILME

Reliability in a qualitative sense can mean a host of different things relating to the confidence in the goodness of the equipment, and is closely connected, but often confused with the concepts of maintainability, availability, safety and even security of the system. Quantitatively reliability can be formulated mathematically as the probability that the system will perform its intended function over the stated duration of time in the specified environment for its usage.

As equipment becomes more complex the chances of system unreliability becomes greater, since the reliability of an equipment depends on the reliability of its components. The relationship between parts reliability and the system reliability can be formulated mathematically to varying degrees of precision depending on the scale of the modeling effort. The mathematics of reliability is based on parts failure rate statistics and probability theoretic relationships. The mathematical theory of reliability is used to model, simulate and predict the equipment's proneness to failure under expected operating conditions.

There have been two distinct and viable approaches taken to enhance system reliability. One is based on component technology, i.e., manufacturing the component as intrinsicly reliable as possible followed by parts screening, quality control, pretesting to remove early failures (infant mortality effects), etc. The second approach is based on the organization of the system itself, e.g., fault-tolerant architectures where the architecture makes use of protective redundancy to mask or remove the effects of failure, and thereby provide greater overall system reliability than would be possible by the use of the same components in a simplex or nonredundant configuration.

Fault-tolerance is the capability of the system to perform its functions to its design specifications even in the presence of hardware failures. If, in the event of faults, the system's functions may be performed but do not meet the design specifications with respect to the time required to complete the job or the storage capacity required for the job, then the system is said to be partial or quasi fault-tolerant. Since the number of possible hardware failures can be very large, in practice it is necessary to restrict fault-tolerance to prespecified classes of faults from which the system is designed to recover.

Faults may be classified as transient or permanent, deterministic or indeterminate, local or catastrophic. The first category refers to the duration of the fault, the second to its effect on the values of the system design parameters and the third to the propagation of the fault to its neighboring elements.

Fault-tolerance is provided by the application of protective redundancy — use of more resources so as to upgrade system reliability. These resources may consist of more hardware, software or more time or combination of all of these. Extra time is required to retransmit messages or to reexecute programs, extra software is required to perform diagnosis on the hardware, extra hardware is required to provide replication of units.

Hardware redundancy may be of the fault-masking or self-repair types or a hybrid of these two. In fault-masking, redundancy is of a static nature, faults are masked instantly and the operations of fault detection, location and correction are indistinguishable. In self-repair, redundancy is used dynamically, faults are selectively masked, and are detected, located and subsequently corrected by the replacement of the failed uni. by an unfailed replica. Examples of the former are Triple Modular Redundancy (TMR) and quadding, and of the latter standby-replacement (SR) systems and reconfigurable systems. Schemes using combinations of these two basic approaches are called hybrid or adaptive redundancy.

#### 1.1 SOME FUNDAMENTAL PRINCIPLES

The fundamental principle of reliability is that reliability is not solely inherent to a component but is also a function of how the component is used. Another fundamental principle of achieving reliability by means of protective redundancy is that redundancy be applied to the smallest level of complexity of the system in order to maximize gain in reliability. This is an idealized statement since, in practice, there are tradeoffs due to overhead required in utilizing redundancy techniques, e.g., providing voters in TMR systems and detection-switching requirements in standby-sparing systems. The application of mathematical theory of reliability to model such systems provides quantitative design guidelines to make such tradeoffs and optimizations in practice. If the above are the first and second principles of fault-tolerance, then the third principle states that a system may be made arbitrarily reliable provided that the degree or redundancy is made high, i.e., a sufficiently large number of replicas are provided. Again this principle holds only in an idealized situation; in practice, since the probability of detecting a failure and correctly switching in a spare is less than unity, this parameter, called coverage, limits the advantages postulated by the third principle.

A fourth principle concerns the problem of requiring the checking elements (those elements that are used for the diagnosis of the rest of the system and the subsequent reconfiguration of the system units) also to be checkable. This is the problem of "checking the checker." Thus, the fourth principle is formulated to state that any system utilizing protective redundancy will have major and minor "hardcores" (i.e., unprotected system elements) and that these cannot be totally eliminated from the system design, however, they may be made arbitrarily small by the judicious use of a mixture of different protective redundancy techniques.

#### 1.2 MATHEMATICAL THEORY OF RELIABILITY

Some relationships between reliability parameters and the underlying probability theoretic relationships are as follows. If a fixed large number  $N_0$  of identical items is being tested of which  $N_s$  is the number of items surviving after time t,  $N_f$  the number of items which failed during time t then, for all t,  $N_0 = N_s + N_f$ . Now, for a sufficiently large  $N_0$ , the reliability R(t) of an item is  $N_s/N_0$ . The failure rate  $\lambda(t)$ , which is defined to be the rate at which the population changes at time t, can be shown to be given by

$$\lambda(t) = -\frac{1}{R(t)} \frac{dR(t)}{dt}$$

(1)

so that

$$R(t) = e^{-\int_{0}^{t} \lambda(\tau) d\tau}.$$

(2)

3 3

14.1

The reliability function R(t) is often called the survival probability function since it measures the probability that failure of an item does not occur during the time interval [0,t].

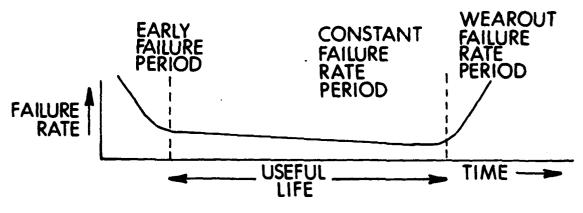

# 1.2.1 Failure Rate

Statistical data on equipment failure yields a characteristic "bath tub" curve as shown in Figure 1. When the equipment is first put into service inherently weak components fail early; this stage is also called "infant mortality." Subsequently the failure rate stabilizes quickly to a relatively constant value; this period is called the useful life period. After much usage failure rate begins to increase rapidly due to deterioration and wearout.

Figure 1. Bath-tub curve of failure rate.

#### 1.2.2 Exponential Failure Law

In general the failure law of a component is the probability distribution obeyed from the moment at which a component enters service up to the moment of its failure. In practice the most commonly used failure law is the exponential law, which applies when a component is subject only to failures which occur at random intervals and the average number of failures is the same for equal time periods. These constraints are valid for a component which is no longer subject to infant mortality failures and whose failure rate is a constant within the "useful-life" span. Thus, for operating periods within the useful life, the component reliability over a period of time t can be expressed as  $R(t) = e^{-\lambda t}$  where  $\lambda$  (usually expressed in failures per hour or per million hours) is the constant failure rate of the device. A characteristic of the exponential failure law is that, within the useful life period, the reliability of the device is the same for operating times of equal duration.

From the definition of R(t) it follows that the mean time between failures (MTBF) or the mean time to first failure (MTTF), usually expressed in hours, are given by  $\int_{0}^{\infty} R(t)dt$ , i.e., it is the area underneath the relia-

bility curve R(t) plotted versus t. This result is true for any failure distribution. For the specific case of the exponential failure law the MTBF, m, is equal to  $1/\lambda$ . Further, when the product  $\lambda t$  is small, the equation for R(t) may be approximated by R(t) $\pm 1 - \lambda t$ . Thus, if  $\lambda t = 0.01$ , R(t) =  $e^{-0.01} = 0.99$  or 99.0 percent. The product  $\lambda t$  is often referred to as the "normalized" time, since  $\lambda t = t/m$ , i.e., the mission time t normalized with respect to the MTBF.

# 2.0 PRINCIPAL REDUNDANCY STRUCTURES AND THEIR MODELS

#### 2.1 SERIES RELIABILITY

If a system is composed of elements in such a way that the failure of any one element causes a failure of the system, then these elements are considered to be functionally in series. For the system to survive each element must survive. The probability of survival for the system cannot be better than the element with the lowest probability of survival; e.g., a chain is no better than its weakest link. When these series elements are independent of each other then, by the probability multiplication law, the system survival probability is the product of the individual survival prob-

abilities of the elements, i.e.,  $R_{system} = \sum_{i=1}^{n} R_i$  where  $R_i$  is the reliability of the i<sup>th</sup> element of an n element system.

# 2.2 PARALLEL RELIABILITY

Parallel reliability is an illustration of protective redundancy. The system is composed of functionally parallel elements in such a way that if one of the elements fails the parallel unit will continue to do the system function.

The system reliability under the assumption of independence of failure of the elements is expressed by

$$R_{system} = 1 - (1-R)^n$$

which is the probability that not all the n elements have failed. The term (1-R), known as the unreliability of a unit, is the probability that a unit will fail.

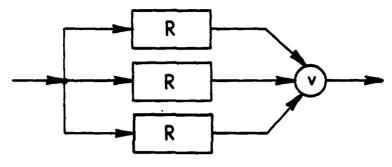

#### 2.3 TRIPLE MODULAR REDUNDANCY (TMR)

A TMR system is also known as the multiple-line voting system (see Figure 2). One of the earliest and most influential schemes was developed by J. von Neumann [1]. The simplex unit is triplicated and each of the three independent units feed into a majority voter which outputs the majority signal. The system fails if more than one unit fails in which case the failed units outvote the good one. This scheme is generalized to N-modular redundancy (NMR) where N is any odd number of units. Various schemes of protecting the voter are available and also various other variants of the basic TMR strategy have been developed. The TMR system reliability is expressed as

$$R_{system} = [R^{3} + 3R^{2}(1-R)]R_{v}$$

which is the product of the reliability  $R_v$ , the voter reliability, and the reliability of the idealized TMR system. The idealized TMR system reliability is the sum of the probabilities of the two events that (i) all three units survive,  $R^3$  and (ii) that at least any two units survive and at most one unit fails,  $3R^2(1-R)$ .

Figure 2. TMR system

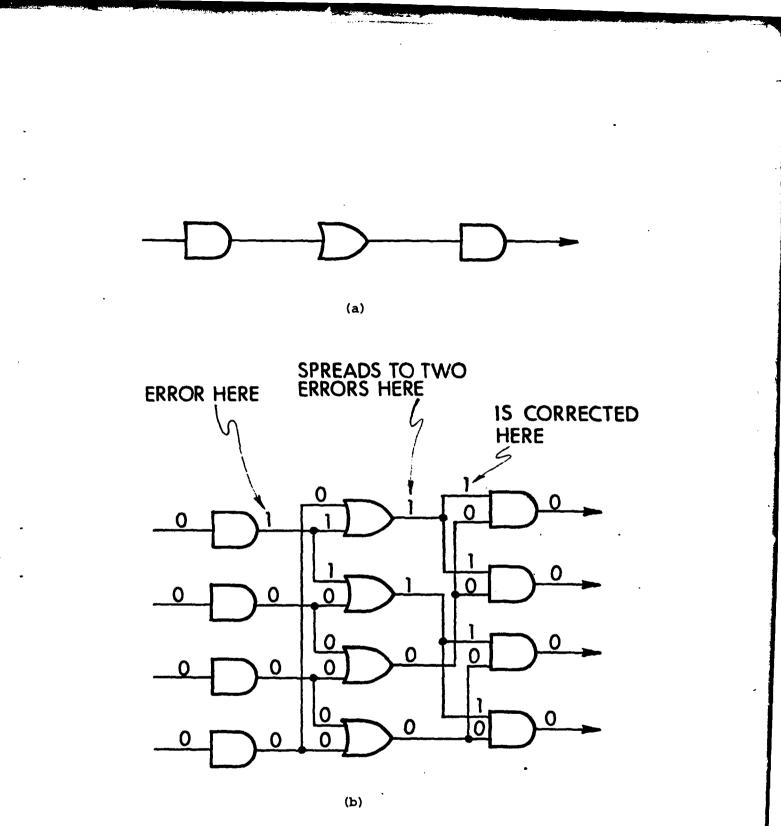

# 2.4 QUADD REDUNDANCY

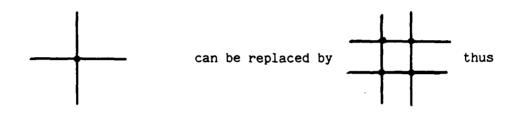

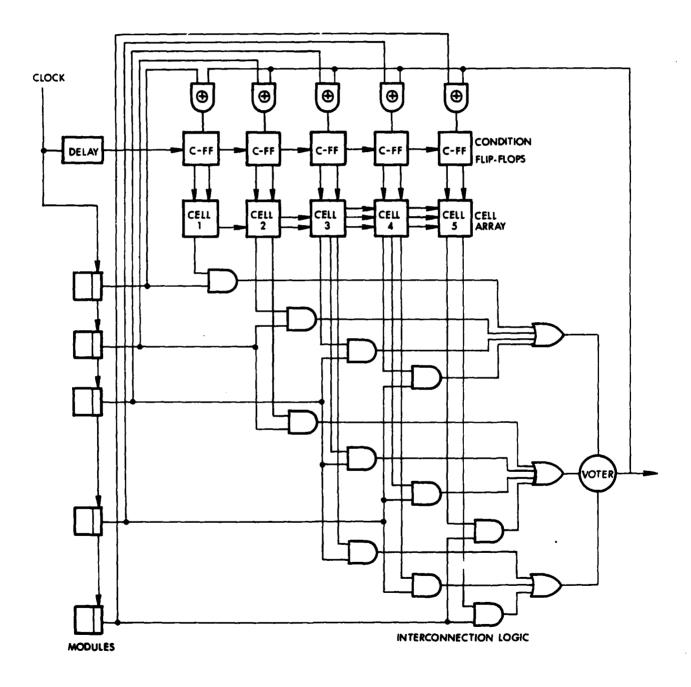

Quadding is an illustration of component redundancy and is similar in concept to TMR. The major difference is that the voting or restoration or fault-masking functions are distributed into the network and are not separable as in TMR. An example of quadding is shown in Figure 3 where the non-redundant logic circuit in Figure 3a is shown "quadded" in Figure 3b. The process of how an error downstream is subsequently corrected upstream is illustrated. In general the quadding procedure requires that each logic gate be quadriplicated and that each of the gates in a quadd stage will have twice as many inputs as the non-redundant gates replaced. The outputs of a stage are interconnected to the inputs of the succeeding stage by an interconnection pattern such that the effects of errors in earlier stages gets subsequently "restored" in the latter stages, i.e., the originally "good" signal is restored.

#### 2.5 STANDBY REPLACEMENT REDUNDANCY

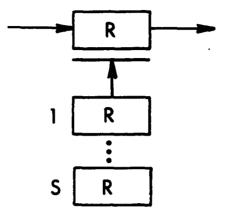

For standby replacement redundancy, unlike TMR, only one unit is operational at a time (see Figure 4). When the active unit fails this event is detected by additional circuitry and a spare unit from a reserve of spares is switched-in to replace the failed unit thereby restoring the system to its operational state. The reliability of this system is expressed as

$$R_{system} = 1 - (1-R)^{S+1}$$

which is the probability that not all units have failed.

Figure 3. An example of quadding. (a) Non-redundant circuit (b) circuit in (a) protected by quadding

10

Figure 4. Standby replacement

# 2.6 HYBRID REDUNDANCY

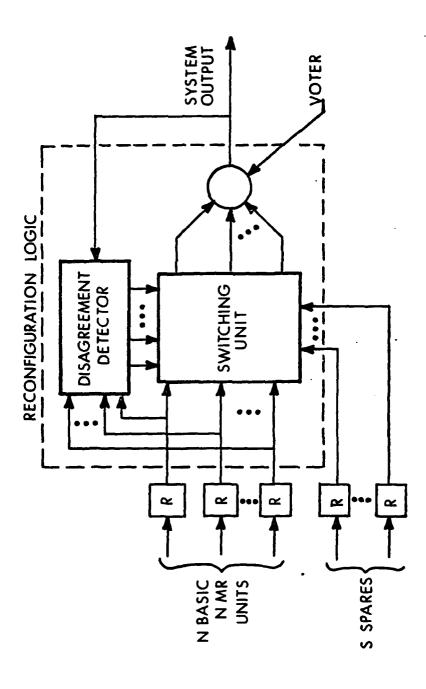

Hybrid-redundancy is a synthesis of TMR and standby replacement redundancy (see Figure 5). It consists of a TMR system (or in general an NMR system) with a bank of spares such that when one of the TMR units fails, the failed unit is replaced by a spare unit. Failure detection is achieved by means of the disagreement detector which compares the individual outputs of each of the TMR'd units with the system output. Upon a disagreement the disagreement detector issues a signal to the switching network to replace the failed unit by a spare unit. At such time as all spares are utilized the hybrid redundancy system reduces to a TMR system. Variations of the hybrid or adaptive redundancy schemes are available. The system reliability in its simplest terms may be expressed as

$$R_{system} = 1 - [(1-R)^{S+3} + (S+3)(1-R)^{S+2} R]$$

which is the probability that not all S+3 units fail and that not any S+2 units fail with one not failing.

A comparison of reliability improvement and mean-life improvements of systems using no redundancy (simplex systems), TMR, standby sparing, and hybrid redundancy is presented by Mathur [27].

S.

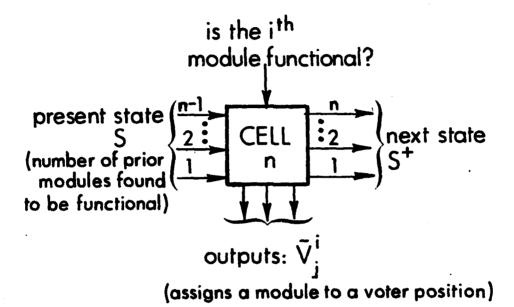

# 2.7 K-OUT-OF-N REDUNDANT ARCHITECTURE

This section gives a unified treatment of the various protective redundancy structures described in the preceding. It is contended that by and large all fault-tolerant computers are particular cases of the class of partitioned K-out-of-N redundant structures. The main differences being in (i) the degree of partitioning used and (ii) the means of error-detection employed.

The basic underlying structure of all Hardware Implemented Fault-Tolerant (HIFT) systems is the so-called K-out-of-N structure. It is composed of a total of N identical units. For the structure to function at least K of the N replicated units must remain operational. Hence its name. This structure can tolerate up to (N-K) independent failures, one in each of (N-K) out of the total N units. Thus, these structures exhibit a fault-tolerance, t equal to N-K. Here by fault-tolerance is meant the total number of replicas that the system can afford to have failed yet itself remain operational.

If r is the reliability (survival probability) or an individual replicated unit then the reliability of the K-out-of-N structure under the assumption that failures are independent events is given by the expression

$$R(K-out-of-N) = \sum_{i=1}^{N} {N \choose i} r^{i} (1-r)^{N-i}$$

where

$$\binom{N}{i} = \frac{N!}{(N-i)!i!}$$

This reliability expression is simply the summation of all the successful events, i.e., the system survives provided K,K+1,K+2,...,N-1 or N units survive. The probability of exactly i units surviving is  $r^{i}$ . The probability of exactly (N-i) units having failed is  $(1-r)^{N-i}$ , and the number of ways in which this event can occur is N-combinatorial-i. The summation of all these events from i =K to N yields the above general expression. This powerful expression has a number of special cases which

represent many of the commonly used protectively redundant structures. These special cases will now be described.

Case where K = N: Here all units need to survive for the structure to survive. This is the case when all units are in *series* reliability, and is representative of *simplex* (i.e., non-redundant) designs. Here the system reliability in terms of the unit reliability r is:

$R(N-out-of-N) = r^{N}$

and this structure exhibits zero fault-tolerance.

Case where K = 1: Here only one unit of the total N needs to survive for the structure to survive. This is typical of standby-spare redundancy, where one unit is active at any given time and the remaining are dormant as standbys.

$R(1-out-of-N) = 1-(1-r)^{N}$

The above reliability expression for standby-spares states that for the structure to be functional not all of the N units should have failed. Thus the case K = 1 represents a structure in *parallel* reliability, and exhibits a fault-tolerance of t = N-1.

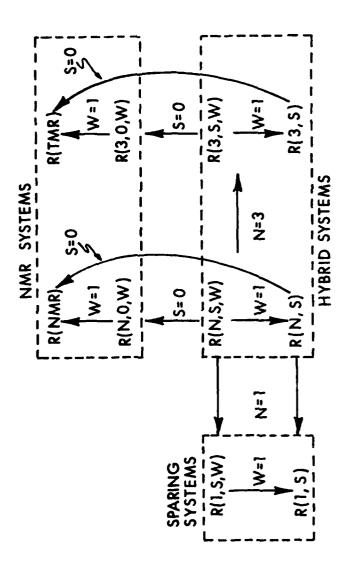

Case where K = 2: The above two cases of K = 1 and K = N are the upper and lower bounds on the K-out-of-N structures. Now for the intermediate values of K. If K = 2, then the structure survives provided that at least two out of the N units are operative. This is the condition for a Hybrid redundant system having 3 units in triple modular redundancy (TMR) and the remaining units as standbyspares. In the Hybrid redundant architecture (hybrid because it combines TMR and standby-spare redundant structures) three of the total N units are operated in TMR and the remaining N-3 units as backup units. Whenever one of the units composing the TMR structure fails it is replaced by one of the backup units. This process would continue until all backup units are exhausted at which time the hybrid structure reduces to a TMR structure. The TMR structure remains operative as long as at least 2 out of the three units, remain functional. Since only two units were required to remain operational throughout the system life of the structure and is equivalent to the hybrid redundant architecture. The system reliability is given by

.. .

$$R(2-out-of-N) = 1 - (1-r)^{N-1}[1+r(N-1)]$$

the fault-tolerance of a hybrid redundant system is equal to N-2.

Case where K = 2 and N = K+1: It is well known that hybrid redundant system H(3,S) with no spares is equivalent to a TMR configuration. Thus in the previous case if the total number of units N is three and K is still 2 we then have the classical von Neumann TMR system, i.e., for the system to remain operational at least 2 out of the three total units must remain operational. The reliability equation of the TMR system is given by

$R(2-out-of-3) = r^3 + 3r^2(1-r)$

\$23.

has a fault-tolerance, t of one.

Case wehre K = (N+1)/2: The TMR structure can be generalized to an Nmodular redundant (NMR) structure when N is any odd number of units operating in a majority configuration, i.e., an (N+1)/2-out-of-N configuration. The reliability expression for the NMR system is

$$R((N+1)/2-out-of-N) = \sum_{i=0}^{(N-1)/2} {N \choose i} (1-r)^{i} r^{N-i}$$

This system is capable of tolerating (n-2)/2 failures.

Case where K = (n+1)/2 with n odd: This case corresponds to the generalized hybrid redundant architectecture having a general nMR core and (N-n) spares. If the number of spares is zero then this case reduces to the previous one for NMR. The general hybrid redundant architecture can tolerate (N-n)+(n-1)/2failures.

#### Composition of K-out-of-N Structures

The fact that hybrid redundancy is a combination of TMR and standbysparing is readily seen from the *composition* of the following two K-outof-N structures:

- (i) 1-out-of-N ..... standby-sparing

- (ii) 2-out-of-3 ..... TMR

(i) and (ii) are composed to yield:

(2-out-of-3)-out-of-N+3 ..... Hybrid redundancy

the composition of (i) and (ii) is the Hybrid(3,N) system using a total of N+3 units.

Similarly for the generalized Hybrid redundancy case, NMR redundancy and standby-sparing can be composed thus:

(iii) 1-out-of-S ..... standby-sparing

(iv) (N-1)/2-out-of-N ..... NMR

The composition of (iii) and (iv) yields:

((N-1)/2-out-of-N)-out-of-S+N ..... General hybrid

This composition represents the general hybrid redundant structure of H(N,S) having a total of N+S units.

Similarly other redundancy schemes can be shown to have a K-out-of N structure. The intent has not been to exhaustively list all equivalences, the reader may readily try to represent some of the other redundant structures as K-out-of-N. The structures described here are summarized in Table I.

| STRUCTURE   | К                    | FAULT-TOLERANCE, t |

|-------------|----------------------|--------------------|

| Series      | K = N                | 0                  |

| Parallel    | K = 1                | N - 1              |

| TMR         | K = 2; N = K+1       | 1                  |

| NMR         | K = (N+1)/2; N = odd | (N-1)/2            |

| Hybrid(3,S) | K = 2                | N - 2              |

| Hybrid(n,S) | K = (n+1)/2; n = odd | S + (n-2)/2        |

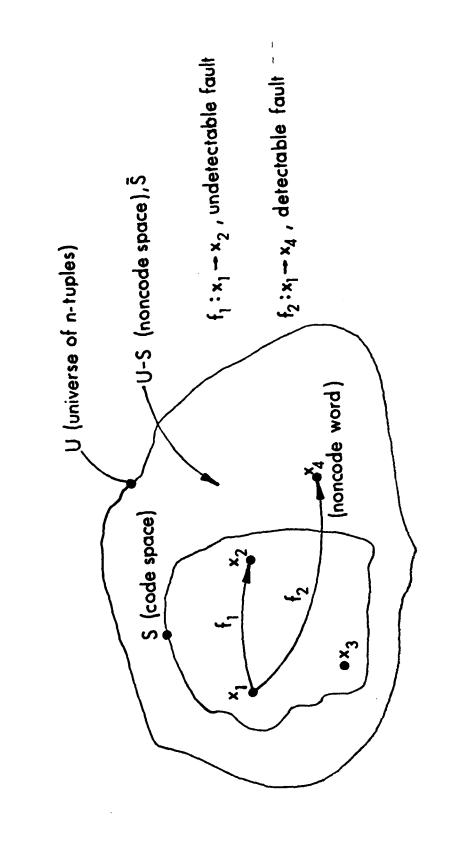

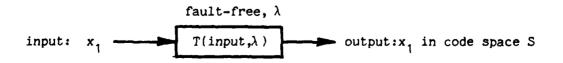

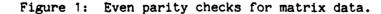

Table I: Summary of K-out-of-N Structures