SYSTEMS Instrument Corporation

FAIRCHILD IMAGING SYSTEMS

A Division of Fairchild Camera and Instrument Corporation

9 quarterly technical reptinoss, Oct - Dec 79.

(11) 75 Jan 80

Report #ED-CX-141-5 A 0 80 96 %

Analog Frame Store Memory

15 January 1980

12,62

CDRL SEQ. NO. A002

SELECTE MAR 1 3 1980

Contract DAAK70-78-C-0165

NIGHT VISION LABORATORY

This document is furnished in response to the Night Vision Laboratory Contract No. DAAK70-78-C-0165. The Government shall have the right to duplicate, use, or disclose the data to the extent provided in the contract. This restriction does not limit the Government's right to use information contained in the data if it is obtained from another source

DISTRIBUTION STATEMENT A

Approved for public release Distribution/Unlimited

A. Roberts Program Manager I. Hirschberg

Director, Electro-Optical Equipment

401913 St

A Division of Fairchild Camera and Instrument Corporation

THIS FIFTH QUARTERLY REPORT

COVERS THE PERIOD FROM

OCT. 1979 THROUGH DEC. 1979

| Aless inteer            |   |

|-------------------------|---|

| Wils dual               |   |

| Incl FAB - Inappeniaged |   |

| Alle Cup                | 4 |

| Ey                      |   |

| Distributions/          |   |

| Avalue                  |   |

| 10.00                   |   |

| Dist   Suc 11           |   |

| 111                     |   |

|                         |   |

A Division of Fairchild Camera and Instrument Corporation

# TABLE OF CONTENTS

| SECTION | TITLE                                 | PAGE |

|---------|---------------------------------------|------|

| 1.0     | INTRODUCTION                          | 1-1  |

| 1.1     | SYSTEM DESCRIPTION                    | 1-2  |

| 1.1.1   | Analog Frame Store Memory             | 1-2  |

| 1.1.2   | Analog Field Storage Device           | 1-4  |

| 1.1.3   | Image Analyzer Digital Display (IADD) | 1-4  |

| 1.2     | PROGRAM'S GOAL                        | 1-5  |

| 1.3     | TEST RESULTS                          | 1-6  |

| 2.0     | PROGRAM STATUS                        | 2-1  |

| 2.1     | SCHEDULE                              | 2-1  |

| 2.2     | TECHNICAL                             | 2-1  |

| 2.2.1   | Analog Field Storage Device (001AA)   | 2-1  |

| 2.2.2   | IADD (001AD)                          | 2-3  |

| 2.2.3   | Analog Frame Store Memory (001AC)     | 2-3  |

| 2.3     | ACTIVITIES FOR NEXT QUARTER           | 2-3  |

| 3.0     | DESIGN                                | 3-1  |

| 3.1     | ANALOG FIELD STORAGE DEVICE           | 3-1  |

| 3.1.1   | Input Circuit                         | 3-1  |

| 3.1.2   | Parallel Register                     | 3-1  |

| 3.1.3   | Output Circuit                        | 3-2  |

| 3.1.4   | Timing Requirement                    | 3-3  |

| 3.2     | ANALOG FRAME STORE MEMORY             | 3-4  |

| 3.2.1   | Input Circuits                        | 3-4  |

| 3.2.2   | Timing Circuits                       | 3-5  |

| 3.2.3   | Output Circuits                       | 3-6  |

| 3.2.4   | Control ID                            | 3-7  |

| 3.2.5   | Temperature Control Circuit           | 3-7  |

| 3.2.6   | Mode 3 Operation                      | 3-8  |

| 3.3     | IMAGE ANALYZER DIGITAL DISPLAY (IADD) | 3-10 |

| 3.3.1   | Input Section                         | 3-12 |

A Division of Fairchild Camera and Instrument Corporation

# TABLE OF CONTENTS (Continued)

| SECTION | TITLE                               | PAGE |

|---------|-------------------------------------|------|

| 3.3.2   | Memory Subsystem                    | 3-13 |

| 3.3.3   | Output Logic                        | 3-17 |

| 3.3.4   | TV Sync Generator/Master Oscillator | 3-17 |

| 3.3.5   | Video Processor                     | 3-18 |

| 3.4     | POWER REQUIREMENTS                  | 3-18 |

| 3.4.1   | Analog Frame Store Memory           | 3-18 |

| 3.4.2   | IADD                                | 3-18 |

| 3.5     | PACKAGING                           | 3-19 |

| 3.5.1   | Analog Field Storage Device         | 3-19 |

| 3.5.2   | Analog Frame Store Memory           | 3-19 |

| 3.5.3   | IADD                                | 3-20 |

A Division of Fairchild Camera and Instrument Corporation

# APPENDIX

|   | TITLE                                    | PAGE   |

|---|------------------------------------------|--------|

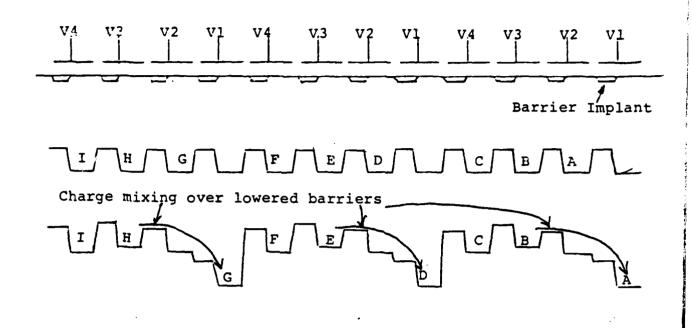

| 1 | CHARGE SPILLAGE IN A' FOUR PHASE SYSTEM  | A1 - 1 |

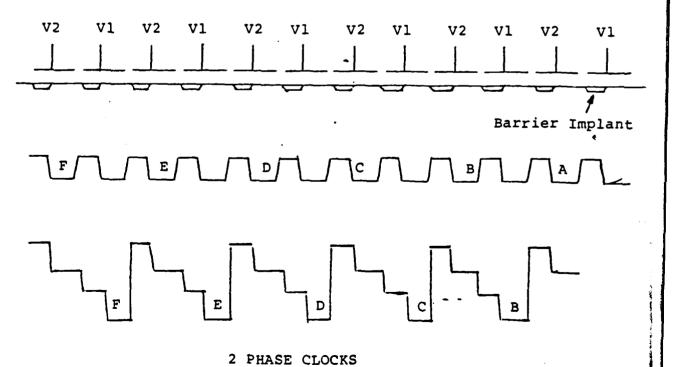

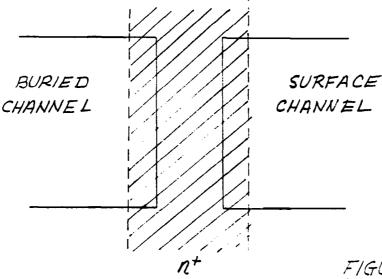

| 2 | DESCRIPTION OF BURIED-TO-SURFACE CHANNEL | A2 - 1 |

A Division of Fairchild Camera and Instrument Corporation

# LIST OF FIGURES

|        |                                              | FOLLOWS     |

|--------|----------------------------------------------|-------------|

| FIGURE | TITLE                                        | PAGE NO.    |

|        | _                                            |             |

| 1-1    | Analog Frame Store Memory PRV Application    | 1-2         |

| 1-2    | Mode 3 Composite Display                     | 1-4         |

| 2-1    | Project Schedule                             | 2-1         |

| 2-1A   | Project Schedule (Revised Plan)              | 2-1         |

| 2-2    | Chip Layout                                  | 2-1         |

|        |                                              |             |

| 3-1    | Analog Field Storage Device<br>Block Diagram | 3-1         |

| 3-2    | Input Circuit                                | 3-1         |

| 3-3    | Interleaved Clocking                         | 3-2         |

| 3-4    | Output Circuit                               | 3-2         |

| 3-5    | Timing Diagram                               | 3-3         |

| 3-6    | Analog Frame Store Memory<br>Block Diagram   | 3-4         |

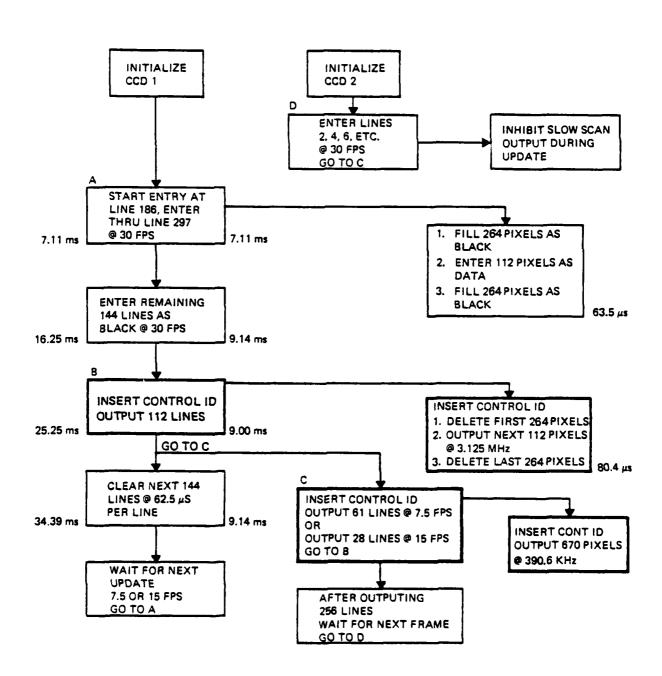

| 3-7    | Algorithm; Dual Data Rate<br>Non-Interlaced  | 3-8         |

| 3-8    | Algorithm; Dual Data Rate<br>Non-Interlaced  | 3-8         |

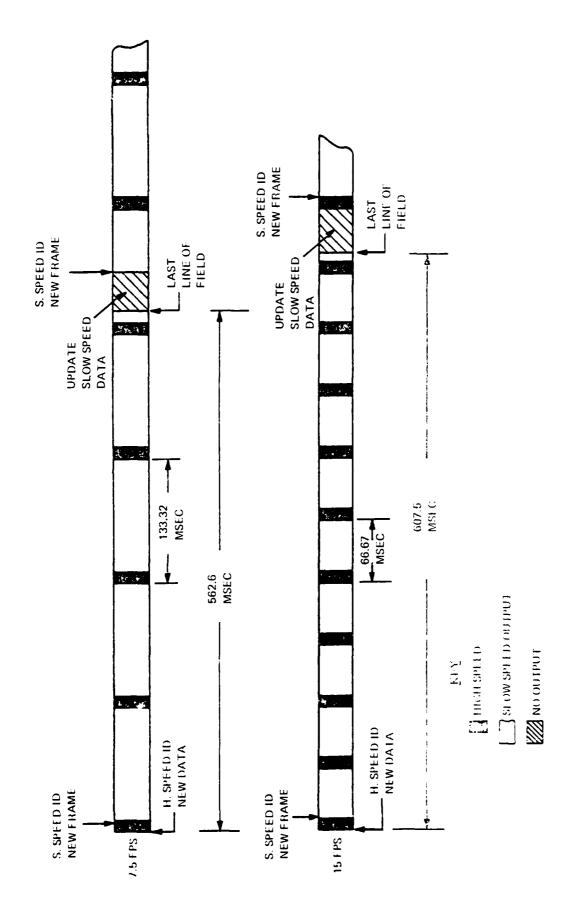

| 3-9    | Dual Data Rate Output                        | 3-9         |

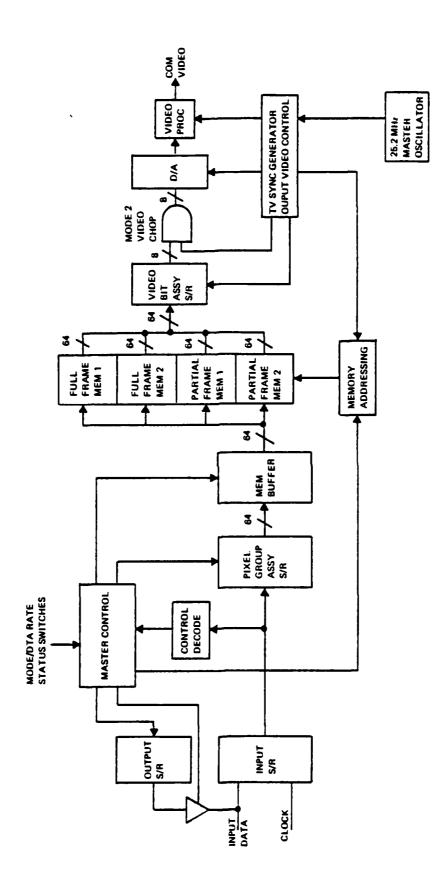

| 3-10   | IADD Block Diagram                           | 3-11        |

| 3-11   | Control Codes                                | 3-13        |

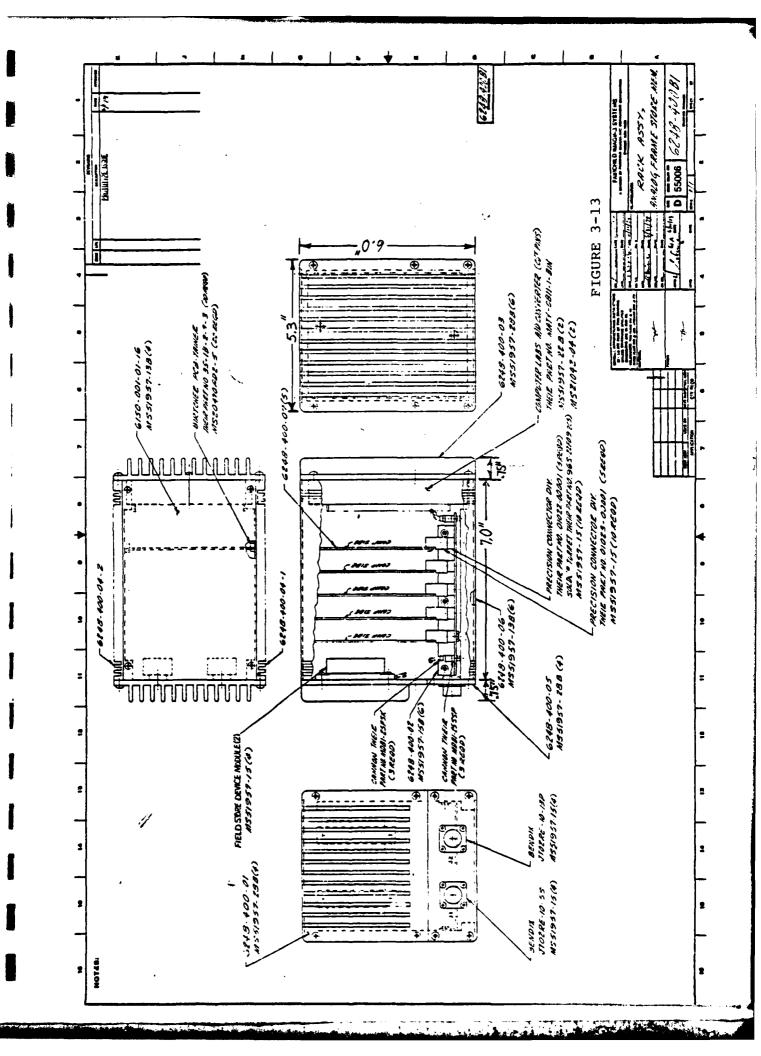

| 3-12   | Field Storage Device (30712)                 | 3-19        |

| A1-1   | Clocking Schemes                             | A1-1        |

| A2-1   | N+ Diffusion                                 | on pg. A2-1 |

| A2-2   | Well Diagram                                 | A2-1        |

A Division of Fairchild Camera and Instrument Corporation

# LIST OF TABLES

| Table | <u>Title</u>                | Page No. |

|-------|-----------------------------|----------|

| 2-1   | Device Pin Outs             | 2-2      |

| 3-1   | Field Storage Device Design | 3-1      |

A Division of Fairchild Camera and Instrument Corporation

#### SECTION I

1.0

#### INTRODUCTION

The Analog Frame Store Memory is an all solid state high density storage unit capable of storing a full frame of TV information in analog form for periods up to ten (10) seconds. The storage element is a state-of-the-art monolithic charge coupled device (CCD) which contains a sufficient number of storage sites for a field of TV information. The Frame Store Memory combines two (2) devices to obtain a full frame of storage. Data is inputted to memory in analog form at the standard TV rate of 30 Frames Per Second (FPS) and is outputted through an A/D converter at one of six (6) selectable rates; 0.1 to 7.5 FPS.

When installed in the RPV, the Analog Frame Store Memory provides a frame storage buffer between the TV camera and the data compression encoder. Full frame storage of the TV imagery minimizes the complexity of the data compressor when transmitting over the RPV's narrow band data link. The small size, low power and ruggedness of the Analog Frame Store Memory make it an attractive candidate for the Army RPV application, in particular, and to act as an intermediate buffer for general TV based imaging systems.

Image reconstruction of the received signal, after decoding, is accomplished in the Image Analyzer Digital Display (IADD). The IADD consists of two (2) full frame dynamic random-access digital memories operating in a "ping-pong" fashion to provide a continuous display on a standard TV monitor. The IADD also provides the operating instructions (Mode Select, Data Rate, etc.) for the Analog Frame Store Memory.

A Division of Fairchild Camera and Instrument Corporation

#### 1.1 SYSTEM DESCRIPTION

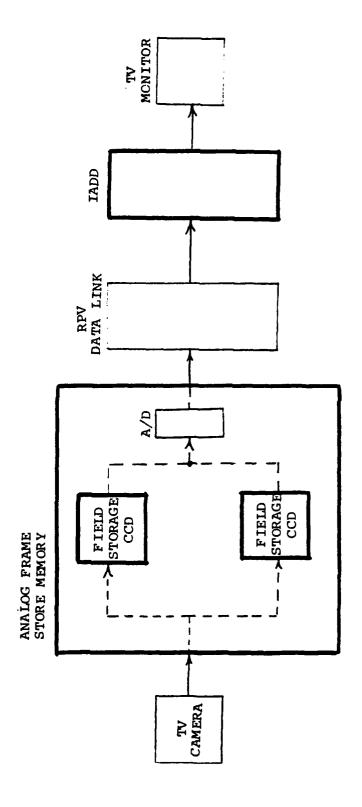

Figure 1-1 illustrates the Analog Frame Store Memory System concept in the RPV application. Those elements designed and developed under this contract are shown in heavy outline.

# 1.1.1 Analog Frame Store Memory

The Analog Frame Store Memory combines two (2) field storage devices with the necessary electronics (drivers, logic, video processor, etc.) to operate on the incoming video in the following modes:

- A. Mode 1 In this mode the Analog Frame Store Memory operates in a scan rate reduction mode. Data is inputted to memory at 30 FPS in either interlaced or non-interlaced format. The storage capacity is 512 lines at 640 samples per line. Data is digitized and outputted at one of six (6) selectable rates from 0.1 to 7.5 FPS.

- B. Mode 2 Sampling theory dictates that at least two samples per pixel are required in order to resolve imagery unambiguously at the Nyquist limit. However, this would require 1280 samples per line. Mode 2 requires only 640 samples to achieve unambiguous resolution at Nyquist.

In this mode, multiplexed sampling is used at twice the Nyquist limit for each horizontal line. In this fashion, two TV lines contain interleaved sampling data which is at twice the Nyquist limit. Twice Nyquist data is stored in the frame store memory by inputting data to device 2 with input transfer clocks that are 1/2 pixel delayed with respect to the transfer clocks for device 1. For example, a black-white pattern at

FIG. 1 - 1 ANALOG FRAME STORE MEMORY RPV APPLICATION

all complete to

A Division of Fairchild Camera and Instrument Corporation

twice Nyquist frequency will result in all white levels being stored in device 1 for lines 1,3,5, etc. and all black levels in device 2 for lines 2,4,5, etc. This data is scan converted, digitized and sent to the IADD as in Mode 1.

The IADD will reconstruct the picture by reading lines 2,4,6, etc. out of memory with a 1/2 pixel shift. Prior to the D/A conversion, the odd and even fields are chopped at twice Nyquist with in phase and 180° out of phase signals, respectively. This will result in a dot pattern display on the monitor of a full TV frame having increased horizontal resolution greater than the Nyquist limit of the storage devices.

From the above, it is apparent that as long as the display is reconstructed in the same mode, and with the same timing, as the original sampled video a "dot matrix" display is obtained which contains video frequency components proportioned to the width of the sample pulse. This technique will be evaluated from a human factors standpoint as well as from a resolution standpoint.

C. Mode 3 - There are applications where it is necessary to view a portion of a scene, containing targets of interest, with more frequent updates than are available in the scan rate reduction mode and still maintain compatibility with the information handling capability of the data link. It is also desirable to preserve the remainder of the scene as background. This is typical of a system operating in a target acquisition or tracking mode. In Mode 3, this is accomplished by storing two sets of data in the Analog Frame Store Memory. One set of data represents a field of the incoming video and is updated at a rate of 1 FPS. The other set of data represents the center 112 lines of a frame of the same incoming video. These 112 lines

A Division of Fairchild Camera and Instrument Corporation

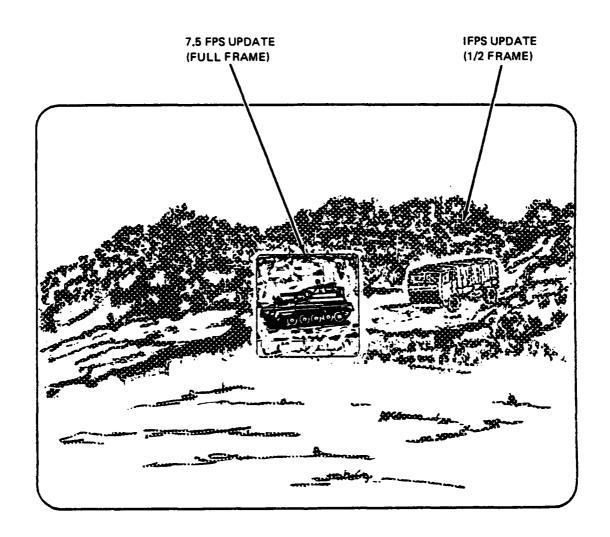

are truncated so that only the center 112 of the 640 available samples are stored. This data is updated at a rate of 7.5 or 15 FPS. The two sets of data are transmitted to the IADD in a time interleaved fashion. The resulting composite picture displayed on the TV monitor is illustrated in Figure 1-2. This concept can readily be adapted to target tracking by providing variable position information to move the 112 x 112 area to any point in the raster.

The outputs from the field storage devices are combined and A/D converted into an eight bit serial format. The code idents for start of line, start of frame, etc., are added to the combined output and formatted to operate directly into the IADD.

# 1.1.2 Analog Field Storage Device

The Analog Field Storage Device is a solid state monolithic array operating on the "charge coupled" principle. It consists of 640 columns of storage registers with each column containing 256 storage sites. An input register, capable of clocking data in at rates from 40KHz to 12.0MHz, is located at the top of the array, with an ouput register having the same clocking capability located along the bottom edge. A device is thus capable of storing 164K samples of analog data or one field of standard TV. Data can be held in storage for periods up to 10 seconds with cooling. The entire device is contained on a single 199 x 740 mil chip.

# 1.1.3 <u>Image Analyzer Digital Display (IADD)</u>

The IADD performs the picture reconstruction function. It accepts the digital data stream from the Analog Frame Store Memory and creates a digital image frame of  $488 \times 640 \times 8$  bits. It performs digital to analog conversions to create a 30 FPS composite video

FIGURE 1-2. ILLUSTRATED TV MONITOR DISPLAY OF THE IMAGERY AT THE IADD OUTPUT DURING MODE 3 OPERATION

A Division of Fairchild Camera and Instrument Corporation

signal for display on a standard TV monitor. The IADD consists of two (2) 512 x 1024 x 8 bit dynamic random-access memories operating in a "ping-pong" fashion to provide a continuous display of the video signals from the Analog Frame Store Memory in modes 1 and 2. In Mode 3, two (2) 112 x 112 static memories are operated to re-construct the high speed data while the dynamic memory is used to reconstruct the background.

### 1.2 PROGRAM'S GOAL

The program's goal is to demonstrate an operational capability to provide scan rate reduction of standard TV signals employing solid state analog storage techniques using charge coupled devices.

To achieve this goal, the program provides for the development of a state-of-the-art analog field storage CCD and the design, fabrication and evaluation of the Analog Frame Store Memory.

The program is to be carried out in three (3) phases. Phase I provides for the design, fabrication (six devices) and characterization of the analog field storage device. Phase II provides for the design, fabrication, test and evaluation of one Analog Frame Store Memory. The frame store memory will be fabricated, using two (2) field storage devices from Phase I. During Phase II, the IADD will be designed and built for use during evaluation. The results of both the Phase I characterization and Phase II evaluation will be used to optimize the storage device during Phase III.

Twelve (12) optimized devices will be fabricated, two will be used to retrofit the Analog Frame Store Memory and the remainder delivered to NVL.

A Division of Fairchild Camera and Instrument Corporation

#### 1.3 TEST RESULTS

The storage function of the field storage device, hereafter referred to by P/N 3071Z, has been demonstrated by the operation of the reduced scale test device. This includes operation of the input/output registers, amplifers and storage sites. The test device included in the 3071Z wafer contains 209 x 254 storage sites and is a direct scaling of the 3071Z device, except that it does not contain on-chip logic and drivers. Additional testing is in progress to quantify the results, and will be included in the next quarterly report. The results obtained form the initial testing of the 3071Z device is inconclusive. The presence of a mask error in the on-chip logic circuitry precluded testing of the device. The mask error has been verified in the testing of the logic and driver test chip which is fabricated from the same mask set as the on-chip logic and drivers for the 3071Z device and is located on the same wafer.

As presently configured, the error in the on-chip logic circuit results in an inoperative 3071Z device. A two-chip approach has been formulated and approved by NVL which will correct this error during the current phase, using the existing wafers, by implementing a minor mask change. This two-chip approach removes the logic and driver circuit from the storage chip ad re-locates only the drivers in a separate chip. The driver circuit is identical to the driver test circuit already designed into the wafer mask set. During this phase, the logic will be provided by discrete circuitry.

A Division of Fairchild Camera and Instrument Corporation

The two chip approach offers several advantages over the present configuration, including a more effective distribution of power and complexity. To retain these benefits in the optimization phase, while minimizing the perpheral circuitry, a new mask set will be generated to include the logic in the driver chip. The storage chip will be modified as required by the results of phase 1. The resulting two-chip configuration from this phase will maintain the TTL interfaces required by the one-chip design. Each individual chip will be assembled into a dual-in-line package (dip).

A Division of Fairchild Camera and Instrument Corporation

#### SECTION II

### 2.0 PROGRAM STATUS

#### 2.1 SCHEDULE

There are two schedules included in this report. The schedule shown in Figure 2-1 represents the program status prior to the implementation of the two-chip approach described in section 1.3 and contains the entire program history. The schedule shown in Figure 2-1A details the planning for the implementation of the corrective action. A three-month slip in delivery of the full system will result with integration test taking place in June 1980.

The major milestones achieved during this quarter are:

- Achieved device yield, from the initial wafer fab, for test and evaluation.

- Verfied the device packaging through assembly.

- Began device test and evaluation.

- Completed fabrication of the IADD and Frame Store Memory.

- Began Frame Store Memory and IADD debug.

#### 2.2 TECHNICAL

# 2.2.1 Analog Field Storage Device

Twelve wafers of the first run came out of fab, six wafers were assembled for test. A wafer consists of 23 30712 devices, 10 test storage chips and 10 test logic and driver chips. The test storage chip is a reduced scale 30712 containing only 209 x 254 storage sites and no on-chip logic

A Division of Fairchild Camera and Instrument Corporation

and drivers. The test logic and driver chip is identical to the on-chip logic and drivers of the 30712.

Initial testing of the test storage chip is encouraging. The storage function, including input/output registers, amplifiers and storage sites, appear to be functioning as expected. Testing is continuing to quantify the results.

Testing of the 3071Z device was inconclusive. The on-chip logic and driver circuits did not provide the necessary output required to operate the storage registers. The logic and driver test chip exhibited the same malfunction. The driver circuits in the test chip were successfully exercised by external logic circuitry. The malfunction was isolated to the logic circuits and subsequently to an error in the mask set.

The corrective action outlined in Section 1.3 has been initiated to correct this error. This action will result in a two chip configuration which offers a more effective distribution of power and complexity while preserving the integrity of the present mask set. The removal of the on-chip logic and drivers from the storage chip reduces the power consumption of the packaged storage device to where the T.E. cooler need only to cool the mass of the package. (See Figure 3-12 for a photograph of the fully assembled storage device). The individual chips of the two-chip set, being less complex than the single chip combining their functions, will be more manufacturable.

Those items in this report that are effected by this corrective action (i.e., block diagrams, narrative, etc.) will be updated in the next quarterly report.

A Division of Fairchild Camera and Instrument Corporation

### 2.2.2 IADD

Fabrication of the IADD has been completed and the test is in progress. The IADD is unaffected by two-chip configuration.

# 2.2.3 Analog Frame Store Memory

Minor modifications to the Frame Store Memory will be required to accept the the two-chip configuration. These modifications will be configured after evaluation of the devices. However, testing of the Frame Store Memory will continue with simulated inputs. Debug of the microprocessor program and hardware is in progress.

# 2.3 ACTIVITIES FOR NEXT QUARTER

- Complete MASK set modifications

- Begin fabrication of modified devices.

- · Complete test and debug of IADD and Frame Store Memory.

|                                                                                       | FIG. 2-1                              |             | , [ | 国              | INC.     | 7          | SCH                                                                         | 11.10[]       | 1.1.      |               |         |        |         |             | ļ                                                |                     |           |                |          |            |                 |               |              |               |

|---------------------------------------------------------------------------------------|---------------------------------------|-------------|-----|----------------|----------|------------|-----------------------------------------------------------------------------|---------------|-----------|---------------|---------|--------|---------|-------------|--------------------------------------------------|---------------------|-----------|----------------|----------|------------|-----------------|---------------|--------------|---------------|

| oj. Engr. Date (1) Cus                                                                | Customer                              |             |     | Pro            | Project  |            | ıtle                                                                        |               |           |               |         |        |         |             |                                                  |                     | ပိ        | Contract       | act      | cc         | Ž.              | •             |              |               |

| Roberts 4/5/79                                                                        | NVL                                   |             |     |                | 7        | MAIO       | ANALOG FRAME                                                                | AME           | STORE     | <b>3</b>      |         |        |         |             | M                                                | DAAK70-78-C-0165    | -78       | 0              | 165      |            |                 | 6248          |              | 1             |

| YEAR                                                                                  |                                       | 1978        |     | ļ              |          | 19         | 1979                                                                        |               |           |               |         |        |         |             |                                                  | 1                   | 1980      |                |          |            |                 |               |              |               |

| TASK                                                                                  | 1 2                                   | 3 4         | 2   | 9              | 7        | <b>℃</b> . | Ü.                                                                          | Ξ             | 7         | 13 14         |         | .5     | 1       | 37          | 3.                                               | <u> </u>            | 21 2.2    | 2.3            | ~;       | 151        | 72              | 7:            | 7)           | ~             |

| MONTH                                                                                 | TH S O                                | O<br>Z      | 5   | Ŀ              | Σ        | Z Z        | 7                                                                           | 5             | Z.        | S             | Z       | ۵      | ù       | Ŀ           | Σ                                                | A                   | N         | J              | A        |            |                 | $\dashv$      | -            | _             |

| )lAA, DEVICE; DESIGN                                                                  | 772.277                               | 777.77      | 13  | 77             | <u> </u> |            |                                                                             |               | :         |               |         |        |         |             | -:                                               | • • •<br>• • •<br>• | · •       |                | •        |            | • • •           |               |              | <del></del> . |

| MPSK MAKING                                                                           |                                       |             |     |                | 11       | 7          | 1.12                                                                        |               |           |               |         |        |         |             |                                                  |                     |           |                | !        |            | -               | !             |              |               |

| PACKAGING                                                                             |                                       | !           |     |                |          |            |                                                                             |               |           |               |         |        |         |             |                                                  |                     |           | ·              |          |            |                 |               |              | <del></del> ; |

| WAFER FAB                                                                             |                                       |             |     |                |          |            |                                                                             | MIL           | 11.       | .27.7M        |         |        |         |             |                                                  |                     |           |                |          |            |                 |               |              |               |

| ASSY                                                                                  | :                                     | ,<br>       | i   | <u></u> -      |          | <u></u>    | 1                                                                           |               | <br> <br> |               | TITE.   | TANEE. |         | !           | !                                                |                     |           |                | !        |            | • <del></del>   |               |              |               |

| TEST                                                                                  |                                       | 1           |     | <del>:</del> - | :        | <u>;</u>   | <u>}</u>                                                                    |               | П         | <u> </u>      | TT      | TO THE |         | 77          | <del></del>                                      | !<br>               |           |                |          |            |                 |               |              |               |

| IAB, FRAME DELAY B.B.;                                                                |                                       | -           |     |                | I        | -          | -                                                                           |               | -         |               |         | _      |         | <u> </u>    |                                                  |                     |           |                |          |            |                 | <del></del>   | <del>-</del> | <u>!</u>      |

| DESIGN                                                                                |                                       | !<br>!      |     |                | i<br>    |            |                                                                             | 13            | }<br>!    |               |         | !<br>! |         |             | !                                                |                     |           | _              |          |            |                 |               |              | :             |

| FABRICATION                                                                           | !                                     | <u>  · </u> |     | <del> </del>   | 1        | -          | 1                                                                           |               | IJ        | 7             | -       | !      |         | !           |                                                  | <u>:</u>            | <u>'</u>  | -              | :        |            | <del></del> -   | -             | <del>!</del> | 1             |

| TEST                                                                                  |                                       | !           |     | :              |          | !          | <u> </u>                                                                    |               |           | -3            |         | : :    | <u></u> | 1           | <del></del>                                      | -                   | <u>.</u>  |                | <u> </u> |            | •<br>i          | !<br>         | -            | <del>!</del>  |

| UELIVERY (2)                                                                          |                                       |             |     |                | -        | -          |                                                                             |               |           |               |         |        | >       |             |                                                  | ند                  |           |                | !        |            |                 |               | <u>.</u>     | ;             |

| LAC, ANALOG FRAME STORE MENDRY;                                                       | RY;                                   |             |     | _              |          |            |                                                                             |               |           |               |         |        |         |             |                                                  |                     | <u></u> i |                |          |            |                 |               |              | !             |

| DESIGN (FIECT, MECH.)                                                                 | БСН.)                                 |             |     |                | 7        | 7          | 7/                                                                          | LI            |           |               |         |        |         |             | _                                                |                     |           |                |          |            |                 |               |              | :             |

| DEVICE INTERFACE                                                                      | <u>ы</u>                              |             |     | -              |          |            | LI                                                                          |               | 1         |               | F-1     | -      |         |             | -                                                |                     |           |                |          |            | <del></del>     |               | į            |               |

| FABRICATION                                                                           |                                       |             |     |                |          |            |                                                                             |               |           | [3]           | <i></i> |        |         |             |                                                  |                     |           | ·              |          |            |                 | !             |              |               |

| TEST                                                                                  |                                       |             |     |                |          | -          |                                                                             |               |           |               |         |        | Ŀ       |             |                                                  |                     |           |                |          |            |                 |               |              |               |

| INTEGRATION TEST                                                                      | FI                                    |             |     |                |          | ·          | ;                                                                           |               |           |               |         |        |         | _           | П                                                |                     |           |                |          |            | ;               |               | :            | :             |

| 1AD, IADD; MEMORY SPEC. & PR                                                          | PROC.                                 |             | 777 |                |          |            |                                                                             |               |           |               |         |        |         |             | -                                                | - <del></del> !     |           |                |          |            | <del></del> - ; | <del></del> ; |              | !             |

| DESIGN (ELECT. /MECH)                                                                 | VECTI)                                | !           |     | <b>. 121</b> . | aura     | 77.C.      | 1777                                                                        | ַּ            |           | ·             |         |        |         | i           | i                                                | ;                   |           |                |          |            |                 |               |              |               |

| FABRICATION                                                                           |                                       | <u> </u>    |     |                |          |            |                                                                             |               |           |               |         |        |         | _           |                                                  |                     |           |                |          |            |                 |               |              |               |

| TEST                                                                                  |                                       |             |     |                |          |            |                                                                             |               | -         |               | - Z     |        |         | 1-7         | <del>                                     </del> |                     |           |                |          |            |                 |               |              | !             |

| INTEGRATION TEST                                                                      | -                                     |             |     |                |          |            | ·                                                                           |               |           | <del></del> ; |         | !      |         | 11.         | $T \cap A$                                       | <del> </del><br>    |           | <del>i</del> - |          |            | - :             |               |              | !.            |

| DELIVERY (3)                                                                          |                                       | -           |     | -              |          |            | _                                                                           |               |           |               |         |        |         | -           | · -                                              | -                   |           | ! <sub>1</sub> | ;        |            | - •             | ;             | ·<br>        |               |

| JAE, REPRODUCIBILITY & RETROFIT                                                       | TT                                    | -           |     | -              | -        | -          |                                                                             |               | -         |               | _       | _      |         |             | $\exists 1$                                      |                     |           | _              |          | -          |                 |               |              |               |

| i ES (1) Schedule revised as of (2) Delivery of 0001AA and (3) Delivery of 0001AC and | s of /37H<br>and 0001AB<br>and 0001AD | Monthly     |     | Report         | FT.      | PAGE       | Ort<br>THIS PAGE IS BEST QUALITY PRACTICABLE<br>PROGREGORY PREMISHED TO DDG | est q<br>Febr | UALI      | TY PI         | ACE     | ad /   | 3 1     | <b>以田</b> > | Col                                              | Complete            | .; c-     | 7.             | 3111     | c.−s<br>]_ |                 | Det.          | );<br>       | .~            |

|                                                                                       |                                       |             |     | 1              |          |            |                                                                             |               |           |               |         |        |         |             |                                                  |                     |           |                |          |            |                 |               |              |               |

Sec. Line

REVISED

PROTECT SCHEDIII E

| FIG.                             | 4           | PROJECT SCHEDULE              |                                            |            |

|----------------------------------|-------------|-------------------------------|--------------------------------------------|------------|

| Engr. Date                       |             | Project Title                 | Type of Contract Job No.                   | -          |

| A. Roberts 1/15/80 NVL           |             | Analog Frame Store            | )-78-C-016                                 |            |

| Month                            |             |                               |                                            |            |

| TASK Week                        | 1 2 3 4 5 6 | 7 8 9 10 11 12 13 14 15 16 17 | 18 19 20 21 22 23 24 25 25 27 28 30 91     | 3€         |

| Week<br>Ending                   | J F M A M J | JASOND                        |                                            |            |

| Device; Mask Modifications       |             |                               |                                            | <u></u> .  |

|                                  |             |                               |                                            | <br>!      |

| Frame Delay BB; Mods             |             |                               |                                            |            |

| Test.                            |             |                               |                                            |            |

| delivery                         | ₽           |                               |                                            |            |

| IADD/FSM debug                   |             |                               |                                            |            |

| FSM; Mods.                       | 0           |                               |                                            |            |

| device instal.                   | IJ          |                               |                                            |            |

| Integration Test                 |             |                               |                                            | ,          |

| Device Optimization              | 11          |                               |                                            |            |

|                                  |             |                               |                                            |            |

|                                  |             |                               |                                            | <u> </u>   |

|                                  |             |                               |                                            |            |

|                                  |             |                               |                                            |            |

|                                  |             |                               |                                            |            |

|                                  |             |                               |                                            | <b>-</b>   |

|                                  |             |                               |                                            | <br>i      |

| 6                                |             |                               |                                            |            |

| FROM COLLE BEST QUALITY PRACTICA |             |                               |                                            | ;          |

| 000 OL                           |             |                               |                                            |            |

| PU 1.11 MI                       |             |                               | K Complete-Planned-Sup-Deirery E F/7/7/7/7 | · <u> </u> |

A Division of Fairchild Camera and Instrument Corporation

#### SECTION III

- 3.0 DESIGN

- 3.1 ANALOG FIELD STORAGE DEVICE

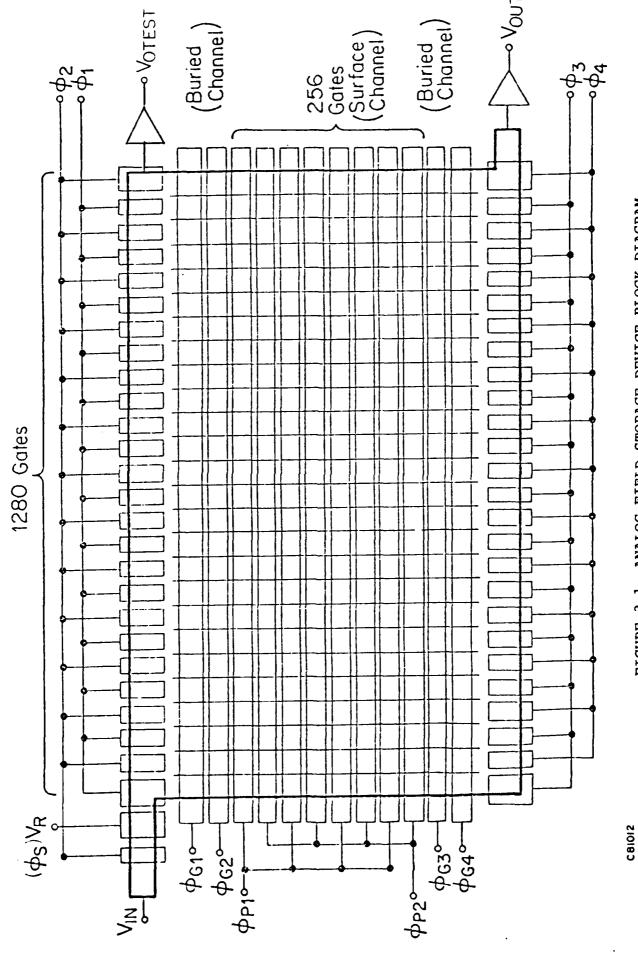

The design objectives for the field storage device are listed in Table 3-1. The device block diagram is shown in Figure 3-1.

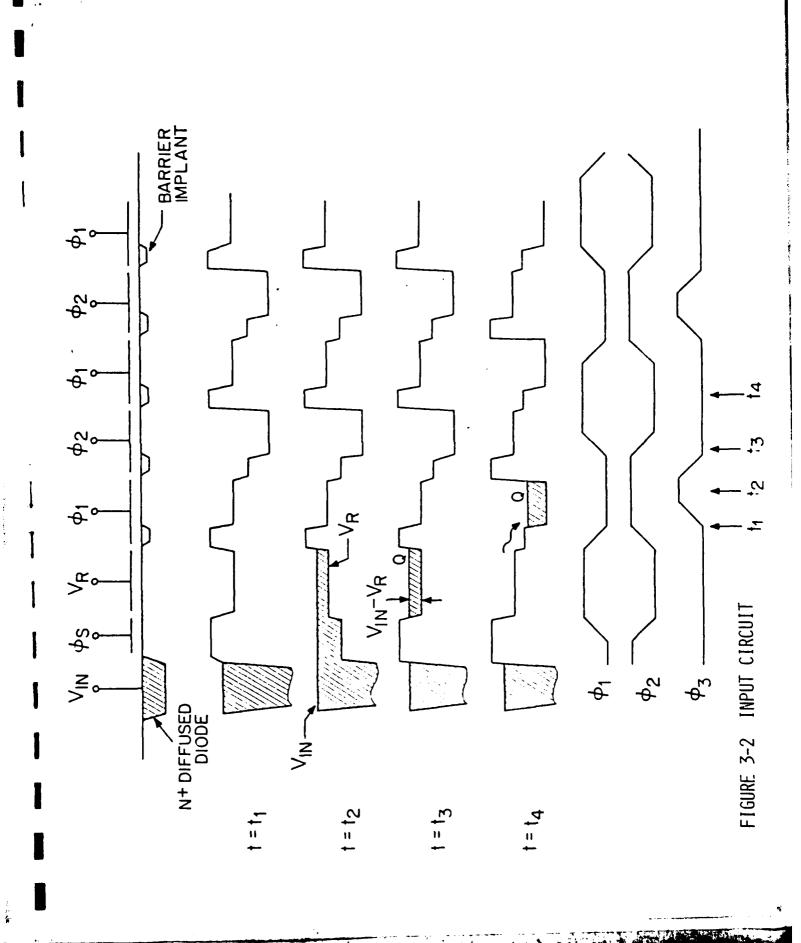

# 3.1.1 <u>Input Circuit</u>

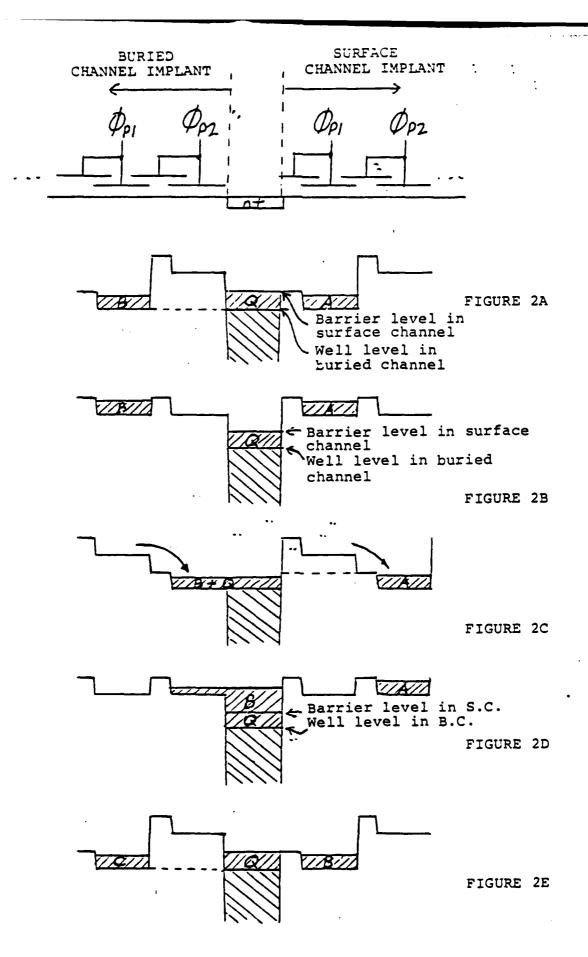

The input circuit consists of a diffused diode  $V_{IN}$  and two polysilicon gates  $\emptyset_3$  and  $V_R$ . The input structure and clocking is shown in Figure 3-2. The input voltage is applied to  $V_{IN}$ .  $\emptyset_S$  is clocked high to sample  $V_{IN}$  during the  $\emptyset_1$  low time. After  $\emptyset_S$  has returned to the low state, a charge packet Q is stored in the input circuit and can be transferred along the input register by clocks  $\emptyset_1$  and  $\emptyset_2$ . These input horizontal clocks are generated by off-chip clock drivers. It can be seen that the magnitude of Q is determined by the difference of the potentials between  $V_{IN}$  and  $V_R$ . By applying an appropriate dc voltage to  $V_R$ , the magnitude of the charge packet Q is proportional to the input voltage  $V_{IN}$ .

The input register is designed using buried channel technology to insure good charge transfer efficiency at the high speed clocking rates.

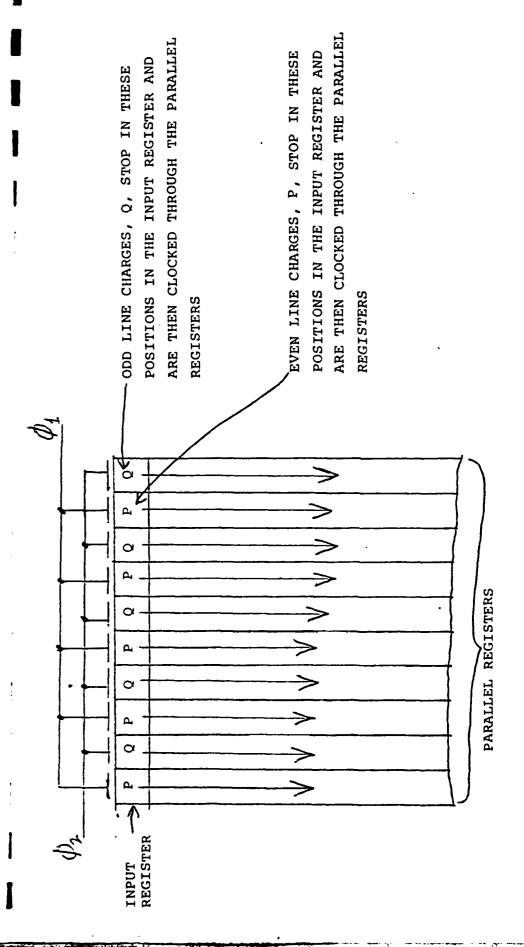

# 3.1.2 Parallel Register

The parallel registers are surface channel devices. Surface channel technology allows more charge to be stored per unit area. Since the major portion of the chip is taken up by these registers, this greatly influences the chip size. The parallel registers are low frequency registers so the speed advantage of buried channel

FIGURE 3-1 ANALOG FIELD STORAGE DEVICE BLOCK DIAGRAM

# FIELD STORE DEVICE DESIGN OBJECTIVES

STORAGE CAPACITY

MAX. HORIZONTAL DATA RATE 12 MHz

MAX. VERTICAL DATA RATE

INPUT SIGNAL SWING

OUTPUT SIGNAL SWING

NONLINEARITY

CTE

SATURATION CHARGE

SIGNAL-TO-NOISE RATIO

MAX. DC SUPPLY

AC CLOCK INPUT

POWER DISSIPATION

CHIP AREA

640 X 256

16 KHz

1 V TYP.

1 V TYP.

<sup>+</sup> 3% TYP., <sup>+</sup> 5% MAX.

0.99995 MIN.

$0.9 \times 10^6$  ELECTRONS TYP.

50 dB MIN.

+ 15 V

4 TTL CLOCKS + 2 MOS CLOCKS

300 mW MAX.

199 mil X 740 mil

A Division of Fairchild Camera and Instrument Corporation

technology is unnecessary. A discussion of buried to surface channel transfer is contained in Appendix 2.

The parallel registers are clocked by two phase clocks. The input register and output register clocks are also two phase. Therefore, when a line is clocked in, the signal charge resides under every other gate. As this line is clocked through the parallel registers, only half the available space is used. Each signal charge is clocked down a vertical register adjacent to the gate it was stopped at in the input register. Since only every other gate had charge under it in the input register, only every other vertical register is used by each line. So as not to waste half the vertical register area, alternate lines are clocked in and stopped under different sets of gates in the input register. Odd lines are stopped under the  $\mathcal{L}_2$  gates and even lines under the  $\mathcal{L}_2$  gates. With this interlacing scheme all parallel register area is used, (see figure 3-3).

There are two special gates at each end of the parallel registers. Charge is not stored under these gates. They are included to isolate the storage area from the high speed input and output registers. Capacitive coupling between the parallel and I/O registers during input and output clocking is minimized by the insertion of these gates Gl, G2, G3, and G4, (see Figure 3-1).

All clocks to run the parallel registers and G1, G2, G3, and G4 are generated on chip from 2 TTL clocks supplied to the chip.

# 3.1.3 Output Circuit

A schematic diagram of the output circuit is shown in Figure 3-4. The output register employs the same two phase structure as the input register. The on-chip generated clocks  $\mathcal{G}_3$  and  $\mathcal{G}_4$  (SEE NOTE 1) transfer the charge packets along the output register into a diffused

FIGURE 3-3

INTERLEAVED CLOCKING

FIGURE 3-4 OUTPUT CIRCUIT

A Division of Fairchild Camera and Instrument Corporation

diode. The potential of this diode is monitored by a three stage source-follower output amplifier. A gating transistor is positioned between the two stages so that a sample-and-hold output waveform can be obtained. The sample and hold clock  $\emptyset_{\text{SH}}$  is also generated on-chip.

Note 1: For clocking speeds in excess of 400KHz, off-chip clock drivers must be provided.

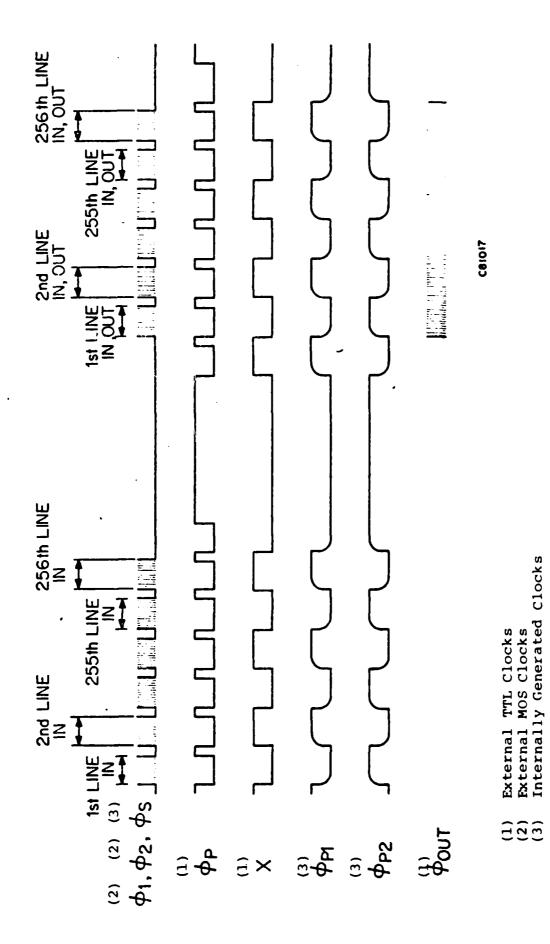

### 3.1.4 Timing Requirement

As illustrated by the block diagram of Figure 3-1, a maximum of three external TTL level clocks and two MOS clocks are required to operate the device, at output rates less than 400KHz. A detailed timing diagram is shown in Figure 3-5.  $\emptyset_I$  is a continuous MOS level input clock which controls the input circuit and the input serial registers.  $\emptyset_{OUT}$  is a continuous TTL level clock which controls the output register and the output amplifier.  $\emptyset_P$  is a TTL level input clock which controls the parallel registers.  $\emptyset_P$  is typically operated at the 15.7KHz line rate with 10  $\mu$ s high time. During this 10  $\mu$ s horizontal blanking time, the serial register clocks are stopped and the parallel clock generators are activated. In this manner, the internal logic circuits to generate the parallel clocks are disabled during the 53.5  $\mu$ s active line time when read-in and read-out occur. No coupling of the parallel clocks will be visible in the output waveform.

### 3.2 ANALOG FRAME STORE MEMORY

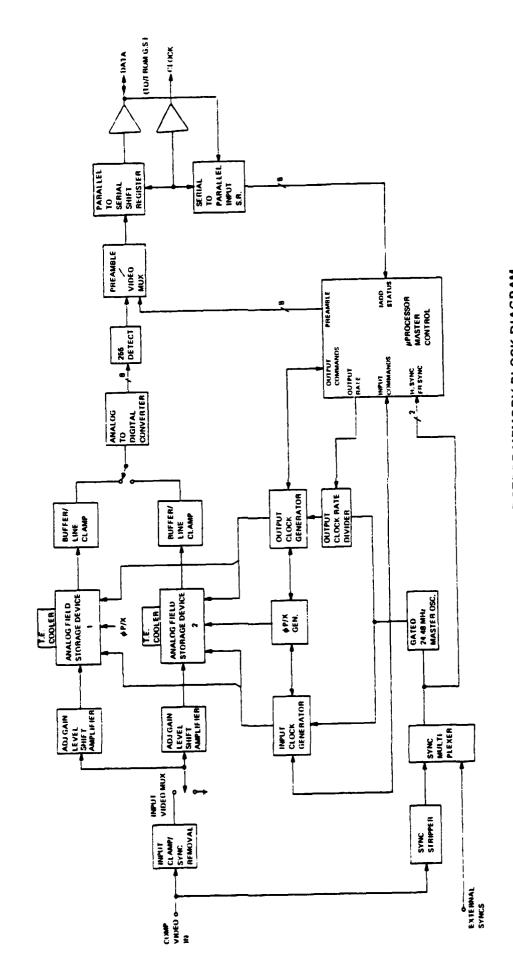

The block diagram of the Analog Frame Store Memory is shown in Figure 3-6.

FIG. 3-5 TIMING DIAGRAM

FIGURE 3-6. ANALOG FRAME STORE MEMORY BLOCK DIAGRAM

A Division of Fairchild Camera and Instrument Corporation

### 3.2.1 Input Circuits

The 30 FPS composite video is clamped during the "back porch" period of each line and the sync is removed from the signal. The resulting video passes through the input video multiplexer to the two independent adjustable gain amplifiers. The input is grounded for the first right pixels to provide a black clamp level for the outputs. Although the video is present at the input of each device, gating of the input clocks determines when video is to be stored in the devices.

Each video channel is independently adjustable to the desired gain and offset for the particular storage device through a wide band video amplifier. This data is inputted to the device via  $\emptyset_{\tilde{1}}$  as described in paragraph 3.1.1. During Mode 2, alternate line video is inputted 180° out of phase. In this fashion, two TV lines contain interleaved sampling data which is at twice the Nyquist limit. For example a black-white pattern at twice Nyquist results in all white levels being stored for lines 1, 3, 5 etc., and all black levels for lines 2,4, 6 etc. This data is scan converted, digitized and sent to the IADD as in Mode 1.

The sync stripper circuit derives Horizontal and Frame Sync from standard EIA composite video. If the video input is in the form of non-interlaced serial data, Horizontal and Frame Syncs must be supplied.

# 3.2.2 Timing/Control Circuits

An 8085A microprocessor provides overall control for the system. The instructions for the microprocessor are stored in a UV Eraseable PROM of 2K x 8 bits. 256 x 8 bits of RAM are available for use by the microprocessor for temporary storage. The microprocessor controls the input and output functions of the field storage memories on a line oriented basis.

A Division of Fairchild Camera and Instrument Corporation

Real-time control is attained by the use of three hard-wired interrupts-line sync, frame sync, and output sync. The first two interrupts permit the microprocessor to maintain an input line count of the incoming composite video, while the latter interrupt indicates the completion of one line of output. Status information from the I.A.D.D. is converted to an 8 bit word in the serial to parallel input shift register, and then input to the microprocessor via an 8 bit input port. Control I.D. words are generated by the microprocessor and inserted into the data path via the preamble/video multiplexer.

The maximum clock frequency required to output the slow scan digital data is 24.48 MHz at 7.5 FPS. The clock frequency required to input data to the storage device at 30 FPS is 12.24 MHz. In order to maintain a synchronous system, a master 24.48 MHz oscillator will be used with all clocks derived from this source. The input clock must be gated to provide precise synchronization with the incoming Since the input clock is derived from the master oscillator, the master oscillator must be capable of being gated at the start of each line during the input operation. Start-up of the oscillator will be delayed for an additional half cycle for alternate lines in Mode 2 operation. All clocking rates will be binary multiples of the master clock frequency. Therefore, the actual frame rates are .117, .469, .938, 1.88, 3.75 and 7.5 FPS.

The output clock divider, under microprocessor control, provides the output clock generator with the proper frequency clocks corresponding to the frame rate selected. The output clock generator, upon receipt of a command from the microprocessor, generates the clock pulses necessary for outputting one line of video from either of the two field storage devices. Upon completion of one line, an output complete interrupt is sent to the microprocessor. Each line outputted requires a separate output command.

A Division of Fairchild Camera and Instrument Corporation

The input clock generator, upon reciept of a command from the microprocessor and at the beginning of a line of video generates the appropriate clock pulses necessary for inputting video into one or both of the field storage devices. Inputting will continue for the multiple lines until a stop input command is received.

# 3.2.3 Output Circuits

The output from each device is independently amplified and filtered to eliminate clock modulation in the output amplifier. Independent black clamp circuits are provided to establish a dc reference for each device. The dc reference is derived from the first 8 pixels of each line which were referenced to black during input. The data is outputted from the storage device via  $\emptyset_0$  as described in paragarph 3.1.3

The output multiplexer recombines the slow scan outputs from the storage devices into a serial output data format by "ping-pong" action between devices. The multiplexing is controlled via the Mux control signal.

The analog video information is converted to an 8 bit binary word by the A/D converter. A sample and hold circuit (internal to the A/D) provides the means to store the analog video level present at strobe time and hold this level for the entire conversion time. Strobe repetition rates from 47.8KHz to 3.06MHz are possible, yielding an equal number of A/D conversions. The A/D converter selected is capable of conversions from d.c. to 11 mega-conversions per second. The conversion time is 150 nanoseconds.

A Division of Fairchild Camera and Instrument Corporation

Each pixel time is divided into 8 bits representing 256 intensity levels. The bit time is eight times the pixel clock, yielding a maximum rate of 24.43MHz. At the beginning of each pixel time the next character is loaded in parallel to an 8 bit shift register. The data is then shifted out under control of the bit clock. The bit clock and S/R output are sent to the IADD for reconstruction and display through differential line drivers.

## 3.2.4 Control ID

In any transmission system involving serial digital data, synchronizing information must be inserted to identify the data and to establish the "frame" of the serialized byte (in this case, pixel). This synchronizing data must be unique in that the actual data must not be confused with the synchronizing data. In this system, the Frame Store Memory A/D converter generates data from 0 - 255 with 255 having the binary value of all ones. The A/D output will be tested for this condition and if it occurs, the least significant bit will be inverted changing the value to 254. Thus, the all ones condition cannot occur in normal data. This code will be reserved for synchronizing purposes. Each line of transmitted video will be preceded by three characters. The first two characters will be all ones. The third character will be uniquely defined by its relationship to the all ones data. This byte will always begin with a zero bit to establish the byte or pixel frame. Each line of video will contain a start of line character unless it is the first line of a frame.

Each line of video will contain:

2 characters of all ones

1 control character

640 image pixels

A Division of Fairchild Camera and Instrument Corporation

These characters will be inserted to read from the Frame Store Memory at the appropriate time under control of the central timing logic.

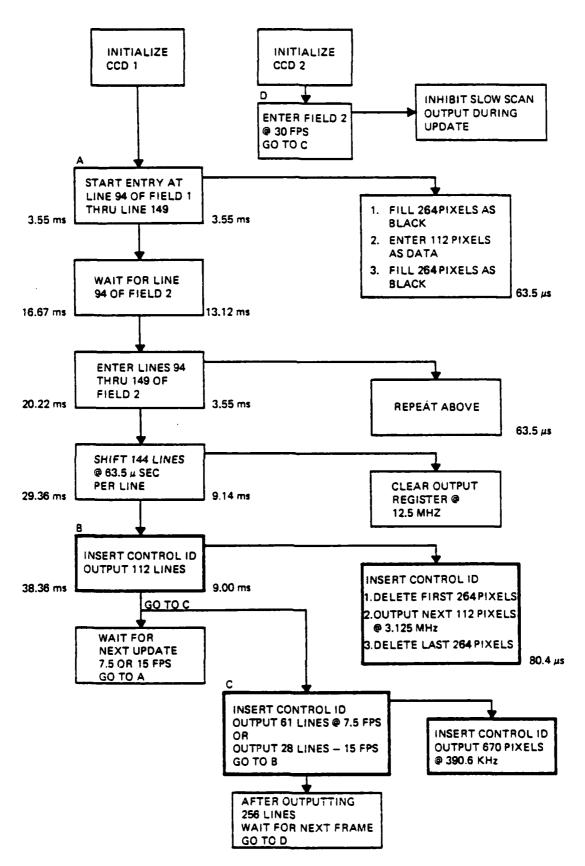

# 3.2.5 Mode 3 Operation

The implementation if the dual data rate mode is in accordance with the algorithms described in Figure 3-7 or Figure 3-8 depending upon the interlaced nature of the input video. The first set of data, stored in device 2, consists of 256 lines x 640 pixels representing a field of TV data and shall be referred to as the slow speed data. The second set of data, stored in device 1, is the center 112 pixels of the center 112 lines of the input video. This data shall be referred to as high speed data. Using an actual count of 112 rather than 100 maintains compatibility with the counting sequence of the IADD.

The slow speed data is outputted at .938 FPS and is time interleaved with the high speed data. After each high speed output, slow speed data is transmitted. The slow speed data requires several cycles to complete a full field. At 7.5 FPS the time allocated for slow speed transmission is:

$$T = (4 \times T_{st}) - T_{hs}$$

(EQ 1)

Where  $T_{st}$  is the standard frame time 33.33 msec., and  $T_{hs}$  is the time required to output 112 lines at 7.5 FPS.

Substituting the above in EQ 1 we have

$$T = (4 \times 33.33) - 9.0 = 124.32 \text{ msec.}$$

A 15 TO SHAPE THE HER WINDOWS AND A PROPERTY OF THE PROPERTY O

FIGURE 3-7. ALGORITHM; DUAL DATA RATE, INTERLACED

FIGURE 3-8. ALGORITHM; DUAL DATA RATE, NON-INTERLACED

A Division of Fairchild Camera and Instrument Corporation

The number of lines transmitted per cycle is

#Lines/Cycle =

$$\frac{\text{T Cycle}}{\text{T Line}}$$

(EQ 2)

Where  $T_{\mbox{line}}$  is the time required to output one line at .938 FPS. Substituting the above in EQ 2 we have

# Lines/Cycles =

$$\frac{124.32}{2.022}$$

= 61.47

Using 61 lines, the number of cycles for 256 lines is:

# Cycles =

$$\frac{256}{61}$$

= 4.19 Cycles

or the time to output a complete field of slow speed data is:

$$T_s = (\#Lines \times \#Cycles \times T_{line}) + (T_{line} \times Overflow)$$

+ Update time (EQ 3)

Substituting in EQ 3:

$$T_s = (61 \times 4 \times 2.022) + (2.022 \times 12) + 45$$

$T_s = 562.63 \text{ msec}$

The interleaved output is shown in Figure 3-9. With the high speed data rate at 15 FPS, the total time to complete a field at slow speed is:

$$T_s = (28 \times 9 \times 2.022) + (4 \times 2.022) + 90 = 607.5 \text{ msec.}$$

The data received by the IADD is reconstructed into a split screen display with the center 112 lines x 112 pixels being updated at 7.5 or 15 FPS, and the remainder of the display at

FIGURE 3-9. DUAL DATA RATE OUTPUT

. .

A Division of Fairchild Camera and Instrument Corporation

.938 FPS. The horizontal resolution of both sections will be the same while the vertical resolution of the center portion will be greater than that of the outer portion.

## 3.3 IMAGE ANALYZER DIGITAL DISPLAY (IADD)

The function of the IADD is to reconstruct the digital video information received from the Frame Store Memory for display on a standard TV monitor.

The digital video information is received via a simulated transmission data link from the Frame Store Memory at data rates from 0.1 to 7.5 frames per second. All IADD operations (mode, update rate, and interlace format) are controlled by front panel switches. This status information is provided to the Frame Store Memory over the same data link, when the Frame Store is being reloaded.

The IADD memory is required to store 488 lines, 640 pixels per line, with 8 intensity bits per pixel. A memory configuration of 512 x 1024 x 8 will store one frame of data. To provide an uninterrupted display while the memory is being updated requires two full frame memories of storage. While one frame is updated with the latest low speed video information, the other frame is providing the display with 30 frames per second video. Following completion of the low speed update and at the beginning of the next display frame, the memories' roles are reversed providing continuous display. Two additional partial frame memories are provided for use during mode 3 operation when the center 112 pixels of the center 112 lines are updated at a higher rate than the remaining background data. The two partial frame memories, each consisting of 128 x 128 x 8 bits of storage, provide the same "ping-pong" updating operation as the full frame memories for uninterrupted display of the center area in mode 3 operation.

A Division of Fairchild Camera and Instrument Corporation

Refer to Figure 3-10 for the overall block diagram of the IADD. The input data is clocked into the Input Shift Register by the input clock to provide a single 8 bit pixel. The Control Decode detects the control identification codes being transferred (such as start frame, start line, etc.) and also provides synchronization information with respect to the 8 bit pixels. The Pixel Group assembly shift register assembles eight, 8 bit pixels into a single 64 bit word for writing into one of the four frame memories. memory addressing circuitry sequentially counts through the 80 pixel groups (of 8 pixels each) per line and 488 lines per frame, converting each screen position to a memory address for write-in into one of the four frame memories. The Master Control logic, evaluating the mode/data rate status switches and the control identification decode, selects one of the frame memories. readout utilizes equivalent pixel group and line counters to address one of the four frame memories selected for the display mode. The Sync Generator/Output Video Control circuitry generates the timing signals necessary to sequentially read the memory in synchronization with composite sync applied to the video processor. memory outputs, 64 bits wide each, are tri-state outputs enabling one of the four memories to be presented to the Video Bit Assembly Shift Register as eight pixels. The video shift register sequentially clocks one pixel at a time (8 intensity bits per pixel) to the Digital to Analog Converter for conversion to one of 255 levels of video. The Video Processor mixes this video signal with composite sync and composite blanking to provide the composite video necessary for display on a standard TV monitor. The Video Chop Circuit is enabled in mode 2 only to present the D/A converter with two digital codes per pixel time consisting of the pixel's actual bit weight and then all zeroes; this provides resolution enhancement when coupled with the video acquisition performed by the Frame Store Memory in mode 2.

FIGURE 3-10. IADD BLOCK DIAGRAM

A Division of Fairchild Camera and Instrument Corporation

# 3.3.1 Input Section

The primary function of the input circuitry is to convert the serial data stream into a 64 bit parallel word for memory write-in. As discussed previously, the speed of the input data ranges from 0.1 to 7.5 frames per second. This corresponds to pixel rate from 47.8KHz to 3.06MHz. However, since there are 8 intensity bits per pixel, the actual data rates range from 382.5KHz to 24.48MHz. Therefore, Shottky TTL devices have been selected for the input shift register and control decode areas to handle the 25MHz data rates.

As an 8 bit pixel appears at the output of the input shift register, each bit is transferred to the input of one of the eight shift registers composing the Pixel Group Assembly Shift Register. This transfer occurs once for every eight input clock cycles enabling the use of low power Shottky technology in this and succeeding stages. Following the filling of all 64 bits of the Pixel Assembly shift register, the Memory Buffer is strobed. Clocked once per 64 input clocks, the clock rate ranges from 6.1KHz to 382.5KHz. This implies a memory cycle time of less than 2.56 microseconds - well within the 500 nanosecond cycle time of the memories selected.

The control decode sequence involves two steps. First a preamble of sixteen "ones" followed by two "zeroes" must be detected. The first zero following the sixteen ones if the first bit of the eight bit control identification word. As all input data is received in eight bit multiples, this detection provides synchronization for all succeeding pixels until another control code is detected. The control identification will be Start Frame, Start Line, Start Hi Frequency, Start Lo Frequency, or Status Request. The absence of a valid code detection will enable a front panel

A Division of Fairchild Camera and Instrument Corporation

fault light to indicate transmission unlock. The combination of this code and the front panel switch information provides all the data required for the Master Control Logic to enter the eight pixels in the correct address of the correct memory.

Decoding the "Status Request" code indicates to the IADD that the Frame Store Memory is about to go "OFF LINE" on the data line while still providing a clock signal. The Master Control will then enable its own tri-state data driver and shift out the mode/data rate status of the front panel switches to the Frame Store Memory. The clock frequency during this transfer will be 1.56MHz (slow enough to prevent errors due to clock/data skew arising from unequal delays). This sequence will occur only during normally "dead" time for the link, i.e., when the Frame Store Memory is reloading. Figure 3-11 illustrates the control identification codes to be used.

# 3.3.2 <u>Memory Subsystem</u>

The Memory System consists of two full frame dynamic random access memories and two partial frame static random access memories. Each of the four memories is completely independent with separate read/write controls and addressing logic. Two full frames of storage are required to provide an uninterrupted display while asynchronously receiving a new frame of data. In addition, during mode 3 operation only, the center, 112 pixels of the center 112 lines are stored in the two partial frame memories with one frame serving as the display memory while the other partial frame serves as the update memory.

The 30 frame per second display refreshing imposes a 12.6MHz video update rate upon the memories. This would correspond to a memory read cycle time of 80 nanoseconds. By reading 8 pixels of video simultaneously, the cycle time can be increased to 640 nanoseconds - a realistic time for commercially available memory systems. 8 pixels

STATUS REQUEST

O

0

0

0

0

OUTPUTS

START HI FREQ.

0

0

0

0

0

START FRAME

0

START LINE

START LO FREQ.

|         | MODE       | Σ        | ΣO | DATA RATE       | RATE     | $D_2$ | D | 0          |

|---------|------------|----------|----|-----------------|----------|-------|---|------------|

|         |            |          |    |                 |          |       |   |            |

|         | <b>-</b>   | 0        | 7  | .117            | FPS      | 0     | 0 | 0          |

|         | 7          | <b>~</b> | 0  | .469            | FPS      | 0     | 0 | Н          |

|         | ٣          | -        | ~  | .938            |          | 0     | - | 0          |

|         |            |          |    | 1.88            |          | 0     | - | -1         |

| INI     | INTERLACE  | GT.      | Н  | 3.75            |          | ~     | 0 | 0          |

| NON-INI | INTERLACED | 30       | 0  | 7.5             | FPS      | ~     | 0 | <b>~</b> i |

| INI     | Interlaced | 30       | -  |                 |          |       |   |            |

|         |            |          |    | HI-SPD DTA RATE | DTA RATE | 63    |   | H          |

|         |            |          |    | ر<br>ب          | 500      |       |   | _          |

|         |            |          |    | _               | FPS      |       |   | <b>э</b> н |

A Division of Fairchild Camera and Instrument Corporation

of video, with 8 intensity bits per pixel requires 64 bits of data to be read simultaneously from the memory-defining the memory architecture as 64 bits wide. Each TV line containing 640 pixels is organized as 80 pixel-groups of 8 pixels each). The 8 pixels are loaded into shift registers following each memory read cycle and shifted out at the proper 12.6MHz rate while the memory is operating at 1.56MHz. 488 lines of 30 pixel groups each requires the storage of 39,040 64 bit words per frame. A commercially available memory system of 65,536 words by 64 bits has been selected to fulfill these requirements for each frame of dynamic memory.

Four printed circuit boards of 65K by 16 each will provide the desired one frame storage. Each board is composed of sixty-four 16,384 bit dynamic RAM devices. Four additional boards of buffering and control are required to complete one frame of storage. Two full frames of 8 boards each are required.

The partial frame memories require considerably less storage.

112 lines of 14 pixel groups each yields 1,568 64 bit words.

Thirty-two static RAM devices (1,024 x 4) will be configured to provide a partial frame memory of 2,048 by 64. Two partial frame memories, as described above, are required.

The two dynamic full frame memories impose an additional constraint on operation, a need for period refreshing of the stored data to prevent data loss. 128 memory cycles performed on certain addresses are required within a 2 millisecond period to prevent data loss. The memory controller P.C. board associated with each frame memory contains circuitry to automatically provide one of these memory cycles every 16 microseconds. This function is not possible during display readout as every memory cycle during the active line period (53 microseconds) is utilized. However, normal display readout cycles will also refresh the memory as long as all of the 128 addresses

A Division of Fairchild Camera and Instrument Corporation

of all of the memory devices are utilized within a two millisecond period. By proper direction of the address lines to the memory, this mode of refresh would be possible. Another factor to be considered is the time period during vertical retrace (approximately 13 milliseconds) and in mode 3 during the center 112 lines when the memory is not being accessed. Switching to the automatic refresh mode during these time periods is not practical because the refresh address counter of the memory controller would not be synchronized with the display readout address. This condition could leave a gap of greater than 2 milliseconds between refreshes during the transition periods to and from automatic refresh.

A solution compatible with all modes of operation which has been selected involves no dependence upon normal read or write cycles to provide refreshing. Instead the TV Sync-Generator circuitry will provide refresh requests during the horizontal retrace time (a 10 microsecond period where no memory cycles are required). This refresh will continue through vertical retrace. The memory controller will provide the refresh address for this mode. Then when the frame memory is switched from display readout to frame update mode, the refresh mode can switch to automatic (using the same refresh address counter) without any refresh gaps. The automatic mode is allowed during frame update because successive memory cycles are not necessary (one write cycle every 2.56 microseconds is the fastest update rate).

The three modes of operation present various requirements to the memories' operation. Mode 1 and 2 are indistinguishable to the memories, the video of mode 2 is "chopped" following memory readout. The input data of modes 1 and 2 consists of 488 lines of pixel groups (640 pixels) per line in either interlaced or non-interlaced format. One write-in counter (composed of a modulo 80 pixel group counter, modulo 244 field line counter, and field flip/flop) is used for both full frame memories; the frame memory being updated has the write-in counters multiplexed onto its

A Division of Fairchild Camera and Instrument Corporation

address lines. Non-interlaced input involves interchanging the field flip/flop with the l.s.b. of the field line counter. One read out counter (with an identical configuration as the write-in counter) is utilized by all four frame memories. In mode 1 or 2, the frame memory not updated is addressed by the readout counter for readout synchronized with the TV Sync Generator.

Mode 3 operation involves the storage of one field of data (background) in one of the full frame memories, and a partial field of data (center 112 pixels of center 112 lines) received in either interlaced or non-interlaced form stored in one of the partial frame memories. The two data types are received at different update rates with the low speed (1 frame per second) background data being interrupted several times during the field transfer by the high speed (7.5 or 15 frames per second) center area data. This fact necessitates an additional set of write-in counters for the high speed data so that the line number at which the low speed data was interrupted can be maintained for use when that data transfer is resumed. At the start of a display frame, the most recently updated full frame and partial frame memories are selected for readout; if either frame's alternate memory completes a new update following this time, the memories are not switched until the start of the next display frame. The single readout counter (interlaced readout only) will initially be addressed to one of the full frame memories at the start of a field and begin readout or pseudoreadout (in the odd field there is no available data and consequentially all "zeroes" are substituted for memory data) until the center 112 area is decoded. At this time the readout address is directed to the partial frame memory selected at the start of the frame and readout then continues with this memory. Display readouts will continue alternating between these two memories as the center area is traversed. Following the center 112 lines, control and addressing will revert back to the full frame memory for the

A Division of Fairchild Camera and Instrument Corporation

remainder of the field. The partial frame memory will not actually see the same address as the full frame memory, but will instead pass through a subtraction circuit (pixel group minus 33, and field line minus 94) which compensates for the different memory sizes of the full frame and partial frame memories.

# 3.3.3 Output Logic

The digital representation of the video at the output of the memory consists of 64 bits representing 8 pixels. At the end of each memory cycle all 64 bits are loaded into eight parallel to serial shift registers. During the time the next memory cycle is in process, each of the 8 pixels is individually presented to the Digital to Analog Converter. In modes 1 and 3, the D/A converter is clocked once for each 8 bit pixel (12.6Mhz) with the resulting analog voltage appearing at its output. Mode 2 provides a slight complication to this scheme. In this mode the D/A converter is clocked twice per each pixel output from the shift register. video chopper sequentially presents the 8 bit pixel and then all "zeroes" (or vice versa) to the D/A converter once per pixel output. The resulting analog video output appears as normal video for onehalf the normal pixel time of 80 nanoseconds and is zero for the other half of the normal pixel time. The phasing of the chopped video is reversed on alternate fields to provide enhanced resolution. The Digital to Analog converter selected must be capable of updating at either 12.5 or 25 MHz, providing a relatively "glitchless" output. A commercally available 30MHz D/A converter with an add-on deglitcher has been selected to perform this function.

# 3.3.4 TV Sync Generator/Master Oscillator

The main component of the TV Sync Generator is a CMOS LSI TV sync generator integrated circuit. Clocked by 504KHz (obtained by a synchronous countdown of the Master 25.2MHz oscillator), this I.C.

A Division of Fairchild Camera and Instrument Corporation

provides all TV line, field, and frame related signals used in the IADD. Combining these signals with 25.2MHz and its derivatives yields the video, chop, and D/A clocks used in the output area.

# 3.3.5 Video Processor

The video processor passes the D/A converter analog output through a low pass filter prior to mixing the video with composite sync and blanking to produce a composite video output suitable for display on a standard TV monitor.

## 3.4 POWER REQUIREMENTS

# 3.4.1 Analog Frame Store Memory

The operating voltages for the analog frame store memory circuitry will be derived from commercially available power supply modules operating off 115V, 60Hz laboratory power.

The A/D converter will be powered by a separate dedicated power module. The power to the TE coolers will be derived from a separate dedicated power module.

### 3.4.2 IADD

The power supplies selected for the IADD will be standard commercially available computer grade supplies operating off the laboratory 115VAC, 60Hz line.

The two full frame dynamic memories require +12V, +5V, and -5V at currents under 13, 33 and 1 Amp, respectively. Additionally, a power-on sequence and failure control will not enable the +12V and +5V supplies without the presence of the -5V (VBB) supply.

A Division of Fairchild Camera and Instrument Corporation

The two static partial frame memories require +5V at approximately 6 Amps. The remaining TTL logic circuitry requires +5V at approximately 8 Amps. The D/A converter requires +15V, -15V, +5V, and -5.2V at currents under 150ma., 250ma., 30ma., and 100ma., respectively.

## 3.5 PACKAGING

# 3.5.1 Analog Field Storage Device