-----

-----

# INTEGRATED THIN-FILM TRANSISTOR DISPLAY

FIRST QUARTERLY PROGRESS REPORT 28 SEPTEMBER TO 31 DECEMBER 1977

CONTRACT DAAB07-77-C-0583, CDRL C002, DI-S-1800

Prepared by W. J. Helm, Project Engineer

for

US ARMY ELECTRONICS COMMAND FORT MONMOUTH, NEW JERSEY

**REPORT 5705-1**

14 APRIL 1978

The findings in this report are not to be construed as an official Department of the Army position unless so designated by other authorized documents. 1

1

[

0

0

[]

1

0

[

[]

Π

Destroy this report when it is no longer needed. Do not return it to the originator.

This project has been accomplished as part of the U.S. Army Manufacturing Methods and Technology Program, which has as its objective the timely establishment of manufacturing processes, techniques, or equipment to insure the efficient production of current or future defense programs.

|                                                                                                                                                                                                                                                                                                                                                                                    | READ INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                          | BEFORE COMPLETING FORM                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                    | CESSION NO. 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14 AFSC-5765-1                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INTEGRATED THIN-FILM TRANSISTOR DISPLAY.                                                                                                                                                                                                                                                                                                                                           | Quarterly Zechnical Report<br>28 Sept. 31 Dec. 277                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                    | 6. PERFORMING ORG. REPORT NUMBE<br>5705-1                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AUTHOR(.)                                                                                                                                                                                                                                                                                                                                                                          | - CONTRACT OR GRANT NUMBER(+)                                                                                                                                                                                                                                                                                                                                                                                                                              |

| W. J./Helm                                                                                                                                                                                                                                                                                                                                                                         | (15) DAABØ7-77-C-0583<br>CDRL C002                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                           | 10. PROGRAM ELEMENT, PROJECT, TA                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Aerojet ElectroSystems Company√<br>1100 W. Hollyvale St.<br>Azusa, CA 91702                                                                                                                                                                                                                                                                                                        | 10. PRÓGRAM ELEMENT, PROJECT, TA<br>AREA & WORK UNIT NUMBERS<br>Project 2779835                                                                                                                                                                                                                                                                                                                                                                            |

| CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                | 12 REPORT DATE                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| U.S. Army Electronics Command                                                                                                                                                                                                                                                                                                                                                      | 11 14 April 78                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Fort Monmouth, New Jersey 07703                                                                                                                                                                                                                                                                                                                                                    | 12 H 42 P                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| . MONITORING AGENCY NAME & ADDRESS(II different from Control                                                                                                                                                                                                                                                                                                                       | ling Office) 15. SECURITY CLASS. (of this report)                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                    | Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                    | 154. DECLASSIFICATION/DOWNGRADIN<br>SCHEDULE                                                                                                                                                                                                                                                                                                                                                                                                               |

| Approved for Public Release; Distribution                                                                                                                                                                                                                                                                                                                                          | Unlimited.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>DISTRIBUTION STATEMENT (of the obstract entered in Block 20, in</li> <li>SUPPLEMENTARY NOTES         The findings in this report are not to be of the Army position unless so designated     </li> <li>KEY WORDS (Continue on reverse side if necessary and identify by the BBD Bucket Brigade Device Addit EL Electroluminescence Vacuu</li> </ul>                       | different from Report)<br>construed as an official Department<br>by other authorized documents.                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>DISTRIBUTION STATEMENT (of the observed entered in Block 20, in</li> <li>SUPPLEMENTARY NOTES         The findings in this report are not to be of the Army position unless so designated         KEY WORDS (Continue on reverse side if necessary and identify by E BBD Bucket Brigade Device Addit EL Electroluminescence Vacuu TFT Thin-Film Transistor     </li> </ul> | different from Report)<br>e construed as an official Department<br>by other authorized documents.                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>DISTRIBUTION STATEMENT (of the obstract entered in Block 20, in</li> <li>SUPPLEMENTARY NOTES         The findings in this report are not to be of the Army position unless so designated     </li> <li>KEY WORDS (Continue on reverse side if necessary and identify by the BBD Bucket Brigade Device Addit EL Electroluminescence Vacuu</li> </ul>                       | <pre>different from Report)  c construed as an official Department by other authorized documents.  dock number) cive Thin-Film Deposition m Deposition Chamber  ock number) during the first quarter (28 Septemb nose purpose is to develop techniques splays with integrated thin-film tra of the overall design and configurati re of the electroluminescent elements dressing circuits of the display devi ricate these devices; the process dev </pre> |

I

I

1

Received a

-----

Common P

0

1

[]

Q

Ð

[]

0

0

Û

| 8715          | -  | tte Saction | > |

|---------------|----|-------------|---|

| 306           | ŧu | I Section   | 0 |

| UNANNO UNCED  |    |             | D |

| AUSTIFICATION |    |             |   |

| §Y            |    |             |   |

| SISTELEUTIS   |    |             |   |

| SISTELEUTIS   |    | ABILITY O   |   |

| SISTELEUTIS   |    |             |   |

# INTEGRATED THIN-FILM TRANSISTOR DISPLAY

FIRST QUARTERLY PROGRESS REPORT 28 September to 31 December 1977

Contract DAAB07-77-C-0583, CDRL C002, DI-S-1800

Prepared by W. J. Helm, Project Engineer for US ARMY ELECTRONICS COMMAND Fort Monmouth, New Jersey

Report 5705-1

0

0

14 April 1978

A DIVISION OF ALROJET GENERAL CALIFORNIA 91702

Approved for public release; distribution unlimited.

1

1

-

0

0

0

- Summer

1

0

0

0

Survey (

Province of

The second

0

1

#### ABSTRACT

This report summarizes the work performed during the first quarter (28 September 1977 through 31 December 1977) on a program whose purpose is to develop techniques for producing flat-panel electroluminescent displays with integrated thin-film transistor circuitry. Included are descriptions of the overall design and configuration of the display device; the design and structure of the electroluminescent elements, thin-film transistors, driver circuits, and addressing circuits of the display device; the processes and equipment being used to fabricate these devices; the process development and improvement efforts being conducted, their results to date, and plans for the next quarter's effort.

The report is submitted in accordance with approval letter DELSD-D-PC, dated 24 March 1978, from Headquarters, U.S. Army Electronics Research and Development Command, Adelphi, Maryland.

Page

# TABLE OF CONTENTS

Section

2

3

REES

I

1

I

10

and the second

0

0

0

0

[]

0

0

1

.0

0

0

0

0

0

| 1     | NARRATIVE AND DATA                           |   |

|-------|----------------------------------------------|---|

| 1.1   | DEVICE DESCRIPTION 1-1                       |   |

| 1.1.1 | General                                      |   |

| 1.1.2 | Active Matrix Concept                        |   |

| 1.1.3 | Thin-Film EL Structure         1-3           |   |

| 1.1.4 | Thin-Film Transistor (TFT)                   |   |

| 1.1.5 | Driver Circuit                               |   |

| 1.1.6 | Addressing Circuit Concept                   |   |

| 1.2   | FABRICATION PROCESSES AND EQUIPMENT          | 3 |

| 1.2.1 | Additive Thin-Film Deposition 1-1            | 3 |

| 1.2.2 | AESC Vacuum Deposition Chambers 1-1          | 3 |

| 1.2.3 | EL Deposition                                | 5 |

| 1.2.4 | Electronic Deposition                        | 6 |

| 1.2.5 | Process Improvement Efforts and Results 1-10 | 6 |

| 2     | CONCLUSIONS                                  |   |

| 3     | PROGRAM FOR THE NEXT QUARTER                 |   |

| 4     | PUBLICATIONS AND REPORTS                     |   |

| 5     | IDENTIFICATION OF PERSONNEL                  |   |

|       | DISTRIBUTION LIST                            |   |

iii

Page

0

Ó

1

0

0

0

0

0

Q

D

D

0

1)

D

0

Î

D

D.

# FIGURES

0

Figure No.

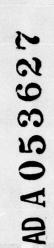

| 1 | PROGRAM SCHEDULE BY CONTRACT LINE ITEM                                                                        |

|---|---------------------------------------------------------------------------------------------------------------|

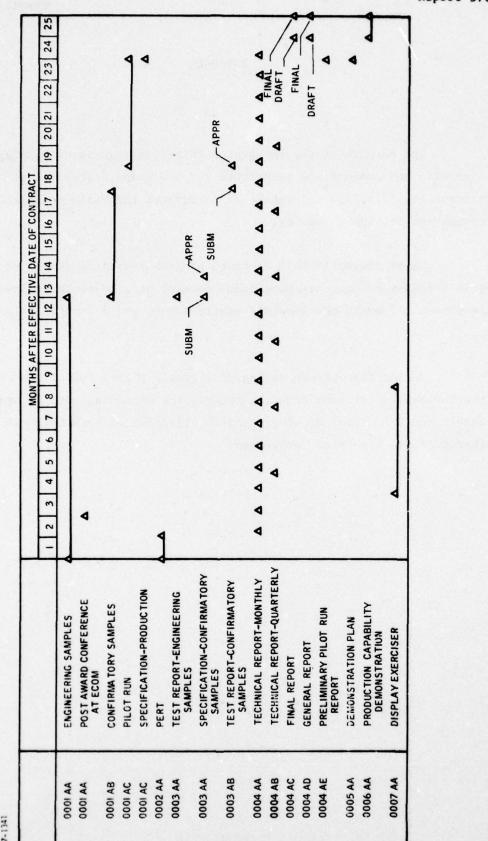

| 2 | SKETCH OF ELECTROLUMINESCENT (EL) ELEMENT STRUCTURE -<br>SHOWING TYPICAL MATERIALS AND FILM THICKNESSES 1-4   |

| 3 | SKETCH OF THIN-FILM TRANSISTOR - SHOWING DOUBLE GATE<br>STRUCTURE, TYPICAL MATERIALS AND FILM THICKNESSES 1-5 |

| 4 | CASCODE EL DRIVER                                                                                             |

| 5 | VIRTUAL CASCODE CONFIGURATION                                                                                 |

| 6 | SIMPLIFIED DISPLAY ELECTRONICS CIRCUIT DIAGRAM 1-8                                                            |

| 7 | TIMING DIAGRAM                                                                                                |

# TABLES

| Table No. |                                                                                      | Page |

|-----------|--------------------------------------------------------------------------------------|------|

| 1         | MAJOR PHYSICAL AND PERFORMANCE SPECIFICATIONS OF<br>INTEGRATED TF TRANSISTOR DISPLAY | 1-2  |

| 2         | ADDRESSING CIRCUIT EVENT SEQUENCE                                                    |      |

| 3         | PROFESSIONAL AND TECHNICAL PERSONNEL AND MANHOURS<br>EXPENDED DURING FIRST QUARTER   | 5-1  |

4

#### PURPOSE

The purpose of the Integrated Thin-Film Transistor Display Program is to develop and demonstrate techniques for producing flat-panel electroluminescent (EL) displays consisting of integrated thin-film transistor (TFT) addressing and driving circuitry.

Major phases of this 25-month program indicated in Figure 1 (Program Schedule by Contract Line Item) consist of a 12-month Engineering sample phase, a 5-month confirmatory sample phase, and a 5-month pilot run phase.

During the current engineering sample phase, two of the key tasks are the development of manufacturing methods for producing both EL panels and the associated TFT circuits. The specific objective of both tasks is establishing reproducible, high yield processes.

377-1341

REB

vi

Report 5705-1

1 0 1 П 0 [] 0 1 Π Í

Í

[]

0

[]

FIGURE 1 PROGRAM SCHEDULE BY CONTRACT LINE ITEM

0

1

0

1

#### GLOSSARY

Bucket Brigade Device - One form of charge transfer device which may be implemented with discrete transistors (e.g., TFTs) and capacitors. Under control of a two-phase clock, sampled signal data is propagated along the structure to provide a delay function.

Electroluminescence - The emission of light resulting from the application of an electric field to a solid and not due to temperature alone. As used here, the term applies to a thin-film sandwich structure composed of layers of dielectric, e.g.,  $Y_2O_3$ , and of doped active material, e.g., ZnS:Mn, excited by an applied a-c voltage.

TFT

BBD

EL

Ţ

Thin-Film Transistor - A field-effect transistor in thin-film form, fabricated by vacuum deposition of evaporated materials through a series of stencil masks onto an insulating substrate.

#### Section 1

NARRATIVE AND DATA

#### 1.1 DEVICE DESCRIPTION

### 1.1.1 General

The integrated thin-film transistor display of interest on this program consists of an array of individually addressable and controllable electroluminescent elements. The major physical and performance specifications for the display are listed in Table 1.

# 1.1.2 Active Matrix Concept

The display design is based on the active matrix concept--that is, the matrix of light-emitting elements incorporates, at each site, an active circuit to store ON or OFF data and to provide the requisite switching state for controlling the EL element. A thin-film transistor (TFT) provides the switching function, with the ON or OFF gate control voltage stored on a capacitor. Charge leakage makes it necessary to update or refresh the control voltage periodically. Row and column AND gates, controlled by corresponding scan generators, are used to enable a data line to set the appropriate charge level on the selected capacitor. Parallel data lines addressing 7 of the 222 columns simultaneously are presently contemplated as a means of reducing the data rates for compatibility with thin-film transistor capabilities.

The selection of seven data lines conveniently accommodates the intended ASCII character format of five active and two inactive (but still addressable) columns per character. The column and row scan generators, to be implemented with TFT bucket brigade device (BBD) delay lines or shift registers, will consequently consist of 32 and 77 delay stages respectively. At the required rate of 30 frames/sec, the data rate is  $32 \times 77 \times 30 = 73,920$  bits/ second on each of the seven data lines.

# TABLE 1 MAJOR PHYSICAL AND FERFORMANCE SPECIFICATIONS OF INTEGRATED TF TRANSISTOR DISPLAY

Display Panel Maximum Dimensions Display Area

Number of EL Elements EL Element Shape and Size

Number of Alphanumeric Characters

Character Format

Display Weight Power Dissipation

Viewability

Contrast

Operating Life

4.0 inches x 8.0 inches

$2.90 \pm 0.05$  inches x  $6.60 \pm 0.06$  inches

77 rows of 222 elements

Rectangular, 0.015 x 0.021 inch minimum

256 (8 rows of 32 characters)

5 x 7 element dot matrix configuration

7 oz. maximum

2.0 watts maximum all elements on; 1.0 watt maximum all elements off

Characters viewable and recognizable with 2000 footcandle ambient light intensity on the display

Ratio of on-element luminescence to luminescence of off-element or neighboring dark space (whichever is greater) to be 20 or more

600 hours minimum through ON-OFF cycles, including 500 hours of ON operation

#### 1.1.3 Thin-Film EL Structure

The basic light-emitting element of the display matrix is a rectangular shaped capacitor fabricated by vacuum deposition techniques. The lateral dimensions of such an element are bounded by the specified minimum size of 0.015 by 0.021 inches and the approximate 0.030- by 0.038-inch center-to-center spacing defined by the specified display size and format.

Figure 2 is a sketch of an EL element structure which describes the typical materials, film thicknesses and structure of an EL element. When an a-c voltage is applied to these elements, a yellowish-orange light is produced and can be viewed through the substrate and transparent electrode. The luminescence or brightness of an element is a function of the excitation voltage, a function of frequency for a continuous sine wave drive, or of pulse shape and duty cycle for pulsed operation.

# 1.1.4 Thin-Film Transistor (TFT)

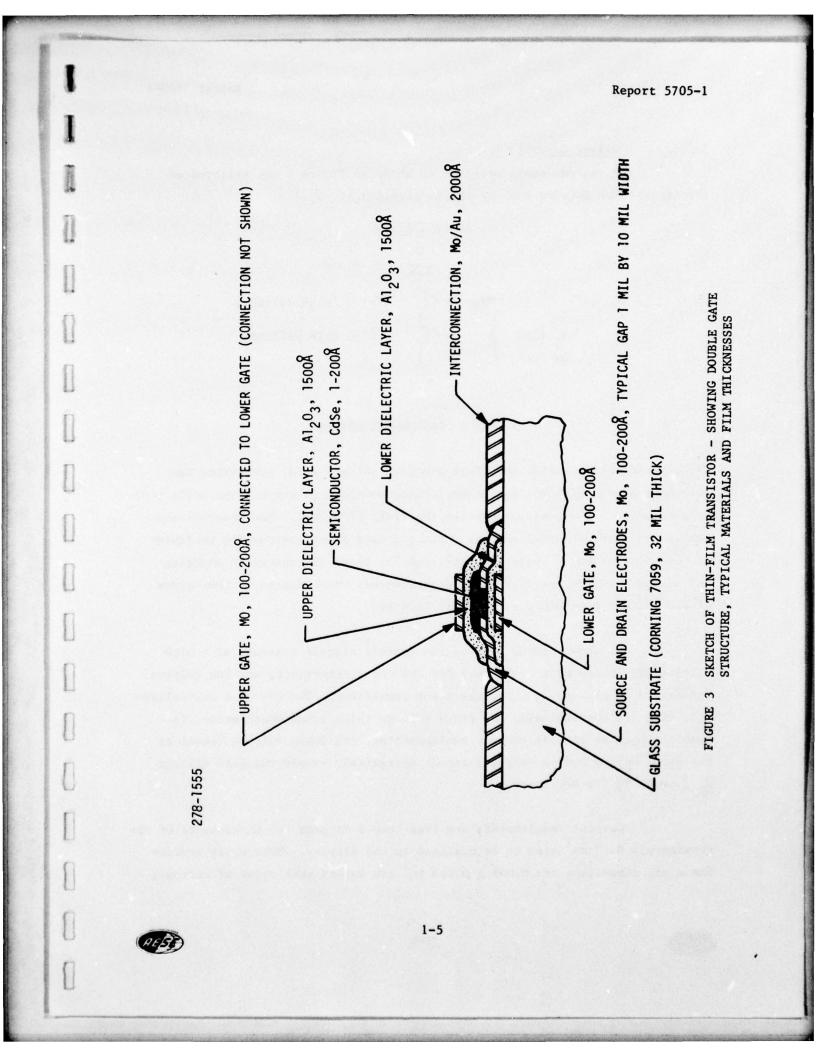

The thin-film transistor is an insulated gate, field effect device, fabricated by vacuum deposition techniques. In its simplest form the TFT consists of a thin layer of semiconductor with source and drain electrodes at either end; an insulating layer covering the semiconductor and partly covering the source and drain electrodes; and a gate electrode on the insulator centered over the source drain gap and extending slightly beyond the gap.

More commonly, TFTs are fabricated as double-gate devices, having an insulated gate both above and below the semiconductor. This construction provides double the transconductance for a given geometry since both gate fields are effective in modulating the semiconductor. In addition, the characteristics of the drain current in the saturated region are improved and flatter than those of single-gate transistors. The double gate structure is illustrated in Figure 3 which also notes representative materials and film thicknesses.

0

0

0

Gun

-

-

-----

0

1

1

0

0

7

Trees of

[]

0

278-1556

COUNTERELECTRODE, Mo/Au, 2000Å BLACK LAYER, 3000Å DIELECTRIC,  $Y_2O_3$ , 2000Å EL LAYER, Mn-DOPED ZnS, 6000Å DIELECTRIC,  $Y_2O_3$ , 2000Å TRANSPARENT ELECTRODE, Mo, 60Å GLASS SUBSTRATE, CORNING 7059, 32 MIL THICK

VIEWING DIRECTION (ALL LAYERS TRANSPARENT EXCEPT BLACK LAYER AND COUNTER ELECTRODE)

FIGURE 2 SKETCH OF ELECTROLUMINESCENT (EL) ELEMENT STRUCTURE -SHOWING TYPICAL MATERIALS AND FILM THICKNESSES

Ū

-

0

0

-

0

0

I

-

[]

#### 1.1.5 Driver Circuit

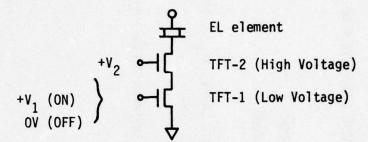

A cascode configuration, as shown in Figure 4 was selected as the circuit for driving each of the EL elements.

FIGURE 4 CASCODE EL DRIVER

The circuit configuration in effect provides voltage gain, permitting the switching of the high voltage EL excitation waveform (a few hundred volts p-p) by a relatively low gate-voltage (on the order of 5-10V). Two benefits are realized: external drive circuitry for the data lines can readily be implemented using standard logic circuits; and the power dissipated in charging and discharging the row and column capacitances, which scales as the square of the voltage excursion, is markedly reduced.

As shown in the figure, the cascode circuit consists of a high voltage TFT (thick gate insulator) for the upper transistor, and low voltage (thin gate insulator) unit for the lower transistor. The use of a low-voltage TFT, with its corresponding low drive voltage (high transconductance), is possible because in this circuit configuration, its drain voltage (equal to the upper unit's source voltage) cannot appreciably exceed the gate voltage  $V_2$  (~40 V) in the OFF state.

Current requirements are less than 1 mA peak for EL elements of approximately 0.25 mm<sup>2</sup> area to be utilized in the display. TFTs whose sourcedrain gap dimensions are 0.001 x 0.010 in. can supply that order of current;

1-6

low voltage units at gate voltages below 10V, and high voltage units with approximately 40V on the gate.

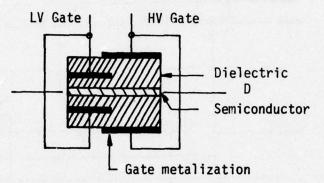

The cascode circuit configuration can be fabricated using a pair of separate TFTs or as a so-called virtual cascode illustrated in Figure 5.

FIGURE 5 VIRTUAL CASCODE CONFIGURATION

The virtual cascode configuration uses a combination of a low voltage (thin gate dielectric) and a high voltage (thick gate dielectric) TFT. It makes possible an appreciable size reduction by eliminating unneeded connections, and provides for physical separation of the high and low voltage gates even for the overlap case indicated in Figure 5.

# 1.1.6 Addressing Circuit Concept

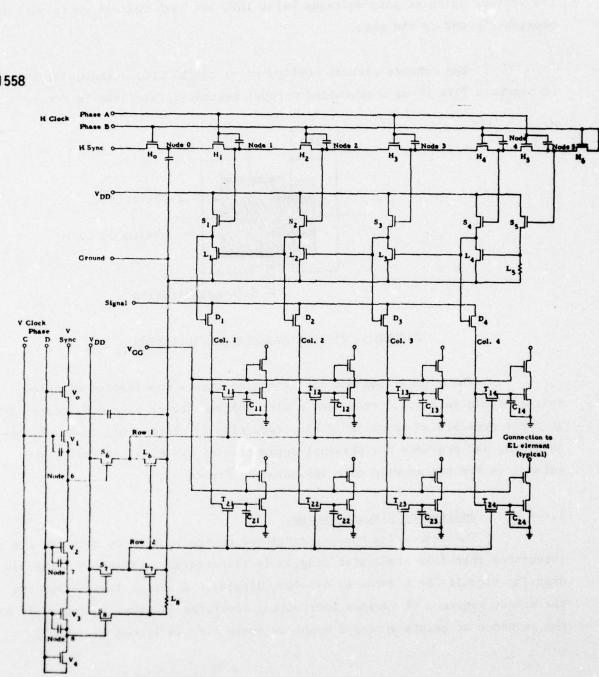

The addressing concept developed on the program to date for the integrated thin-film transistor display is illustrated in Figure 6 - the addressing circuit for a 2-row by 4-column display. A timing diagram showing the proper sequence of various controlling waveforms is given in Figure 7, and the sequence of events during a complete frame time is listed in Table 2.

1

[]

0

0

1

0

0

0

0

Π

0

[]

[]

0

278-1558

FIGURE 6 SIMPLIFIED DISPLAY ELECTRONICS CIRCUIT DIAGRAM

REST

| I      |          |                                                                                                 | Report 5705-1                   |

|--------|----------|-------------------------------------------------------------------------------------------------|---------------------------------|

| I      | 278-1557 |                                                                                                 |                                 |

| 0      |          | Start Frame 1/2 t clock                                                                         | Start Frame                     |

| 0      |          | Phase B                                                                                         |                                 |

| 0      |          | Phase C                                                                                         |                                 |

| U      |          | Phase D                                                                                         |                                 |

|        |          | t <sub>line</sub>                                                                               |                                 |

| 0      |          | H Sync                                                                                          |                                 |

|        |          | V Sync                                                                                          |                                 |

| 0      |          | Signal $D_{11}$ $D_{12}$ $D_{13}$ $D_{14}$ $D_{21}$ $D_{22}$ $D_{23}$<br>$\rightarrow \Delta t$ | D <sub>24</sub> D <sub>11</sub> |

|        |          | Node 1                                                                                          |                                 |

| 1      |          | Node 2                                                                                          | <b>Г</b>                        |

|        |          | Node 3                                                                                          |                                 |

| U      |          | Node 4                                                                                          |                                 |

|        |          | Node 6                                                                                          |                                 |

|        |          | Node 7                                                                                          |                                 |

| n<br>N |          | FIGURE 7 TIMING DIAGRAM                                                                         |                                 |

|        |          | 1-9                                                                                             |                                 |

0

[]

0

0

1

0

D

-----

$\Box$

0

$\Box$

[]

Π

0

0

Π

# TABLE 2 ADDRESSING CIRCUIT EVENT SEQUENCE

| the second secon |                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>t = 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V gate pulse on node 6; enables row 1 via $S_1$ . H gate<br>pulse on nodes 1 and 5; node 1 enables $D_1$ via $S_1$ ,<br>node 5 disables $D_4$ via $S_5$ and $L_4$ . Signal line carry-<br>ing data level $D_{24}$ (briefly) tied to column 1, and to<br>$C_{11}$ via $T_{11}$ .                   |

| $t = \Delta t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Signal line shifts to data level $D_{11}^{}$ , setting poten-<br>tial on column 1 and storage capacitor $C_{11}^{}$ . ON or<br>OFF condition for corresponding EL element set.                                                                                                                    |

| $t = 1/2 t_{clock}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H gate pulse appears on node 2, disabling $D_1$ via $S_2$<br>and $L_1$ , allowing column 1 to float at $D_{11}$ ; enabling<br>$D_2$ . Data level $D_{11}$ on signal line (briefly) tied to<br>column 2 and $C_{12}$ . Gate circuit voltage on $L_4$ decays<br>off through source resistor $L_5$ . |

| $t = 1/2 t_c + \Delta t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Signal line shifts to $D_{12}^{}$ , setting potential on column 2 and $C_{12}^{}$ .                                                                                                                                                                                                               |

| $\frac{t = t_c}{c}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H gate pulse on node 3, disabling $D_2$ and letting column 2 float at $D_{12}$ , enabling column 3.                                                                                                                                                                                               |

| $t = t_c + \Delta t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Signal line shifts to D <sub>13</sub> , setting C <sub>13</sub> .                                                                                                                                                                                                                                 |

| $t = 3/2 t_{c}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Column 3 floats at D <sub>13</sub> , column 4 enabled.                                                                                                                                                                                                                                            |

| $\frac{t = 3/2 t_c + \Delta t}{t}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C <sub>14</sub> set to D <sub>14</sub> (end of first line).                                                                                                                                                                                                                                       |

| $t = 2 t_c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V gate pulse appears on node 7, disabling row 1 via $L_6$ , enabling row 2 via $S_7$ . H gate pulse on nodes 1 and 5, enabling column 1 and disabling column 4. All row 2 storage capacitors $C_{2j}$ set to existing column potentials ( $C_{21}$ briefly).                                      |

| $t = 2t_c + \Delta t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $C_{21}$ set to $D_{21}$ .                                                                                                                                                                                                                                                                        |

REZZ

1-10

TABLE 2 ADDRESSING CIRCUIT EVENT SEQUENCE (CONT.)

| $T = 5/2 t_c$            | D <sub>1</sub> disabled, D <sub>2</sub> enabled.                   |

|--------------------------|--------------------------------------------------------------------|

| $t = 5/2 t_c + \Delta t$ | C <sub>22</sub> set to D <sub>22</sub> .                           |

| $t = 3 t_c$              | D <sub>2</sub> disabled, D <sub>3</sub> enabled.                   |

| $t = 3 t_c + \Delta t$   | C <sub>33</sub> set to D <sub>23</sub> .                           |

| $t = 7/2 t_{c}$          | D <sub>3</sub> disabled, D <sub>4</sub> enabled.                   |

| $t = 7/2 t + \Delta t$   | $C_{24}$ set to $D_{24}$ (end of line 2 and of frame)              |

| $t = 4 t_c$              | V gate pulse on nodes 6 and 8, enabling row 1 and disabling row 2. |

|                          | Continue through frame sequence.                                   |

It is the function of this circuit (Figure 6) to distribute digital (i.e., ON and OFF) data from the signal line to the storage capacitors  $C_{ij}$  at each display element site. The ON or OFF voltage level so stored on each capacitor controls the state of the cascode switch in series with the corresponding EL element.

Distribution of the data is controlled by means of gating pulses used to enable rows and columns one at a time through the use of bucket brigade device (BBD) shift registers. TFTs  $V_i$  together with their associated capacitors constitute the vertical shift register. A synchronizing pulse introduced to its input once each frame time is used to enable the row lines in sequence as the pulse is shifted along the register at the line rate in synchronism with the vertical clock pulses. (Source followers  $S_i$ , along with their active source loads  $L_i$  are used to minimize loading of the BBD nodes).

1-11

0

In a similar fashion, the horizontal sync pulse, introduced into the horizontal shift register (TFTs H<sub>j</sub> and associated capacitors) once each line time, is shifted along that register at the element rate. The pulse is coupled via a source follower to each column data gate, D<sub>j</sub>, in sequence, allowing data appearing on the signal line to be impressed on the columns, one after the other. The column voltages charge up corresponding storage capacitors in the enabled row via TFTs T<sub>ij</sub>, establishing the ON or OFF states for the cascode switch circuits.

It can be seen that as each data gate  $D_j$  turns off (aided by the active load  $L_j$ ) its associated column floats at the potential established during the on time of the gate. (This feature must be provided, since the column line is still connected via  $T_{ij}$  to the storage capacitor in that column and in the selected row). The timing of data as shown for the signal line in Figure 2 is delayed with respect to the clock transitions to ensure that the column just addressed is completely disconnected from the signal line before the next data transition occurs.

At the end of a line time, all columns are floating at the potentials established during that line time. Thus when the next row is enabled, all of the storage capacitors are set to the potentials of corresponding elements in the row above. Elements at the ends of the lines could thus be in the wrong state for a full line time (other elements for a shorter time in proportion to their positions). In our two-row example, this would be totally unacceptable, but for the 77-line display to be implemented on this program, the contrast ratio for the elements most affected would still be 77. It has tentatively been concluded that this slight contrast degradation is more acceptable than the added circuit complexity and power dissipation required to eliminate it.

#### 1.2 FABRICATION PROCESSES AND EQUIPMENT

#### 1.2.1 Additive Thin-Film Deposition

All of the electronic and light emitting elements of the integrated thin-film transistor display are fabricated using additive, thin-film deposition processes. These processes involve the evaporation of metallic, dielectric, and semiconductor materials in a vacuum by electron beam gun or resistance heating; and the deposition of each evaporated material though a stencil mask onto a substrate, typically glass or ceramic. Each material and mask combination results in a deposition pattern on the substrate. Sequences of depositions of different materials through each of a set of masks are used to produce devices, circuits or complete subsystems such as the integrated thin-film transistor display.

#### 1.2.2 AESC Vacuum Deposition Chambers

The equipment being used to fabricate the integrated thin-film transistor display consists of three vacuum deposition chambers currently installed and available in the AESC Vacuum Deposition Laboratory. These chambers have been designed and developed by AESC over the past ten years. Key features of their design, installation, and operation are as follows:

a. The vacuum disposition systems are installed in a clean room (class 10,000). Access to this room is controlled and clean room garments are required for all personnel. All pneumatic, hydraulic, and high voltage lines are installed beneath a second floor surface for both cleanliness and personnel safety.

b. All chambers are of a top loading design--the bell jars and cylinders are provided with gasket seals at the system base. The deposition mechanism forms the top of the cylinder and is similarly gasket sealed. This design permits direct mechanical linkage between the deposition mechanism and the control knobs on the top of the chamber. It also permits quick turnaround between operations--the entire mechanism is lifted from the top of the chamber for installation or removal of masks and substrates.

0

[]

0

c. The deposition mechanisms are designed to hold six masks and six substrates. Six configurations of as many as 11 deposition materials (i.e., as many as 66 depositions) can be made on six substrates during a single pumpdown of a single chamber. The deposition mechanism uses ball and socket connections which register each mask to each substrate to an accuracy of 0.1 mil (0.0001 inch).

d. The chambers are typically evacuated to  $10^{-7}$  to  $10^{-8}$  torr for thin-film electronic depositions. Four stages of pumping are used for rapid evacuation. A Stokes mechanical pump (375 CFM) assisted by a Roots blower (500 to 800 CFM) is used to bring chamber pressure down to 100 microns. Sorption pumps (Zoelite pellets chilled to liquid nitrogen temperature) further reduce pressures to about 5 x  $10^{-4}$  torr. A helium cold finger or liquid nitrogen cold trap is used to reduce pressures to  $10^{-5}$  torr; and a titanium gettertype ion pump, together with quartz-iodine lamp bakeout, bring the system down to 3 x  $10^{-8}$  torr.

e. Electron beam guns are used to vaporize deposition materials, both by direct beam impingement on the material and indirectly by beam heating of the material boat or container. Direct electron beam vaporization avoids possible contamination by boat materials and permits deposition of very high melting point materials. (Sapphire,  $Al_20_3$ , for example, is frequently used as a dielectric and sealant.) A system of rotatable trays and shields permits a selection of up to 11 different materials in any sequence during a single chamber pumpdown. Techniques and schedules have been developed and standardized for the deposition of a wide variety of conductor, semiconductor and dielectric materials.

f. Very accurate automatic control of the deposition process is provided by a system which uses a quartz crystal vibration at 5 megahertz inside the chamber. Deposition of material on the crystal increases its mass and reduces its frequency. The control system converts frequency to thickness or deposition rate of a given meterial, or both, and adjusts the power to the electron beam gun accordingly, shutting off the gun when a desired thickness

is achieved. The desired thickness and deposition rate are entered into the control system prior to the deposition and deposition thicknesses are commonly controlled to one Angstrom  $(10^{-8} \text{ cm})$ .

In addition, the electrical characteristics of devices being formed can be measured and observed during the deposition process. Electrical leads contact the edge of the substrate where a sample or monitoring transistor is deposited, and are connected to an external oscilloscope where the changes in electrical characteristics during the deposition process can be directly observed.

# 1.2.3 EL Deposition

The EL structure is fabricated in three sequences. For each of these, the vacuum chamber is prepared by cleaning deposition shields, cleaning and loading glass substrates and masks (if required), loading source materials, pumping down the chamber, and outgassing sources and substrates. During the first step, both sides of the substrate are coated with a 60 Å layer of molybdenum (together with copper edge electrodes for electrical contact). One layer will serve as the transparent electrode, while the other will be used for substrate heating during the next sequence in which the actual EL layer is fabricated. Several substrates may be coated simultaneously.

For the second step, electrical contacts are made to the heater layer, and access to the transparent electrode contacts is preserved by masking them from subsequent depositions, when the substrates are mounted in the chamber. The first deposition, carried out in an  $0_2$  background pressure of  $5 \times 10^{-5}$  torr with a substrate temperature of  $300^{\circ}$ C, results in the first dielectric layer of  $2000 \text{ Å of } Y_2 0_3$ . The heater is turned off and the substrate is allowed to cool, prior to deposition of the Mn-doped ZnS layer. Thickness and Mn doping concentration may be varied to achieve different brightnessvoltage characteristics; typical values are 6000 Å and 3 percent by weight, respectively. After the ZnS:Mn deposition cools, the second  $2000 \text{ Å } Y_2 0_3$ dielectric layer is deposited in an  $0_2$  background. Finally, a 3000 Å thick black layer is applied. The desired counter electrode pattern, which defines

1-15

-----

the geometry of the display, is deposited through a metal stencil mask as a separate step.

# 1.2.4 Electronic Deposition

For fabrication of thin-film transistors, chamber preparations similar to those described above for EL fabrication are carried out. The first deposition is that of an  $Al_20_3$  dielectric layer, carried out in a high  $(2 \times 10^{-4} \text{ torr}) 0_2$  background. (This step is found useful in obtaining better device uniformity over the substrate.) The transistor structure shown in Figure 3 is then built up by successive depositions, through corresponding metal masks, of Mo lower gate electrode; lower  $Al_20_3$  gate insulator (again in an  $0_2$  background); Mo source and drain electrodes; CdSe semiconductor; upper gate insulator; upper gate electrode (using the same mask as for the lower one); Mo/Au interconnecting electrodes; and finally a protective  $Al_20_3$ overcoat.

During the CdSe deposition, the characteristics of a test device are monitored, permitting the development of transistor action to be observed. If the as-deposited semiconductor is found to be improperly conductive, either too high or too low, as a result either of source material properties or of deposition conditions, the stoichiometry is adjusted by the carefully controlled addition of Cd or Se, as appropriate, until the desired TFT characteristics are observed.

As the upper gate insulator is deposited, the TFT characteristics can be seen to change dramatically, approaching an open circuit. A postdeposition heat treatment is required to regain the desired TFT character. Again a test device is used, with resistance between drain and gate-source being the quantity monitored.

### 1.2.5 Process Improvement Efforts and Results

Thin film display work at Aerojet ElectroSystems during the two years prior to this program has demonstrated that high quality electroluminescent films and electronic devices can be made by additive, vacuum

deposited, thin film processes. However, little information has been obtained on the reproducibility and yield of these processes as used in various display component experiments and demonstrations.

The development of high yield, reproducible processes is obviously critical to the success of this program and to any future application of thin film technology to military or industrial needs. The investigation of process variables--determining the material, process, and procedural factors which cause nonuniformity and non-reproducibility--is an essential first step towards high yield processes which will permit routine fabrication of displays in a manufacturing environment, and has been the principal activity during this first quarter of the program. Fabrication procedures outlined in the preceding sections are the results of the evolution which took place during these investigations; this evaluation is described in the following paragraphs for the two areas.

### 1.2.5.1 EL Processes

At the beginning of the program, EL fabrication, as now, began with deposition of the Mo transparent electrode, and of the  $Y_2O_3$  dielectric, but with substrate heat supplied by quartz-iodine lamp radiation. The need for substrate heating had been established earlier, in order to minimize cracking of the films because of thermal stress during the subsequent heat treatment. Quartz-iodine lamps, already used for pre-deposition substrate outgassing, were adapted for this use.

While radiative heating was helpful during the early development in obtaining high quality EL films, yield and uniformity were poor because of uncontrollable temperature variations over a given substrate or between one substrate and another. Initially on the program, a copper coating, slightly oxidized to increase absorption, was applied to the back of the substrate the side on which the radiation was incident - in an attempt to obtain more uniform heating. This was somewhat more successful, but uniformity and reproducibility were still inadequate. Next the use of the transparent electrode as a resistance heater was tried. First experiments involved deposition

Francis

0

0

0

0

0

-

-

0

0

1

of  $Y_{2}0_{3}$  dielectric only on the transparent electrode, followed by heat treatment in a separate vacuum oven and by visual examination for cracking or crazing. From these experiments it was determined that reproducible temperatures, reasonably uniform over a sizeable fraction of the substrate, could be obtained, and that a temperature of about  $300^{\circ}$ C was required to avoid problems of thermal stress during the subsequent  $500-550^{\circ}$ C vacuum oven bake cycle. However, allowance must be made for the difference in sticking coefficients for the arriving vapor stream between the heated substrate and the room temperature quartz crystal thickness monitor.

Full EL film fabrication was then attempted, still using resistance heating via the transparent electrode during both  $Y_2 0_3$  depositions. With the Mn-doped ZnS present, deposited at room temperature and prior to its heat treatment, problems were encountered during the second  $Y_2 0_3$  deposition with electrical breakdown, presumably due to conductive regions in the ZnS as the result of non-uniform Mn distribution. This problem was avoided by going to a second, dedicated heater, electrode on the back of the substrate. With this approach, the way was also opened for performing the ZnS heat treatment in place, immediately after its deposition. Studies are still underway to determine the optimum heat cycle; a temperature of  $500^{\circ}$ C for 1 hour is fairly successful.