ADA 043817

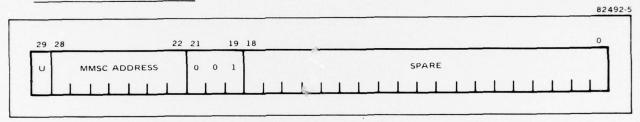

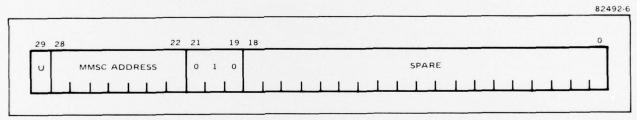

P.

HUGHES

HUGHES AIRCRAFT COMPANY FULLERTON, CALIFORNIA

MOST ProJect -3

**VOLUME I - OPERATIONAL PROGRAMMING**

SOFTWARE MEMO FOR THE MULTIMODE SONAR CONSOLE DISPLAY SYSTEM

9 AUGUST 1968 N00123-67-C-0833

DISTRIBUTION STATEMENT A

Approved for public release; Distribution Unlimited

in the world the second that is not not the second

UNCLASSIFIED

# SOFTWARE MEMO FOR THE MULTIMODE SONAR CONSOLE DISPLAY SYSTEM .

Volume I - Operational Programming

Submitted to Navy Undersea Warfare Center San Diego, California

by

Hughes Aircraft Company Hughes-Fullerton Fullerton, California

FR-68-11-653 9 Aug**ust 1968** N00123-67-C-0833

12) 113p.

D D C

DECIDING

SEP 7 1977

DEGETT EN

A

172 350

DISTRIBUTION STATEMENT A

Approved for public release; Distribution Unlimited

#### FOREWORD

This report, submitted to the Navy Undersea Warfare Center San Diego, by Hughes Aircraft Company, is a contractually required document under Contract No. N00123-67-C-0833. The report describes the operations of the Multi-Mode Sonar Console and Passive Data Memory Unit from the viewpoint of the computer programmer. Instruction and dataword formats for each of the equipments are described, as are the actions that occur in response to the instructions and data words. For convenience in handling, the document is divided into two volumes: Volume I describes operational programming and Volume II describes diagnostic programming.

In the preparation of this report, it has been assumed that the reader is familiar with the UNIVAC 1230 computer, with logical operations, and with the basic principles of computer-controlled display generation. The information in this report will permit the reader to write valid programs for generating versatile sonar displays.

### CONTENTS

| SUMMARY S                                                                                                                                      | S-0                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| SECTION 1 - COMPUTER/DISPLAY SYSTEMS COMMUNICATIONS                                                                                            |                                        |

| Functional Organization for Communications                                                                                                     | 1-0                                    |

| Computer Communications to MMSC and PDMU                                                                                                       |                                        |

| Formats for MMSC/PDMU Memory Control Command Words Formats for MMSC Indicator Words and PDMU Passive Format Word Format for Test Stimulus Word | 1-2<br>1-4<br>1-6<br>-10               |

| MMSC or PDMU Communications to Computer                                                                                                        |                                        |

| MMSC Function Codes                                                                                                                            | -14<br>-16<br>-18<br>-20<br>-24<br>-25 |

| SECTION 2 - MEMORY ALLOCATIONS                                                                                                                 |                                        |

| MMSC and PDMU Memory Allocations                                                                                                               | 2-0                                    |

| SECTION 3 - MMSC PROGRAMMING                                                                                                                   |                                        |

|                                                                                                                                                | 3-0                                    |

| Memory Addressing                                                                                                                              |                                        |

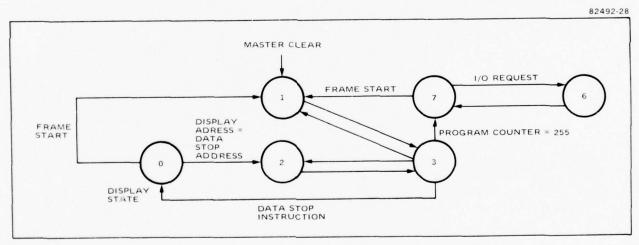

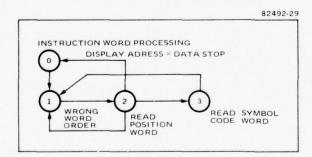

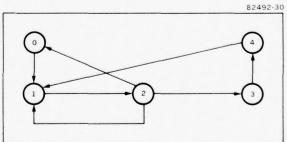

| State Diagrams for the Program Control Counter                                                                                                 | 3-2<br>3-6<br>3-8                      |

| MMSC Instructions                                                                                                                              |                                        |

| Format of Brightness Group Word 3-                                                                                                             | -12<br>-16<br>-18                      |

| MMSC Data Words                  |                                                                                              |                              |

|----------------------------------|----------------------------------------------------------------------------------------------|------------------------------|

| Format of Line<br>Format of Alpl | e Word                                                                                       | 3-22<br>3-24<br>3-26<br>3-28 |

| MMSC Symbols                     |                                                                                              |                              |

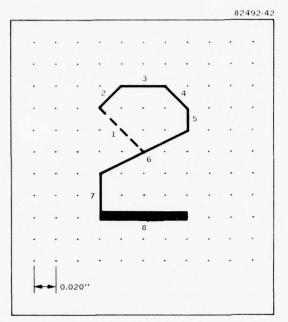

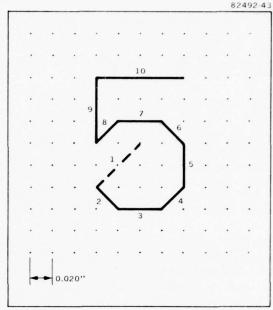

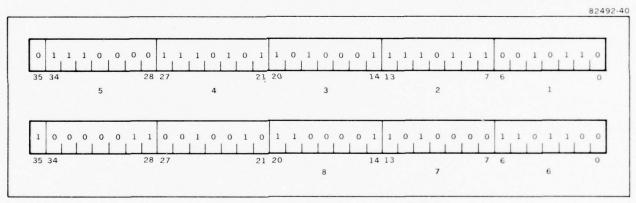

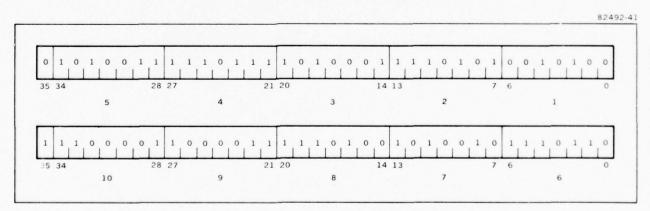

| Design Guideli                   | Length Coding for Symbols                                                                    | 3-30<br>3-32<br>3-34         |

| Special Features                 |                                                                                              |                              |

|                                  | es, In-Line Alphanumeric and Passive Data<br>splacement and Expanded-Sector Displays         | 3-36<br>3-37                 |

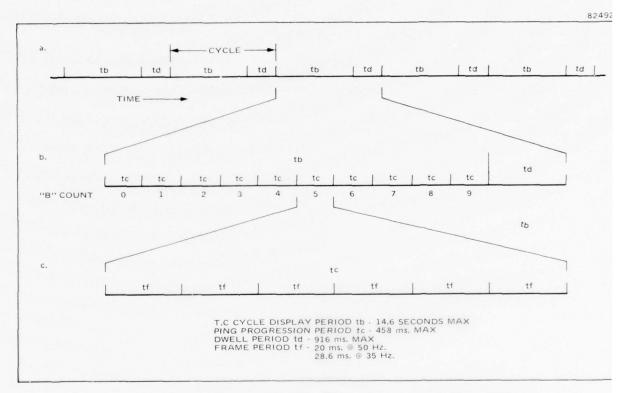

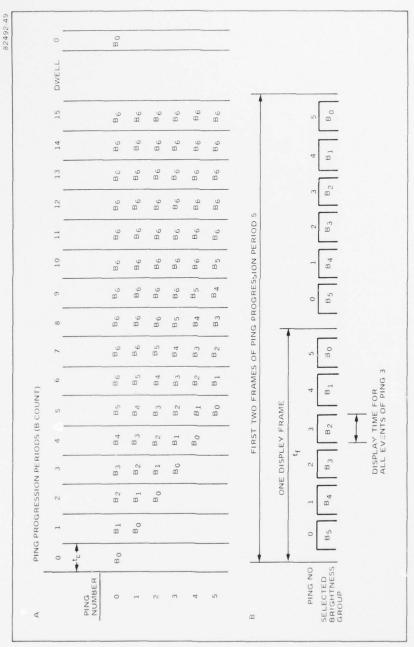

| Time-Compressed F                | Ping History                                                                                 |                              |

| History                          | quence in Displaying Time-Compressed Ping                                                    | 3-38<br>3-40                 |

| SECTION 4 - PDMU PROG            | RAMMING                                                                                      |                              |

| PDMU Functional De               | escription                                                                                   |                              |

| Program-Acce<br>Displays.        | iples of Operation of Passive Data Memory Unit essible PDMU Units Involved in Generating BTR | 4-0<br>4-2<br>4-4            |

|                                  |                                                                                              | 4-4                          |

| PDMU Word Format                 |                                                                                              | 4-6                          |

| Format of PDI<br>Using PDMU V    | MU Instruction Word                                                                          | 4-6<br>4-7<br>4-8<br>4-12    |

|                                  | HE MAINTENANCE PANEL IN PROGRAM                                                              | A-1                          |

| APPENDIX B - PASSIVE I           | DISPLAY LINES/SYMBOL TIMING                                                                  | B-1                          |

| APPENDIX C - SINGLE ST           | YMBOL MODE TIMING                                                                            | C-1                          |

| APPENDIX D - TABLE OF            | F MMSC AND PDMU FORMATS                                                                      | D-1                          |

SUMMARY

#### SUMMARY OF MMSC DISPLAY SYSTEM

The MMSC display system combines a group of stored-program, general-purpose Multi-Mode Sonar Consoles with a Passive Data Memory Unit for interface with a UNIVAC computer to provide for storage and display of sonar data.

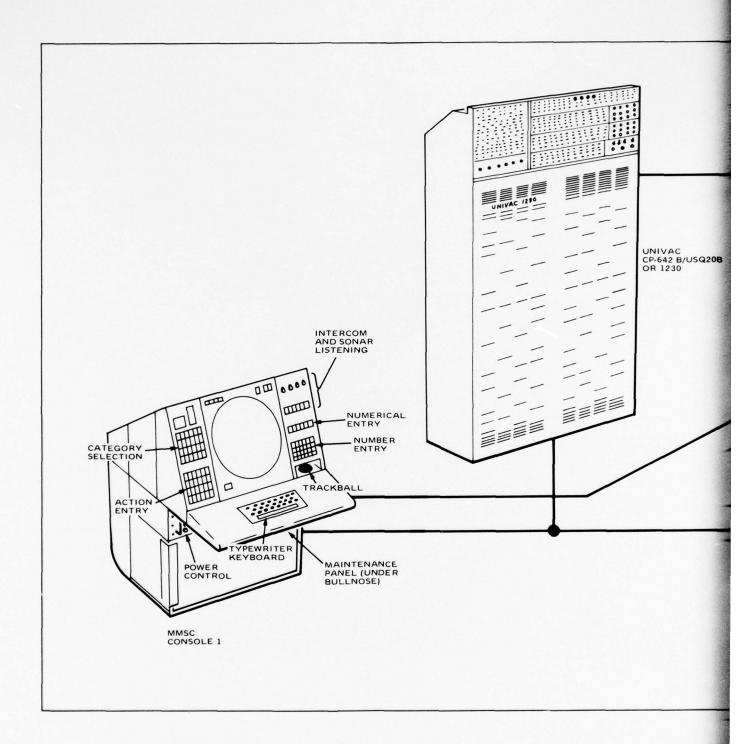

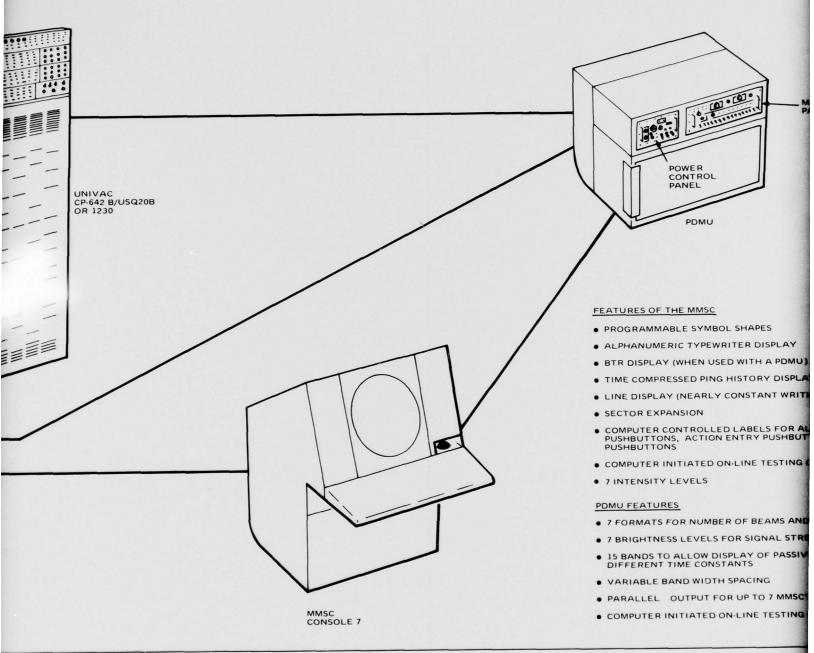

The Multi-Mode Sonar Console display-system consists of one to seven Multi-Mode Sonar Consoles (MMSC's) and a single Passive Data Memory Unit (PDMU). The MMSC display system provides versatile display capability for computer-aided sonar systems. The MMSC's and PDMU will interface with either the militarized UNIVAC CP-642B/USQ-20B or the UNIVAC 1230 computer. (See the facing figure.) The MMSC display system does not interface directly with the sonar sensor sub-system. All active and passive sonar data are assembled, formatted, and transmitted to the MMSC display-system by the computer.

The design of the MMSC's will allow seven consoles or less to time-share a single, fast-interface, input/output channel of the computer. The PDMU operates on its own fast interface channel.

MMSC Features - The MMSC is a stored-program general-purpose sonar console. The program and display data are stored in the console's 8K, 36-bit word, random-access memory. Information is displayed on the CRT by cycling through the memory under control of the stored program. A selectable frame rate of either 35 or 50 Hz permits a steady state, non-flickering display. Features of the MMSC are summarized on the figure.

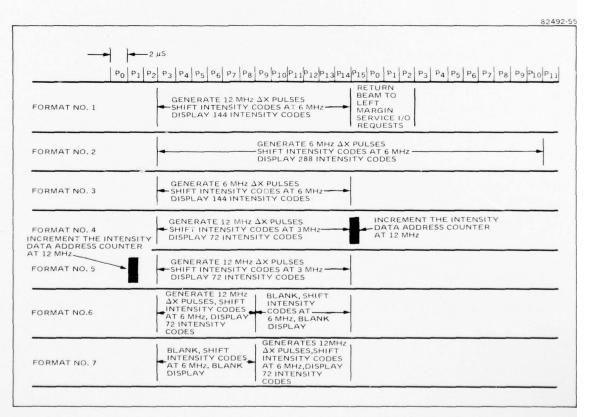

PDMU Features – The PDMU provides BTR display data in a variety of formats for the MMSC consoles. In performing this function the PDMU is required to store passive sonar data transmitted by the computer. The passive data, along with a limited number of program words, are stored in an 8K, 36-bit word, random access memory. The program words allow the BTR raster to be displayed in up to 15 bands with variable band spacing. In addition, the program words allow optimizing the data rate between the computer and PDMU. The computer may instruct the PDMU to format the passive data in one of seven formats which define the number of beams to be displayed and their widths. The format determines the required pulse trains to be transmitted by the PDMU to the consoles. The PDMU can transmit raster data in parallel to up to seven MMSC's.

Programming — Two essentially different types of programming exist within the MMSC display-system. One group of instructions is used in the exchange of information between the computer and MMSC display-system. This type of communication initiates a direct action in either the computer or MMSC display-system (e.g., a command transmitted by the computer to a particular MMSC to load the next block of transmitted words into its memory). This type of programming is similar for both the MMSC and PDMU and is presented in Section 1. In the second group, the instructions are initially data words which are transmitted by the computer to be loaded into an MMSC's or PDMU's memory. However, when these words are read out of memory during the normal course of operation, they become instructions which directly control the display on the CRT in the case of the MMSC, or raster generation in the case of the PDMU. This second group of instructions is presented in two sections as MMSC programming (Section 3) and PDMU programming (Section 4).

existed the contraction of the c

Configuration of the Multi-Mode Sonar Console Display-System. Features of the MMSC and P

82492-1

POWER CONTROL PANEL

PDMU

PDMU

FEATURES OF THE MMSC

PROGRAMMABLE SYMBOL SHAPES

- . ALPHANUMERIC TYPEWRITER DISPLAY

- . BTR DISPLAY (WHEN USED WITH A PDMU)

- . TIME COMPRESSED PING HISTORY DISPLAY

- LINE DISPLAY (NEARLY CONSTANT WRITING RATE FOR ALL LINES)

- . SECTOR EXPANSION

- COMPUTER CONTROLLED LABELS FOR ALERTS, CATEGORY SELECTION PUSHBUTTONS, ACTION ENTRY PUSHBUTTONS, AND NUMERICAL ENTRY PUSHBUTTONS

- COMPUTER INITIATED ON-LINE TESTING CAPABILITY

- 7 INTENSITY LEVELS

#### PDMU FEATURES

- 7 FORMATS FOR NUMBER OF BEAMS AND WIDTH

- 7 BRIGHTNESS LEVELS FOR SIGNAL STRENGTH

- 15 BANDS TO ALLOW DISPLAY OF PASSIVE DATA WITH DIFFERENT TIME CONSTANTS

- . VARIABLE BAND WIDTH SPACING

- PARALLEL OUTPUT FOR UP TO 7 MMSC'S

- . COMPUTER INITIATED ON-LINE TESTING CAPABILITY

ay-System. Features of the MMSC and PDMU are listed in the figure.

####

| Functional Organization for Communications                                        | 1-0                                          |

|-----------------------------------------------------------------------------------|----------------------------------------------|

| Computer Communications to MMSC and PDMU                                          |                                              |

| Format for External Function Words                                                | 1-2<br>1-4<br>1-6<br>1-10<br>1-12            |

| MMSC or PDMU Communications to Computer                                           |                                              |

| Computer Notification of MMSC Actions: Interrupt Word Format  MMSC Function Codes | 1-14<br>1-16<br>1-18<br>1-20<br>1-24<br>1-25 |

|                                                                                   |                                              |

and the form the second the second to the second to the second the second to the secon

#### FUNCTIONAL ORGANIZATION FOR COMMUNICATIONS

Similar Input/Output units are contained in both the MMSC and PDMU to enable cummunications with the computer.

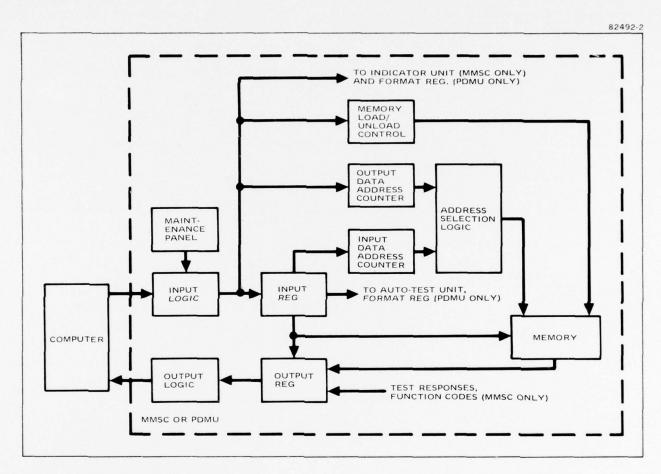

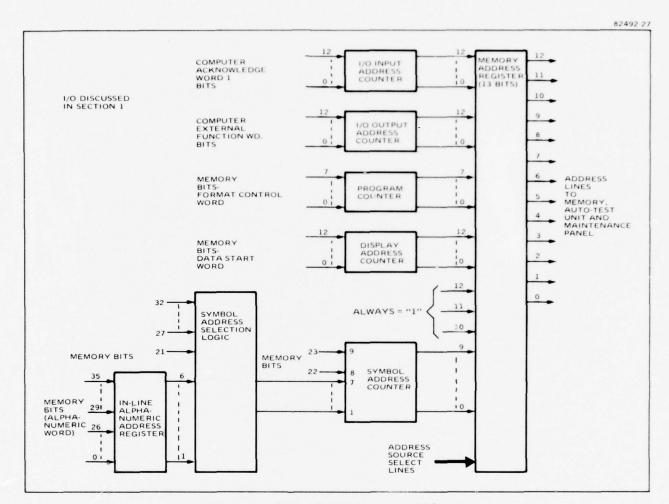

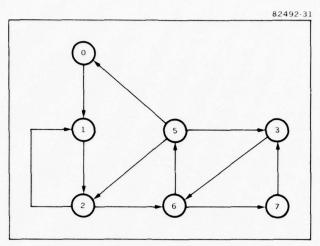

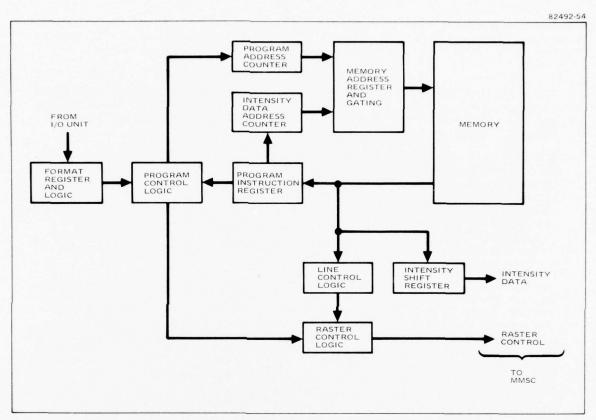

Each MMSC and PDMU contains an Input/Output (I/O) unit which acts as a buffer for communications between the computer and the equipment containing the I/O unit. The I/O unit for the MMSC and PDMU are essentially identical. A block diagram of the functions used in communications between the computer and the MMSC or the PDMU is shown in the facing figure. A brief discription of these functions follows.

Input Logic - The Input Logic consists of three functional logic groups: Input Source Selection Gates, Assembly Logic, and the Input Load Control Logic. The Input Source Selection Gates are used to select either the 30-bit lines from the computer or the 30-bit switches from the maintenance panel. The source selection is controlled by the "On-Line/Off-Line" switch on the maintenance panel. The Assembly Logic is used to convert two 30-bit acknowledge words from the computer into a 36 bit word for storage in the memory. The Input Load Control Logic detects word types, external function, acknowledge word 1 or acknowledge word 2, and generates control and timing signals.

<u>Input Register</u> - The Input Register provides temporary buffer storage for assembled <u>acknowledge</u> words or external function words.

Memory Load/Unload Control — The memory load flip-flop and memory unload flip-flop are contained in the Memory Load/Unload Control. These flip-flops are set and reset by external function commands, thus storing the load and unload commands. A PDMU or MMSC is capable of full duplex operation, thus both flip-flops may be set at the same time. The Memory Load/Unload Control logic generates timing signals that control memory operation.

Input Data Address Counter – The Input Data Address Counter is preset with an address contained in word 1 of an output acknowledge word pair. This address specifies the location in memory in which the 36-bit word in the input register is to be stored. The counter is only activated after the MMSC or PDMU receives a memory load start external function. The counter has an increment mode that may be used by setting to zero, bit 13 of each acknowledge word 1.

Output Data Address Counter - This counter is used after receipt of a memory unload start external function to address words in the memory for return to the computer. It is preset to the start address by the memory unload start external function.

Address Selection Logic - The Address Selection Logic allows the address lines to the memory to be time shared by a number of sources. There are other sources than the two indicated in the drawing but they are not used in computer communications.

Output Register – The Output Register is a 36-bit buffer storage that stores memory words, auto-test responses, or function codes. One memory word is transmitted to the computer by two input request words. The Output Register isolates the memory from the computer input channel.

Output Logic - The Output Logic consists of the disassembly logic gates and the output mode control logic. The disassembly logic converts the 36-bit memory word into two 30-bit input request words. The mode control logic sets the interrupt and input request lines to the computer and generates internal timing signals.

Functions Used in Communications with the Computer. Input/Output units in the MMSC and PDMU are essentially identical

the second and the second second was a second second second

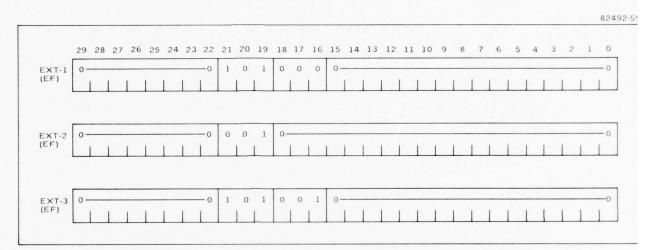

#### FORMAT FOR EXTERNAL FUNCTION WORDS

External function words control memory loading/unloading, initiate auto-tests, set panel indicators in an MMSC, and select the passive display format in the PDMU.

General Description of External Function Word — External function words are sent from the computer to an MMSC or PDMU and used to load and unload the memory, initiate auto-tests, set panel indicators in an MMSC, and define the passive display format in a PDMU. External function words can be sent when the external function request line to the computer is set. Use of the forced external function by the computer may cause loss of the data in the MMSC's or PDMU's Input Register.

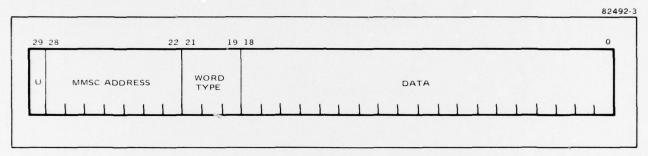

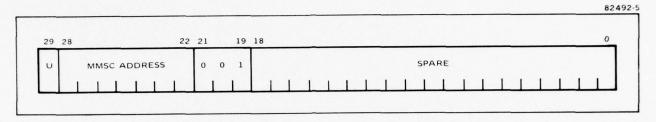

#### General Format of External Function Word

Bits 0 - 18

Bits 19 - 21

Contains auxiliary data which is loaded into bits 0 - 18 of the input register.

Word type – defines the operation to be performed.

|    | Cod | des |       | Definition                                |

|----|-----|-----|-------|-------------------------------------------|

| 21 | 20  | 19  | Octal |                                           |

| 0  | 0   | 0   | 0     | not used                                  |

| 0  | 0   | 1   | 1     | memory load start                         |

| 0  | 1   | 0   | 2     | memory load stop                          |

| 0  | 1   | 1   | 3     | memory unload start                       |

| 1  | 0   | 0   | 4     | memory unload stop                        |

| 1  | 0   | 1   | 5     | indicator (MMSC)<br>passive format (PDMU) |

| 1  | 1   | 0   | 6     | test stimulus                             |

| 1  | 1   | 1   | 7     | not used                                  |

<u>Bit 22-28</u> - These bits are unused in the PDMU. In the MMSC, they specify the console address. The operation defined by the word type will be performed at the console(s) whose corresponsing address bit is set. Any number of address bits may be set simultaneously.

|    | 0 0 0 0 1 0 | Console |    |    |    |    |             |

|----|-------------|---------|----|----|----|----|-------------|

| 28 | 27          | 26      | 25 | 24 | 23 | 22 |             |

| 0  | 0           | 0       | 0  | 0  | 0  | 1  | 1           |

| 0  | 0           | 0       | 0  | 0  | 1  | 0  | 2           |

| 0  | 0           | 0       | 0  | 1  | 0  | 0  | 3           |

| 0  | 0           | 0       | 1  | 0  | 0  | 0  | 4           |

| 0  | 0           | 1       | 0  | 0  | 0  | 0  | 5           |

| 0  | 1           | 0       | 0  | 0  | 0  | 0  | 6           |

| 1  | 0           | 0       | 0  | 0  | 0  | 0  | 7           |

| 1  | 1           | 1       | 1  | 1  | 1  | 1  | 1 through 7 |

Bit 29

unused - may be 1 or 0

Section 1 - Computer/Display System Communications Subsection - Computer Communications to MMSC and PDMU

#### FORMATS FOR MMSC/PDMU MEMORY CONTROL COMMAND WORDS

The MMSC/PDMU Memory Control Command Words consist of the memory load start, memory load stop, memory unload start, and memory unload stop.

Memory Load Start Description - The memory load start command causes the Memory Load FF to become set. With the Memory Load FF set, the MMSC or the PDMU will store output acknowledge words from the computer in its memory.

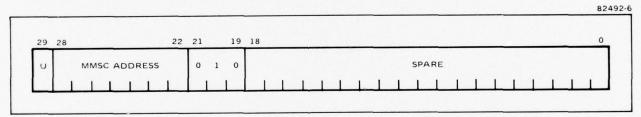

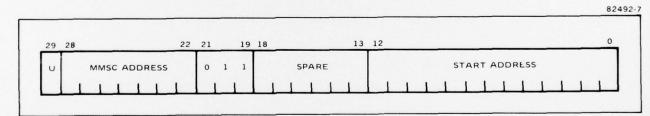

Format of Memory Load Start Word

Memory Load Stop Description - The memory load stop command causes the Memory Load FF to be reset. With the Memory Load FF reset, MMSC or PDMU will not store output acknowledge words in its memory.

Format of Memory Load Stop Word

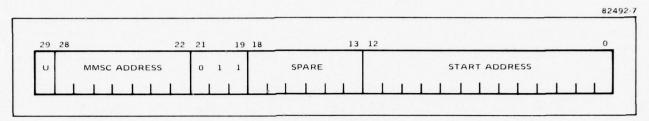

Memory Unload Start Description — The memory unload start command causes bits 0-12 to be loaded into the Output Data Address Counter and the Memory Unload FF to become set. With the Memory Unload FF set the MMSC or PDMU will access the memory address specified by the Output Data Address Counter, disassemble the 36 bit word into two 30 bit words, transmit the two words to the computer as input data request words and then increment the Output Data Address Counter. This process will continue until the Memory Unload FF is reset.

Format of Memory Unload Start Word

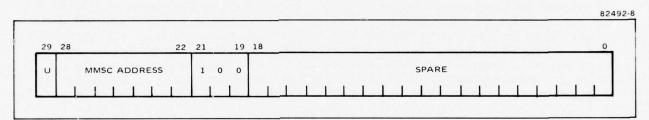

Memory Unload Stop Description - The memory unload stop command causes the Memory Unload FF to be reset. With the Memory Unload FF reset, the MMSC or PDMU will discontinue transmission of input data request words after the current transmission is complete.

Format of Memory Unload Stop Word

Section 1 – Computer/Display System Communications Subsection – Computer Communications to MMSC and PDMU

#### FORMATS FOR MMSC INDICATOR WORD AND PDMU PASSIVE FORMAT WORD

The MMSC Indicator Word and PDMU Passive Format word have the same word type. The Indicator Word is only used when addressing an MMSC while the Passive Format Word is used when addressing a PDMU.

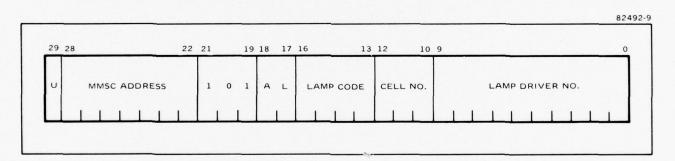

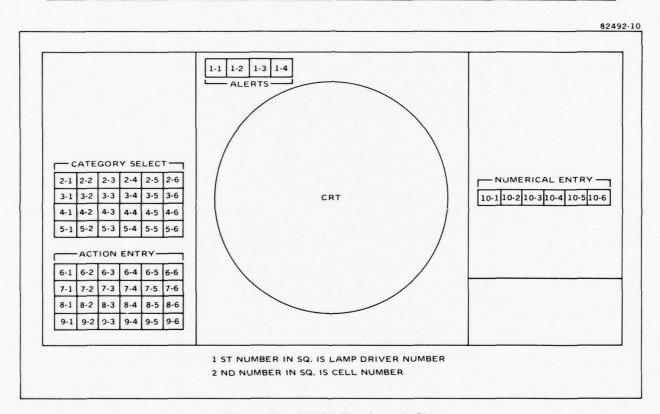

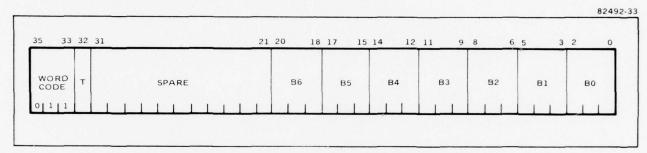

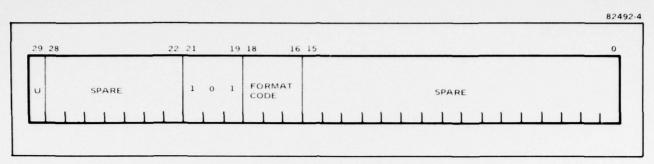

Indicator Word (MMSC Only) — The format of MMSC Indicator words is shown in Figure A. There are 58 rear-projection readout devices in an MMSC each with 12 selectable lamps. Each lamp can display a different message in the readout. The lighting of the 58X12=696 lamps is under computer control via the indicator word. The coding for this information is given in Table I. Once a lamp is lit, it will remain lit until a new indicator word is sent to either blank the readout or change to a new lamp within the readout. The correlation of the readout coding to panel location of the readout is shown in Figure B.

In addition to the 12 selectable labels, the alert readouts have 3 selectable backgrounds. These are indicated as background 1, 2, and blank. When a particular background is selected, all four of the alert readouts will be illuminated or blanked by the selection. To activate the background requires sending an external function indicator word with the desired AL code. No lamp driver no., cell no., or lamp code must be specified as is required to light a particular label on an alert. It is intended that one of the background colors be used as an operational or tactical alert while the other will be used as an equipment fault alert. The codes for selecting the backgrounds are specified in Table II. The alert background must be in the blank state when either background 1 or 2 is initiated to prevent two colors being on simultaneously.

Figure A. Format of MMSC Indicator Words

#### TABLE I. INDICATOR WORD CODING

| Bits 0 - 9   | La                                              | ımp            | Dri           | ver  | Co     | ode    |               |     |      |                 |

|--------------|-------------------------------------------------|----------------|---------------|------|--------|--------|---------------|-----|------|-----------------|

|              | $\frac{9}{0}$ $\frac{8}{0}$                     | 7 0            | <u>6</u>      | 5 5  | 4      | 3      | $\frac{2}{0}$ | 1   | Ω    | Lamp Driver No. |

|              |                                                 |                | $\frac{6}{0}$ |      |        |        |               | 0   | 0    | None            |

|              | 0 0                                             | 0              | 0             |      |        |        | 0             | 0   | 1    | 1               |

|              | 0 0                                             | 0              | 0             |      |        |        | 0             | 1   | 0    | 2               |

|              | 0 0                                             | 0              | 0             |      |        |        | 1             | 0   | 0    | 3               |

|              | 0 0                                             | 0              | 0             |      | 0      |        | 0             | 0   | 0    | 4               |

|              | 0 0                                             | 0              | 0             |      |        |        | 0             | 0   | 0    | 5               |

|              | 0 0                                             | 0              | 0             |      |        |        | 0             | 0   | 0    | 6               |

|              | 0 0                                             | 0              | 1             |      |        |        | 0             | 0   | 0    | 7               |

|              | 0 0                                             | 1              | 0             |      | 0      |        | 0             | 0   | 0    | 8               |

|              | 0 1                                             | 0              | 0             |      | 0      |        | 0             | 0   | 0    | 9<br>10         |

|              | $\begin{array}{ccc} 1 & 0 \\ 1 & 1 \end{array}$ | 1              | 0 1           |      | 1      | 0<br>1 | 0<br>1        | 0   | 0 1  | 1 thru 10       |

| Bits 10 - 12 |                                                 | Ce             | ell N         | Juml | be     | r C    | od            | е   |      |                 |

|              | <u>12</u>                                       | 11             | <u>10</u>     | 0    | cta    | al     |               |     |      |                 |

|              | 0                                               | 0              | 0             |      | 0      |        |               | ne  |      |                 |

|              | 0                                               | 0              | 1             |      | 1      |        | Ce            | ell | 1    |                 |

|              | 0                                               | 1              | 0             |      | 2      |        |               |     | 2    |                 |

|              | 0                                               | 1              | 1             |      | 3      |        |               |     | 3    |                 |

|              | 1                                               | 0              | 0             |      | 4      |        |               |     | 4    |                 |

|              | 1                                               | 0              | 1             |      | 5      |        |               |     | 5    |                 |

|              | 1<br>1                                          | 1<br>1         | 0<br>1        |      | 6      |        | No            | ne  | 6    |                 |

| Bits 13 - 16 |                                                 |                |               | np l |        |        |               |     |      |                 |

|              | 16                                              | 15             | 14            | 13   | 3      | Oc     | tal           |     | Lami | Number          |

|              | $\frac{29}{0}$                                  | $\frac{20}{0}$ | 0             | -0   | 5      | 0      | 0             |     |      | 1               |

|              | 0                                               | 0              | 0             | 1    |        | 0      |               |     |      | 2               |

|              | 0                                               | 0              | 1             | C    |        | 0      |               |     |      | 3               |

|              | 0                                               | 0              | 1             | 1    |        | 0      |               |     | æ    | 4               |

|              | 0                                               | 1              | 0             | 0    | )      | 0      | 4             |     |      | 5               |

|              | 0                                               | 1              | 0             | 1    | L      | 0      | 5             |     |      | 6               |

|              | 0                                               | 1              | 1             | (    | )      | 0      |               |     |      | 7               |

|              | 0                                               | 1              | 1             | 1    |        | 0      |               |     |      | 8               |

|              | 1                                               | 0              | 0             | (    |        | 1      |               |     |      | 9               |

|              | 1                                               | 0              | 0             | 1    |        | 1      |               |     |      | 10              |

|              | 1                                               | 0              | 1             | (    |        | 1      |               |     |      | 11              |

|              |                                                 | -              |               |      |        |        | ^             |     |      | 10              |

|              | 1                                               | 0              | 1             | 1    |        | 1      |               |     |      | 12              |

|              | 1<br>1                                          | 1              | 0             | 0    | )      | 1      | 4             |     | 5 a  | nd 9            |

|              | 1                                               |                |               |      | )<br>L |        | 4<br>5        |     | 5 ar |                 |

the second and the second seco

#### FORMATS FOR MMSC INDICATOR WORD (Continued)

TABLE II.

Bits 17 - 18

(AL) Alert Background Code

| 18 | 17 | Octal | | Octal | | Octal |

Figure B. MMSC Readout Coding

the second of the second second second second

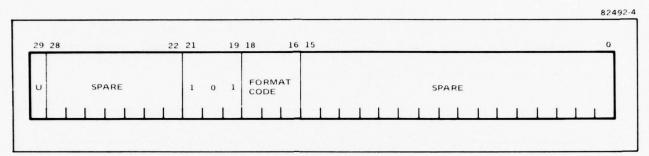

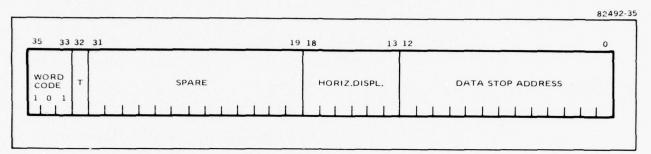

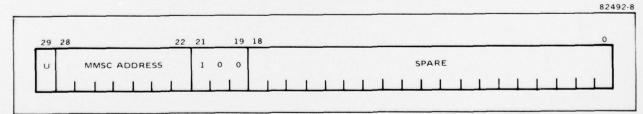

Passive Format Word (PDMU Only) - The passive format word contains the format code which is stored in a register. The format code specifies the number and placement of the data beams on the MMSC display.

Figure C. Coding of the Passive-Format Word to Control MMSC Display of Data Beams

| Format                | Display Parameters*                     |

|-----------------------|-----------------------------------------|

| 18 17 16 <u>Octal</u> |                                         |

| 0 0 0 0               | No Display - I/O Operations Only        |

| 0  0  1  1            | 680 Lines, 144 Beams Full Width         |

| 0 1 0 2               | 340 Lines, 288 Beams Full Width         |

| 0 1 1 3               | 680 Lines, 144 Beams Left Half          |

| 1  0  0  4            | 680 Lines, 72 Beams (1-72) Full Width   |

| 1 0 1 5               | 680 Lines, 72 Beams (73-144) Full Width |

| 1 1 0 6               | 680 Lines, 72 Beams (1-72) Half Width   |

| 1 1 1 7               | 680 Lines, 72 Beams (73-144) Half Width |

<sup>\*</sup>Refer to Section 4 for detailed display information.

Section 1 - Computer/Display System Communications Subsection - Computer Communications to MMSC and PDMU

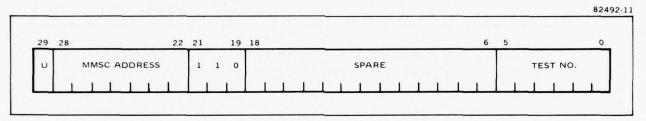

#### FORMAT FOR TEST STIMULUS WORD

The test stimulus word initiates an auto-test specified by the test number in bits 0-5.

The test stimulus word initiates an auto-test. The specific auto-test to be performed is specified by the test number in bits 0-5. The codes for the auto-tests are defined in the table. Use of the test stimulus words to perform auto-testing is described in Diagnostic Programming, Software Memo-Volume II.

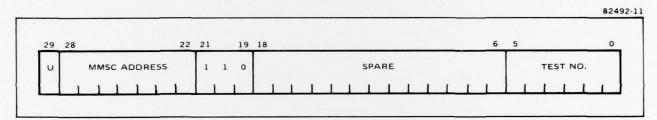

Format of Test Stimulus Word

#### TEST STIMULUS WORD

| Bits $0-5$ | Test Number   |               |                |               |               |   |       |                          |  |  |  |

|------------|---------------|---------------|----------------|---------------|---------------|---|-------|--------------------------|--|--|--|

|            | $\frac{5}{0}$ | 4             | $\frac{3}{0}$  | $\frac{2}{9}$ | $\frac{1}{0}$ | 0 | Octal | Test<br>Auto-Test Unit   |  |  |  |

|            | 0             | $\frac{4}{0}$ | $\overline{0}$ | 0             | 0             | 0 | 00    | Auto-Test Unit           |  |  |  |

|            | 0             | 0             | 0              | 0             | 0             | 1 | 01    | I/O Unit                 |  |  |  |

|            | 0             | 0             | 0              | 0             | 1             | 0 | 02    | I/O Counters             |  |  |  |

|            | 0             | 0             | 0              | 0             | 1             | 1 | 03    | Frame Rate Generator     |  |  |  |

|            | 0             | 0             | 0              | 1             | 0             | 0 | 04    | Spare                    |  |  |  |

|            | 0             | 0             | 0              | 1             | 0             | 1 | 05    | Memory Data Register -   |  |  |  |

|            | 0             | 0             | 0              | 1             | 1             | 0 | 06    | Memory Data Register - : |  |  |  |

|            | 0             | 0             | 0              | 1             | 1             | 1 | 07    | Display Generator        |  |  |  |

|            | 0             | 0             | 1              | 0             | 0             | 0 | 10    | Line Counter             |  |  |  |

|            | 0             | 0             | 1              | 0             | 0             | 1 | 11    | G. P. Counters           |  |  |  |

|            | 0             | 0             | 1              | 0             | 1             | 0 | 12    | Registers                |  |  |  |

|            | 0             | 0             | 1              | 0             | 1             | 1 | 13    | Address Register 1       |  |  |  |

|            | 0             | 0             | 1              | 1             | 0             | 0 | 14    | Address Register 2       |  |  |  |

|            | 0             | 0             | 1              | 1             | 0             | 1 | 15    | Address Register 3       |  |  |  |

|            | 0             | 0             | 1              | 1             | 1             | 0 | 16    | Address Register 4       |  |  |  |

|            | 0             | 0             | 1              | 1             | 1             | 1 | 17    | Address Register 5       |  |  |  |

|            | 0             | 1             | 0              | 0             | 0             | 0 | 20    | Symbol Address Register  |  |  |  |

|            | 0             | 1             | 0              | 0             | 0             | 1 | 21    | Data Stop                |  |  |  |

|            | 0             | 1             | 0              | 0             | 1             | 0 | 22    | Raster Generator         |  |  |  |

|            | 0             | 1             | 0              | 0             | 1             | 1 | 23    | Time Compression         |  |  |  |

|            | 0             | 1             | 0              | 1             | 0             | 0 | 24    | Intensity 1              |  |  |  |

|            | 0             | 1             | 0              | 1             | 0             | 1 | 25    | Intensity 2              |  |  |  |

|            | 0             | 1             | 0              | 1             | 1             | 0 | 26    | Intensity 3              |  |  |  |

|            | 0             | 1             | 0              | 1             | 1             | 1 | 27    | Symbol Generator         |  |  |  |

|            | 0             | 1             | 1              | 0             | 0             | 0 | 30    | Deflection 1             |  |  |  |

|            | 0             | 1             | 1              | 0             | 0             | 1 | 31    | Deflection 2             |  |  |  |

|            | 0             | 1             | 1              | 0             | 1             | 0 | 32    | Display Control          |  |  |  |

|            | 0             | 1             | 1              | 0             | 1             | 1 | 33    | Display Control Counter  |  |  |  |

|            | 0             | 1             | 1              | 1             | 0             | 0 | 34    | Program Control Counter  |  |  |  |

|            | 0             | 1             | 1              | 1             | 0             | 1 | 35    | Spare                    |  |  |  |

|            | 0             | 1             | 1              | 1             | 1             | 0 | 36    | Spare                    |  |  |  |

|            | 0             | 1             | 1              | 1             | 1             | 1 | 37    | Spare                    |  |  |  |

|            | 1             | 1             | 1              | 1             | 1             | 1 | 77    | Auto-Test Unit           |  |  |  |

Section 1 - Computer/Display System Communications Subsection - Computer Communications to MMSC and PDMU

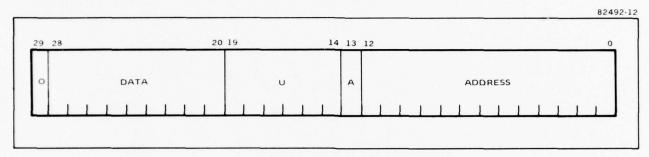

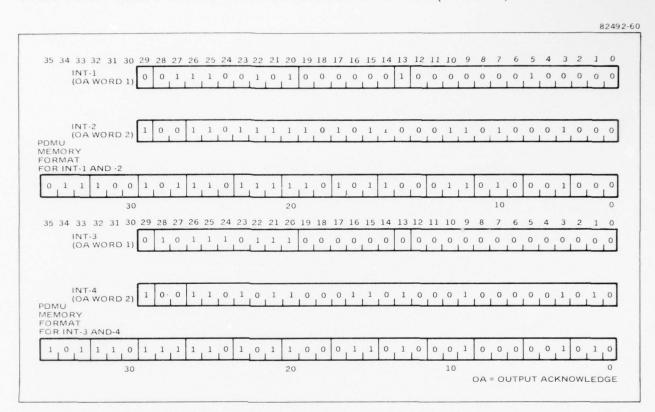

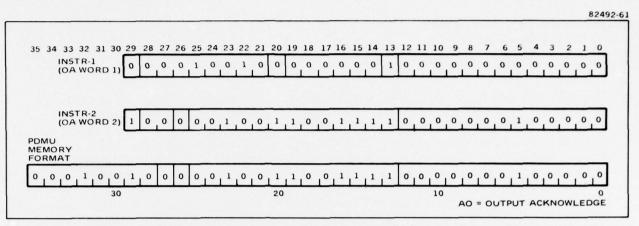

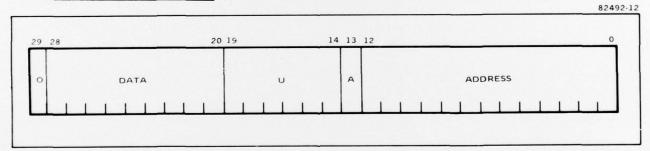

#### FORMAT FOR OUTPUT ACKNOWLEDGE WORDS

Two 30-bit output acknowledge words are used to form one 36-bit MMSC or PDMU memory word.

Output acknowledge words are sent from the computer and used to load the memory and to provide bit patterns for auto-testing. Output acknowledge words consist of two types, designated word 1 and word 2. Successive transmission of word 1 and a word 2 is required to form a 36-bit memory word. The 36-bits obtained from the 2 words are assembled in the Input Register. The Input Register data is then stored in the address specified by the Input Data Address Counter if the memory load FF is set.

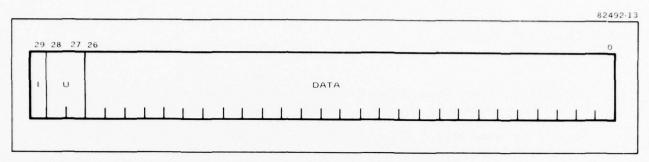

Word 1 of the Output Acknowledge Word Pair

| Contains a 13 bit address which is loaded into bits 0-12 of the Input Data Address Counter when bit 13 is true. |

|-----------------------------------------------------------------------------------------------------------------|

| A = 0, increment the Input Data Address<br>Counter by 1.                                                        |

| A = 1, load bits 0-12 into the Input Data Address Counter.                                                      |

| Unused                                                                                                          |

| Contains data which is loaded into bits 27-35 of the Input Register.                                            |

| Always a 0 to indicate word 1.                                                                                  |

|                                                                                                                 |

Word 2 of the Output Acknowledge Word Pair

Description

Bits 0-26 Contains data which is loaded into bits

0-26 of the Input Register.

Bits 27 - 28 Unused

Bit 29 Always a 1 to indicate word 2.

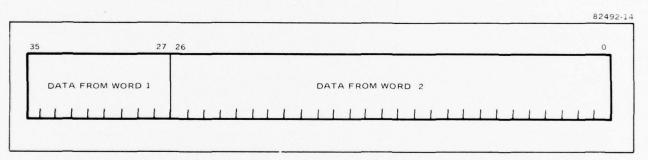

The reception of word 2 and memory load FF set is a command to store the word in the Input Register in the memory location specified by the Input Data Address Counter. The format of the resulting memory word is:

Format of Memory Word

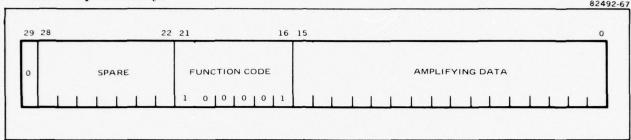

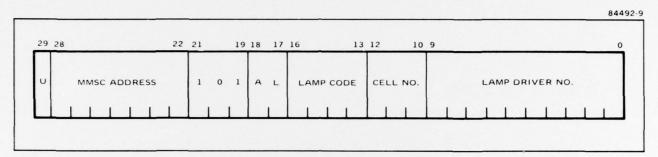

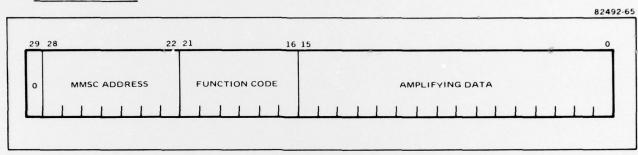

#### COMPUTER NOTIFICATION OF MMSC ACTIONS: INTERRUPT WORD FORMAT

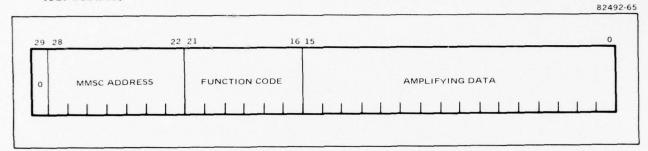

Interrupt words are sent to the computer from an MMSC to notify the computer of actions occurring at a console.

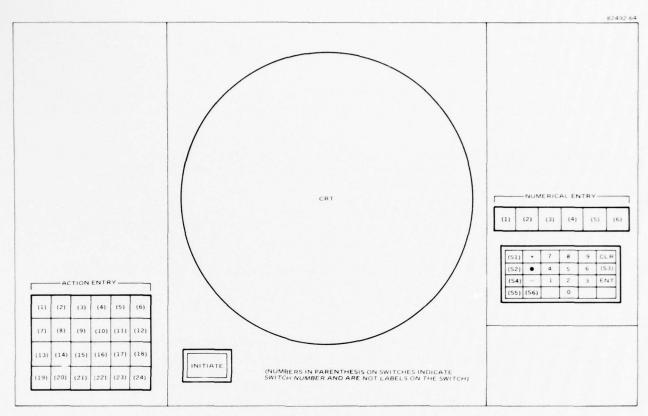

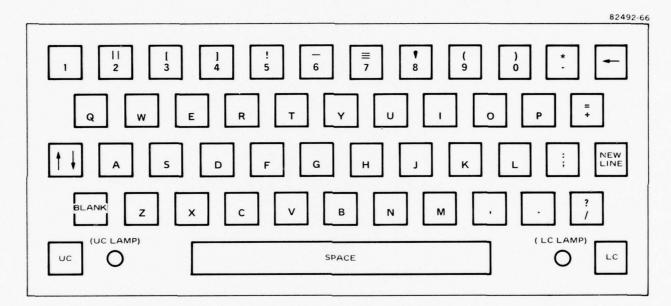

An interrupt will result when an action entry, numerical entry, number entry, keyboard or the initiate pushbutton is depressed. (See facing figure.) Only one interrupt will result from a single depression of a pushbutton. Interrupts will also result when rolling the trackball or when the end of a display frame is reached before all information has been displayed. During auto-testing, the interrupt is used to inform the computer of test results.

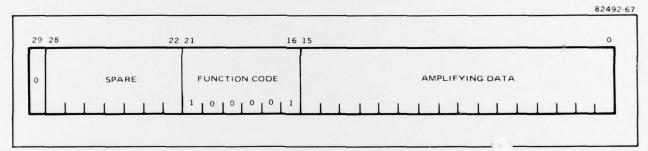

#### General Interrupt Word Format

#### Word Format Description Contains amplifying data used to supple-Bits 0-15 ment the function code Function code - defines the type of inter-Bits 16-21 rupt word. The codes for the functions are defined in the table of the next topic. MMSC address – defines to the computer Bits 22-28 the MMSC which transmitted the interrupt. Only one of the 7 bits will be set. Console Code 28 27 26 25 24 23 22 0 0 0 0 0 0 1 1 0 2 0 0 0 0 1 0 0 0 0 0 0 3 0 1 0 0 0 0 0 0 1 4 0 1 0 0 0 0 5 0 0 0 0 0 6 0 0 0 0 0 0 Always 0 Bit 29

MMSC Front Panel Pushbutton Locations

#### MMSC FUNCTION CODES

Function codes for the Action Entry, Numerical Entry, and Initiate switches, located on the front panel of the MMSC are presented in the table, together with those of the Display Overflow, Auto-Test Response functions, Number Entry, Trackball and Keyboard.

Action Entry – The function codes for the action entry switches are listed in the facing table. The correlation of switch number to panel location of the switch is shown in the figure of the previous topic.

Numerical Entry – The function codes for the numerical entry switches are listed in the facing table. The correlation of switch number to panel location of the switch is shown in the figure on page 1-15.

<u>Initiate</u> - The initiate pushbutton is located in the lower left-hand corner of the CRT panel (see figure in previous topic.) The function code for initiate is listed in the facing table.

<u>Display Overflow</u> - When MMSC reaches the end of its specified display frame before all data has been displayed, an interrupt will occur. The interrupt will be transmitted once each frame until the problem is corrected. The function code for display overflow is listed in the facing table.

Auto-Test Response - In response to an external function test stimulus word, an MMSC will transmit an interrupt word consisting of the function code listed in the facing table and amplifying data A-1 (next topic). The amplifying data A-1 varies with the type of test initiated. This data is specified in Diagnostic Programming, Software Memo-Volume II.

The Number Entry, Trackball, and Keyboard interrupt words all contain amplifying data. These words are presented in the next two topics.

| FIIN | CT | OI | N ( | OI | DES |

|------|----|----|-----|----|-----|

| 101.01.01.000                |   |                         |    |    |    |    |    |       |          |  |  |

|------------------------------|---|-------------------------|----|----|----|----|----|-------|----------|--|--|

| Switch/Action<br>Description |   | Amplifying<br>Code Type |    |    |    |    |    |       |          |  |  |

|                              |   | 21                      | 20 | 19 | 18 | 17 | 16 | Octal |          |  |  |

| Action Entry Switch          | 1 | 0                       | 0  | 0  | 0  | 0  | 1  | 01    | All Zero |  |  |

|                              | 2 | 0                       | 0  | 0  | 0  | 1  | 0  | 02    |          |  |  |

|                              | 3 | 0                       | 0  | 0  | 0  | 1  | 1  | 03    |          |  |  |

|                              | 4 | 0                       | 0  | 0  | 1  | 0  | 0  | 04    |          |  |  |

|                              | 5 | 0                       | 0  | 0  | 1  | 0  | 1  | 05    |          |  |  |

|                              | 6 | 0                       | 0  | 0  | 1  | 1  | 0  | 06    |          |  |  |

|                              | 7 | 0                       | 0  | 0  | 1  | 1  | 1  | 07    |          |  |  |

|                              | 8 | 0                       | 0  | 1  | 0  | 0  | 0  | 10    |          |  |  |

|                              | 9 | 0                       | 0  | 1  | 0  | 0  | 1  | 11    | All Zero |  |  |

|                              |   |                         |    |    |    |    |    |       |          |  |  |

### FUNCTION CODES (Continued)

| Switch/Action<br>Description |    | Amplifying<br>Code Type |    |    |    |    |    |       |          |

|------------------------------|----|-------------------------|----|----|----|----|----|-------|----------|

|                              |    | 21                      | 20 | 19 | 18 | 17 | 16 | Octal |          |

| Action Entry Switch          | 10 | 0                       | 0  | 1  | 0  | 1  | 0  | 12    | All Zero |

|                              | 11 | 0                       | 0  | 1  | 0  | 1  | 1  | 13    |          |

|                              | 12 | 0                       | 0  | 1  | 1  | 0  | 0  | 14    |          |

|                              | 13 | 0                       | 0  | 1  | 1  | 0  | 1  | 15    |          |

|                              | 14 | 0                       | 0  | 1  | 1  | 1  | 0  | 16    |          |

|                              | 15 | 0                       | 0  | 1  | 1  | 1  | 1  | 17    |          |

|                              | 16 | 0                       | 1  | 0  | 0  | 0  | 0  | 20    |          |

|                              | 17 | 0                       | 1  | 0  | 0  | 0  | 1  | 21    |          |

|                              | 18 | 0                       | 1  | 0  | 0  | 1  | 0  | 22    |          |

|                              | 19 | 0                       | 1  | 0  | 0  | 1  | 1  | 23    |          |

|                              | 20 | 0                       | 1  | 0  | 1  | 0  | 0  | 24    |          |

|                              | 21 | 0                       | 1  | 0  | 1  | 0  | 1  | 25    |          |

|                              | 22 | 0                       | 1  | 0  | 1  | 1  | 0  | 26    |          |

|                              | 23 | 0                       | 1  | 0  | 1  | 1  | 1  | 27    |          |

|                              | 24 | 0                       | 1  | 1  | 0  | 0  | 0  | 30    |          |

| Numerical Entry              | 1  | 0                       | 1  | 1  | ō  | 0  | 1  | 31    |          |

| Switch                       | 2  | 0                       | 1  | 1  | 0  | 1  | 0  | 32    |          |

|                              | 3  | 0                       | 1  | 1  | 0  | 1  | 1  | 33    |          |

|                              | 4  | 0                       | 1  | 1  | 1  | 0  | 0  | 34    |          |

|                              | 5  | 0                       | 1  | 1  | 1  | 0  | 1  | 35    |          |

|                              | 6  | 0                       | 1  | 1  | 1  | 1  | 0  | 36    |          |

| Initiate                     |    | 0                       | 1  | 1  | 1  | 1  | 1  | 37    | •        |

| Display Overflow             |    | 1                       | 0  | 0  | 0  | 0  | 0  | 40    | All Zero |

| Auto-Test Response           |    | 1                       | 0  | 0  | 0  | 0  | 1  | 41    | A-1      |

| Number Entry                 |    | 1                       | 0  | 1  | 0  | 0  | 0  | 50    | A-2      |

| Trackball                    |    | 1                       | 1  | 0  | 0  | 0  | 0  | 60    | A-3      |

| Keyboard                     |    | 1                       | 1  | 1  | 0  | 0  | 0  | 70    | A-4      |

#### AMPLIFYING DATA FOR THE NUMBER ENTRY AND TRACKBALL INTERRUPT

A list of the amplifying data for the Number Entry Panel and Trackball are tabulated and described.

Number Entry Panel — The interrupt word for switches on the number entry panel consists of a fixed function code plus amplifying data A-2 which depends on the specific button pushed on the number entry panel. The function code is listed in the table of the previous topic. The amplifying data A-2 is specified in the facing table. The correlation of pushbutton symbol to panel location of the pushbutton is shown in the figure on page 1-15.

<u>Trackball</u> – Trackball increments are transmitted to the computer by interrupt once each frame if the increment counters are detected to be non-zero. The interrupt word consists of a fixed function code plus amplifying data A-3 which specifies the  $\Delta X$  and  $\Delta Y$  increments. The  $\Delta X$  and  $\Delta Y$  increments represent the circumferential distance in X and Y that the surface of the trackball has been displaced since the last frame. If the trackball is being rotated at a high speed such that the increment counters reach all ones, the counters will remain in the all ones state until the increments are sent to the computer. The counters are then reset to begin the next accumulation. This allows the display system to follow maximum ball rate movements of 23.1 in/sec when in the 35 frame per second mode and 33 in/sec when in the 50 frames per second mode. This corresponds to CRT movement of the trackball of 8.4 in/sec and 12 in/sec respectively in X and Y when maximum resolution is utilized. The function code for the trackball word is listed in the table of the previous topic. The format for the amplifying data is specified in the facing table.

#### AMPLIFYING DATA CODES

| Code Description |            |    |             |    | Int | errı | ipt ' | Wo: | rd | Bit | s |   |     |     |   |   |   |       |

|------------------|------------|----|-------------|----|-----|------|-------|-----|----|-----|---|---|-----|-----|---|---|---|-------|

|                  |            | 15 | 14          | 13 | 12  | 11   | 10    | 9   | 8  | 7   | 6 | 5 | 4   | 3   | 2 | 1 | 0 |       |

| A-1 (Auto-Test)  |            |    | erns<br>mmi |    |     |      |       |     |    |     |   |   | gno | sti | с |   |   |       |

| A-2 (Number En   | try)       |    |             |    |     |      |       |     |    |     |   |   |     |     |   |   | ( | Octal |

| Spare Switch     | S1         | 0  | 0           | 0  | 0   | 0    | 0     | 0   | 0  | 0   | 0 | 1 | 0   | 0   | 0 | 0 | 1 | 41    |

|                  | <b>S</b> 2 |    | 1           |    |     | 1    |       |     | 1  | 1   | 1 | 1 | 0   | 0   | 0 | 1 | 0 | 42    |

|                  | S3         |    |             |    |     |      |       |     |    |     |   | 1 | 0   | 0   | 0 | 1 | 1 | 43    |

|                  | S4         |    |             |    |     |      |       |     |    |     |   | 1 | 0   | 0   | 1 | 0 | 0 | 44    |

|                  | <b>S</b> 5 |    |             |    |     |      |       |     |    |     |   | 1 | 0   | 0   | 1 | 0 | 1 | 45    |

|                  | S6         | 0  | 0           | 0  | 0   | 0    | 0     | ò   | 0  | 0   | 0 | 1 | 0   | 0   | 1 | 1 | 0 | 46    |

#### AMPLIFYING DATA CODES (Continued)

| Code Description Interrupt Word Bits |           |       |           |    |    |    |              |   |      |          |          |                 |            |    |    |            |       |

|--------------------------------------|-----------|-------|-----------|----|----|----|--------------|---|------|----------|----------|-----------------|------------|----|----|------------|-------|

|                                      | <u>15</u> | 14    | <u>13</u> | 12 | 11 | 10 | 9            | 8 | 7    | <u>6</u> | <u>5</u> | $\underline{4}$ | 3          | 2  | 1  | 0          | Octal |

| Enter                                | 0         | 0     | 0         | 0  | 0  | 0  | 0            | 0 | 0    | 0        | 1        | 0               | 1          | 0  | 0  | 0          | 50    |

| Clear                                |           |       |           |    |    |    |              |   |      |          | 1        | 0               | 1          | 0  | 0  | 1          | 51    |

| Plus                                 |           |       |           |    |    |    |              |   |      |          | 1        | 0               | 1          | 0  | 1  | 1          | 53    |

| Minus                                |           |       |           |    |    |    |              |   |      |          | 1        | 0               | 1          | 1  | 0  | 1          | 55    |

| Decimal Point                        |           |       |           |    |    |    |              |   |      |          | 1        | 0               | 1          | 1  | 1  | 0          | 56    |

| 0                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 0  | 0  | 0          | 60    |

| 1                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 0  | 0  | 1          | 61    |

| 2                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 0  | 1  | 0          | 62    |

| 3                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 0  | 1  | 1          | 63    |

| 4                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 1  | 0  | 0          | 64    |

| 5                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 1  | 0  | 1          | 65    |

| 6                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 1  | 1  | 0          | 66    |

| 7                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 0          | 1  | 1  | 1          | 67    |

| 8                                    |           |       |           |    |    |    |              |   |      |          | 1        | 1               | 1          | 0  | 0  | 0          | 70    |

| 9                                    |           |       |           |    |    |    | 0            | 0 | 0    | 0        | 1        | 1               | 1          | 0  | 0  | 1          | 71    |

| A-3 (Trackball)                      | 0         | 0     | 0         | 0  | 0  | 0  | $\mathbf{S}$ | M |      |          |          |                 |            |    | Μ  |            |       |

|                                      |           |       |           |    |    |    | У            |   | 3 y2 | y1       | y0       | X               | <b>x</b> 3 | x2 | x1 | <b>x</b> 0 |       |

|                                      | S         | = Sig |           |    |    |    |              |   |      |          |          |                 |            |    |    |            |       |

| "1" = - Direction                    |           |       |           |    |    |    |              |   |      |          |          |                 |            |    |    |            |       |

| M = Magnitude                        |           |       |           |    |    |    |              |   |      |          |          |                 |            |    |    |            |       |

| $M_0 = 1 = 0.044 \text{ in.} *$      |           |       |           |    |    |    |              |   |      |          |          |                 |            |    |    |            |       |

$M_1 = 1 = 0.088$  in.

$M_2 = 1 = 0.176$  in.

$M_3 = 1 = 0.352$  in.

\*Inches of ball surface movement.

#### AMPLIFYING DATA FOR THE KEYBOARD INTERRUPT WORD

The amplifying data for the interrupt word of switches on the keyboard panel, located on the bullnose of the MMSC console, are listed and described.

The interrupt word for switches on the keyboard panel consists of a fixed function code plus amplifying data A-4 (see facing table) which depends on the specific button pushed on the keyboard. The function code is listed in the table on 1-16. The correlation of pushbutton symbol to pushbutton location on the keyboard is shown in the figure below. It should be noted that the upper/lower case selection is controlled by the two switches on the keyboard labeled UC and LC. The lamp adjacent to each switch determines which switch is activated. Activating one switch automatically resets the other.

Console Keyboard Panel

#### AMPLIFYING DATA CODES (Continued)

| Co | de Description        |           |           |           |           | Inte | erru      | ipt ' | Wo | rd | Bits | 5 |   |   |   |   |   |       |

|----|-----------------------|-----------|-----------|-----------|-----------|------|-----------|-------|----|----|------|---|---|---|---|---|---|-------|

| Α- | 4 (Keyboard)          | <u>15</u> | <u>14</u> | <u>13</u> | <u>12</u> | 11   | <u>10</u> | 9     | 8  | 7  | 6    | 5 | 4 | 3 | 2 | 1 | 0 | Octal |

| *  | (Down 1 line) (LC)    | 0         | 0         | 0         | 0         | 0    | 0         | 0     | 0  | 0  | 0    | 0 | 0 | 1 | 0 | 1 | 0 | 012   |

|    | New Line              | 1         | 1         | 1         | 1         | 1    | 1         | 1     |    | 1  | 1    | 0 | 0 | 1 | 1 | 0 | 1 | 015   |

|    | Space                 |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 0 | 0 | 0 | 0 | 040   |

| +  | (Plus)                |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 1 | 0 | 1 | 1 | 053   |

| ,  | (Comma)               |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 1 | 1 | 1 | 1 | 054   |

| -  | (Minus)               |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 1 | 1 | 0 | 1 | 055   |

|    | (Period - Dec. Point) |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 1 | 1 | 1 | 0 | 056   |

| /  | (Slash)               |           |           |           |           |      |           |       |    |    |      | 1 | 0 | 1 | 1 | 1 | 1 | 057   |

| Ø  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 0 | 0 | 0 | 060   |

| 1  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 0 | 0 | 1 | 061   |

| 2  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 0 | 1 | 0 | 062   |

| 3  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 0 | 1 | 1 | 063   |

| 4  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 1 | 0 | 0 | 064   |

| 5  |                       |           |           |           |           |      |           |       |    | 1  |      | 1 | 1 | 0 | 1 | 0 | 1 | 065   |

| 6  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 1 | 1 | 0 | 066   |

| 7  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 0 | 1 | 1 | 1 | 067   |

| 8  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 1 | 0 | 0 | 0 | 070   |

| 9  |                       |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 1 | 0 | 0 | 1 | 071   |

| ;  | (Semi-colon)          |           |           |           |           |      |           |       |    |    |      | 1 | 1 | 1 | 0 | 1 | 1 | 073   |

|    | Blank                 |           |           |           |           |      |           |       |    |    | 0    | 1 | 1 | 1 | 1 | 1 | 1 | 077   |

| A  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 0 | 0 | 1 | 101   |

| В  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 0 | 1 | 0 | 102   |

| C  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 0 | 1 | 1 | 103   |

| D  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 1 | 0 | 0 | 104   |

| E  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 1 | 0 | 1 | 105   |

| F  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 |   | 0 |   | 1 | 0 | 106   |

| G  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 0 | 1 | 1 | 1 | 107   |

| Н  |                       |           |           |           |           |      |           |       |    | 1  | 1    | 0 |   |   | 0 | 0 | 0 | 110   |

| I  |                       |           |           |           |           |      |           |       |    |    | 1    |   | 0 |   | 0 |   | 1 | 111   |

| J  |                       |           |           |           |           |      |           |       |    |    | 1    | 0 | 0 | 1 | 0 | 1 | 0 | 112   |

| K  |                       | 0         | 0         | 0         | 0         | 0    | 0         | 0     | 0  | 0  | 1    | 0 | 0 | 1 | 0 | 1 | 1 | 113   |

## AMPLIFYING DATA FOR THE KEYBOARD INTERRUPT WORD (Continued)

#### AMPLIFYING DATA CODES (Continued)

| Code Description   |           |           |           |           | Inte | rru       | pt \ | Vor | d l | Bits | 3 |   |   |   |   |   |             |

|--------------------|-----------|-----------|-----------|-----------|------|-----------|------|-----|-----|------|---|---|---|---|---|---|-------------|

| A-4 (Continued)    | <u>15</u> | <u>14</u> | <u>13</u> | <u>12</u> | 11   | <u>10</u> | 9    | 8   | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0 | Octa        |

| L                  | 0         | 0         | 0         | 0         | 0    | 0         | 0    | 0   | 0   | 1    | 0 | 0 | 1 | 1 | 0 | 0 | 114         |

| M                  |           | 1         | 1         | 1         | 1    | 1         | 1    | 1   | 1   | 1    | 0 | 0 | 1 | 1 | 0 | 1 | 115         |

| N                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 0 | 1 | 1 | 1 | 0 | <b>11</b> 6 |

| O                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 0 | 1 | 1 | 1 | 1 | 117         |

| P                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 0 | 0 | 0 | 120         |

| Q                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 0 | 0 | 1 | 121         |

| R                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 0 | 1 | 0 | 122         |

| S                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 0 | 1 | 1 | 123         |

| T                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 1 | 0 | 0 | 124         |

| U                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 1 | 0 | 1 | 125         |

| V                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 1 | 1 | 0 | 126         |

| W                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 0 | 1 | 1 | 1 | 127         |

| X                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 1 | 0 | 0 | 0 | 130         |

| Y                  |           |           |           |           |      |           |      |     |     | 1    | 0 | 1 | 1 | 0 | 0 | 1 | 131         |

| Z                  |           |           |           |           |      |           |      |     | -   | 1    | 0 | 1 | 1 | 0 | 1 | 0 | 132         |

| ← (Back Space)     |           |           |           |           |      |           |      |     | 0   | 1    | 0 | 1 | 1 | 1 | 1 | 1 | 137         |

| (Up 1 Line (UC)    |           |           |           |           |      |           |      |     | 1   | 0    | 0 | 0 | 1 | 0 | 1 | 0 | 212         |

| = (Equal)          |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 0 | 1 | 0 | 1 | 1 | 253         |

| * (Asterisk)       |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 0 | 1 | 1 | 0 | 1 | 255         |

| ? (Question Mark)  |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 0 | 1 | 1 | 1 | 1 | 257         |

| ) (Right Paren)    |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 0 | 0 | 0 | 260         |

| " (Quotation Mark) |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 0 | 1 | 0 | 262         |

| [ (Left Bracket)   |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 0 | 1 | 1 | 263         |

| [] (Right Bracket) |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 1 | 0 | 0 | 264         |

| ! (Exclamation)    |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 1 | 0 | 1 | 265         |

| _ (Underline)      |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 1 | 1 | 0 | 266         |

| ≡ (Equivalence)    |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 0 | 1 | 1 | 1 | 267         |

| ' (Apostrophe)     |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 1 | 0 | 0 | 0 | 270         |

| ( (Left Paren)     |           |           |           |           |      |           |      |     | 1   | 0    | 1 | 1 | 1 | 0 | 0 | 1 | 271         |

| : (Colon)          | 0         | 0         | 0         | 0         | 0    | 0         | 0    | 0   | 1   | 0    | 1 | 1 | 1 | 0 | 1 | 1 | 272         |

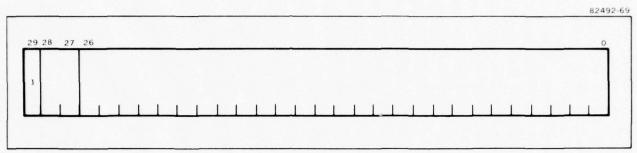

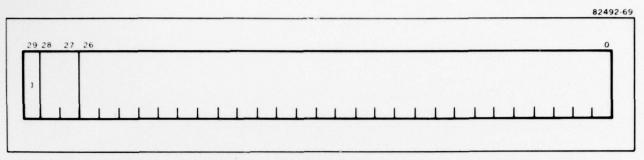

#### COMPUTER NOTIFICATION OF PDMU ACTIONS: INTERRUPT WORDS

The interrupt word for Auto-Test Response, which is the only one that is sent to the computer from a PDMU, is formatted and described.

<u>Auto-Test Response</u> - Interrupt words are sent to the computer from a PDMU with auto-test responses only.

#### Interrupt Word Format

#### Description

| Bits | 0  | <del>- 15</del> |  |

|------|----|-----------------|--|

| Bits | 16 | -21             |  |

| Bits | 22 | - 28            |  |

| Bit  | 29 |                 |  |

Contains auto-test responses

Function code is always the auto-test code 41

Spare

Always a 0.

#### USE OF MMSC IN COMPUTER TO PDMU COMMUNICATIONS

The MMSC operator specifies passive display format parameters via the computer.

There is no electrical connection for direct MMSC to PDMU communication. The system computer must contain as part of its program, routines to convert console action entry, numerical entry and/or keyboard interrupts into PDMU format external function words. Since the computer controls PDMU operations, other input devices connected to it such as typewriters, keysets, etc. could also be utilized to specify passive display formats. When a PDMU drives several consoles, all with passive display selected, will observe the same passive display data and in the same format.

The PDMU contains no operator panels, only a maintenance panel and a power panel. By placing the PDMU off-line from the computer the maintenance panel may be used to simulate any computer word or message.

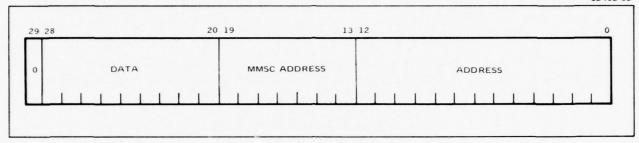

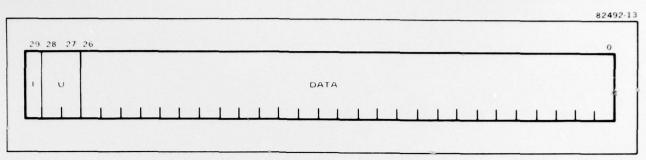

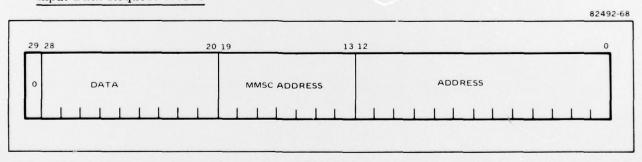

#### DATA WORDS TO COMPUTER FROM MMSC OR PDMU: INPUT DATA REQUEST WORDS

Input data request words are sent to the computer from an MMSC or a PDMU during a memory unload process and during certain auto-tests.

A memory word consisting of 36 bits is loaded into the Output Register and then disassembled into two 30 bit words to be transmitted to the computer as word types 1 and 2. Input data request words result only from either a memory unload command or certain auto-test commands from the computer.

Word 1 Format

Bits 0-12

Data address — contains the contents of the Output Data Address Counter. During memory unload this address is the memory address from which the current data word being transmitted was extracted.

Bits 13 - 19

These bits are all zeros for the PDMU. In the MMSC, they contain the address of the MMSC transmitting the input data request word.

|    |    | (  | Code | е  |    |    | Console |

|----|----|----|------|----|----|----|---------|

| 19 | 18 | 17 | 16   | 15 | 14 | 13 |         |

| 0  | 0  | 0  | 0    | 0  | 0  | 1  | 1       |

| 0  | 0  | 0  | 0    | 0  | 1  | 0  | 2       |

| 0  | 0  | 0  | 0    | 1  | 0  | 0  | 3       |

| 0  | 0  | 0  | 1    | 0  | 0  | 0  | 4       |

| 0  | 0  | 1  | 0    | 0  | 0  | 0  | 5       |

| 0  | 1  | 0  | 0    | 0  | 0  | 0  | 6       |

| 1  | 0  | 0  | 0    | 0  | 0  | 0  | 7       |

Bits 20 - 28

Contains the data stored in bits 27-35 of the memory word being transmitted.

Bit 29

Always a 0 to indicate word 1.

Word 2 Format

Bits 0-26

Bits 27 - 28

Bit 29

Contains the data stored in bits 0-26 of the memory word being transmitted.

May be "0"s or "1"s should be ignored.

Always a 1 to indicate word 2. Input data request words are always transmitted in pairs with word 2 always transmitted following word 1. In the case of the MMSC, word 2 will always be transmitted from the same MMSC as the previously transmitted word 1. This eliminates any ambiguities when more than two consoles are commanded to unload their memories.

# $\begin{array}{c} {\rm SEC\,TION\,\,2} \\ {\rm MEMORY\,\,ALLOCATIONS} \end{array}$

| MMSC and PDMU Memory Allocations |  | .0 |

|----------------------------------|--|----|

|----------------------------------|--|----|

#### MMSC AND PDMU MEMORY ALLOCATIONS

The MMSC memory is partitioned into three storage blocks and the PDMU memory is partitioned into two storage blocks, with allocations as defined below.

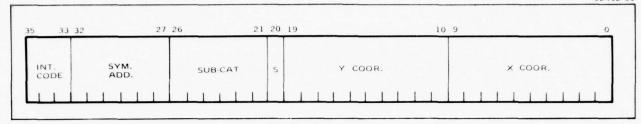

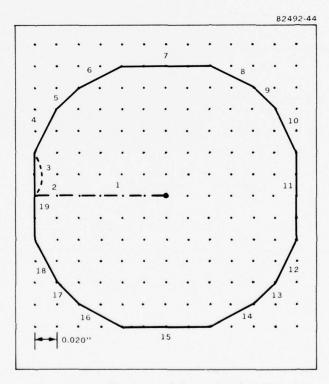

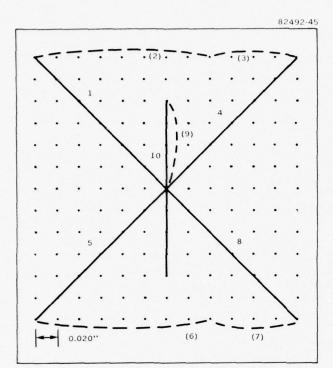

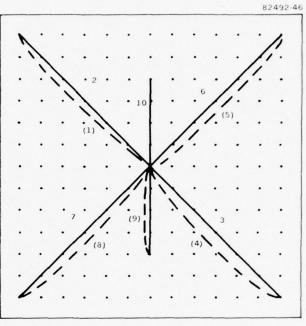

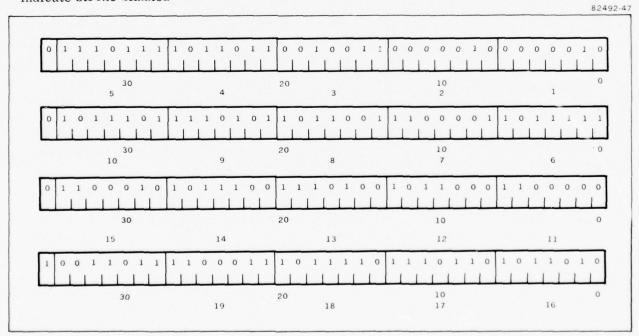

MMSC Memory Allocations – The MMSC memory (see Table I) is partitioned into three blocks for storage of the various types of MMSC memory words. The MMSC instruction words, are stored in octal locations 00000 through 00377. Symbol code words and line words (for lines-type II) are stored in the last 1024 locations 16000 through 17777. Position, line and alphanumeric words may be stored at any location in memory not in use for an instruction word or a symbol code word. Normally, these words will be stored between the instruction word store and the symbol code store, i.e., 00400 through 15777.

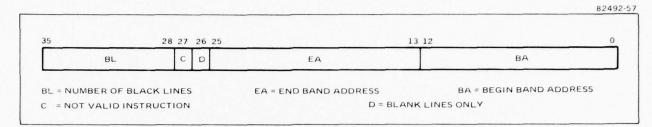

PDMU Memory Allocations – The PDMU memory (see Table II) is partitioned into two sections: instruction word store and intensity word store. The first 32 locations, octal 00000 through 00037, are for storage of instruction words only. The remainder of the PDMU memory is for storage of passive sonar display intensity words.

If the MMSC or PDMU memory is being used as a bulk storage device, there are no restrictions as to the placement of data. In this case, all memory locations are available for storage of data.

TABLE I. MMSC MEMORY MAP

| 00000<br><del> </del><br>00377 | instruction words                         |

|--------------------------------|-------------------------------------------|

| 00400<br>↓ 15777               | position, line,<br>and alphanumeric words |

| 16000<br><del>†</del><br>17777 | symbol code words                         |

TABLE II. PDMU MEMORY MAP

| 00000<br><del> </del><br>00037 | instruction words               |

|--------------------------------|---------------------------------|

| 00040                          | passive display intensity words |

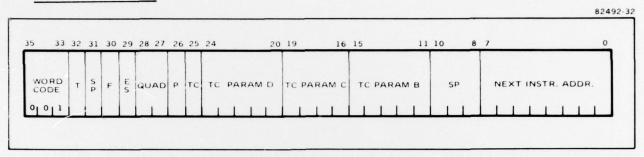

## SECTION 3 MMSC PROGRAMMING

| General Description of the Multi-Mode Sonar Console Display Program :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-0                      |

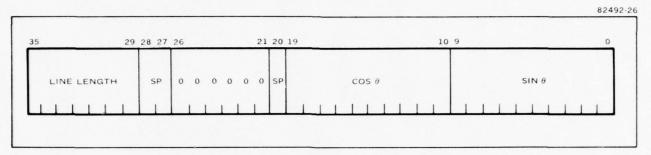

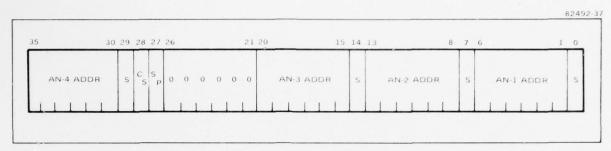

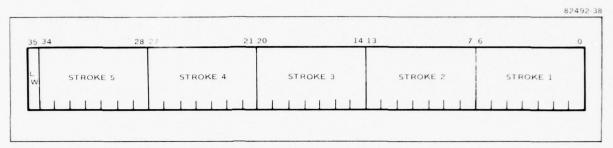

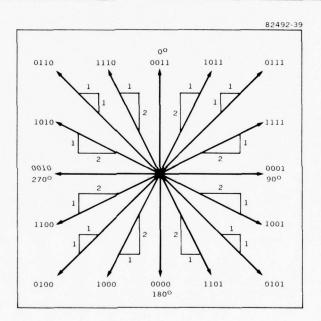

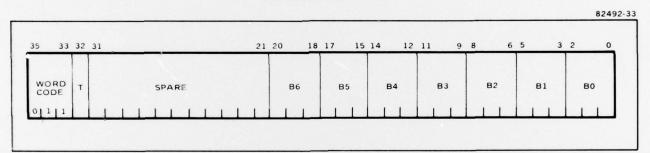

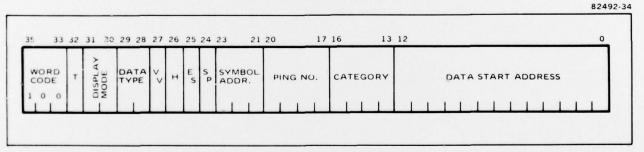

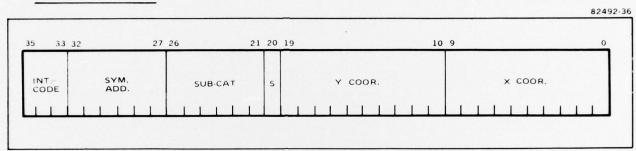

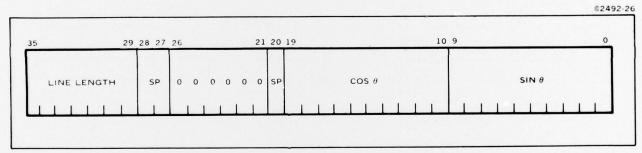

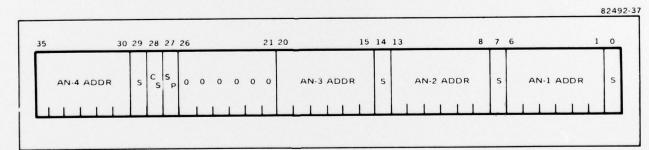

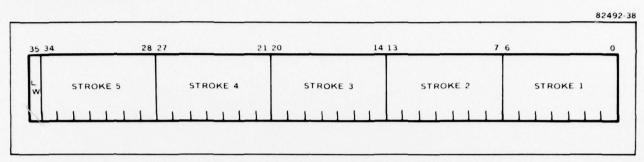

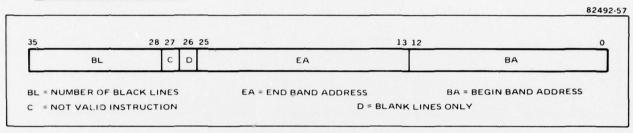

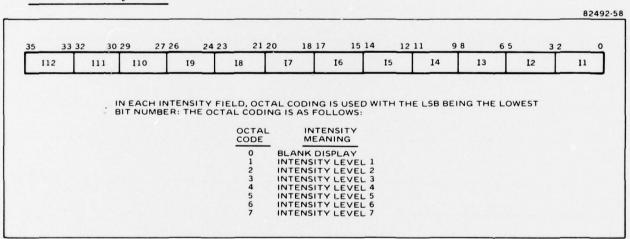

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|