AD-A010 478

IMPROVED MTI RADAR SIGNAL PROCESSOR

W. H. Drury

Massachusetts Institute of Technology

Prepared for:

Federal Aviation Administration

3 April 1975

**DISTRIBUTED BY:**

| . Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                | 2. Government Accession Ne.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3. Recipient's Catalog No.                                                                                                                                                                                                                                                             |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| FAA-RD-74-185                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AD-A010 47                                                                                                                                                                                                                                                                             | 8           |

| Title end Subtitle                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5. Report Date<br>3 April 1975                                                                                                                                                                                                                                                         |             |

| Improved MTI Radar Signal Processor                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6. Performing Organization Code                                                                                                                                                                                                                                                        |             |

| Author(s)                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8. Performing Organization Report No.                                                                                                                                                                                                                                                  | <del></del> |

| W.H. Drury                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ATC-39                                                                                                                                                                                                                                                                                 |             |

| Performing Organization Nome and A                                                                                                                                                                                                                                                                                                                                                                                                          | ddress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10. Work Unit No. (TRAIS)                                                                                                                                                                                                                                                              |             |

| Massachusetts Institute of 7                                                                                                                                                                                                                                                                                                                                                                                                                | Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ······································                                                                                                                                                                                                                                                 |             |

| Lincoln Laboratory<br>P. O. Box 73                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11. Contract or Grant No.<br>IAG-DOT-FA72WAI-242                                                                                                                                                                                                                                       |             |

| Lexington, Massachusetts                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13. Type of Report and Period Covered                                                                                                                                                                                                                                                  |             |

| Sponsoring Agency Name and Addres                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |             |

| Department of Transportation<br>Federal Aviation Administra                                                                                                                                                                                                                                                                                                                                                                                 | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Project Keport                                                                                                                                                                                                                                                                         |             |

| Systems Research and Deve<br>Washington, D.C. 20591                                                                                                                                                                                                                                                                                                                                                                                         | lopment Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14. Sponsoring Agency Code                                                                                                                                                                                                                                                             |             |

| Supplementary Notes                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L                                                                                                                                                                                                                                                                                      |             |

| This work was performed at<br>of Technology under Air For                                                                                                                                                                                                                                                                                                                                                                                   | t Lincolu Laboratory, a center for res<br>rce Contract F19628-73-C-0002.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | earch operated by Massachusetts Institute                                                                                                                                                                                                                                              |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |             |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter a<br>provides discrimination aga<br>into different Doppler frequ                                                                                                                                                                                                                       | otive thresholds. This combination of<br>er present ASR's and is within 2 dB of<br>ed to allow detection of any target trav-<br>return in the occupied range/azimuth c<br>hinst weather clutter if the returns fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall                                          |             |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter n<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq                                                                                                                                                                                            | blished by combining a 3-pulse cancell<br>otive thresholds. This combination of<br>er present ASR's and is within 2 dB of<br>ed to allow detection of any target trav-<br>return in the occupied range/azimuth c<br>tinst weather clutter if the returns from<br>ency regions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. |             |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter a<br>provides discrimination aga<br>into different Doppler frequ                                                                                                                                                                                                                       | ASR)       18. Distribution         18. Distribution       10. Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. |             |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter r<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq<br>The output from this eq<br>Key Words<br>Aimport Surveillance Radar<br>Radar<br>MTI<br>Clutter<br>Dopple: Processing                                                                     | Alished by combining a 3-pulse cancell         bitve thresholds. This combination of         per present ASR's and is within 2 dB of         ed to allow detection of any target trav.         return in the occupied range/azimuth c         inst weather clutter if the returns from         ency regions.         pulpment is digital hit reports for transmost         (ASR)         Docu         the N         Sprin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. |             |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter r<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq<br>The output from this eq<br>Key Words<br>Aimport Surveillance Radar<br>Radar<br>MTI<br>Clutter<br>Dopple: Processing                                                                     | ASR)       18. Distribution         18. Distribution       10. Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. | 5           |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter n<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq<br>The output from this eq<br>The output from this eq<br>Airport Surveillance Radar<br>Radar<br>MTI<br>Clutter<br>Dopple: Processing<br>Security Clessif. (of this report)<br>Unclassified | a)       20.         b)       20.         b)       20.         b)       20.         b)       20.         b)       20.         b)       21.         b)       22.         b)       22.         b)       22.         c)       23.         c)       24.         c)       25.         c)       25.         c)       25.         c)       25.         c)       25. <td< td=""><td>er with an 8-point, weighted, discrete<br/>circuits provides a 20-dB increase in<br/>optimum processing results. An<br/>eling tangentially if its return exceeds<br/>ell. The spectral processing technique<br/>m weather and from the target fall<br/>smittal to the ARTS-III IOP computer.</td><td>5</td></td<> | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. | 5           |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter n<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq<br>The output from this eq<br>Key Words<br>Aimort Surveillance Radar<br>Radar<br>MTI<br>Clutter<br>Dopple: Processing<br>Security Clessif. (of this report)                                | Alished by combining a 3-pulse cancell         bitve thresholds. This combination of         per present ASR's and is within 2 dB of         ed to allow detection of any target trav.         return in the occupied range/azimuth c         inst weather clutter if the returns from         ency regions.         puipment is digital hit reports for transmost         (ASR)         18. Distribution         Sprin         20. Security Classif. (of this page)         Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. | 5           |

| spectral processing accomp<br>Fourier transform and adap<br>MTI improvement factor ov<br>auxiliary channel is provide<br>the level of ground clutter n<br>provides discrimination aga<br>into different Doppler frequ<br>The output from this eq<br>The output from this eq<br>Aimort Surveillance Radar<br>Radar<br>MTI<br>Clutter<br>Dopple: Processing<br>Security Clessif. (of this report)<br>Unclassified                             | Alished by combining a 3-pulse cancell         bitve thresholds. This combination of         per present ASR's and is within 2 dB of         ed to allow detection of any target trav.         return in the occupied range/azimuth c         inst weather clutter if the returns from         ency regions.         puipment is digital hit reports for transmost         (ASR)         18. Distribution         Sprin         20. Security Classif. (of this page)         Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er with an 8-point, weighted, discrete<br>circuits provides a 20-dB increase in<br>optimum processing results. An<br>eling tangentially if its return exceeds<br>ell. The spectral processing technique<br>m weather and from the target fall<br>smittal to the ARTS-III IOP computer. | 5           |

## TABLE OF CONTENTS

ateria di

the second second second

....Act

| I.    | INTRODUCTION |                                                 |    |

|-------|--------------|-------------------------------------------------|----|

| II.   | BLC          | OCK DIAGRAM DISCUSSION                          | 2  |

|       | А.           | Timing                                          | 2  |

|       | в.           | Input Processing                                | 2  |

|       | c.           | Saturation Detector and Interference Eliminator | 4  |

|       | D.           | Three-Pulse Canceller                           | 5  |

|       | E.           | Zero Velocity Filter                            | 5  |

|       | F.           | Discrete Fourier Transform                      | 6  |

|       | G.           | Weighting and Magnituding                       | 6  |

|       | H.           | Thresholds                                      | 7  |

|       | Ι.           | Output Interface                                | 7  |

|       | J.           | MTI Weather Video Output                        | 8  |

|       | к.           | Auxiliary Memory                                | 8  |

| ш.    | TIN          | AING                                            | 11 |

|       | Α.           | PRF Generation - Theory                         | 11 |

|       | в.           | PRF Generation - Details                        | 13 |

|       | C.           | Signals that Repeat at the PRF                  | 15 |

|       | D.           | Fast Timing                                     | 17 |

|       | E.           | Selected Range Gate                             | 18 |

| IV.   | INF          | PUT PROCESSING                                  | 18 |

|       | А.           | Sample Combiner                                 | 20 |

| •     | в.           | Memory and Controller                           | 20 |

|       | c.           | Single Range Gate Pickoff                       | 23 |

| V.    |              | TURATION DETECTOR AND INTERFERENCE<br>IMINATOR  | 24 |

| VI.   | TH           | REE-PULSE CANCELLER                             | 27 |

| VII.  | ΖE           | RO VELOCITY FILTER                              | 27 |

| VIII. | DIS          | CRETE FOURIER TRANSFORMER AND CONTROLLER        | 27 |

| IX.   | WE           | IGHTING CIRCUITS                                | 47 |

| x.    | МА           | GNITUDE-CALCULATION CIRCUITS                    | 49 |

iii

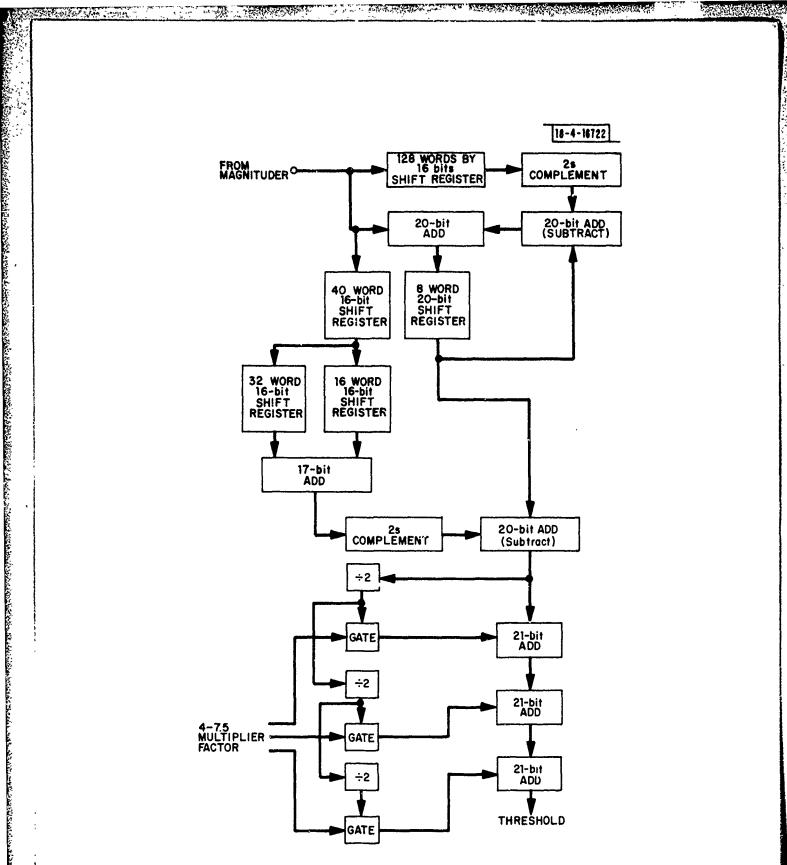

| XI.   | WEATHER THRESHOLD GENERATOR          | 52 |

|-------|--------------------------------------|----|

|       | A. Running Summer                    | 54 |

|       | B. Subtracter                        | 54 |

|       | C. Multiplier                        | 54 |

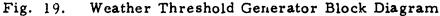

|       | D. Video Generator                   | 56 |

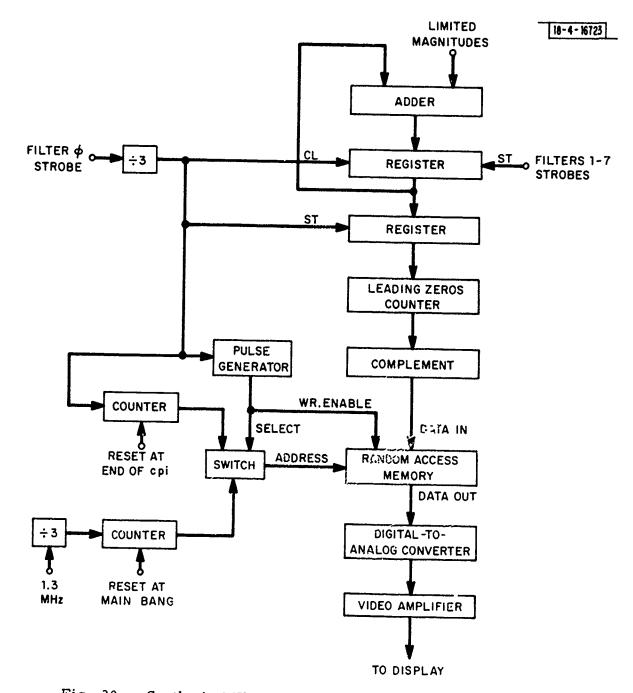

| XII.  | CLUTTER THRESHOLD GENERATOR          | 58 |

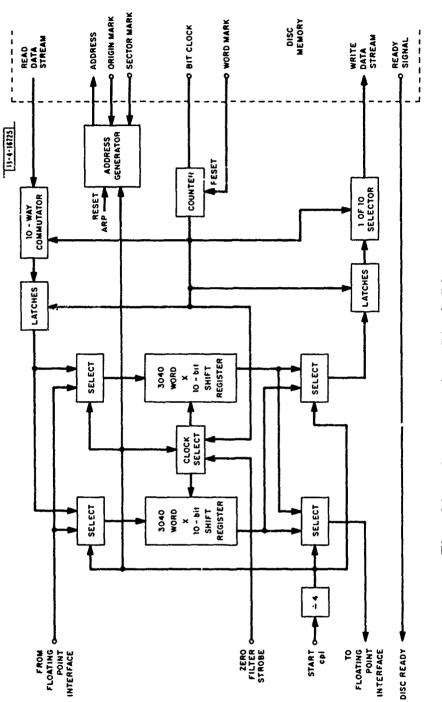

| XIII, | DISC MEMORY CONTROLLER AND INTERFACE | 61 |

|       | A. Interface                         | 61 |

|       | B. Controller                        | 63 |

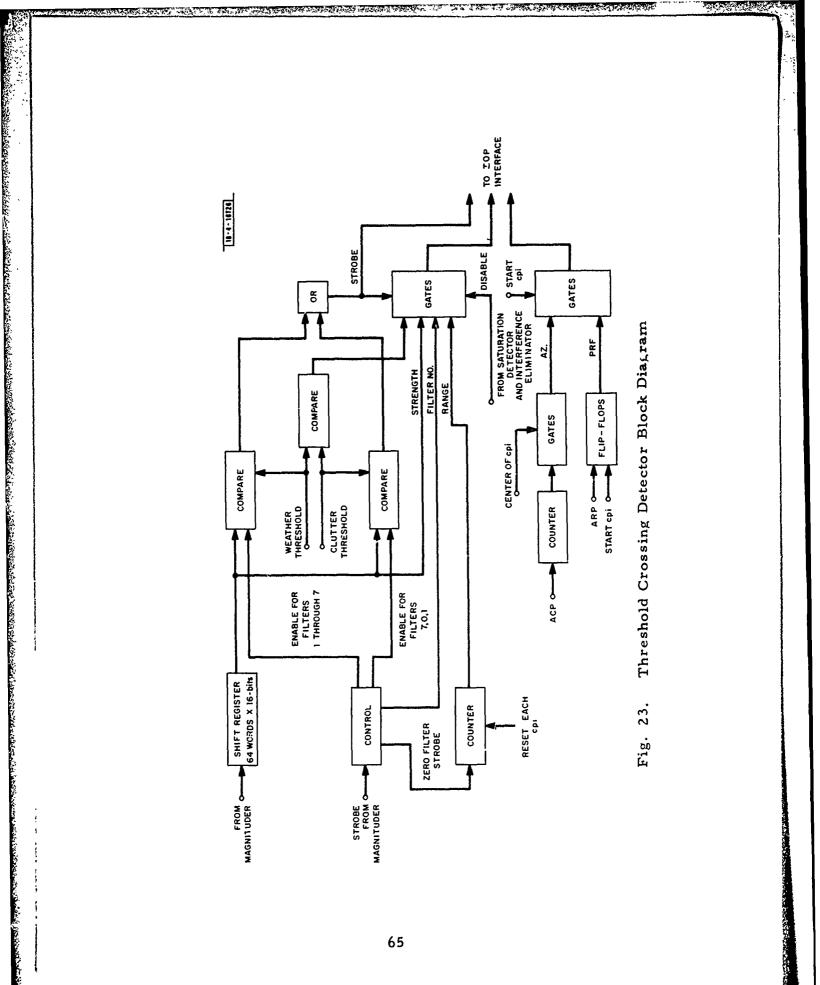

| XIV.  | THRESHOLD DETECTORS                  | 64 |

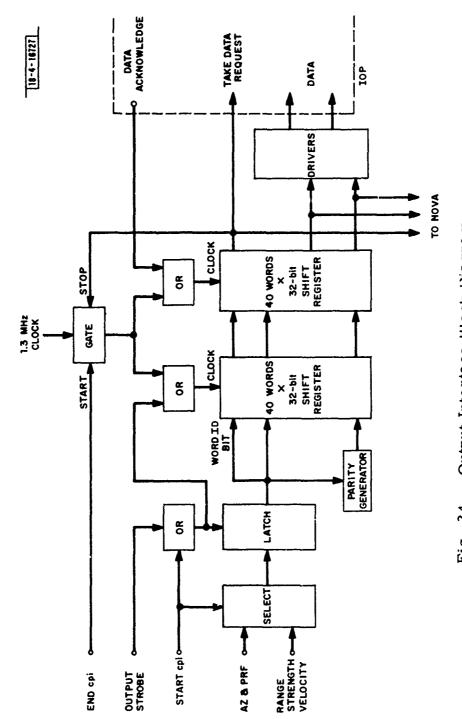

| XV.   | IOP INTERFACE                        | 69 |

| XVI.  | TEST MEMORY AND CONNECTION           | 71 |

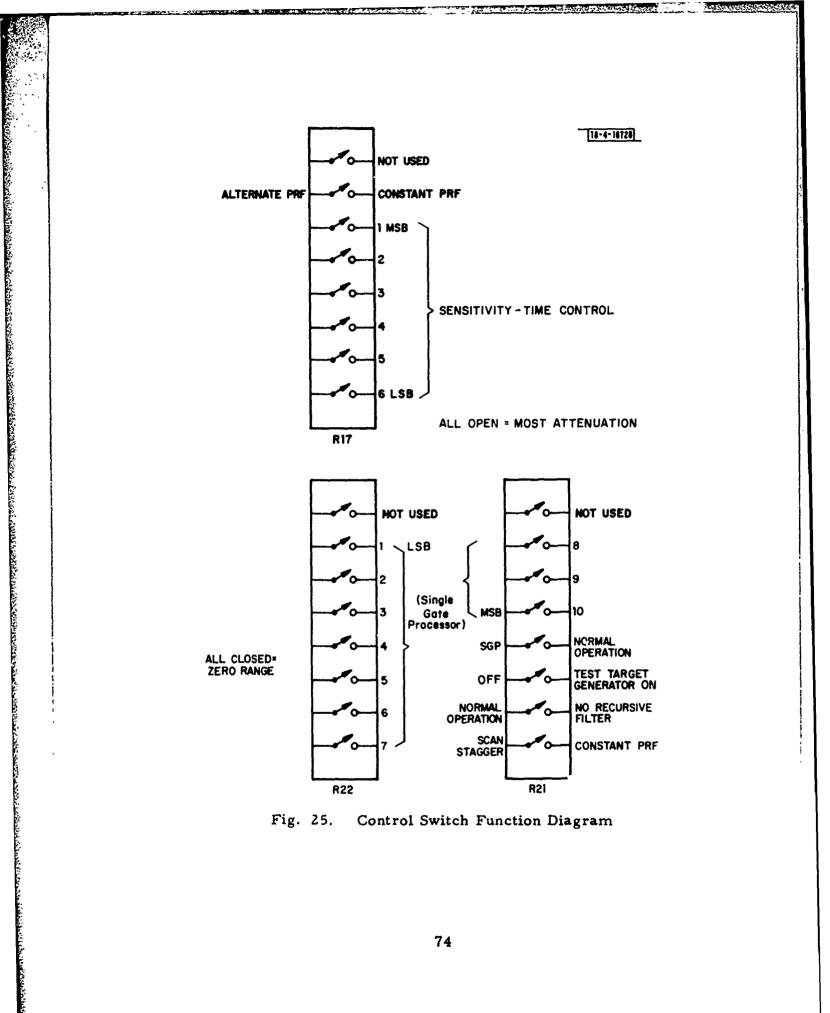

| APPE  | NDIX A - Site Adaptation Alignment   | 72 |

| APPE  | NDIX B - Checking and Testing        | 76 |

Constant of Market States in the light of the light

NYN A

PARTIN BERTHER

6.06

an contraction of the second

## I. INTRODUCTION

The Moving Target Detector system (MTD) is a signal processor to improve the performance of Airport Surveillance Radars (ASR's). It features spectral processing with adaptive thresholds and thereby provides a 20 dB increase in signal improvement factor over the present ASR's. An auxiliary channel is included to allow detection of any target traveling tangentially if its return exceeds the level of ground clutter return in the specific range/azimuth cell occupied. The spectral processing technique provides discrimination against weather clutter if the returns from weather fall into frequency regions which do not include the target returns.

CAST STANKED

The system parameters are:

| Transmitter pulse width                       | lμsec.                   |

|-----------------------------------------------|--------------------------|

| Pulse repetition frequency                    |                          |

| Pair "A"                                      | 1.1131 kHz<br>1.3677 kHz |

| Pair "B"                                      | 1.1208 kHz<br>1.3794 kHz |

| Pulses per Coherent Processing Interval (CPI) | 10                       |

| CPI's per antenna scan                        | 480                      |

| Range gate length                             | 1/16 mi                  |

| Range coverage                                | 47. 5 mi                 |

| Azimuth coverage                              | 360 <sup>0</sup>         |

| Azimuth resolution                            | 0.75 <sup>0</sup>        |

| Antenna beamwidth (two-way)                   | 10                       |

| Sensitivity Time Control (STC) curve          | varies as $(range)^{-4}$ |

The prf alternates from CPI to CPI in order to resolve Doppler ambiguities, and changes between "A" and "B" pairs on alternate scans to identify secondtime-around range returns.

## II. BLOCK DIAGRAM DISCUSSION

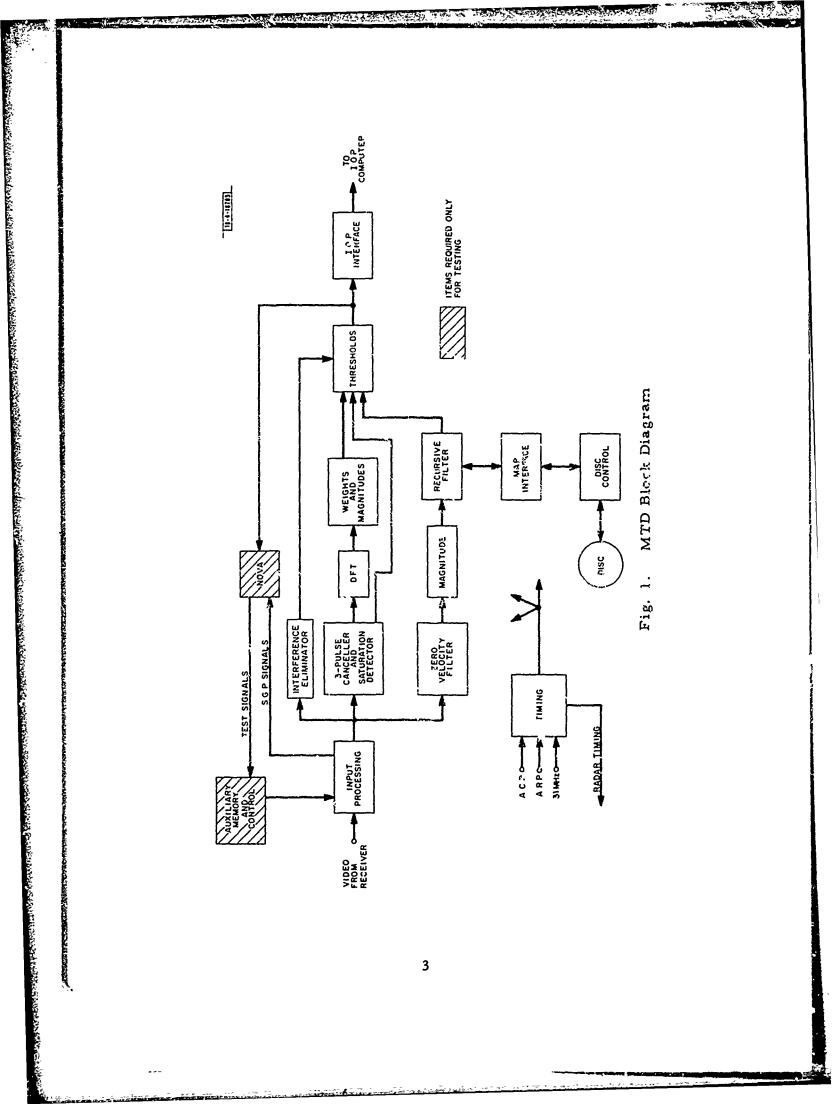

Figure 1 is a system gross block diagram. This discussion will treat each block in turn.

A. Timing

The timing portion of u.e MTD accepts antenna position information and the 30.9875 MHz master oscillator signal and outputs all the necessary triggers and pulses which are radar related. The signals used for timing within the latter stages of the processor are generated by the DFT control unit to be described later.

The outputs are:

Azimuth change pulse Azimuth reference pulse Azimuth data word Transmitter pre-trigger 31 MHz pulse to exciter Zero range trigger End sweep time trigger Encode commands for A/D converters Operator selected range gate sampler Start CPI End CPI STC attenuation word H. V. power supply regulator control gate

There are also several signals output which are generated by combining one or more of the above.

B. Input Processing

The Computer Labs model 5103 A/D converters that are used to digitize the quadrature video are capable of converting each 335 nsec, although the targe

interval of the radar is 775 nsec (1/16 mile). To take any possible advantage of this fact, two samples are taken during each range gate and the results added together. Thus, with 10-bit converters, we present an 11-bit sample to the input of the processor.

Since spectral analysis with an 8-point discrete Fourier transform requires eight samples of the input wave and two pulses are required to "charge up" the 3-pulse canceller, the system must gather ten samples of an input signal before processing can be started.

A core memory is used to store data from ten radar sweeps of 760 range gates each. The processing can then begin by putting the ten samples trom the first range gate into the canceller. These are followed by the ten samples of the second gate, etc.

The addressing for the 8K core memory is such that each cell is filled with new data as soon as it has been read out. In this way, only 7600 words of storage are required.

A set of switches is provided to allow selection of one particular range gate of the 760. The digitized video from this selected gate is fed to the NOVA computer for use in the Single Gate Processor (SGP) program. The SGP is not required for normal operation and is only used as a diagnostic tool to examine the stability of various parts of the radar.

C. Saturation Detector and Interference Eliminator

Since the system processes ten signal samples as a unit, it must remember and discard an output formed from an input set where any sample

saturated the A/D converter. For simplification of hardware, saturation is defined as 0.5 dB below converter limits. Interference from other radars in the vicinity appears as one large return in the series of ten, unless the radar is synchronous with the FPS-18 radar, which is unlikely. The interference eliminator compares the magnitude of each pulse of the ten against the average magnitude of the ten. If any pulse is greater than five times the average, all information from that range/azimuth cell is discarded.

# D. Three-Pulse Canceller

A BANK BANK ALES

The output of the 8K core memory feeds the canceller and zero velocity filter (ZVF) as well as the saturation detector. The canceller uses the algorithm a-2b+c where, a, b and c are three consecutive samples. Since coherent processing intervals (CPI's) alternate in pulse repetition frequency, the output of the canceller is meaningless until the third sample of a CPI has been accepted. Only the last eight of the ten numbers output from the canceller are passed on to subsequent circuits.

## E. Zero Velocity Filter

The canceller not only masks clutter but also prevents the observation of targets traveling at radial velocities near zero or multiples of the prf. Since many range/azimuth cells will exhibit very low, if any, clutter returns, it is a waste to discard them all. The implementation of the zero velocity filter (ZVF) allows detection of any targe' at low velocity whose return exceeds the level of clutter in that particular cell. Since most ground clutter is of a fixed nature, the system uses a disc memory to "remember" the clutter level in every cell from scan to scan, thereby providing a reference to threshold new signals against.

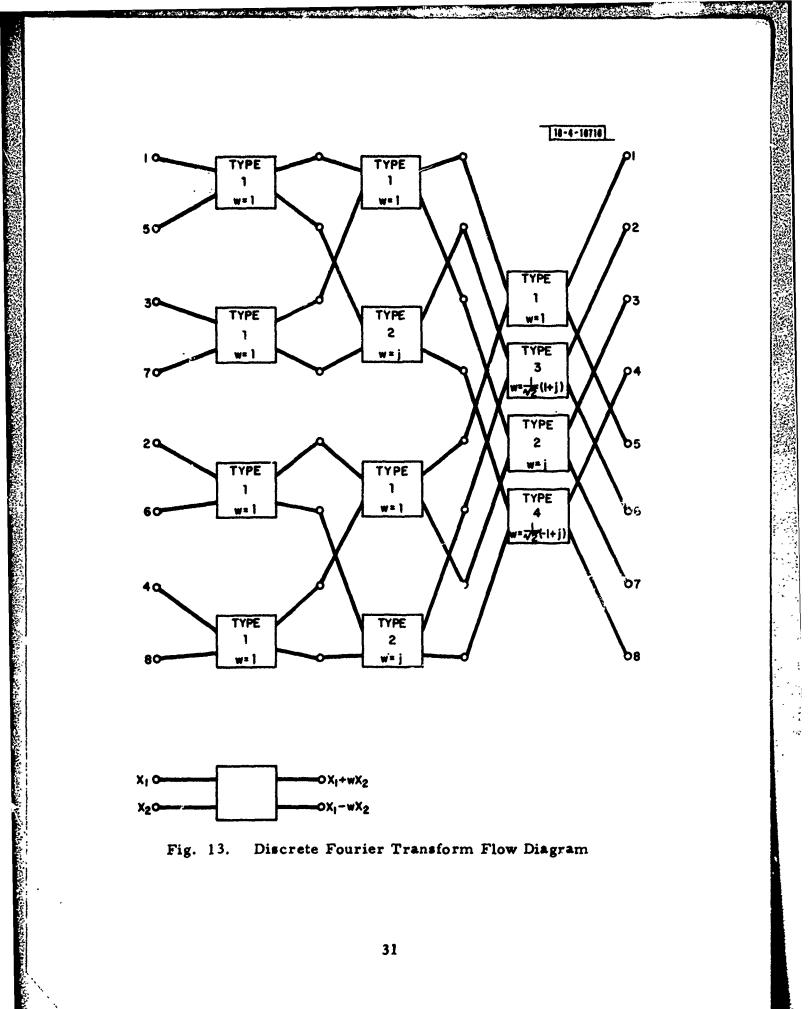

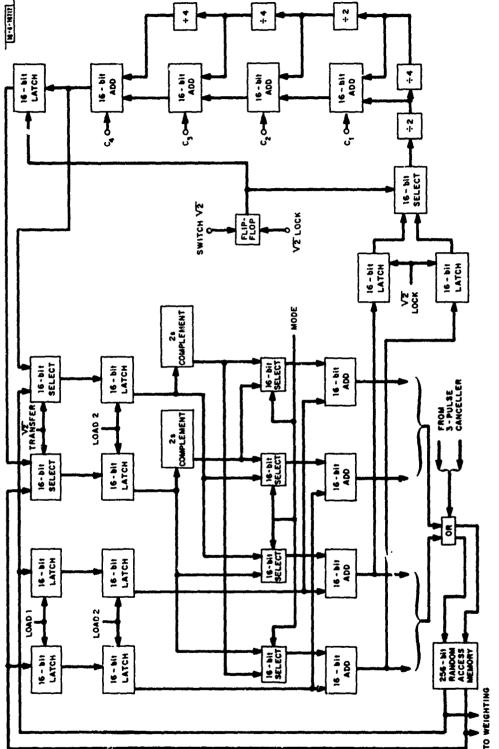

## F. Discrete Fourier Transform

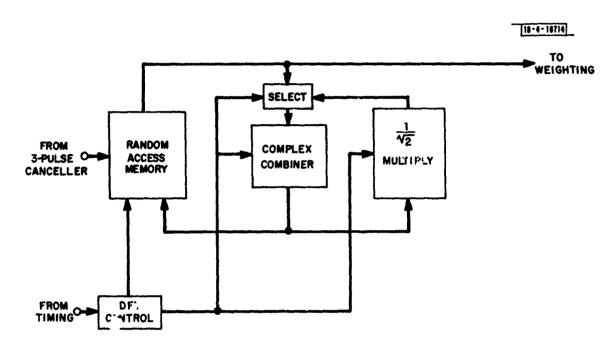

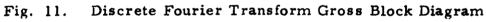

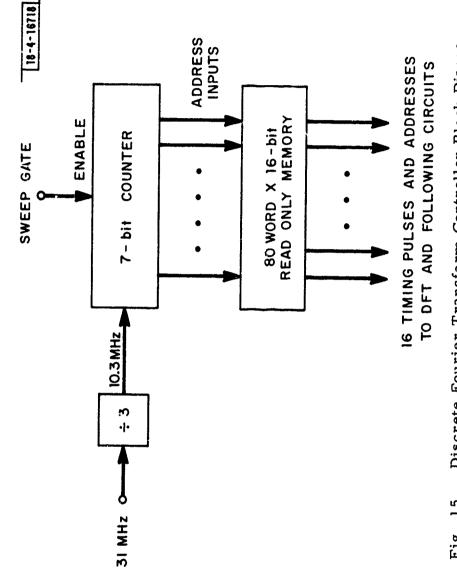

The MTD uses an 8-point discrete Fourier transform (DFT) implemented by the fast Fourier transform (FFT) algorithm. The hardware uses no multiplies except by powers of two (shifts) to compute the transform. The only fraction,  $1/\sqrt{2}$ , is approximated by the sum 1/2 + 1/8 + 1/16 + 1/64 + 1/256which is all implemented by shifts and carrys. The DFT is made up of an arithmetic unit, a scratch-pad memory and a controller containing a hard-wired program of 80 instructions. This controller provides the timing pulses for the DFT and all subsequent portions of the MTD. The input to the DFT is eight samples in time of each of 760 range gates while the output is the response of eight digital filters presented sequentially for each of the 760 gates.

G. Weighting and Magnituding

CALCULAR STUD BALLAND

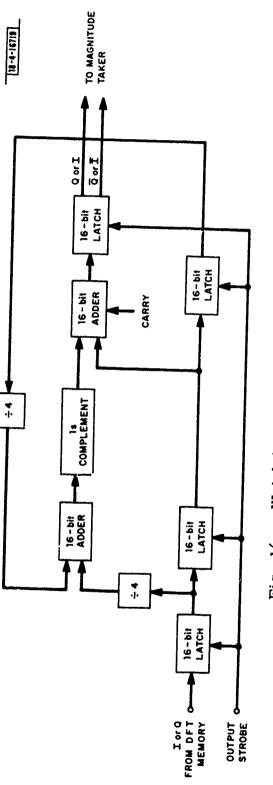

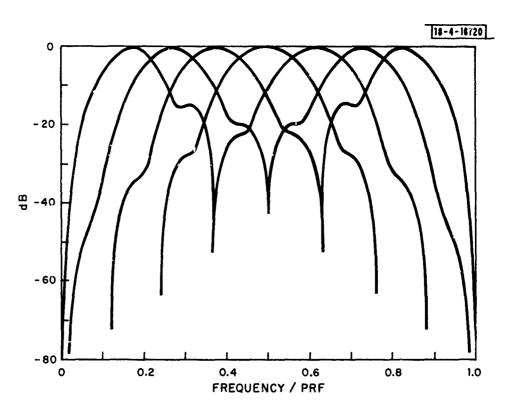

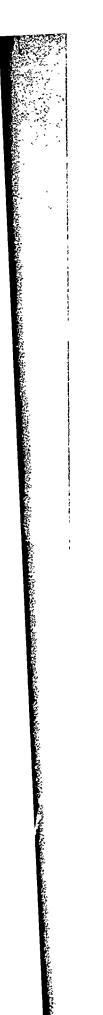

The DFT output is weighted by using the algorithm that each filter output is diminished by 1/4 the value of each of the two adjacent filters. For this purpose the zeroth filter is adjacent to the seventh filter. The weighted signals are then fed to a magnitude-taking circuit which uses the algorithm M = greater of: |L|, 7/8 |L| + 1/2 |S| where L and S are the larger and smaller of the I and Q components of the signal. It can be shown that this diverges from  $\sqrt{I^2 + Q^2}$  in the worst case by less than 0.2 dB.

At the input of the magnituder, the output from the ZVF is substituted into the time-slot of the zeroth DFT filter, since the zeroth filter has had all DC removed by the canceller.

## H. Thresholds

Separate thresholding takes place on each filter output. The thresholds for the non-zero filters are based on the average returns in that filter for a one-mile range interval centered on the cell of interest. The threshold for the ZVF is based on the past history over many minutes of the returns in the cell of interest. These two concepts of thresholding were chosen because of the character of ground and weather clutter. Weather clutter will generally be dispersed in range over several cells, whereas ground clutter is quite independent from cell to cell. On the other hand, weather clutter is quite time-varying, but ground clutter in a given cell remains relatively constant in level over long periods of time. The problem of storing ground clutter information for each of 365,000 range/azimuth cells is solved by using a disc memory unit. However, the asynchronism between the radar and the disc and the relatively long access time of the disc requires that some 3,000 words must be buffered into and out of the disc memory. This is accomplished by using MOS shift registers. If the appropriate threshold is exceeded and there were no A/Dsaturations or interference in the raw data, an output message is entered into the output interface circuitry.

I. Output .'nterface

The output circuitry contains double buffering for up to 38 detections per CPI. Double buffering is required because the MTD and the Input/Output Processor (IOP) are a ynchronous devices. At the start of each CPI, a prf/ azimuth (PAZ) word is entered into the first buffer. When a threshold crossing takes place a velocity/range/strergth (VRS) word for that detection is entered into the first buffer. At the end of each CPI the PAZ word and any VRS words for that CPI are transferred from the first to the second buffer. During the next CPI the contents of the second buffer is transferred to the IOP. The NOVA computer is also connected to this output and receives data in parallel with the IOP.

J. MTI Weather Video Output (Not required for automatic operation)

In most cases, it is useful for the operator to be able to see the location of storms on his display screen. Since the MTD does an excellent job of eliminating the radar returns from bad weather, an ancillary channel was added to form such a signal. The returns from all <u>non-zero</u> filter outputs are added together at the magnituder output and then averaged over three range gates, thus forming 254 outputs in range for each CPI. A 256 word memory is used to store these numbers and is read out to the display each sweep. As each piece of new information is generated i<sup>+</sup> is stored in the proper cell of the memory, replacing the previous value for that cell.

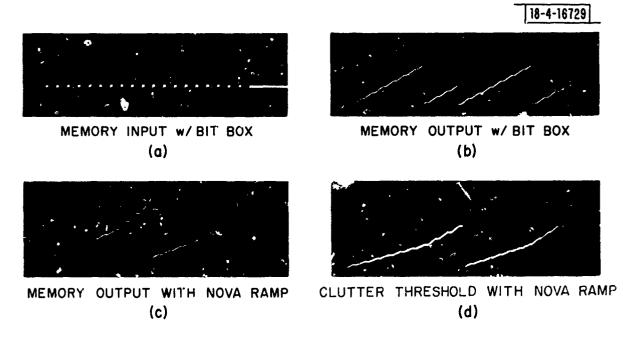

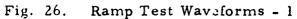

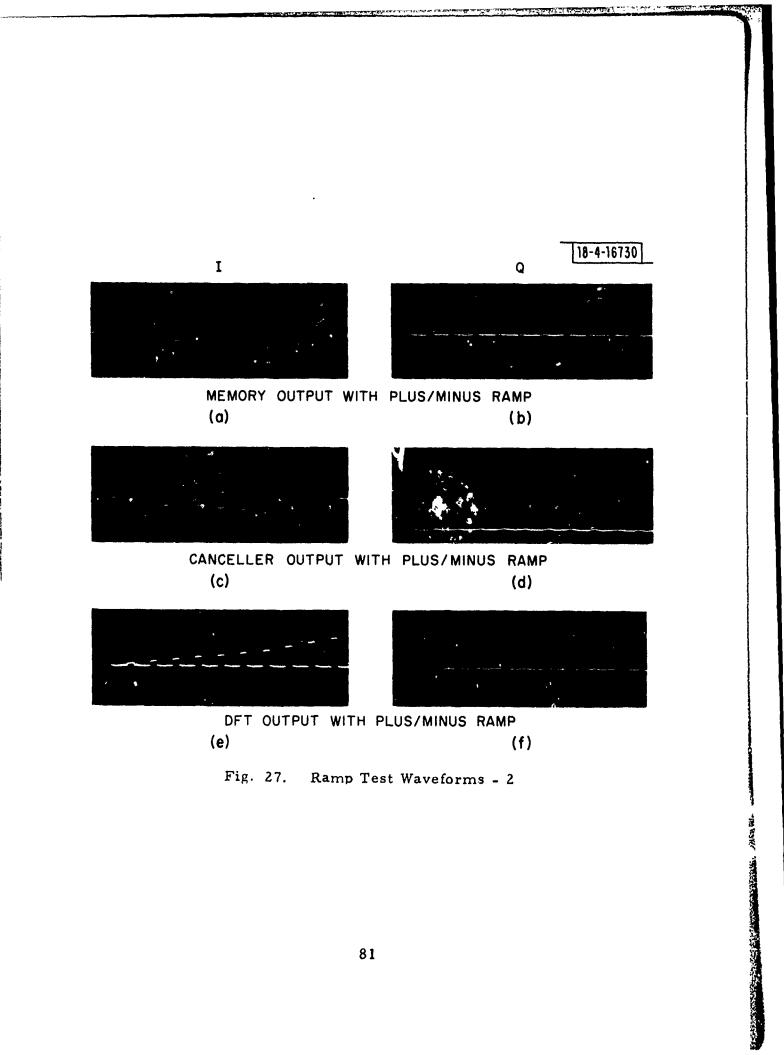

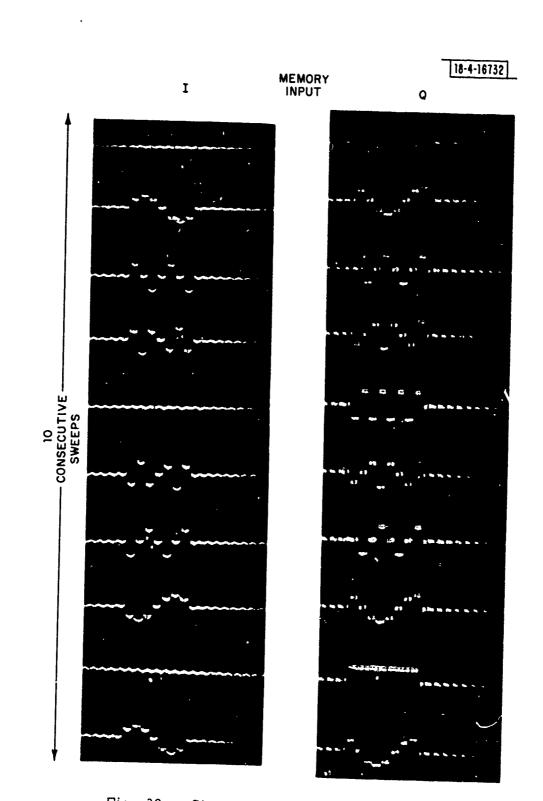

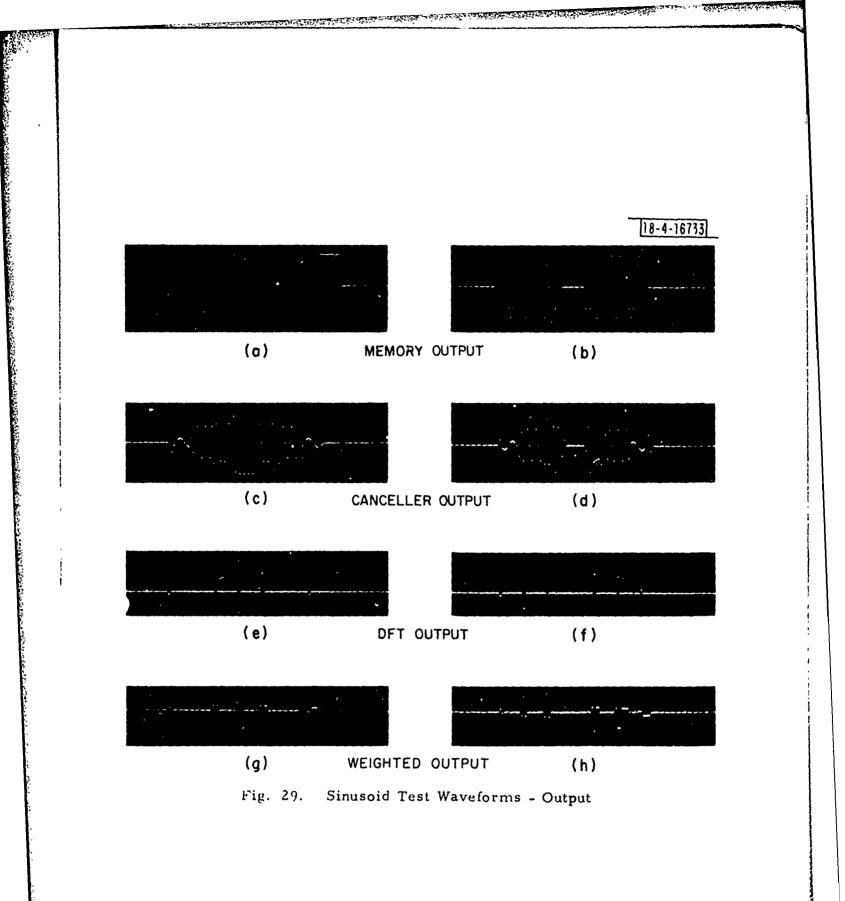

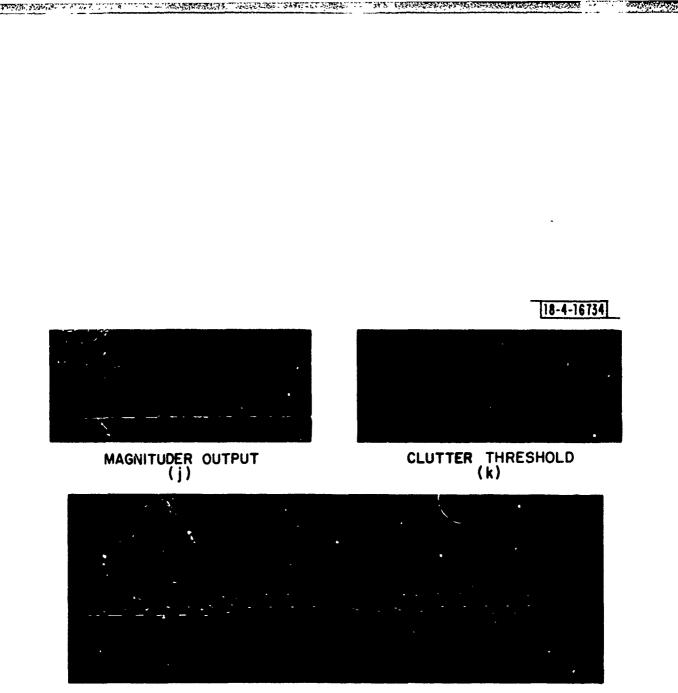

K. Auxiliary Memory (Required only for testing purposes)

A core memory is supplied which can be connected to the input of the MTD in place of the A/D converters for testing. This memory can be loaded with 7,600 words (a full CPI) of known input data. The MTD will then process this data with identical and predictable results in each CPI, thus making it easy to observe processor faults.

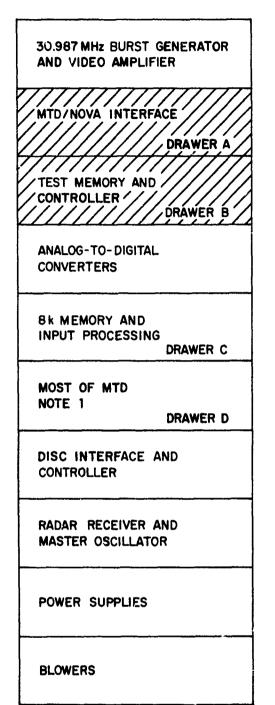

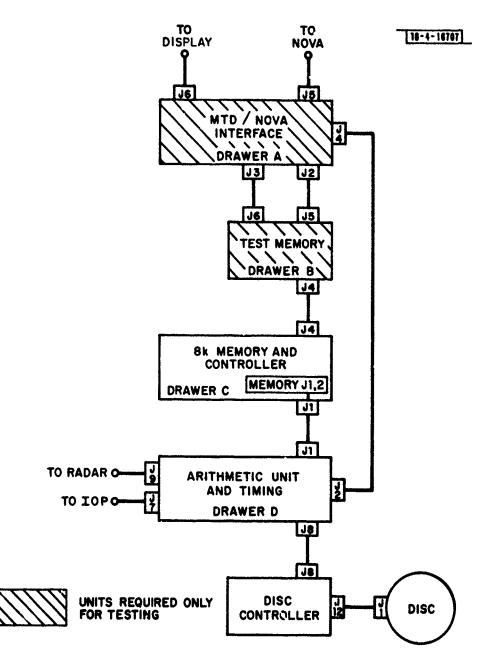

Figure 2 is a diagram of the physical layout of the MTD rack and Figure 3 is a diagram showing the layout of the inter-chassis cabling.

and a start of the second start of the second start and the second start of the second start of the second start

----

18-4-16706

#### NOTE 1

CONTENTS OF DRAWER D

- (a) 3-PULSE CANCELLER

- (b) SATURATION DETECTOR

- (c) INTERFERENCE ELIMINATOR

- (d) ZERO VELOCITY FILTER

- (e) DFT AND CONTROL

- (f) WEIGHTING

- (g) MAGNITUDING

- (h) THRESHOLD GENERATORS

- (i) THRESHOLD CROSSING DETECTOR

- (j) TIMING

- (k) OUTPUT INTERFACE

- (1) ALL SITE ADAPTATION PARAMETER SETTINGS

UNITS REQUIRED ONLY FOR TESTING

Fig. 2. MTD Physical Configuration

Fig. 3. MTD Cabling Diagram

13

SALE OF THE

III. TIMING

redere fin skande se en hande dare der die het die der der der der der der die die die die die die die die die

and the second states a

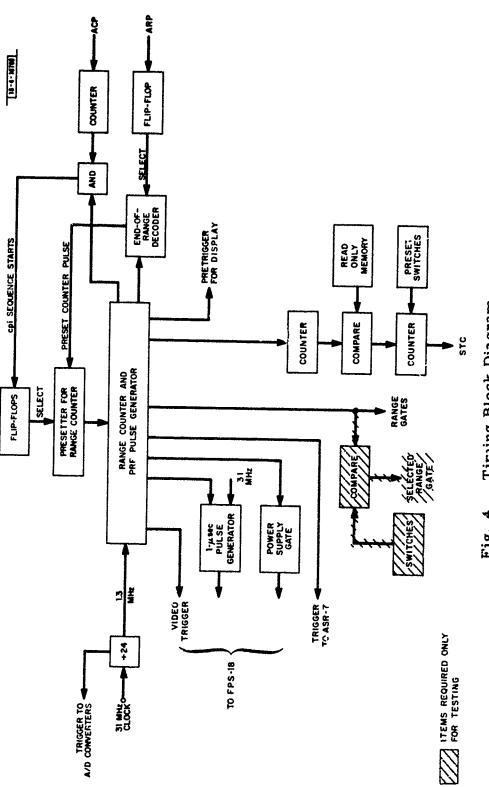

The timing shown by the block diagram of Figure 4 can be logically divided into four sections:

1. Generation of the pulse repetition frequency (prf) for the radar.

2. Signals generated each prf.

- 3. Fast timing.

- 4. Selected range gate.

The entire timing section is located in the top rear panel of drawer "D".

A. PRF Generation - Theory

The prf is generated in bursts of ten pulses, two such bursts constituting a (.PI pair. The initiation of a CPI pair must depend on antenna position since the use of a clutter map dictates that CPI's be correlated with azimuth. In the  $\approx 4.8 \ s^2$  conds that it takes for one revolution of the antenna, 240 CPI pairs are generated. Azimuth change pulses (ACP's) are generated by the antenna at the rate of 4096 per revolution. In order that the CPI's be distributed as equally as possible in azimuth, a CPI pair is initiated each 17 ACP's. Simple calculation reveals that 240 CPI pairs will be generated in less than 4096 ACP times, so each 15th CPI pair is initiated after 18 ACP's rather than 17. This distributes the error through the entire scan.

During the period of 17 ACP's the transmitter must be triggered at one prf ten times, at a second prf ten times and at an average of the two prf's as many times as necessary to fill the rest of the interval. This last number may be any number from one to about four because the antenna speed changes slightly with wind loading, causing differences in inter-ACP time. The time filled with average prf must be long enough so that it never goes to zero under worst case antenna speed variation.

· · : ")

BY BELINGS BURNESS

t

,

I

ないたいたいないが、

4

トーーングリ یں ب

, Ì

.

٠. -

During the 17-ACP interval, a range counter is counting at a 1.3 MHz (1/16 mile) rate up to the end-of-range trigger. When that point is reached the counter jumps to a negative number, shown by point B in Figure 5 and continues counting up through zero range and to the next end-of-range time. End range times D and E on Figure 5 are used on alternate scans, providing a slight jitter in prf from scan to scan.

Following recepit of each 17th (or 18th) ACP the jumpback point for the counter is shifted to point A for 10 times, then to point C for 10 times, before reverting to point B. The table in Figure 5 gives a summary of the prf frequencies that are generated by this method.

## B. PRF Generation - Details

The second

ACP pulses are routed to a counter whose output feeds a comparitor. The counter is reset to zero by the azimuth reference pulse (ARP) each time the antenna passes through north. The other side of the comparitor is fed from the output of another counter which is incremented in units of 17 counts. (Each 15th time it is incremented by 18 counts.) Incrementing is caused by the occurrence of an output pulse from the comparitor (COMF). In effect, the other side of the comparitor advances 17 (18) counts each time the ACP counter catches up to it.

Video trigger (VTRG), generated near zero range count, is ANDed with COMP to produce a sequence initiate pulse (SEQ). SEQ zeros a counter which counts VTRG pulses. P10 and P20 are counter outputs which are divide-by-10 and divide-by-20, respectively. These are decoded to reset the range counter to the proper number for low, high or average prf.

# 118-4-18768

With a second second

| PRESET | TRANSMITTER | ZERO     | DISPLAY    | END-OF-RANGE |

|--------|-------------|----------|------------|--------------|

| TIMES  | TRIGGERS    | RANGE    | PRETRIGGER | TRIGGERS     |

| AIBC   |             | <u> </u> |            | DE           |

| INTERVAL | NO. COUNTS | LISEC | PRF GENERATED (LHz) |         |

|----------|------------|-------|---------------------|---------|

| A TO D   | 1152       | 892   | 1.1208              | LCW     |

| CTOD     | 936        | 725   | 1.3794              | HIGH    |

| BTOD     | 1040       | 805   | 1.2415              | AVERAGE |

| A TO E   | 1160       | 898   | 1.1 131             | LOW     |

| C TO E   | 944        | 731   | 1.3677              | HIGH    |

| B TO E   | 1048       | 812   | 1.2320              | AVERAGE |

Fig. 5. Timing Diagram

Note that the two CPI's of the pair start at SEQ and P10. These two signals are ORed and then ANDed with a zero range pulse (ZT) to produce start CPI (SCPI). This pulse is also known as load increment (LINC). The first ZT after SCPI is selected also and called set increment (SINC). These last two signals are used in the input processing section and the reason for their names will become obvious when that section is covered. After the 10th cycling of the range counter in a CPI, the end sweep time (EST) pulse is selected and called end CPI (ECPI). A gate is generated between SCPI and ECPI and appropriately identified as the CPI gate.

The ACP counter which was used to generate COMP contains real-time azimuth information. Midway in each CPI, azimuth sample (AZSAM) is decoded which latches the azimuth count into a double buffer. This is necessary because the Fourier transform processing is all performed one CPI late and the azimuth of the past CPI must be remembered. This azimuth word will become part of the output data package.

In the absence of ACP and ARP pulses (such as when the antenna is stopped) an internal generator in the MTD automatically takes over so that the transmitter will continue operating.

C. Signals that Repeat at the PRF

Each pulse repetition interval the range counter counts at 1.3 MHz (1/16 mi) from a preset negative number up through zero count (ZT) to end of sweep time (EST). The counter resets to the negative number at DTT pulse time. The position of DTT changes by eight counts from scan to scan providing a slight jitter. Various triggers are decoded along the way as the counter runs and these are summarized in Table 1. The bits of the counter form real-

Testes

18 C ( )

and the second second

## TIMING PULSES GENERATED EACH PULSE REPETITION TIME

| Name           | Time in Counts | Time in usees | Purpose                                  |

|----------------|----------------|---------------|------------------------------------------|

| PT             | -129           | -100          | Display pretrigger                       |

| ASRTRG         | -31            | -24           | Coho lock pulse for ASR-7<br>radar       |

| VTRG           | -10            | -8            | Modulator trigger for FPS-18 and ASR-7   |

| RFTRG          | - 5            | -4            | RF trigger for FPS-18 and ASR-7          |

| ZT             | 0              | 0             | Zero range time, start of sweep          |

| ONEGATE        | 1              | 1             | Time of first range gate                 |

| EST            | 760            | 589           | Time of last range gate,<br>end sweep    |

| <b>EST</b> + 1 | 761            | 590           | One count after EST                      |

| DTT            | 768 or<br>776  | 595 or<br>601 | Reset range counter to starting point    |

| SWGT           | extends from   | ZT to EST     | Sweep gate                               |

| PSGT           | extends from   | EST to VTRG   | HV power supply regulator control signal |

time range and are distributed through the system. The sweep gate (SWGT) and power supply control signal (PSGT) are intervals between some of these pulses and are, therefore, included in Table I. PSGT is a function of prf and is used to provide a constant duty cycle to the high voltage power supply of the transmitter.

The sensitivity time control (STC) attenuator in the receiver is driven from a counter in the timing section. This counter is preset at main-bang time to a number selected by switches and is then decremented to zero by a pulse train whose frequency is a function of range time to the minus fourth power. Each pulse in the train is formed by comparing the output of the range counter with a set of range numbers stored in a read-only memory (ROM). As each comparison is successful, the next word, representing the range of the next pulse, is drawn from the ROM and applied to the comparitor. It is expected that for each given radar siting the optimum number for initial attenuation at main-bang time will be determined. This number will thereafter remain fixed.

D. Fast Timing

The fast timing generates all signals that occur more often than once per sweep. The input from the master oscillator (MO) is nominally 31 MHz and is divided by two to yield 15.5 MHz. Commencing at RFTRG, 16 pulses of this frequency are counted to form a nominal 1- $\mu$ sec gate. The gate is ANDed with the 31 MHz signal to produce a 1- $\mu$ sec burst of pulses. This burst if filter@d to make the pulses sinusoidal, amplified, gated again and sent to the exciter. The second gating is performed in a balanced mixer and is necessary because leakage through the TTL gate is excessive. The 15.5 MHz train is further divided by 6 to form a 2.6 MHz signal to be used as the encode command for the A/Dconverters. An additional division by two yields 1.3 MHz, the range counter clock.

E. Selected Range Gate (Required only for testing purposes)

A single range gate (SRG) is selected manually by setting a bank of switches to the desired range. This setting is compared to the range counter output and a pulse generated at the time of coincidence. The output is used to sample and hold the outputs of the A/D converters in that particular range gate for transmission to the NOVA and its SGP spectrum analysis program. A pulse slightly ahead of SRG is used to initiate a second burst of 31 MHz for the exciter. This burst generates a test target in all azimuths at SRG time. A switch is included to prevent generation of this second burst when no test target is desired.

IV. INPUT PROCESSING

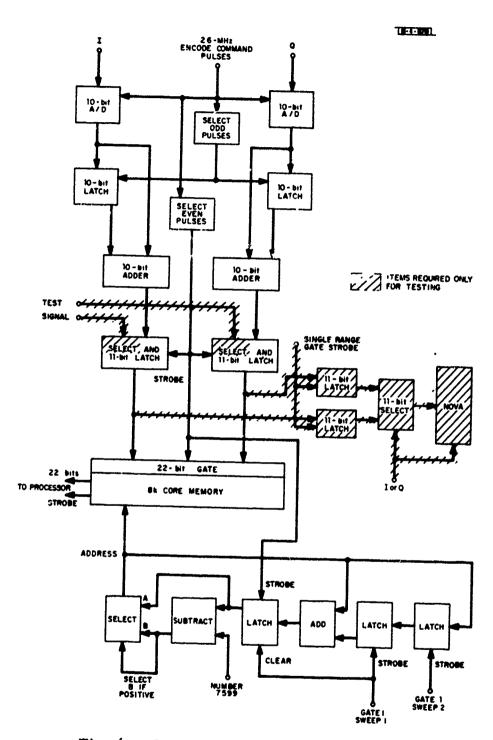

The input processing section of the MTD, shown in Figure 6 and located in drawer 'C' can be divided into three sections.

1. Sample combiner

2. Memory and controller

3. SRG pickoff

A States

1

ÚX.

THE PARTY PROPERTY IN

والمعادة والمتعادية والمتحدين والمتلفظ والمعادية

というないとなったななどがないたとうないとなったいないないないないなったのなのでもというためであるのです。

è

.

÷

s n-: Alexant

Input Processing Block Diagram Fig. 6.

### A. Sample Combiner

Two 10-bit samples are taken in each range gate by the A/D converters on command of the 2.6 MHz clock signal. The first sample of a pair is stored and added to the second to produce a single 11-bit sample in each gate. This sum is then entered into a memory via a selector switch. When this switch is in the TEST position, the sample word is replaced by a word drawn from a "test" memory to be discussed later.

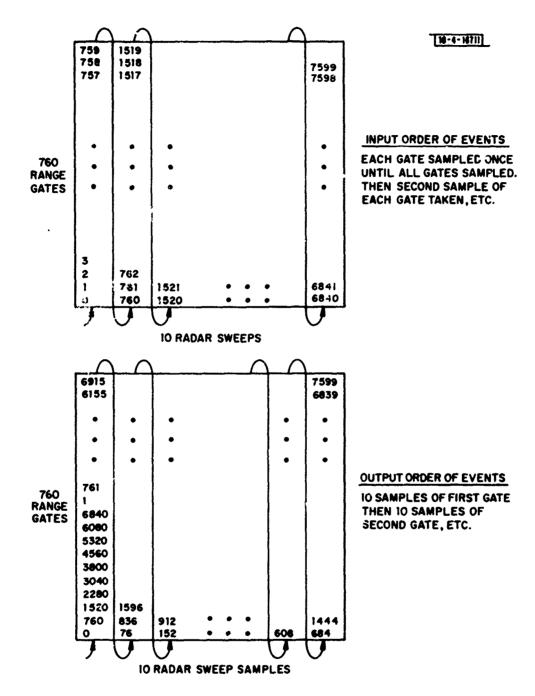

B. Memory and Controller

Since the MTD must process ten samples from the same range gate as a group, there must be storage for ten samples of each of the 760 range gates or 7600 pairs of 11-bit I & Q words. To eliminate the need for "pingponging" two memories, split-cycle operation with an intricate addressing system is used. The memory units can perform a read/modify/write operation in 700 nsecs. The addressing is such that each cell is filled with new data as soon as it is emptied, while maintaining the "orthogonality" or "corner-turning" necessary to re-order the input data for processing. The output of the memory then becomes ten consecutive samples of each of the 760 range gates, as opposed to the input which is 760 range samples for each of ten consecutive sweeps. Figure 7 shows why this process is called orthogonality or corner-turning.

The addressing algorithm is shown in Figure 8 for a small memory array. The entire memory is used each CPI, but the order of cell use changes. The

and a start of the second start of the second

i h

Fig. 7. Input Data Re-ordering

| 4 9 1 <b>4 19</b> | 1 7 13 <b>19</b> | 5 16 8 19  | 6 4 2 19                 |

|-------------------|------------------|------------|--------------------------|

| 3 8 13 18         | 15 2 8 14        | 18 10 2 13 | 14 12 10 8               |

| 2 7 12 17         | 10 16 3 9        | 12 4 15 7  | 3 1 18 16                |

| 1 6 11 16         | 5 11 17 4        | 6 17 9 1   | 11 9 7 5                 |

| 0 5 10 15         | 061218           | 0 11 3 14  | 0 17 15 13               |

| -1-               | -2-              | -3-        | -4-                      |

|                   |                  |            |                          |

|                   |                  |            |                          |

| 11 1 10 19        | 17 5 12 19       | 9 6 3 19   | 7 11 15 19               |

| 13 3 12 2         | 8 15 3 10        | 2 18 15 12 | 10 14 18 3               |

| 15 5 14 4         | 18 6 13 1        | 14 11 8 5  | 13 17 2 6                |

| 17 7 16 6         | 9 16 4 11        | 74117      | 16 1 5 9                 |

| 0 9 18 8          | 0 7 14 2         | 0 16 13 10 | 0 4 8 12                 |

| لب<br>-5-         | -6-              | -7-        | ت<br>-8-                 |

| •                 | •                | ·          | -                        |

|                   |                  |            |                          |

| 16 17 18 19       | 4 9 14 19        |            |                          |

| 12 13 14 15       | 3 8 13 18        |            | NGE GATES<br>EPS PER CPI |

| 8 9 10 11         | 2 7 12 17        |            | RED MEMORY CELLS         |

| 4 5 6 7           | 1 6 11 16        |            | IT IS MODULO-19          |

| 0123              | 051015           |            |                          |

|                   | -1-              |            |                          |

| -9-               | - <b>J</b> -     |            |                          |

|                   |                  |            |                          |

$c_{H} \leq c$

18-4-16712

inder Gesternander

るためなどがなるのというと言語のないというななというです。

Fig. 8. Representative Addressing - Small Array

address of the first cell of the second sweep of each CPI is numerically equal to the address counter increment (modulo 19) for the next CPI. In the first CPI, the increment is <u>1</u> and information is stored in sequential locations for each gate of the first sweep followed by each gate of the second sweep, etc. The address for storing the first gate of the second sweep is <u>5</u> so that is the increment to be used for storing sweeps five through eight. Since the memory is of the read/modify/write type, the contents of cells 0-5-10-15 are read out as sweep five is being loaded in. Note that these cells contain the four samples of gate #1 taken in the first CPI. In this way, corner-turning is accomplished. Note also that the increment cycles through nine numbers and the tenth CPI is addressed exactly like the first CPI.

These value principles were used for the 7600-cell array in the MTD, with the increment cycling through 592 numbers before repeating. The address of the first gate of the second sweep is stored and held as the increment for the next CPI. If the address number is greater than 7599, the number is reduced by that amount before application to the memory.

The strobe RI which enters a new piece of data into memory also increments the address counter. The data-ready strobe ST from the memory is used to gate the signals out of memory to the rest of the MTD as far as the entrance into the weighting circuits. Details of memory operation may be found in the Standard Memories Inc. manual.

C. Single Range Gate Pickoff (For testing only)

The pulse from the selected range gate generator SRG in the timing section is used to gate the I & Q data from that particular gate into registers. The contents of the I register is then gated to output lines and a strobe sent

to the NOVA computer. Approximately 100  $\mu$ secs later the Q data is put on line and a second strobe sent. One bit is added to the words to identify the data. This bit is <u>1</u> in an I word and <u>0</u> in a Q word.

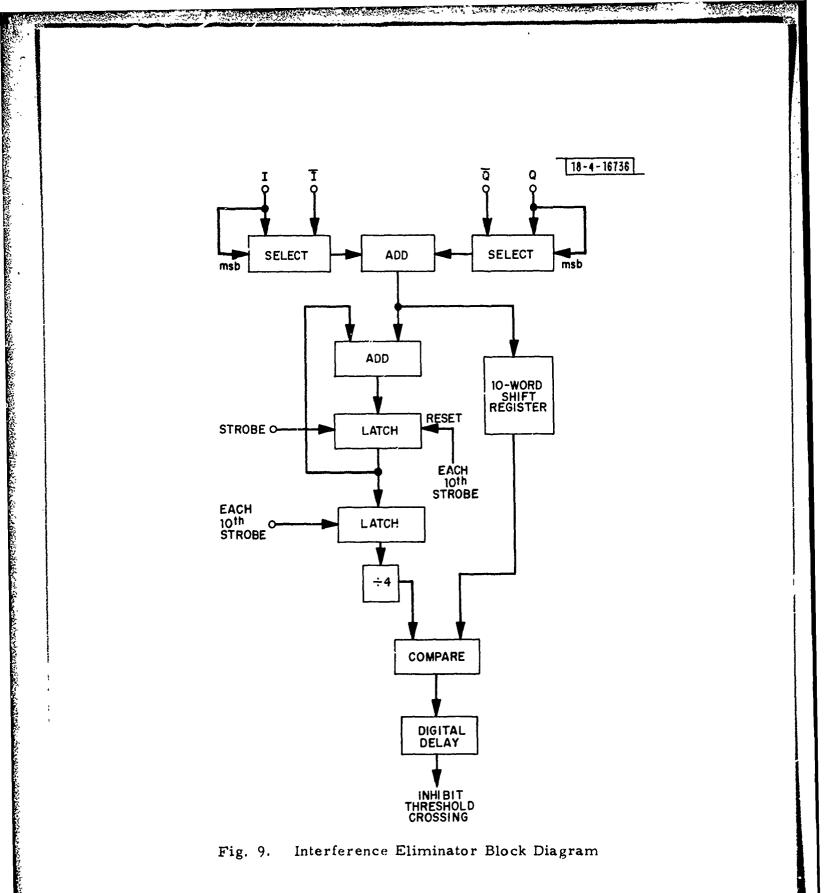

V. SATURATION DETECTOR AND INTERFERENCE ELIMINATOR

The interference eliminating circuits are shown in the block diagram of Figure 9. The magnitude of each of the 10 pulses is taken by adding the absolute values of I & Q. This algorithm is quite crude but still is accurate within 1 dB. The 10 magnitudes are summed and divided by two forming a number that is five times the average magnitude. The 10 magnitudes are also stored in a shift register delay line until the average has been computed. They are then compared sequentially with the five times average and if any one exceeds this number a flip-flop is set. This information is held until all Doppler processing has taken place and used to inhibit any threshold crossings that might occur in that range gate during the CPI interval.

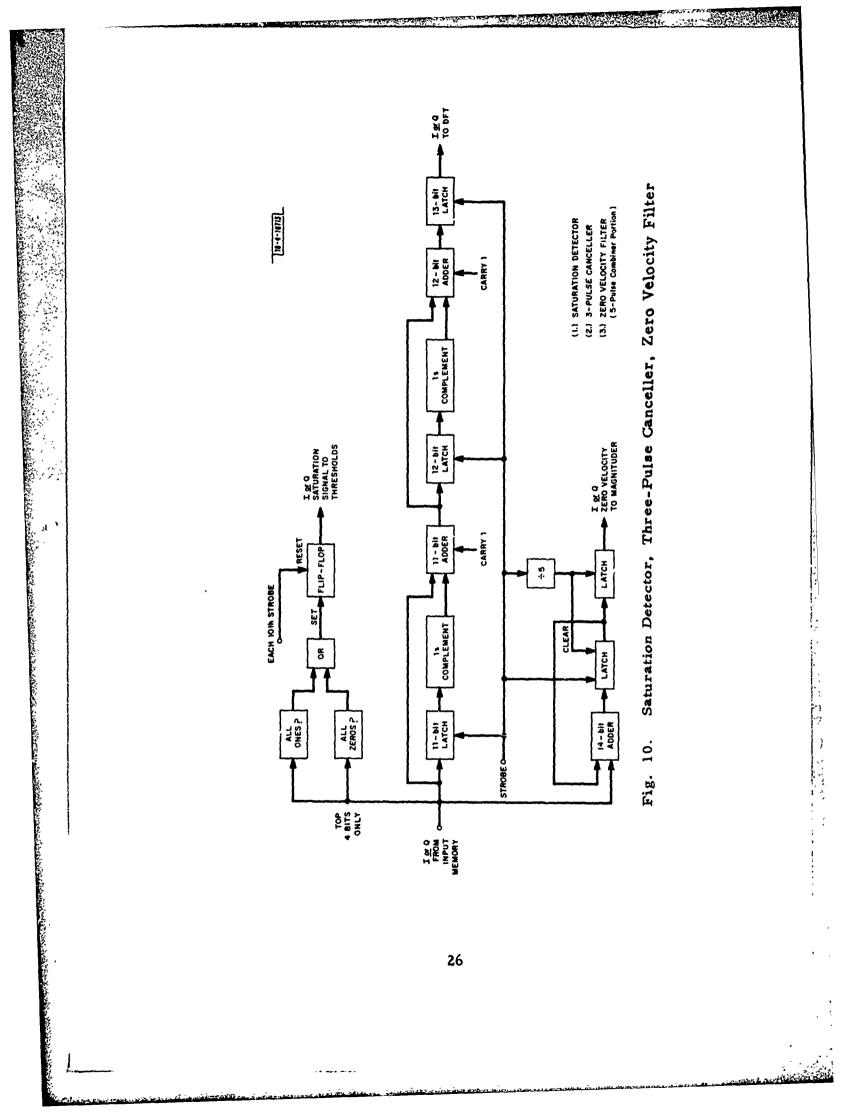

The saturation detection circuits are shown in the block diagram of Figure 10. Saturation is defined as occurring whenever the four most significant bits of the I or Q signal are all ones or all zeros at the output of the core memory. The word is expressed in offset binary code so these conditions represent about 95% peak signal of either polarity. If saturation exists a flip-flop is set and held until the entire ten samples have been tested. This is necessary because if any I or Q sample saturates the A/D converters, all results from those 10 samples are void. The output of the flip-flop is stored for use in the threshold circuits at the appropriate time.

25

and a same of the second

če u

and a station of the second second second second

## VI. THREE-PULSE CANCELLER

The canceller is also shown in Figure 10. The circuits perform a subtraction function by taking the 1's complement of the subtrahend and adding to the minuend with a carry. The algorithm is A-2B+C, where A, B, C are successive input samples in I or Q. Passage through the canceller is time by the read strobes (ST) generated by the memory. Since complete passage requires three strobes, the output from the canceller after the first two strobes is meaningless and is ignored by succeeding circuits. At this point the 11-bit word from the memory has grown to a possible 13 bits for completely coherent signals. VII. ZERO VELOCITY FILTER

The first part of the zero velocity filter (ZVF) is shown in Figure 10. The algorithm is to accumulate the I and Q signals in registers for the first five input signals and take the magnitude of the result. The process is repeated for the second five signals of the ten and the two magnitudes are then added to form a number indicating the strength of the zero velocity component of the signal. Passage through the accumulators is controlled by the read strobe (ST) generated in the core memory.