## **AFRL-RY-WP-TR-2016-0200**

# MULTIBAND RADIO FREQUENCY-INTERCONNECT (MRFI) TECHNOLOGY FOR NEXT GENERATION MOBILE/AIRBORNE COMPUTING SYSTEMS

Mau-Chung Frank Chang, Wei-Han Cho, Jieqiong Du, Yuan Du, Sheau Jiung Lee, Yilei Li, and Chien-Heng Wong University of California, Los Angeles

## FEBRUARY 2017 Final Report

Approved for public release; distribution unlimited.

See additional restrictions described on inside pages

## STINFO COPY

AIR FORCE RESEARCH LABORATORY

SENSORS DIRECTORATE

WRIGHT-PATTERSON AIR FORCE BASE, OH 45433-7320

AIR FORCE MATERIEL COMMAND

UNITED STATES AIR FORCE

## NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report is the result of contracted fundamental research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated 10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09. This report is available to the general public, including foreign nationals.

AFRL-RY-WP-TR-2016-0200 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH ASSIGNED DISTRIBUTION STATEMENT.

SCARPELLI.ALFR

SCARPELLI.ALFR

ED.J.1230195222

DN: c=US, 0=U.S. Government, ou=DoD, ou=PkI, ou=USAF, on=USAF, on Date: 2017.01.06 15:26:28 -05'0

ALFRED J. SCARPELLI Program Manager Advanced Sensors Components Branch Aerospace Components & Subsystems Division PAUL.BRADLE Y.J.1209885146 ou=DoD, ou=PKI, ou=USAF, cn=PAUL.BRADLEY.J.1209885146

PAUL.BRADLEY.J.1209885146 DN: c=US, o=U.S. Government, Date: 2017.01.09 15:23:36 -05'00'

BRADLEY J. PAUL, Chief Advanced Sensors Components Branch Aerospace Components & Subsystems Division

BEARD.TODD, Digitally signed by BEARD.TODD. (DN: c=US, c=U.S, c=U.S, Government, ou=DoD, ou=PKI, ou=USAF, on=BEARD.TODD.W.1140628677 On=BEARD.TODD.W.1140628677 Date: 2017.01.18 16:14:10-0500'

TODD W. BEARD, Lt Col, USAF Deputy Aerospace Components & Subsystems Division Sensors Directorate

This report is published in the interest of scientific and technical information exchange, and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

\*Disseminated copies will show "//Signature//" stamped or typed above the signature

## REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YY)                                                                                    | 2. REPORT TYPE      |                                                                                 | 3. DATES | COVERED (From - 10)                                                             |

|--------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------|

| February 2017                                                                                                | Final               |                                                                                 | 5 Nov    | ember 2014 – 30 September 2016                                                  |

| 4. TITLE AND SUBTITLE MULTIBAND RADIO FREQUEN                                                                | CY-INTERCONNE       | CT (MRFI)                                                                       | !        | 5a. CONTRACT NUMBER<br>FA8650-15-1-7519                                         |

| TECHNOLOGY FOR NEXT GEN                                                                                      | ERATION MOBILI      | E/AIRBORNE                                                                      | ;        | b. GRANT NUMBER                                                                 |

| COMPUTING SYSTEMS                                                                                            |                     |                                                                                 |          | 5c. PROGRAM ELEMENT NUMBER<br>61101E                                            |

| 6. AUTHOR(S)                                                                                                 |                     |                                                                                 |          | 5d. PROJECT NUMBER                                                              |

| Mau-Chung Frank Chang, Wei-Har                                                                               | n Cho, Jieqiong Du, | Yuan Du, Sheau Ji                                                               | iung     | 1000                                                                            |

| Lee, Yilei Li, and Chien-Heng Wor                                                                            | ng                  |                                                                                 | :        | 5e. TASK NUMBER                                                                 |

|                                                                                                              |                     |                                                                                 |          | N/A                                                                             |

|                                                                                                              |                     |                                                                                 | :        | 5f. WORK UNIT NUMBER                                                            |

|                                                                                                              |                     |                                                                                 |          | Y17Q                                                                            |

| 7. PERFORMING ORGANIZATION NAME(S) AI                                                                        | ND ADDRESS(ES)      |                                                                                 | ;        | B. PERFORMING ORGANIZATION REPORT NUMBER                                        |

| University of California, Los Ange                                                                           | eles                |                                                                                 |          | REPORT NUMBER                                                                   |

| 420 Westwood Plaza                                                                                           |                     |                                                                                 |          |                                                                                 |

| Los Angeles, CA 90095-1594                                                                                   |                     |                                                                                 |          |                                                                                 |

| 9. SPONSORING/MONITORING AGENCY NAM                                                                          | ME(S) AND ADDRESS(E | S)                                                                              |          | 10. SPONSORING/MONITORING<br>AGENCY ACRONYM(S)                                  |

| Air Force Research Laboratory                                                                                |                     | Defense Advanced                                                                |          | AFRL/RYDI                                                                       |

| Sensors Directorate Wright-Patterson Air Force Base, OH 4 Air Force Materiel Command United States Air Force |                     | Research Projects<br>Agency/DARPA/M<br>675 N Randolph Str<br>Arlington, VA 2220 | reet     | 11. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER(S)<br>AFRL-RY-WP-TR-2016-0200 |

| 12. DISTRIBUTION/AVAILABILITY STATEMEN                                                                       | ΙΤ                  |                                                                                 |          |                                                                                 |

Approved for public release; distribution is unlimited.

#### 13. SUPPLEMENTARY NOTES

This report is the result of contracted fundamental research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated 10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09. This material is based on research sponsored by Air Force Research laboratory (AFRL) and the Defense Advanced Research Agency (DARPA) under agreement number FA8650-15-1-7519. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation herein. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies of endorsements, either expressed or implied, of Air Force Research Laboratory (AFRL) and the Defense Advanced Research Agency (DARPA) or the U.S. Government. Report contains color.

#### 14. ABSTRACT

The aims of this two-phase research program were to analyze, model and realize a multiband radio frequency interconnect technology (MRFI) to enable high scalability and re-configurability for inter-CPU/Memory communications with an increased number of communication channels in the frequency-domain and reduced number of physical pads/wires to accomplish higher effective bandwidth, superior energy efficiency (in terms of energy/bit) and decreased size/area of both silicon (on-chip) and PCB (off-chip) for future mobile and airborne computing systems.

## 15. SUBJECT TERMS

multiband; RF interconnect; frequency-domain multiplexing; memory;

| 16. SECURIT               | Y CLASSIFICATIO | N OF:                        | 17. LIMITATION OF | 8. NUMBER OF | 19a. NAME OF RESPONSIBLE PERSON (Monitor)                       |  |

|---------------------------|-----------------|------------------------------|-------------------|--------------|-----------------------------------------------------------------|--|

| a. REPORT<br>Unclassified |                 | c. THIS PAGE<br>Unclassified | ABSTRACT:<br>SAR  | 104          | Alfred Scarpelli  19b. TELEPHONE NUMBER (Include Area Code) N/A |  |

# **Table of Contents**

| Section      |                                                                        | Page |

|--------------|------------------------------------------------------------------------|------|

| List of Figu | res                                                                    | iii  |

| List of Tabl | es                                                                     | vii  |

| 1. ACKN      | OWLEDGEMENT                                                            | 1    |

| 2. EXECU     | UTIVE SUMMARY                                                          | 2    |

| 3. INTRO     | DUCTION                                                                | 4    |

| 4. METH      | ODS, ASSUMPTIONS, AND PROCEDURES                                       | 9    |

| 4.1 Phas     | se I (Five-Band QPSK Parallel Link)                                    | 9    |

| 4.1.1        | Differential Mode Signaling                                            | 9    |

| 4.1.2        | TX and RX Designs                                                      |      |

| 4.1.3        | VCO Design and Calibration Algorithm                                   | 12   |

| 4.1.4        | Phase Synchronization and Implementation                               |      |

| 4.1.5        | One-byte MRFI bus designed with five carriers and QPSK modulation      | 20   |

| 4.1.6        | TX/RX Path                                                             | 21   |

| 4.1.7        | Physical Interconnect Emulations                                       | 22   |

| 4.1.8        | TX Design and Layout                                                   |      |

| 4.1.9        | TX/RX Design and Layout                                                |      |

| 4.1.10       | Frequency Carrier Generation.                                          | 25   |

| 4.1.11       | Wide-Tuning-Range, Low-Jitter PLL Design                               | 26   |

| 4.1.12       | VCO design                                                             |      |

| 4.1.13       | Frequency Band Selection and Process Tracking                          | 27   |

| 4.1.14       | Divider Design                                                         | 28   |

| 4.1.15       | Phase-Frequency Detector Design                                        | 28   |

| 4.1.16       | Charge Pump and Loop Filter Design                                     | 28   |

| 4.1.17       | Phase Delay Correction Algorithm                                       | 29   |

| 4.2 Phas     | se II (Tri-Band 16QAM Parallel Link)                                   | 29   |

| 4.2.1        | Self-Equalization of Double-Sideband Signaling                         |      |

| 4.2.2        | Transceiver System Analysis and Design                                 | 36   |

| 4.2.3        | Circuit Design of Tri-Band PAM-4 / 16-QAM Transmitter                  | 41   |

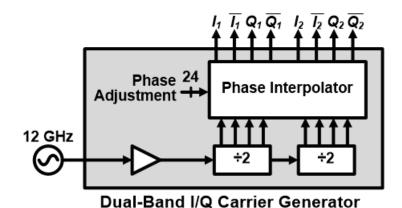

| 4.2.4        | Circuit Design of Dual-Band Carrier Generator                          | 43   |

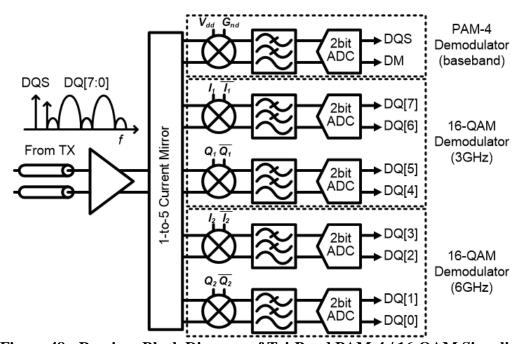

| 4.2.5        | Circuit Design of Tri-Band PAM-4 / 16-QAM Receiver                     | 44   |

| 4.2.6        | Circuit Design of 4-Lane Transceiver with Built-In Self-Testing (BIST) | 47   |

| 4.3 Dev      | elopment of MRFI Serial Links                                          | 49   |

| 4.3.1        | TX Design for MRFI Serial Links                                        | 51   |

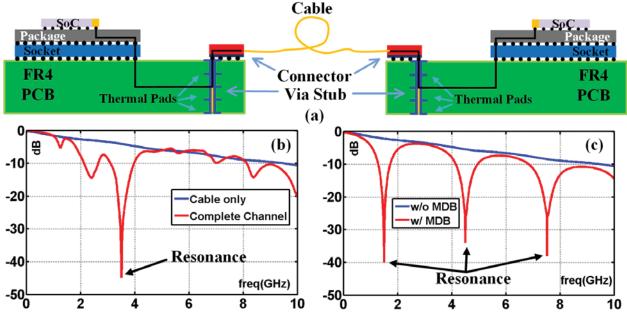

| 4.3.2        | Channel Responses with Frequency Notches                               | 53   |

| 4.3.3        | Phase Calibration and Phase Recovery for Serial Interface              | 55   |

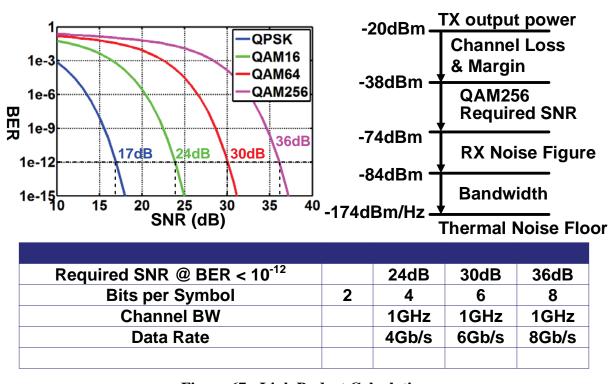

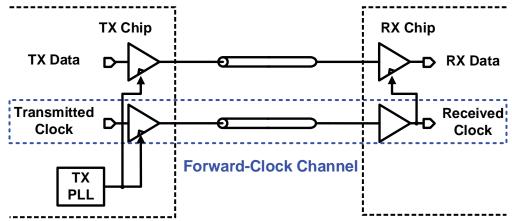

| 4.3.4        | Link Budget Calculation and Clock Forwarded Architecture               | 57   |

| 4.3.5        | Circuit Design Cognitive Tri-Band Transmitter Building Blocks          | 58   |

| 4.3.6        | MRFI Serial Link Receiver Design                                       |      |

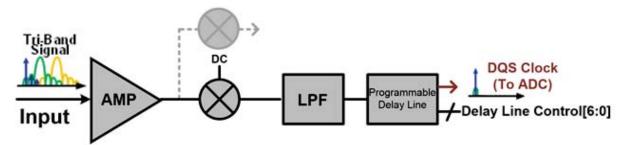

| 4.3.7        | Receiver Clock Recovery and Sample Timing Optimization                 | 62   |

| 4.3.8        | Inter-band Interference and the Cancellation Algorithm                 |      |

| 4.3.9        | Circuit Design of Multi-Band RF Receiver Analog Front-End              |      |

| Section                                                          | Page |

|------------------------------------------------------------------|------|

| 4.4 Receiver Front-End Die Photo and Post-Layout Simulation      | 69   |

| 4.5 Benchmarking with State-of-the-Art                           | 70   |

| 5. RESULTS AND DISCUSSIONS                                       | 72   |

| 5.1 Phase-I Test Results and Benchmarking with State-of-the-Art  | 72   |

| 5.2 Phase-II Test Results and Benchmarking with State-of-the-Art | 77   |

| 5.3 MRFI Serial Link Performance Summary                         | 81   |

| 5.3.1 TX Test Results and Benchmark with State-of-the-Art        | 81   |

| 5.3.2 RX Test Results and Benchmark with State-of-the-Art        | 85   |

| 6. CONCLUSION                                                    | 88   |

| 7. REFERENCES                                                    | 89   |

| LIST OF ACRONYMS, ABBREVIATIONS, AND SYMBOLS                     | 92   |

# **List of Figures**

| Figure                                                                                        | Page |

|-----------------------------------------------------------------------------------------------|------|

| Figure 1: Exemplary N <sup>th</sup> Processor with Eight Concurrent Memory Buses (256Bit/Bus) | 5    |

| Figure 2: Parallel Byte Bus (10Bit) Transmitted and Received Simultaneously via Multiple      |      |

| Frequency Carriers                                                                            | 6    |

| Figure 3: MRFI with Self-Track Pulse Generator and Restoration for I/O Data                   |      |

| Synchronization                                                                               |      |

| Figure 4: Direct Current Reduction Circuit with Process Variation Track                       |      |

| Figure 5: Differential Current Steering Mixer with Quarter Duty Cycle Carrier                 |      |

| Figure 6: Voltage Control Oscillator                                                          |      |

| Figure 7: CML Inverter Chain                                                                  |      |

| Figure 8: CML Inverter with Programmable Resistor                                             |      |

| Figure 9: Self-Calibration Controller                                                         |      |

| Figure 10: Flow Chart of Calibration Controller                                               |      |

| Figure 11: Circuit Blocks for Phase Adjustment                                                |      |

| Figure 12: Flow Chart for Phase Adjustment                                                    | 19   |

| Figure 13: Block Diagram of One-Byte MRFI by Five Frequency Carriers and QPSK                 |      |

| Modulation                                                                                    |      |

| Figure 14: Multi-band QPSK RF-Interconnect Channel Spectrum                                   |      |

| Figure 15: Layout of MRFI Test Chip in 40nm Technology                                        |      |

| Figure 16: TX/RX Path in the Full-Chip Layout                                                 |      |

| Figure 17: Layout of the Interconnect Emulator                                                |      |

| Figure 18: Layout of the Five-Band QPSK Transmitter                                           |      |

| Figure 19: TX Output Current Spectrum in Typical/Worst / Best Cases and SF/FS Corners         |      |

| Figure 20: Layout of the Five-Band QPSK Receiver                                              |      |

| Figure 21: Frequency Response of Current Gain and Group Delay of the Current-Mode LPF         |      |

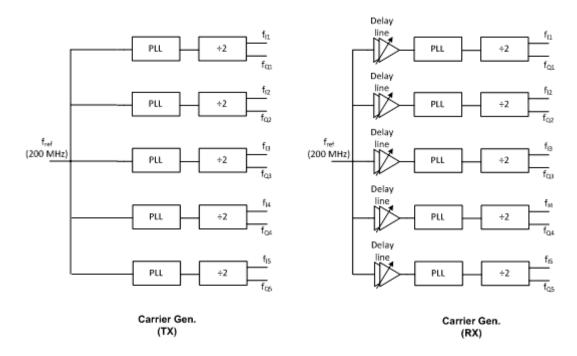

| Figure 22: Carrier Generation in the Full Chip Layout                                         |      |

| Figure 23: Carrier Generation Block Diagram                                                   |      |

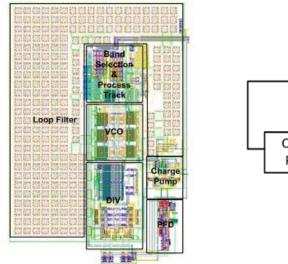

| Figure 24: Blocks in the Layout of Carrier Generation                                         |      |

| Figure 25: PLL Layout.                                                                        |      |

| Figure 26: PLL Block Diagram                                                                  |      |

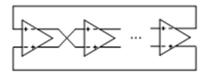

| Figure 27: Ring Oscillator VCO                                                                |      |

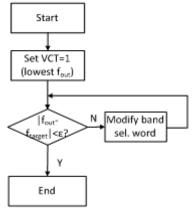

| Figure 28: Band Selection Algorithm Flow Chart                                                |      |

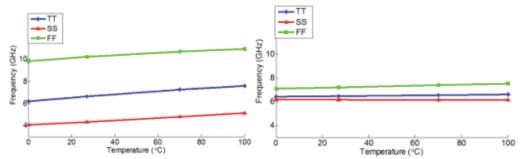

| Figure 29: Free-Run Frequency of VCO (a) Without and (b) With Process Track                   |      |

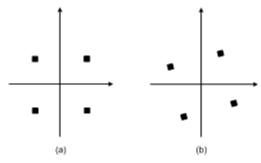

| Figure 30: Received Constellation (a) Without and (b) With Phase Error                        |      |

| Figure 31: Phase Adjustment Algorithm Flow Chart                                              | 29   |

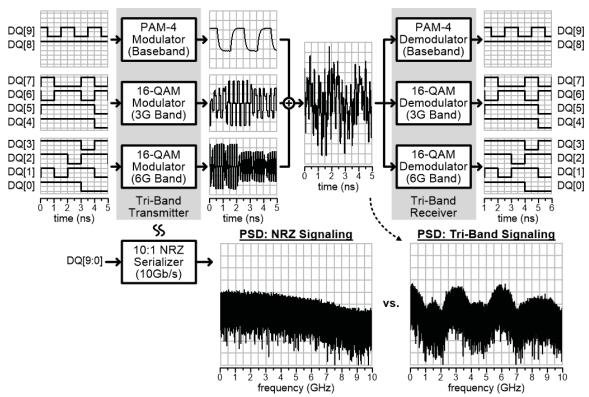

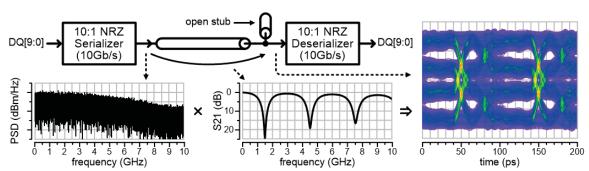

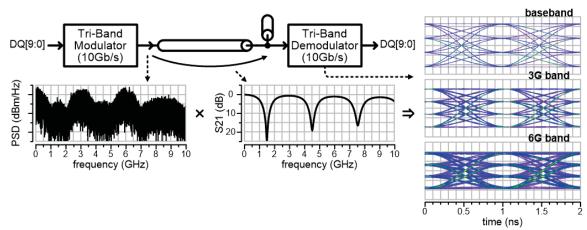

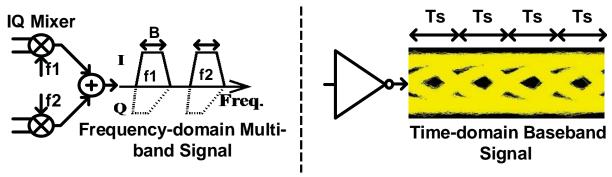

| Figure 32: Tri-Band Signaling in Time and Frequency Domain, and Comparison with NRZ           |      |

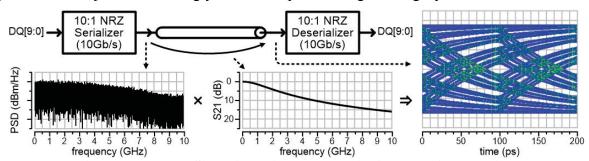

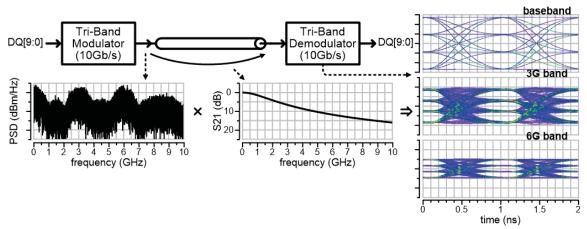

| Signaling                                                                                     |      |

| Figure 33: NRZ Signaling with Channel Frequency Notches                                       |      |

| Figure 34: PAM-4 / 16-QAM Tri-Band Signaling with Channel Frequency Notches                   |      |

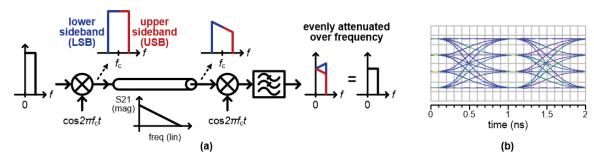

| Figure 35: NRZ Signaling with Monotonic Channel Attenuation.                                  |      |

| Figure 36: PAM-4 / 16-QAM Tri-Band Signaling with Monotonic Channel Attenuation               |      |

| Figure 37: (a) Self-Equalization and (b) DSR Signaling Output Eye Diagram                     | 34   |

| rigure                                                                                                                                                                                                      | age   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

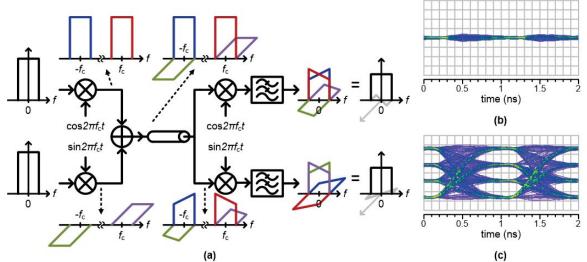

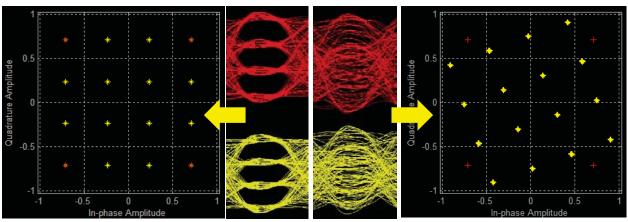

| Figure 38: (a) I/Q Interference of Quadrature Modulation due to Uneven Channel Attenuation; (b) Folded Waveform of I/Q Interference in Time-Domain; (c) Degraded Output Eye Diagram due to I/Q Interference | 35    |

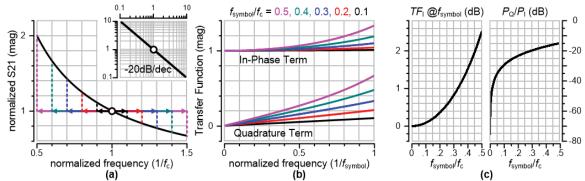

| Figure 39: (a) Example of Channel Frequency Response with Slope of -20dB/dec;                                                                                                                               | . 55  |

| (b) Effective I/Q Transfer Functions Derived from the Example; and (c) Peaking/Interference                                                                                                                 |       |

| of the Transfer Functions                                                                                                                                                                                   | . 36  |

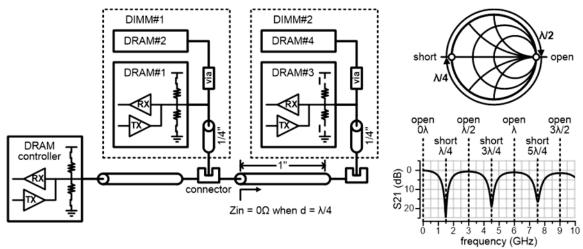

| Figure 40: Dual-DIMM Multi-Drop Memory Bus and Analysis of Induced Frequency                                                                                                                                | . 50  |

| Notches                                                                                                                                                                                                     | . 37  |

| Figure 41: (a) Adjacent-Band Interference Analysis; (b) Folded Waveform of the Remaining                                                                                                                    |       |

| Interference; (c) the Eye Diagram of the Demodulated Signal from 6GHz Band                                                                                                                                  |       |

| Figure 42: Output Eye Diagram of the PAM-4 / 16-QAM Tri-Band Signaling and                                                                                                                                  | . 50  |

| Constellation of 3GHz and 6GHz Bands                                                                                                                                                                        | 30    |

| Figure 43: Phase Noise Shaping of Synchronous Signaling and its Effect on Carrier Jitter                                                                                                                    |       |

| Figure 44: Bit Error Rate and Jitter Requirement Calculation of 16-QAM                                                                                                                                      |       |

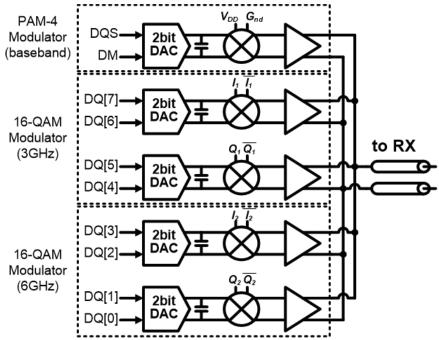

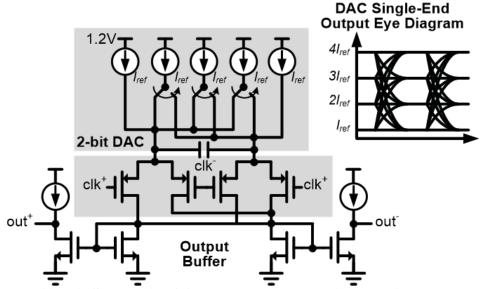

| Figure 45: Transmitter Block Diagram of Tri-Band PAM-4 / 16-QAM Signaling                                                                                                                                   |       |

| Figure 46: Circuit Schematic of One Modulation Path in the Tri-Band Transceiver                                                                                                                             |       |

| Figure 47: Block Diagram of the Dual-Band I/Q Carrier Generator                                                                                                                                             |       |

| Figure 48: Receiver Block Diagram of Tri-Band PAM-4 / 16-QAM Signaling                                                                                                                                      |       |

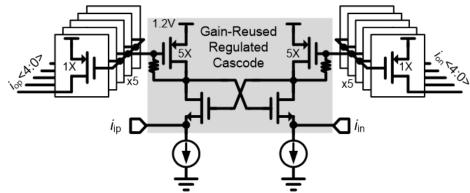

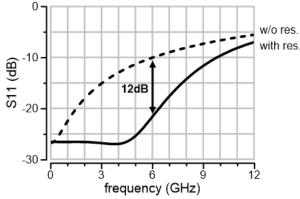

| Figure 49: Circuit Schematic of the Gain-Reused Regulated Cascade Input Buffer                                                                                                                              |       |

| Figure 50: Simulated S <sub>11</sub> Frequency Response of the Gain-Reused Regulated Cascade                                                                                                                | . т   |

| Input Buffer                                                                                                                                                                                                | 45    |

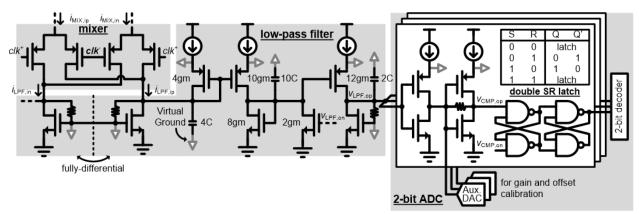

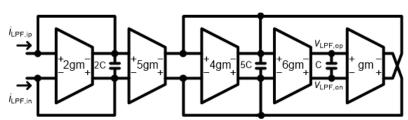

| Figure 51: Circuit Schematic of One Demodulation Path in the Tri-Band Transceiver                                                                                                                           | -     |

| Figure 52: Block Diagram of the 3 <sup>rd</sup> -Order Bessel Gm-C Low-Pass Filter                                                                                                                          |       |

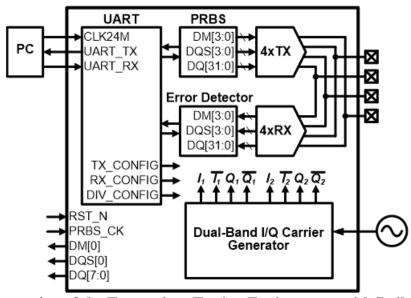

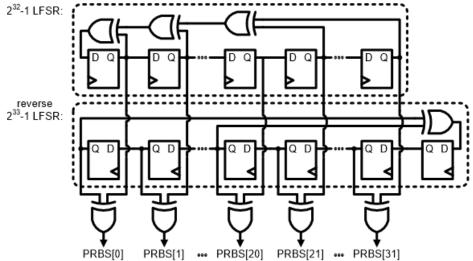

| Figure 53: Illustration of the Transceiver Testing Environment with Built-In Self-Tester                                                                                                                    |       |

| Figure 54: 32-bit PRBS Generator Implemented with Reversely Combined Linear Feedback                                                                                                                        | . 🔻 / |

| Shift Registers (LFSRs)                                                                                                                                                                                     | . 48  |

| Figure 55: Illustration of the Transceiver Testing Environment with Built-in Self-Testing                                                                                                                   |       |

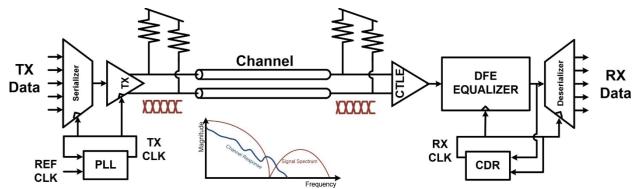

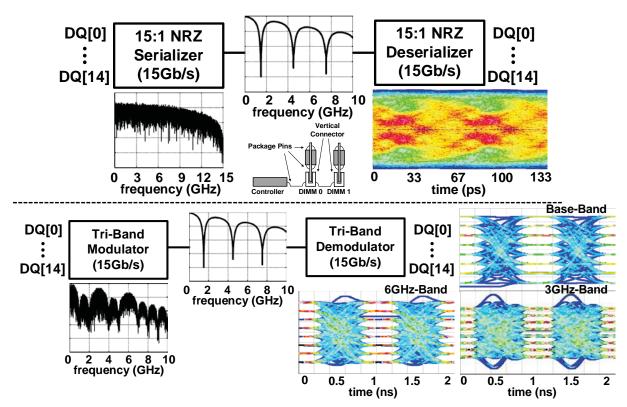

| Figure 56: System Architecture of a Typical NRZ Serial Link                                                                                                                                                 |       |

| Figure 57: Conceptual Multi-Band Serial Links                                                                                                                                                               |       |

| Figure 58: Self-Equalization of Direct-Conversion Multi-Band Links [7]                                                                                                                                      |       |

| Figure 59: System Architecture of Cognitive Transmitter with Multi-Band Signaling and                                                                                                                       | 1     |

| Channel Learning Mechanism                                                                                                                                                                                  | 52    |

| Figure 60: (a) Common Periphery Serial Link; (b) Cable-Only and Complete Channel                                                                                                                            |       |

| Insertion Loss; (c) With and Without MDB Insertion Loss                                                                                                                                                     | 53    |

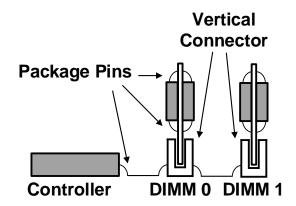

| Figure 61: Memory Controller with Two DIMMS per Channel                                                                                                                                                     |       |

| Figure 62: Time-Domain Single-Bit Response                                                                                                                                                                  |       |

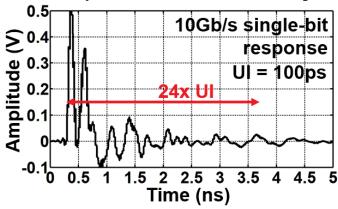

| Figure 63: Conceptual Comparison of Baseband TX and Multi-Band TX                                                                                                                                           |       |

| Figure 64: Baseband TX vs Multi-Band TX on Multi-Drop Memory Interface Channel                                                                                                                              |       |

| Figure 65: Phase Offset Impact on Data Eye Quality                                                                                                                                                          |       |

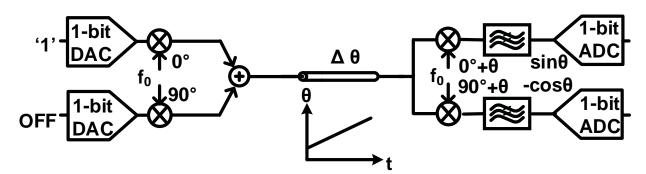

| Figure 66: Proposed Phase Calibration Scheme with One-Bit ADC                                                                                                                                               |       |

| Figure 67: Link Budget Calculation                                                                                                                                                                          |       |

| Figure 68: Conventional Source-Synchronized / Forward Clocking Architecture                                                                                                                                 | 58    |

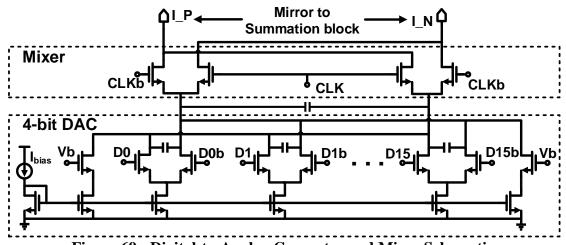

| Figure 69: Digital-to-Analog Convertor and Mixer Schematics                                                                                                                                                 |       |

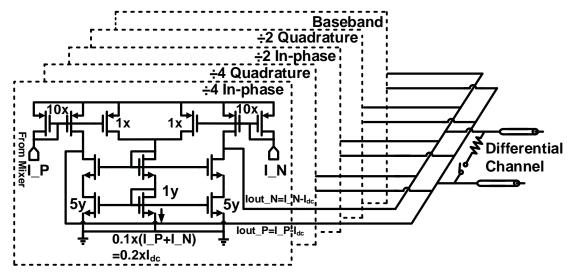

| Figure 70: 10 Five-Slice Summation Block Schematics                                                                                                                                                         |       |

| Figure                                                                                          | Page    |

|-------------------------------------------------------------------------------------------------|---------|

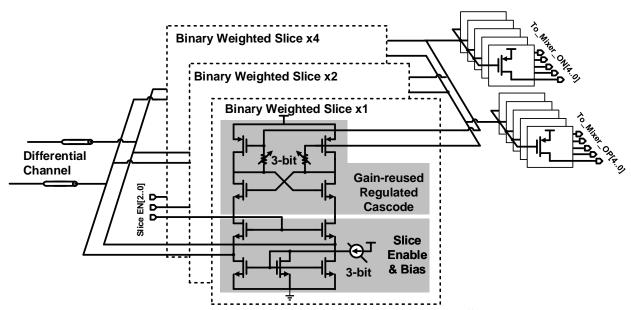

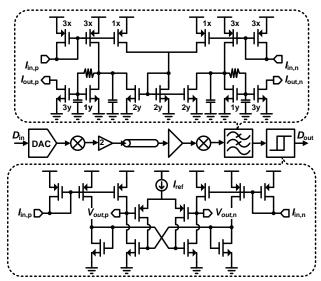

| Figure 71: Fully Reconfigurable Receiver Front End Schematics                                   | 59      |

| Figure 72: Embedded Forwarded Clock                                                             |         |

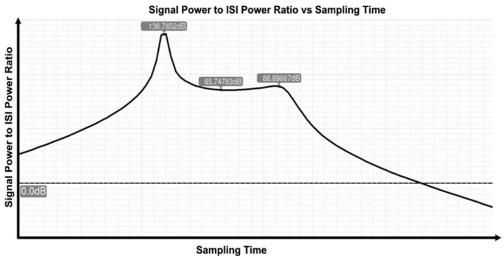

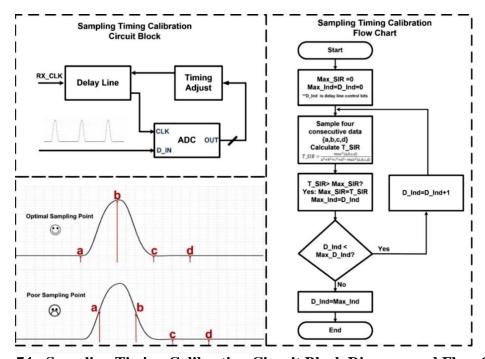

| Figure 73: SIR vs Sampling Timing                                                               | 63      |

| Figure 74: Sampling Timing Calibration Circuit Block Diagram and Flow Chart                     | 63      |

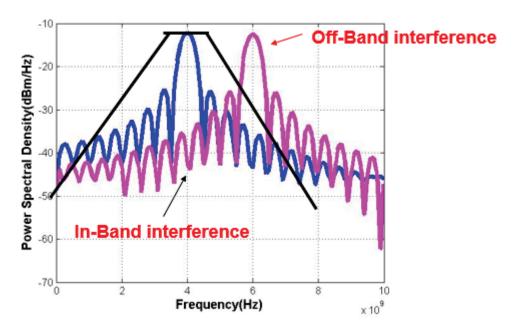

| Figure 75: Inter-band Interferences in Frequency Domain                                         |         |

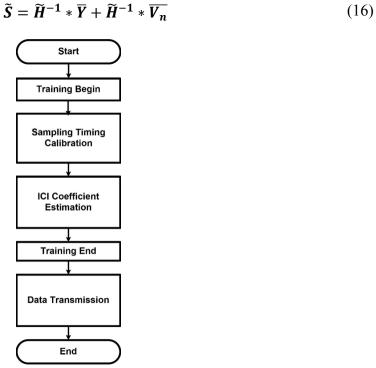

| Figure 76: System Operation Flow                                                                |         |

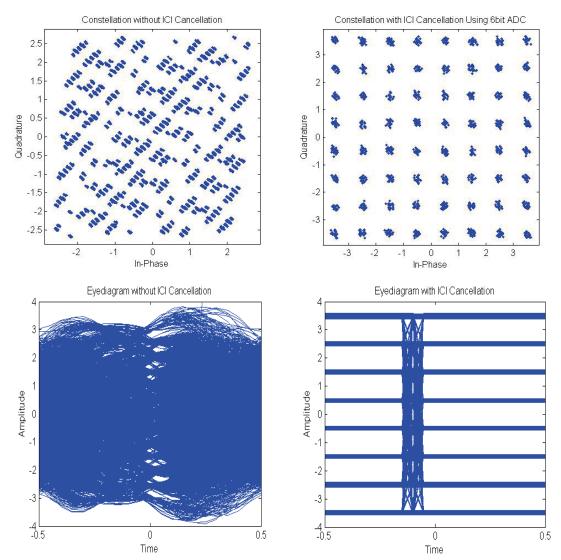

| Figure 77: Constellation and Eye Diagram With and Without Inter-Band Interference               | 66      |

| Cancellation                                                                                    |         |

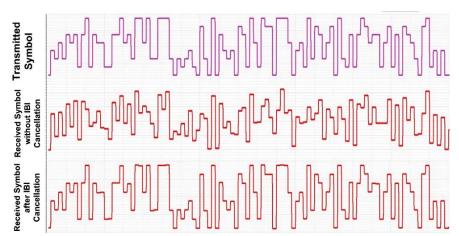

| Figure 78: Transient Response With and Without Inter-Band Interference Cancellation             |         |

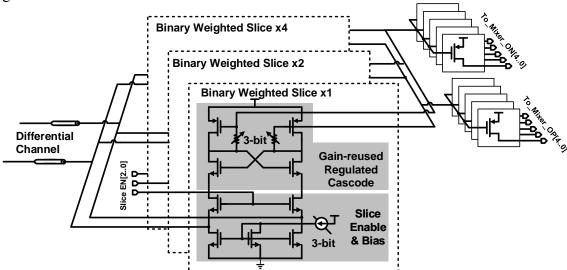

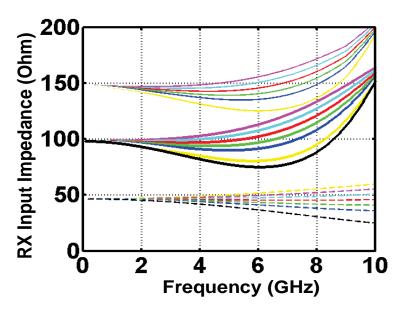

| Figure 79: Programmable Receiver Input Buffer Schematic                                         |         |

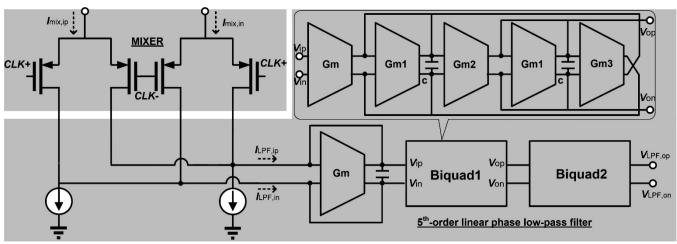

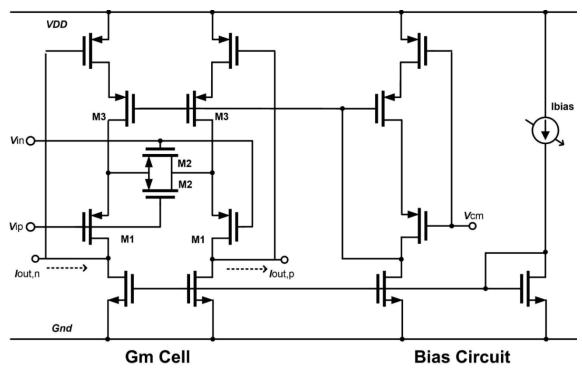

| Figure 81: Mixer and Low-Pass Filter Schematics                                                 |         |

| Figure 82: Linearized Transconductance (Gm) Cell for Low-Pass Filter                            |         |

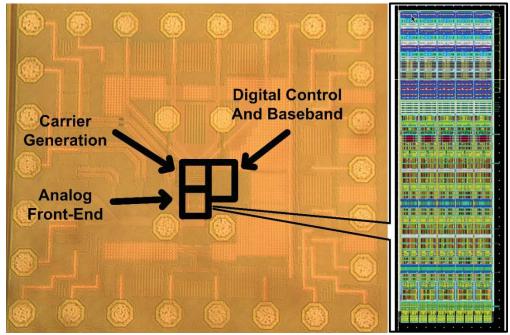

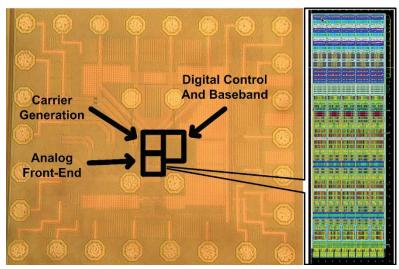

| Figure 83: Die Photo and Layout of Receiver Front-End                                           |         |

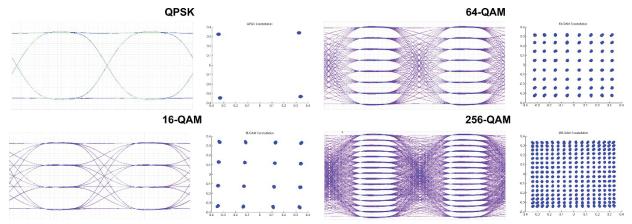

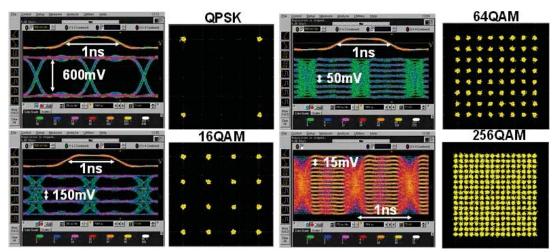

| Figure 84: Eye Diagram and Constellation of Post Layout Simulation                              |         |

| Figure 85: Channel Spectrum of the FDM Memory Interface with Five-Band QPSK                     | , 70    |

| Modulation                                                                                      | 72      |

| Figure 86: Illustration of Self-equalized QPSK Modulation                                       |         |

| Figure 87: Block Diagram of the Five-Band QPSK Transceiver                                      |         |

| Figure 88: Schematics of the Differential Current-Steering DAC and the Receiver Input           |         |

| Figure 89: Schematics of the Current-Mode Low-Pass Filters and the Current-Mode                 | / -     |

| Schmitt Trigger                                                                                 | 74      |

| Figure 90: Micrograph of the Test Chip with Both TX/RX and 1-pF On-Chip Interconnec             | tion to |

| Emulate TSV Loading in 3DIC                                                                     |         |

| Figure 91: (a) Demodulated 400-Mb/s 2 <sup>31</sup> -1 PRBS Eye Diagrams of I/Q Channels at     |         |

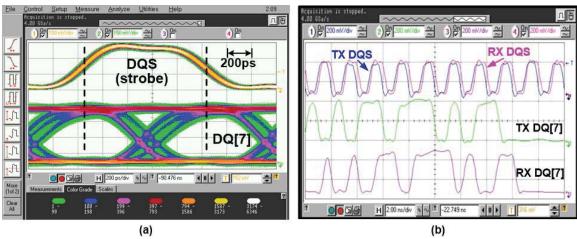

| $f_1$ (Upper) and $f_2$ (Lower); (b) 250-Mb/s $2^{31}$ -1 PRBS Eye Diagrams of Original (Upper) |         |

| and Demodulated (Lower) DQ/DQS                                                                  | 75      |

| Figure 92: Top View of the Test Board with Separate TX/RX Connected with a 5-cm                 |         |

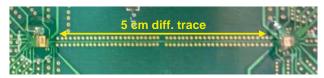

| FR-4 Differential Trace                                                                         | 75      |

| Figure 93: (a) Demodulated 400-Mb/s 2 <sup>31</sup> -1 PRBS Eye Diagrams of the 1-cm (Upper)    |         |

| and the 5-cm (Lower) Test Boards; (b) Latency of 2.4 ns Found by Subtracting Out                |         |

| Measured Cable Delay (Upper) from Measured Total Delay (Lower, Output Inverted)                 | 76      |

| Figure 94: Real-Time Flexible BER Testing Platform for Five-Band QPSK Transceiver               | 76      |

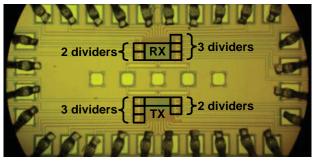

| Figure 95: Die Photo of the Four-Lane Tri-Band Transceiver with Built-In Self-Tester            | 77      |

| Figure 96: Testing Environment and the Test Board with 2-Inch Dense FR-4 Differential           |         |

| Bus                                                                                             |         |

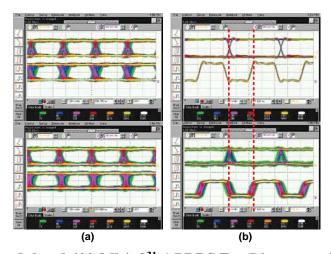

| Figure 97: Measured Output Eye Diagram and Transient Waveform                                   |         |

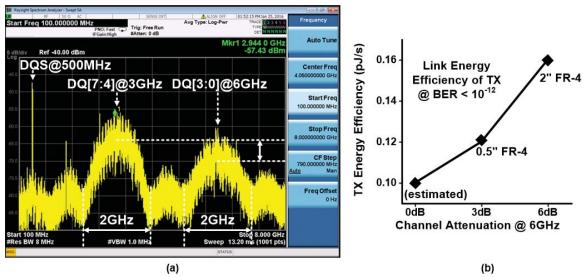

| Figure 98: Transmitter Output Spectrum and Energy Efficiency vs Channel Attenuation             |         |

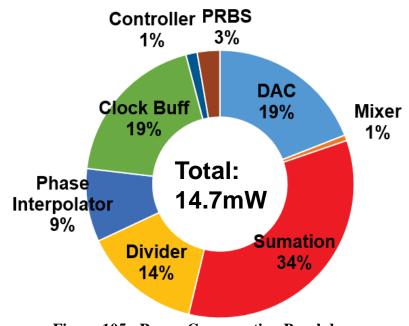

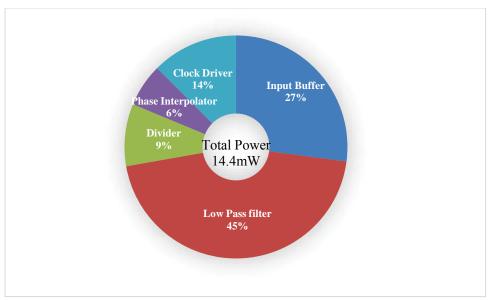

| Figure 99: Power Breakdown of the Four-Lane Tri-Band Transceiver                                |         |

| Figure 100: Measurement Platform                                                                | 81      |

| Figure 101: Time-Domain Measurement Results                                                     |         |

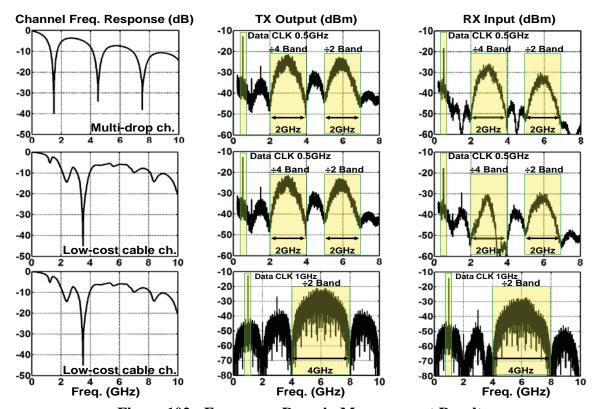

| Figure 102: Frequency-Domain Measurement Results                                                |         |

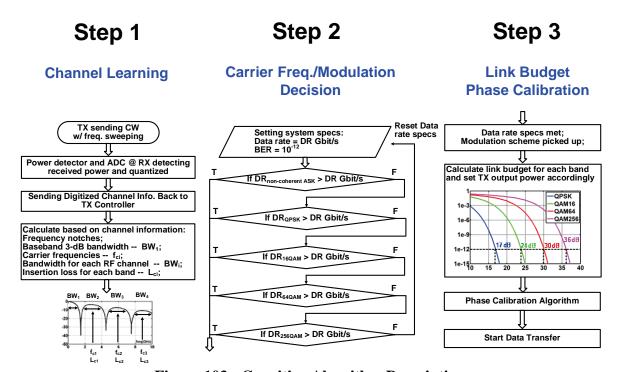

| Figure 103: Cognitive Algorithm Description.                                                    |         |

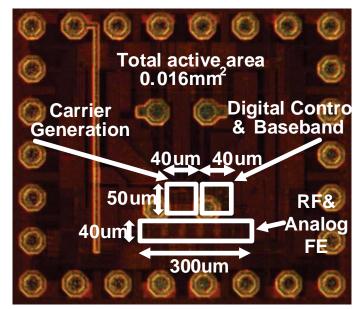

| Figure 104: Die Photo of Cognitive Tri-Band Transmitter                                         | 84      |

| Figure      |                                                       | Page |

|-------------|-------------------------------------------------------|------|

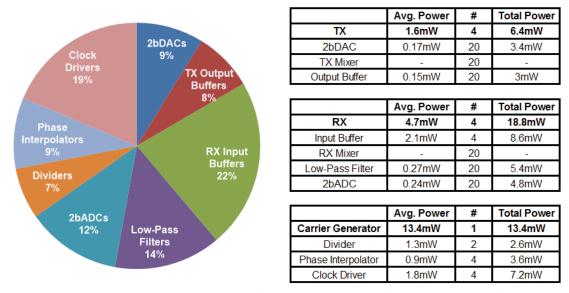

| Figure 105: | Power Consumption Breakdown                           | 84   |

| Figure 106: | Die Photo and Layout of MRFI Serial Link RX Front-End | 85   |

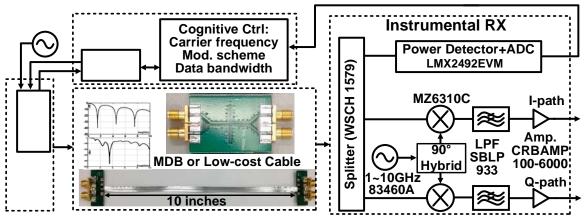

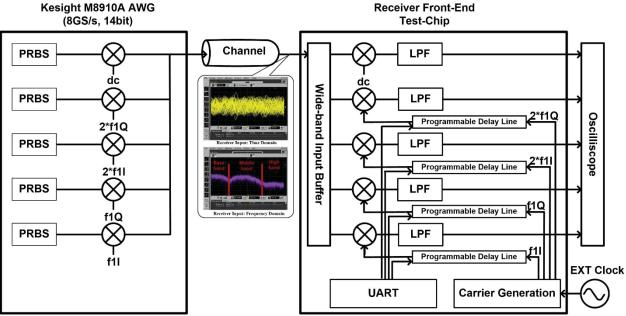

| Figure 107: | Measurement Platform                                  | 86   |

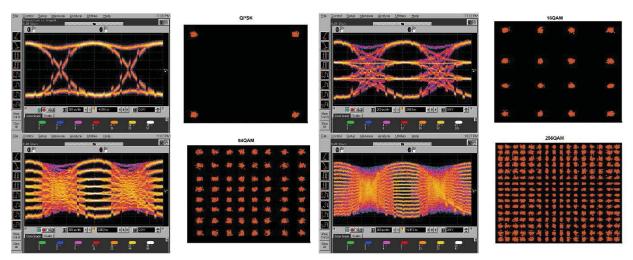

| Figure 108: | Measurement Results (Eye Diagram and Constellation)   | 86   |

| Figure 109: | Power Consumption Breakdown                           | 87   |

# **List of Tables**

| Table    |                                                                            | Page |

|----------|----------------------------------------------------------------------------|------|

| Table 1. | Targeted MRFI Specification                                                | 3    |

|          | Comparison of MRFI with State-of-the-Art Counterparts                      |      |

| Table 3. | ADC Resolution Specs of Phase Calibration for Different Modulation Schemes | 56   |

| Table 4. | MRFI Serial Link Performance Metrics                                       | 60   |

| Table 5. | Benchmarking with State-of-the-Art                                         | 71   |

| Table 6. | Benchmarking with State-of-the-Art                                         | 80   |

| Table 7. | Benchmarking MRFI Serial Link TX Performance with State-of-the-Art         | 85   |

## 1. ACKNOWLEDGEMENT

The authors would like to thank Taiwan Semiconductor Manufacturing Company (TSMC) for chip fabrication, Minji Zhu for help of assembling and testing in the University of California, Los Angeles (UCLA) Center for High Frequency Electronics, and Dr. Afshin Momtaz at Broadcom Corporation for valuable advice and technical discussions on the high-speed wireless implementation. The authors would also like to thank Janet Lin for proofreading and editing the final technical report.

## 2. EXECUTIVE SUMMARY

The aims of this two-phase research program were to analyze, model and realize a multiband radio frequency interconnect technology (MRFI) to enable high scalability and re-configurability for inter-central processing unit (CPU)/Memory communications with an increased number of communication channels in the frequency-domain and reduced number of physical pads/wires to accomplish higher effective bandwidth, superior energy efficiency (in terms of energy/bit) and decreased size/area of both silicon (on-chip) and printed circuit board (PCB) (off-chip) for future mobile and airborne computing systems.

The goal of Phase I (6 months) was to quickly validate the functionality of all complementary metal oxide semiconductor (CMOS) building blocks (including digital to analog converter (DAC), analog to digital converter (ADC), Modulator, de-Modulator, Oscillators, phase lock loops (PLL), Track Pulse Generator/Restorer) and the data access and transfer operations of the entire byte of data (containing 8 bit of data, 1 bit of byte mask, 1 bit of data strobe) simultaneously by using 5 frequency carriers (1.6GHz, 2.4GHz, 3.2GHz, 4GHz, and 5.2GHz) and Quadrature Phase Shift Keying (QPSK) modulation, for verifying its effective bandwidth, energy efficiency, latency, etc. We successfully delivered a 1-Byte MRFI Bus prototype by using 40nm CMOS technology according to the performance specs listed in the 2<sup>nd</sup> column of Table 1.

In Phase II (12 months), we taped out One Full Channel (4-Byte or 32bit data, 4 bit of byte mask, 4 bit of data strobe) MRFI Physical Layer (PHY) based on Taiwan Semiconductor Manufacturing Company (TSMC) 28nm CMOS technology. The 4-Byte MRFI PHY was designed by using more energy/area-efficient 16 quadrature amplitude modulation (QAM) signal modulation and 2 frequency carriers (two frequency carriers at 1.2GHz and 2.4GHz, respectively) in addition to the baseband for achieving even higher energy efficiency (<0.5pJ/bit) and smaller Input/Output (I/O) die area. We again successfully delivered a Full Channel 4-Byte MRFI PHY on 28nm CMOS technology according to the performance specs listed in the 3<sup>rd</sup> column of Table 1.

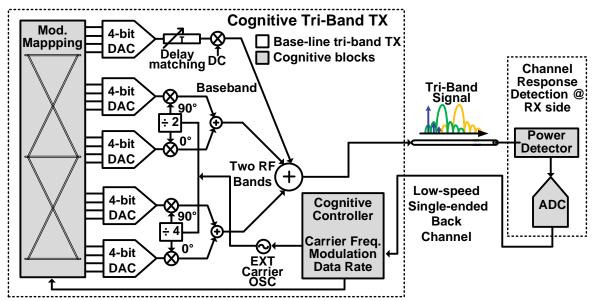

In addition to developing the aforementioned MRFI PHY for parallel interconnect links primarily applicable to multi-byte communications between CPU and memories, we also evaluated MRFI serial links for integrating heterogeneous die on high performance interposer. A serial link transmitter in 28nm CMOS technology was developed with simultaneous high-speed (34Gbps) and high-efficiency (pJ/bit) by using 3-bands (2-carriers/1-baseband) and up to 256QAM modulation. A corresponding serial link receiver was also developed by using the same number of carriers and modulation schemes.

**Table 1. Targeted MRFI Specification**

|                               | Phase I                    | Phase II                   |

|-------------------------------|----------------------------|----------------------------|

| Integration scale             | 1 byte TX/RX               | 4 byte PHY TX/RX           |

| Number of frequency carriers  | 5                          | 2                          |

| Frequency selected            | 1.6/2.4/3.2/4/5.2GHz       | 1.2/2.4GHz                 |

| Modulation                    | QPSK                       | QAM16                      |

| Number of bit per byte        | 10                         | 10                         |

| Data clock rate               | 200MHz                     | 300MHz                     |

| Target peak bandwidth of 2048 | 409.6 Gbit/s               | 614.4 Gbit/s               |

| bit memory bus                |                            |                            |

| Target I/O current per pair   | 1.8 ma                     | 0.9 ma                     |

| Target I/O current per bit    | 0.18 ma                    | 0.09 ma                    |

| Target I/O power per bit      | < 1 pJ/bit                 | <0.5pJ/bit                 |

| Latency of PHY delay          | < 3 ns                     | < 4.5 ns                   |

| Process node                  | 40nm (TSMC)                | 28nm (TSMC)                |

| Supported memory channel      | NA                         | 1 Channel                  |

| Area per bit in PHY           | 900 um <sup>2</sup> (40nm) | 350 um <sup>2</sup> (32nm) |

## 3. INTRODUCTION

The advancement of modern massive parallel computing relies on innovative development of multi-core CPUs and effective interconnects that can link multi-core CPUs with various caches and memories. Advanced mobile and/or airborne computing platforms have even more complicated issues than those of typical computing systems: their power consumption must be minimized while still offering high data rate and low latency to support multi-functional system applications. In addition to data processing, the memory bandwidth required by multi-graphics processing unit (GPU)/accelerated processing unit (APU) applications is equally demanding. These obstacles call for the need for mobile/airborne platforms to be implemented by using an interconnect system (in both architecture and technology) that can facilitate not only higher bandwidth, lower latency, and lower power consumption but also with more competitive production cost.

The conventional memory hierarchy of high speed computing systems suffers serious constraints from its latency, bandwidth and power consumption due to conventional time-domain multiplexing techniques such as Low Power Double-Data-Rate (LPDDR). For instance, the size of the on-chip cache is limited to 128Mbyte due to processing yield problems of integrating memories with Application-Specific Integrated Circuits (ASIC). The memory bus width and memory channels are also limited, respectively, owing to excessive power dissipation from large number of chip interconnects with high speed signaling and clocking. To overcome such technical barriers, we proposed to develop a novel MRFI interconnect technology by using multiband concurrent signal processing through shared physical wires (either traditional T-lines or advanced through-silicon vias (TSV) to revolutionize future inter-CPU/Memory interconnect technology with the highest bandwidth, lowest latency, lowest energy/bit (by factor 10 lower than that of existing LPDDR) and the lowest packaging cost (compatible with traditional low cost 2D Fine Pitch Ball Grid Array (FBGA) and high performance 2.5D Interposer and 3DIC). Such an interconnect scheme is not only more scalable than state-of-art technologies due to its use of multiband and QAM communications but also more reconfigurable by using software programming for load balance among all communication channels. Our proposed interconnect scheme would enable performance/ energy/ cost-effective connectivity to both on and off-chip larger size caches, and to wider memory bus with larger number of concurrent memory channels, without paying penalties to accessing latency, power consumption, or production yield/cost.

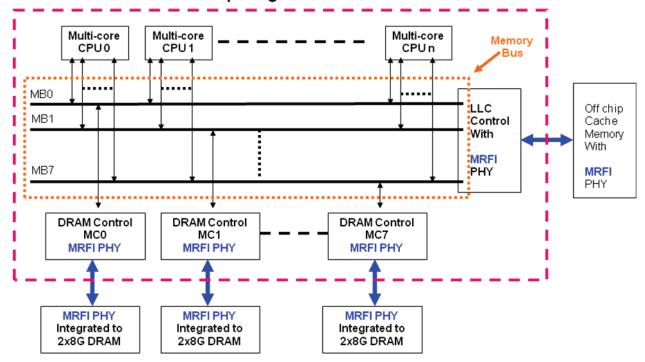

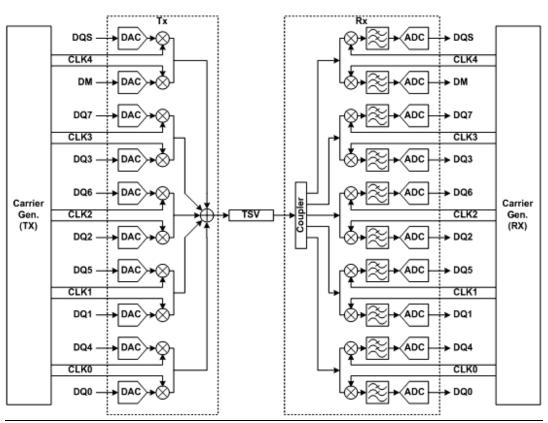

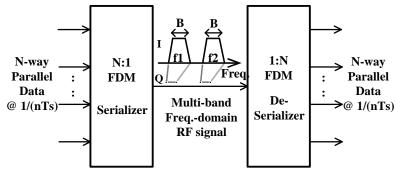

Figure 1 shows the designed high performance computing node in multi-core massive parallel computing systems based on our proposed MRFI. Figure 2 shows a concurrent multi-bit byte bus which can simultaneously access and transfer 10 bits (8 bits of data, 1 bit of byte mask and 1 bit of data strobe) by using multiple frequency carriers with separate in phase and quadrature phase (I/Q) modulations.

## A computing node with multi-cores

Figure 1: Exemplary N<sup>th</sup> Processor with Eight Concurrent Memory Buses (256Bit/Bus)

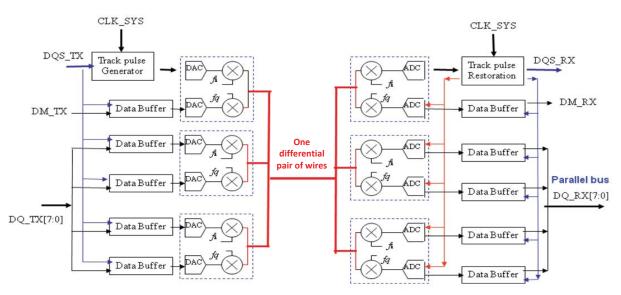

Figure 2 shows a concurrent multi-bit byte bus which can simultaneously access and transfer 10 bits (8 bits of data, 1 bit of byte mask and 1 bit of data strobe) by using multiple frequency carriers with separate I/Q modulations. The modulated signal will be transmitted through differential pair of wires between CPUs and memories, and then demodulated by the same frequency carriers to restore the data back to a parallel bus. This implies that one can reduce the number of interconnects in Wide-input/output (I/O) by a factor X5. In this exemplary system, one only uses 892 interconnects for communicating 4096 I/O signals. Furthermore, MRFI PHY (i.e. transceivers) will operate under current steering logic over a differential pair circuitry. This can also reduce the simultaneous switching noise (SSN) problem to several orders-of-magnitude lower than that of competing Wide-I/O where large rail-to-rail CMOS logic swings are being used.

Figure 2: Parallel Byte Bus (10Bit) Transmitted and Received Simultaneously via Multiple Frequency Carriers

Furthermore, since MRFI modulates bus data in frequency domain and traditional transmission line problems only occur on its carriers and not on its low frequency data, it is therefore more forgiving in choosing its packaging types and does not require costly 3DIC as that of Wide-I/O. This allows us to deploy MRFI PHY over low cost conventional FBGA packaging technologies. This also shows that we can solve most Wide-I/O problems and retain its performance with even lower power consumption (X5 according to simulations) as well as with lower cost production.

## **MRFI Performance Benchmarking**

Table 2. Comparison of MRFI with State-of-the-Art Counterparts

|                                            | LPDDR4<br>(Intel and<br>others)                                              | Wide I-O<br>(Samsung)             | R+LPDDR3<br>(RAMBUS)                                                         | MRFI                                                                  |

|--------------------------------------------|------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Signal type                                | Single-ended                                                                 | Single-ended                      | Single-ended                                                                 | Differential                                                          |

| Voltage swing                              | voltage mode  400mv center Vtt=Vdd/2                                         | voltage mode  1.2V rail-to- rail  | 300mv near ground                                                            | differential +/- 15mv with common mode                                |

| Signal toggling rate                       | 3.2GHz                                                                       | 0.2GHz                            | 3.2GHz                                                                       | <b>0.3GHz</b> with carrier modulation                                 |

| Termination                                | Parallel vtt -<br>terminated at<br>50ohm                                     | un-terminated                     | parallel<br>ground-<br>terminated 50<br>ohm                                  | un-terminated<br>(leads to no<br>power dissipation<br>by terminators) |

| Minimum I/O drive<br>per I/O signal        | >8ma                                                                         | >0.8 ma                           | >6ma                                                                         | 0.8ma (pair)                                                          |

| Maximum loading                            | 5PF                                                                          | 1PF                               | 5PF                                                                          | 1PF                                                                   |

| Number of signals in I/O interface         | <b>76</b> (2ch)                                                              | <b>773</b> (4ch)                  | <b>76</b> (2ch)                                                              | <b>75</b> pair (4ch)                                                  |

| Minimum interface current                  | >608 ma                                                                      | >678 ma                           | >456 ma                                                                      | 60 ma                                                                 |

| Interface SSN with (1nH) parasitic         | 1.94V (serious aggressor)                                                    | 0.136v<br>(possible<br>aggressor) | 1.46v (serious aggressor)                                                    | 0.001v (not aggressor)                                                |

| Required Power-<br>ground to combat<br>SSN | >140                                                                         | >427                              | >140                                                                         | >33 pair                                                              |

| Minimum interface<br>Pads                  | >216 pads                                                                    | >1200 TSV                         | >216 pads                                                                    | 216 pads                                                              |

| PHY size with pads or TSV                  | 216 *(45*450)<br>28lp ~5X                                                    | 1200*(45*90)<br>28lp ~5X          | 216*(45*450)<br>28lp ~5X                                                     | 216*45*90 28lp<br>~1X                                                 |

| Package type                               | PoP, discrete<br>Package, 256<br>FBGA<br>(14mmx14mm)<br>for dual<br>channels | 3DIC                              | PoP, discrete<br>Package, 256<br>FBGA<br>(14mmx14mm)<br>for dual<br>channels | PoP, discrete<br>package, 216<br>FBGA for quad<br>channels, 3DIC      |

| Number of channel per device               | 2                                                                            | 4                                 | 2                                                                            | 4                                                                     |

| Time Multiplex: Demultiplex                | 8:1 / 1:8                                                                    | NA                                | 8:1 / 1:8                                                                    | NA                                                                    |

| Required skew<br>adjust for each<br>DQ/DQS                            | yes                                     | no                                         | yes                                     | no                                                    |

|-----------------------------------------------------------------------|-----------------------------------------|--------------------------------------------|-----------------------------------------|-------------------------------------------------------|

| Write leveling                                                        | required                                | NA                                         | required                                | NA                                                    |

| CA Training                                                           | required                                | NA                                         | required                                | NA                                                    |

| Latency in TX PHY for Mux, skew adjustment, fly time                  | >4 ns (8 clk of 3.2GHz, PCB fly time)   | 5 ns (register delay)                      | >4 ns (8clk of 3.2GHz, PCB fly time)    | 1.2 ns (DAC,<br>Modulation<br>delay, PCB fly<br>time) |

| Latency in RX PHY<br>for demux, skew,<br>byte/word align, fly<br>time | >6 ns (DLL adjust, align, demux)        | <b>5 ns</b> (register delay)               | >6 ns (DLL adjust, align, demux)        | 1.8 ns<br>(demodulation,<br>Low pass filter)          |

| TC 4 1 1 4 C                                                          |                                         |                                            |                                         |                                                       |

| Total latency of TX/RX PHY                                            | >10 ns                                  | >10 ns                                     | >10 ns                                  | 3 ns                                                  |

| 3                                                                     | >10 ns<br>102.4Gb/s at<br>3.2Ghz toggle | >10 ns<br>102.4Gb/s at<br>0.2GHz<br>toggle | >10 ns<br>102.4Gb/s at<br>3.2Ghz toggle | 3 ns 153.6Gb/s at 0.3Ghz toggle with modulation       |

| TX/RX PHY Peak bandwidth per                                          | 102.4Gb/s at                            | <b>102.4Gb/s</b> at 0.2GHz                 | 102.4Gb/s at                            | 153.6Gb/s at 0.3Ghz toggle                            |

MRFI multiplexes data in-parallel through the frequency domain instead of in-serial through the time domain. This avoids high speed data/clock toggling and consequent high power consumption. This also avoids timing adjustment-related latency for matching data strobe signal (DQS)/output data (DQ) traces. As a result, MRFI is able to support a very wide data bus with very short latency and low power consumption.

## 4. METHODS, ASSUMPTIONS, AND PROCEDURES

## 4.1 Phase I (Five-Band QPSK Parallel Link)

In Phase I, we aimed to analyze, model and implement the designed MRFI to enable high scalability and reconfigurability for inter-CPU/Memory communications with an increased number of communication channels in frequency-domain and a reduced number of physical pads/wires to obtain higher effective bandwidth, superior energy efficiency (in terms of energy/bit) and decreased size/area of both silicon (on-chip) and PCB (off-chip) for future mobile and airborne computing systems. Our methods are listed below:

## **4.1.1 Differential Mode Signaling**

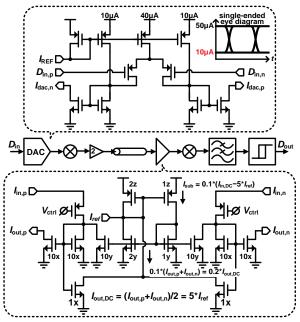

We exploited a novel innovative differential current mode modulation/demodulation method to achieve shorter latency, lower power, and resilience to process variations for multi frequency band QAM transceiver circuits to make the method possible to become the foundation for MRFI. The invention achieves shorter latency delay and lower power consumption with higher yield manufacturing. It also includes a DC current reduction circuit element to improve the signal-to-noise ratio. The proposed circuits were all implemented by using current mirrors with proven higher manufacturing yield. A current mode Schmitt Trigger with adjustable hysteresis value was included in the demodulation circuit to improve data recovery without creating bit error.

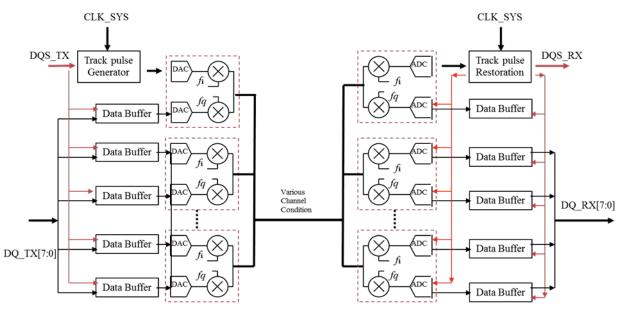

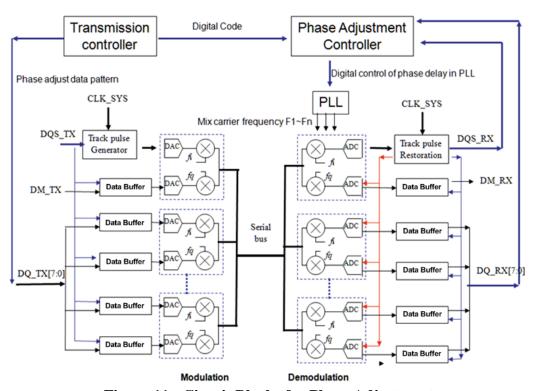

The modulation and demodulation circuit (Figure 3) consists of two parts: the modulation circuit performs transmission (TX) while the demodulation circuit performs reception (RX). The modulation circuit includes digital-to-analog converter and mixer. The demodulation circuit includes mixer and analog-to-digital converter. The circuit transmits one byte of digital signal after applying multi frequency modulation and combines all output of mixer and then transmits from TX. The circuit receives a byte of digital signal by applying the same multi frequency to demodulate the combined signal from TX and then generating the receiving digital signal in byte.

Figure 3: MRFI with Self-Track Pulse Generator and Restoration for I/O Data Synchronization

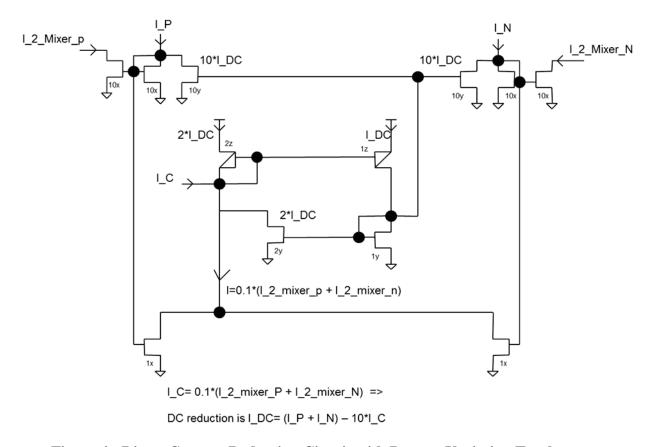

The circuit transmits the differential current signal after converting the digital voltage signal by the digital-to-analog converter. The differential current signal will be modulated by applying a defined frequency carrier which is in voltage control signal. The differential current signal being modulated by mixer will be combined before TX sends the combined signal through connection pins. The circuits receive the differential current signal from TX, which will be sent to mixer for demodulation. A circuit performs direct current reduction to improve the signal ratio and reduce the power consumption before sending the receiving differential current signal directly to all mixers. Figure 4 shows this direct current reduction circuit.

Figure 4: Direct Current Reduction Circuit with Process Variation Track

The reduced direct current will remove any extra direct current to ensure the sum of the differential current to mixer equals 10\*I\_C. This circuit also shows that the amount of direct current removed changes as I\_P and I\_N changes to ensure the sum of input to mixer remains constant. The constant differential current signal allows a consistent circuit behavior of mixer.

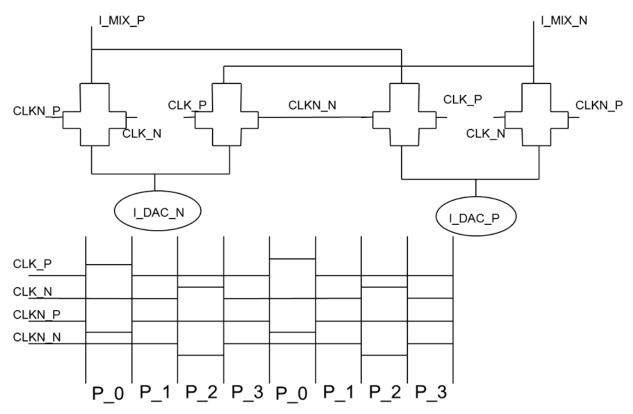

## 4.1.2 TX and RX Designs

To transmit the data, the modulation circuit uses a differential current mode digital-to-analog converter. Once the digital signals are converted into differential current signal, this differential signal is modulated by current mode mixer. Figure 5 shows the mixing carrier being a quarter duty cycle of digital steering signal, which can be used to avoid the interference between I-channel and Q-channel. A four phase mixing carrier can be implemented to keep fast current steering to avoid starvation of current in the differential pair. The four phase carrier operates as follows: during phase P\_0, CLK\_P and CLKN\_N are high to make (I\_MIX\_P = I\_DAC\_P, I\_MIX\_N = I\_DAC\_N). Phase 0 produces the differential current signal in the same phase of current mode DAC output. During phase 1, CLKN\_P and CLKN\_N are high to make [I\_MIX\_P = I\_MIX\_N = 0.5\*(I\_DAC\_P + I\_DAC\_N)]. Phase 1 produces the differential current signal to be zero. During Phase 2, CLK\_N and CLKN\_P are high to make (I\_MIX\_P = I\_MIX\_N = I\_DAC\_N). Phase 2 produces the differential current signal in 180 degrees of current mode DAC output. During phase 3, CLKN\_P and CLKN\_N are high to make [I\_MIX\_P = I\_MIX\_N = 0.5\*(I\_DAC\_P + I\_DAC\_N)]. Phase 3 produces the differential

signal to be zero. Current will not turned off at any given time, thus avoiding current spike and reducing unexpected noise during mixing. The direct current level allows the mixer to operate at high frequency without serious degradation.

Figure 5: Differential Current Steering Mixer with Quarter Duty Cycle Carrier

In the transmission circuit, the out pin of TX will drive the signal from the sum of output signals. Because the signal is in differential current mode, one can wire all output current mirrors directly after the mixer. This differential current signal is then passed to RX which implements a direct current reduction circuit to reduce the direct current level to the predefined level. The residual differential current signal will be sent to the demodulation mixer. After demodulation, a low pass filter can be used to filter out adjacent frequency band signal. An analog-to-digital converter can be used to restore the digital signal from the analog signal.

The signal (after low pass filter) carries adjacent channel interference, generating a ripple. To ensure the robust operation with the presence of the unwanted ripple, a hysteresis can be applied in the ADC to prevent the incorrect signal generation. Because this is differential current signal, the amount of hysteresis can be digitally programmed through the current mirror in the comparators of the ADC.

## 4.1.3 VCO Design and Calibration Algorithm

Tunable voltage control oscillator (VCO) is the key circuit block for frequency synthesizer and phase lock loop in the MRFI connection. A good tunable VCO with low jitter can improve the system performance greatly. The frequency gain by control voltage (KVCO) should be kept as

small as possible over the target tuning frequency range to obtain the low jitter performance in VCO. However, the KVCO needs to be increased to cover not only the target tuning frequency range but also the chip fabrication process variation. The typical variation is about 50% between slow-slow process corner and fast-fast process corner so if the VCO is designed with 20% frequency tuning range, the KVCO must cover 70% tuning range. As a result, unnecessary high KVCO causes large jitter of VCO.

We implemented a tunable VCO that can compensate for the process variation through self-calibration circuits which can reduce the large fabrication process variation and allows the implementation of a VCO with low KVCO to cover the target tuning range and avoid unnecessary large KVCO. This implementation of VCO can optimize the jitter for a given target tuning range and cover wide chip fabrication process. The self-calibration circuits inside the chip is realized by an implementation of feedback control circuits to create a constant resistor-capacitor (RC) delay for each stage of current mode inverter inside VCO even as the process changes. Even with variation due to the process change, the feedback control circuit will prevent the KVCO characteristic of VCO from changing. The reduction of RC delay variation will reduce the variation of oscillation frequency in VCO.

The uniqueness of this VCO is that the automatic feedback circuits emulate the external constant device which reduces the variation caused by the fabrication process variation. This invention not only optimizes the performance for a given process but also allows the design to be transferred to different foundries.

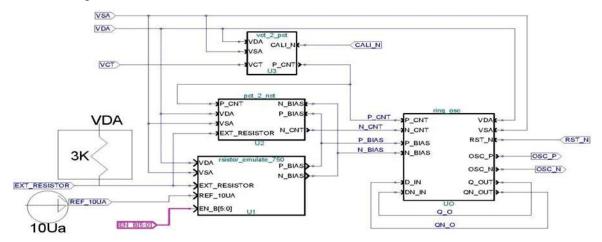

The VCO (Figure 6) consists of 4 parts: Part1 is a circuit of vct\_2\_pct gain buffer amplifying VCT from low pass filter to P\_CNT that changes the resistance of positive metal-oxide semiconductor (PMOS) and current in current mode logic (CML) inverter. By varying P\_CNT, CML inverter can operate with different delay time as P\_CNT changes. When P\_CNT fully turns on PMOS to increase the current in CML inverter to a maximum, CML inverter will operate at the shortest delay time. When P\_CNT fully turn off PMOS to reduce the current in CML inverter to a minimum, CML inverter will operate at the longest delay time. The control pin, CALI\_N, will provide the control mechanism to the self-calibration controller during the calibration operation.

Figure 6: Voltage Control Oscillator

Part2 is a circuit of pct\_2\_vct that keeps the constant voltage swing for CML inverter during P\_CNT changes. The voltage swing of CML is equal to product of current and resistance of the loaded device. When P\_CNT changes to reduce the resistance of load device in CML inverter in order to increase speed, Part2 circuit will generate more current to CML inverter such that voltage swing is maintained as a constant. This circuit ensures the same operating point of circuit so that all parasitic contribution to circuit operation is the same even when P\_CNT changes.

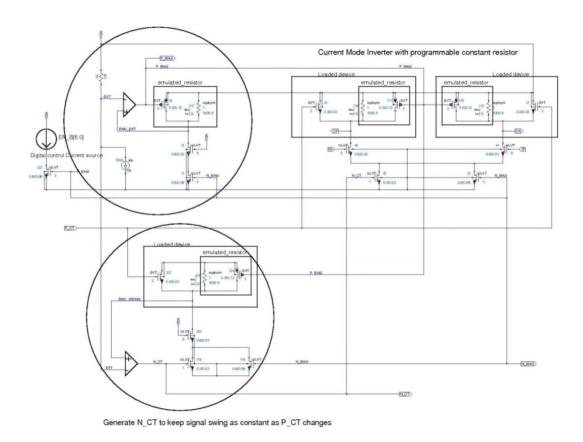

Part3 is a circuit of resistor emulation. Figure 7 shows that an external resistor outside the chip is tied to power supply. An external current source is applied to the circuit. With these two external components, the internal loaded device of CML inverter can be programmed to track with fabrication process variation. This circuit has 6 bits of programming control that can be used by the self-calibration controller to control the based current under the fixed voltage swing.

Figure 7: CML Inverter Chain

The circuits show the oscillator consisting of a chain of several stages of CML inverters. Each stage of CML inverter has a delay of Td. The amount of Td is dependent on C\*Swing/current, where C is total node capacitance, swing is the difference of highest voltage and lowest voltage in the oscillation wave form, and current is the current supplied to each CML inverter. Since the swing is fixed by the circuits in part2 and part3 and the node capacitance is fixed by the device size, the current supplied to CML inverter changes as N\_CNT changes to track P\_CNT and P\_CNT is amplified from VCT, voltage to control the VCO frequency. Changing VCT will change current and Td, and once Td changes, the VCO frequency changes. The VCO frequency is proven to be inversely proportional to twice the sum of Td in each stage of the chain.

Thus if the voltage swing is kept constant in spite of process changes, the current can be programmed by part3 circuit to compensate for the capacitance loading changes due to process variation. By such calibration, the design of KVCO for VCO can be greatly minimized for a given tuning range because the process variation can be compensated. As a result of low KVCO, the design can achieve the low jitter for VCO.

Figure 8 shows the detailed circuit in transistor level to implement part2 and part3 along with tracking CML inverter. The CML inverter shown consists of two loaded devices, two switch NMOS and two current source n-channel metal-oxide semiconductor (NMOS). The loaded devices consist of three parallel circuit elements: one poly resistor, one PMOS for compensating process variation, and one PMOS for tuning frequency. Two current source NMOS, a fixed current that is programmed to compensate the process variation and one that changes as P\_CNT

changes to keep the voltage swing constant, will tune the frequency of VCO over its tunable range.

Figure 8: CML Inverter with Programmable Resistor

P\_CNT is pulled to VDD when the low pass filter pulls VCT close to VDD. Then the resistance of the loaded device of CML inverter changes to maximum because the PMOS is turned off. In this case, N\_CNT will cut off the current shown in Figure 8. As a result, CML inverter always operates with the same voltage swing at the highest resistance and lowest current source. One can assure that CML operates at its lowest possible oscillating frequency under this condition. Figure 8 further shows that combining part2 and part3 circuit by the operation bias will remain the same during P\_CNT changes to tune the VCO frequency.

When P\_CNT turns off the PMOS, the emulated resistor circuit will generate P\_BIAS such that the effective resistance of loaded device, parallel ploy resistor and PMOS, will be always equal to the fixed voltage across loaded device divided by the programmable current in part3 circuit. The fixed voltage across the loaded device is achieved through differential amplifier feedback as shown in part3 circuit. Because this is referred to an external resistor with a fixed current source, the voltage across the loaded device will remain constant over operating conditions and process variations. If there is a change in poly resistance or PMOS characteristic, the part3 circuit can always generate P\_BIAS to produce an effective resistance of loaded device equal to that of fixed voltage across the device divided by current source. One can always produce a target effective resistance regardless of the process variation with this method. Combining the

calibration controller, part3 circuit can compensate for different operation conditions with process variation.

Part2 circuit is to change the supply current of CML inverter when P\_CNT changes. This is the main function of voltage control oscillator, changing frequency by changing control voltage. As stated earlier, CML inverter will operate at the constant C\*Swing/current by using part2 and part3 circuits. Part3 defines the minimum current to CML invert at a constant C\*Swing/current. Part2 will change the supply current according the PMOS biased by P\_CNT. The CML inverter (Figure 8) has two current supply: one NMOS biased by part3 circuit (minimum supply current), and the other NMOS biased by part2 circuit (variation of current to change the Td). When P\_CNT changes from high to low, resistance of PMOS biased by P\_CNT in the loaded device will decrease, and the total resistance of the loaded device will decrease. However, part2 circuit ensures that the voltage drop across the loaded device is the constant and will force the N\_BIAS in part2 to increase in order to keep the voltage swing constant. Increase of N\_BIAS will increase NMOS supply current in CML inverter. By keeping the swing of CML inverter constant, the part2 circuit will change the CML convert supply current through NMOS biased by N\_BIAS. Thus CML convert can change its delay time with P\_CNT changes.

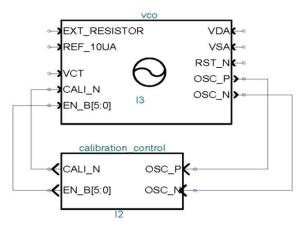

Based on the operation principle of circuits of tracking in part2 and part3, a self-calibration controller is shown in Figure 9.

Figure 9: Self-Calibration Controller

The calibration controller starts the calibration process by asserting CALI\_N to low. The controller will pull P\_CT in Figure 8 to high in order to turn off the PMOS through circuit part1. CML inverter will then operate at the longest delay, i.e. will oscillate at the lowest frequency. Then, by adjusting EN\_B[5:0], the calibration controller can adjust the lowest frequency close to the lowest target tuning frequency. The calibration controller process for calibration is shown in Figure 10.

Figure 10: Flow Chart of Calibration Controller

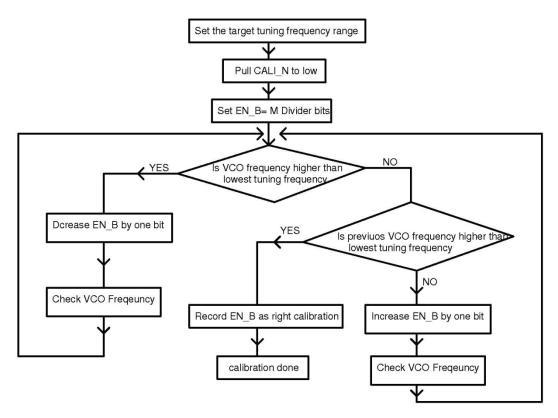

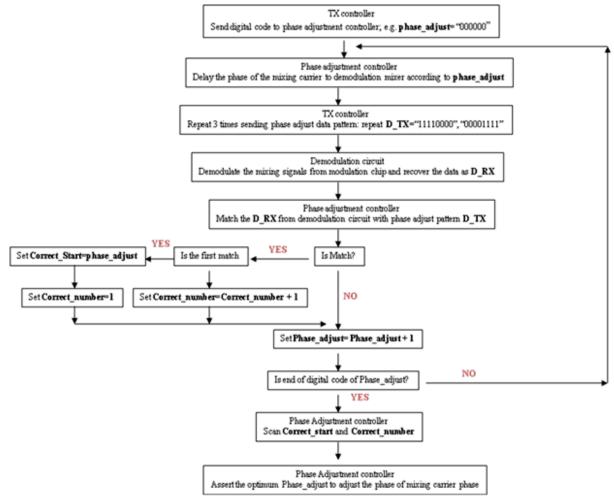

## **4.1.4** Phase Synchronization and Implementation

The phase synchronization between the modulation and demodulation carriers is traditionally carried out through digital signal processing, requiring a complicated algorithm implemented in Digital Signal Processing (DSP). It increases not only the latency of signal processing but also the power consumption.

We realized a new method to perform the phase synchronization between the modulation at TX and the demodulation at RX which can perform synchronization without complicated DSP and achieves a short latency with low power consumption. The phase synchronization is conducted by combining 1) predefined signal pattern sent by transmit controller; 2) a set of digital code to adjust the phase delay of PLL; 3) a phase adjustment controller to validate the correctness of demodulator output; and 4) phase adjustment controller adopting an algorithm to assert a digital code to achieve the maximum recovered signal strength base on its recorded correct digital code during the phase adjustment cycle.

This phase adjustment can be performed without bearing heavy overhead of digital signal processing. This can reduce the signal propagation latency by removing the digital-locked-loop (DLL) used to synchronize the carrier phase between the modulation and demodulation. The simplicity of circuit implementation can also substantially reduce the power consumption compared with that of a digital signal processor.

In Figure 11, both modulation and demodulation mixers require a mixing carrier with selected frequency to mix with the data signals. In radio frequency (RF) communication, the phases of modulation carrier and demodulation carrier need to be in phase so that the strength of recovered signal after demodulation can be maximized. The modulation mixer and demodulation mixer in Figure 11 belong to different chips to communicate with each other through wire connections. The modulated signal after mixer needs to travel through pad to the connection channel and reach pads of another connected chip. Then the pad circuit of the connected chip will further propagate the signal to the demodulated mixer for down-converting data signal to the base frequency band signal. A phase delay exists due to signal propagation through various elements. In order to maximize the strength of the recovered signal, one must adjust the phase between modulation and demodulation mixers to compensate for the phase delay from signal propagation. Instead of performing phase adjustment by digital signal processing, one implements a scheme with transmission controller and phase adjustment controller. The phase adjustment controller will adjust the phase of mixer based on an algorithm to maximize the strength of recovered signal.

Figure 11: Circuit Blocks for Phase Adjustment

Figure 11 shows the circuit blocks to perform the phase adjustment: a transmission controller and phase adjustment controller integrated to multi frequency band QAM circuits. The phase adjustment is completed by executing steps 1 through 5 below:

- 1) Transmission controller sends a predefined phase adjust data pattern to D TX.

- 2) Transmission controller sends a set of digital code to the phase adjustment controller to adjust the phase delay of phase lock loop (PLL). The phase adjustment controller will control the phase difference of mixing carrier for each different digital code.

- 3) Mixing carrier with phase delay is applied to the mixer of demodulation. The output data D\_RX from demodulator are fed back to the phase adjustment controller.

- 4) Phase adjustment controller check that the output data D\_RX matches the predefined phase adjust data pattern. Record all check comparison results of phase adjust data pattern.

- 5) Phase adjustment controller examines the comparison result and asserts the optimum phase delay to PLL to maximize the strength of recovered signal.

Figure 12: Flow Chart for Phase Adjustment

The phase adjustment controller implements a set of registers to record the adjustment result. One register records which digital code of phase adjustment starts to produce the correct recovered data pattern matching the phase adjust data pattern from transmission controller. Another register records how many consecutive digital codes will be needed to produce the correct recovered data pattern. When all possible digital code of phase adjust is exercised, phase adjustment controller will scan the registers. The linear algorithm can be applied to achieve the optimum phase adjustment. That is, the digital code of optimum phase adjustment is set to be the Correct\_start + Correct\_number/2. This digital code can produce the highest signal strength after demodulation if the system behaves linearly. This requires the delay element in PLL to behave linearly as digital code of phase adjust changes.

Because both transmission controller and phase adjustment controller is in parallel with the signal path of modulation/demodulation, there will be no additional penalty of signal propagation. This phase adjustment cycle can start whenever the central processing unit sees the need of phase adjustment. Both transmission controller and phase adjustment controller are idle without consuming power during the normal modulation/demodulation cycles.

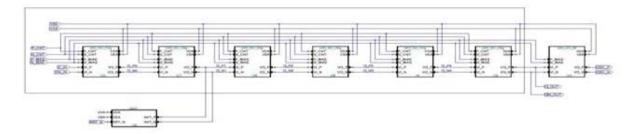

## 4.1.5 One-byte MRFI bus designed with five carriers and QPSK modulation

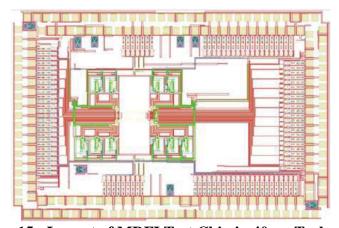

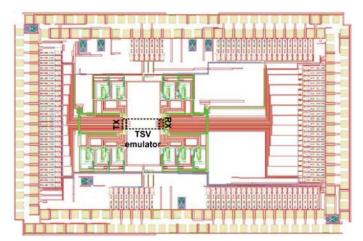

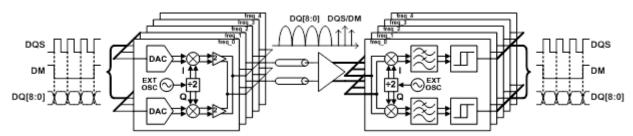

Figure 13 shows the block diagram of the 1-Byte MRFI, design on 40nm CMOS technology.

Figure 13: Block Diagram of One-Byte MRFI by Five Frequency Carriers and QPSK Modulation

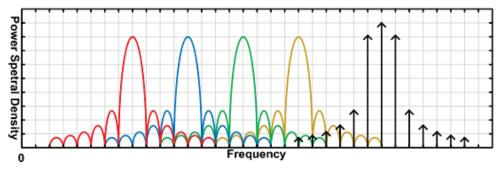

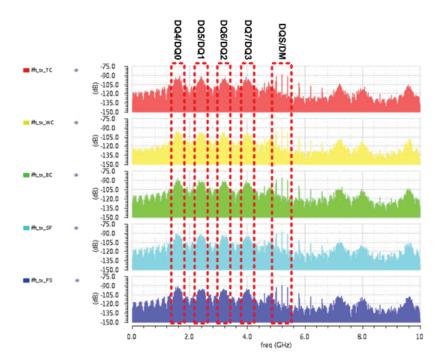

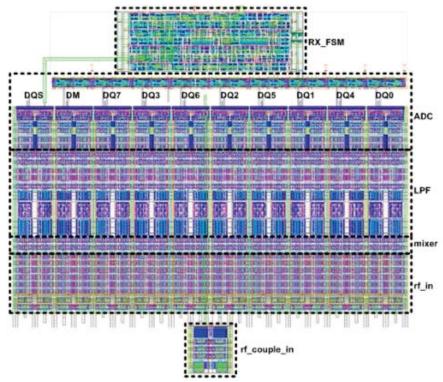

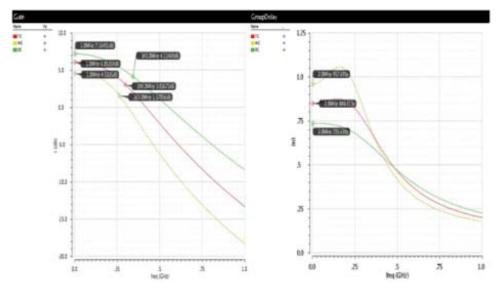

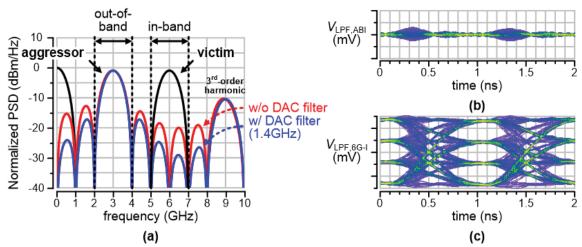

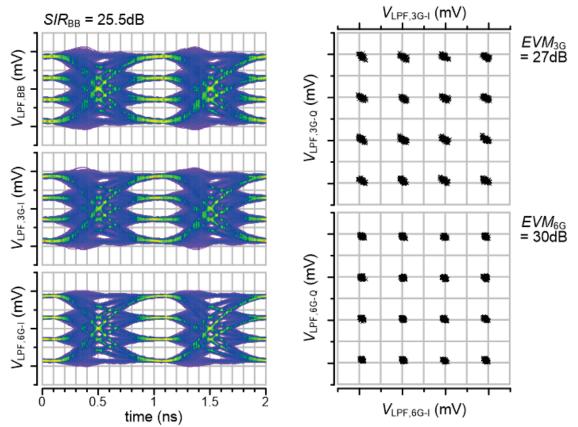

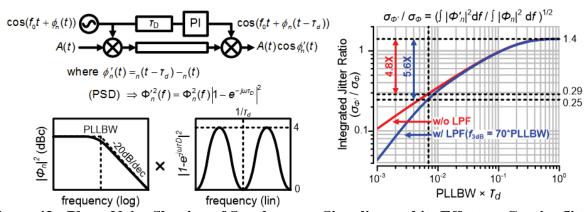

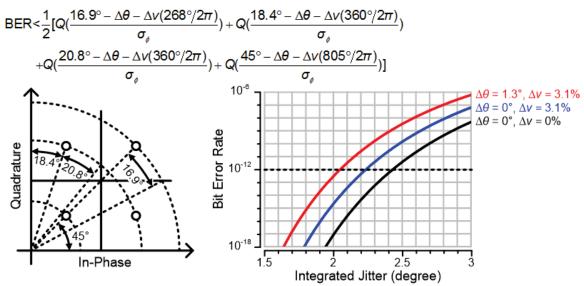

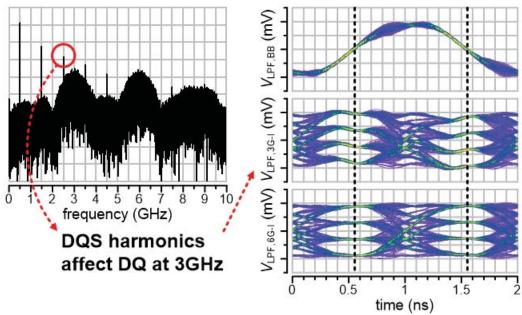

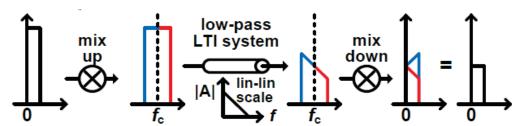

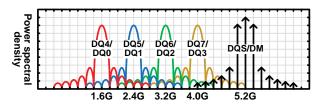

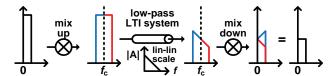

The MRFI transceiver adopts frequency-domain multiplexing (FDM) to simultaneously transmit eight bits of data signal (DQ0-DQ7), one tracking pulse signal (DQS), and one data mask signal (DM). These signals are up-converted by I/Q components of five carriers (1.6/2.4/3.2/4/5.2GHz) in TX, and then down-converted in RX. Low-latency (< 3 ns) signaling is achieved by sending tracking pulse and data mask signals together with data. The aggregate data rate of transceiver is 1.6 Gbps with I/O energy efficiency < 1 pJ/bit. With MRFI, the pin-count required for a given bandwidth is greatly reduced and multiple concurrent channels for processor/memory communication are available. The frequency allocation and inter-channel interference is shown in Figure 14.

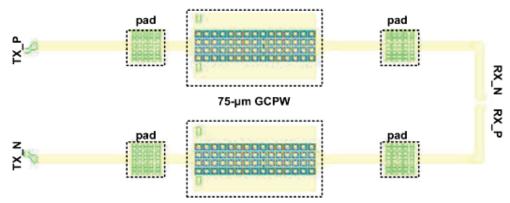

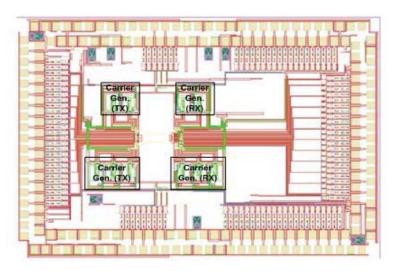

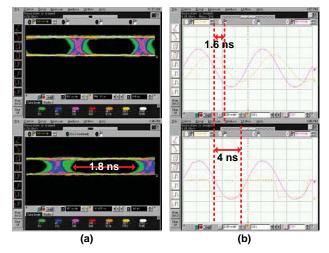

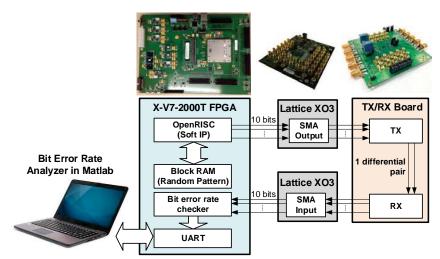

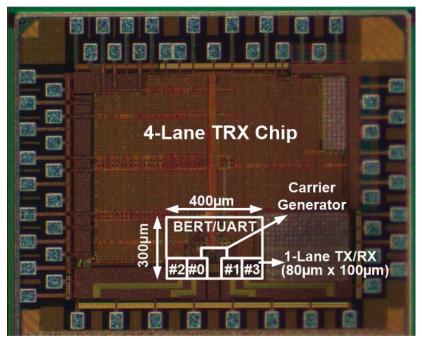

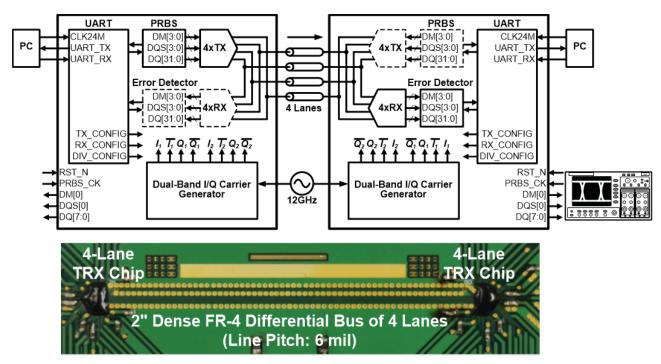

Figure 14: Multi-band QPSK RF-Interconnect Channel Spectrum