| UNCLASSIFIED                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD NUMBER                                                                                                                                                                                            |

| AD879465                                                                                                                                                                                             |

| LIMITATION CHANGES                                                                                                                                                                                   |

| TO: Approved for public release; distribution is unlimited.                                                                                                                                          |

| FROM: Distribution authorized to U.S. Gov't. agencies and their contractors; Administrative/Operational Use; 13 OCT 1970. Other requests shall be referred to Army Materiel Command, Alexandria, VA. |

| AUTHORITY                                                                                                                                                                                            |

| USAMC ltr, 14 Jan 1972                                                                                                                                                                               |

## THIS PAGE IS UNCLASSIFIED

rse les e

cytical 1

# ENGINEERING DESIGN HANDBOOK FIRE CONTROL SERIES SECTION 3 \*\*EDSTONE SCIENTIFIC INFORMATION CENTER 5 0510 000078463 4

FIRE CONTROL

72-19

COMPUTING SYSTEMS

10 FEB 到1

HEADQUARTERS, U.S. ARMY MATERIEL COMMAND

OCTOBER 1970

# tIEADQUARTERS UNITED STATES ARMY MATERIEL COMMAND WASHINGTON, D. C. 20315

AMC PAMPHLET No. 706-329 13 October 1970

#### ENGINEERING DESIGN HANDBOOK

SECTION 3, FIRE CONTROL COMPUTING SYSTEMS

| Paragraph                                                 |                                                                                                                                                                                                     | Page                                      |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                                                           | LIST OF ILLUSTRATIONS LIST OF TABLES LIST OF EXAMPLES. LIST OF INFORMATION SUMMARIES LIST OF DERIVATIONS ACKNOWLEDGMENTS FOREWORD PREFACE INTRODUCTION PART I. MATHEMATICAL MODELS FOR FIRE CONTROL | xviii<br>xix<br>xx<br>xxi<br>xxii<br>xxii |

|                                                           | COMPUTING SYSTEMS                                                                                                                                                                                   |                                           |

| CHAPT                                                     | TER 1. THE ROLE OF THE MATHEMATICAL MODEL IN THE DESIGN PROCESS                                                                                                                                     |                                           |

| 1 - 1<br>1 - 2<br>1 - 3                                   | DEFINITION AND ILLI'ORTANCE OF A MATHEMATICAL MODEL MATHEMATICAL MODELS FOR PHYSICAL SYSTEMS                                                                                                        | 1-1<br>1-7<br>1-11                        |

| CH                                                        | APTER 2. DETERMINATION OF THE ACCURACY AND DYNAMIC RESPONSE OF A SYSTEM FROM STUDIES OF ITS MATHEMATICAL MODEL                                                                                      |                                           |

| 2-2<br>2-2.1<br>2-2.2<br>2-2 3                            | INTRODUCTION.  MATHEMATICAL TECHNIQUES  GENERAL  LINEAR-DIFFERENTIAL-EQUATION THEORY.  FREQUENCY-DOMAIN ANALYSIS.                                                                                   | 2-1<br>2-1<br>2-2<br>2-2                  |

| 2-2.3.1<br>2-2.3.2<br>2-2.3.3<br>2-2.4<br>2-2.5           | Laplace and Fourier Transforms                                                                                                                                                                      | 2-3<br>2-5<br>2-10                        |

| 2-2.5.1<br>2-2.5.2<br>2-2.6<br>2-2.7                      | Block Diagrams.  Signal- Flow Graphs.  STATISTICAL, THEORY  NONLINEAR ANALYSIS.                                                                                                                     | 2-11<br>2-15<br>2-20<br>2-24              |

| 2-2.7.1<br>2-2.7.2<br>2-2.7.2.1<br>2-2.7.2.2<br>2-2.7.2.3 | General  Nonlinearities Found In Many Control Systems  Limiting  Dry Friction  Hysteresis                                                                                                           | 2 - 27<br>2-27<br>2-27                    |

| 2-2.7.2.4<br>2-2.7.2.5<br>2-2.7.2.6<br>2-2.7.2.7          | Relays Diodes Orifices Products and Transcendental Functions.                                                                                                                                       | 2-28<br>2-28<br>2-28                      |

| 2-2.7.3<br>2-2.7.3.I<br>2-2.7.3.2<br>2-2.7.3.3            | Classification of Nonlinear Systems                                                                                                                                                                 | 2-29<br>2-29<br>2-29                      |

| Paragraph                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

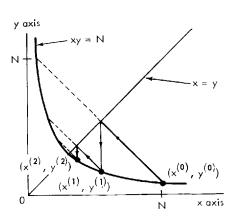

| 2-2.7.3.4<br>2-3<br>2-3.1<br>2-3.2<br>2-3-3<br>2-4<br>2-4.1<br>2-4.2<br>2-4.2.1<br>2-4.2.2<br>2-4.2.3<br>2-4.2.4<br>2-4.3<br>2-4.6 | Phenomena Peculiar to Nonlinear Systems  SIMULATION TECHNIQUES. GENERAL. ANALOG TECHNIQUES. DIGITAL TECHNIQUES. NUMEKICAT. TECHNIQUES GENERAL. REPRESENTATION OF MATHEMATICAL FUNCTIONS Iteration Series Approximation Interpolation. Curve Fitting. NUMERICAL DIFFERENTIATION NUMERICAL INTEGRATION METHODS FOR SOLVINC. DIFFERENTIAL EQUATIONS METHODS FOR SOLVING SYSTEMS OF LINEAR ALGEBRAIC EQUATIONS REFERENCES GENERAL BIBLIOGRAPHY OF BOOKS AND PAPERS RELATING TO NONLINEAR SYSTEMS. Describing Functions Nonlinear Differential Equations | 2-30<br>2-30<br>2-31<br>2-32<br>2-32<br>2-33<br>2-34<br>2-34<br>2-45<br>2-46 |

| _                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 00                                                                         |

| P                                                                                                                                  | ART II. COMPUTING DEVICES USEFUL IN FIRE CONTROL SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |

|                                                                                                                                    | CHAPTER 3. THE CLASSIFICATIONS OF COMPUTING DEVICES  USED IN FIRE CONTROL SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                              |

| 3-1<br>3-1.1<br>3-1.2<br>3-1.3<br>3-1.4<br>3-1.5<br>3-2<br>3-2.1<br>3-2.2<br>3-3<br>3-4<br>3-5                                     | INTROHUCTION  CHARACTERISTICS OF FIRE CONTROL COMPUTERS. CLASSIFICATION SCHEMES BASIC COMPUTER CONCEPTS USER CLASSIFICATIONS. DESIGNER CLASSIFICATIONS. MANUAL COMPUTING DEVICES FIRING TABLES NOMOGRAMS. MANUALLY OPERATED AUTOMATIC COMPUTERS AUTOMATIC COMPUTING DEVICES DIGITAL, DIGITAL DIFFERENTIAL ANALYZER, AND ANALOG COMPUTING DEVICES TYPES OF PHYSICAL EQUIPMENT EMPLOYED IN COMPUTERS SPECIAL-PURPOSE AND MULTIPURPOSE COMPUTING DEVICES. REFERENCES                                                                                   | 3-1<br>3-2<br>3-2<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4                         |

|                                                                                                                                    | CHAPTER 4. DIGITAL COMPUTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

| 4-1<br>4-1.1<br>4-1.2<br>4-1.3                                                                                                     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1<br>4-1<br>4-2<br>4-2                                                     |

| 11                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              |

| Paragraph   |                                                  | Page   |

|-------------|--------------------------------------------------|--------|

| 4-2         | SYSTEM DESIGN                                    | 4-8    |

| 4-2.1       | EQUATIONS TO BE SOLVED                           | 4 – 8  |

| 4-2.2       | USE OF NUMERICAL ANALYSIS AND OTHER              |        |

|             | MATHEMATICAL TECHNIQUES                          | 4 – 8  |

| 4-2.3       | ACCURACY AND RESPONSE TIME                       | 4-11   |

| 4-2.4       | USE OF SAMPLED-DATA THEORY                       | 4-12   |

| 4-3         | THE GENERAL CONFIGURATION OF A FIRE CONTROL      |        |

|             | DIGITAL COMPUTER                                 | 4 – 13 |

| 4-3.1       | INPUT AND OUTPUT CONSIDERATIONS                  | 4-14   |

| 4-3.2       | COMPUTER SPEEDS                                  | 4-19   |

| 4-4         | DETERMINATION OF COMPUTER STORAGE CONFIGURATION  | 4-20   |

| 4-4.1       | SIZE OF COMPUTER PROGRAM                         | 4-20   |

| 4-4.2       | CODING SYSTEM AND WORD LENGTH                    | 4-25   |

| 4-4.3       | SUBROUTINES, REQUIREMENTS FOR TEMPORARY STORAGE  | 4-29   |

| 4-4.4       | DATA STORAGE REQUIREMENTS                        | 4-25   |

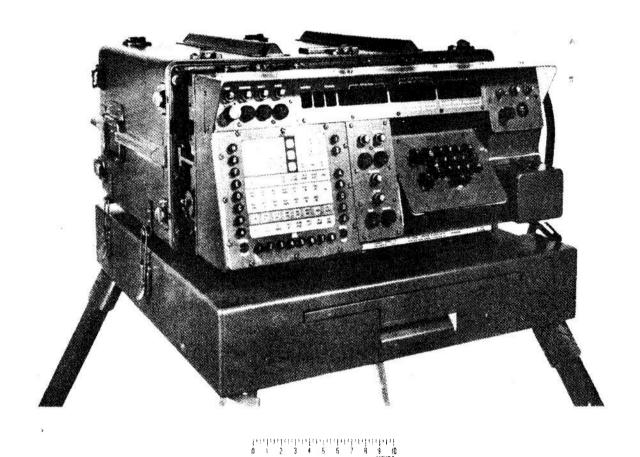

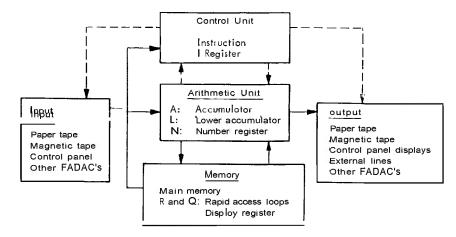

| 4-4.5       | EXAMPLE OF FADAC MEMORY                          | 4-29   |

| 4-5         | FILEXIBILITY REQUIREMENTS                        | 4-30   |

| 4-5.1       | SPECIAL-PURPOSE VERSES GENERAL-PURPOSH COMPUTERS | 4-30   |

| 4-5.2       | CHOICH OF BUILT-IN COMPUTER OPERATIONS           | 4-30   |

| 4-5.3       | CHOICE OF PROGRAMMING SYSTEMS                    | 4-31   |

| 4-6         | COMPUTER TYPES                                   | 4-32   |

| 4-6.1       | SYNCHRONOUS AND ASYNCHRONOUS                     | 4-32   |

| 4-6.2       | WHOLE-TRANSFER AND INCREMENTAL COMPUTERS         | 4-37   |

| 4-6.3       | OPERATIONAL.COMPUTERS                            | 4-37   |

| 4-6.3       | COMPUTERS AS SERVO ELEMENTS                      | 4-37   |

| 4-7         | TIPICAL DIGITAL COMPUTER                         | 4-38   |

| 4-8         | I OGICAL DESIGN                                  | 4-41   |

| <b>3-</b> 9 | COMPUTER NUMBER SYSTEMS                          | 4-46   |

| 4-9.1       | BINARY SYSTEM                                    | 4-46   |

| 4-9.2       | BINARY CODES                                     | 4-46   |

| 4-9.2.1     | Reflected Binary (Gray) Code                     | 4-46   |

| 4-9.2.2     | Decimal Codes                                    | 4-46   |

| 4-9.2.3     | Error-detecting and Correcting Codes             | 4-48   |

| 4-10        | CLASSES OF COMPUTER LOGIC                        | 4-49   |

| .3 - 11     | PREDOMINANT LOCICAL COMBISATIONS                 | 4-51   |

| 4-11.1      | GATES                                            | 4-51   |

| 4-11.2      | FLIP-FLOPS                                       | 4-53   |

| 4-11.3      | ADHERS AND SUBTRACTORS                           | 4-53   |

| 4-11.3.1    | Half-adder                                       | 4-53   |

| 4-11.3.2    | FuIl-adder                                       | 4-53   |

| 4-11.3.3    | Accumu lator                                     | 4-53   |

| 4-11.3.4    | Serial and Parallel Adders                       | 4-57   |

| 4-11.3.5    | Simultaneous Carry Techniques                    | 4-57   |

| 4-11.3.6    | Subtractors                                      | 4-57   |

| 4-11.4      | MULTIPLIERS AND DIVIDERS                         | 4-57   |

| 4-11.5      | MATRIX MEMORIES                                  | 4-59   |

| 4-11.6      | COUNTERS                                         | 4-59   |

| 4-11.7      | ARITHMETIC UNITS                                 | 4-59   |

| 4-12        | CIRCUIT COMPONENTS                               | 4-59   |

| 4-12.1      | VACUUM TUBES                                     | 4-59   |

| Paragraph      |                                                    |

|----------------|----------------------------------------------------|

| 4-12.2         | SEMICONDUCTORS                                     |

| 4-12.3         | MAGNETIC DEVICES                                   |

| 4-12.4         | NEW DEVELOPMENTS                                   |

| 4-13           | STORAGE                                            |

| 4-13.1         | SEQUENTIAL-ACCESS STORAGE                          |

| 4-13.1.1       | Magnetic Sequential Storage                        |

| 4-13.1.1.1     | Magnetic Drums                                     |

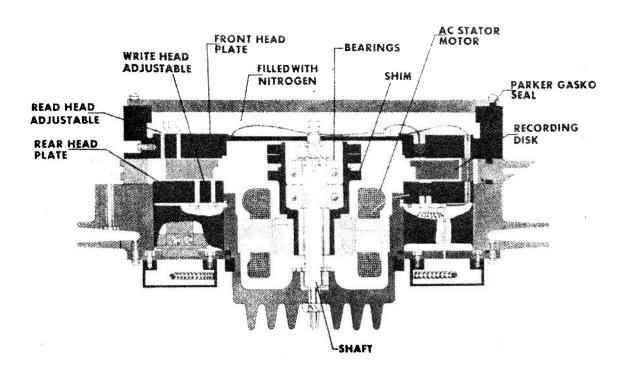

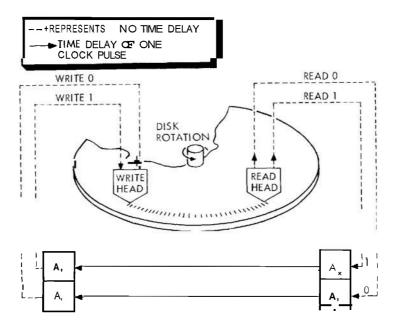

| 4-13.1.1.2     | Magnetic Discs                                     |

| 4-13.1.1.3     | Magnetic Tape                                      |

| 4-13.1.2       | Delay-line Storage                                 |

| 4-13.1.3       | Punched Paper Tape and Cards                       |

| 4-13.1.4       | Photoelectric Storage.                             |

| 4-13.2         | RANDOM-ACCESS STÖRAGE                              |

| 4-13.2.1       | Magnetic Core and Other Coincident-current Devices |

| 4-13.2.2       | Diode-capacitor Storage                            |

| 4-13.2.3       | Cathode-ray-tube Electrostatic-mosaic Storage      |

| 4-13.2.4       | Photoelectric Storage                              |

| 4-13.2.5       | Ferroelectric Storage                              |

| 4-14           | CONSTRUCTION PRACTICES                             |

| 4-14.1         | COMPONENT SELECTION                                |

| 4-14.2         | PACKAGING TECHNIQUES (MINIATURIZATION)             |

| 4-14.3         | MICROMINIATURIZATION                               |

|                | REFERENCES                                         |

|                | CHAPTER 5. DIGITAL DIFFERENTIAL ANALYZERS          |

| 5-1            | INTRODUCTION                                       |

| 5-2            | LOGICAL CIRCUITRY                                  |

| 5-3            | SOLUTION OF DIFFERENTIAL EQUATIONS                 |

| 5-4            | SCALING                                            |

| 5-5            | ERRORS IN THE DDA                                  |

| 5-6            | DDA COMPONENTS, CIRCUITS, AND HARDWARE             |

|                | REFERENCES                                         |

|                |                                                    |

|                | CHAPTER 6. ANALOG COMPUTERS                        |

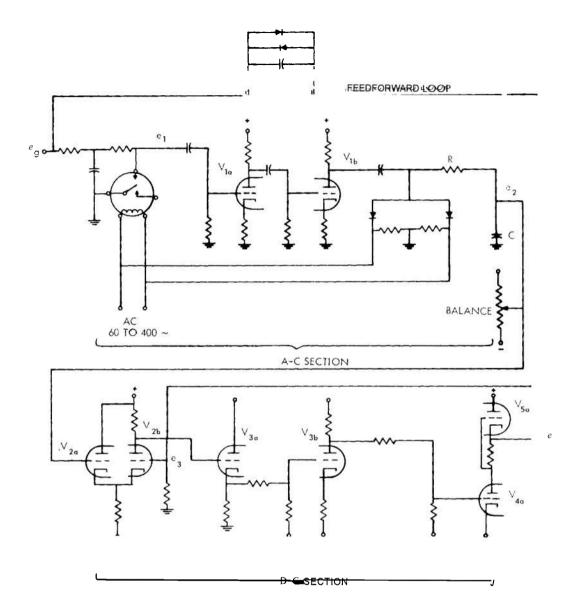

| 6-1            | N'TRODUCTION                                       |

| 6-1.1          | SOLUTION OF EQUATIONS BY ANALOG MEANS              |

| 6-1.2          | Common Mechanical and Electrical Analogs           |

| 6-1.3          |                                                    |

| 6-1.4          | Analog Computer Diagrams                           |

| 6-1.5          | TYPES OF ANALOG COMPUTERS                          |

| 6-1.6<br>6-1.7 | Electromechanical and Electronic Analog Computers  |

| 6-1.8          | A-C Type                                           |

| 6-1.8<br>6-1.9 | D-C Type                                           |

| 6-1.10         | Electrical Analog Computers                        |

| 6-1.11         | •                                                  |

|                | Mechanical Analog Computers                        |

| 6-2            | Mechanical Analog Computers                        |

| Paragraph |                                                  | Page         |

|-----------|--------------------------------------------------|--------------|

| 6-2.2     | Ordinary Differential Equations                  | 6-16         |

| 6-2.3     | Simultaneous Linear Equations                    | 6-18         |

| 6-2.4     | Nonlinear Algebraic Equations                    | 6-19         |

| 6-2.5     | Partial Differential Equations                   | 6-20         |

| 6-2.6     | SCALE FACTORS AND TIME SCALES                    | 6-21         |

| 6-2.7     | LINEAR OPERATIONS                                | 6-24         |

| 6-2.8     | Scale Changing                                   | 6-24         |

| 6-2.9     | Summation                                        | 6-25         |

| 6-2.10    | Integration                                      | 6-25         |

| 6-2.11    | Synthesis of Rational Transfer Functions         | 6-27         |

| 6-2.12    | NONLINEAR OPERATIONS                             | 6-32         |

| 6-2.13    | Multiplication and Division                      | 6- 32        |

| 6-2.14    | Vector Resolution                                | 6-33         |

| 6-2.15    | Direction Cosines                                | 6-34         |

| 6-2.16    | Euler Angles                                     | 6- 35        |

| 6-2.17    | Generation of Arbitrary Nonlinear Functions      | 6-40         |

| 6-3       | ELECTRONIC DIFFERENTIAL ANALYZERS                | 6-43         |

| 6-3.1     | OPERATIONAL AMPLIFIERS                           | 6-43         |

| 6-3.2     | MULTIPLIERS                                      | 6 – 45       |

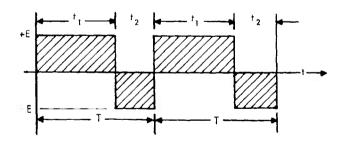

| 6-3.3     | Time-division Multiplier                         | 6-47         |

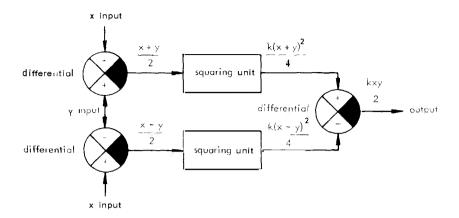

| 5-3.4     | Quarter-square Multiplier                        | 6-48         |

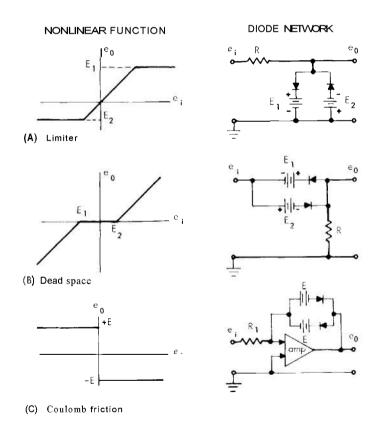

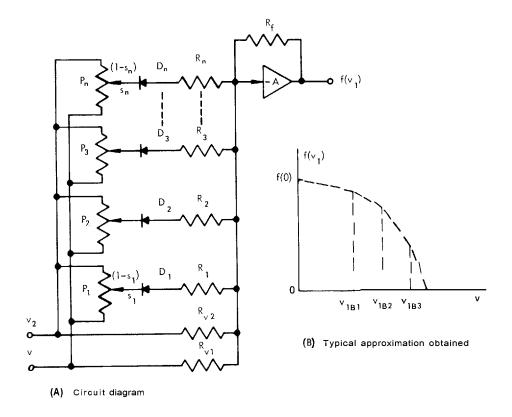

| 6-3.5     | FUNCTION GENERATORS                              | 6-48         |

| 6-3.6     | DECISION UNITS                                   | <b>6-4</b> 9 |

| 6-3.7     | INPUT-OUTPUT EQUIPMENT                           | 6-52         |

| 6- 3.8    | Input Equipment                                  | 6-52         |

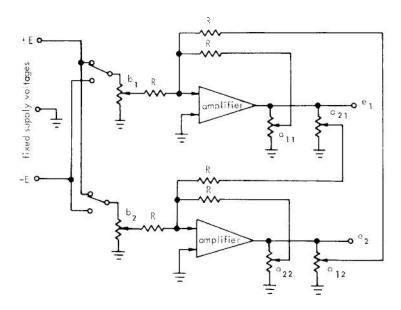

| 6-3.9     | Reference Voltage Supplies                       | 6-52         |

| 6-3.10    | Noise Generators                                 | 6-52         |

| 6-3.11    | Output Equipment                                 | 6-55         |

| S-4       | MECHANICAL, AND DILECTROMECHANICAL DIFFERENTIAL  |              |

|           | ANALYZERS                                        | 6-55         |

| 6-4.1     | SUMMATION DEVICES                                | 6-55         |

| 6-4.2     | INTEGRATORS                                      | 6-55         |

| 6-4.3     | MULTIPLIERS ANI) DIVIDERS                        | 6-57         |

| 6-4.4     | milechanical Multipliers                         | 6-57         |

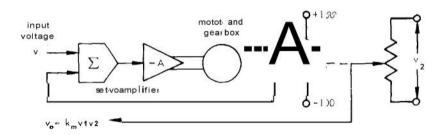

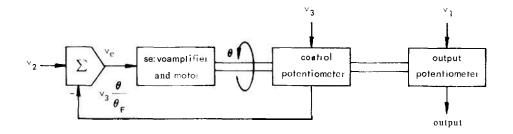

| 6-4.5     | Servomultipliers                                 | <b>6-</b> 58 |

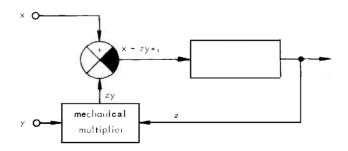

| 6-4.6     | Mechanical Dividers                              | <b>6</b> −59 |

| 6-4.7     | Electromechanical Dividers                       | 6-60         |

| 6-4.8     | COOK DINATE-SYSTEM CONVERTERS                    | 6-60         |

| 6-4.9     | Mechanical Converters                            | 6-61         |

| 6-4.10    | Electromechanical ('onverters                    | 6-61         |

| 6-4.11    | Three-dimensional Vector Resolution by Computers | 6-62         |

| 6-4.12    | FUNCTION GENERATORS                              | 6-67         |

| 6-4.13    | Mechanical Trigonometric Generators              | 6- 67        |

| 6-4.14    | Electrical Trigonometric Generators              | 6-67         |

| 6-4.15    | Arbitrary Function Generators                    | <b>6-6</b> 9 |

| 6-4.16    | Cams and Noncircular Gears                       | 6-70         |

| 6-4.17    | Linkage Mechanisms                               | 6- 70        |

| 6-4.18    | Special Potentiometers                           | 6-71         |

| 6-4.19    | Electromechanical Curve Readers                  | 6-71         |

| 6-5       | COMPLETE COMPUTERS                               | 6-71         |

| Paragraph |                                                                        | Page         |

|-----------|------------------------------------------------------------------------|--------------|

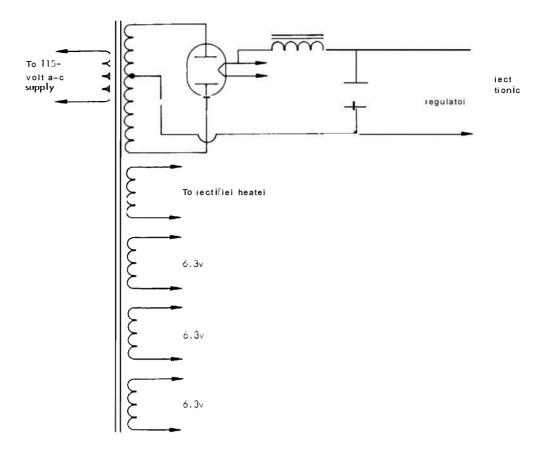

| 6-5.1     | POWER SUPPLIES                                                         | 6-72         |

| 6-5.2     | Filament Power Supplies                                                | 6-72         |

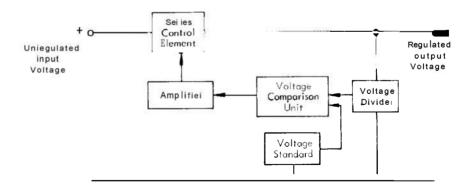

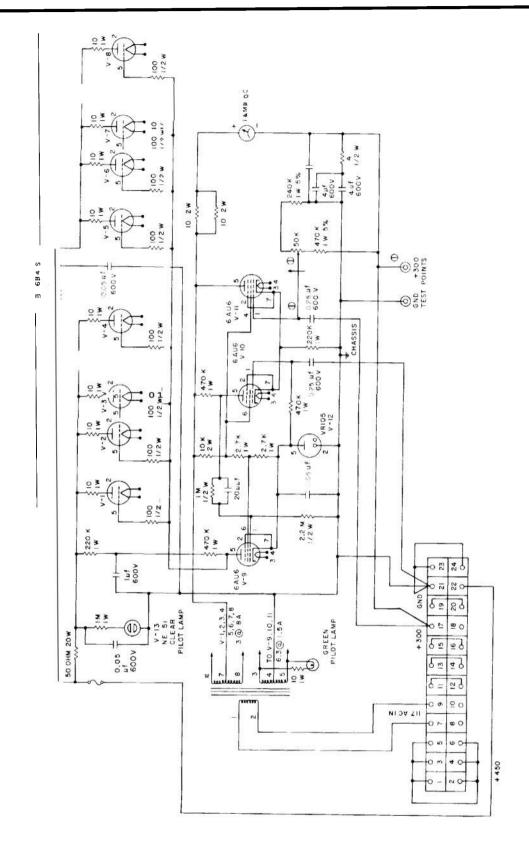

| 6-5.3     | High-voltage D-C Supplies                                              | 6-73         |

| 6-5.4     | Relay Supplies                                                         | 6-78         |

| 6-5.5     | A-C Supplies                                                           | 6-78         |

| 6-5.6     | Grounding Systems                                                      | 6-80         |

| 6-5.7     | PATCHING AND PROGRAMMING EQUIPMENT                                     | 6-80         |

| 6-5.8     | Patching Equipment                                                     | 6-81         |

| 6-5.9     | Programming Equipment                                                  | 6-82         |

| 6-5.10    | OUTPUT AND OVERLOAD EQUIPMENT                                          | 6-85         |

| 6-5.11    | Strip Recorders                                                        | 6-85         |

| 6-5.12    | Plotting Tables                                                        | 6-87         |

| 6-5.13    | Oscilloscopes                                                          | 6-88         |

| 6-5.14    | Servo and Digital Voltmeters                                           | 6-89         |

| 6-5.15    | Overload Indication Circuits                                           | 6-90         |

| 6-5.16    | CONSTRUCTION TECHNIQUES AND MAINTENANCE                                | 0 30         |

| ,         | CONSIDERATIONS                                                         | 6-90         |

| 6-5.17    | Maintenance and Checking                                               | 6-91         |

| 6-5.18    | Maintenance                                                            | 6-91         |

| 6-5.19    | Checking                                                               | 6-92         |

| 6-5.20    | ENVIRONMENTAL EFFECTS                                                  | 6-92         |

| 6-5.2 1   | Size, Weight, and Power Considerations                                 | 6-92         |

| 6-5.22    | Temperature. Humidity, Altitude. Shock. and Vibration                  | 6-93         |

| 0 0.22    | APPENDIX: THE BASIC OPERATIONS OF MATRIX ALGEBRA                       | 6-94         |

|           | REFERENCES                                                             | 6-98         |

|           | GENERAL BIBLIOGRAPHY FOR ANALOG COMPUTERS                              | <b>6-</b> 99 |

|           | CHAPTER 7. ANALOG-DIGITAL CONVERSION TECHNIQUES                        |              |

| 7- 1      | PURPOSE OF CONVERSIONS                                                 | 7-1          |

| 7-2       | CONVERSION OF AN ANALOG VOLTAGE TO A DIGITAL OIJTPUT                   | 7-1          |

| 7-2.1     | COMPARISON CIRCUITS                                                    | 7 – 1        |

| 7-2.1.1   | Level-at-a-time Voltage-to-digital Encoders                            | 7 – 1        |

| 7-2.1.2   | Digit-at-a-time Voltage-to-digital Encoders                            | 7-5          |

| 7-2.2     | THE LOGIC USED TO OPTIMIZE THE SPEED OF CONVERSION                     | 7–7          |

| 7-2.3     | THE USE OF SERVOS WITH SHAFT ENCODERS                                  | 7-8          |

| 7-2.4     | STEPPING SWITCHES, RELAYS, AND TRANSISTOR SWITCFIES FOR A D CONVERSION | 7-8          |

| 7-3       | CONVERSION OF MECHANICAL MOTION TO A DIGITAL OUTPUT                    | 7-8          |

| 7-3.1     | COMMUTATOR-TYPE ENCODING DISCS ANI) DRUMS                              | 7-8          |

| 7-3.2     | MAGNETIC ENCODERS                                                      | 7-9          |

| 7-3.3     | PHOTOELECTRIC ENCODERS                                                 | 7-11         |

| 7-3.4     | CODES ANI) BRUSH (READING HEAD) ARRANGEMENTS EMPLOYED                  | 7-11         |

| 7-4       | CONVERSION OF A DIGITAL SIGNAL TO AN ANALOG VOLTAGE                    | 7-11         |

| 7-5       | CONVERSION OF A DIGITAL SIGNAL TO MECTTANICAL MOTION REFERENCES        | 7-16<br>7-17 |

| Paragraph    |                                                                                             | Page                             |

|--------------|---------------------------------------------------------------------------------------------|----------------------------------|

|              | CHAPTER 8. ANALOG-DIGITAL COMPARISONS                                                       |                                  |

| 8-1          | BASIS OF COMPARISON :                                                                       | 8-1                              |

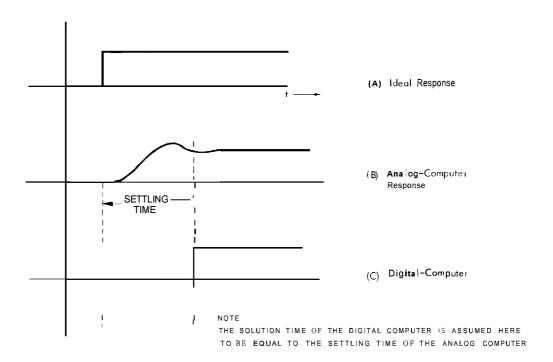

| 8-2          | COMPARISONS BASED ON THE SPEED WITH WIIICTT SOLUTIONS ARE OBTAINED                          | 8-1                              |

| 8-3          | COMPARISONS BASED ON THE ACCURACY OF THE SOLUTIONS OBTAINED                                 | 8-3                              |

| 8-4          | COMPARISONS BASED ON THE COMPLEXITY OF THE                                                  | 0.4                              |

| <b>8-</b> 5  | COMPUTING DEVICES INVOLVE11                                                                 | 8-4<br>8-4                       |

| 8-6          | COMPARISONS BASED OK TITE NATURE OF ENVIRONMENTAL                                           | 0 6                              |

| 8-7          | EFFECTS                                                                                     | 8-6                              |

|              | POWER CONSIDERATIONS                                                                        | 8-6                              |

|              | REFERENCES                                                                                  | 8-7                              |

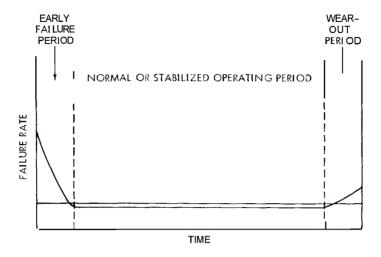

|              | CHAPTER 9. RELIABILITY AND CHECK-OUT PROCEDURES                                             |                                  |

| 9-1          | INTRODUCTION                                                                                |                                  |

| 9-2          | EFFECT OF ENVIRONMENT ON RELIABILITY                                                        | 9-2                              |

| 9-3          | LOGICAL DESIGN OF COMPUTERS TO OBTAIN THE DESIRED DEGREE OF RELIABILITY                     | 9-3                              |

| 9-4          | COMPUTER CHECK-OUT PROCEDURES AND EQUIPMENT                                                 | 9-8                              |

| 9-4.1        | MAINTENANCE                                                                                 | 9-8                              |

| 9-4.2        | MARĞINAL CHECKING                                                                           | 9-8                              |

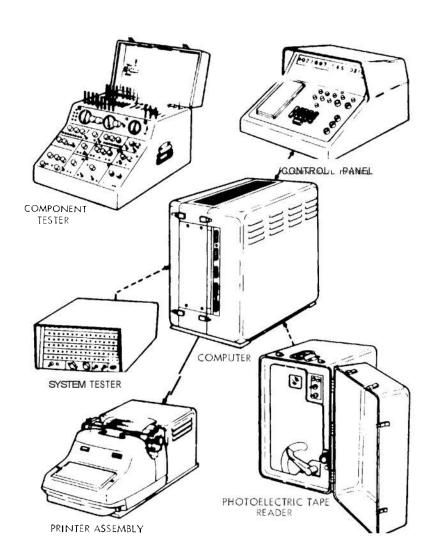

| 9- 5         | SPECIAL-PURPOSE CHECK-OUT EQUIPMENT                                                         | 9-9                              |

| 9-5.1        | GENERAL DESCRIPTION                                                                         | 9-9                              |

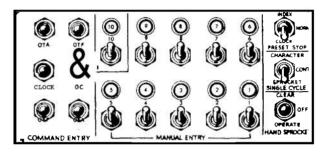

| 9-5.2        | DETAILED DATA                                                                               | 9-10                             |

| 9-5.3        | BASIC ELEMENTS                                                                              | 9-13                             |

| 9-5.4        | GENERAL METHOD OF OPERATION                                                                 | 9- 15                            |

| 9-6          | MEANS AND FACTORS TO BE CONSIDERED IN VERIFYING                                             | 0 15                             |

| 9- 7         | THE DESIGN OF REAL-TIME FIRE CONTROL COMPUTERS CONCLUSION                                   | 9-15<br>9-16                     |

| ;;-/         | REFERENCES                                                                                  | 9-16                             |

|              |                                                                                             | 11                               |

| P/           | ART III. THE REALIZATION OF A PROTOTYPE FIRE CONTROL SYSTEM BASED UPON A MATHEMATICAL MODEL |                                  |

|              | CHAPTER 10. PROBLEMS ASSOCIATED WITH THE MECHANIZATION OF MATHEMATICAL MODELS               |                                  |

| 10-1<br>10-2 | KINDS OF PROBLEMS ASSOCIATED WITH MECHANIZATION 1 COVERAGE OF REMAINDER OF PART III         | . 0 <b>-</b> 1<br>. 0 <b>-</b> 2 |

|              | CHAPTER 11. CHARACTERISTICS PECULIAR TO COMPUTERS USED FOR FIRE CONTROL APPLICATIONS        | -                                |

| 11-1         | OVERALL DESIGN. · · · · · · · · · · · · · · · · · · ·                                       | 11-1                             |

| 11-1.1       | MECHANICAL ANALOG COMPUTERS                                                                 | 11-1                             |

| 11-1.2       | ELECTROMECHANICAL ANAL.OG COMPUTERS                                                         | 11-2                             |

| 11-1.3       | OTHER COMPUTER TYPES · · · · · · · · · · · · · · · · · · ·                                  | 11-3                             |

# ${\bf TABLE\ OF\ CONTENTS}({\bf cont})$

| Paragraph     |                                                       | Page    |

|---------------|-------------------------------------------------------|---------|

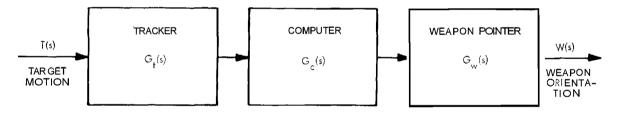

| 11-2          | INPUT-OUTPUT CONSIDERATIONS                           | . 11-3  |

| 11-2.1        | SOURCESOF DATA                                        | 11-3    |

| 11-2.2        | TRANSMISSION OF DATA                                  | 11-4    |

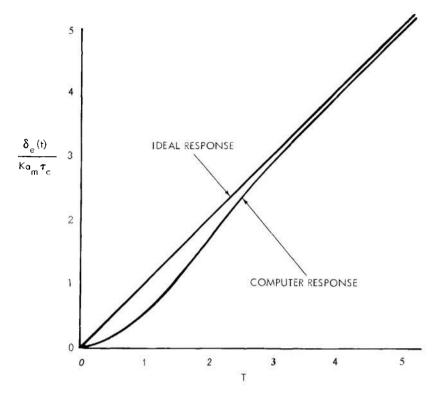

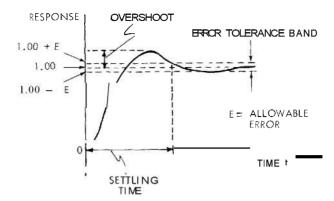

| 11-3          | TIME-RESPONSE CONSIDERATIONS                          | . 11-5  |

| 11-3.1        | REAL-TIME COMFUTATION                                 | . 11-5  |

| 11-3.2        | CONSIDERATIONS ASSOCIATED WITH THE DESIGN OF          |         |

|               | ANALOG COMPUTERS FOR REAL-TIME OPERATION              | . 11-9  |

| 11-3.3        | CONSIDERATIONS ASSOCIATED WITH THE DESIGN OF          |         |

|               | DIGITAL COMPUTERS FOR REAL-TIME OPERATION             |         |

| 11-4          | ACCURACY CONSIDERATIONS                               |         |

| 11-4.1        | GENERAL CONCEPTS                                      | 11-13   |

| 11-4.2        | THE ACCURACY OF SOLUTIONS OBTAINED                    |         |

|               | FROM ANALOG COMPUTERS                                 | . 11-16 |

| 11-4.3        | THE ACCURACY OF SOLUTIONS OBTAINED                    |         |

|               | FROM DIGITAL COMPUTERS                                | 11-19   |

| 11 <b>-</b> 5 | OPERATIONAL CONSIDERATIONS                            |         |

|               | REFERENCES                                            | . 11-22 |

|               | CHAPTER 12. EXAMPLES OF MEANS USED TO MEET PARTICULAR |         |

|               | TYPES OF DESIGN PROBLEMS                              |         |

| 12-1          | INTRODUCTION                                          | 12-1    |

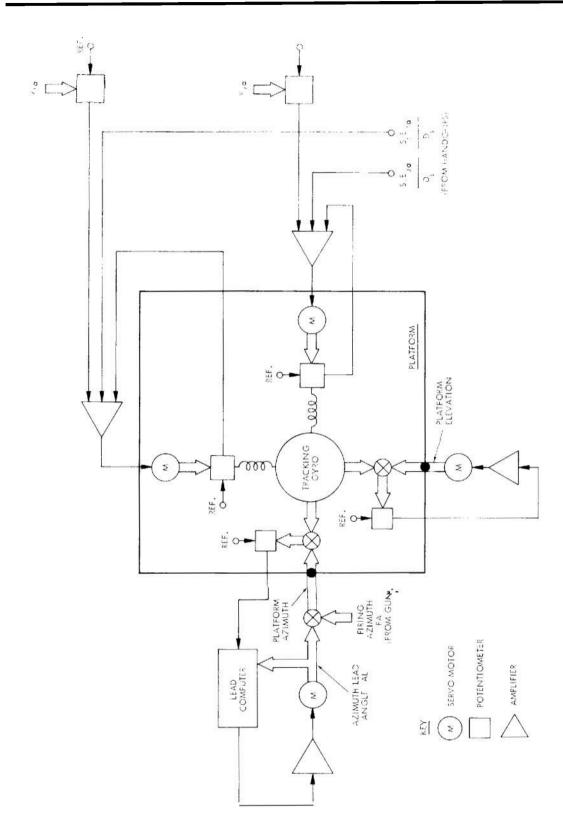

| 12-1          | GUN DATA COMPUTER T29E2                               |         |

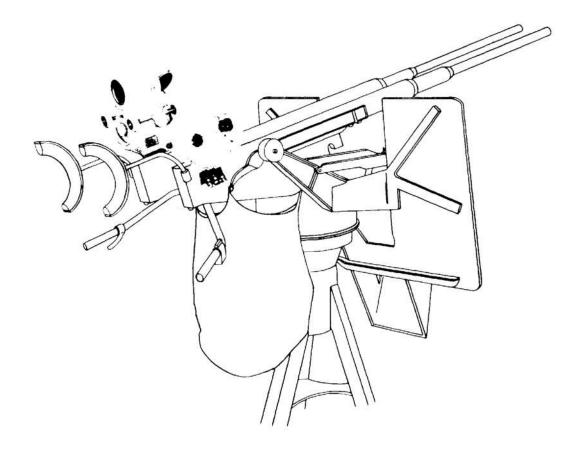

| 12-3          | LIGHTWEIGHT FIRE CONTROL EQUIPMENT                    | • 12 1  |

| 12-5          | FOR ROCKET LAUNCHERS                                  | . 12-5  |

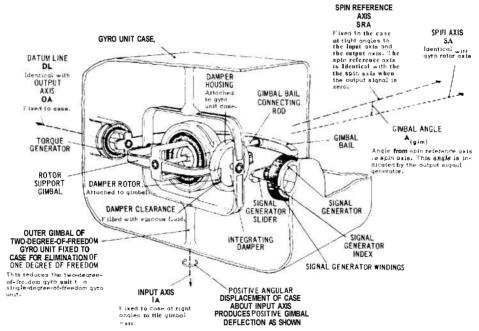

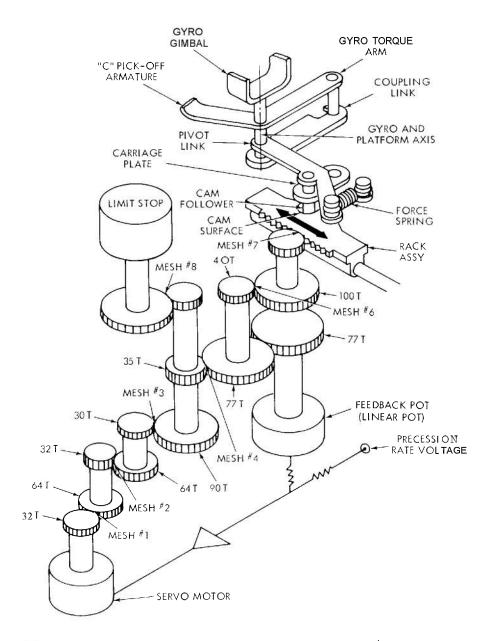

| 12-4          | VIGILANTE COMPUTER GYRO/PLATFORM SYSTEM               |         |

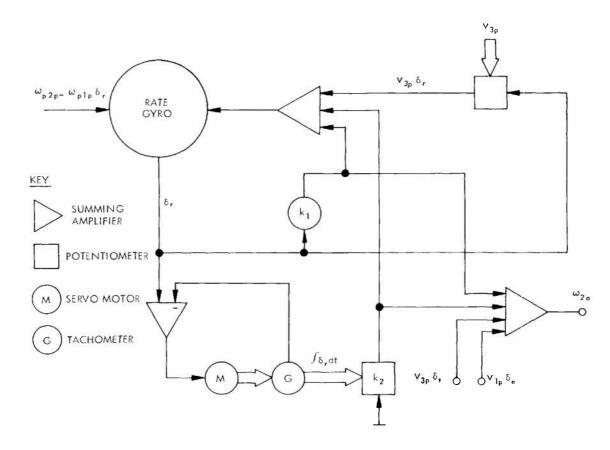

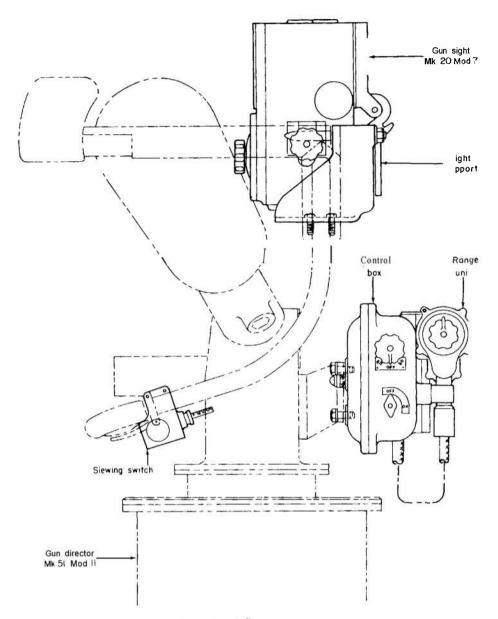

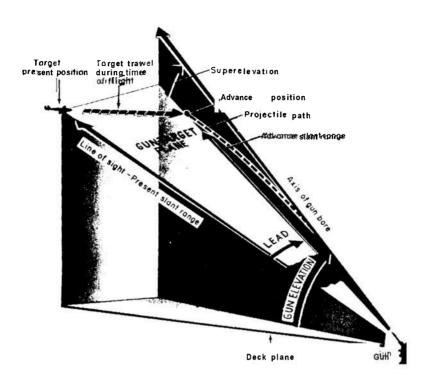

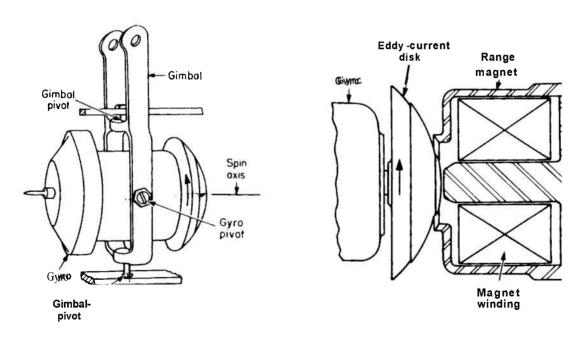

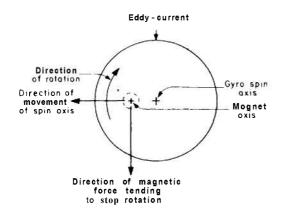

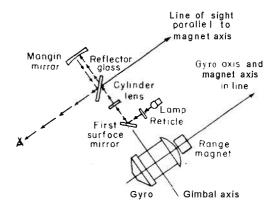

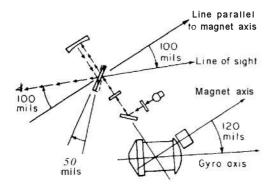

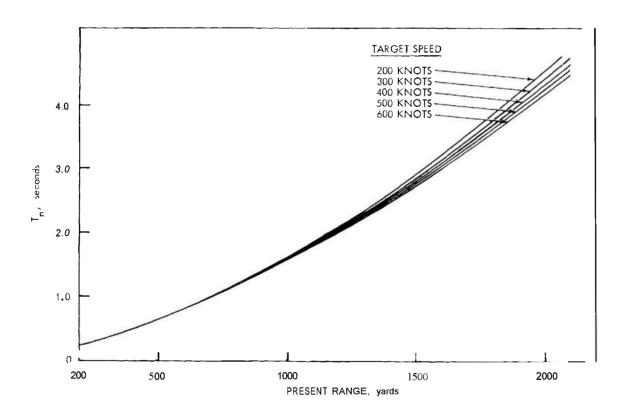

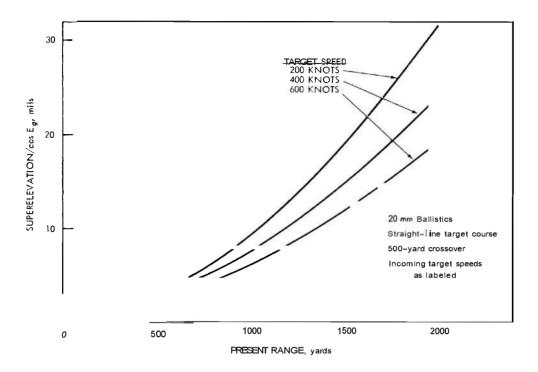

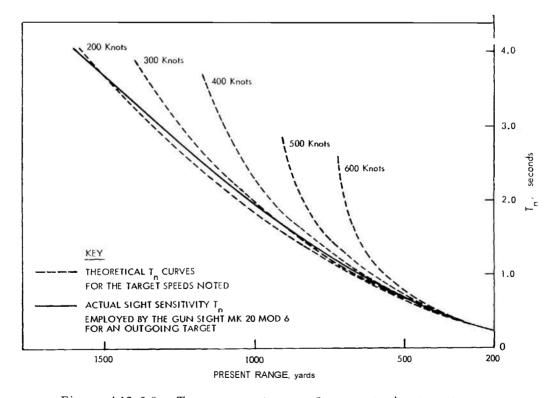

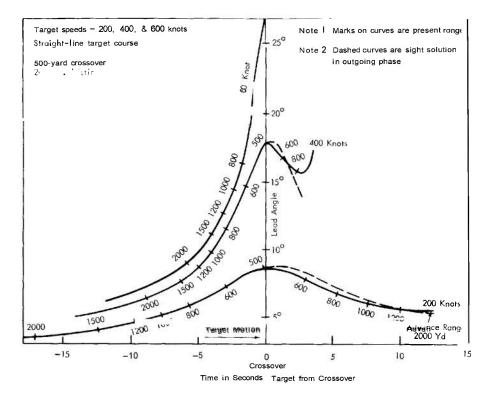

| 12-5          | MARK 20 GYRO COMPUTING SIGHT                          |         |

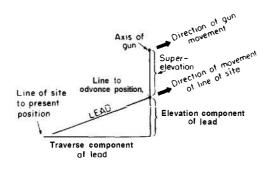

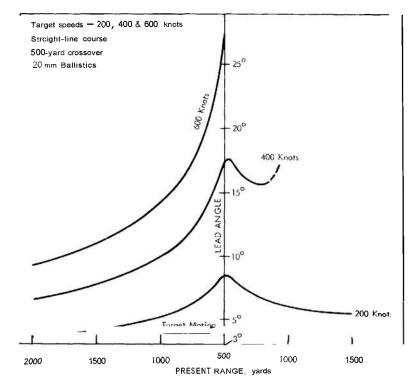

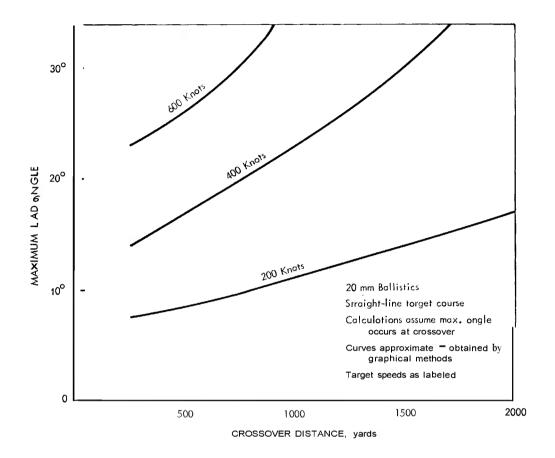

| 12-5.1        | COMPUTATION OF LEAD                                   |         |

| 12-5.2        | TIME OF FLIGHT AND MAGNET CURRENT                     |         |

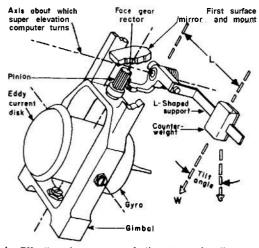

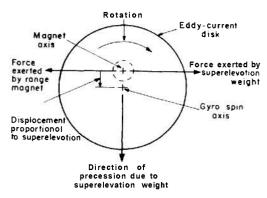

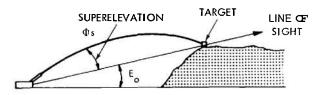

| 12-5.3        | COMPUTATION OF STJPERELEVATION                        |         |

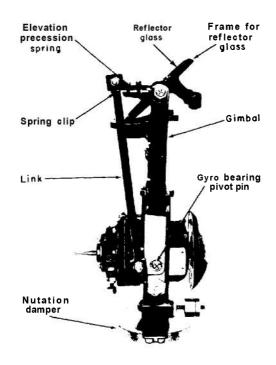

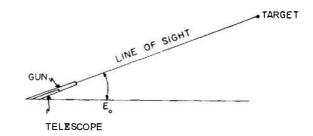

| 12-5.4        | DISPLACEMENT OF THE LINE OF SIGHT                     |         |

| 12-5.5        | FUNCTIONS OF THE SIGMA FACTOR                         |         |

| 12-6          | CANT-CORRECTION SYSTEM OF BALLISTIC COMPUTER XM17     |         |

| 12-6.1        | BACKGROUND OF BALLISTIC COMPUTER XM17                 |         |

| 12-6.2        | THE DESIGN USED FOR THE CANT-CORRECTION SYSTEM        |         |

| 12-6.3        | ACCURACY ANALYSIS OF THE CANT-CORRECTION SYSTEM       |         |

| 12-6.4        | FACTORS TO BE CONSIDERED BEFORE                       |         |

| 12-0.4        | UNDERTAKING AN IMPROVED DESIGN                        | .12-37  |

| Appendix      |                                                       |         |

| • •           | THE MATURIAL TRACE OF LEAD COMPANY TWO                | 10.00   |

| 12-1          | THE MATHEMATICS OF LEAD COMPUTATION                   | . 12-38 |

| 12-2          | CALIBRATION CHARACTERISTICS OF GUN SIGHT MARK 20      |         |

|               | MOD 6 AND DATA ON LEAD ANGLE AND TIME OF FLIGHT       | 10 44   |

|               | TOTAL 20 MINI BALBELS TIES                            | . 12-41 |

|               | REFERENCES                                            | 12 - 49 |

| Paragraph |                                                                                    | Page         |

|-----------|------------------------------------------------------------------------------------|--------------|

|           | CHAPTER 13. EXAMPLE OF A PROBLEM INVOLVING THE INTERCONNECTION OF A COMPLEX SYSTEM |              |

| 13-1      | INTRODUCTION                                                                       | 13-1         |

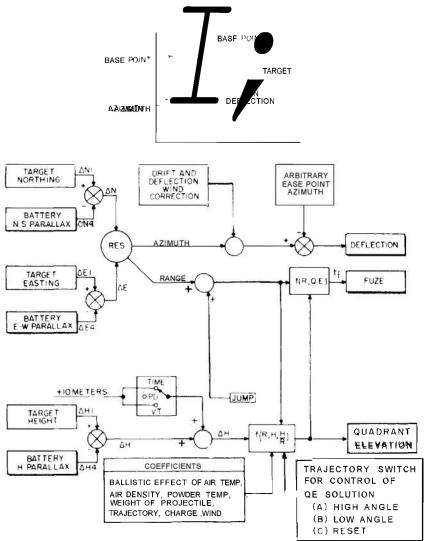

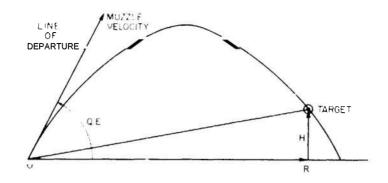

| 13-2      | TRAJECTORY COMPUTATIONS                                                            | 13-2         |

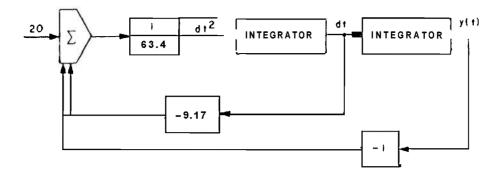

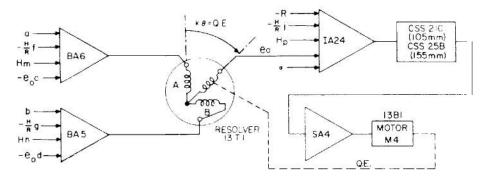

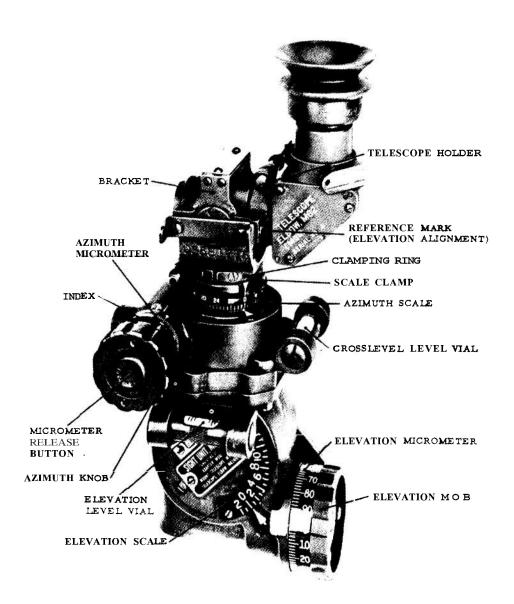

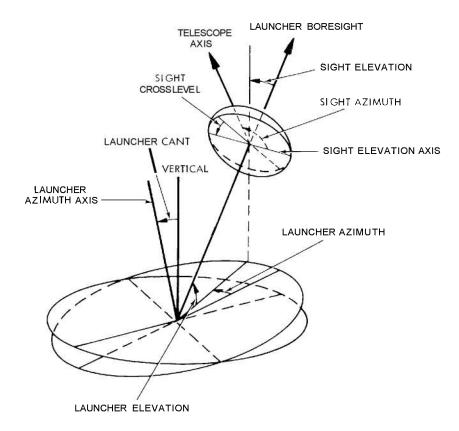

| 13-3      | COMPUTER DESIGN                                                                    | 13-4         |

| 13-4      | CONCLUSIONS                                                                        | <b>13-</b> 9 |

|           | INDEX                                                                              | IN-1         |

#### LIST OF ILLUSTRATIONS

| Fig. No.                | Title                                                                                                                        | Page         |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|

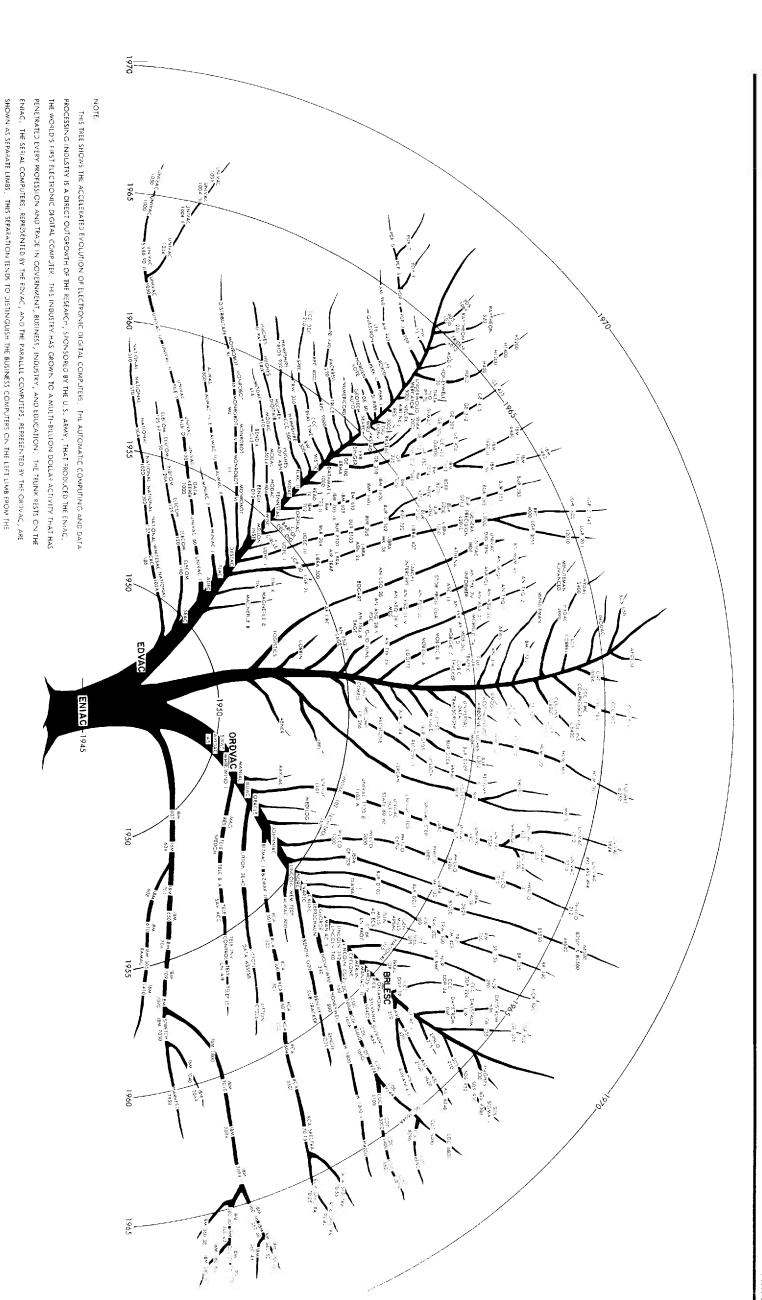

| I- 1                    | The Computer Tree €or Electronic Digital Computers                                                                           | I-5          |

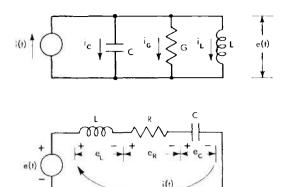

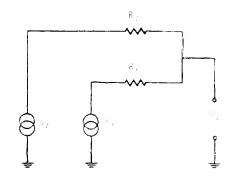

| 1-1                     | Equivalent. or Dual, Electrical Networks                                                                                     | 1 _7         |

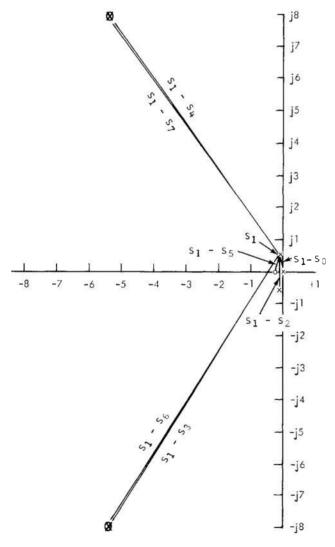

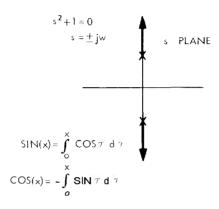

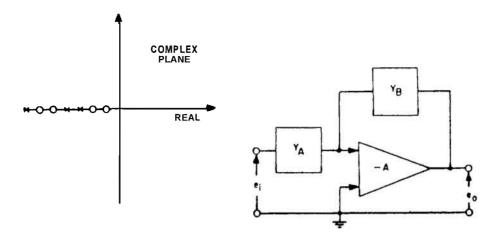

| 2-1                     | Locations of the Roots of Eq. 2-45 in the s-plane                                                                            | 2-10         |

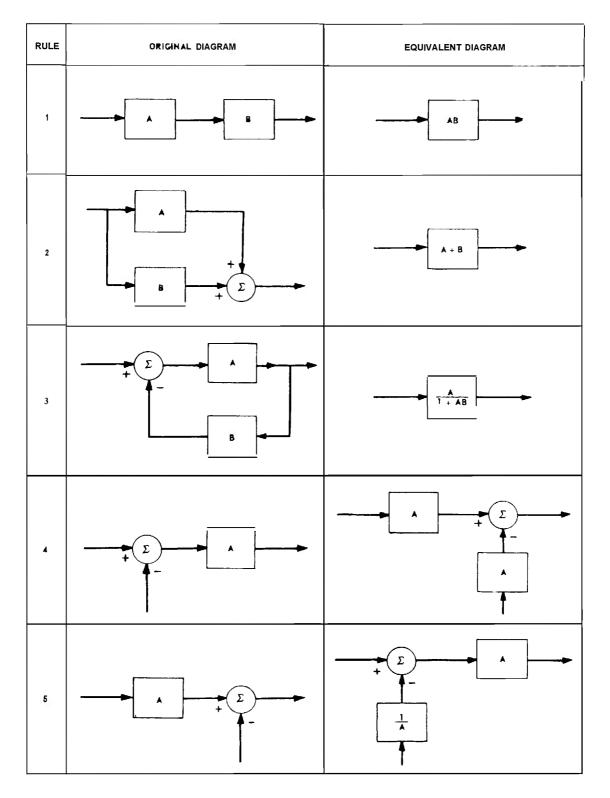

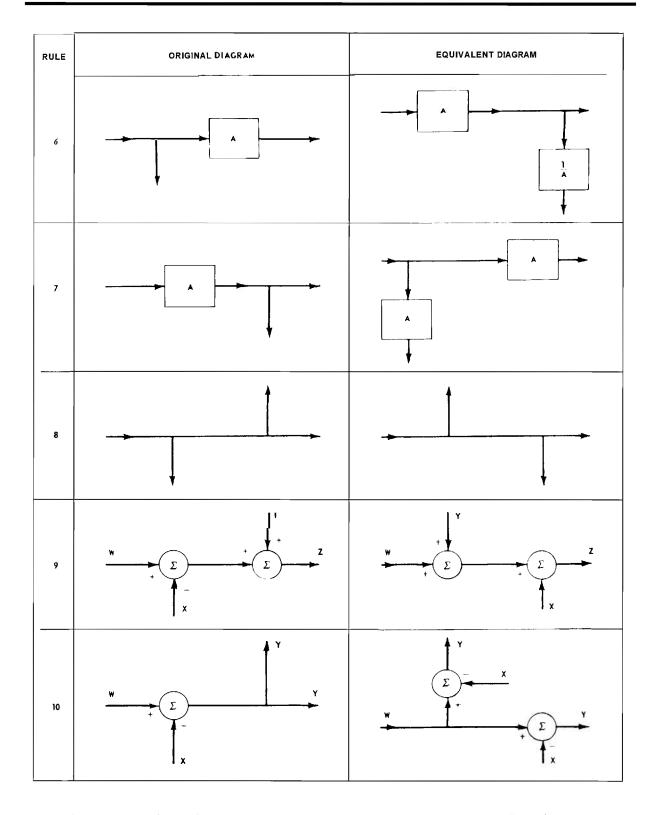

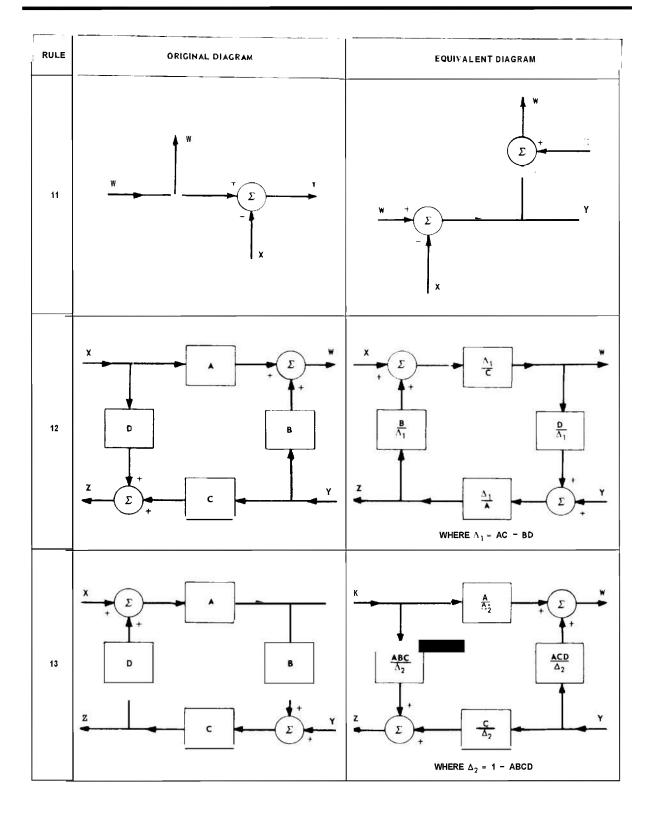

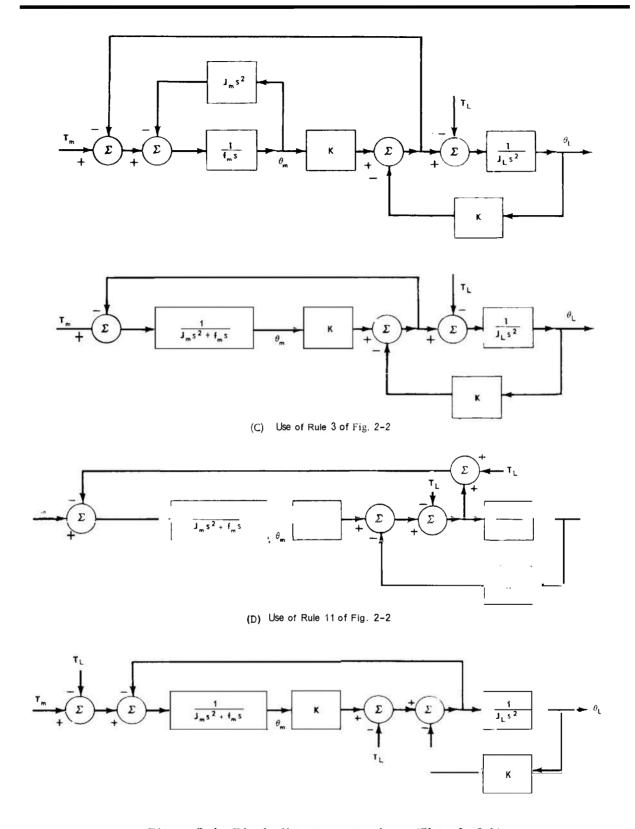

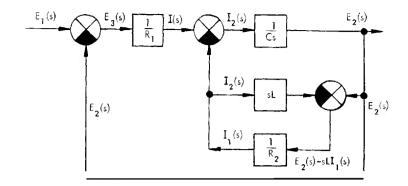

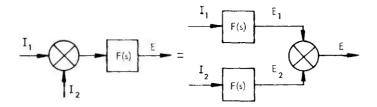

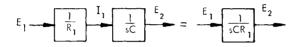

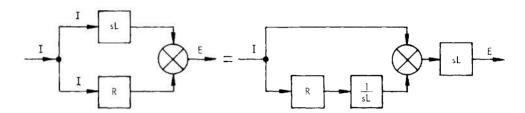

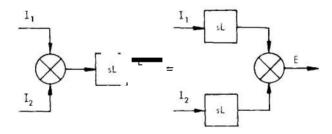

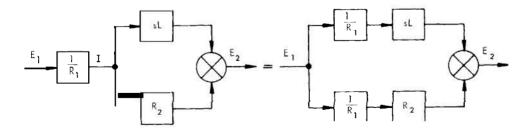

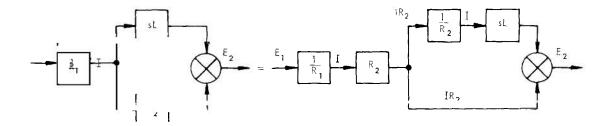

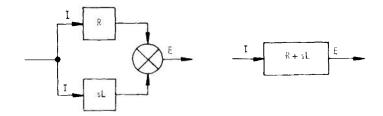

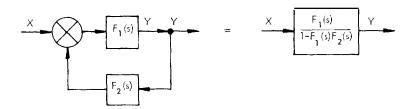

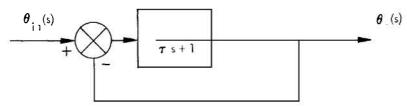

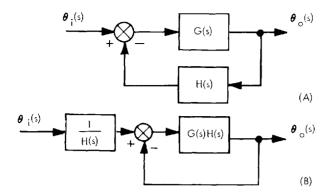

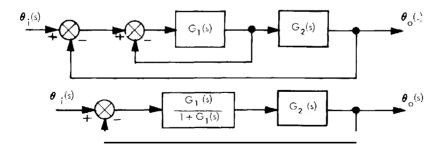

| 2-2                     | Block-diagram Manipulation and Reduction "Rules"                                                                             | 2-12         |

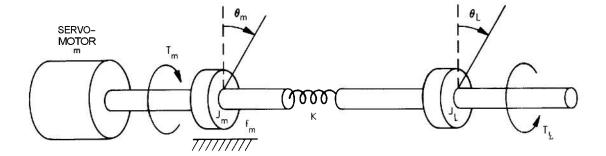

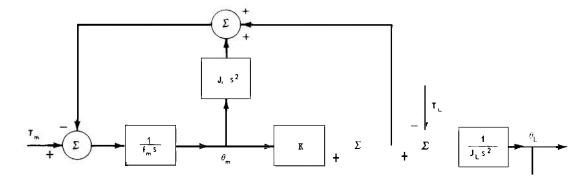

| 2-3                     | Mechanical Schematic Diagram of a Servomotor Coupled                                                                         |              |

|                         | to an Inertial Load by Means of a Flexible Shaft                                                                             | 2-15         |

| 2-4                     | Block-diagram Examples                                                                                                       | 2-15         |

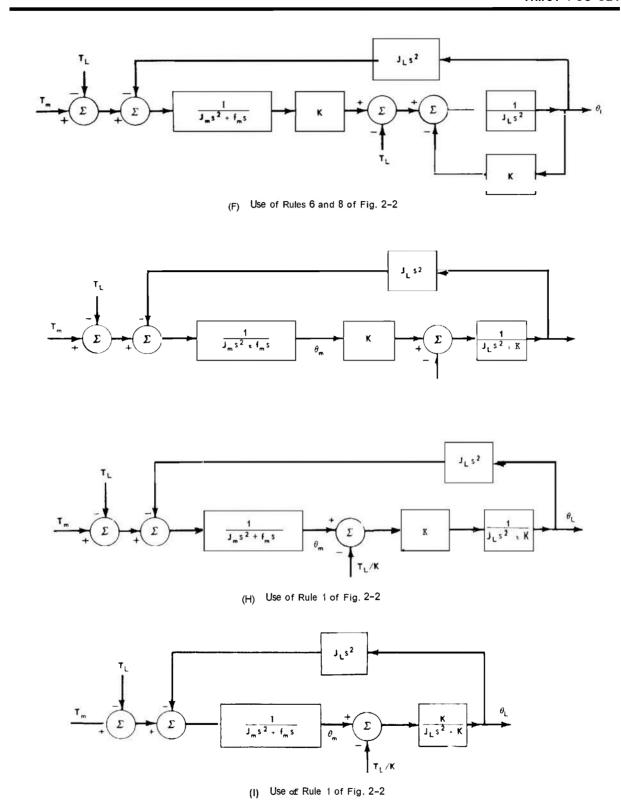

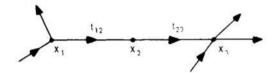

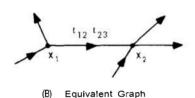

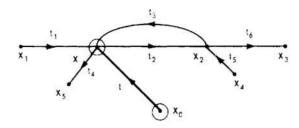

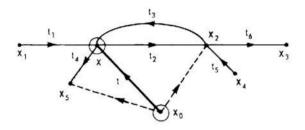

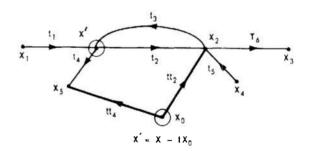

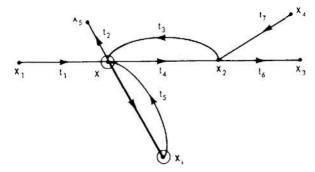

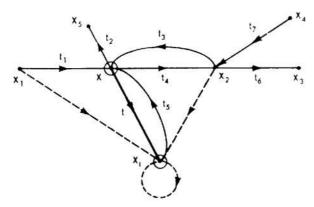

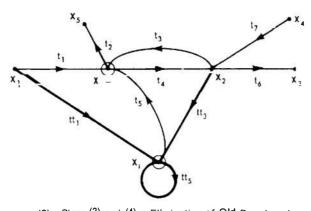

| 2-5                     | Signal-flow Graph in Three Variables                                                                                         | 2-18         |

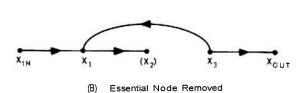

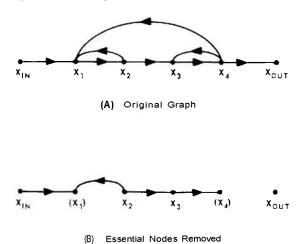

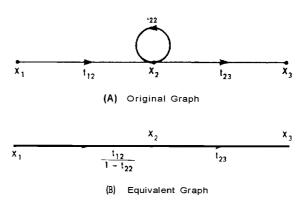

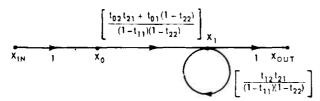

| 2-6                     | Signal-flow Graph of Order One                                                                                               | 2-18         |

| 2-7                     | Signal-€low Graph of Order Two                                                                                               | 2-18         |

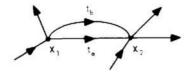

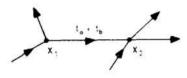

| 2-8<br>2-9              | Signal-flow Graph Showing Addition of Parallel Branches                                                                      | 2-19         |

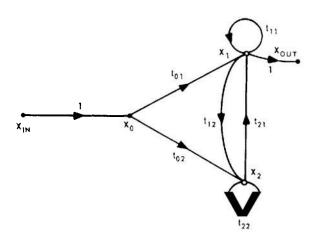

| 2-9                     | Signal-flow Graph Showing Multiplication of Cascaded Branches                                                                | 2-19<br>2-19 |

| 2- 10                   | Signal-flow Graph Showing Termination Shifted One Node Forward Signal-flow Graph Showing Origin Shifted One Node Backward    | 2-19         |

| 2- 11                   | Signal-flow Graph Showing Elimination of a Self-loop                                                                         | 2-20         |

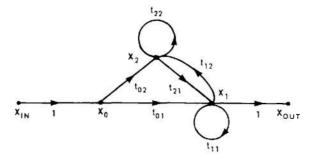

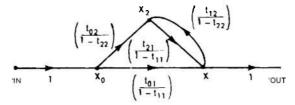

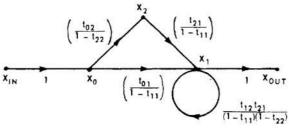

| 2- 12                   | Signal-flow Graph Showing Reduction of Second-order Graph                                                                    | 2-20         |

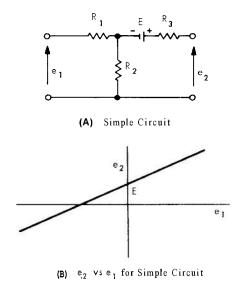

| 2- 13                   | A Simple Circuit and its Associated Input-output Relationship                                                                | 2-21         |

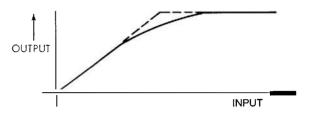

| 2-15                    | Plot Depicting the Limiting Type of Nonlinearity                                                                             | 2-27         |

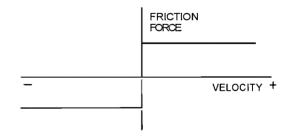

| 2- 16                   | Graphical Representation of Coulomb Friction                                                                                 | 2-27         |

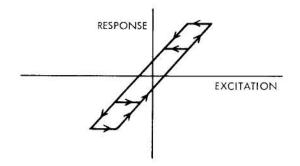

| 2- 17                   | Graphical Representation of Hysteresis                                                                                       | 2-28         |

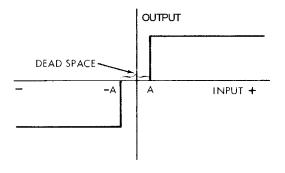

| 2-18                    | Graphical Representation of a Relay with                                                                                     |              |

|                         | Dead-space but no Hysteresis                                                                                                 | 2-28         |

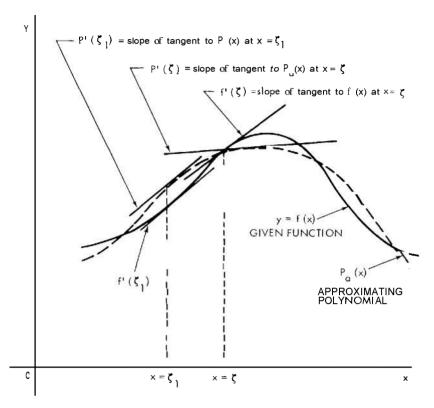

| 2- 19                   | The Difference Between the Derivative of a Given Function                                                                    |              |

|                         | and the Derivative of its Approximating Polynomial                                                                           | 2-45         |

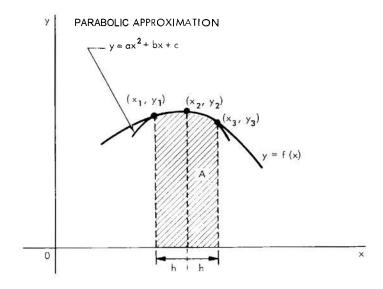

| 2- 20                   | Integration by Means of Simpson's Rule                                                                                       | 2-46         |

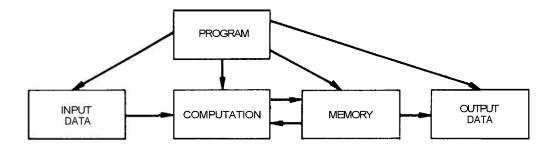

| <i>3</i> - 1            | The Computing Process                                                                                                        | 3-3          |

| 3-2                     | Basic Nomogram                                                                                                               | 3-4          |

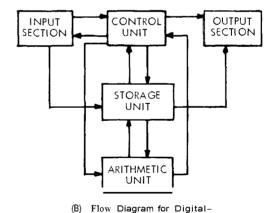

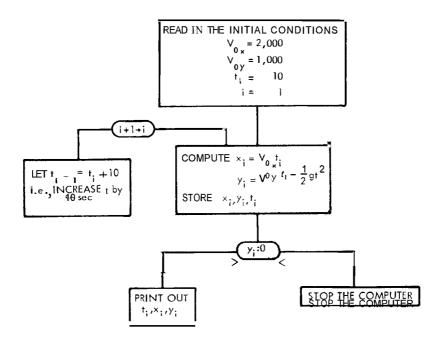

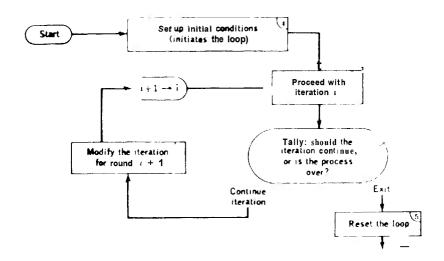

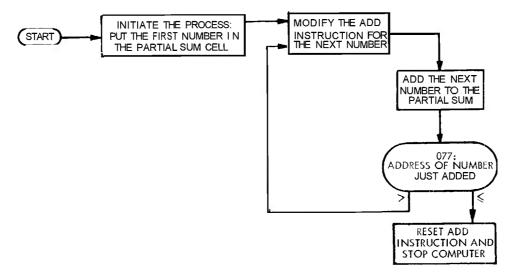

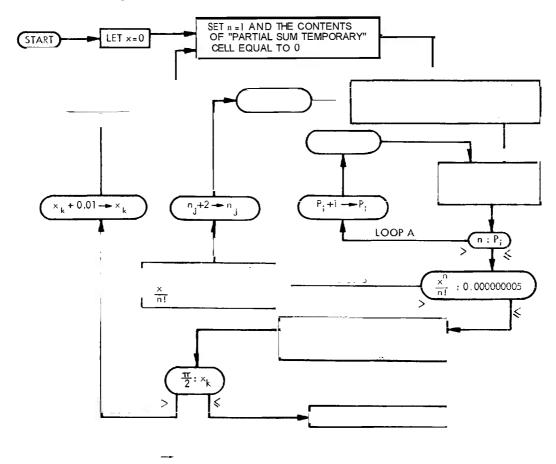

| 4- 1                    | Computation Flow Diagrams                                                                                                    | 4-1          |

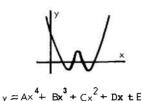

| 4-2                     | Fourth-degree Polynomial. All Roots Real and Positive                                                                        | 4-9          |

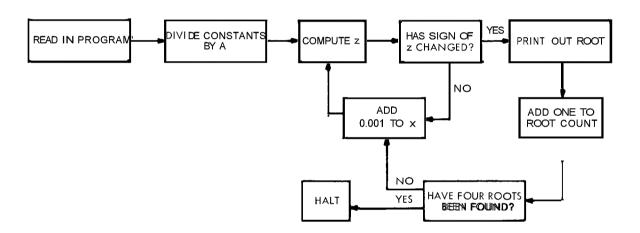

| 4-3                     | Flow Diagram Depicting the Steps Involved in Computing                                                                       |              |

|                         | the Roots of a Polynomial                                                                                                    | 4-10         |

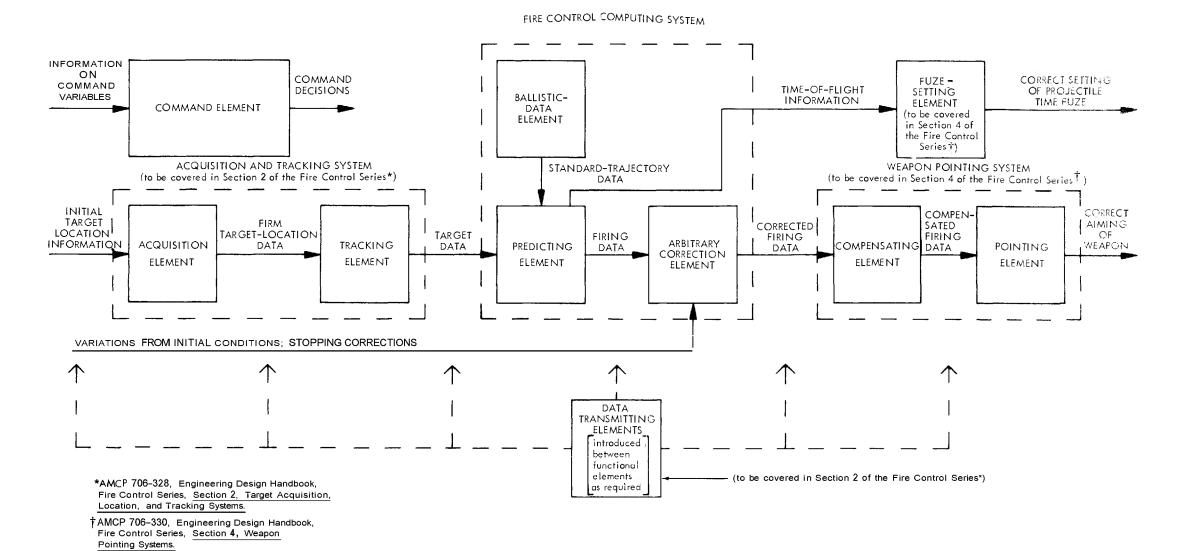

| 4-4                     | Functional Diagram of a Hypothetical Fire Control System that                                                                |              |

|                         | Contains All of the Functional Elements Associated with                                                                      |              |

| 4 - 7                   | Fire Control Equipment                                                                                                       | 4-15         |

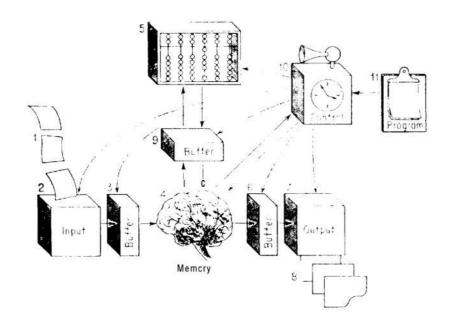

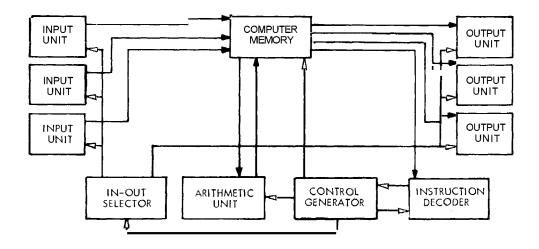

| 4-5                     | Organization of the Computer in Pictorial Form                                                                               | 4-17         |

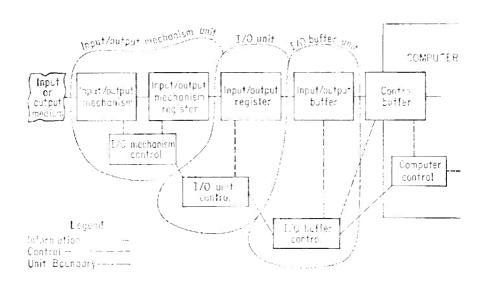

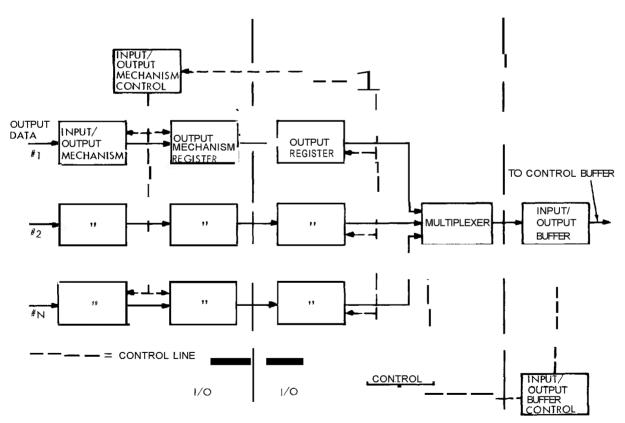

| 4-6<br>4-7              | Relation of the Input/Output to the Computer                                                                                 | 4-17<br>4-18 |

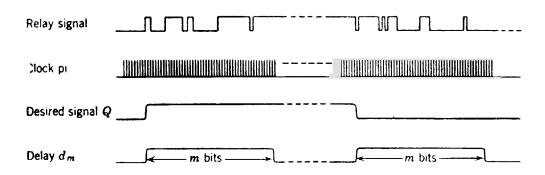

| 4- /                    | Computer Input/Output Configuration for Multiple Inputs  Derivation of a Smoothed Signal From an Asynchronous Signal Device. | 4-18         |

| <b>4-</b> 8 <b>4-</b> 9 | Flow Chart for Computation of Missile Trajectory                                                                             | 4-19         |

| 4- 10                   | Flow Chart of Generalized Loop                                                                                               | 4-22         |

| 4- 11                   | Flow Chart for Instruction Medification                                                                                      | 4-23         |

| 4- 12                   | Flow Chart of Loops Within Loops                                                                                             | 4-23         |

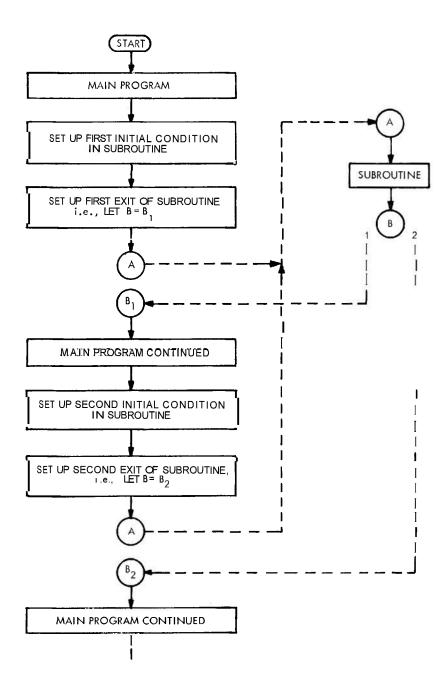

| 4-13                    | Flow Chart for Setting Up Initial Conditions and                                                                             | . 23         |

|                         | Different Exits of a Subroutine                                                                                              | 4-24         |

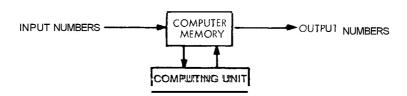

| 4- 14                   | Memory and Computing Unit                                                                                                    | 4-25         |

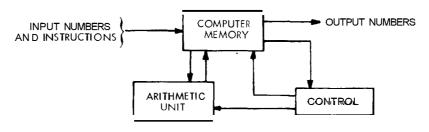

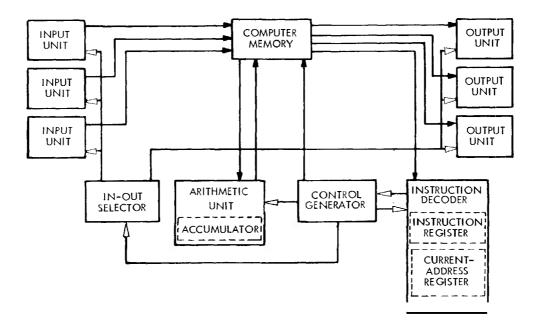

| 4- 15                   | Arithmetic Unit and Control                                                                                                  | 4-25         |

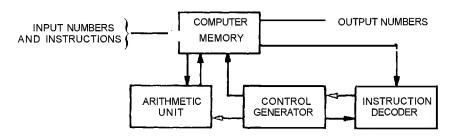

| 4- 16                   | Instruction Decoder and Control Generator                                                                                    | 4-26         |

|                         |                                                                                                                              |              |

| Fig. No.         | Title                                                                                                                                            | Page |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4- 17            | Input and Output Functional Units                                                                                                                | 4-26 |

| 4-18             | Accumulator. Instruction Register. and Current-address Register                                                                                  | 4-27 |

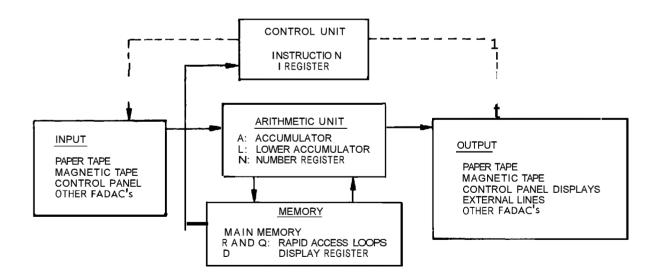

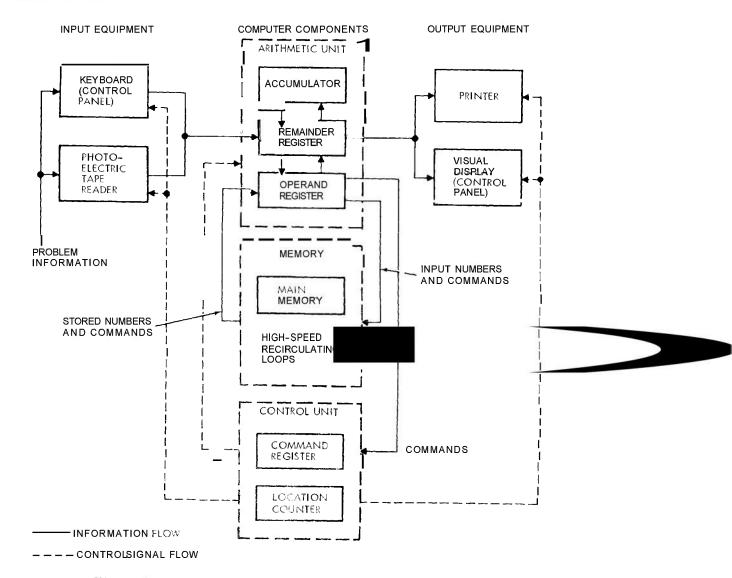

| 4- 19            | Functional Diagram of FADAC System                                                                                                               | 4-29 |

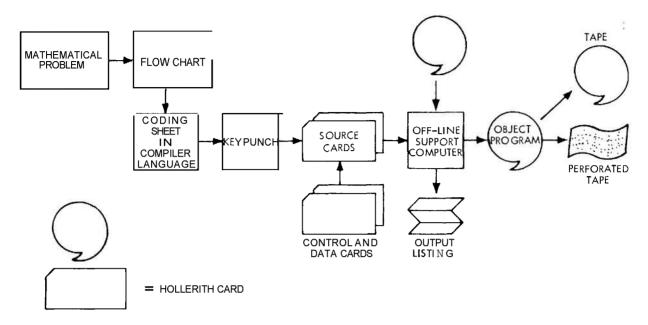

| 4- 20            | The Basic Programming Process                                                                                                                    | 4-32 |

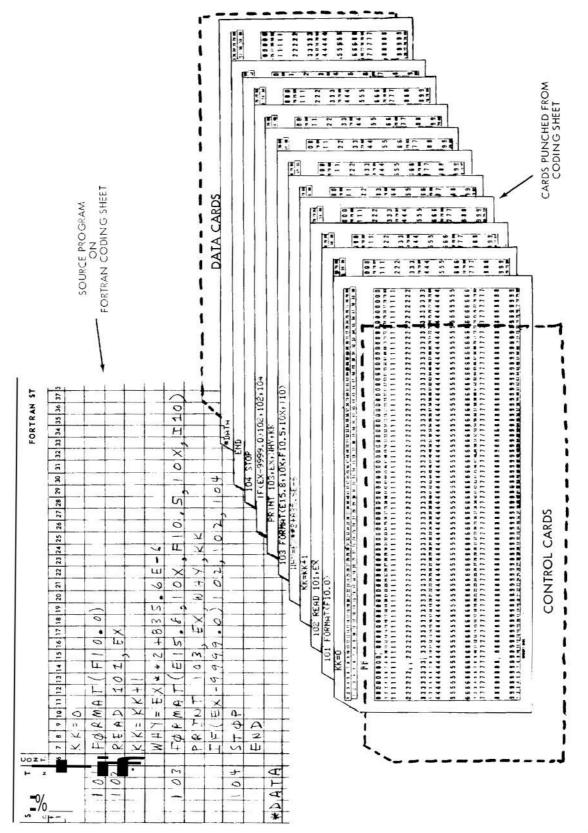

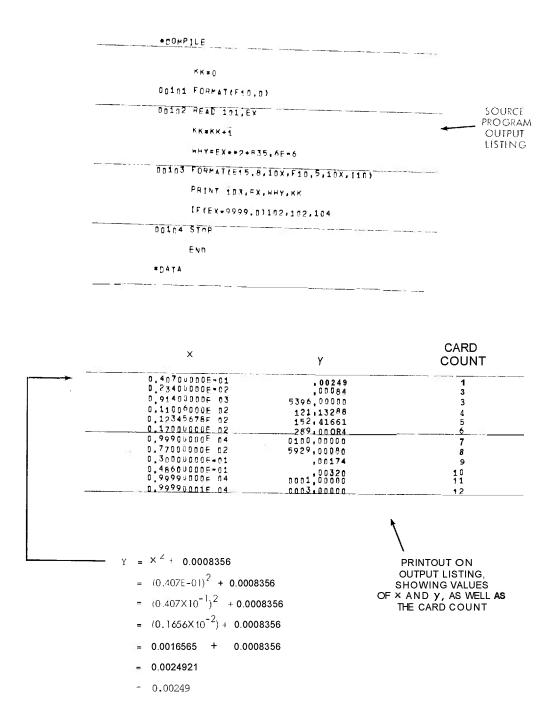

| 4-21             | An Illustrative FORTRAN Program                                                                                                                  | 4-33 |

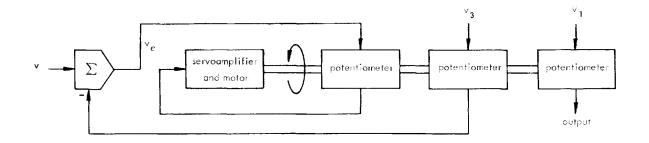

| 4-22             | Typical Digital Servo                                                                                                                            | 4-38 |

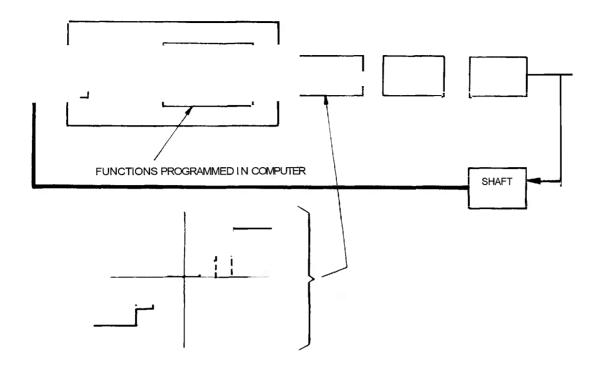

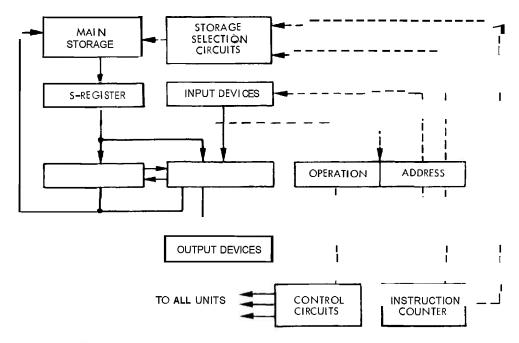

| 4-23             | Typical Arrangement for a Stored-program Computer                                                                                                | 4-39 |

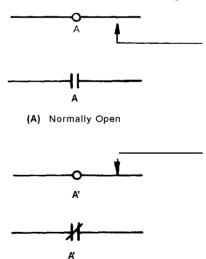

| 4-24             | Representation of Relay Contacts                                                                                                                 | 4-42 |

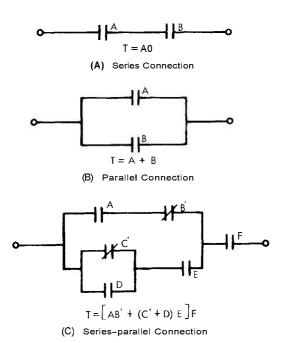

| 4-25             | Three Simple Contact Networks                                                                                                                    | 4-44 |

| 4- 26            | Simplification Resulting From Application of Theorems                                                                                            | 4-45 |

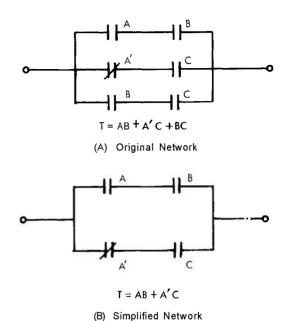

| 4- 27            | Serial vs Parallel Computer                                                                                                                      | 4-50 |

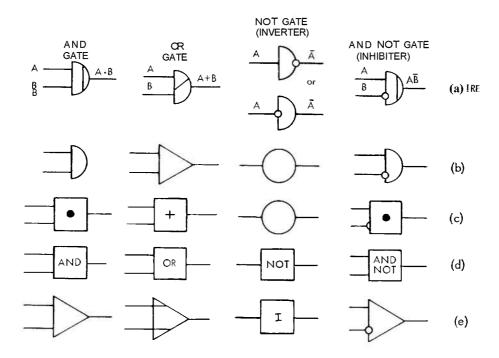

| 4-28             | Logical Symbols for Inverters. Thhibiters. and Two-input AND-OR                                                                                  |      |

|                  | Gates                                                                                                                                            | 4-52 |

| 4- 29            | Logical Symbols for Two-input NAND-NOR Gates                                                                                                     | 4-52 |

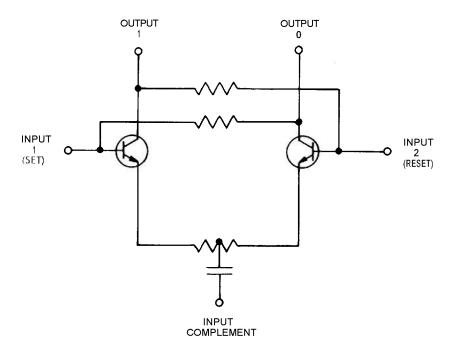

| 4- 30            | The Basic Flip-flop                                                                                                                              | 4-54 |

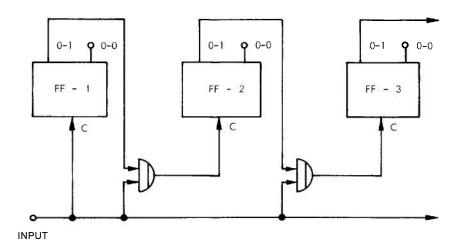

| 4-31             | A Typical Binary Counter                                                                                                                         | 4-54 |

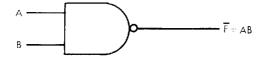

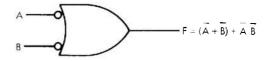

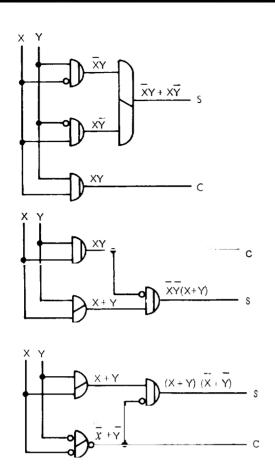

| 4- 32            | Forms of Half-adder Logic                                                                                                                        | 4-55 |

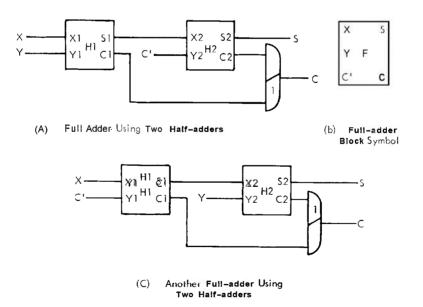

| 4-33             | Full-adder Using Two Half-adders                                                                                                                 | 4-55 |

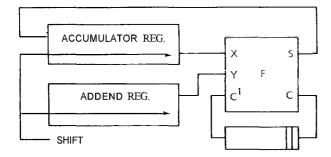

| 4-34             | Serial Binary Accumulator                                                                                                                        | 4-57 |

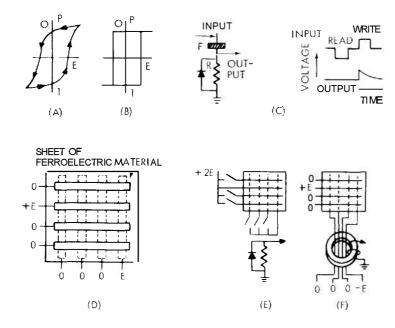

| 4-35             | Ferroelectric Storage                                                                                                                            | 4-67 |

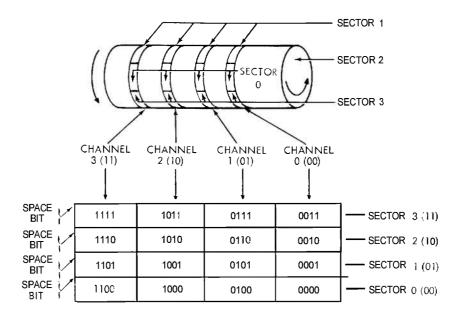

| 4-36             | Arrangement of a Hypothetical, Sixteen-word Serial                                                                                               |      |

|                  | Memory on the Surface of a Drum                                                                                                                  |      |

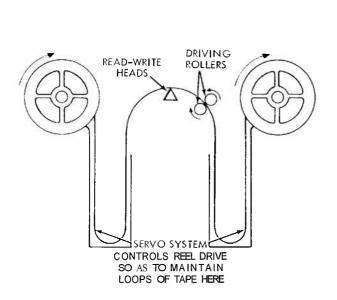

| 4-37             | Typical Reel System for Magnetic Tape                                                                                                            |      |

| 4-38             | Method of Providing an Endless Tape                                                                                                              | 4-69 |

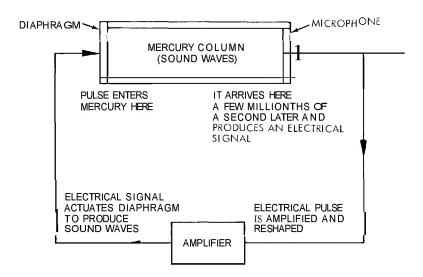

| 4-39             | Acoustic Delay Line                                                                                                                              | 4-70 |

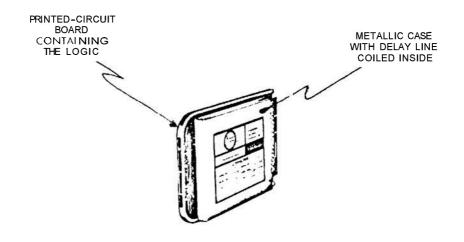

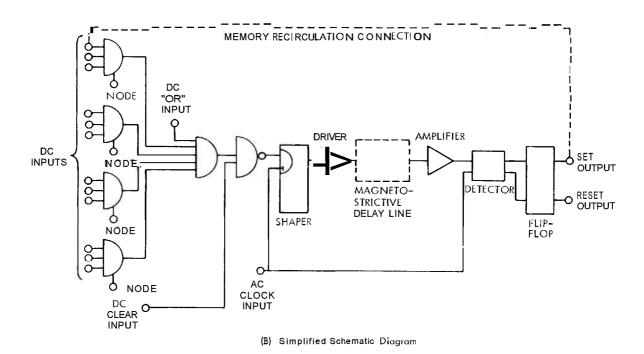

| 4-40             | A Typical Serial Memory Utilizing a Magnetostrictive Delay Line                                                                                  | 4-71 |

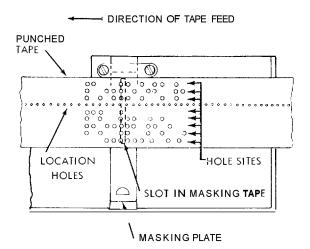

| 4-41             | Reading of Punched Paper Tape                                                                                                                    | 4-72 |

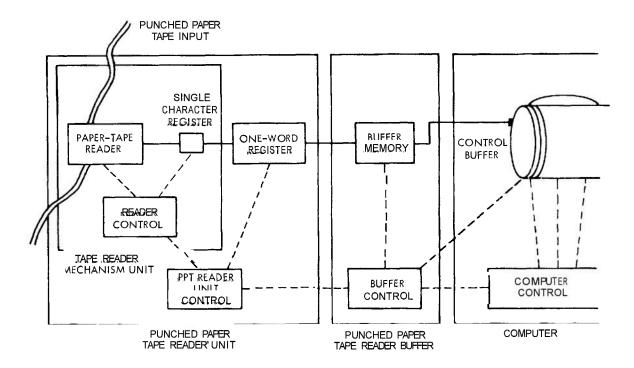

| 4- 42            | Typical Arrangement for Reading Punched Paper Tape                                                                                               | 4-73 |

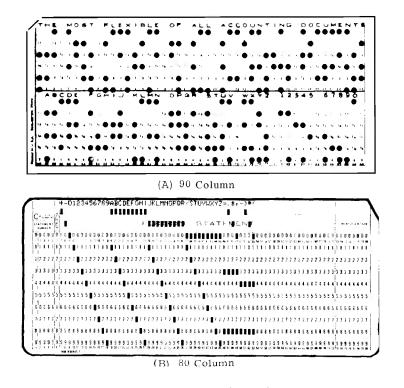

| 4-43             | Punch Cards                                                                                                                                      | 4-73 |

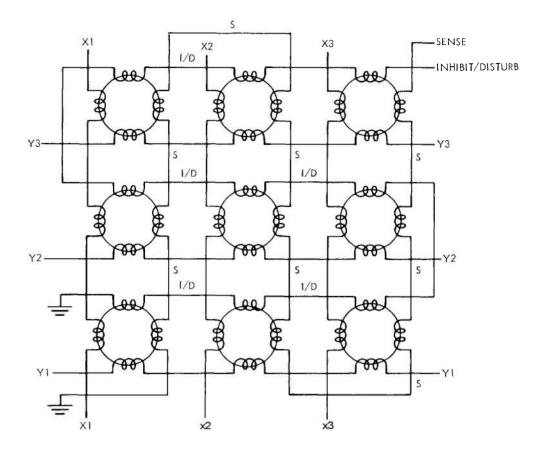

| 4-44             | Corner of a Core Matrix                                                                                                                          | 4-74 |

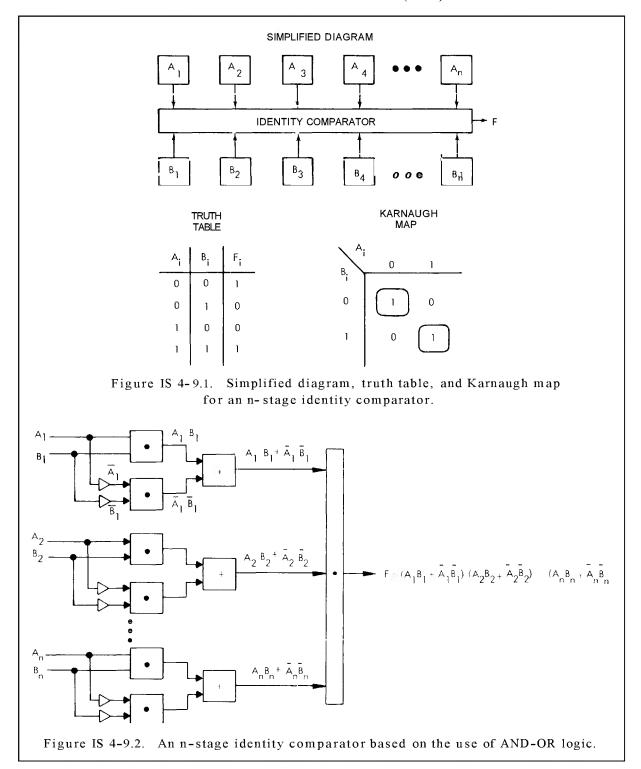

| IS4-9.1          | Simplified Diagram. Truth Table. and Karnaugh Map for an n-stage                                                                                 |      |

|                  | Identity Comparator                                                                                                                              | 4-61 |

| 1 <b>S</b> 4-9.2 | An n-stage Identity Comparator Based on the Use of AND-OR Logic                                                                                  | 4-61 |

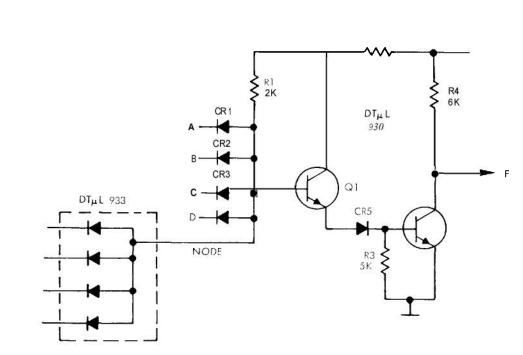

| IS4-9.3          | Schematic Representation of a Single DTpL 930 Gate                                                                                               |      |

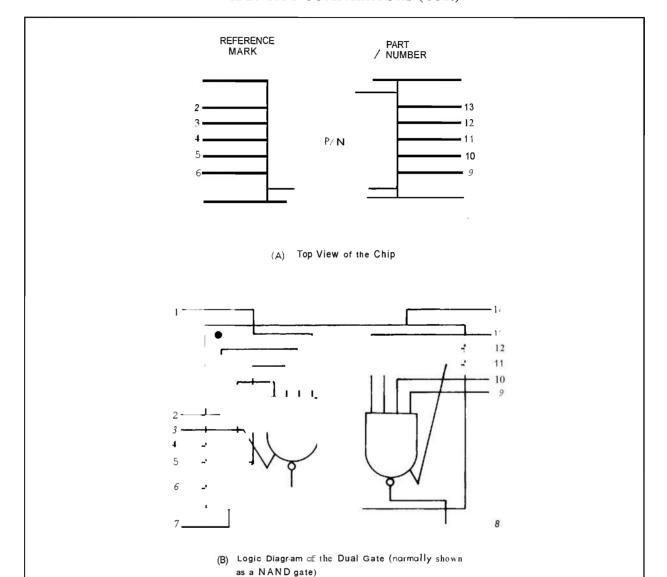

| IS4-9.4          | Physical Structure ard Actual Pin Connections of the                                                                                             |      |

|                  | DTpL 930 Monolithic Chip                                                                                                                         | 4-63 |

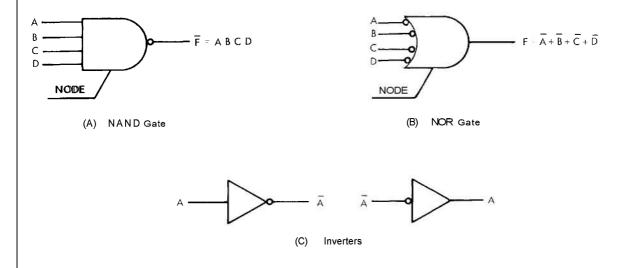

| IS4- 9.5         | Logic Symbols for the DTpL 930 Gate                                                                                                              | 4-64 |

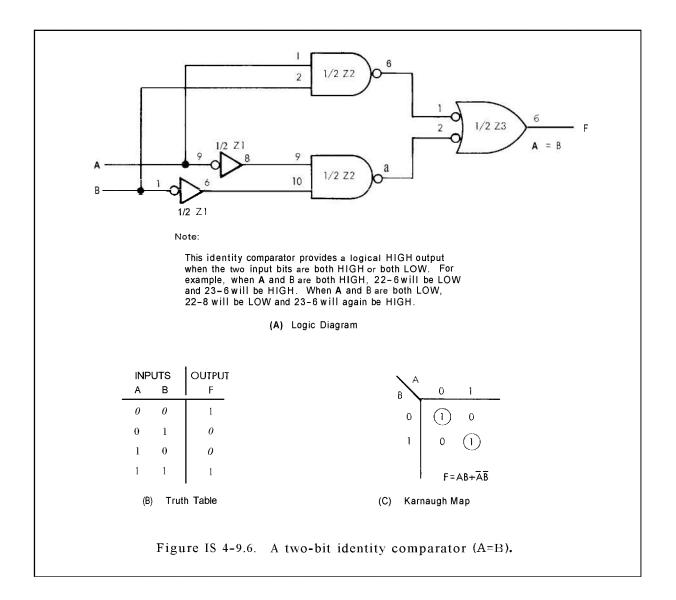

| IS4-9.6          | A Two-bit Identity Comparator (A=B)                                                                                                              | 4-65 |

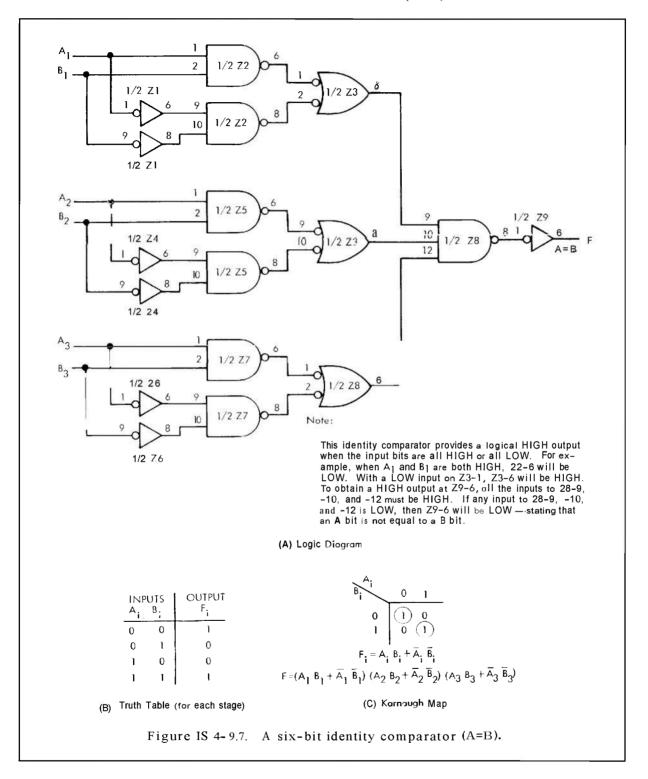

| TS4- 9.7         | A Six-bit Identity Comparator (A=B)                                                                                                              |      |

| 5 1              | Concert of the Digital Differential Assissan                                                                                                     |      |

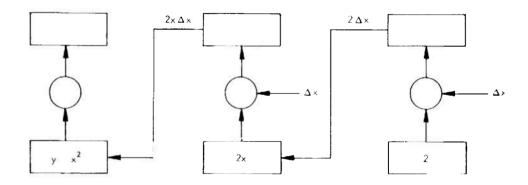

| 5-1              | Concept of the Digital Differential Analyzer                                                                                                     |      |

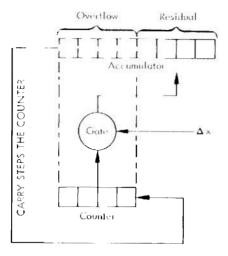

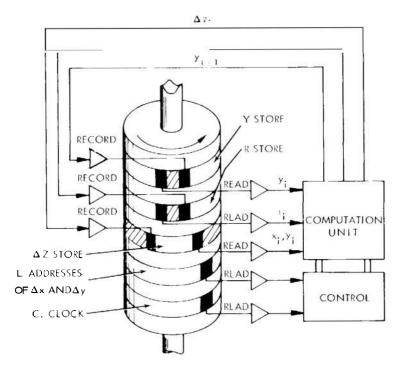

| 5-2              | The DDA Computing Unit                                                                                                                           | 5-5  |

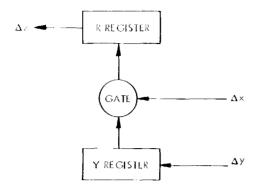

| 5-3<br>5-4       | An Illustrative Combination of Two DDA Computing Units                                                                                           | 5-5  |

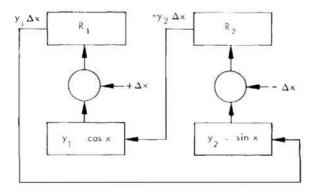

| 5-4<br>5-5       | The Computation of $y_3 = y_1 y_2 \dots$<br>The Computation of $y = x^2 \dots$                                                                   | 5-6  |

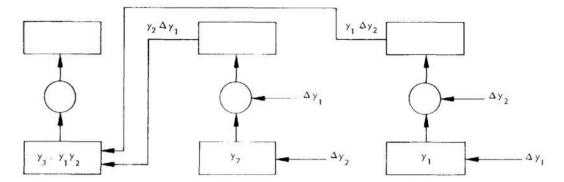

| 5- 5<br>5- 6     |                                                                                                                                                  | 5-6  |

| 5- 0<br>5- 7     | Simplified Representation of DDA Operation                                                                                                       | 5-7  |

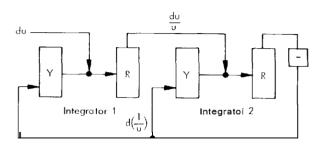

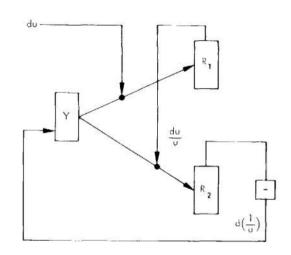

| 5- 7<br>5- 8     | Conventional and Shared-integrator DDA Implementations of 1/u<br>Connections Employed for the solution of                                        | 5-8  |

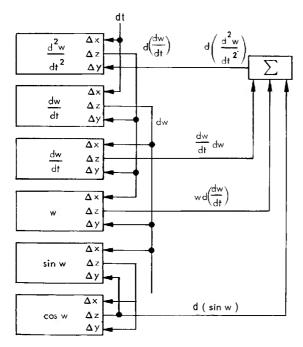

| - 0              | $(d^2w/dt^2)$ _ w(dw/dt) _ sin w = 0                                                                                                             | 5-10 |

|                  | $(a \ w/at) = w(aw/at) = \sin w = 0 \dots \dots$ | 5-10 |

| Fig. No.     | Title                                                                                                                     | Page         |

|--------------|---------------------------------------------------------------------------------------------------------------------------|--------------|

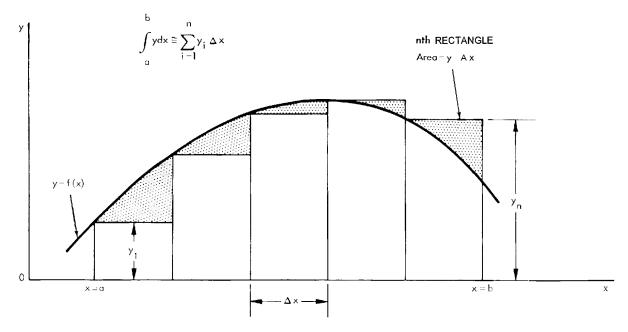

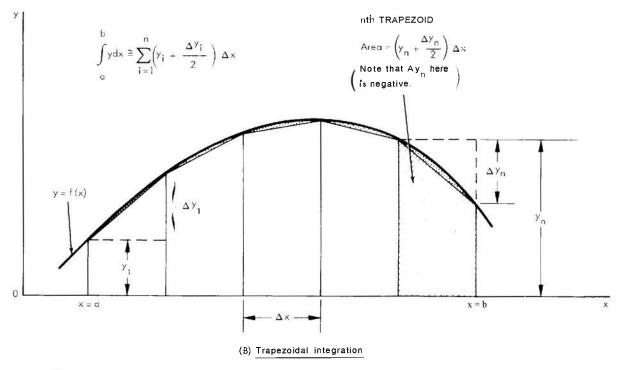

| 5-9          | Truncation Errors Associated with Rectangular and Trapezoidal Integration                                                 | 5-13         |

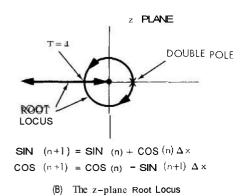

| 5-10         | The Stability of a Continuous (Analog) Solution of the                                                                    |              |

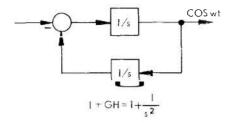

| 5- 11        | Equations for Sine and Cosine Functions                                                                                   | 5-15         |

| 5- 12        | Parallel Implementation                                                                                                   | 5-15         |

| 3-12         | A DDA-integrator Solution of the Sine and Cosine Equations;<br>Serial Implementation                                      | 5-16         |

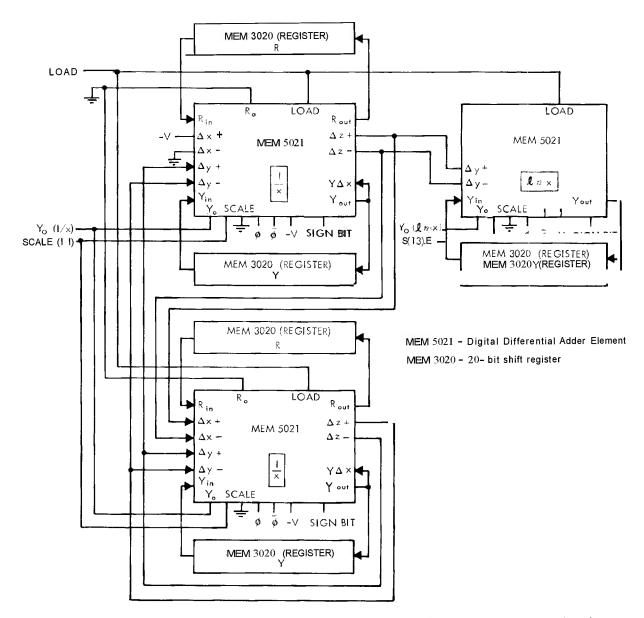

| 5-13         | Interconnection Diagram of DDA and Shift-register Integrated-circuit Elements (MOS) to Solve the Equation $y = \ell n(x)$ | 5-17         |

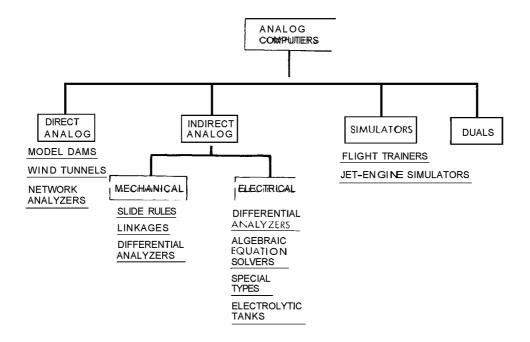

| 6-1          | Classification of Various Analog Devices                                                                                  | 6-2          |

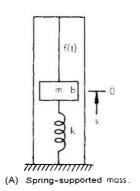

| 6-2          | Analogous Mechanical and Electrical Systems                                                                               | 5 - 3        |

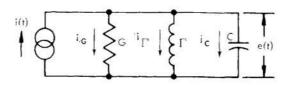

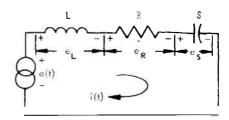

| 6-3          | Block Diagrams of Ohm's Law and Newton's Second Law                                                                       | 6 - 5        |

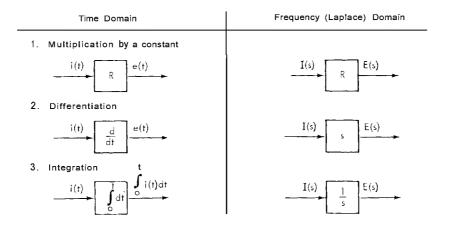

| 6-4          | Block-diagram Operations                                                                                                  | 6-6          |

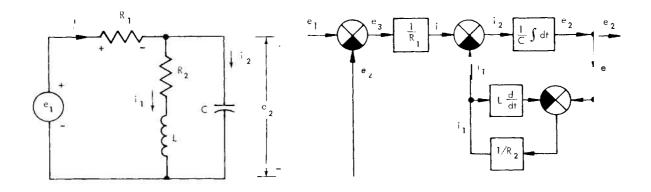

| 6-5          | Symbol for a Summing Point                                                                                                | 6-6          |

| 6-6          | Series-parallel Circuit and its Block Diagram                                                                             | 6-6          |

| 6-7          | Block Diagram of the System of Fig. 6-6 Given in the Laplace Domain                                                       | 6-7          |

| 6-8          | Equivalent Configurations Based upon Superposition                                                                        | 6-8          |

| <b>6-</b> 9  | Combination of Cascaded Elements                                                                                          | 6-8          |

| 6-10         | Movement of an Element Forward Past a Summation Point                                                                     | 6-8          |

| 6-11         | Movement of an Element Backward Past a Summation Point                                                                    | 6-8          |

| 6-12         | Movement of an Element Forward Past a Pickoff Point                                                                       | 6 - 8        |

| 6-13         | Movement of an Element Backward Past a Pickoff Point                                                                      | 6-9          |

| 6-14         | Combination of Parallel Paths                                                                                             | 6 <b>-</b> 9 |

| 6-15         | Removal of a Feedback Loop                                                                                                | 6-9          |

| 6-16         | Steps in the Reduction of the Block Diagram of Fig. 6-7                                                                   | 6-11         |

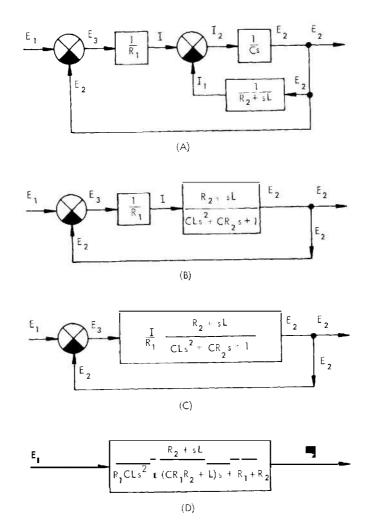

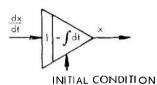

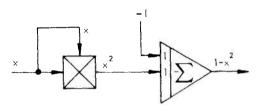

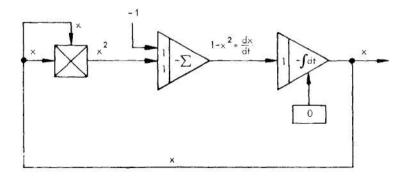

| 6- 17        | Basic Diagrams Associated with the Analog Solution of the Differential Equation $(dx/dt) + x^2 = 1$                       | 6-12         |

| 6-18         | Diagram Combining Figs. 6-17(A) and 6-17(B) to Give the Solution of the Differential Equation $(dx/dt) + x^2 = 1$         | 6-12         |

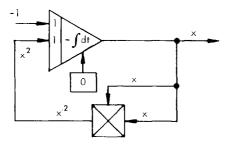

| 6-19         | Simplification of Fig. 6-18                                                                                               | 6-13         |

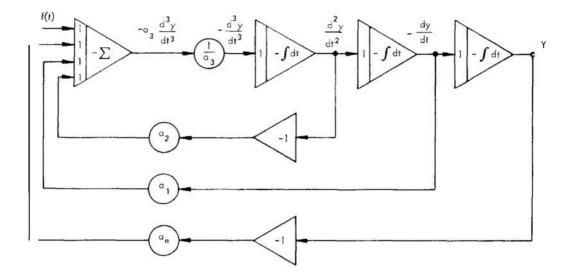

| 6-20         | Setup for the Solution of a Linear Third-order Differential Equation.                                                     | 6-14         |

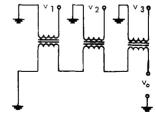

| 6-21         | Transformer Summing Circuit                                                                                               | 6-14         |

| 6-22         | Simple Resistive Summing Circuit                                                                                          | 6-15         |

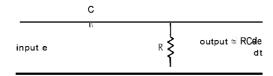

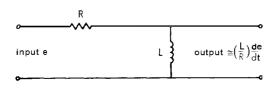

| 6-23         | Differentiating Circuits                                                                                                  | 6 _16        |

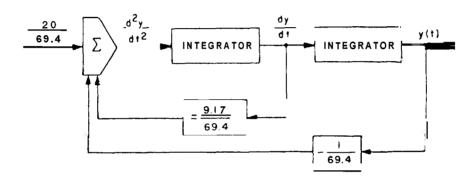

| 6-24         | Analog-computer Setup for a Simple Linear Differential Equation                                                           | 6-17         |

| 6-25         | Alternative Analog-computer Setup for a Simple Linear Differential Equation                                               | 6-17         |

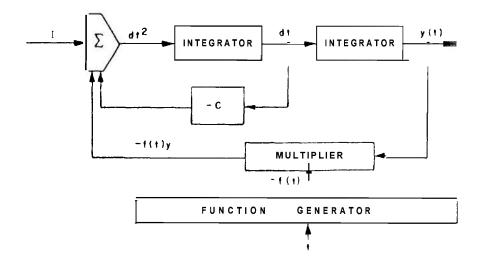

| 6-26         | Analog-computer Setup for a Simple Linear, Time-varying Differential Equation                                             | 6-18         |

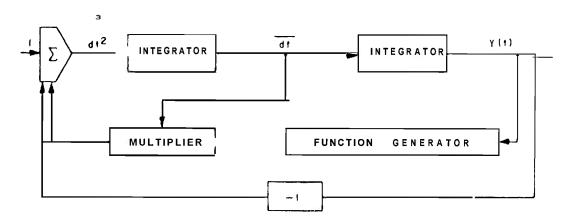

| 6-27         | Analog-computer Setup for a Simple Nonlinear Differential Equation.                                                       | 6-18         |

| 6-28         | Circuit for a Closed-loop Solution of a Pair of Simultaneous                                                              | 5-19         |

| 5 20         | Equations                                                                                                                 | 6-21         |

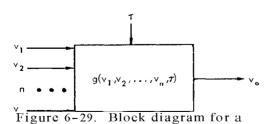

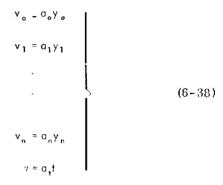

| 5-29<br>6-30 | Multiplication by a Dimensionless Constant                                                                                | 6-21         |

| 6-31         | Computer Equivalent of a Sine Function                                                                                    | 6-22         |

| 6-32         | Determination of a Component of a Force                                                                                   | 6-23         |

| 0-52         |                                                                                                                           | 0 20         |

| Fig. No.       | Title                                                                                          | Page         |

|----------------|------------------------------------------------------------------------------------------------|--------------|

| 6-33           | Operation of an Electronic Integrator                                                          | 6-23         |

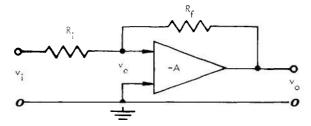

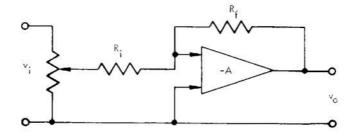

| 6-34           | Amplifier with Resistive Feedback                                                              | 6-24         |

| 6-35           | Use of a Potentiometer for Continuous Gain Adjustment                                          | 6-25         |

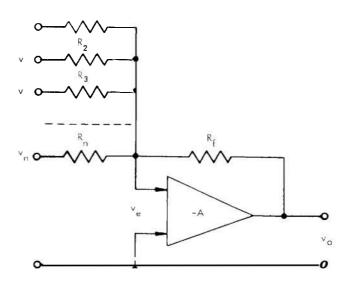

| 6-36           | Representative Circuit for the Summation of n Voltages                                         | 6-25         |

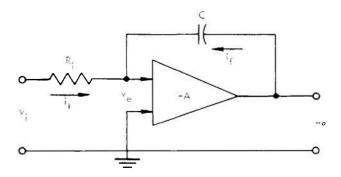

| 6-37           | Basic Circuit for Integration                                                                  | 6-27         |

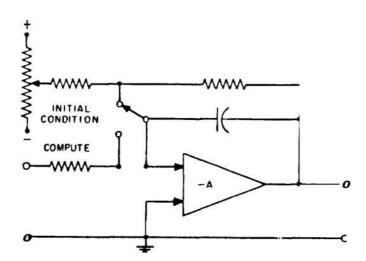

| 6-38           | Electronic Integrator with Initial-condition Circuit                                           | 6-27         |

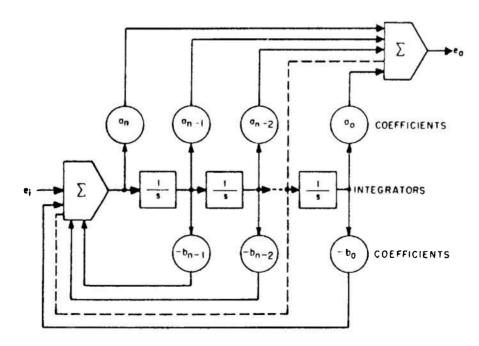

| 6-39           | Integrator Realization                                                                         | 6-28         |

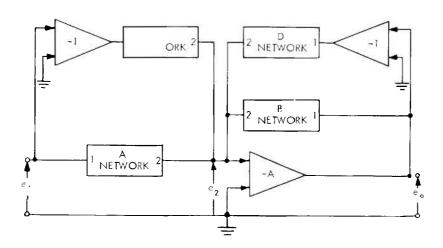

| 6-40           | Block Diagram for One-amplifier Realization with Two-terminal Networks                         | 6-29         |

| 6-41           | Resulting Form of Synthesis Network                                                            | 6-29         |

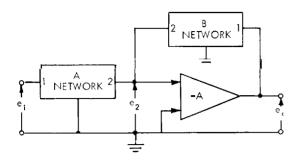

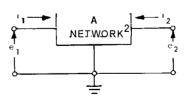

| 6-42           | Block Diagram for One-amplifier Realization with Three-terminal Networks                       | 6-30         |

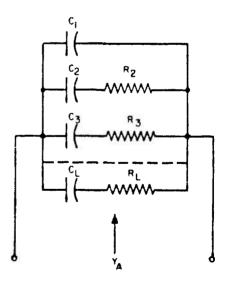

| 6-43           | Definition of Admittances                                                                      | 6-30         |

| 6-44           | Block Diagram for Three-amplifier Realization                                                  | 6-31         |

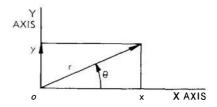

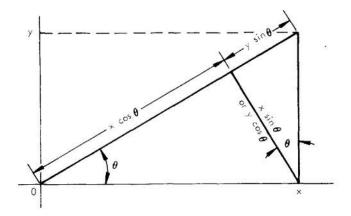

| 6-45           | Representation of a Vector in a Rectangular Coordinate System and in a Polar Coordinate System | 6-34         |

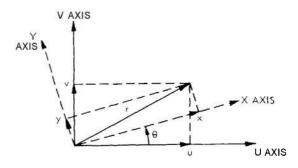

| 6-46           | Rotation of a Rectangular Coordinate System                                                    | 6-34         |

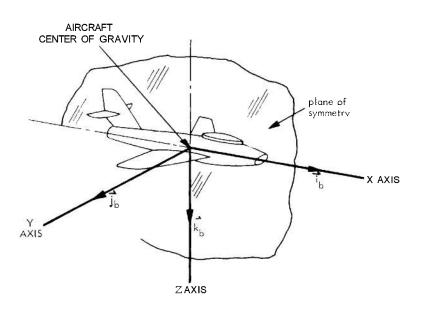

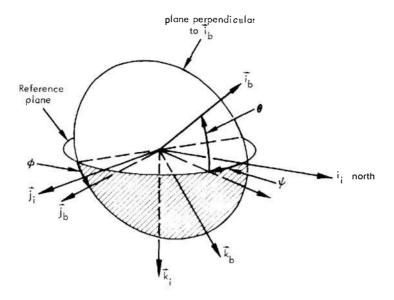

| 6-47           | Example of a Body-axis System                                                                  | 6-35         |

| 6-48           | Orientation of a Body-axis System with Respect                                                 |              |

|                | to an Inertial System                                                                          | 6-36         |

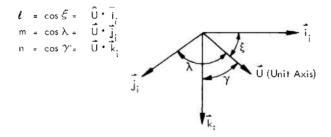

| 6-49           | Direction Cosines Defining the Orientation                                                     |              |

| 6-50           | of an Axis in Inertial Space                                                                   | 6-36<br>6-37 |

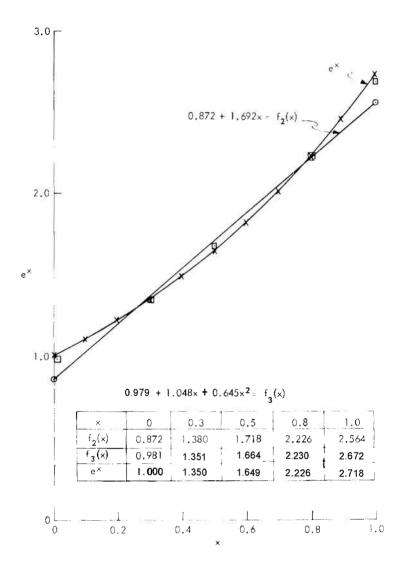

| 6-51           | Plots of $e^x$ and its Approximations, where e is the Error in the Function $y = f(x)$         | 6-42         |

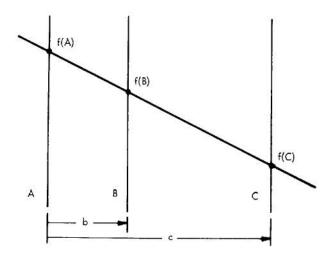

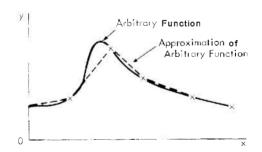

| 6-52           | Straight-line Approximation of an Arbitrary Function                                           | 6-42         |

| 6-53           | A Typical Operational Amplifier                                                                | 6-45         |

| 6-54           | Basic Waveform of a Time-division Multiplier                                                   | 6-47         |

| 6-55           | Diode Networks Used for Generating Three Simple Nonlinear Functions                            | 6-48         |

| 6-56           | Approximation of an Arbitrary Function                                                         | 6-50         |

| 6- 57          | by Means of a Diode Function Generator                                                         | 6-50         |

| 0 0.           | Simple Bivariable Function                                                                     | 6-51         |

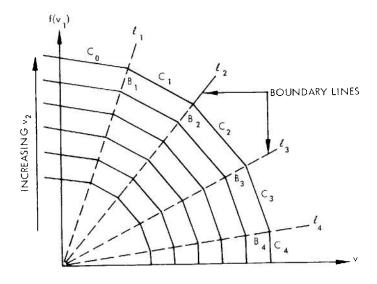

| 6- 58<br>6- 59 | Basic Form of the Photoformer Function Generator                                               | 6-53         |

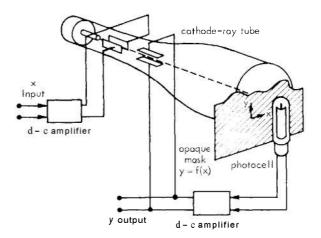

| 6-60           | Block Diagram of a Random-signal Generator                                                     | 6-54         |

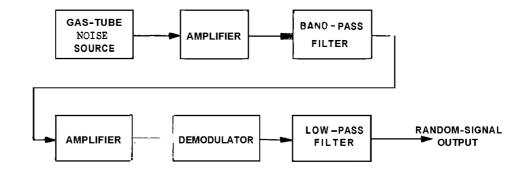

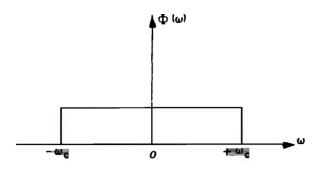

| 6-61           | Rectangular Power Spectrum                                                                     | 6-55         |

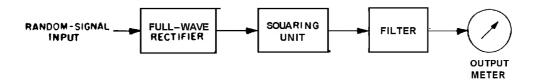

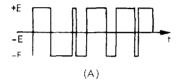

| 6-62           | Non Gaussian Bandom Signals                                                                    | 6-55         |

| 6-63           | Ncn-Gaussian Random Signals                                                                    | 6-56         |

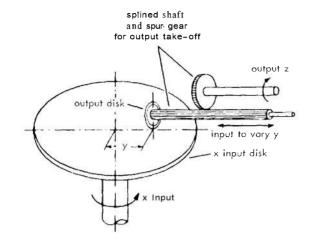

| 6-64           | Geometry of the Disk-disk Integrator                                                           | 6-57         |

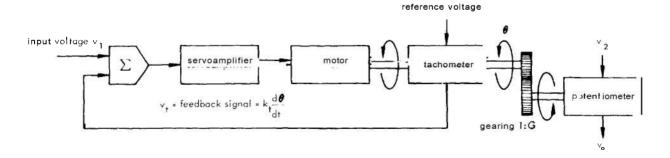

| 6-65           | Block Diagram of a Rate-servo Integrator                                                       | 6-57         |

| 6-66           | Schematic Representation of Multiplication by                                                  | 0-37         |

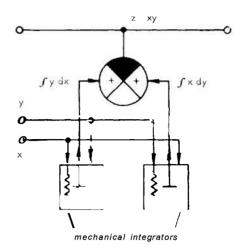

| 0-00           | Means of a Pair of Integrators Plus a Differential                                             | 6-58         |

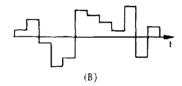

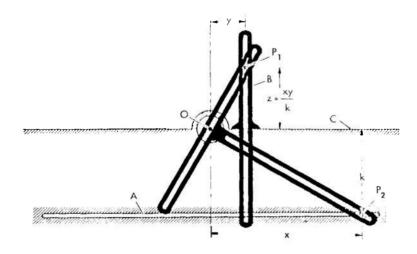

| 6-67           | Linkage multiplier                                                                             | 6-58         |

| 6-68           | Schematic Representation of a Quarter-squares Multiplier                                       | 6-59         |

| 6-69           | Schematic Representation of a Servomultiplier                                                  | 6-59         |

| 6-70           | Block Diagram of a Divider Employing a Servo-driven Multiplier                                 | 6-60         |

| 6-71           | Block Diagram of a Position Servo Used for Division                                            | 6-61         |

| 6-72           | Block Diagram of a Gain-compensated Divider Servo                                              | 6-61         |

| Fig. No.      | Title                                                                                                              |       |  |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|--|--|--|

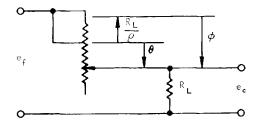

| 6-73          | Division Circuit Eased on a Single. Tapped. Linear Potentiometer                                                   | 6-61  |  |  |  |  |  |  |  |  |  |

| 6-74          | Mechanical Coordinate Converter                                                                                    | 6-62  |  |  |  |  |  |  |  |  |  |

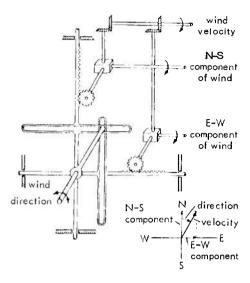

| 6-75          | Simplified Diagram of a Rectangular-to-polar Converter                                                             | 6-62  |  |  |  |  |  |  |  |  |  |

| 6-76          | Geometry of the Coordinate-conversion System                                                                       | 6-63  |  |  |  |  |  |  |  |  |  |

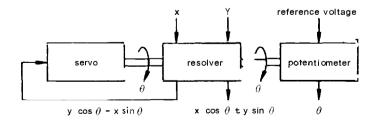

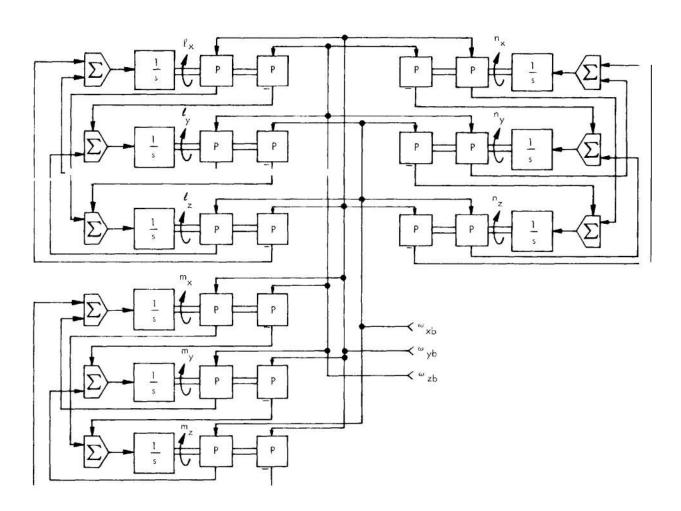

| 6-77          | Block Diagram of a System for Generating Direction Cosines                                                         | 6-64  |  |  |  |  |  |  |  |  |  |

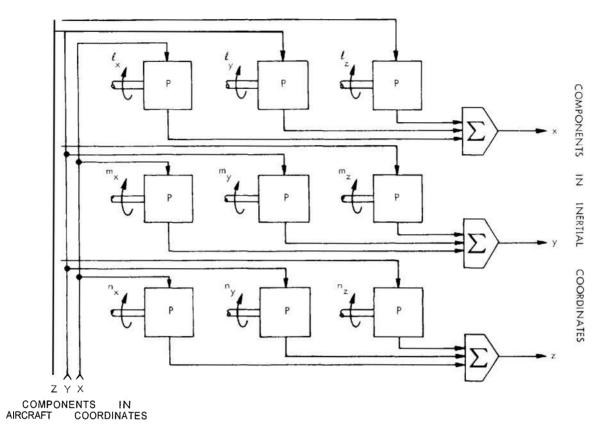

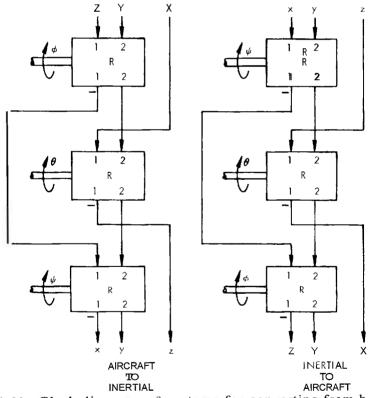

| 6-78          | Block Diagram of a System for Converting from Aircraft Coordinates to Inertial Coordinates                         | 6-65  |  |  |  |  |  |  |  |  |  |

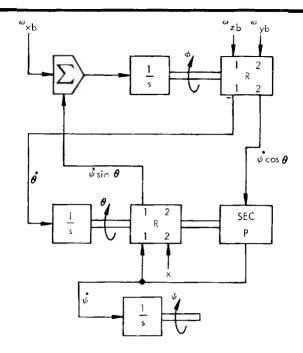

| 6- <b>7</b> 9 | Block Diagram of a System for the Direct Solution of Euler Angles                                                  | 6-66  |  |  |  |  |  |  |  |  |  |

| 6-80          | Block Diagrams of Systems for Converting from Body-axis<br>Coordinates to Inertial-axis Coordinates and Vice Versa |       |  |  |  |  |  |  |  |  |  |

| 0.01          | by the Use of Resolvers                                                                                            | 6-66  |  |  |  |  |  |  |  |  |  |

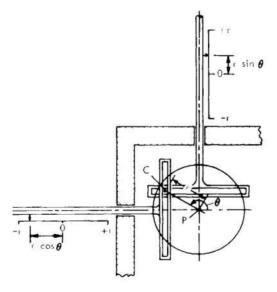

| 6-81          | Double Scotch Yoke Mechanism                                                                                       | 6-67  |  |  |  |  |  |  |  |  |  |

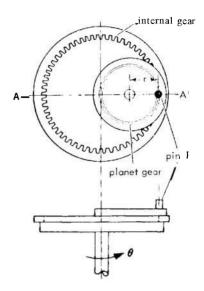

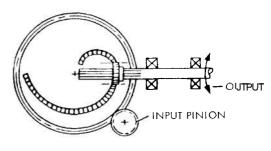

| 6-82          | Gear-type Sine-cosine Generator                                                                                    | 6-67  |  |  |  |  |  |  |  |  |  |

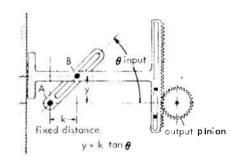

| 6-83          | Modification of the Scotch Yoke for Generating a Tangent Function                                                  | 6-67  |  |  |  |  |  |  |  |  |  |

| 6-84          | Shaped-card Sine-cosine Potentiometer                                                                              | 6-68  |  |  |  |  |  |  |  |  |  |

| 6-85          | Circuit for the Generation of the Tangent Function                                                                 | 6-68  |  |  |  |  |  |  |  |  |  |

| 6-86          | Circuit for Approximating the Secant Function                                                                      | 6-69  |  |  |  |  |  |  |  |  |  |

| 6-87          | Schematic Diagram of an Induction Resolver                                                                         | 6-69  |  |  |  |  |  |  |  |  |  |

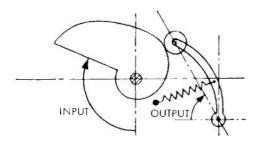

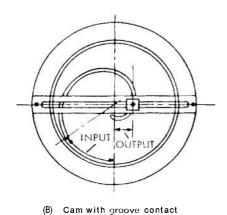

| 6-88          | Typical Cams                                                                                                       | 6-70  |  |  |  |  |  |  |  |  |  |

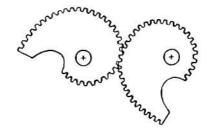

| 6-89          | Typical Function Gears                                                                                             | 6-70  |  |  |  |  |  |  |  |  |  |

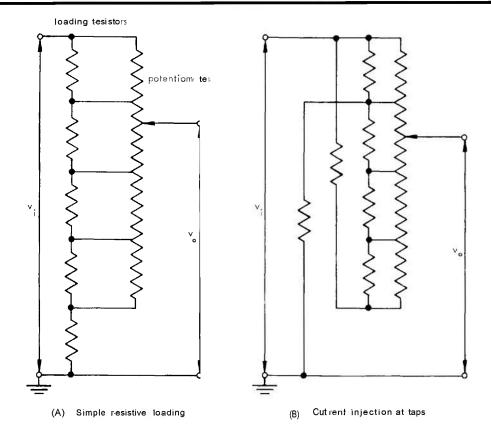

| 6-90          | Function Generation with a Tapped Potentiometer                                                                    | 6-72  |  |  |  |  |  |  |  |  |  |

| 6-91          | Rectifier Section of a Typical Power Supply                                                                        | 6-75  |  |  |  |  |  |  |  |  |  |

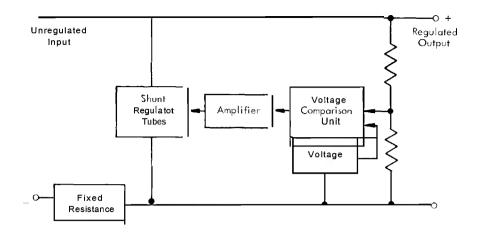

| 6-92          | Block Diagram Showing the Basic Form of the Scries Regulators                                                      |       |  |  |  |  |  |  |  |  |  |

|               | Employed in Most Electronic Voltage-regulator Units                                                                | 6-75  |  |  |  |  |  |  |  |  |  |

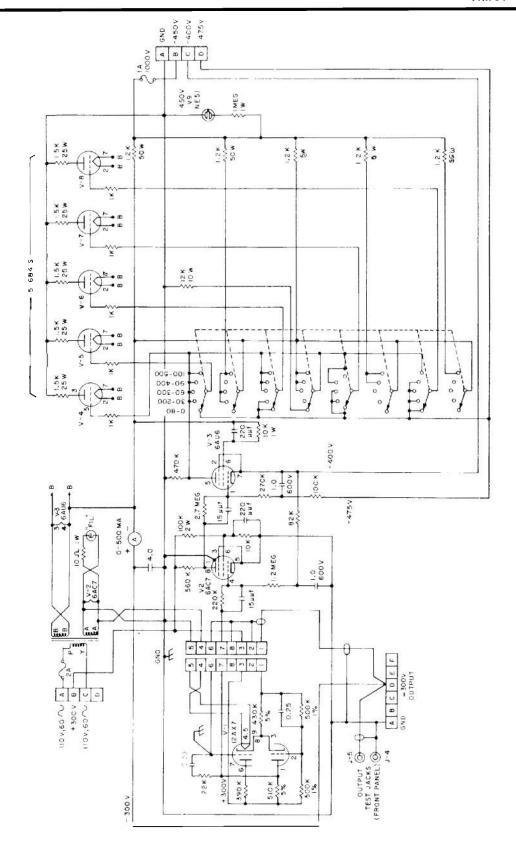

| 6-93          | Schematic Diagram of a Typical +300-v, 800-ma Voltage Regulator                                                    | 6-76  |  |  |  |  |  |  |  |  |  |

| 6-94          | Block Diagram of the Basic Shunt Regulator                                                                         | 6-78  |  |  |  |  |  |  |  |  |  |

| 6-95          | Schematic Diagram of a Typical Shunt Regulator  Designed for Negative Operation                                    | 6-79  |  |  |  |  |  |  |  |  |  |

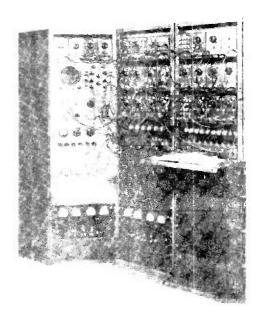

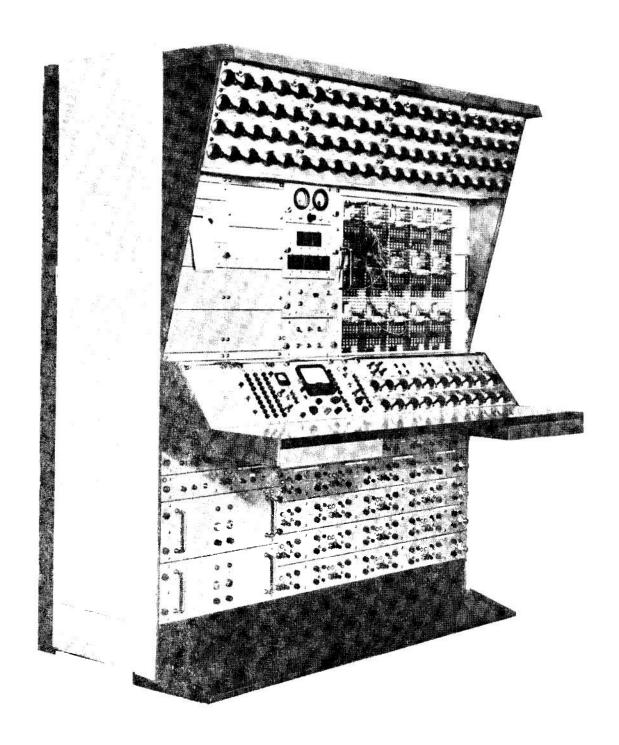

| 6-96          | Typical Analog-computer Installation in which Patching is Accomplished by the Use of Cabling Between Components    | 6-81  |  |  |  |  |  |  |  |  |  |

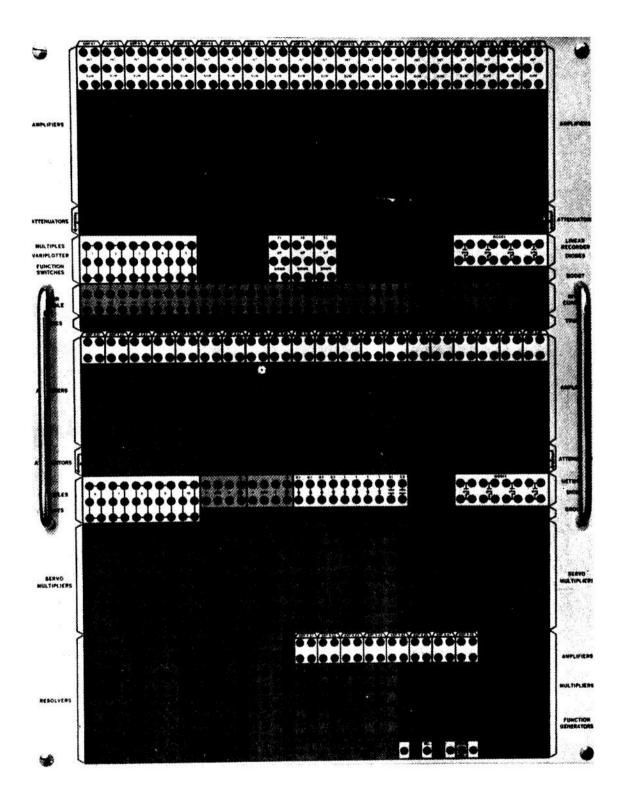

| 6~ 9 <b>7</b> | A Removable Metal Patch Board                                                                                      | 6-83  |  |  |  |  |  |  |  |  |  |

| 6-98          | A General-purpose Analog Computer with its Metal Patch Board in Place                                              | 6-84  |  |  |  |  |  |  |  |  |  |

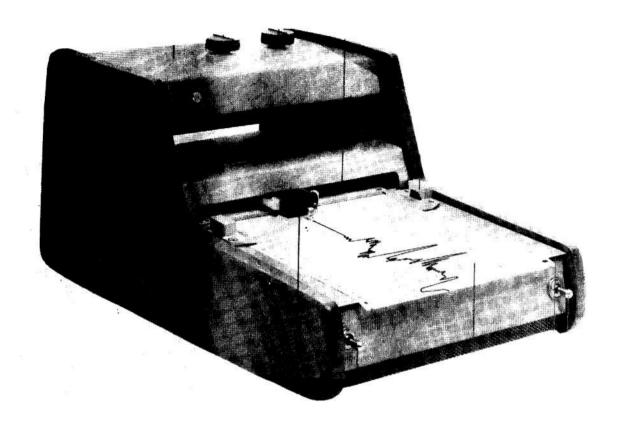

| 6-99          | A Typical Strip Recorder                                                                                           | 6-86  |  |  |  |  |  |  |  |  |  |

| 6-100         | Graph Made from a Typical Strip Recorder                                                                           | 6-86  |  |  |  |  |  |  |  |  |  |

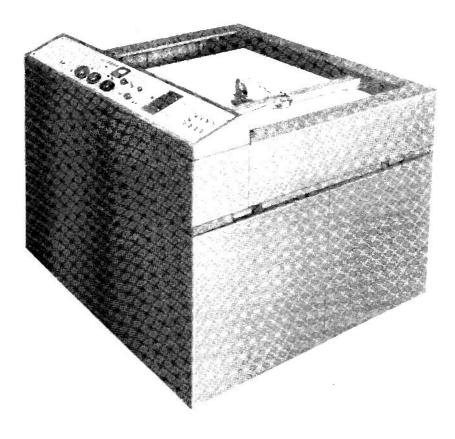

| 6-101         | A Typical Plotting Table                                                                                           | 6-58  |  |  |  |  |  |  |  |  |  |

| 6-102         | A Typical Table-top Plotting Table                                                                                 | 6-89  |  |  |  |  |  |  |  |  |  |

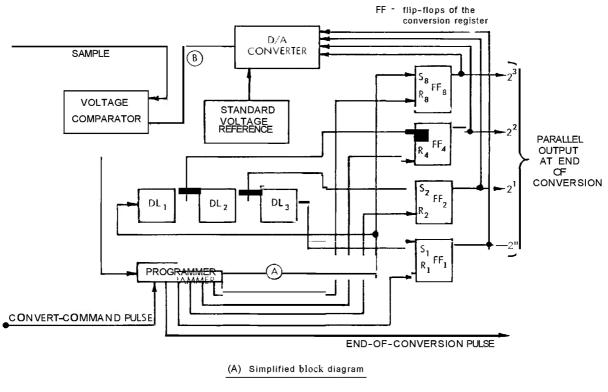

| 7- 1          | Simplified Block Diagram and Associated Wave Forms for a                                                           |       |  |  |  |  |  |  |  |  |  |

|               | Level-at-a-time Type of Voltage-to-digital Encoder                                                                 | 7-2   |  |  |  |  |  |  |  |  |  |

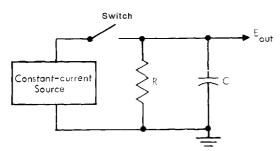

| 7-2           | Schematic Diagram of a Ramp-voltage Generator                                                                      | 7 – 5 |  |  |  |  |  |  |  |  |  |

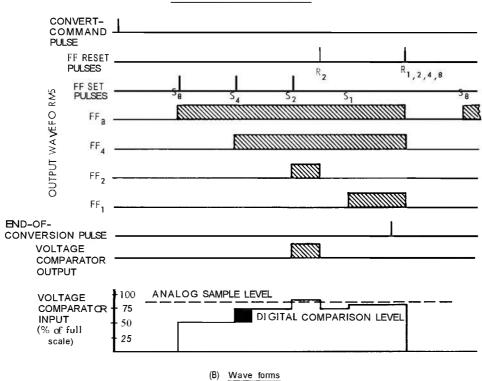

| 7-3           | Simplified Block Diagram and Associated Wave Forms for a Digit-at-a-time Type of Voltage-to-digital Encoder        | 7-6   |  |  |  |  |  |  |  |  |  |

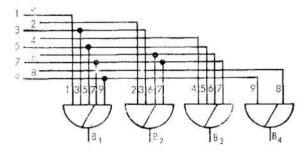

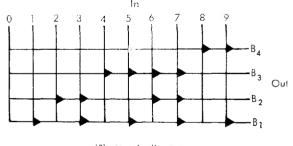

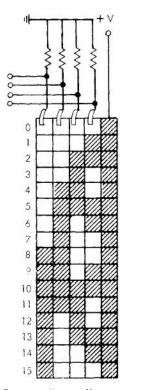

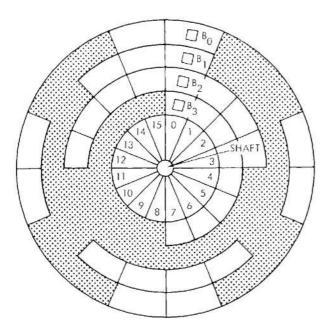

| 7-4           | The Logic Diagram and Matrix Diagram for a Natural Binary Coded Decimal Encoder                                    | 7-8   |  |  |  |  |  |  |  |  |  |

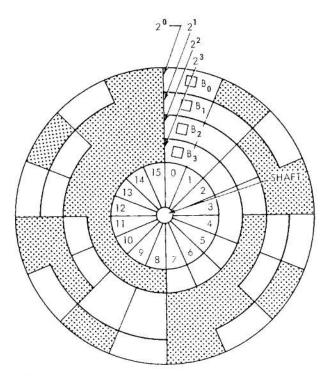

| 7-5           | A Typical Binary Coding Disc                                                                                       | 7-9   |  |  |  |  |  |  |  |  |  |

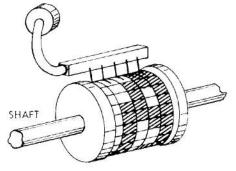

| 7-6           | Direct-drive Angular-shaft-position Analog-to-digital Converter                                                    | 7-9   |  |  |  |  |  |  |  |  |  |

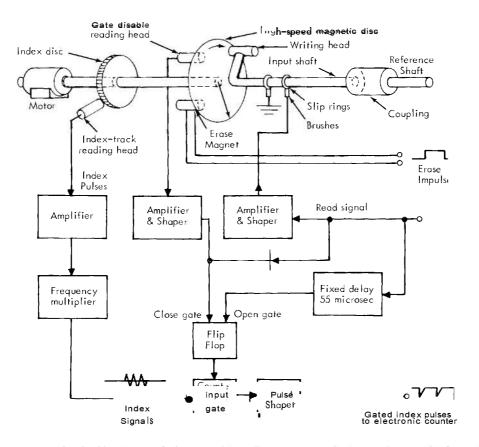

| 7-7           | Block Diagram of the Engineering Research Associates Shaft Monitor.                                                | 7-10  |  |  |  |  |  |  |  |  |  |

| Fig. No.           | Title                                                                                                  | Page         |

|--------------------|--------------------------------------------------------------------------------------------------------|--------------|

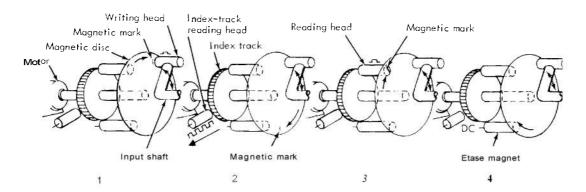

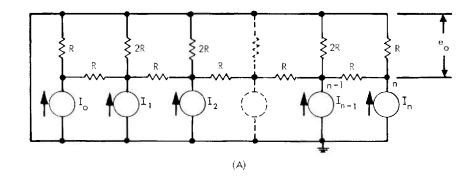

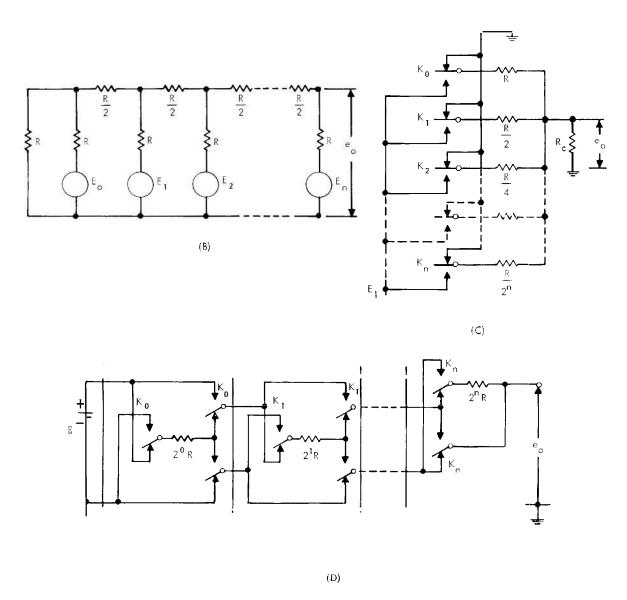

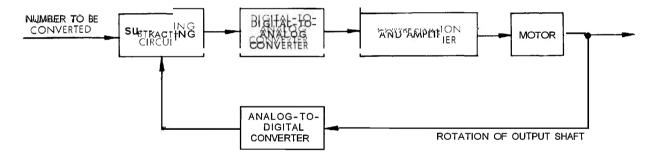

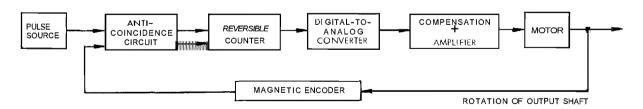

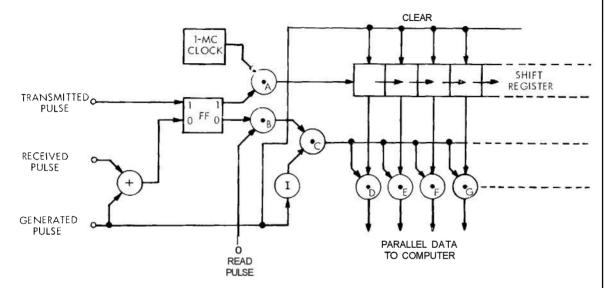

| 7-8                | Operation Sequence of the Engineering Research Associates Shaft Monitor                                | 7-10         |

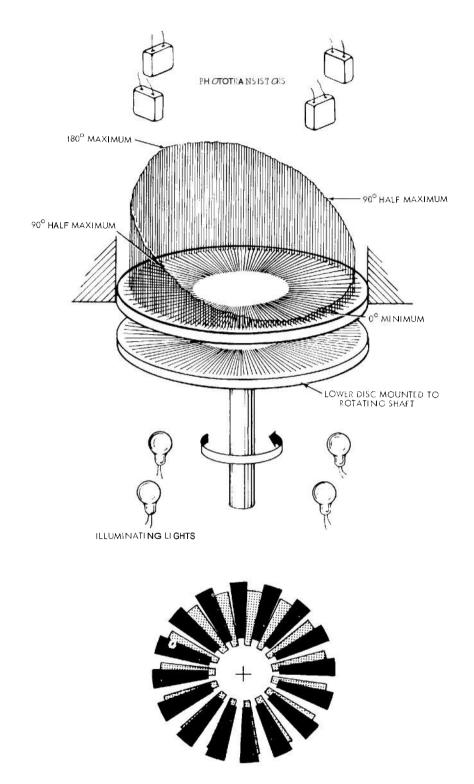

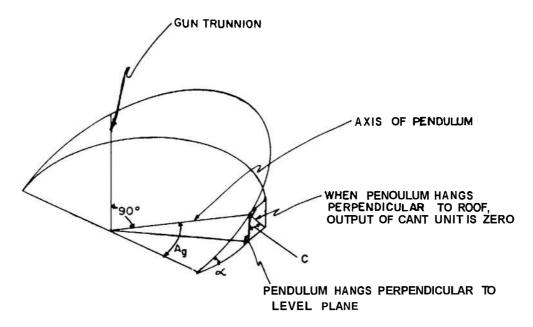

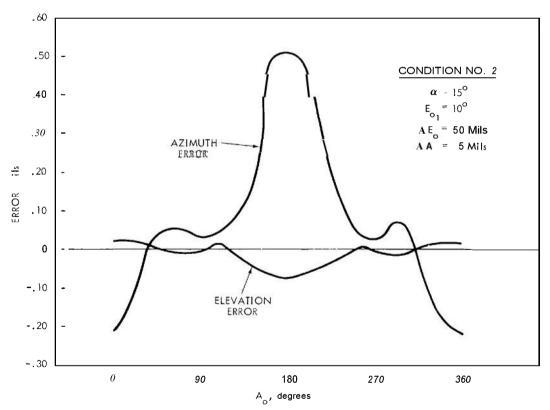

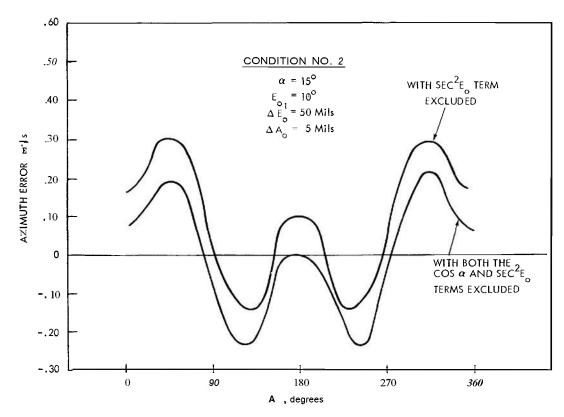

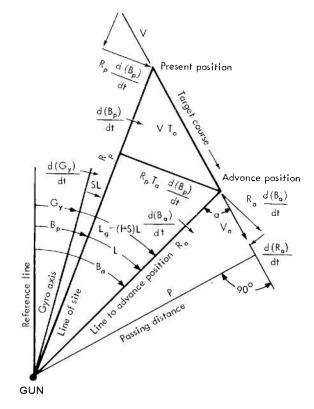

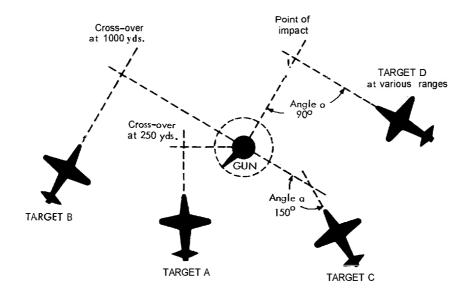

| 7-9                | Arrangement of Sectored Discs and Photodetectors for                                                   | , 10         |