AD-751 316

# 1972 Government Microcircuit Applications Conference ( GOMAC)

- Digest of Technical Papers

Air Force Avionics Laboratory

OCTOBER 1972

Distributed By:

National Technical Information Service

U. S. DEPARTMENT OF COMMERCE

5285 Port Royal Road, Springfield Va. 22151

೬೬

1972

# GOVERNMENT MICROCIRCUIT APPLICATIONS CONFERENCE DIGEST of PAPERS

Note that the second of the se

Approved for public release; distribution unlimited.

444

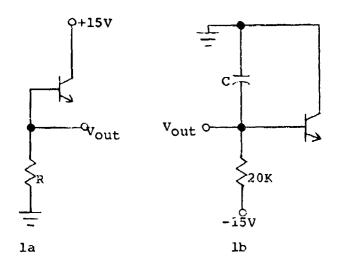

Ia

|                                     | LIN | к 🛦  | LIN    | K 8\ | LIN   | K E  |    |

|-------------------------------------|-----|------|--------|------|-------|------|----|

| KEY WORDS                           |     | ROLS | WT     | ROLE | wt    | NOLE | WY |

|                                     | •   |      |        |      |       |      |    |

| Surface Acoustics                   |     |      |        |      |       |      |    |

| Microcircuit Packaging              |     |      |        |      |       |      |    |

| Optoelectronics                     |     |      | ļ      |      |       |      |    |

| Radiation Hardening                 |     |      |        |      | {<br> |      | Į  |

| Digital Circuits and Systems        | 1   |      |        |      |       |      |    |

| Hybrid Microelectronics             |     |      |        |      |       |      |    |

| Solid State Devices                 |     |      | ļ<br>ļ |      |       |      |    |

| Microwave Integrated Circuit System | ms  |      |        |      |       |      |    |

| Linear Integrated Circuits          |     |      |        |      |       |      |    |

| Microelectronic Memories            |     |      |        |      |       |      | ļ  |

|                                     | •   | :    |        |      |       |      | }  |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      | į      |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       | 1    |    |

|                                     |     | ļ    |        |      | İ     |      | İ  |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     |     |      |        |      |       |      |    |

|                                     | Ib  |      | }      |      |       |      |    |

UNCLASSIFIED

# 1972 GOVERNMENT MICROCIRCUIT APPLICATIONS CONFERENCE DIGEST OF TECHNICAL PAPERS

C G O M A C

OCTOBER 10, 11, 12 SAN DIEGO, CALIFORNIA TABLE OF CONTENTS :

|                                                                                                                   | PAGE |

|-------------------------------------------------------------------------------------------------------------------|------|

| SURFACE ACOUSTICS 5                                                                                               |      |

| DESIGN AND PRODUCTION OF HIGHLY ACCURATE AND STABLE SURFACE WAVE BARKER CODE CORRELATORS                          | 1    |

| LOW DISPERSION VHF SURFACE WAVE ACOUSTICAL FILTER                                                                 | 9    |

| MATCHED FILTERING WITH SURFACE ACOUSTIC WAVE DEVICES                                                              | 24   |

| MICROCIRCUIT PACKAGING                                                                                            |      |

| IC PACKAGES AND HERMETICALLY SEALED-IN CONTAMINANTS                                                               | 31   |

| BLIPIM - BEAM LEADED INTERCONNECT PACKAGING                                                                       | 37   |

| A UNIVERSAL PACKAGING SYSTEM AS APPLIED TO THE ALL APPLICATIONS DIGITAL COMPUTER                                  | 51   |

| OPTOELECTRONICS                                                                                                   |      |

| TV RESOLUTION SOLID-STATE ARRAY CAMERA                                                                            | 73   |

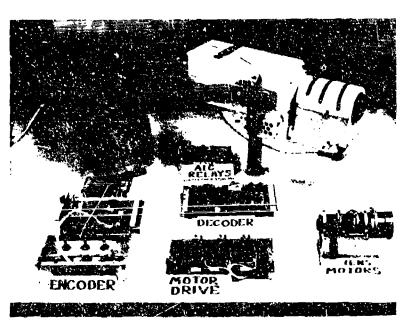

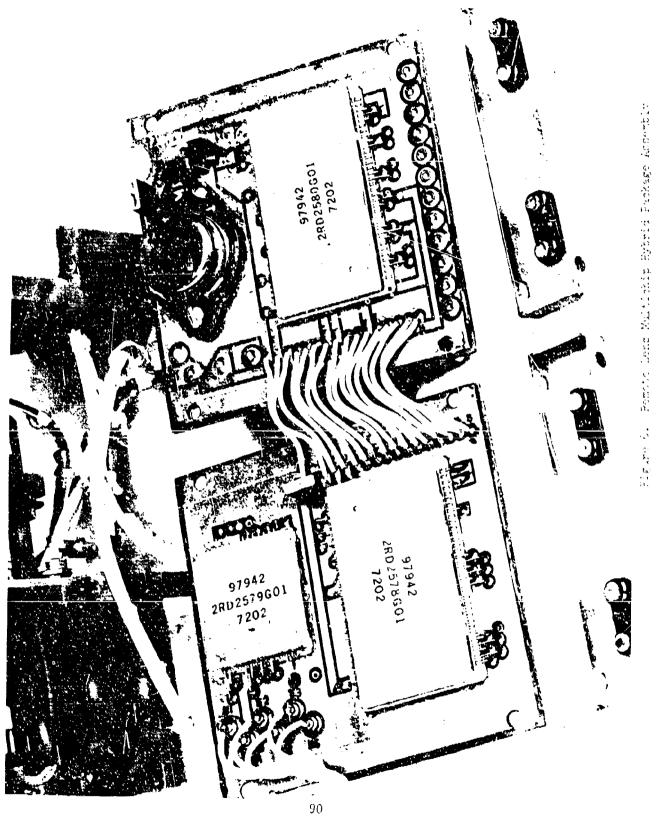

| AN APPLICATION OF MICROELECTRONICS TO THE REMOTE LENS OF THE SKYLAB COLOR TELEVISION CAMERA                       | 90   |

| SELF-SCANNED PHOTODIODE SENSOR FOR POSTAL BAR CODE READING                                                        | 92   |

| RADIATION HARDENING 1                                                                                             |      |

| EFFECTS OF HIGH ENERGY PULSES ON HYBRID CIRCUIT MATERIALS                                                         | 103  |

| NEUTRON RADIATION HARDENED GaAs JUNCTION FIELD-EFFECT TRANSISTORS OPERATING IN THE HOT ELECTRON RANGE             | 107  |

| POWER TRANSISTORS RESPONSE TO HIGH PROMPT CAMMA DOSE RATE LEVELS                                                  | 115  |

| TRANSIENT IONIZATION TESTING OF PULSED MICROWAVE TRANSCEIVER MODULES DESIGNED FOR PHASED-ARRAY RADAR APPLICATIONS | 121  |

| DIGITAL CIRCUITS AND SYSTEMS                                                                                      |      |

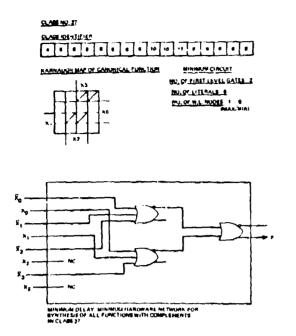

| MINIMUM DELAY/HARDWARE ECL OR/NOR 4-VARIABLE FUNCTION SYNTHESIS CATALOG                                           | 133  |

| ADVANCES IN HIGH SPEED A-TO-D CONVERSION                                                                          | 147  |

| ADAPTIVE MOC/LSI MODEMS                                                                                           | 155  |

| A GENERAL PURPOSE COMPUTER FOR SATELLITE APPLICATIONS                                                             | 166  |

| A TORPEDO SYSTEM DIRECTOR: LOGPRO#3                                                                               | 180  |

## TABLE OF CONTENTS (CONTINUED)

| ALVERIA MICROFIECTRONICE                                                                                             | PAGE           |

|----------------------------------------------------------------------------------------------------------------------|----------------|

| HYBRID MICROELECTRONICS                                                                                              |                |

| DESIGN OF POWER HYBRID MICROCIRCUITS FOR HIGH RELIABILITY APPLICATIONS                                               | 187            |

| SUBMINIATURIZATION OF TELEVISION CAMERAS THROUGH HYBRID I.C. TECHNOLOGY                                              | 191            |

| RADIATION HARDENING II,                                                                                              |                |

| RADIATION CHARACTERISTICS OF HARDENED DIGITAL IC FAMILY                                                              | 203            |

| UNIVERSAL DIGITAL INTEGRATED CIRCUIT                                                                                 | 209            |

| RADIATION TOLERANT GATED VIDEO AMPLIFIER                                                                             | 218            |

| R'DIATION RESISTANCE OF COS/MOS CIRCUITS MADE WITH Al <sub>2</sub> 0 <sub>3</sub> :S10 <sub>2</sub> GATE DIELECTRICS | 226            |

| NEW SOLID STATE DEVICES 1                                                                                            |                |

| LOW FREQUENCY NOISE CHARACTERISTICS OF GDAS JEETS FULL CRYOGENIC OPERATION                                           | 233            |

| MURGLITHIC HIGH POWER MODULATOR                                                                                      | 239            |

| MICROWAVE INTEGRATED CIRCUIT SYSTEMS                                                                                 |                |

| AN INTEGRATED S-BAND SOLID STATE FRONT END                                                                           | 247            |

| APPLICATION OF MIC TECHNOLOGY TO WIDEBAND MICROWAVE RECEIVERS                                                        | 255            |

| LINEAR INTEGRATED CIRCUITS                                                                                           |                |

| UHF HYBRID INTEGRATED 45-WATT TWO-STAGE AMPLIFIER WITH OCTAVE BANDWIDTH                                              | 259            |

| AN INTEGRATED INTERMEDIATE-FREQUENCY AMPLIFIER-LIMITER                                                               | 271            |

| A HYBRID INTEGRATED FERRITE PHASE SHIFTER DRIVER FOR PHASED ARRAY RADAR APPLICATIONS                                 | 278            |

| CROSERCULT PROCESSING AND INTEGRATED CIRCUIT TECHNIQUES: $($                                                         |                |

| PIRMOND: A NEW APPROACH TO MICROELECTRONIC CIRCUIT DESIGN (DILLECTRICALLY ISOLATED ARRAYS OF MONOLITHIC DEVICES)     | <del>289</del> |

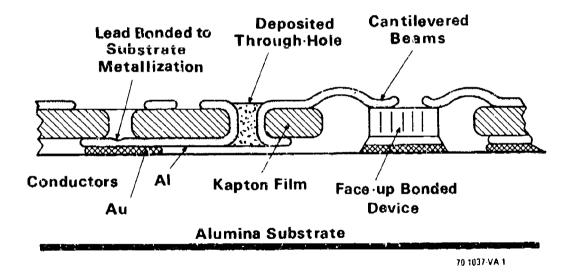

| FLEXIBLE MULTILAYER INTERCONNECTION USING EVAPORATED ALUMINUM CANTILEVERED BEAMS                                     | 297            |

| CNE-MIL GOLD WIRES IN HIGH ACCELERATION HMC APPLICATIONS                                                             | 307            |

| ENGINEERING STUDY OF DEVELOPMENT OF TWO-LEVEL ANODIZED AT INTERCONNECTS FOR MSI AND LSI                              | 327            |

TABLE OF CONTENTS (CONCLUDED)

| NEW SOLID STATE DEVICES II                                                               | PAGE        |

|------------------------------------------------------------------------------------------|-------------|

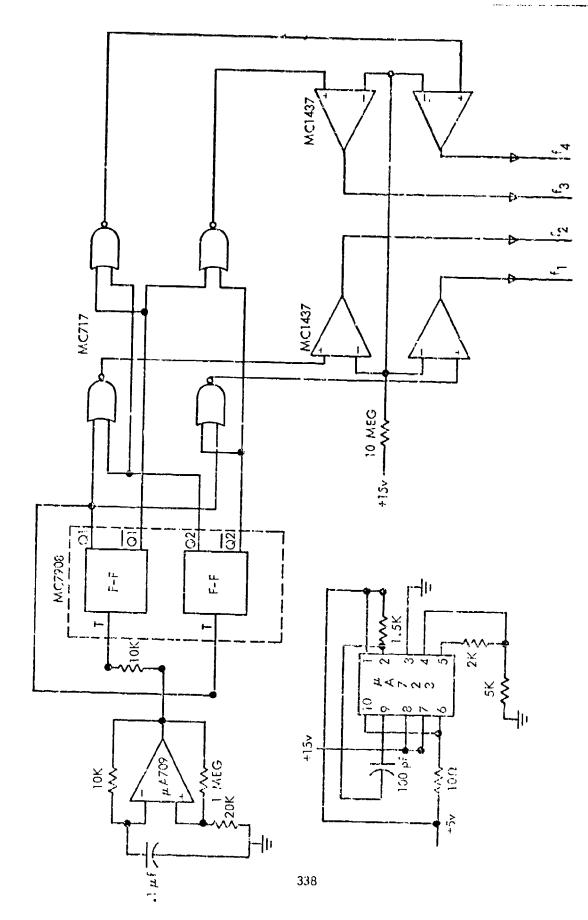

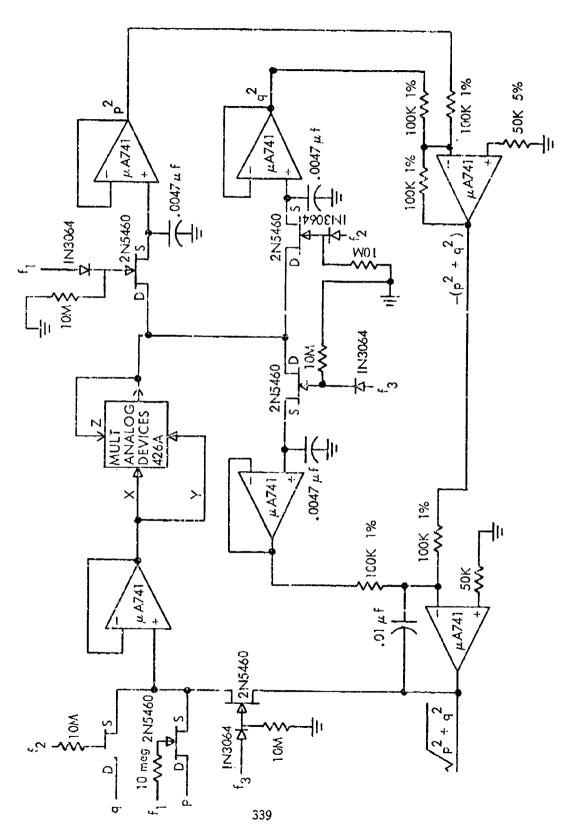

| TIME-SHARED CIRCUITS                                                                     | 333         |

| DEVICE IMPLICATIONS OF ION IMPLANTATION DAMAGE IN SILICON                                | 341         |

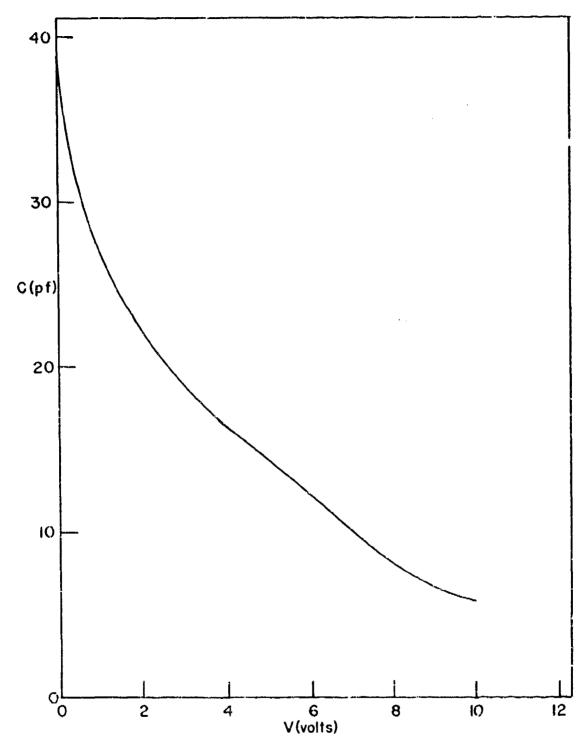

| A VARACTOR-TUNED RF AMPLIFIER INTEGRATED CIRCUIT FABRICATED USING ION-IMPLANTED DEVICES  | 346         |

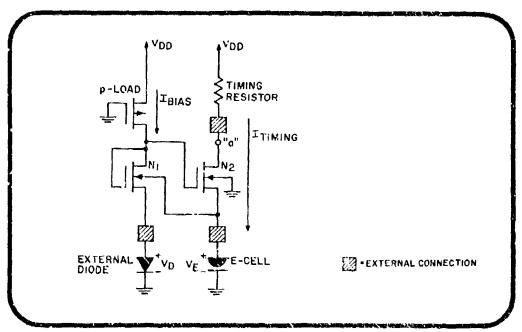

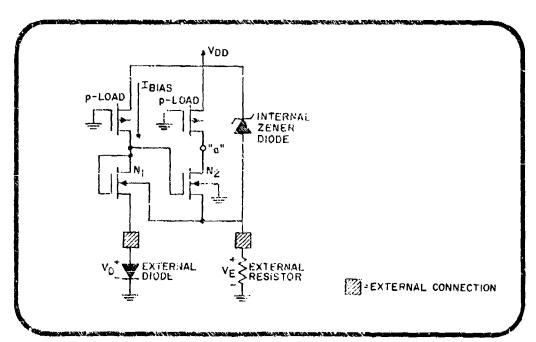

| COS/MOS FUZE TIMER COMBINES SCR AND ANALOG VORTAGE DETECTOR ON SINGLE IC                 | 353         |

| MICROWAVE INTEGRATED CIRCUITS                                                            |             |

| A COMPUTER-AIDED METHOD FOR THE DESIGN OF A WIDE CLASS OF MICROWAVE COUPLERS AND FILTERS | 361         |

| MICROWAVE INTEGRATED FILTERS                                                             | 374         |

| QUASI-LUMPED MICROSTRIP DIRECTIONAL COUPLERS                                             | <b>3</b> 82 |

| VARIABLE DISPERSION MEANDER-LINE                                                         | 393         |

| MICROELECTRONIC MEMORIES                                                                 |             |

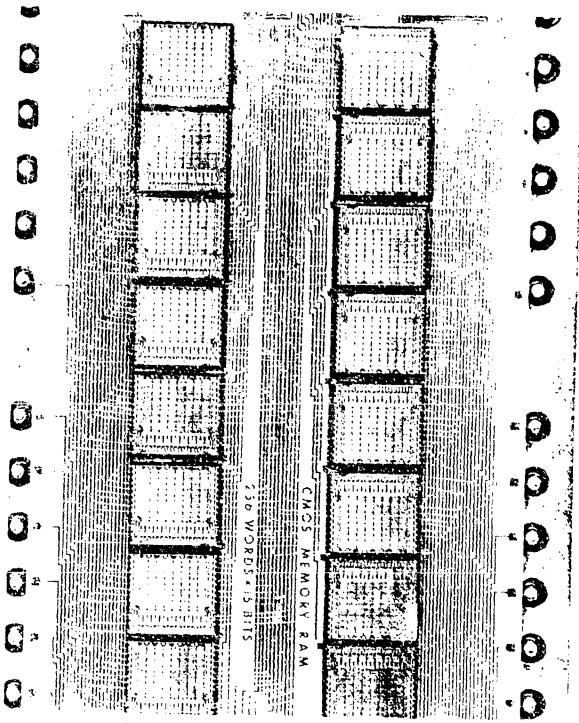

| LOW-POWER CMOS MASS MEMORY                                                               | 401         |

| A 1280-BIT MNOS RAM                                                                      | 412         |

| BUBBLE MEMORY STATUS AND TRENDS IN U.S. GOVERNMENT DATA STORAGE APPLICATIONS             | 420         |

| AN LSI MEMORY SYSTEM FOR MILITARY MAINFRAME APPLICATIONS                                 | 427         |

# DESIGN AND PRODUCTION OF HIGHLY ACCURATE AND STABLE SURFACE WAVE BARKER CODE CORRELATORS

T.M. Foster

C.R. Vale

R. L. Thomas

Westinghouse Defense and Electronic Systems Center

### ARSTRACT

A very stable and precise 30 MHz, 13-bit Barker code correlator has been developed for radar pulse compression. The correlator uses X-propagating surface waves on an ST-cut quartz substrate with Al transducers. A study was performed to determine the factors affecting repeatability of the center frequency. The frequency was set to an accuracy of 1 KHz by making a series of slightly different photoreductions of a master transducer pattern and selecting the reduction which yielded the desired frequency. In production quantities the center frequency has been repeatable to ± 5 kHz by carefully controlling the orientation of the photomask with respect to the crystal axes. Frequency deviation over the temperature range of -40°C to +90°C has been less than 2 KHz. By accurately controlling amplitude, frequency and phase, a 22 dB ratio of correlation peak to maximum sidelobe level has been achieved compared to a theoretical maximum of 22.28 dB.

### INTRODUCTION

This paper describes the development and production of 30 MHz 13 bit Barker code surface wave correlators to replace correlators (or decoders) consisting of 13 bulk wave delay lines for pulse compression in three production radar systems. The Barker code is generated in these systems by an electronic encoder which operates independently of the decoder, and hence, the frequency of the decoder must be independently adjusted to that of the encoder. For proper target detection these systems require at least a 21 dB ratio of correlation peak to maximum sidelobes, compared with a theoretical maximum of 22.3 dB for a 13 bit Barker code. In addition, the decoder is required to maintain this 21 dB ratio over a temperature range of -40°C to +90°C. In order to schieve this performance, the correlator must have transducers with very accurate and stable amplitude, frequency and phase responses.

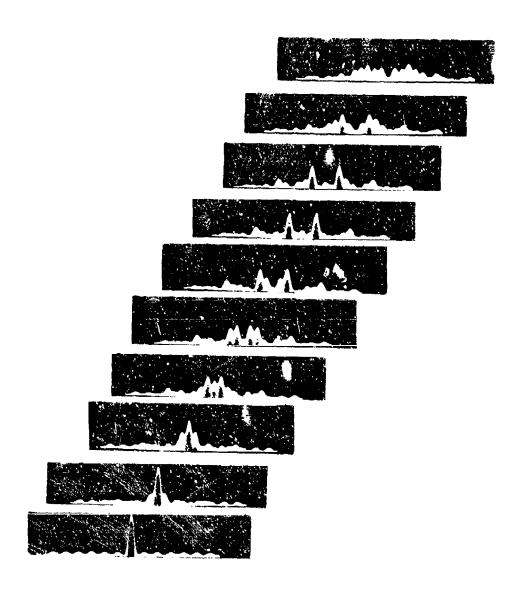

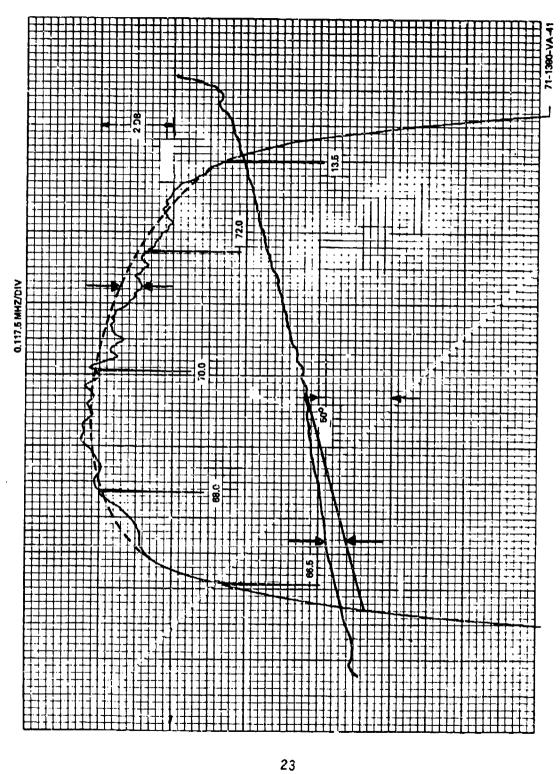

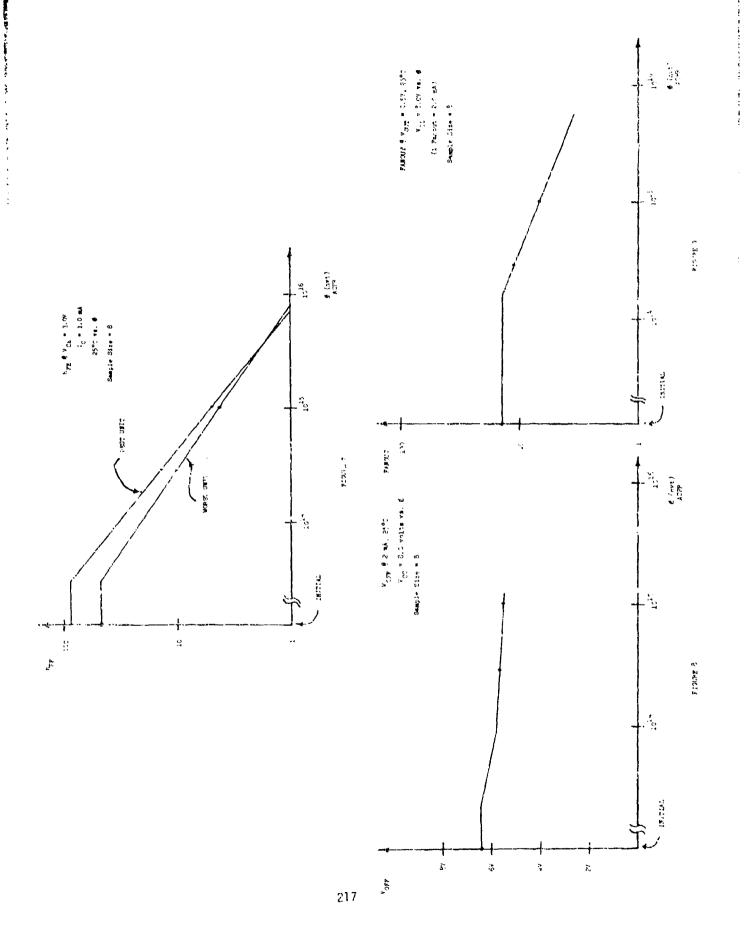

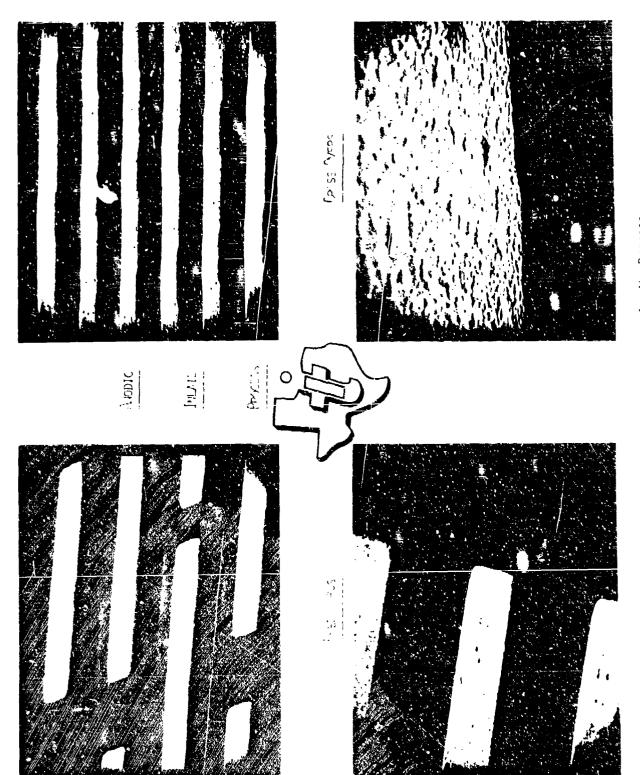

### FREQUENCY CONTROL

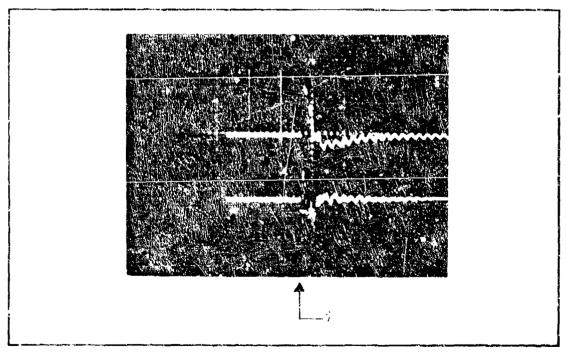

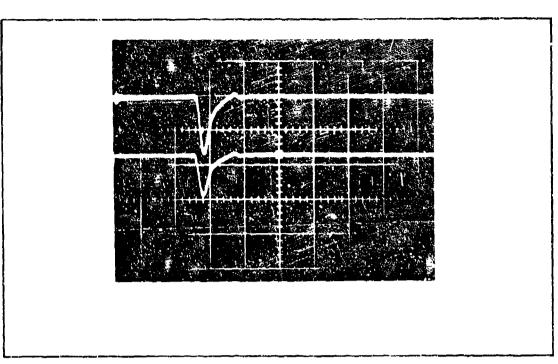

We have found in practice that in order to obtain a 21 dB ratio of correlation peak to maximum sidelobes, the center frequency of the decoder must be within approximately 8 KHz of the frequency of the encoder. This can be seen in Figure 1, which shows the response at the center frequency and at 9 KHz away from the center frequency. The correlation peak does not decrease significantly at 9 KHz off the center frequency but the valley between the peak and the first sidelobe increases until it is higher than the first sidelobe, decreasing the peak to sidelobe ratio to 21 dB. Figure 2 shows further degradation of the peak-to-sidelobe ratio as the frequency deviation increases. The response for frequency increments of approximately 16 KHz is shown starting with the center frequency at the bottom. The sidelobes increase repidly and the main lobe decreases until the peak-to-sidelobe ratio reaches unity at approximately 35 KHz off the center frequency.

In order to allow for possible frequency errors within the ladar those due to the decoder, the frequency deviasystems other than tion limit for the decoders was set at ± 5 KHz instead of the ± 8 kHz required for the system. To obtain a device with a center frequency within ± 5 KHz of the desired center frequency, the following procedure was used: The original photomask was made on a computer-controlled plotter at 20 times the estimated final size. Since the velocity of surface waves on the quartz used was not known to the desired accuracy, the exact photo reduction ratio could not be determined without making devices and measuring the center frequency. The camera was set for a reduction of 20:1 and a series of photo reductions was made near this setting by moving the camera mount in small increments to produce slightly larger and smaller reductions. corresponding to frequency increments of approximately 0.05%. were made with each mask and checked for frequency of best correlation. These dats points were used to plot a rough curve of frequency vs. camers setting. Then another series of masks was made with 0.01% frequency increments and centered at the camera setting nearest 30 Miz. One of these masks was usually the final mask for making the decoders in production.

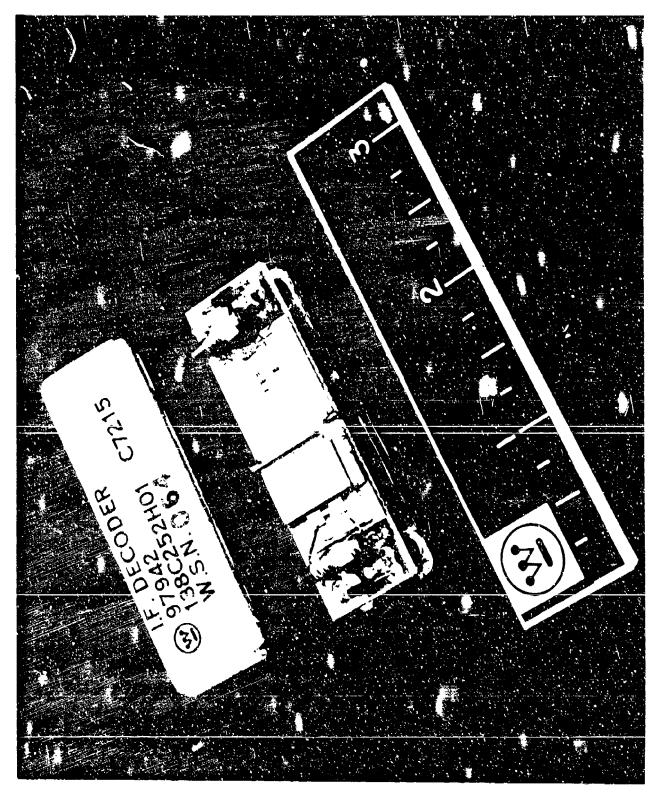

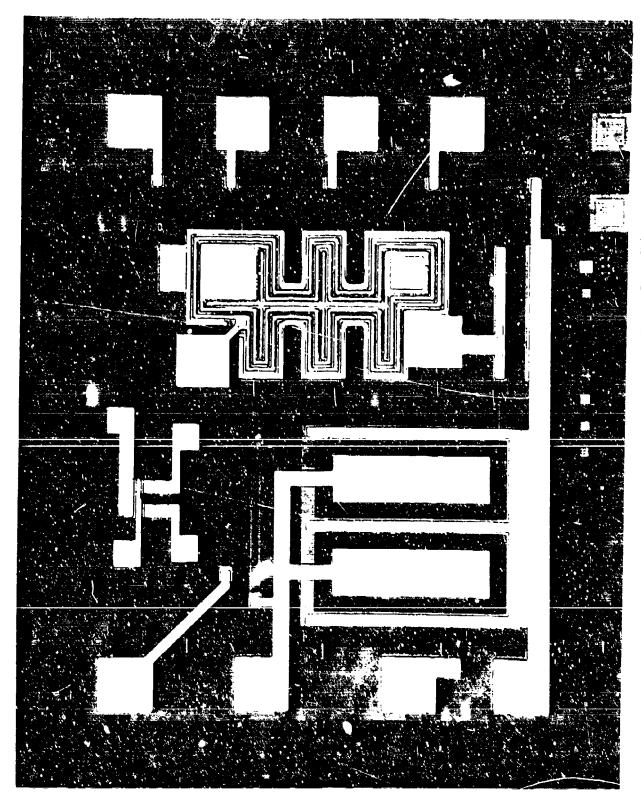

### DEVICE DESCRIPTION

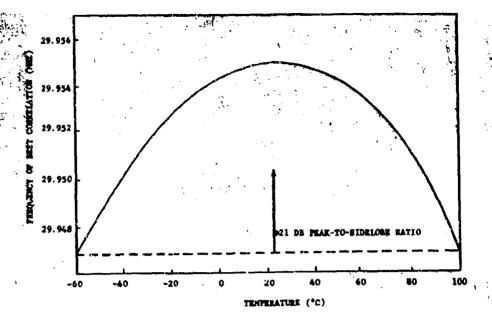

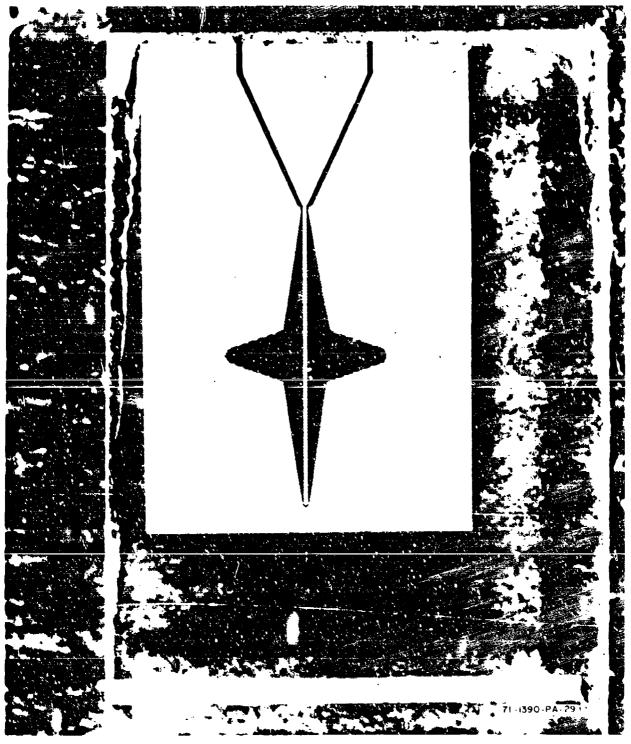

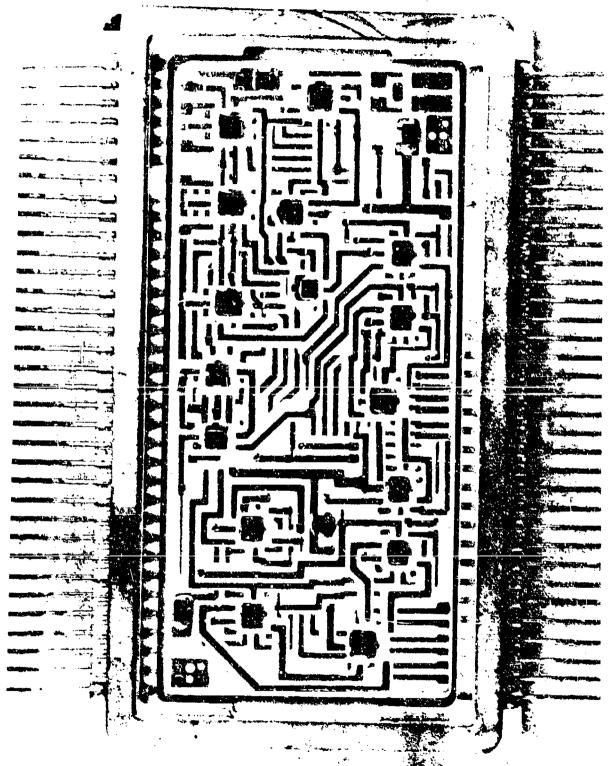

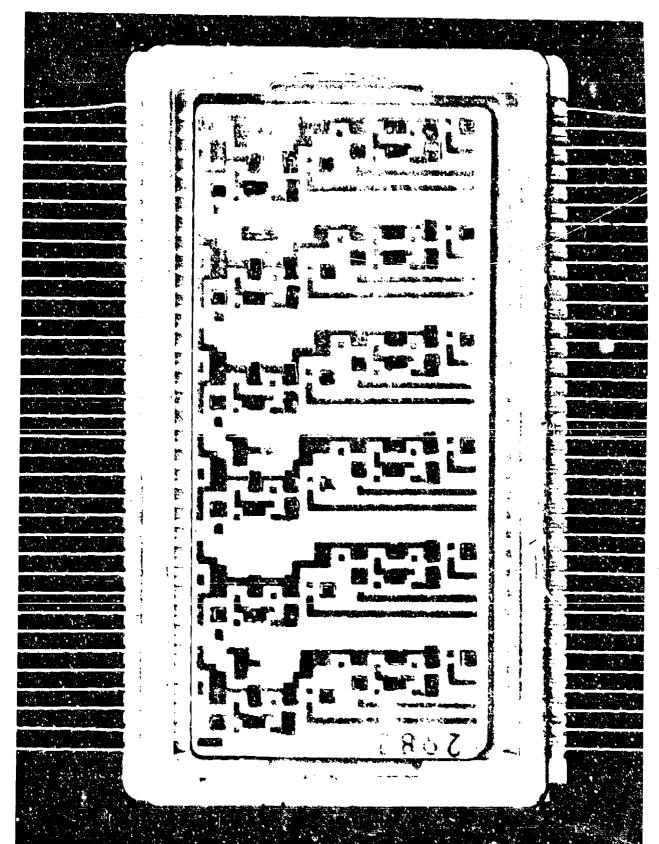

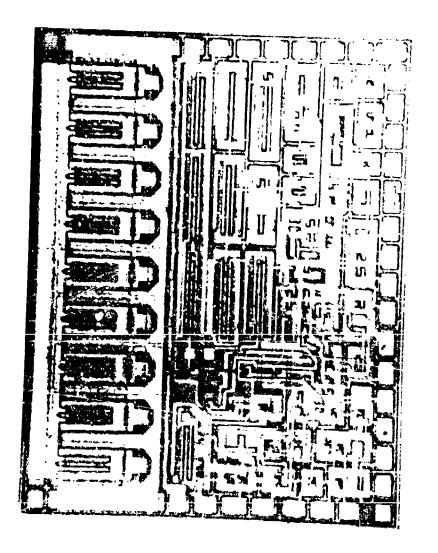

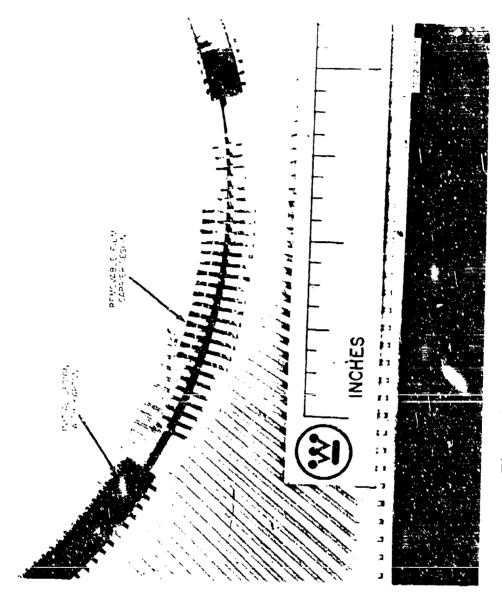

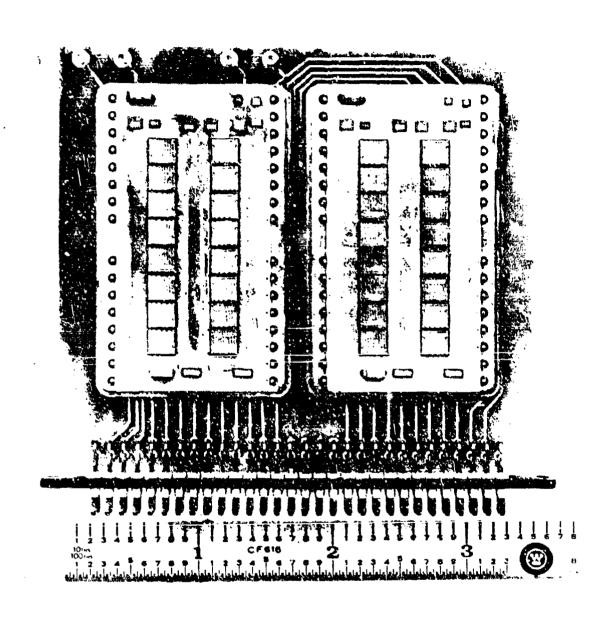

A photograph of the decoder is shown in Figure 3. The launching transducer has 7 pairs of interdigital aluminum electrodes and the receiving transducer has 13 sets of 7 pairs, each in the appropriate position to yield the phase relationship necessary for decoding the Barker coded signal as it propagates along the surface. The substrate is X-propagating ST-cut quartz. This cut was chosen because it has a surface wave velocity which is nearly constant over the temperature range of ~40°C to +90°C. Figure 4 shows that the peak-to-sidelobe ratio is greater than 21 dB over the temperature range of -60°C to +100°C, which is a wider range than the system requirement.

The quertz substrate is glued to a printed signif board to aid in assembly into a package. Gold leads are honded to the aluminum transducer pads using thermocompression bonding. The other end of the lead is bonded to the printed circuit board which is, in turn, connected to hermetically scaled pips mounted in the package. Transformers are used at the input and output to match the impedance of both transducers to 75 ohms. A metal shield is placed above the substrate to prevent electromagnetic feedthrough from the input to the output, which produces a spurious signal. A metal lid is solder-scaled to the package to prevent long term degradation of the performance due to corrosion of the aluminum or condensation of water vapor on the substrate.

### TREQUENCY ERRORS

The errors inherent in this manufacturing process were estimated in order to determine whether it would be possible to produce decoders at the correct frequency with a high yield.

There are several possible sources of frequency error, which can be classified as either errors in the surface wave velocity or errors in the size of the transducer pattern. Size errors can occur in the photoexposure process and cause the decoder pattern to be longer or shorter than the photomask unless proper care is taken. The use of collimated light greatly reduces size errors, however, and we estimate that the total frequency error due to incorrect size is less than 100 Hz.

Much larger frequency errors can result from having deviations from the correct surface wave velocity. One source of these velocity errors is misorientation of the pattern with respect to the crystal axes. Since the pattern is registered with respect to a reference edge, an error in the orientation of the pattern or the crystal axes with respect to this edge can cause velocity and frequency errors. Our calculations of frequency error above that X-axis misregistration will cause no more than 84 Hz deviation from the desired frequency.

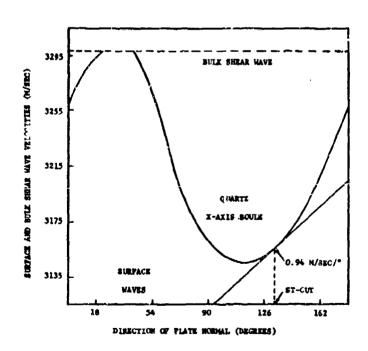

The most serious error occurs as a result of deviation of the quartz crystal's face normal from the desired direction. The surface wave velocity as a function of the direction of the plate normal is shown in Figure 5.1 ST-cut quartz corresponds to an angle of 132.75° on this graph. The slope of velocity vs. angle at this point is approximately 6.94 maters per second per angular degree. Crystal manufacturers can hold the face normal to  $\pm$  15 minutes of arc for substrates cut from different crystals and to less than 15 minutes for substrates cut from the same crystal. This angular error corresponds to a frequency error of 2.3 kHz.

Another possible source of frequency error is the variation of surface wave valocity from one quarts drystal to another due to causes other than axis misregistration, such as impurities in the quarts. Crystal manufacturers do not specify the surface wave valocity to the 2 parts in 10° precision required to assure a frequency accuracy of better than 5 KHs out of 30 MHs. However, the valocity uniformity from one batch of quarts to another has been accellent, and less than 10% of approximately 200 decoders made in production to date have been more than ± 5 KHs from the center frequency.

### CONCLUSION

In conclusion, a 30 MHz bulk wave Barker decoder has been replaced in production by a surface wave tapped line decoder which achievas a 21 dB peak-to-sidelobe ratio and a frequency accuracy of  $\pm$  5 KHz over a temperature range of -60°C to +100°C.

### FOOTNOTES

A.J. Sichodník, Jr. and E.D. Comway, <u>Microwave Acoustics Heudbook</u>, Volume 1, AFCRL-70-0164, Air Force Cambridge Research Laboratories, 1970, p. 59.

13 Bir Barker at f<sub>C</sub>

13 Bit Barker at f<sub>C</sub>+9KHz

71-1390-BA-74

Figure 1. Decoder Response When Peak-to-Sidelobe Level Decreases Below 21 dB

RESPONSE SURFACE

13 BIT BARKER

71-1390-BA-75

Figure 2. Decoder Response at 16 KHz Frequency Increments

Figure 3. Photograph of Production Decoder 7

Figure 4. Frequency of Best Correlation Vs. Temperature for ST-Cut Quartz

Figure 5. Surfece Name Velocity Vr. Direction of Plate Establi

## LOW DISPERSION VHF SURFACE WAVE

### ACOUSTICAL FILTER

J. Acevedo, R. A. Moore, H. Jones

Westinghouse Electric Corporation

Systems Development Division

Baltimore, Maryland 21203

### ABSTRACT

A low dispersion filter has been developed at 70 MHz using surface wave acoustics. The filter has a -0.3 dB bandwidth of 7 MHz and a skirt selectivity which provides a fall-off from -0.3 dB to -35 dB in 2 MHz. Group delay ripple is limited to  $\pm$  25 nanoseconds out of a total delay of 2 microseconds. Filter syntheses at other frequencies are easily obtained by using existing computer programs.

Great progress has been made by numerous authors in demonstrating the essential properties of filters utilizing acoustic surface waves. The type filters being discussed are those which consist of a series of interdigital fingers on the surface of a piezoelectric crystal or piezoelectric film on a nonpiezoelectric crystal. The interdigital finger-pairs are spaced on approximately half wavelength centers such that the electrical field structure is in synchronization with the acoustic wave for the center frequency hand of the transducer. The geometry of a surface wave filter is such that if the adjacent finger-pairs are of alternating polarities the field lines between the electrodes generate acoustic waves that propagate in both directions underneath either transducer. The secondary transducer thus receives half the energy.

Work has been carried out by different investigators toward providing an adequate description of the surface wave transduction process and characteristics related thereto. Much of this work has been based on the assumption that the energy coupled at each finger-pair is very small compared to the total energy which passes by the transducer. This assumption is the basis for using the impulse response model described by Tancrell and Holland in the March '71 issue of IEEE. This result is identical to that generated previously using an equivalent circuit model by Smith, et. al., in the IEEE Transactions on Microwave Theory and Techniques, 1969. In both cases it was shown that the frequency response of transducers can be represented by a Fourier transform. Much design work has been reported in the literature based on this approach to calculate properties of surface wave acoustic filters.

This approach has succeeded in explaining the major characteristics of surface wave acoustic filters. Perhaps the most desirable characteristics in acoustic surface wave filters is their reproducibility. In principle if a filter of a given bandpass and dispersion characteristic is designed it can be reproduced to an exceedingly high degree of precision at low cost. This should make the filter particularly useful for applications in which a large number of filters are needed. The present design approaches which make use of the assumption that the acoustic wave is sampled lightly at each finger-pair provides an excellent means for achieving gross filter characteristics. It cannot be used to achieve the very low dispersion characteristics which was the objective of the filters to be described. It will be shown that a very pronounced phase shift is due to the loading used to set up the metallic finger pattern. Key deficiencies of the lightly sampled approach are the ignoring of the direct loading of the metallic finger pattern and the periodic loading of the electric circuit.

There are some efforts being expended in order to achieve improved description of surface wave transducers. None have been applied to low dispersion, flat top frequency response, filters. The authors have improved on the lightly coupled sampling approach by creating a periodic loading of the piezoelectric surface. This loading leads to periodicity which causes an attenuation in a portion of the filter bandpass. The presence of the metallic loading leads to a 15-25 nsec time delay discontinuity at the center frequency of the filter. This corresponds to a five degree change in slope of the phase characteristic at the same point.

With very lightly coupled materials, such as quartz, reasonably good results can be obtained using only the impulse model. Properties of quartz can be made relatively insensitive to temperature for appropriate propagation directions. Thus quartz is the clear choice where precise work is desired. This same consideration was involved in the Barker Code Demodulator described in a paper by Thomas, et. al., at the Ultrasonic Symposium in December 1971. The design of that filter required a compensation for a 4 63 attenuation along the length of the filter. Many detailed characteristics of the substrate as well as the synthesis technique must be considered to achieve a good reproduction of the decoded Barker signal.

Since the frequency characteristics can be represented as the Fourier transform of the active finger-pair lengths, synthesis is then based on the following procedure:

- (1) Computation of active finger lengths to provide desired frequency bandpass by using an impulse response. For the square frequency response filter this would be a sin x except for the finite length of the transducer. A good approximation is achieved by suitably tapering the sin x time side lobe amplitudes.

- (2) Computation of frequency response of two cascaded transducers representing the input and output of the filter. We have used constant finger overlap lengths for the second transducer. (By virtue of reciprocity it is immaterial whether the frequency selective or constant finger length overlap transducer is used as the input or output unless specific matching conditions dictate one arrangement or the other. We shall refer to the frequency selective transducer as the primary and the constant-finger-overlap transducer as the secondary element.)

- (3) Optimization of response of two transducers. By virtue of the linearity of the Fourier transform, the active region of the filter is divided into N (N = 100 for our program) "channels" as shown in Figure 1.

Each transducer finger intersecting a particular channel must, because of the interger finger length constraint, launch or receive acoustic waves uniformly over the width of that channel. Due to the assumed linearity of the acoustic medium, the transmission through a single channel is equal to the sum of the transmission between each launching finger edge and each receiving finger edge. Furthermore, because of the assumed nonattenuation of the propagating wave and the assumed equipotential of all conductively connected points, the channel transmission (except for delay) between any launching-receiving pair of finger edges is the same as between any other pair.

The program developed takes each of the 100 channels of the active region in turn, computes the transmission through that particular channel and adds this contribution to a running sum of all channel transmissions.

This arrangement provides for computation of the frequency response of the two transducers as a unit. Optimization was then carried cut by letting each finger in sequence occupy a greater or lesser number of channels. The optimization routine stops when no improvement can be obtained by varying the length of any finger.

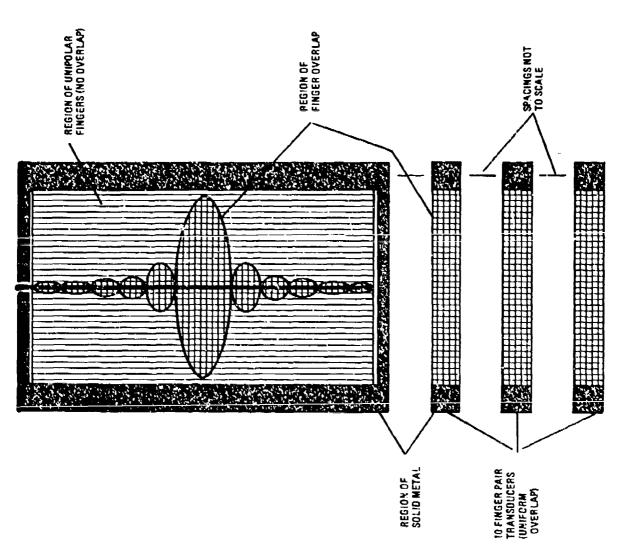

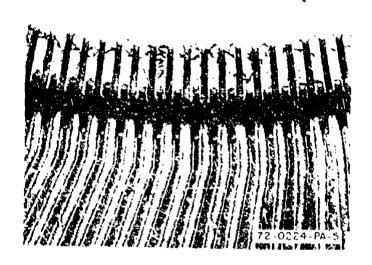

The remainder of this paper will be a discussion of two filters that were developed with the objective of providing dispersionless operation with steep filter skirts and a nominally flat response. Figure 2 shows the interdigital structure. Quartz was used for the filter, metallization is evident by virtue of the lighter color. The time side lobes of the filter are tapered to an approximate cosine pattern in order to provide an optimum square shape for the frequency response. The detailed taper of the side lobes is modified by the synthesis procedure described earlier.

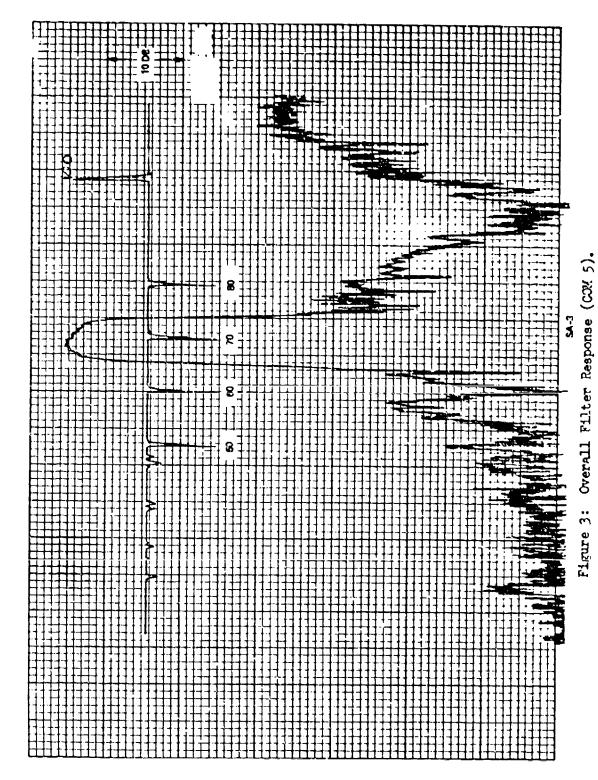

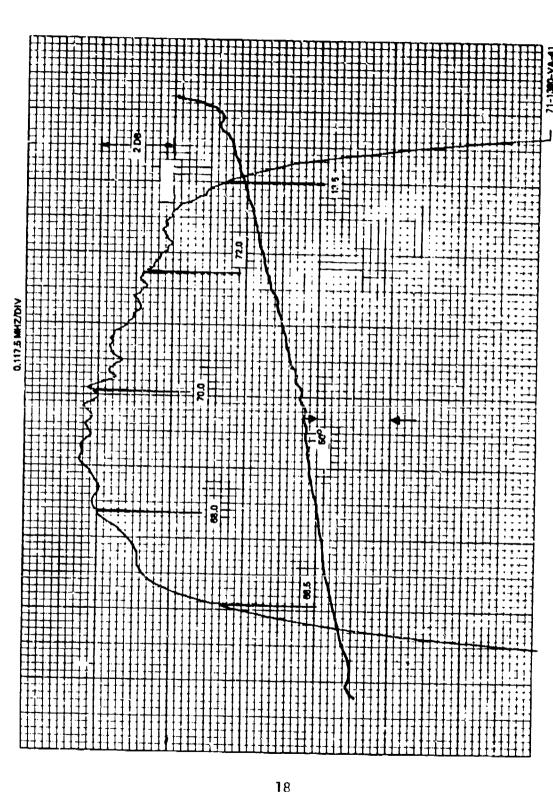

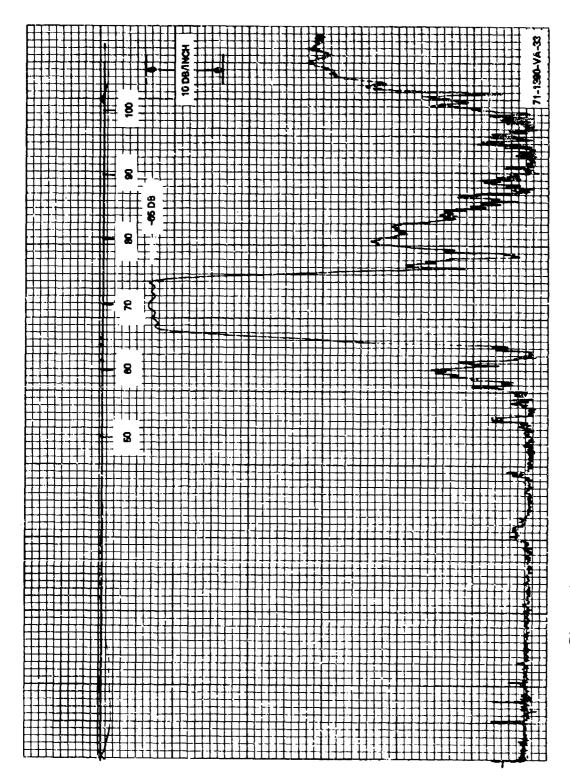

The properties of the filter are illustrated by Figure 3. This shows the center frequency of 70 MHz with steep filter skirts and low spurious response. The bulk of this spurious response are bulk waves which go through the crystal, reflect and come back to the surface to interact with the secondary transducer. Since these can all be eliminated with surface treatment they will not be considered further here. Figure 4 shows more detailed characteristics of the amplitude response as well as the phase characteristics. Except for a slightly attenuated region in the upper half bandpass this response appears to be that of a reasonably rounded top filter with some minor periodicities throughout the bandpass region. These minor periodicities in amplitudes vary between a tenth and 2/10th of a dB and are largely due to multiple reflections in the crystal. Most of which can be eliminated by proper surface treatment. The triple transit echo can also be suppressed by taking reasonable precaution. It should also be noticed that the phase characteristic is a straight line except for a break at the center and the same periodicities which amount to approximately a ripple of ± 2 degrees. In addition to these periodicities however, the phase characteristics have a distinct break in which the phase shifts from approximately 7 degrees per MHz to approximately 12 degrees per MHz or a difference of about 5 degrees. Since the phase slope is relative only the difference is significant. This change in phase slope levels to a distinct delay step in the approximate center band frequency of 70 MHz. It should be noted that except for this distinct shift in slope, phase is substantially dispersionless across the bandpass and shows no tendencies to be dispersive even at the band edges.

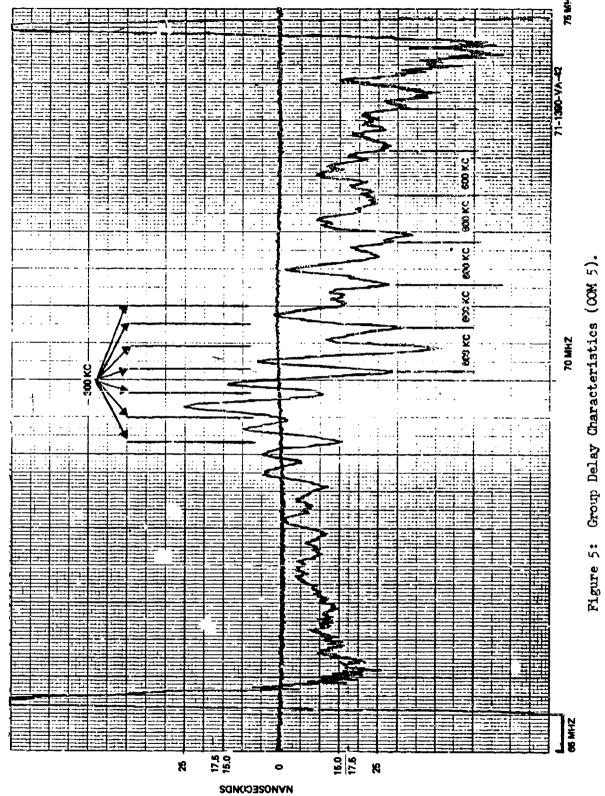

Figure 5 shows the group delay characteristics of this filter. We can see that there are numerous periodicities with frequencies of 300 and 600 KHz and they can be related to the forementioned effects.

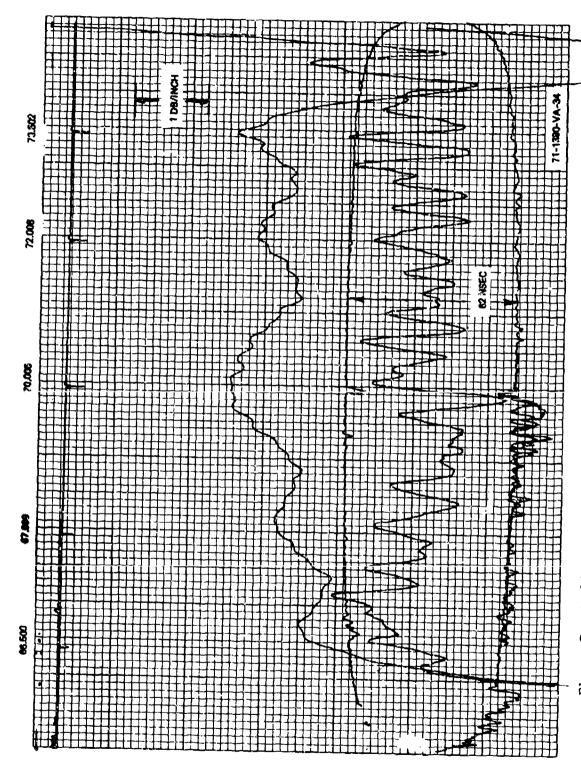

The curved top of this filter was due to the fact the synthesis was carried out ignoring the characteristics of the secondary transducer. Figure 6 shows a flattened top amplitude response by including the secondary transducer in the synthesis. The response is reasonably flat. It should be noticed that the same bulk acoustic wave leakage is evident. Figure 7 shows a more detailed view of the amplitude response and the fine periodicities of the group delay response. They are clearly multiple reflections of both surface

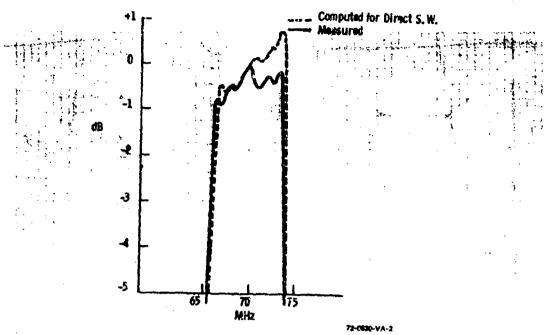

and bulk waves which can be controlled, as mentioned before, by suitable treatment of the surfaces. The large periodicity across the bandpass was a part of the synthesized pattern by virtue of a requirement placed on the program. Thus only the relatively fine periodicities represent deviations from the computed response which is within ± 1/10th of a dB except as will be shown in the next figure. Figure 8 superimposes the experimental and calculated responses of the filter. The computed response is flat top except for the periodicity mentioned earlier and a slope which represents quarter wave length periodicity of the equivalent circuit. The measured response is in good agreement with computed response below the center frequency. A nonsymmetric attenuation along with the break in the phase characteristics of the previous filter is due to metallic loading of the piezoelectric surface.

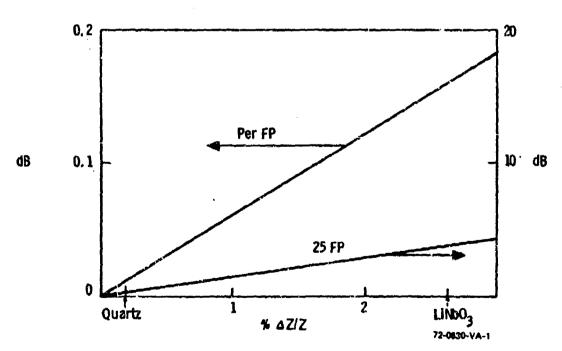

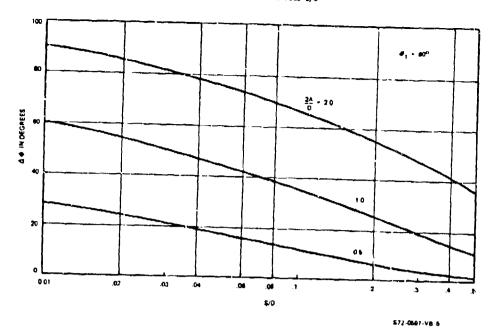

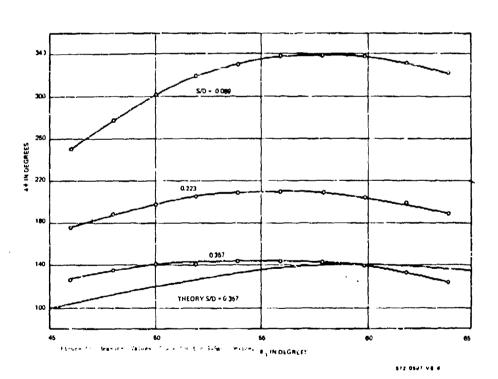

The essential effect of the metallic loading can be analyzed by the straight forward development of the propagation constant of electromechanical energy along the periodic transmission structure for which an expression is available, for example, as from Mathai and Young page 385. Figure 9 shows the maximum attenuation versus  $\frac{\Delta}{z}$ .

Two curves are shown, one for attenuation in dB per finger-pair and one for 25 finger-pairs. Since the attenuation is due to both primary and secondary transducers, this is typical of the filters described in this paper.

If we take the filter of Figure 3, as an example, Figure 10 then shows that for a  $\frac{\Delta}{2}$  value of 0.11 percent, a reasonably good match with the predicted attenuation is achieved. This figure indicates the size of the attenuation due to the periodic metallic structure. This particular comparison (for  $\frac{\Delta Z}{2}$  0.11 percent) appears to agree very well with the computed results. This same figure shows the modified phase characteristic due to the band stops. The five degree per MHz break in phase characteristics is at least Reasonably close to the value of four degrees calculated for the above value of It then appears that the nonsymmetry of the single filter can be explained in terms of periodic metallic loading due to the finger-pairs. It is thus necessary that this periodic loading be introduced into the synthesis process when filters are designed in order to achieve low dispersion surface acoustic wave filters. Based on the results of this study, for instance, if the affected phase break of four degrees is introduced into the synthesis process the residual phase 1 degree break would correspond to the difference between the actual five degrees shown measured in an carlier figure such that the actual break would be 1 degree. Similarly if the attenuation characteristic is suitably synthesized to within ± 1/10th of a degree a filter reproducible to a + 1/10th of a degree should be feasible. With these improvements the surface wave acoustic filter should be amenable to synthesis in many applications requiring a large number of rilters with precise reproducibility at a low cost.

It should be noted that the attenuation due to the metalization periodicity is insufficient to explain the difference between the computed and measured bandpass characteristics of the flat top filter (Figure 6). Since the positive slope of this filter is directly attributable to the cross field model, we must directly question the use of this model vs the in-line model for quartz.

Though the cross field model has been shown preferable for lithium niobate, it has not been shown to be viable for quartz.

CONTRACTOR

- 1. R. H. Tancrell, M. G. Holland, "Acoustic Surface Wave Filters", Proc. IEEE, Vol. 59, No. 3, pp. 393-409; March 1971.

- 2. W. Richard Smith, Henry M. Gerard, Jeffrey H. Collins, Thomas M. Reeder, H. J. Shaw, "Design of Surface Wave Delay Lines with Interdigital Transducers", IEEE Trans., Vol. MTT-17, No. 11, Nov., 1969.

- 3. R. L. Thomas, C. R. Vale, T. M. Foster, "Design and Fabrication of Precise and Repeatable Surface Wave Barker Code Correlators", IEEE Ultrasonics Symposium, Dec. 8, 1971.

Figure 1: Diagramatic Sketch for Computer Synthesis.

Figure 2: Filter Interdigital Structure (COM 5).

Figure 4: Detailed View of Pilter Response (COM 5).

Figure 6: Square Top Filter Response (CCM 6).

Figure 8: Comparison of Experimental and Computed Filter Responses (COM 6).

Figure 9: Metallic Loading Attenuation vs. A z/s.

Computed and Experimental Results for  $\Delta z/z = .11\%$  (COM 5). Figure 10:

### MATCHED FILTERING WITH SURFACE ACOUSTIC WAVE DEVICES

G. Chao and T. R. Larson

Naval Research Laboratory, Washington, D. C. 20390

### ABSTRACT

A review is made of the present state of surface wave matched filters. Recent work at the Naval Research Laboratory and other laboratories in phase coded and frequency modulated devices is described, and salient features of various matched filters are presented.

### SUMMARY

Within the past few years, advances in surface acoustic wave (SAW) technology have resulted in the compact implementation of a variety of matched filtering devices ranging from bi- and poly-phase coded tapped delay lines to linear and nonlinear frequency modulated devices. The purpose of this paper is to report on the state of the rapidly developing surface wave technology, to present recent work at the Naval Research Laboratory and several other laboratories and to summarize the salient features of the various surface wave matched filter implementations.

Conventional photolithographic processes limit transducer patterns to line widths of about one micron. This corresponds to an operating frequency of about 800 MHz on commonly used material such as lithium niobate (LiNbO $_{\rm q}$ ) and quartz. With computer

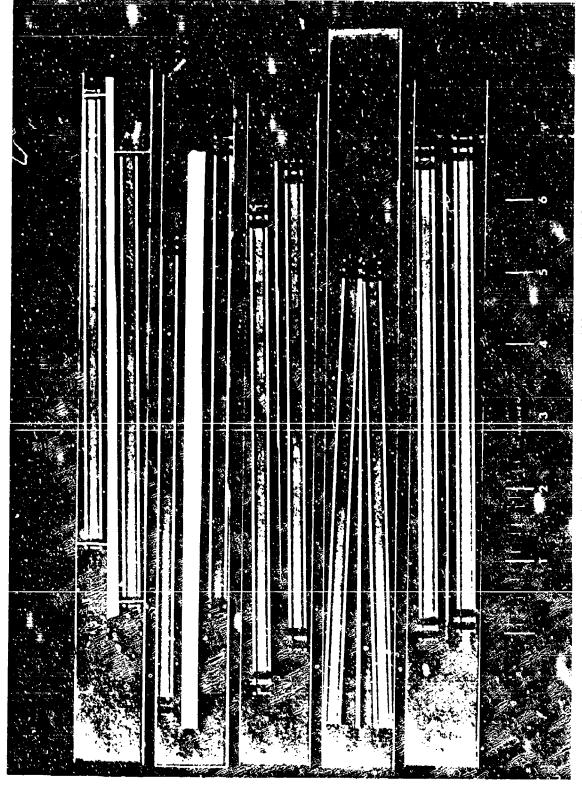

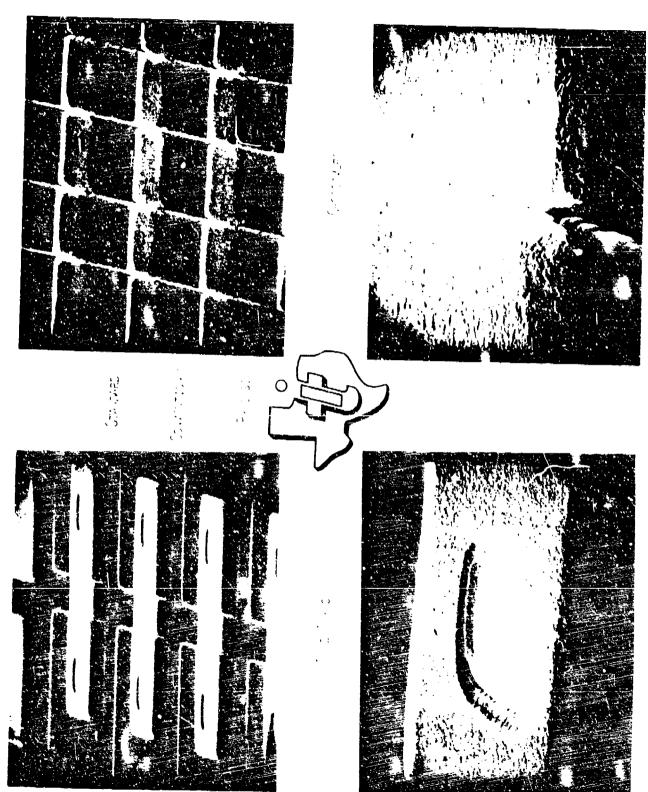

controlled scanning electron beams, line widths of a tenth micron with line stabilities of 0.03 microns are being achieved. Nevertheless, many matched filtering devices are being fabricated with center frequencies below 100 MHz because of various system considerations, and consequently, the critical parameter is time delay, or equivalently propagation length. Transducer patterns of up to six inches long and longer, containing thousands of individual metallized lines have been fabricated and time-bandwidth products into the thousands are presently being achieved. Fig. 1 shows a few representative delay lines developed at Hughes Aircraft Company. These are circulating and reflecting 100 microsecond delay lines consisting of two 50 microsecond linearly dispersive transducers on ST-cut quartz. The center frequencies range from 30 to 60Miz with compression ratios varying from 560:1 to 2000:1.

One of the simplest methods of achieving matched filtering with SAW devices is to phase code a tapped delay line. Bi-phase M sequence codes have been implemented with responses very near the theoretical limits. However, bi-phase codes are inherently restricted by relatively high time sidelobes, and consequently, poly-phase and complimentary-pair codes have been investigated. Although perfect cancellation of sidelobes is theoretically possible in these cases, practical values of about -25 dB are being achieved.

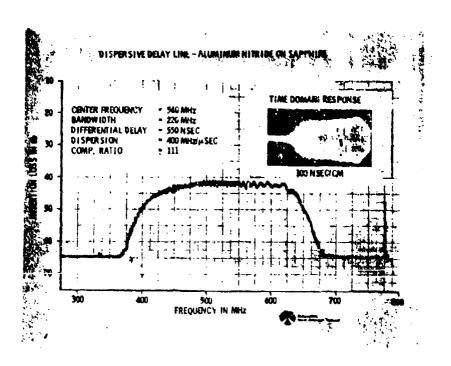

Although basically nondispersive, surface wave delay lines may be made dispersive by proper transducer design. Linear and nonlinear FM matched filters have been proposed along with various weighting procedures. Fig. 2, provided by North American Rockwell, shows the dispersion of a representative transducer pattern designed for 300MHz operation on ST-cut quartz, but deposited on a faster substrate, aluminum nitride on sapphire (ALN/AL203). Although not designed for ALN/AL203, the transducer behaves

very well and demonstrates one advantage of  $ALN/AL_2O_3$ : the extension of the bandwidth of SAW devices with existing transducer technology.

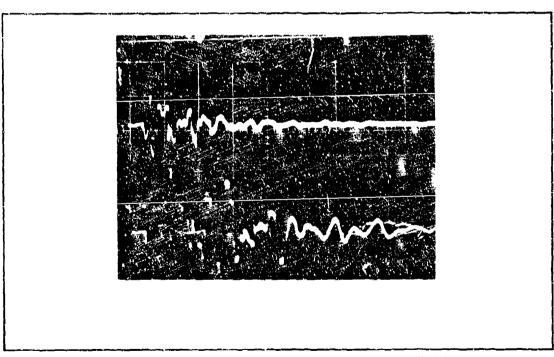

The pulse expansion and compression properties of the transducer pattern of Fig. 2 deposited on ST-cut quartz are shown in Fig. 3, indicating very good characteristics and near theoretical time side lobe levels.

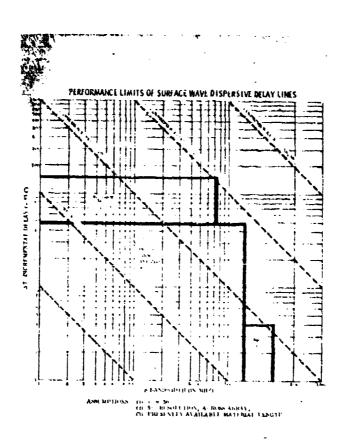

A conservative estimate of compression ratios possible for various substrate materials is given in Fig. 4 suggesting that compression ratios of 10,000:1 and more may be achieved in the very near future.

Within the past few years, matched filtering with surface acoustic waves has yielded devices with ever increasing compression ratios. Delay lines with ratios in the thousands are being fabricated and new materials and advances in transducer technology promise even higher performance.

### ACKNOWLEDGMENTS

The authors wish to acknowledge the help of J.C.Aukland, J.Burnsweig, Dr.E.H.Gregory and R.A.Kempf in providing background from various industrial laboratories.

Figure 1: Photograph of several 100 microsecond delay lines with compression ratios to 2000:1 (from Hughes Aircraft Company)

Figure 2: ALN/AL203 dispersive delay line (from North American Rockwell)

# 300 MHZ COMPRESSION LOOP

OF NELC/PIN HORKS

BIRG TORED PULSE (see SSEC/DIV HORZ)

SPECIALM OF STRENGIED PLESS OF OR/OW VERY 30 MHZ/DIV BORG

# STRETCHED PULSE

RECOMPRESSED PULSE ISIDE FOR TEVEL >22 DIO 20 NSEC/ON HORZ

ENPANDED VIAW OF RECOMPRESSED PULSE (5 NSEC DIV BORZ PULSE WIDTH S IS NSEC & COUPLYS)

# RECOMPRESSED PULSE

and MHy Experience and Comprehending Deep Performance

Figure 3: Pulse expansion and compression at 300MHz on ST-cut quartz (from NAR)

Figure 4: Performance limits of various surface wave delay line substrates (from NAR)

Itia 🕽 🗶 🐇 🤌

# IC PACKAGES AND HERMETICALLY SEALED-IN CONTAMINANTS

R. W. Thomas

Rome Air Development Center, Griff'ss AFB, N.Y.

# **ABSTRACT**

An extensive analysis of gas in integrated circuit packages has revealed a lack of adequate control by the semiconductor industry. Contamination mechanisms, gas analysis procedures, fine and gross leak test inadequacies, and specification recommendations will be discussed.

## IC PACKAGES AND HERMETICALLY SEALED-IN CONTAMINANTS

R. W. Thomas

## RELEVANCY

An extensive analysis of gas in integrated circuit (IC) packages has revealed that there are wide variations in the ambient gas from lot to lot, manufacturer to manufacturer, and with different package designs. These uncontrolled gas ambients became relevant when RADC found that a high percentage of field failures returned for analysis contained large amounts of water vapor. Further, it was found that water vapor behaved as a necessary, but not always sufficient condition for failure, the most noted exception being the distilled water electrochemical etching of nichrome resistors in radiation hardened circuits.

The contamination of the chip ambient has become more prevalent with the proliferation of ceramic packages and solder sealing glasses. The entire blame for hermetically sealing water and other contaminants in the packages cannot fully be laid on the semiconductor industry. MIL-M-38510 and MIL-STD-883 did not specify the remaining chip ambient after sealing. Even more important, there was no data available which gave tolerance levels for integrated circuits in general or specific device types in particular. Further investigation revealed that quantitative water analysis was very difficult and that few companies could afford the equipment necessary for such an analysis.

After establishing through failure analysis that hermetically sealed-in contaminants were a real-world problem both in state-of-the-art devices and those which have been in the field for several years, a program was initiated to develop an accurate gas analysis facility. Such a facility now exists at RADC. The development, design, system sensitivity, and the results of an extensive IC gas analysis program are the subject matter of this presentation.

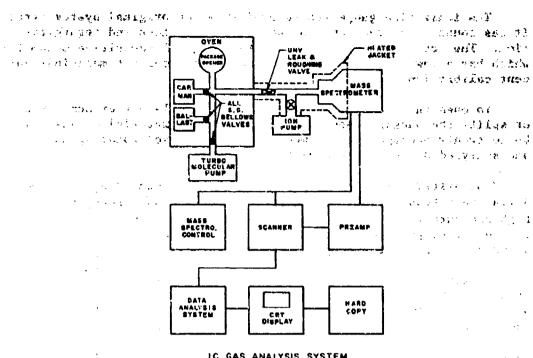

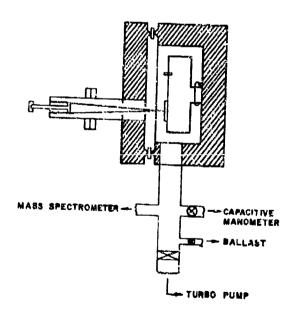

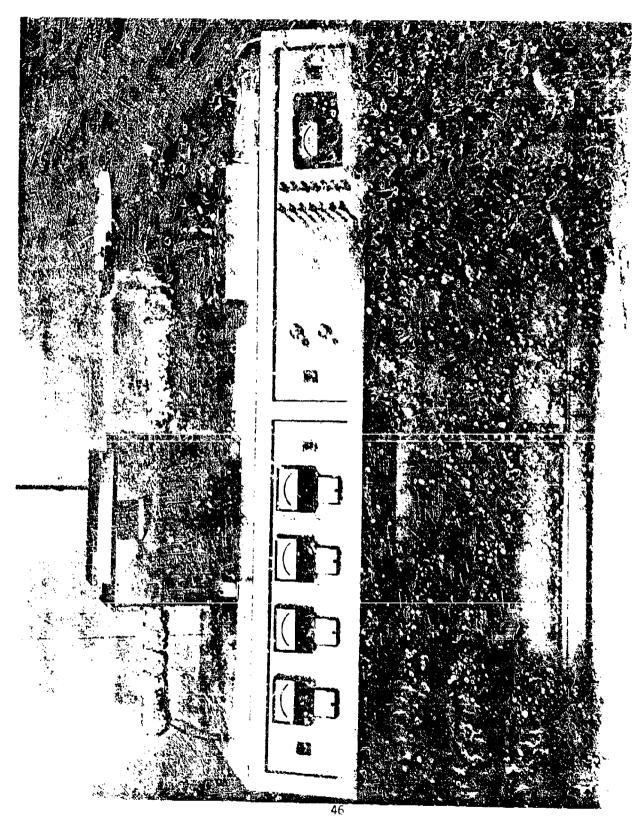

## RADC GAS ANALYSIS SYSTEM

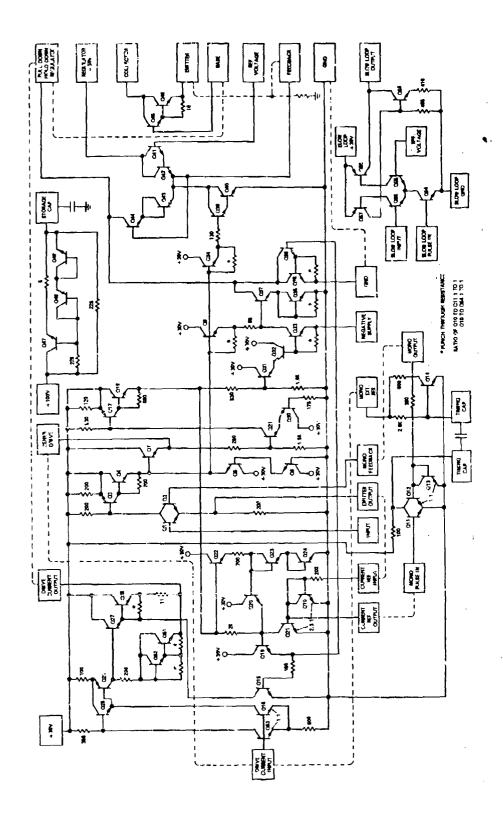

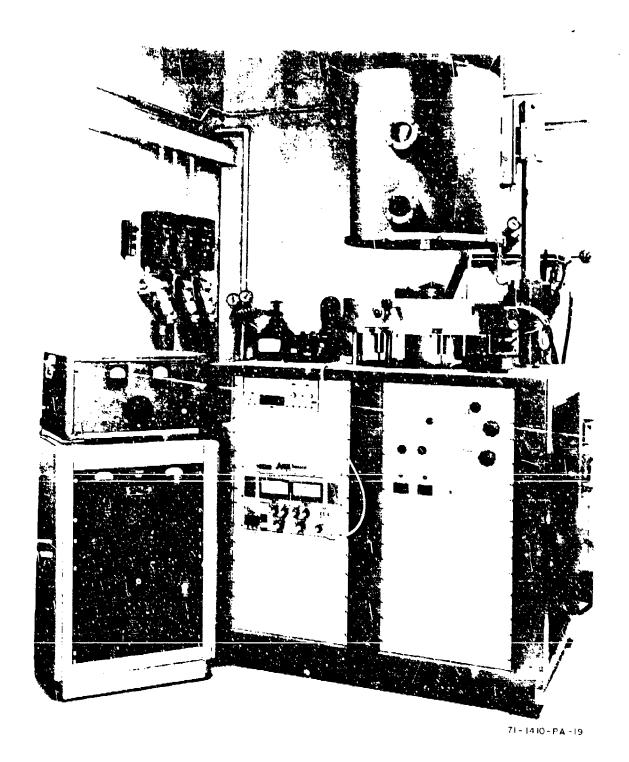

The system fabricated at RADC for package gas analysis has been under continuous development for three years. The present version was fabricated entirely from stainless steel, with copper sealed ultra-high vacuum flanges and welded stainless ace? bellows valves. Ultra-high vacuum fabrication techniques such as notching the internal machine screws for gas relief, polishing large surface areas, and minimizing internal volume were vitally important in achieving maximum performance. Materials such as glass, terlon, viton, and vacuum grease were removed from the system as originally designed to obtain low outgassing rates. The present system is shown in figures 1 and 2.

AND THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON OF THE PERSON O

I.C. GAS ANALYSIS SYSTEM

Y . .

PACKAGE OPENER

The ionization gauge was removed from the original system after it was found to be the cause of secondary reactions and regurgitation. The ion gauge was replaced with a digital capacitive manometer which has a low outgassing rate and makes an excellent mass-independent calibration system.

To open the package, a hardened steal needle either punctures or splits the package depending on the package material or design. Up to twenty packages may be mounted on an indexed rotating holder and analyzed during one vacuum bakeous cycle.

The system volume was designed so that the expanding gas from a flat-pack results in  $\varepsilon$  system pressure of 1 x 10<sup>-5</sup> torr, the high pressure limit of the quadrupole mass spectrometer. To accommodate larger packages, a ballast is valved into the system and adjusted to obtain the proper pressure.

In making quantitative gas analysis measurements, one is confronted with an overwhelping number of mass-selective and gas history-sensitive mechanisms. For instance, all leak valves, vacuum pumps, ionizing chambers and electron multipliers are mass-selective devices. The electron multiplier and ion pump are particularly gas history-sensitive. To make the analysis even more complicated, it was experimentally determined that once the package was opered, each gas specie diffuses from the package at a different rate. It quickly became evident that only a dedicated computer, operating in real time, could analyze and correct for a number of variables operating simultaneously.

## SYSTEM PARAMETERS

The system scans the mass range from 1. to 100. atomic mass units in one second. The absolute accuracy is presently 1.% of the constituent measured. The sensitivity of the system is constituent dependent and varies from 10. parts per billion for oxygen to 6 parts per million for water and hydrogen. All other gases fall into this range. At the time of writing, this is considered to be state-of-the-art. It is expected that, by improving vacuum techniques and using more sophisticated statistical analysis procedures, these system parameters will continually improve.

# RADO IC GAS ANALYSIS PROGRAM

RADC is currently conducting a multilevel program to solve the sealed-in contaminants problem. An ultra-clean package sealing system is currently under development. This system will seal controlled quantities of contaminants into IC packages to determine telerance levels of sensitive circuits to water vapor and other contaminants. The sealer will also permit the packaging of standard ambients for round-robin calibration and sensitivity checks of other gas analysis systems.

Lot sampling of new devices and packages will be expanded. This will allow various sealing systems to be fingerprinted by mass spectromatry to detect possible changes or degradation in sealing integrity and purity.

og fyme) Salvingt Passonia

Working in cooperation with the Physics of Failure Laboratory at RADC, a considerable amount of data has been gathered on contamination-produced failure mechanisms. A brief synopsis of this work is included in the following section. This work will be expanded to include a study of the effect of various stresses on the chip ambient.

The components found in some IC packages indicate that some additional work should be done on the effectiveness of present fine and gross leak tests.

## RESULTS OF GAS ANALYSIS INVESTIGATION

A small but significant percentage of the packages opened contained residual amounts of helium and freon. This led to further experimentation and the discovery that water, freon, and neon could be inserted into the "hermetically" sealed package by a one-way thermomechanical valve action at the lead frame, if the package was bombed at an elevated temperature (150°C.).

Water was found in IC packages in amounts exceeding eight times the water contained in air at 50.% relative humidity and 25.0 C. The circuit failures in these packages were directly related to the excess water.

The thermal atressing of ceramic IC packages will increase the water and carbon dioxide content at lower temperatures (150.°C.), and change to methane and hydrogen at temperatures of 350.°C. This observation can be directly related to improper curing of the binder used in the sealing glass.

From the analysis of more than fifty samples from a particular manufacturing line it was possible to observe groupings in the gas composition. Changes in this fingerprint indicated changes in the sealing frit, purge gas, oven sealing ambient, and procedural changes in the sealing operation. Feasibility was demonstrated in establishment of norms for specific packages and sealing procedures, which could then become the basis for lot acceptance specifications.

## CONCLUSION

The conclusion is self-evident. There is a definite need at the present time for a hard look at the presently-used sealing procedures, gas analysis techniques and specifications for ensuring an inert chip ambient. RADC, through its Air Force

agaring obergrious.

Books of the rearest example of the Bigston of Basical of the residence of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second of the second

A CAR A MARABOLIA A SA A SA A MARABANA A MAR

# The Control of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the State of the

N.J. Grossman & K.K. Heid

Northrop Corporation

Electronics Division

Navigation Department

2301 West 120th Street

Hawthorne, California 90250 (213) 757-5181

#### ABSTRACT

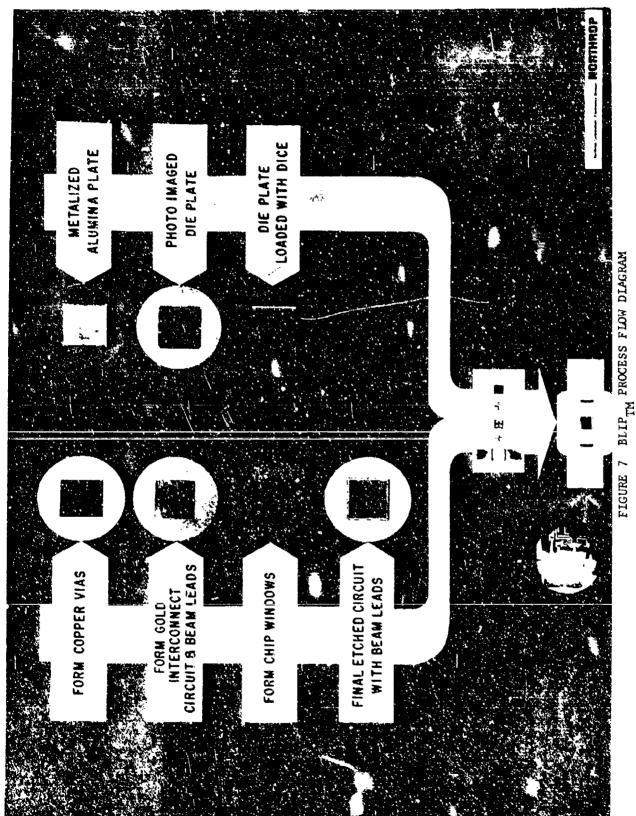

This paper describes a microcircuit packaging approach which eliminates flying wire bonds, a major failure mode in microcircuits, and utilizes beam leads formed independently from the active devices. Both intra- and interconnections are made with beam leads thereby eliminating all flying wire bonds. BLIP<sub>TM</sub> is a multilayered micropackaging concept that is keyed to a disciplined system of component management, interconnection requirements that include integral beam leads, assembly processes and testing of the inprocess or completed functional circuit.

#### I. INTRODUCTION

Hybrid technology has been highly successful in achieving a dramatic reduction in size and weight. The density and complexity of today's hybrid circuits have led to new approaches in fabrication, such as multilayer conductors and beam leaded or flip-chip integrated circuits.

A major disadvantage of the present methods of microcircuit packaging has been that of cumulative processing with an inability to functionally test the circuit until after final assembly when the majority of labor and material costs have been expended. BLIP makes use of parallel processing with functional testing capability prior to commitment of costly material such as integrated circuits.

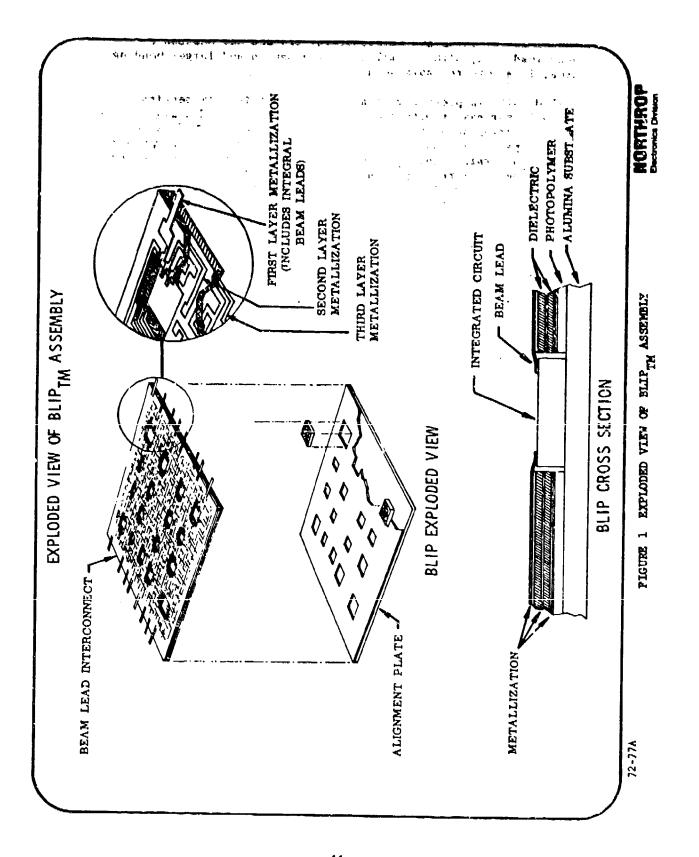

## II. THE BLIP CONCEPT

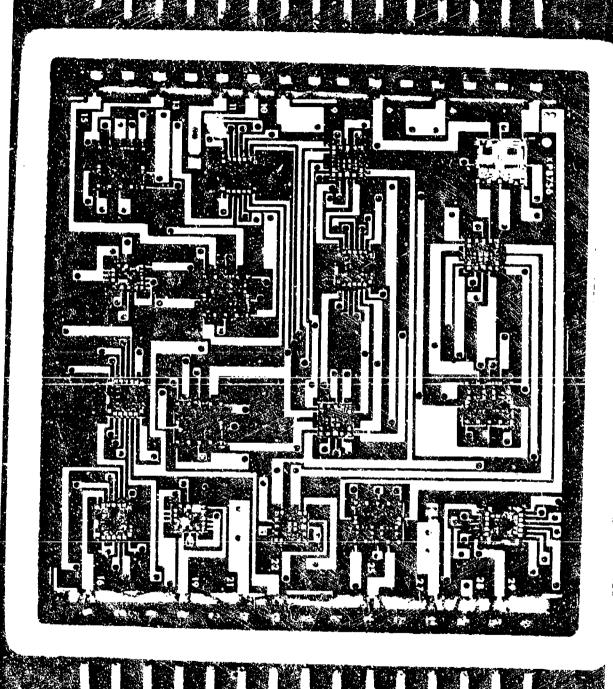

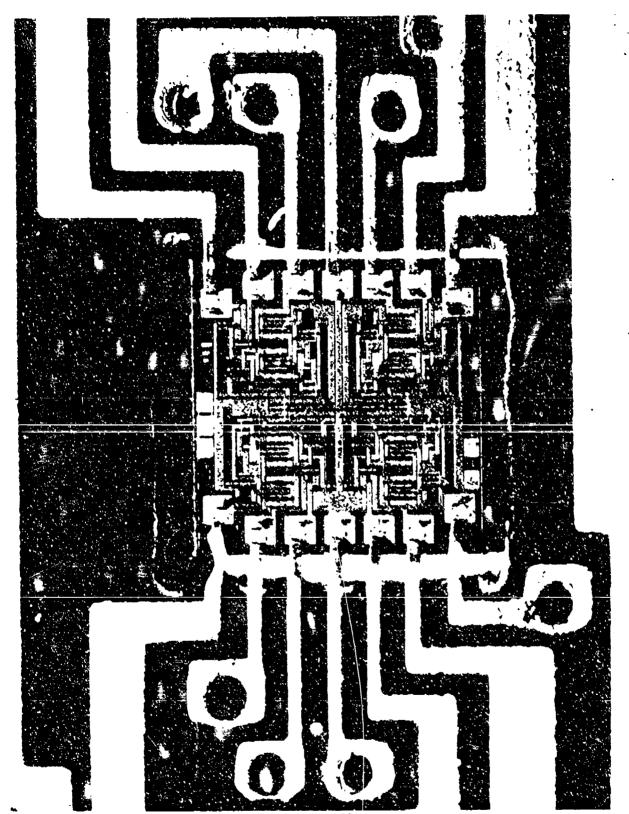

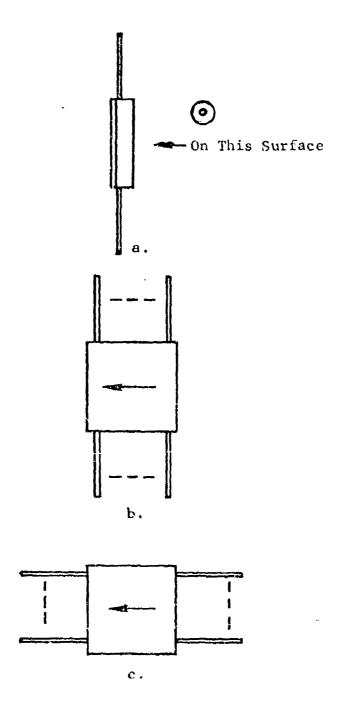

The major features of BLIP are illustrated in Figure 1. The die plate is composed of a photopolymer material laminated to a base plate which may be a standard substrate such as alumina or beryllia. The substrate may be metalized and form one level of interconnection and may also contain resistor elements. The photopolymer material forms cavities in which circuit components nest and, by means of alignment marks, allows the precise attachment of circuit components independently of the interconnect network which is the second BLIP

component. The interconnect network is a multilayer conductor pattern with integral beam leads for connection to the components as well as to the outside world or second level interconnection.

#### III. DIE PLATE FEATURES

The substrate is first processed through standard vacuum deposition and photoetch steps to obtain the desired conductor and resistor patterns. The dry film photopolymer serves as a spacer and therefore its thickness is determined by component heights and by the interconnect network thickness. After the lamination step, the photopolymer is exposed and developed to form device cavities to allow attachment of active devices to the substrate. Keying or alignment marks are also formed during this step around each cavity so that the component may be precisely aligned when it is mounted.

The substrate size is limited only by the uniformity of metalization desired during vacuum deposition and therefore a large number of die plates may be formed on a single substrate. After lamination and photoimaging, the die plate is ready for component attachment. This may be performed before or after the substrate is broken into individual die plates.

#### IV. THE INTERCONNECT LAMINATE

The interconnect laminate is made up of alternating layers of a suitable dietectric such as epoxy glass and conductor paths which serve to interconnect all components. Although the number of conductor layers is not unlimited, three have been found adequate for the most complex of hybrid designs, so far implemented.

The most important feature of the interconnect laminate is the integral beam leads that are formed to make connections to the active devices. These project over the component windows and are formed to make contact with a device bonding pad as illustrated in Figure 2. The external connections are also beam leads so all flying wire connections are eliminated.

Connections between layers are made by plated through holes or vias. The vias are first formed by photochemical etching then electroless and electrolytic plating are used to form the electrical connection.

### V. THE ASSEMBLY PROCESS

The fabrication of the interconnect laminate and the baseplate are both batch processes with each lot capable of producing hundreds of parts. Furthermore, they are parallel processes, each operating independently of the other. After they have been processed, tested, and inspected, they are ready for the final assembly steps.

The interconnect laminate and the baseplate, loaded with components, are now bonded together. Individual circuits may be bonded, if the substrate has been separated into single die plates, or all circuits on a substrate may be bonded simultaneously. Alignment is straightforward since beam leads and device bonding pads are both visible.

After curing the bonding adhesive, the circuit is now ready for ultrasonic bonding of the beam leads to the components. Beams are presently bonded one at a time but the adaptation of a webble or compliant bonder appears quite feasible.

Assembly errors are reduced with BLIP<sub>TM</sub> because subassembly (die plate and interconnect) orientation can be easily checked. This leads to a reduction of labor skill required and therefore a cost reduction. It further minimizes troubleshooting because of the ease of visual inspection.

#### VI. PACKAGING

A major improvement in packaging density is achieved by eliminating the traditional hermetically sealed flat pack. This reduced surface area and volume requirements and also eliminates fan out restrictions imposed by the flat pack. The environmental protection required for the unpackaged BLIP<sub>TM</sub> module is achieved by a vapor deposited conformal coating of parylene whose barrier properties are superior to the silicones.

Parylene is the generic name for members of a unique polymer series developed by Union Carbide Corporation. The basic member of the series is poly-para-xylylene but the two types of interest, designated Parylene C and D, are chlorinated and dichlorinated modifications, respectively.

The replacement of a hermetically sealed package with another form of environmental protection must take into consideration all the common components of a microcircuit such as semiconductors, capacitors, and resistors. In the case of semiconductors, silicon nitride offers much potential for protecting these sensitive devices but ceramic chip capacitors and nickel-chromium resistors are also very susceptible to humidity.

If parylene is to serve as a replacement for hermetically sealed packages, the barrier properties of the material are of prime importance. These properties are given in Table 1 and compared with those of the more common organic coatings.

Table I

# Barrier Properties of Some Representative Organic Coatings

|            | N <sub>2</sub> <sup>(1)</sup> | o <sub>2</sub> (1) | co <sub>2</sub> <sup>(1)</sup> | H <sub>2</sub> (1) | H <sub>2</sub> 0 <sup>(2)</sup> |

|------------|-------------------------------|--------------------|--------------------------------|--------------------|---------------------------------|

| Perylene C | 0.6                           | 5                  | 14                             | 110                | 1                               |

| Parylene D | 4.5                           | 32                 | 13                             | 240                | 0.25                            |

| Epoxies    | 4                             | 5-10               | 8                              | 110                | 1.8-2.4                         |

| Silicones  | -                             | 50,000             | 300,000                        | 45,000             | 4.4-7.9                         |

| Urethanes  | 80                            | 200                | 3,000                          | •                  | 2.4-8.7                         |

- (1) Gas permeability, cc-mil/100 in<sup>2</sup> 24 hrs; ASTM D1434-63T

- (2) Moisture Vapor Transmission, gm-mil/100 in<sup>2</sup> 24 hrs; ASTM E96-63T

The material is deposited from the vapor phase in a "soft" vacuum, with the mean free path of the parylene molecule on the order of 0.1 cm. The result is a truly conformal deposition rather than the line of sight type coating one usually associates with vacuum deposition techniques.

Because of these attractive characteristics, Northrop initiated a program to study parylene coatings on BLIP<sub>TM</sub> microcircuits. A deposition system was designed and built (see Figure 3) and a series of preliminary tests conducted. The results of the preliminary tests, discussed below, were encouraging enough to justify a large scale military qualification type test program which is presently underway.

## VII. ENVIRONMENTAL TEST RESULTS

## A. IONIC Contamination Test

A major concern of any semiconductor passivation coating is that the coating does not introduce ionic contamination. For this test a group of PNP (2N2907) unpassivated transistors were parylene coated and submitted to a humidity test in accordance with MIL-STD-810B.

One hundred eighty of these parts were mounted in unlidded flat packs. The leakage current (I<sub>CBO</sub>) was measured at an ambient temperature of 120°C prior to parylene coating, after the coating was applied, and after the 10-day humidity test which exposed the parts to 85 percent relative humidity and a temperature variation of 25° to 71°C on a 24 hour cycle. Leakage currents remained constant during and after the test, indicating that parylane did not cause any ionic contamination but did protect the parts from the humidity environment.

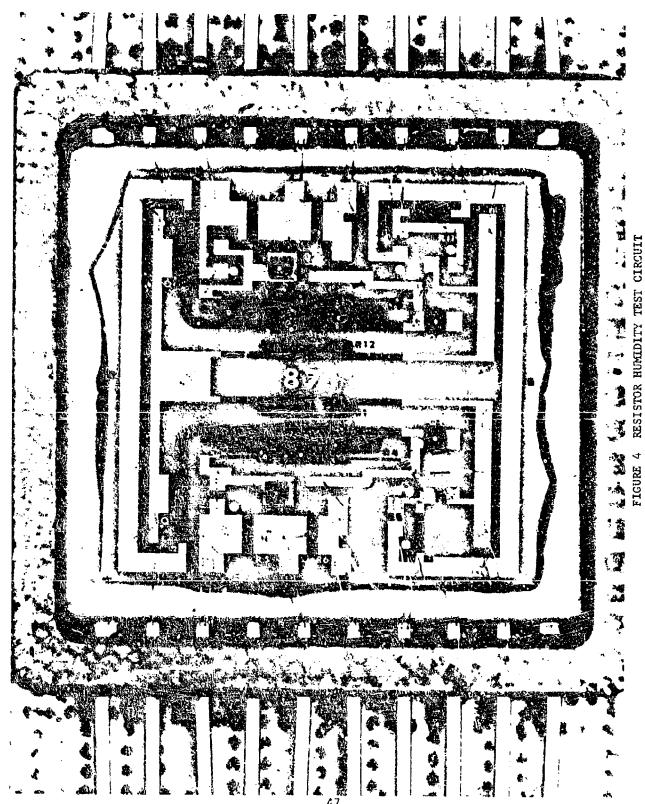

# B. Humidity

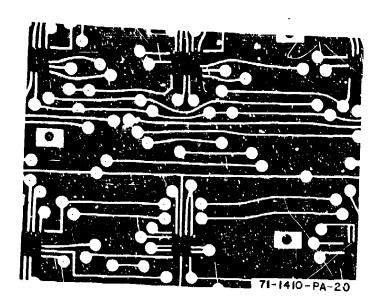

In the presence of an electric field and moisture, thin film nickel-chromium resistors are very susceptible to electrolysis. To determine the effectiveness of parylene as a moisture barrier, one hundred eighty seven nickel-chromium thin film resistors were mounted in unlidded flatpacks and parylene coated. These resistors, of vs ious form factors and values, (see figure 4) were powered at several different power densities to ensure condensation on at least some of them. A control lot of 55 unprotected resistors were also tested and all resistors underwent the MIL-STD-810B test described in Section A above.

Resistor values were read and recorded before and after the parylene deposition and after the humidity test. The parylene costed resistors showed no change in value whereas 10 of the 55 uncosted resistors had catastrophic failures or major resistance changes (≥ 20%) with some of the failures occuring in the first 24 hours of the test. Because some of the resistors in each lot were unpowered and some powered at densities as high as 150 watts/square inch, failure of all resistors in the unprotected group were not anticipated because condensation did not occur on all resistors.

### C. Radiation Induced Ionization

Radiation induced ionization in the parylene costing could cause functional failures in a microelectronic circuit. To determine this, a 2N3960 transistor was employed, using the test matrix below.

|                     | Reverse Bias | No Reverse Blas |

|---------------------|--------------|-----------------|

| Parylene coated     | 6 units      | 6 units         |

| No parylene coating | 6 units      | 6 units         |

Leskage currents and DC current gain at 100 microsuperes and 1 millisupers were recorded before and after radiation. Exposure levels were 7 X 10<sup>4</sup> n/cm<sup>2</sup> and 1 X 10<sup>5</sup> rad/Si. Comparison of before and after data showed no significant difference between cost:d and uncosted devices with and without power applied. This indicates that parylene does not trap a charge or have other deleterious effects, due to radiation, on sensitive semiconductor devices.

## D. Nuclear Testing

Results of recent underground tests on parylene coated BLTP TM circuits, when compared to uncoated circuits, demonstrate that parylene improves the survivability of a circuit in a thermomechanical shock environment.

#### VIII. FUTURE DEVELOPMENTS IN BLIP

A large factor in manufacturing costs of highly complex hybrids is the troubleshooting and rework caused by defective active devices. The ability to test a circuit functionally prior to the permanent attachment of any active devices would overcome this problem and BLIP offers that potential. If the active devices were attached with a long shelf life epoxy, the interconnect laminate could be aligned over the die plate and electrical connection made by means of mechanical pressure. The entire circuit could then be functionally tested before any bonds are made and before the epoxy is cured. Chip replacement would then be a matter of extracting the die from the uncured epoxy and replacing it with a new die. Troubleshooting and rework could then be accomplished early in the assembly process with a reduction in damage due to rework.

If the circuit checks functionally good at the time of the "pressure test," it would be advantageous to bond the beams immediately. The die place and interconnect are already aligned and electrical contact is being made at all the required points. If a form of webble or complaint bonding could be utilized at this point, the assembly could be bonded with no additional handling or alignment.

## IX. CONCLUSIONS

BLIP has been demonstrated to be a multilayer hybrid packaging concept which essentially eliminates flying wire bonds. It utilizes standard active devices rather than the new, face-down devices which are presently more expensive and less available.

BLIP does not involve any radical new technology but rather the evolution of proven processes that have been in widespread use for a number of years. The elimination of flying wire bonds and the use of beam lead bonds is a major reliability factor because

BLTP density is presently equal to current thin film density and will surpass it with the application of improved design rules covering such areas as line width and spacing, via size, and via pads. The use of miltilayer conductors eases design and layout constraints and provides the required termination density for the nawer, more complex active devices. Its application to very large functional blocks with advantages in testing and final packaging within the same manufacturing format is a next important stage of its usefulness.

## X. ACKNOWLEDGEMENTS

The authors wish to express their gratitude to the many people within Northrop who contributed to this project.

FIGURE 2 SCALMING ELECTRON MICROSCOPE PHOTO OF BEAM LEADS AFTER PONDING

PICHAR 3 PARYLENZ DEPOSITION SYSTEM

RESISTOR HUMIDITY TEST CIRCUIT

FIGURE 5 1" X 1" BLIP<sub>TM</sub> HYBRID UTILIZING 3-LAYER METALLIZATION

FIGURE 7

A UNIVERSAL PACKAGING SYSTEM AS APPLIED TO THE ALL APPLICATIONS DIGITAL COMPUTER ាស៊ី (ខក១៩៥ បាន**នៅជ**ន់ទៅ)

5.5 773 N. 12.16

S 3344

10 ge 348025

្ត ស អា មេជា សង្គី

BY Lothar Laermer

The Singer Company Kearfott Division Little Falls, N.J.

# \* ABSTRACT

A universal packaging system is described which will serve the requirements of military and space electronics during the latter part of the decade. Design features and fabrication techniques associated with the All Applications Digital Computer Building Block Module and its Zero Force Cam Operated Connector are highlighted.

In addition, the design of the Higher Level Package, which retains a multiplicity of modules, is covered.

## INTRODUCTION

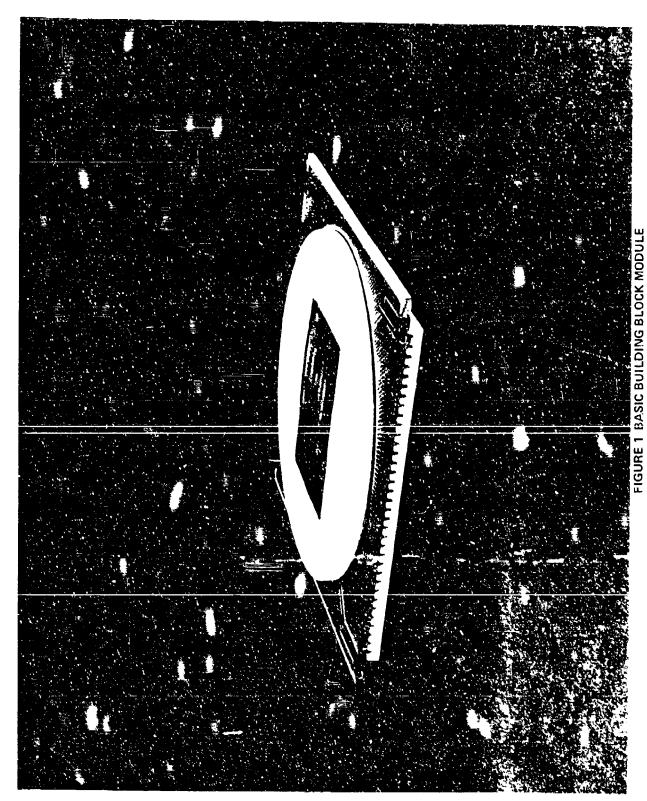

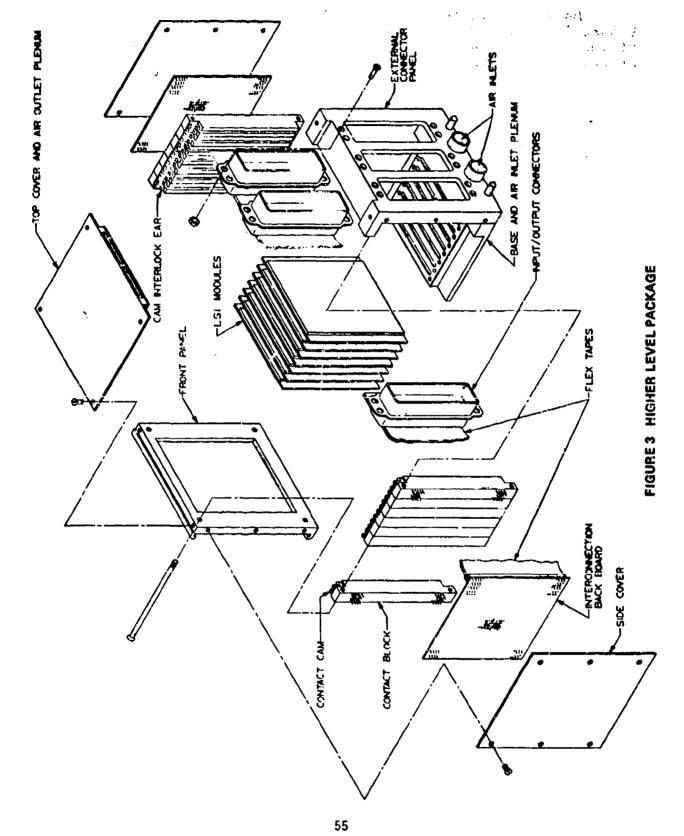

A hardware design and development program for the packaging of the All Applications Digital Computer (AADC) has been in progress, under NASC sponsorship, at the Kearfott Division of the Singer Company since June 1970. A primary objective of this effort has been the evolution of a packaging system that has universal application. Packaging techniques are being perfected concurrent with the development of micro-electronic devices that are to be used in military and space electronics during the latter part of the decade.

The program calls for the design, development, and prototype fabrication of:

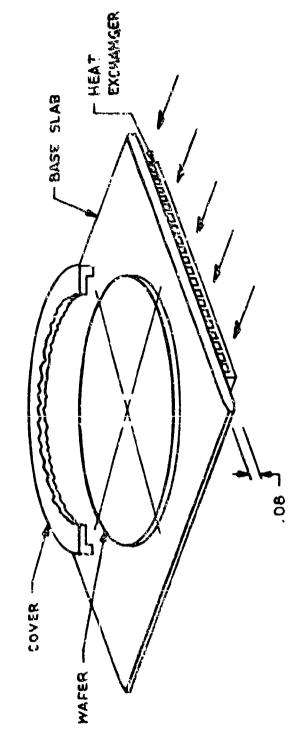

- . A "Building Block Module" capable of retaining a three-inch diameter silicon wafer or hybrid substrate

- . Higher Level Package containing a multiplicity of Building Block Modules.

### SYSTEM DESCRIPTION

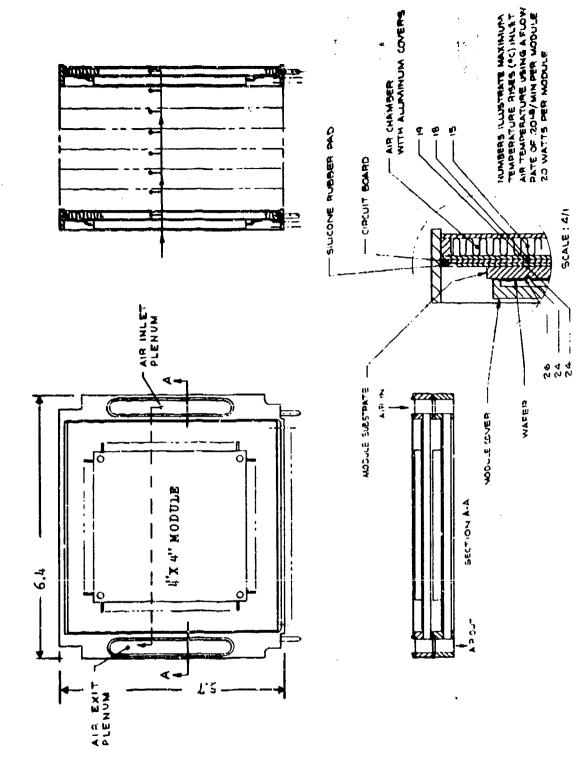

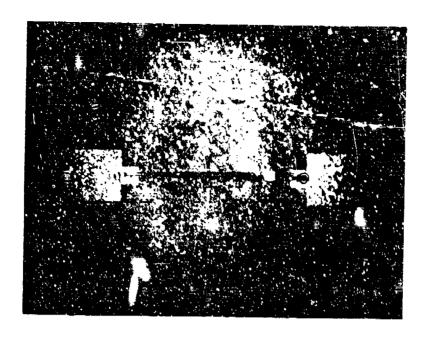

The All Applications Digital Computer packaging system has as its basic element the Building Block Module which provides the hermetic enclosure, interconnect, mounting and heat exchange mechanism for the electronic elements. The module is illustrated in Figure 1.

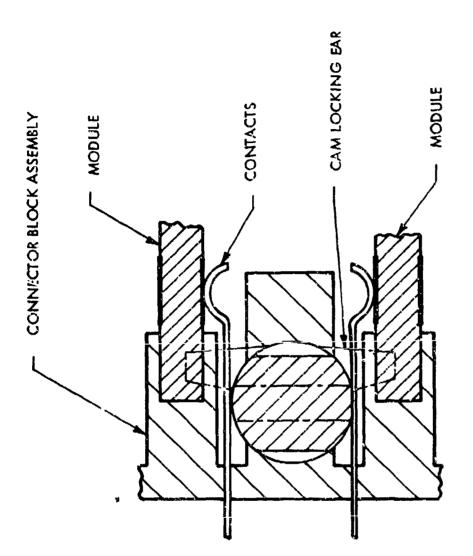

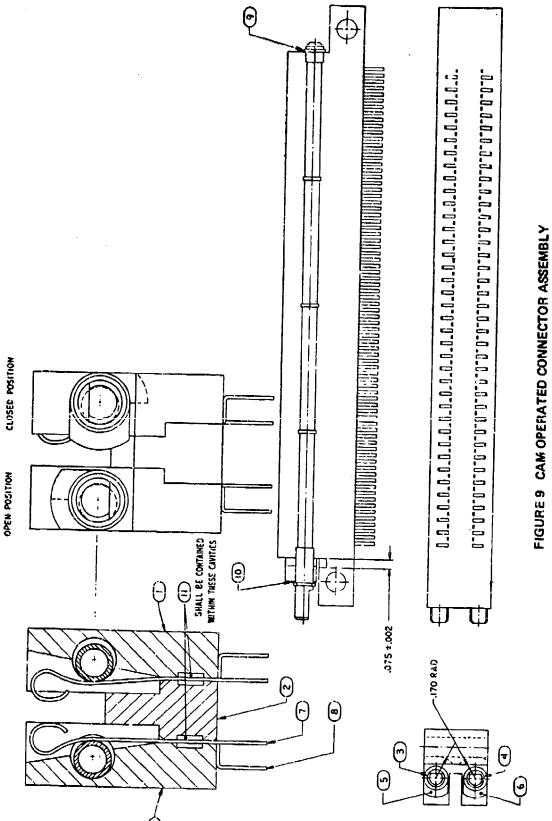

Electrical connections to the module are made via two 152-Pin Cam Operated Connectors as shown in Figure 2.

A series of Building Block Modules which may constitute a complete electronic system, will be retained in the Higher Level Package; this package provides the cooling air distribution and internal-external interconnect system. Figure 3 is an exploded view of the major elements showing the physical relationship of the Building Block Module, Cam Operated Connector and interconnect system.

The following paragraphs will describe in greater detail the characteristics of the major elements and the engineering tradeoffs that were made in arriving at an optimized system.

The AADC Building Block Module illustrated in Figure 1 is capable of retaining a three-inch diameter silicon wafer or a three-inch diameter hybrid circuit substrate. The module's unique features are tabulated below.

- . External Connections 300

- . Power Dissipation Up to 50 watts

- . Maximum Power Density 7.5 watts/square inch

- . Environment MIL-E-5400 Class 4X 200°C max

.

- . Hermetic Seal

- . Provisions for Guiding, Keying and Clamping

- . Interface with Zero Insertion Force Connector

- . Integral Heat Exchanger

- . Vibration Resonant Frequency above 2000 Hz

- . High Speed Circuit Compatibility (10 nsec delay)

- . Size 4 inches x 4 inches x 0.400 inches width (20 watt module)

- . Weight 0.43 pound (20 watt module)

#### DESIGN TRADEOFF

The final configuration was arrived at after an extensive design trade-off process which concerned itself with four major areas:

- . Module thermal and electrical characteristics

- . Interface with the next higher level package

- . Mounting, interconnection, and line routing to the 3-inch diameter wafer or hybrid substrate

- . Module manufacturing processes and lid sealing

The trade-off process was concerned with configurations that provided for efficient heat removal while optimizing the interconnection and line routing requirements.

Conventional techniques (Figure 4) that make use of conductive cooling to heat exchangers at the card edge, were dismissed as being inefficient.

By mounting the heat exchanger directly behind the power dissipating elements (Figure 5), a more efficient thermal design with a considerably shorter conducting path is possible. This latter design, however, is deficient since it requires a 300-pin connector having high insertion and removal forces.

The integral ceramic heat exchanger design illustrated in Figure 1 retains the thermal advantages of direct cooling while eliminating the connector problem. The design provides for:

- . Zero insertion force connectors

- . Short line lengths

- . Direct connections eliminating the need for intermediate circuit boards

- . Integral heat exchanger

Table 1 summarizes the characteristics of the various design approaches.

## INTEGRAL HEAT EXCHANGER MODULE DESIGN

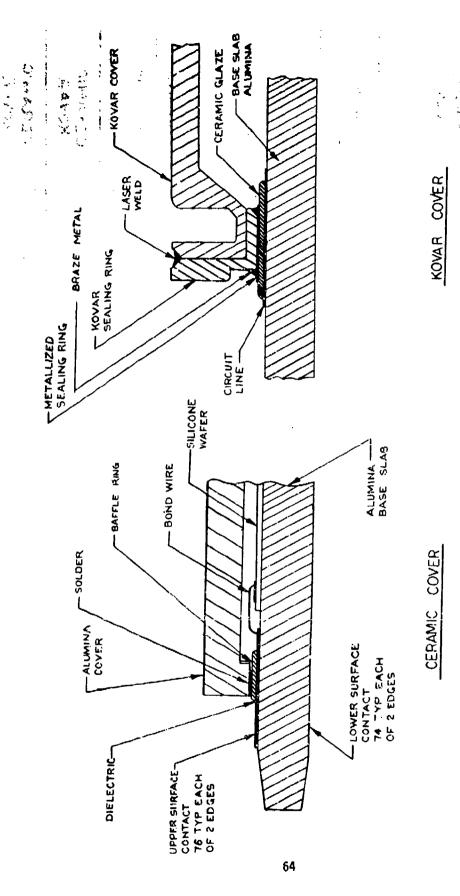

The integral ceramic heat exchanger unit consists of a ceramic slab containing the line routing from the 152-external connector pad terminations, along each of the two edges, to the 3-inch diameter wafer. A molybdenum-titanium metallized sealing ring facilitates hermetic sealing of a ceramic or Kovar cover. Keying pins, which guarantee a unique module location in the Higher Level Package are brazed to the base slab. External connections are made via a set of 152-Pin Cam Operated Connectors contacting the pads on .050 centers. The heat exchanger, who can be sized to be compatible with the power dissipation of the module, is cemented to the base slab.

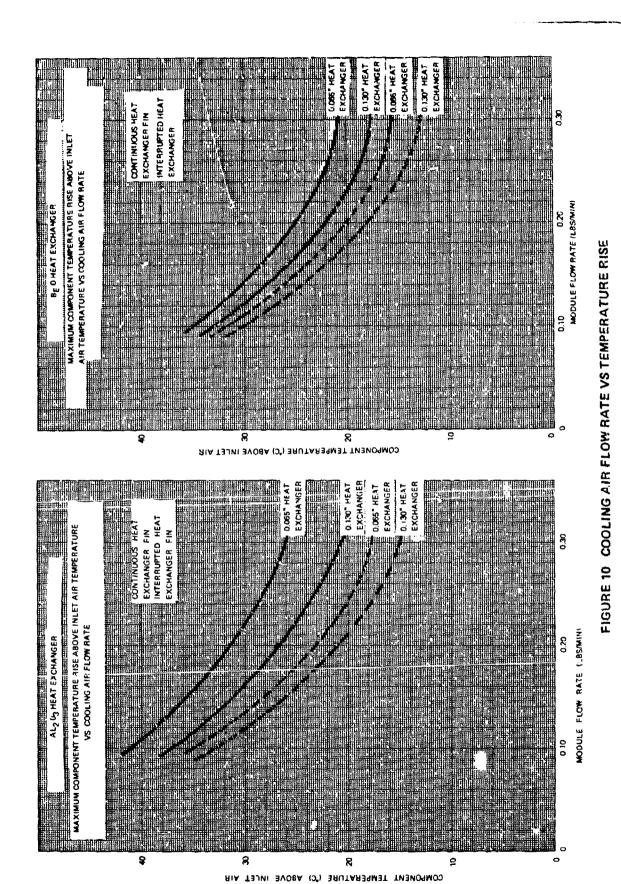

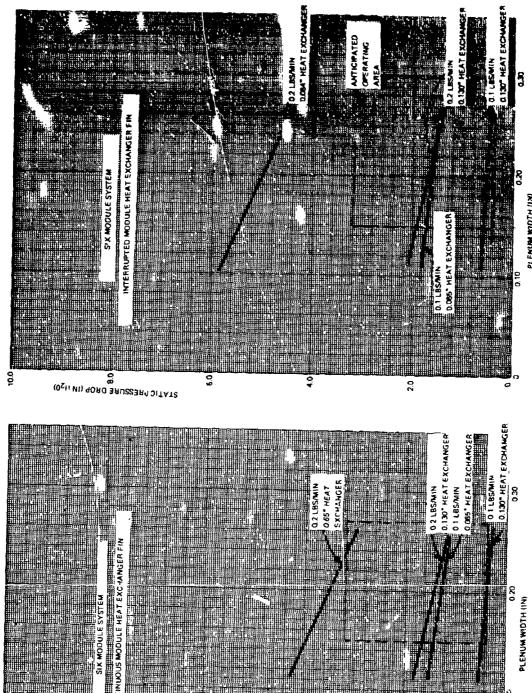

Table 2 summarizes the module's thermal characteristics for various material combinations, flow rates, and heat exchanger designs.

FIGURE 4 COMPUCTIVE COOLING CONFIGURATION

FIGURE 5 DIRECT COOLING CONFIGURATION

TABLE 1. MODULE DESIGN COMPANISON TABLE

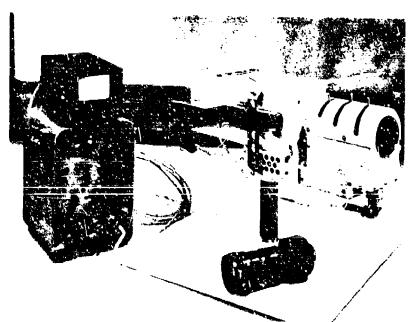

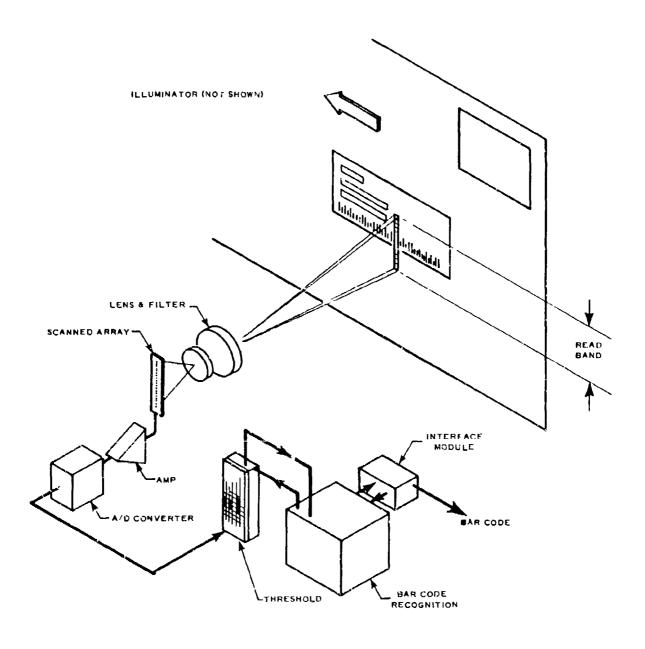

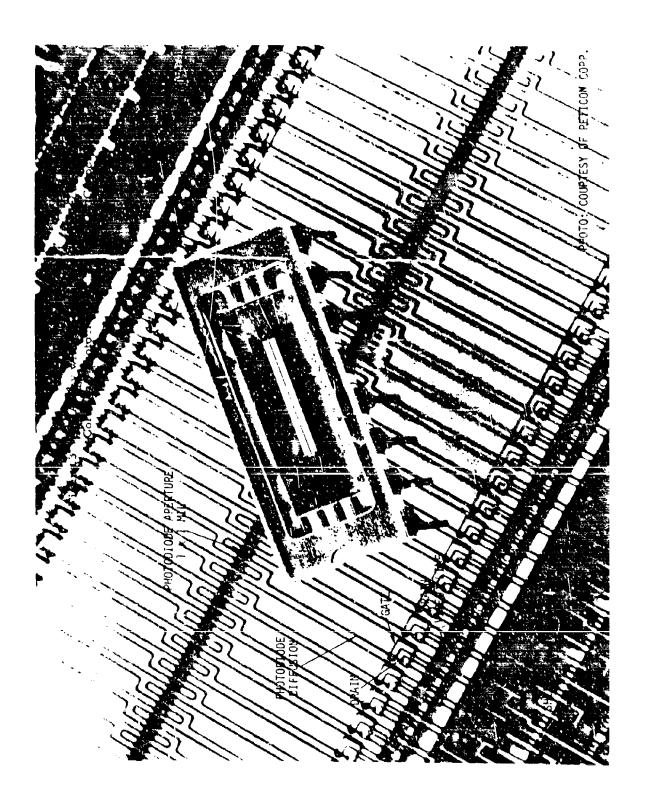

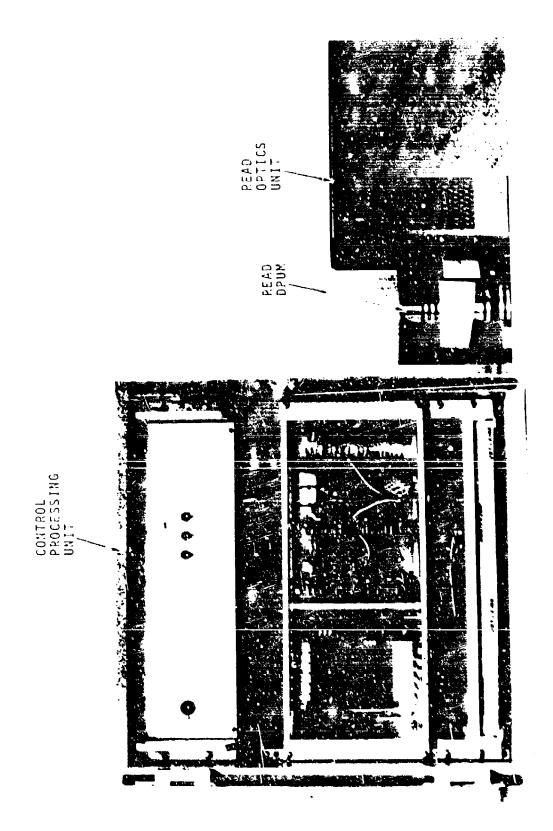

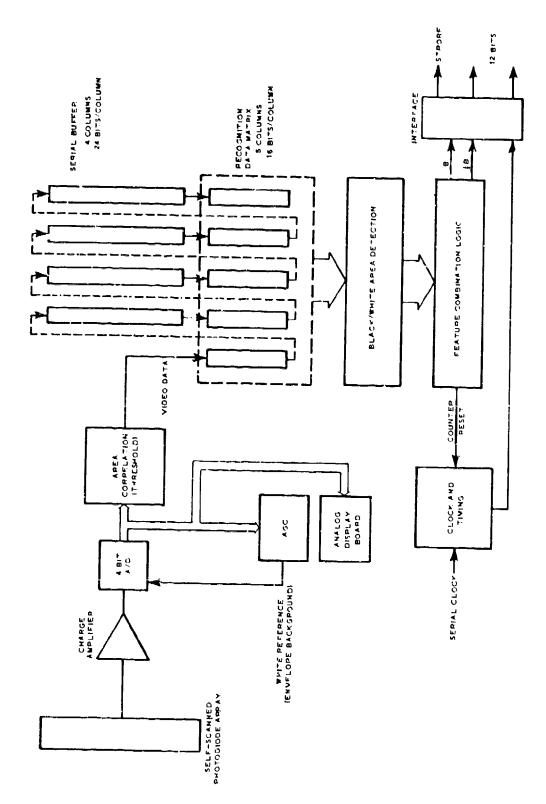

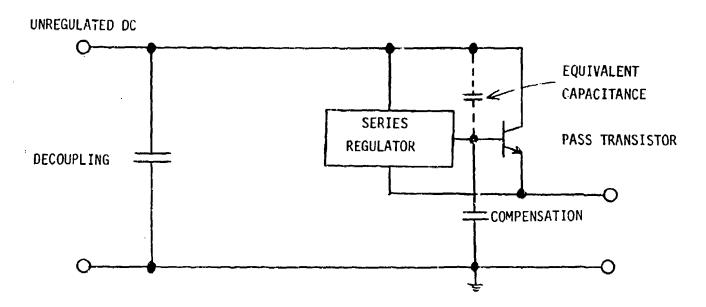

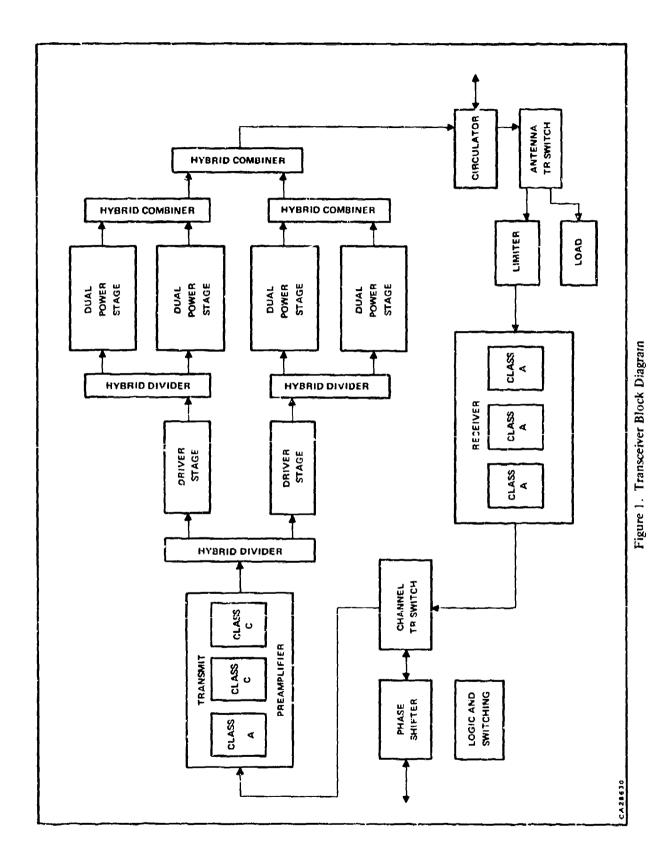

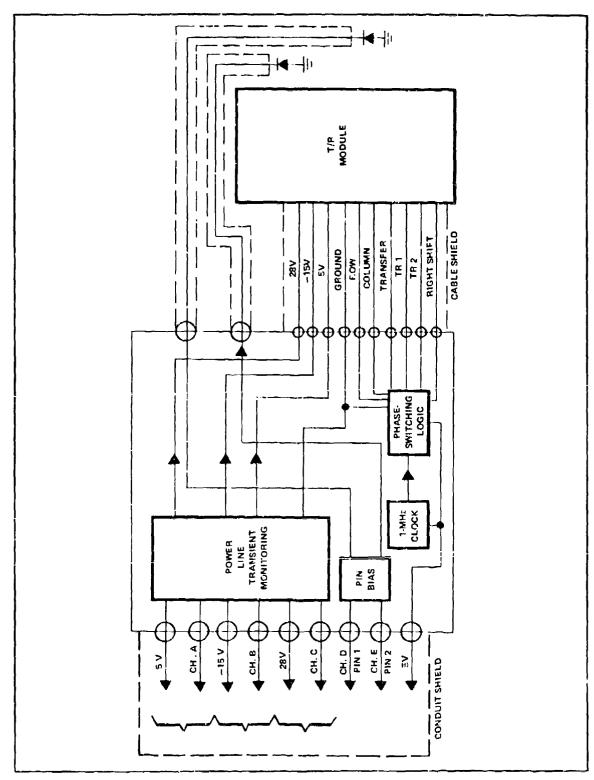

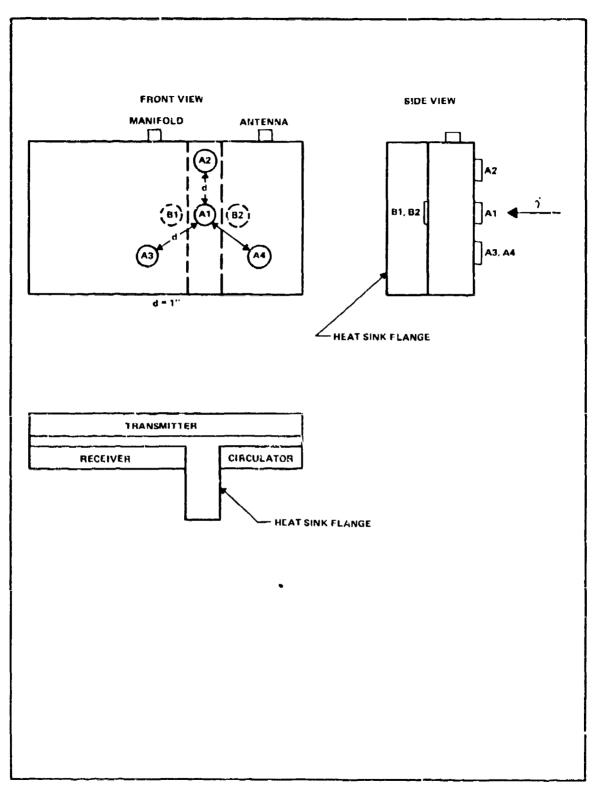

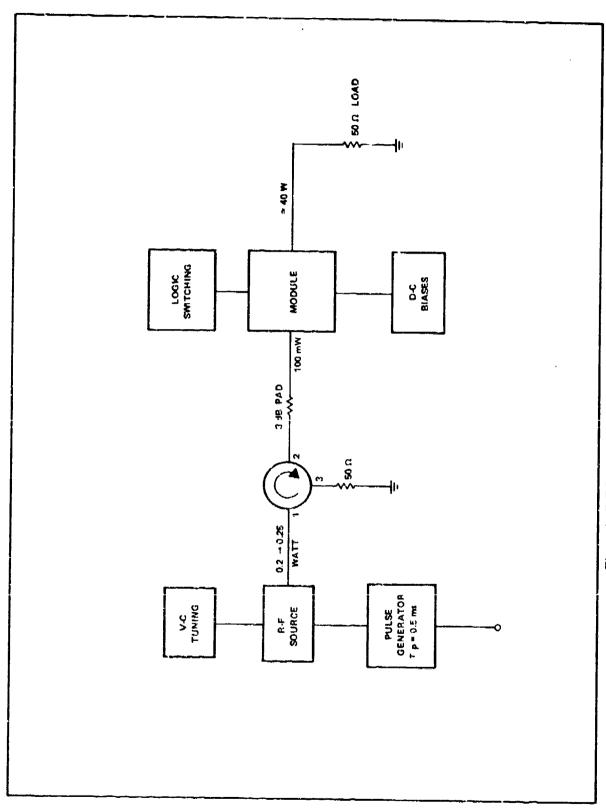

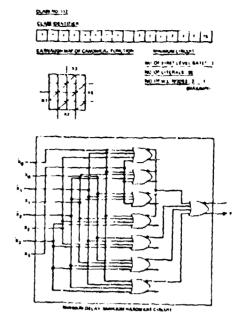

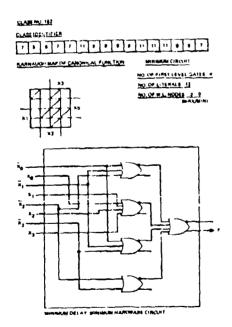

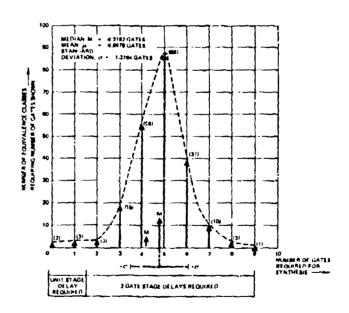

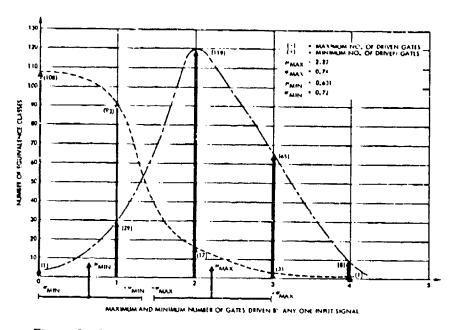

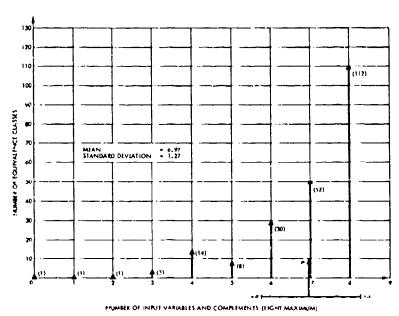

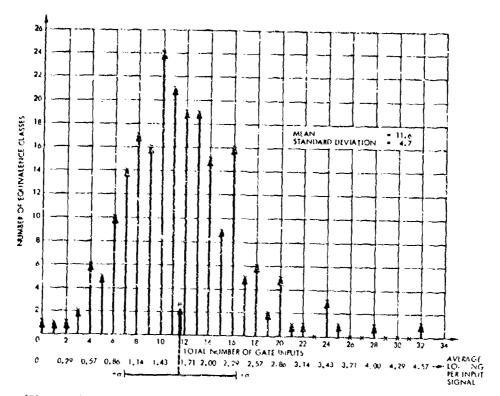

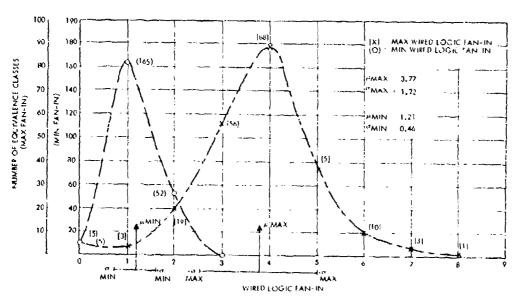

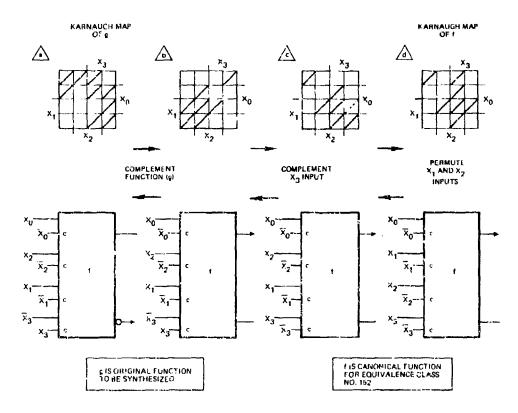

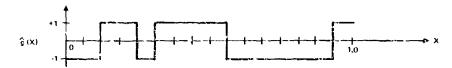

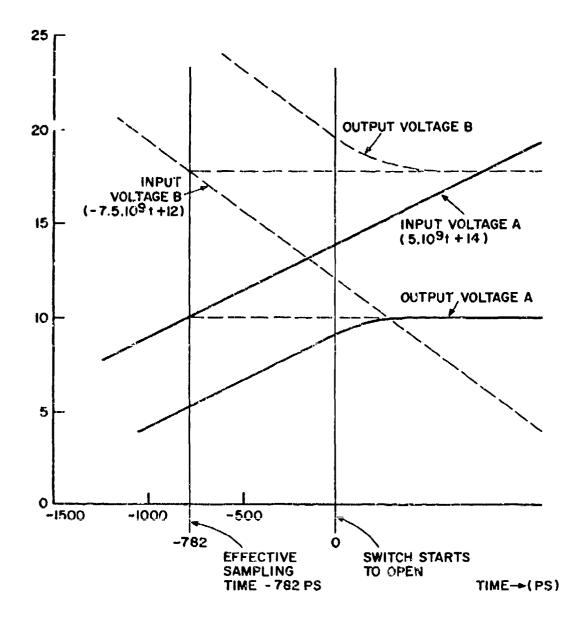

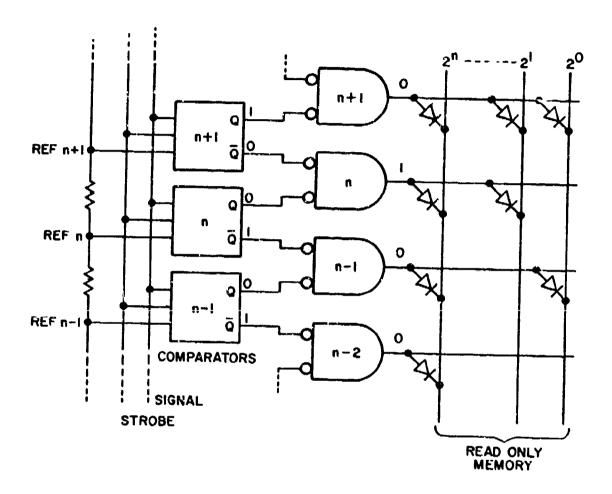

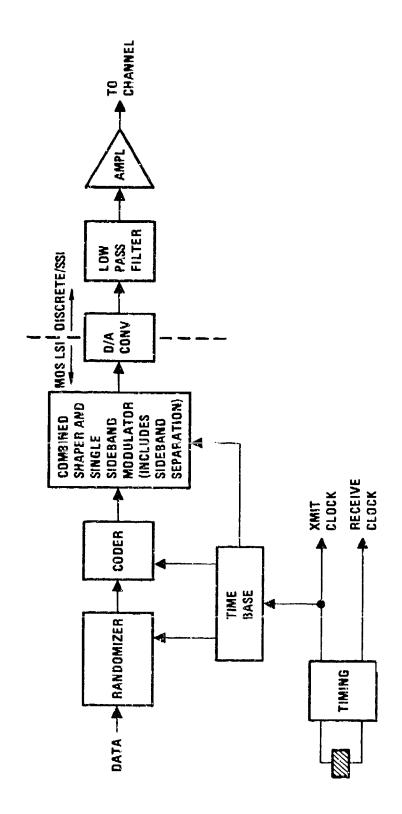

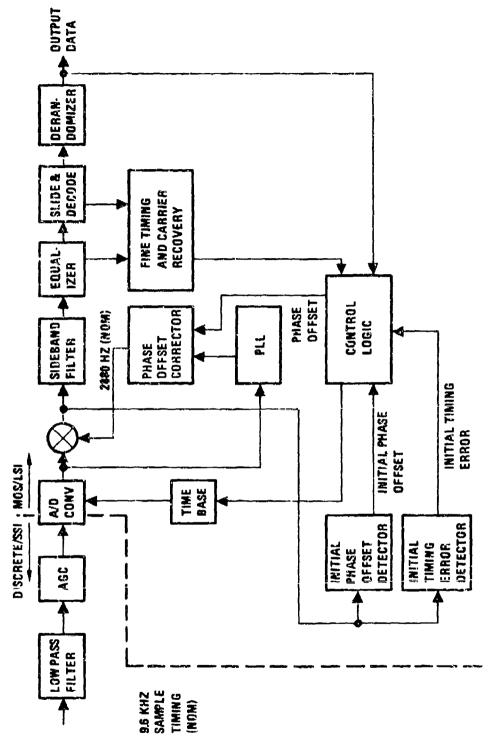

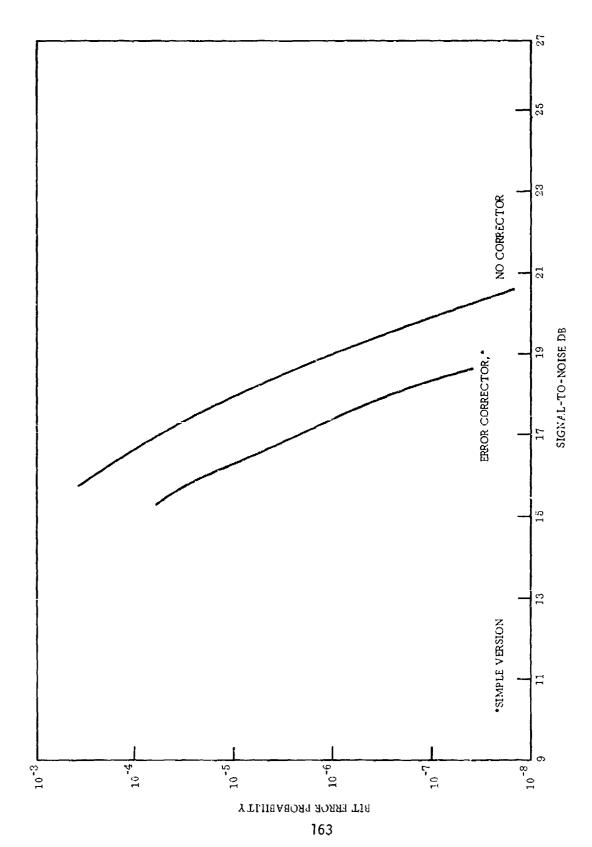

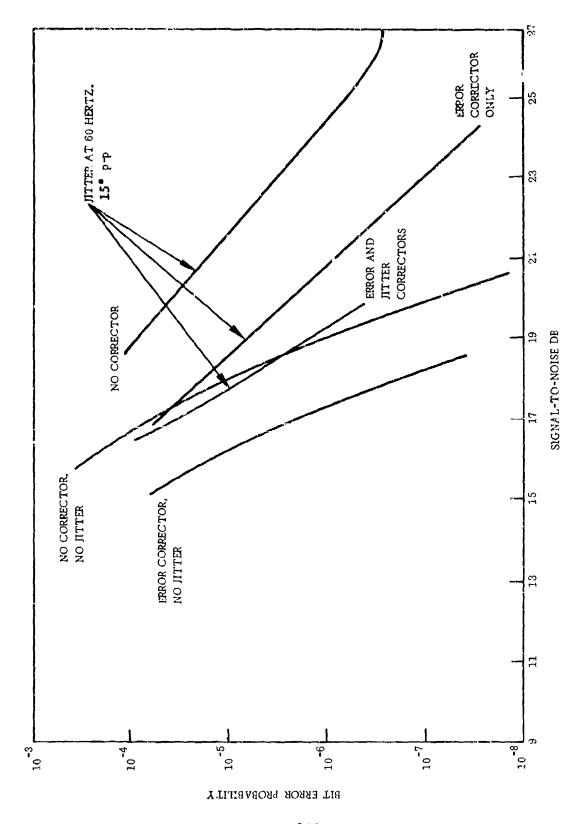

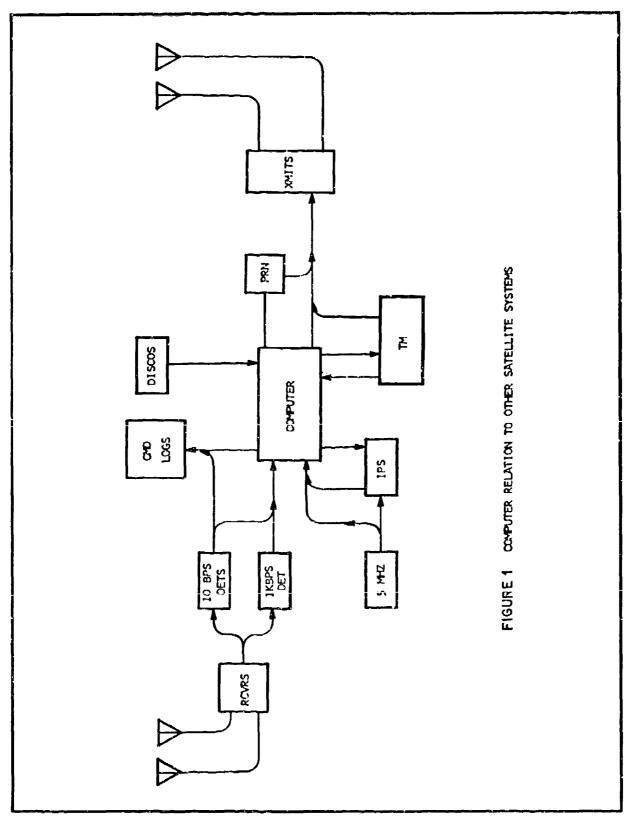

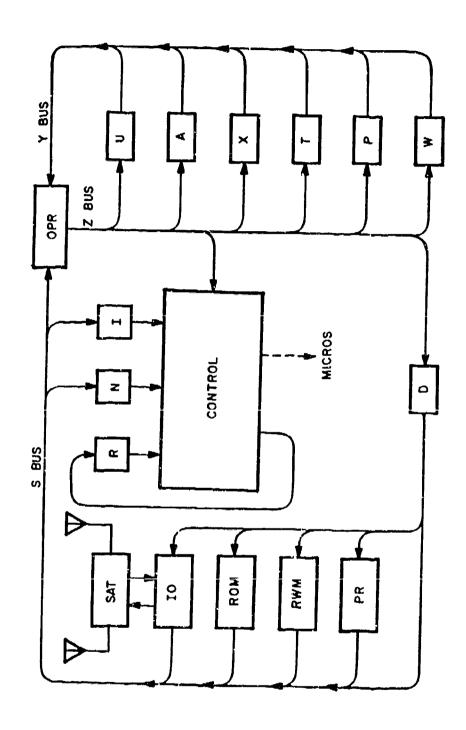

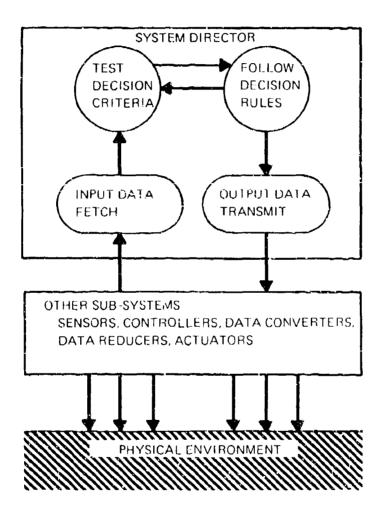

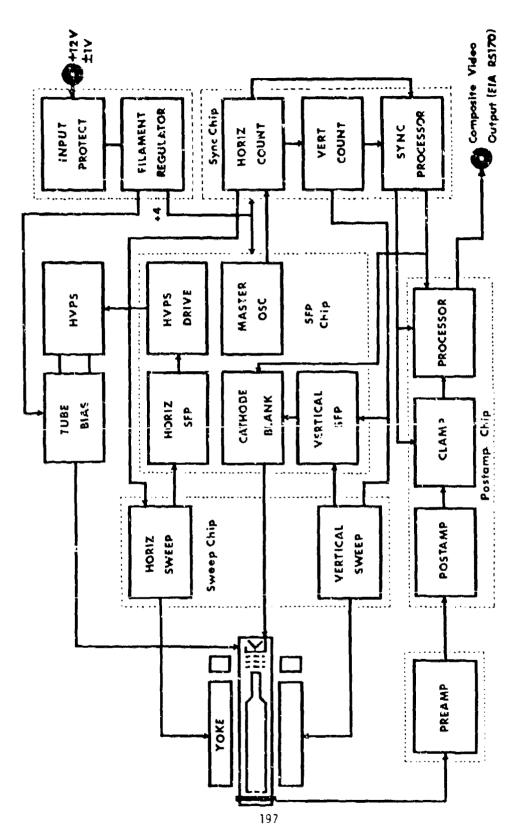

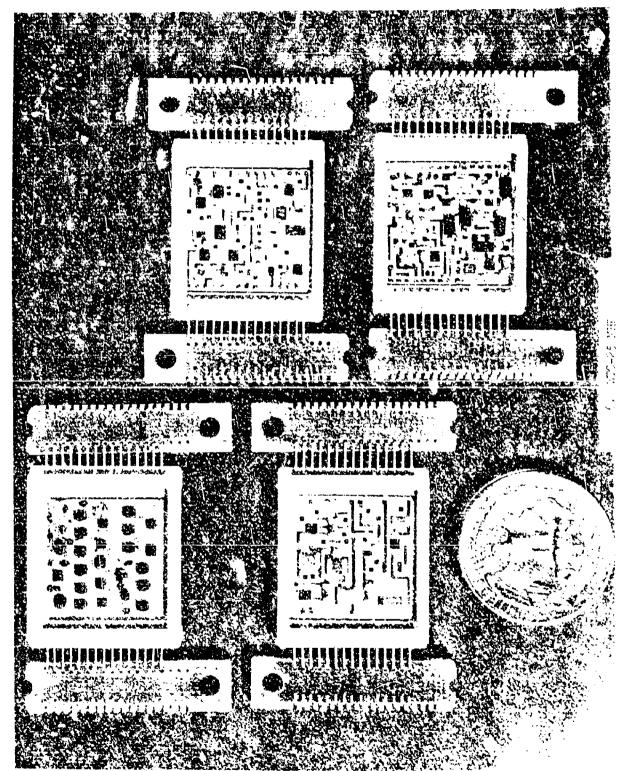

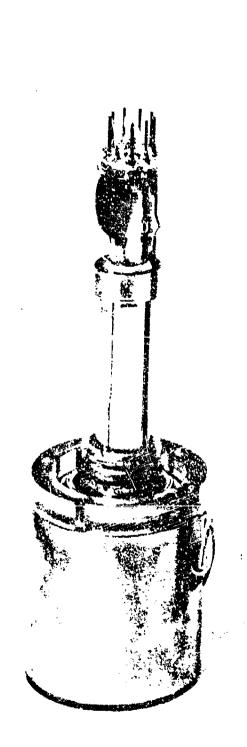

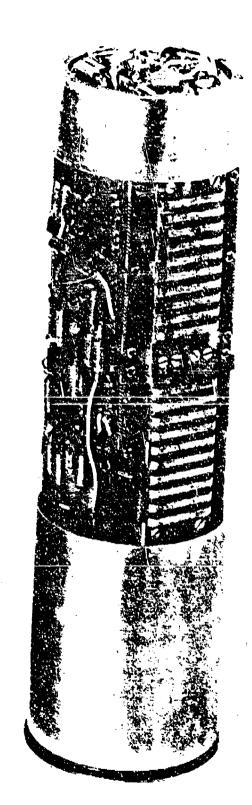

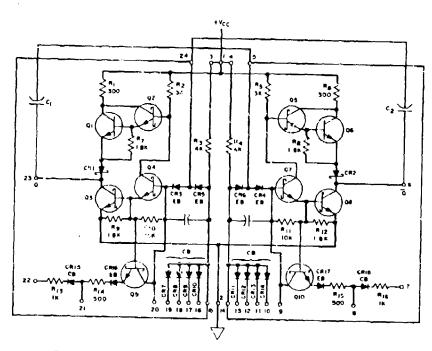

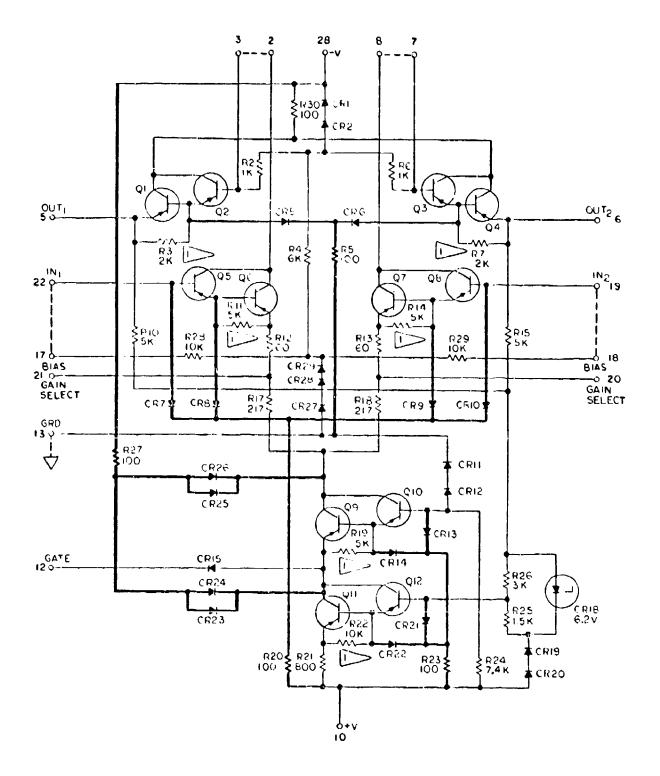

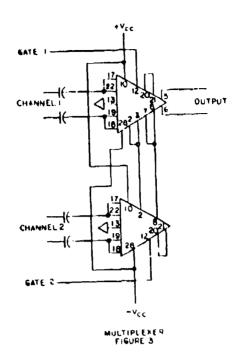

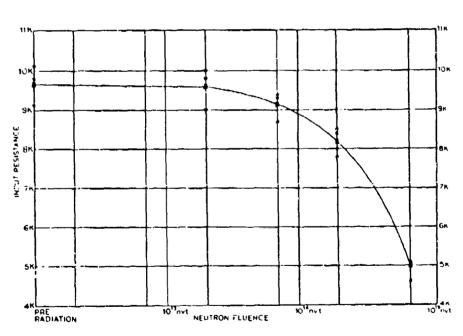

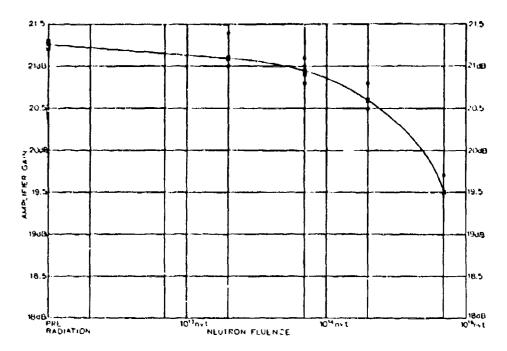

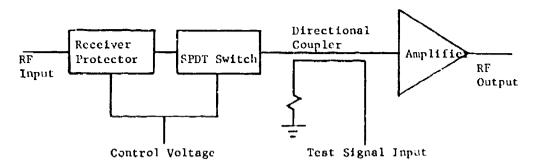

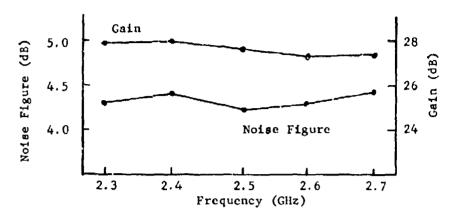

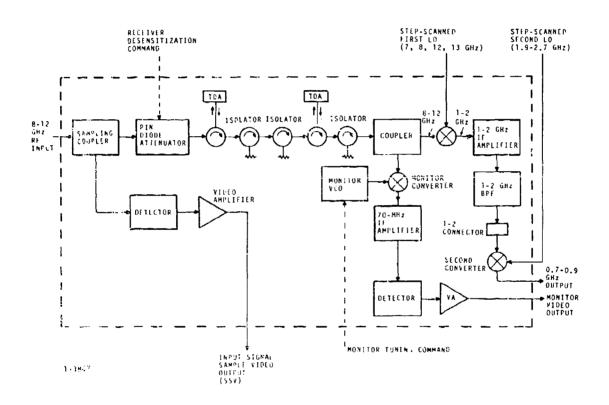

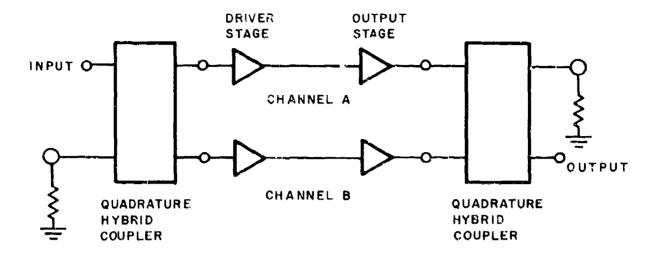

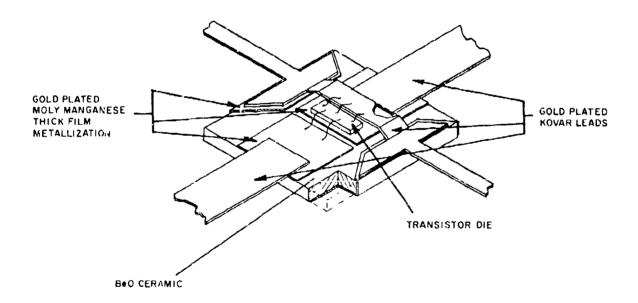

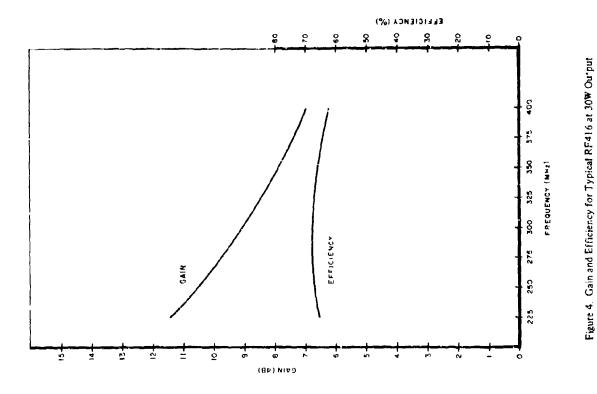

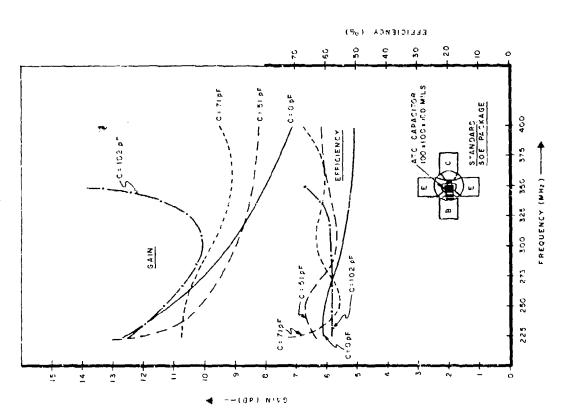

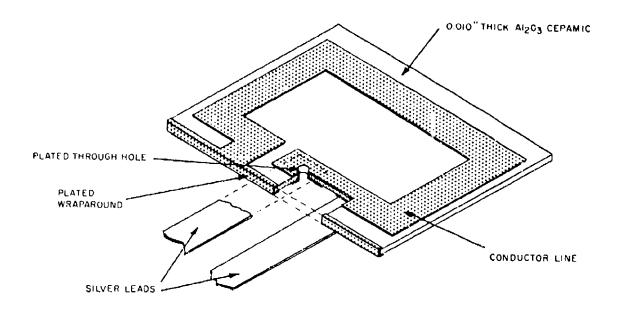

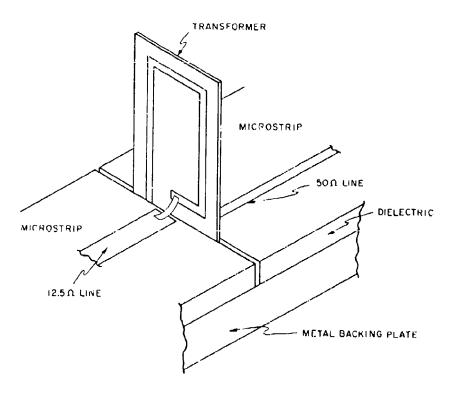

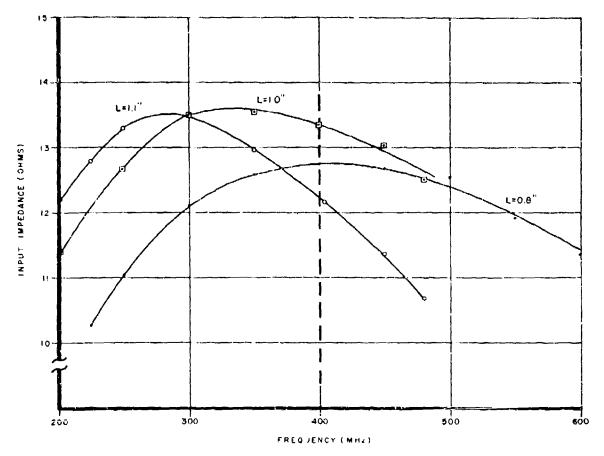

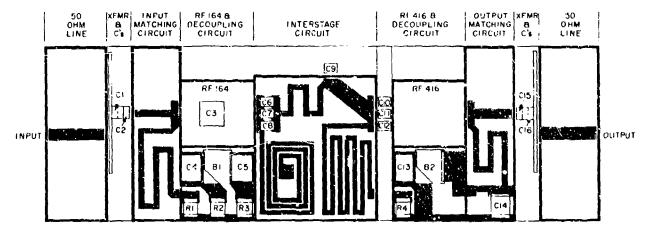

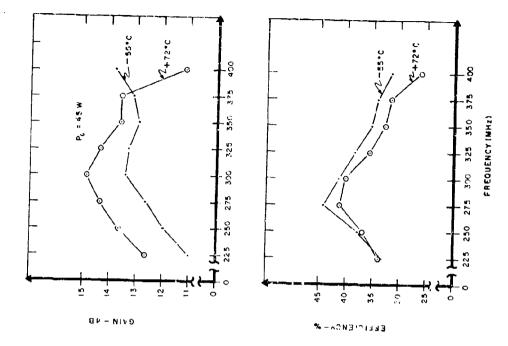

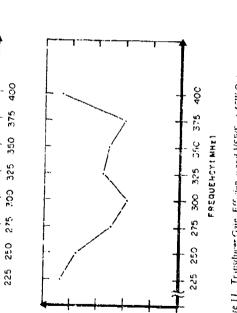

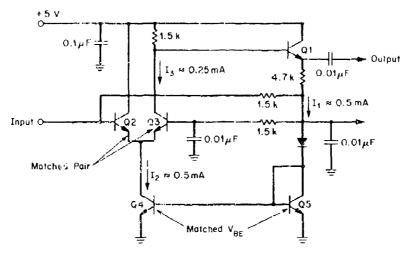

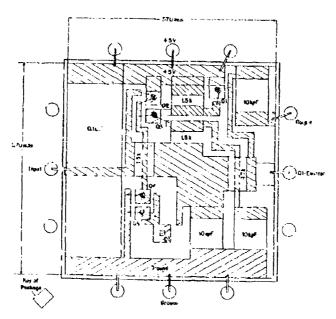

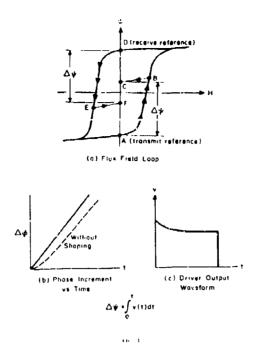

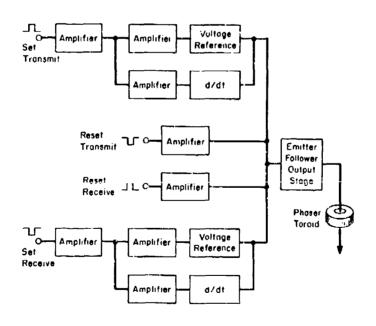

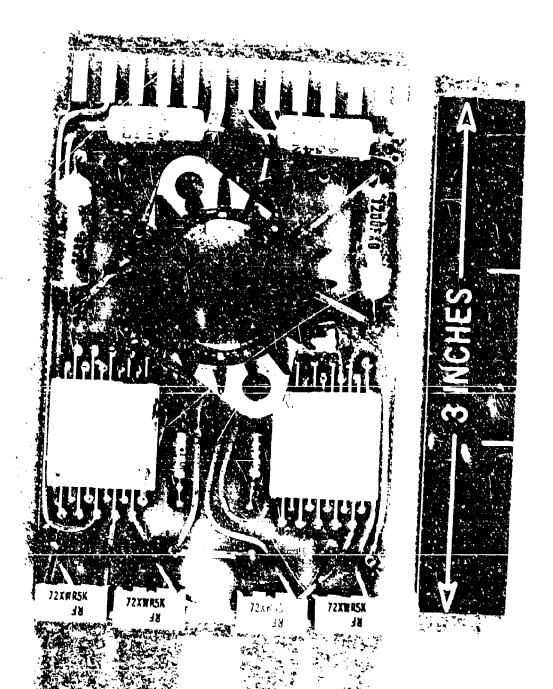

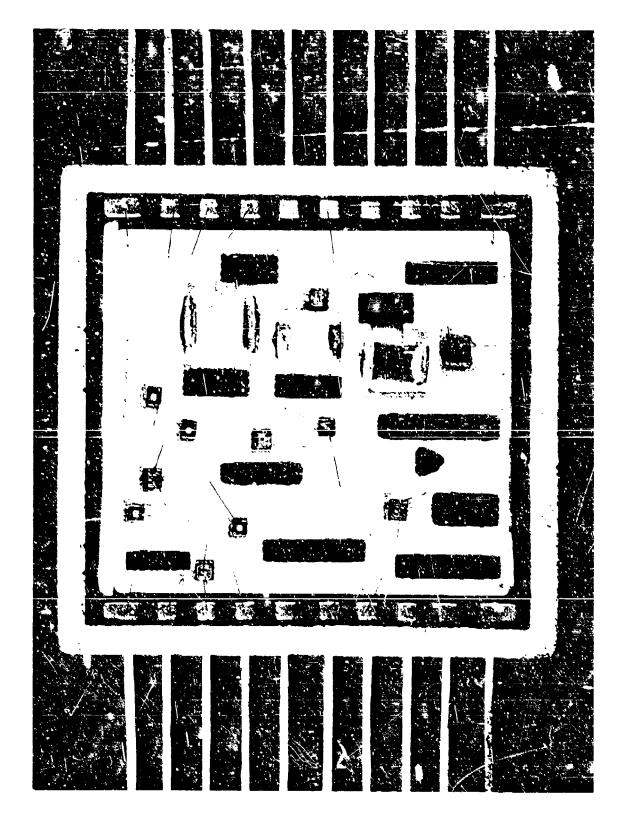

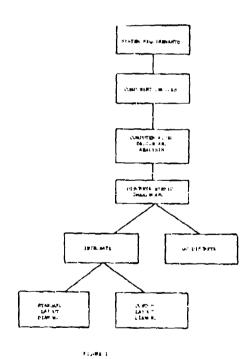

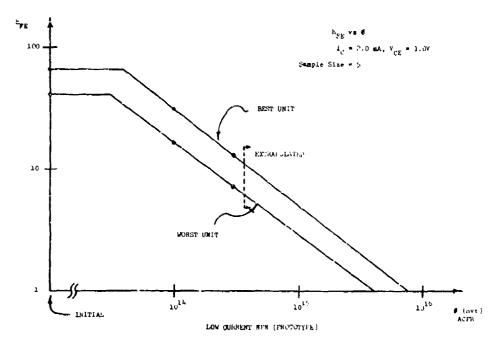

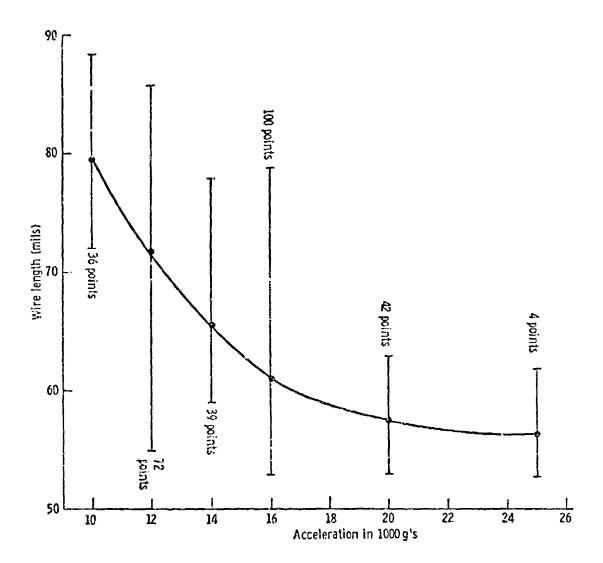

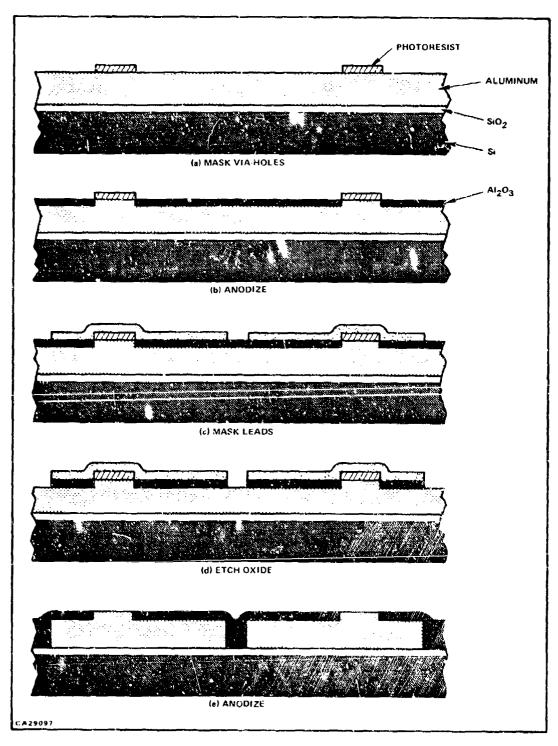

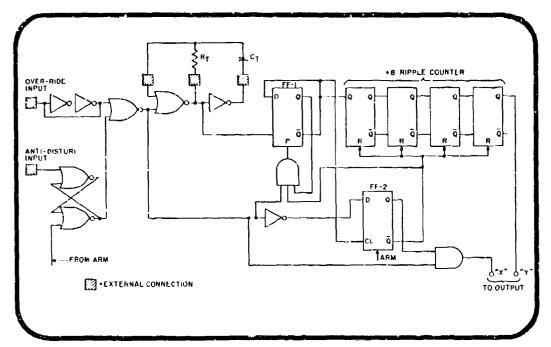

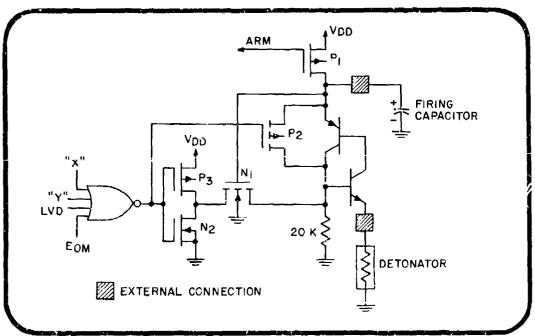

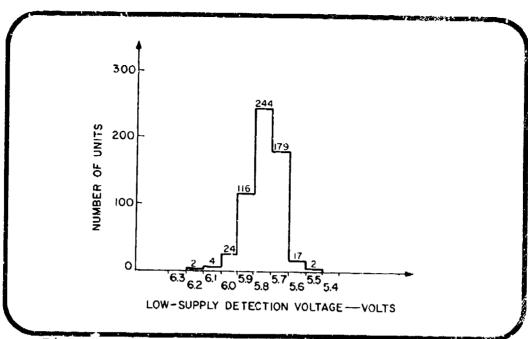

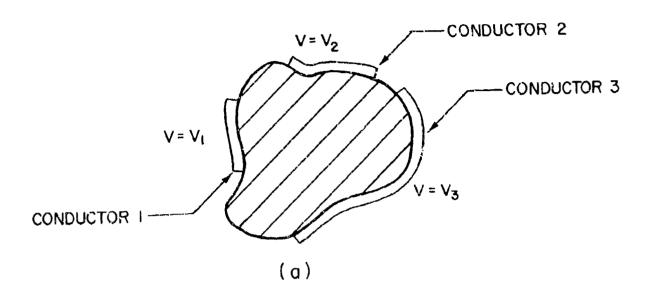

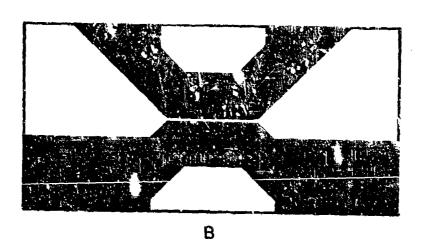

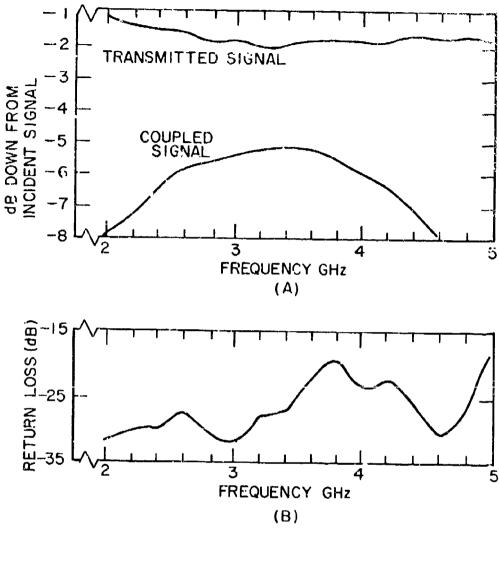

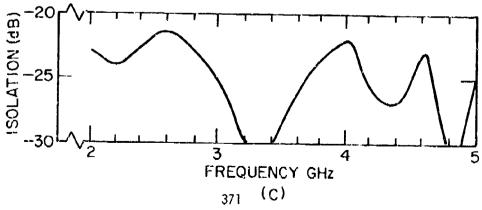

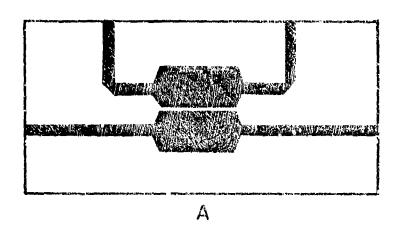

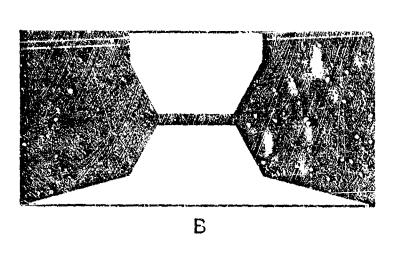

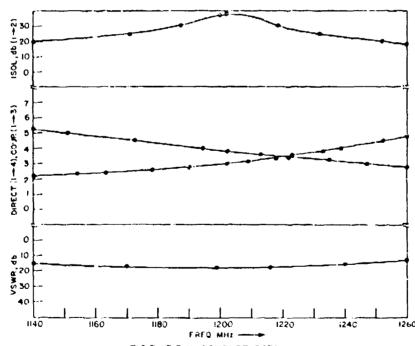

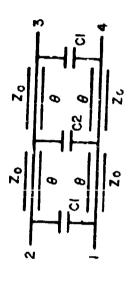

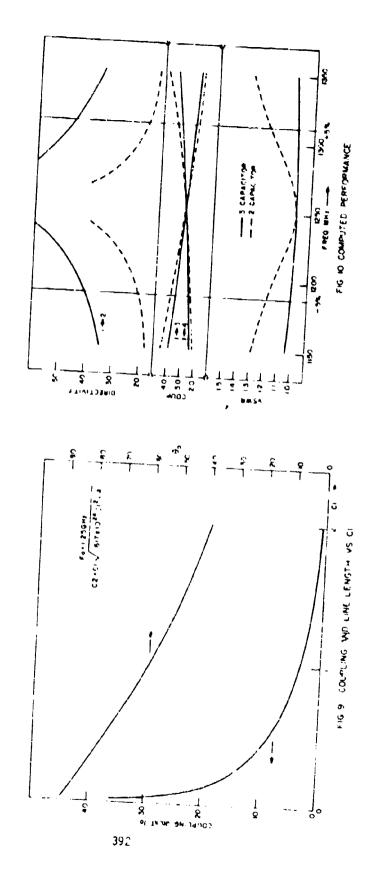

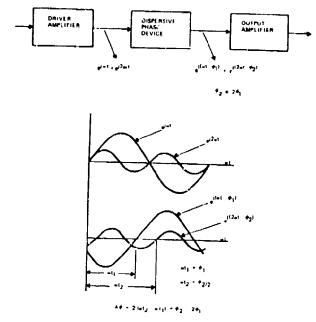

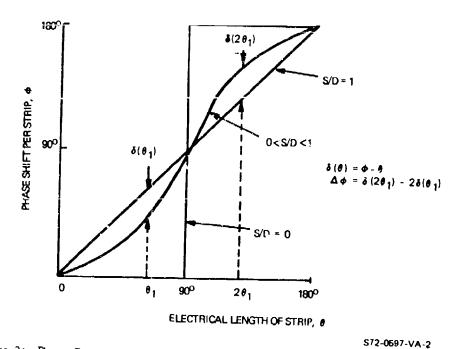

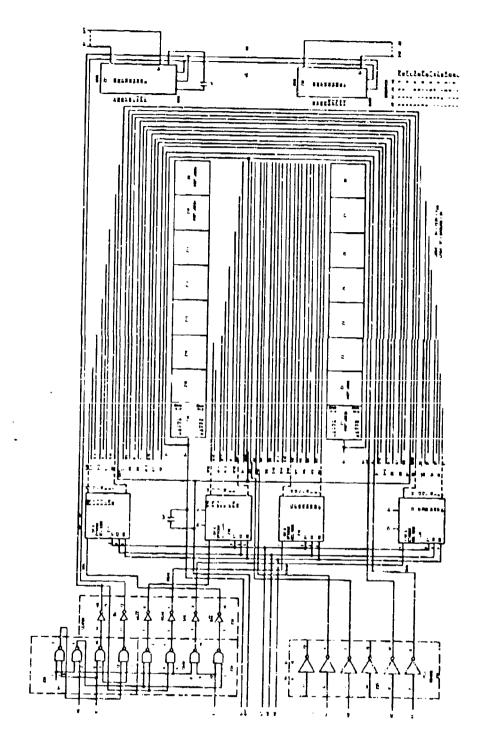

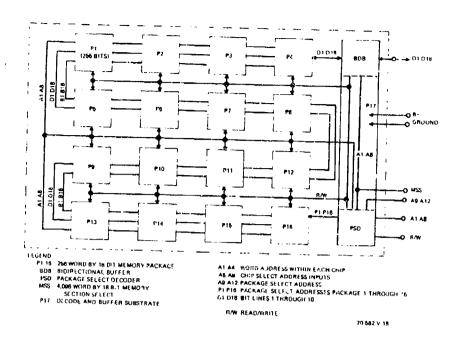

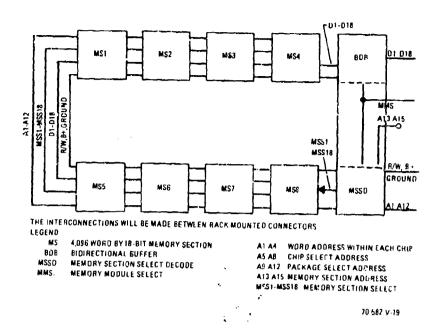

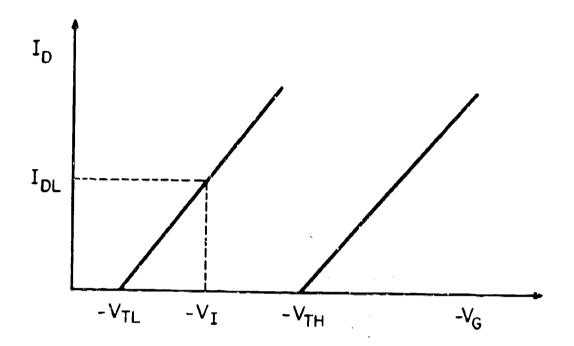

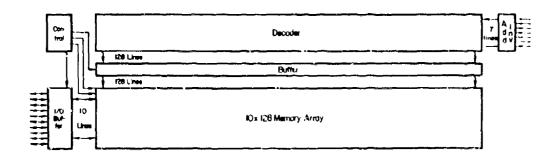

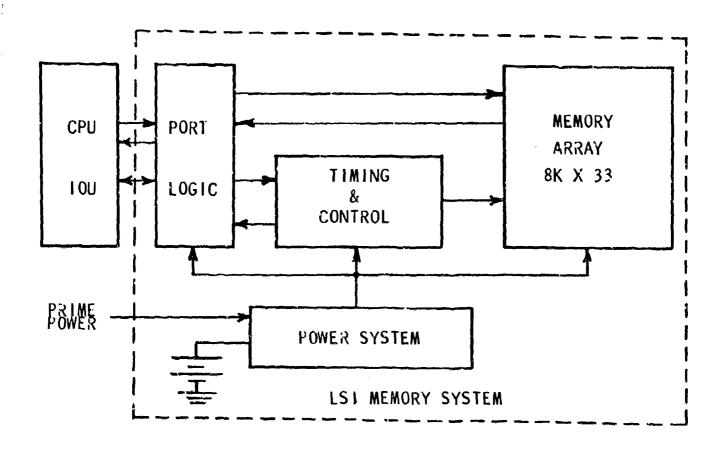

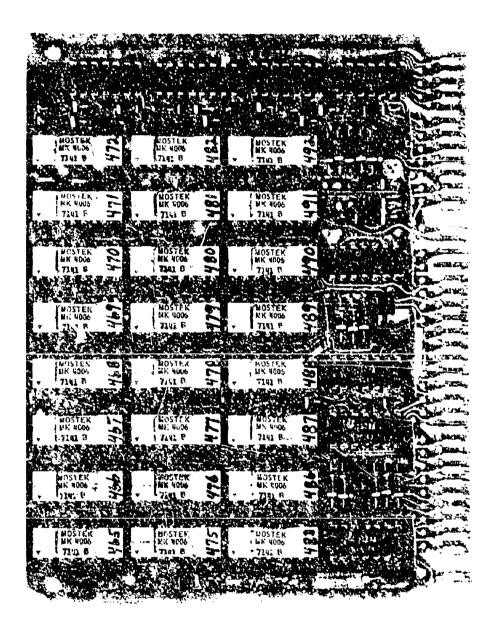

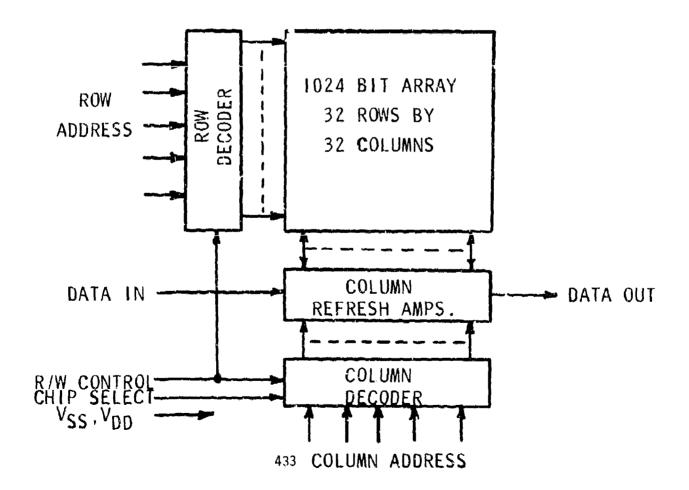

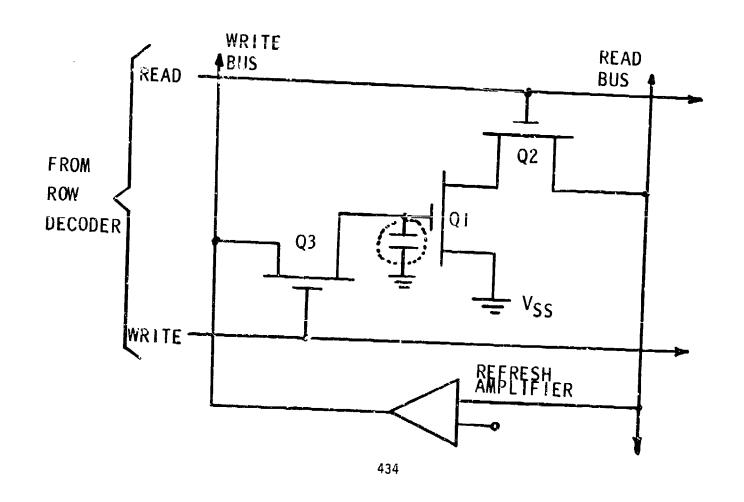

|        | HOHER LEVEL MOCKAGE 12 MODULE SYSTEM |                                            | APPROCIMENTE APPLOXIMATE YOURG WEIGHT | n.o.us.                                                         | 11.5.185.                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |