DEPARTMENT OF THE NAVY NAVAL UNDERSEA WARFARE CENTER DIVISION NEWPORT OFFICE OF COUNSEL (PATENTS) 1176 HOWELL STREET BUILDING 112T, CODE 00OC NEWPORT, RHODE ISLAND 02841-1708

PHONE: 401 832-4736 DSN: 432-4736

FAX: 401 832-1231 DSN: 432-1231

Attorney Docket No. 96276 Date: 3 November 2005

The below identified patent application is available for licensing. Requests for information should be addressed to:

PATENT COUNSEL NAVAL UNDERSEA WARFARE CENTER 1176 HOWELL ST. CODE 00OC, BLDG. 112T NEWPORT, RI 02841

Serial Number 11/217,846

Filing Date

DISTRIBUTION STATEMENT A Approved for Public Release Distribution Unlimited

Inventor Jeremy R. O'Neal

24 August 2005

If you have any questions please contact James M. Kasischke, Supervisory Patent Counsel, at 401-832-4230.

Attorney Docket No. 96276 2 DELAY LOOP CORRECTION FOR PROGRAMMABLE CONTROLLERS 2 4 STATEMENT OF GOVERNMENT INTEREST 5 The invention described herein may be manufactured and 6 used by or for the Government of the United States of America 7 for Governmental purposes without the payment of any royalties 8 9 thereon or therefore. 10 BACKGROUND OF THE INVENTION 11 (1) Field of the Invention 12 The present invention generally relates to programmable 13 controllers and more specifically to correcting delay time 14 15 errors caused by temperature and voltage changes. 16 (2) Description of the Prior Art Electronic systems derive their functionality from 17 programmable controllers such as microprocessors, FPGAs, CPLDs, 18 19 or ASICs. The heart of any programmable system is the clock or oscillator because it tells the system when to execute its 20 instructions. 21 22 Most oscillators exhibit non-uniform frequencies throughout their temperature range. This means that the speed in which an 23 24 electronic system operates will vary depending on its

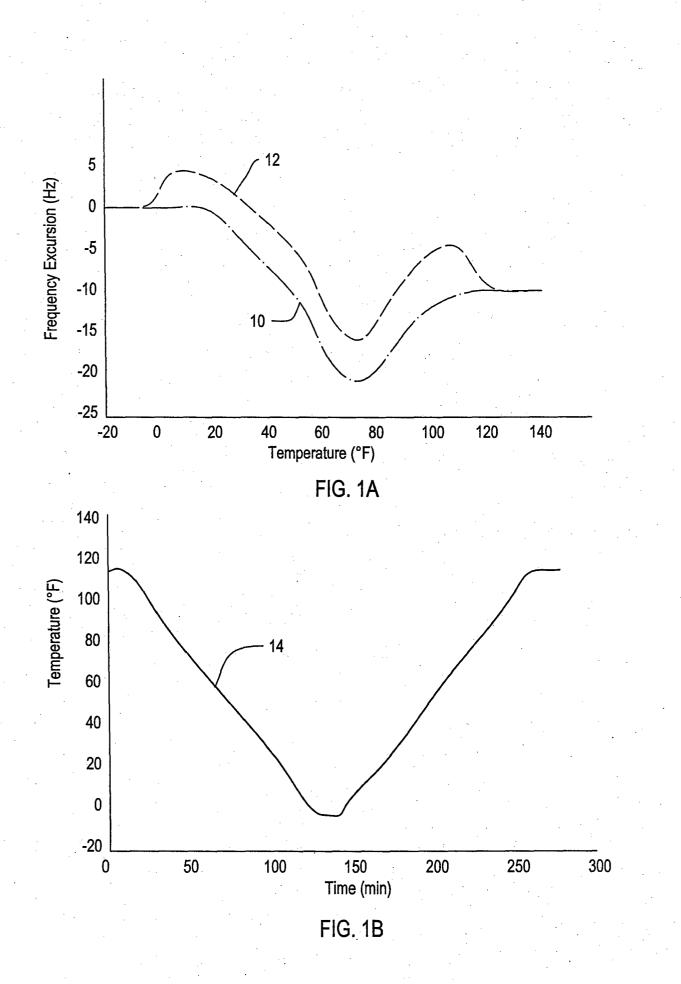

temperature. This is an undesirable condition which causes 1 synchronization and/or other timing errors. FIG. 1A shows the 2 3 frequency excursion from the normal operating frequency versus temperature. Curve 10 shows the excursion when the temperature 4 is declining, and curve 12 shows the excursion when the 5 temperature is increasing. As evident from FIG. 1A, these 6 oscillators not only exhibit frequency variability with respect 7 to temperature, they also display hysteresis when subjected to 8 9 ascending or descending temperatures. 10 These curves were obtained utilizing a temperature controlled oscillator (TCXO) such as the 566Y4995 oscillator 11 12 manufactured by Vectron International whose nominal operating 13 frequency is stated to be 27 MHz plus or minus 5 parts per 14 million (ppm). The temperature data was gathered from a Dallas 15 Semiconductor temperature chip mounted next to the oscillator on a printed circuit board (PCB). FIG. 1B shows the temperature 16 17 versus time profile giving these results. It is also well known that oscillators exhibit timing 18

19 variance based on input voltage. Similar graphs could be 20 obtained by subjecting an oscillator to a time varying input 21 voltage.

Therefore, any electronic system using this oscillator would exhibit timing variance depending on its environment. This variance is compounded as timing offsets tend to be

1 cumulative. For example, if a system designed to be synchronized to a referenced one second time period is off by 2 one millisecond per second, after ten seconds, the 3 synchronization will be off by ten milliseconds, and after one 4 minute the synchronization will be off by 60 milliseconds. 5 Processors and programmable controllers use loops and/or 6 timers to create delays in electronic systems. A loop is simply 7 a large number of instruction cycles that the controller must 8 execute before moving on to its next portion of code. A timer 9 10 can also be used to achieve this by counting to certain preset. number before moving on. If the clock or oscillator is not .11 operating at the correct frequency, these delays will either be 12 too long or too short. 13

To solve this problem, instruction cycles can be added or 14 subtracted from the delays depending on the temperature of the 15 oscillator. For example, if the clock frequency is 10 hertz too 16 slow at some temperature, a calculated number of instruction 17 cycles can be subtracted from the current code so as to speed up 18 the execution time by 10 hertz. The net frequency difference 19 would therefore be 0 hertz resulting in no error. The number of 20 21 instruction cycles needed to remove the frequency error can be calculated from the following: 22

23 Adjustment  $Val(temp) = [f_{CLK}(temp) \times delay(s)] - [Number of cycles in delay] (1)$  $24 where <math>f_{CLK}$  is the frequency of the oscillator,

temp is the temperature of the oscillator,

1

2

3

4

5

delay is the desired time delay of the software loop, and Number of cycles in delay is the calculated number of instruction cycles needed to create the delay (assuming perfect clock frequency).

The prior art acknowledges that oscillators and clock chips 6 have problems with maintaining a stable frequency under changing 7 8 temperature conditions. Richards et al., U.S. Patent No. 9 4,684,897 teach a frequency correction apparatus having a delay 10 line fed by an input signal, the frequency of such signal being corrected a predetermined amount,  $\Delta_f$ . The delay line has a 11 plurality of output taps regularly disposed along the line. The 12 13 output taps produce a plurality of successively time-delayed 14 signals each one having the frequency of the input signal. A 15 switching network is included for successively coupling each one 16 of the plurality of time-delayed signals to an output terminal 17 of a predetermined coupling change rate related to  $\Delta_{f}$ , to produce, at such output terminal, an output signal having a 18 19 frequency shifted from the frequency of the input signal the predetermined amount required for the desired frequency 20 21 correction. When the taps are successively coupled to the output 22 terminal in a direction along the delay line away from the input 23 to such line, the frequency of the output signal is equal to the frequency of the input shift shifted lower in frequency the 24

amount  $\Delta_f$ . On the other hand, when the taps are successively 1 coupled in a direction towards the line input, the frequency of 2 the output signal is shifted higher in frequency the amount  $\Delta_f$ . 3 Moller et al., U.S. Patent No. 5,644,271 teach a 4 temperature compensation system includes a first oscillator to 5 generate a number of pulses which vary from a desired frequency 6 as a function of temperature of the first oscillator. The system 7 also includes a second oscillator to generate digital pulses at 8 a corrective frequency which is greater than the desired 9 10 frequency. A sensor provides a temperature signal for the first oscillator. A digital memory has a digital error table 11 addressable by a signal corresponding to the temperature signal 12 to provide a number of pulse errors corresponding to temperature 13 error for each of the number of pulses. Each pulse error is a 14 function of the corrective frequency and a temperature versus 15 frequency characteristic of the first oscillator. An accumulator 16 receives each pulse error to generate a cumulative error 17 corresponding to one of the number of pulses. A variable delay 18 device counts a quantity of corrective pulses from second 19 20 oscillator to provide a delayed output pulse in accordance with the desired frequency. The quantity of corrective pulses is a 21 function of the cumulative error signal received from the 22 23 accumulator. The converter, memory, accumulator and delay device may be part of a microcontroller. 24

| 1  | While these patents teach corrective actions for oscillator      |

|----|------------------------------------------------------------------|

| 2  | excursion caused by temperature variations, they do not teach    |

| 3  | correcting for hysteresis or for correcting delay times by       |

| 4  | adding instruction cycles.                                       |

| 5  |                                                                  |

| 6  | SUMMARY OF THE INVENTION                                         |

| 7  | Therefore, it is an object of the present invention to           |

| 8  | provide a system that computes delay cycles for a processor      |

| 9  | based on a parameter.                                            |

| 10 | It is a further object of the present invention to compute       |

| 11 | delay cycles for a processor when the oscillator variation is    |

| 12 | subject to hysteresis.                                           |

| 13 | It is yet another object of the present invention to             |

| 14 | compute delay cycles when a fractional delay cycle is required.  |

| 15 | Accordingly, the current invention provides an apparatus         |

| 16 | computing a correction value for a processor delay. At least     |

| 17 | one parameter sensor measures a system parameter influencing the |

| 18 | oscillator. A lookup table determines a cycle adjustment value   |

| 19 | based on the system parameter. A processor joined to the         |

| 20 | oscillator implements the cycle adjustment value to correct for  |

| 21 | oscillator variation. Cycle adjustment values can be computed    |

| 22 | in both whole cycles and partial cycles through accumulated      |

| 23 | error thresholding. The parameter sensor can be a temperature    |

| 24 | sensor, a voltage sensor or both kinds of sensors. The lookup    |

|    |                                                                  |

table and processor can have additional terms to account for

hysteresis in the oscillator.

3

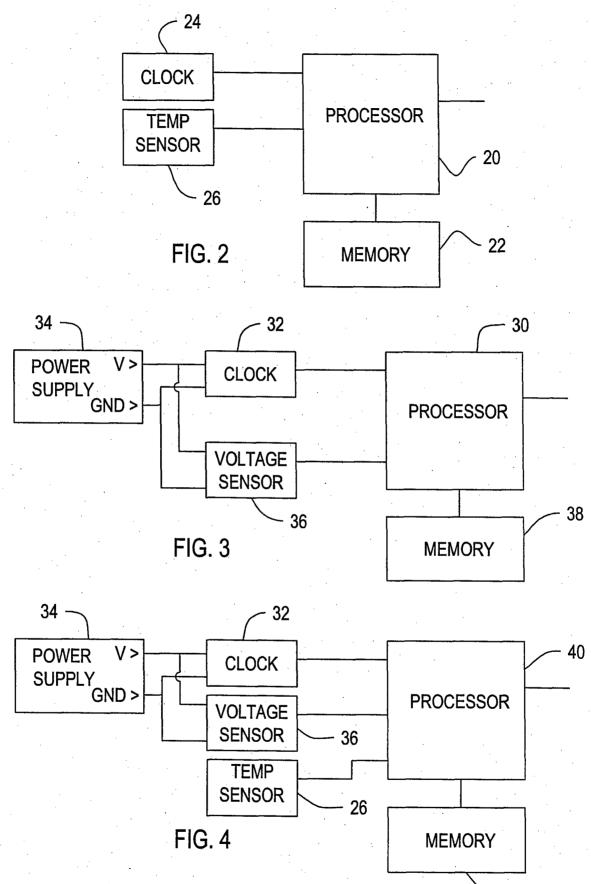

BRIEF DESCRIPTION OF THE DRAWINGS 4 5 The appended claims particularly point out and distinctly claim the subject matter of this invention. The various objects б advantages and novel features of this invention will be more 7 8 fully apparent from a reading of the following detailed description in conjunction with the accompanying drawings in 9 which like reference numerals refer to like parts, and in which: 10 FIG. 1A is a graph showing frequency excursion versus 11 temperature for an oscillator subjected to increasing and 12 decreasing temperatures; 13 14 FIG. 1B is a graph showing the temperature versus time test profile for obtaining the graph of FIG. 1A; 15 FIG. 2 is a block diagram of an embodiment of the invention 16 17 correcting for temperature variations; FIG. 3 is a block diagram of an embodiment of the invention 18 19 correcting for power supply voltage variations; 20 FIG. 4 is a block diagram of an embodiment of the invention correcting for both temperature and power supply voltage 21 variations; 22 FIG. 5 is pseudo code for a first order embodiment of the 23 24 current invention;

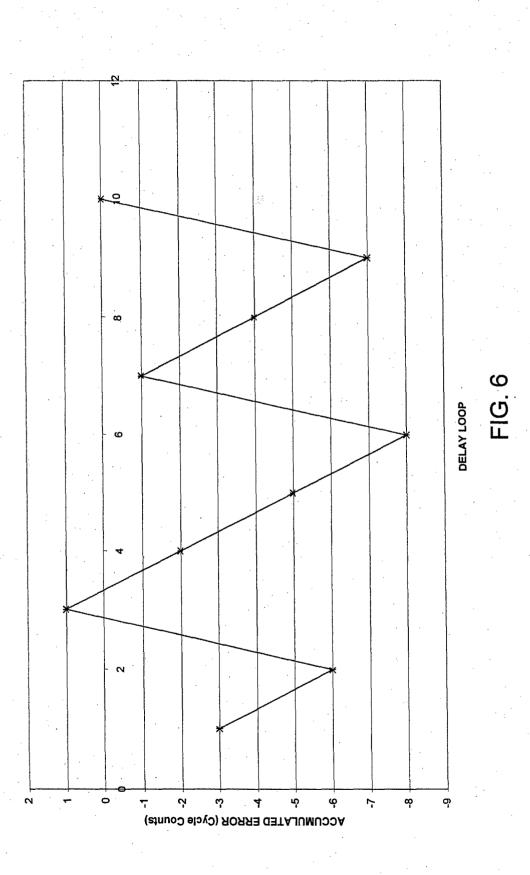

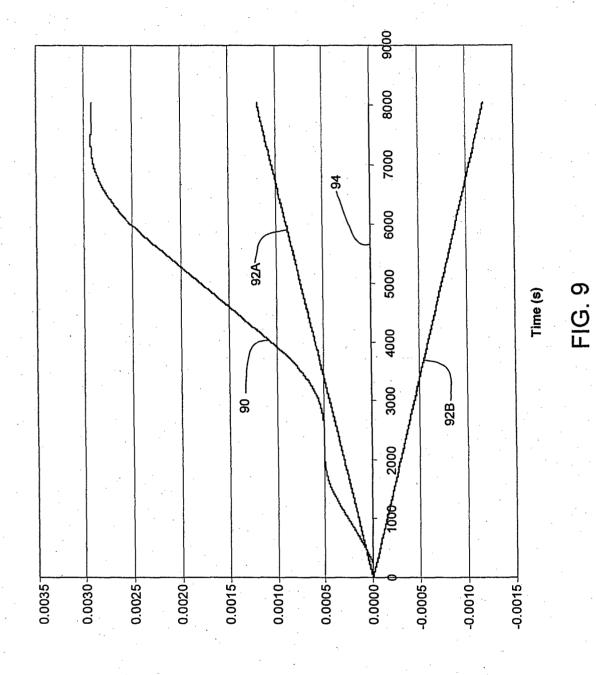

FIG. 6 is a graph showing the results of a simulation of 1 2 error versus delay loops; FIG. 7 is a graph of a test comparing the error with 3 accumulated error thresholding, the maximum error and error 4 5 without using accumulated error thresholding; FIG. 8 is pseudo code for a second order embodiment of the 6 current invention; and 7 FIG. 9 is a graph of a simulation comparing the error with 8 9 second order accumulated error thresholding, the maximum error and error without using accumulated error thresholding. 10 11 12 DESCRIPTION OF THE PREFERRED EMBODIMENT 13 FIG. 2 shows a first embodiment of a generic system 14 utilizing this invention to adjust delay times in a processor 15 20. While processor 20 can be a programmable controller, a digital signal processor, a field programmable gate array or any 16 17 other digital processor, these devices are generically called a "processor" for purposes of describing this system. 18 Processor 20 is in communication with non-volatile memory 22. 19 In the 20 practical application discussed below, the processor 20 is a 21 TMS320c31 digital signal processor manufactured by Texas 22 Instruments. Non-volatile memory 22 is integral memory located 23 on the processor chip. Processor 20 is also joined to an 24 oscillator 24 providing a clock signal. A temperature sensor 26

is positioned near the oscillator 24 and joined to provide a 1 2 temperature output to processor 20. Temperature sensor 26 can be any sensor capable of providing a digital indication of the 3 temperature near oscillator 24. In the practical application 4 5 discussed below, this sensor 26 can be a Dallas Semiconductor DS1620. Sensor 26 could also be a thermal voltage sensor 6 7 coupled to an analog to digital converter. Non-volatile memory 22 can be preprogrammed with a look up table correlating 8 temperature with clock cycles as described hereinafter. 9 10 FIG. 3 shows an alternate embodiment of the generic system utilizing this invention to adjust delay times in a processor 30 11 when the oscillator 32 is subjected to varying voltages from a 12 13 power supply 34. A voltage sensor 36 is joined to monitor the 14 voltage output (v to ground) of the power supply. This should 15 be the same power supply 34 that influences oscillator 32. 16 Voltage sensor 36 can be any voltage sensor capable of providing a digital indication of the voltage received by oscillator 32. 17 Voltage sensor 36 can be a specialized voltage sensor, an analog 18 to digital converter or analog ranging circuitry joined to an 19 20 analog to digital converter. As above, a non-volatile memory 38 is joined to processor 30. Non-volatile memory 38 can be 21 22 preprogrammed with a look up table correlating voltage with 23 clock cycles as described hereinafter.

FIG. 4 shows yet another alternate embodiment having adjustments for both temperature and voltage. Temperature sensor 26 and voltage sensor 36 are joined to processor 40 as in FIGS. 2 and 3. A non-volatile memory 42 is joined to processor 40. Non-volatile memory 42 can be preprogrammed with a look up table correlating voltage and temperature with clock cycles as described hereinafter.

The nature and accuracy of the timing required dictates the 8 structure of the lookup table stored in memory. In the simplest 9 10 case, the lookup table can contain a sensor output correlated 11 with the clock adjustment values for all possible values of the sensor that affect the oscillator. The size of the lookup table 12 13 depends on the resolution of the sensor and the range of 14 variation in question. The presence of hysteresis can increase 15 the amount of data required up to twice that of the simple case, 16 because data must be stored to account for hysteresis both 17 upwardly moving sensor values and downwardly moving sensor 18 values. Hysteresis has been shown for temperature variations 19 but it may not be significant for other parameter variations 20 such as voltage.

A lookup table has been developed for a system like that shown in FIG. 2. The test results are shown in FIG. 1A. In this test, a Dallas Semiconductor DS1620 temperature chip is used as sensor 26. This sensor 26 has a resolution of 0.5°

1 Celsius. For a temperature range of 20 to 29° C, there would be twenty rows in the lookup table stored in memory 22. 2 Table 1 shows the adjustment values corresponding to the data in FIG. 3 In order to account for hysteresis, this table has separate 4 1A. adjustment values for increasing temperatures and decreasing 5 temperatures. There are three options for steady state 6 7 conditions: utilizing the previous adjustment, utilizing the increasing temperature value, or utilizing the decreasing 8 temperature value. System constraints and the nature of the 9 10 data dictate the proper option.

11

Table 1

| Memory Offset (Arbitrary) | Adjustment Value - UP/Steady | Adjustment Value – DOWN |

|---------------------------|------------------------------|-------------------------|

| •                         | •                            |                         |

| • · · · · ·               | •                            | •                       |

| 40,41                     | -20.0                        | -15.3                   |

| 42,43                     | -20.0                        | -15.3                   |

| 44,45                     | -20.0                        | -16.0                   |

| 46,47                     | -20.0                        | -16.0                   |

| 48,49                     | -20.0                        | -16.0                   |

| 50,51                     | -20.4                        | -16.0                   |

| 52,53                     | -20.3                        | -16.0                   |

| 54,55                     | -20.2                        | -16.0                   |

| 56,57                     | -20.0                        | -15.8                   |

| 58,59                     | -20.0                        | -15.0                   |

| 60,61                     | -20.0                        | -15.0                   |

| •                         |                              | •                       |

|                           |                              | •                       |

12

13 The corrections obtained by this table are limited because only 14 integer values of counts can be added or subtracted from the 15 current number of instruction cycles in a delay loop. 16 Therefore, the lookup table's adjustment values must be rounded

to the nearest integer. The rounded values are shown in Table

1

2

3

2.

| Memory Offset (Arbitrary)             | Adjustment Value - UP/Steady | Adjustment Value – DOWN |  |  |

|---------------------------------------|------------------------------|-------------------------|--|--|

|                                       | •                            |                         |  |  |

| · · · · · · · · · · · · · · · · · · · | •                            |                         |  |  |

| 40,41                                 | -20                          | -15                     |  |  |

| 42,43                                 | -20                          | -15                     |  |  |

| 44,45                                 | -20                          | -16                     |  |  |

| 46,47                                 | -20                          | -16                     |  |  |

| 48,49                                 | -20                          | -16                     |  |  |

| 50,51                                 | -20                          | -16                     |  |  |

| 52,53                                 | -20                          | -16                     |  |  |

| 54,55                                 | -20                          | -16                     |  |  |

| 56,57                                 | -20                          | -16                     |  |  |

| 58,59                                 | -20                          | -15                     |  |  |

| 60,61                                 | -20                          | -15                     |  |  |

| •                                     |                              | •                       |  |  |

| •                                     | ·                            |                         |  |  |

#### Table 2

5 The adjustment values are indexed by an arbitrary memory offset 6 value that is directly related to the sensor output. This 7 offset can also be dependent on processor microcode.

As an example assume that at 20° Celsius with a decreasing 8 temperature a delay loop is calculated to be 15.3 counts too 9 10 slow for a one second delay interval as shown in Table 1, row 1, 11 column 3. Due to the fact that only integer values can be added or subtracted fifteen instruction cycles, rather than 15.3, will 12 be subtracted from the loop. While subtracting 15 cycles will 13 14 improve the overall frequency error, it will only do so to a resolution of 3/10 of a count during the one second delay 15 interval. Equation 2, below, can be used to calculate the 16 17 accumulated error:

Accumulated Error =  $\left[\frac{Rounding \ Error}{delav(s)} \times T_{P_{-CLK}}\right] \times Length \ of \ Run(s)$

1

In the system discussed above, each instruction cycle is 1/27,000,000 or 37.04 ns. If the error is 3/10 of a count each time through the one second repetition interval, after one minute of operation the accumulated error of the system will be:

$(2)^{'}$

$$5 \quad \left[\frac{3/10}{1 \sec} \times \frac{1}{27,000,000} \sec\right] \times 60 \sec = 667 ns . \tag{3}$$

7 This may be sufficient for some applications; however,

8 additional processing and storage can be utilized to provide

9 greater accuracy.

The accumulated error thresholding technique stores the 10 11 remainder of the adjustment value, rather than rounding it off, and uses the remainder to improve the accuracy of the system. 12 Rather than letting the error grow, this technique imposes 13 thresholds on the accumulated error. If the accumulated error 14 15 exceeds the thresholds, the adjustment value is change by one count (plus or minus depending on the sign of the error), and 16 the 10's complement of the remainder is added to the accumulated 17 18 error. Table 3 shows the accumulated error thresholding lookup 19 table for the data in FIG. 1A. FIG. 5 provides pseudo code for 20 one embodiment of the accumulated error thresholding technique that could reference table 3. 21

The lookup table values are calculated using the following

(4)

0

2

0

0

2 equations:

-20

-20

-20

-20

68,69,70,71

72,73,74,75

76,77,78,79

80,81,82,83

Remainder Value' =  $[round(Adjustment Value,1) - round(Adjustment Value,0)] \times 10$  (5) 4

| ١. |  |

|----|--|

| •  |  |

|    |  |

|    |  |

1

| Memory Offset<br>(Arbitrary) | Adjustment<br>Value –<br>UP/Steady | Remainder<br>Value –<br>UP/Steady | Adjustment Value –<br>DOWN | Remainder Value –<br>DOWN |

|------------------------------|------------------------------------|-----------------------------------|----------------------------|---------------------------|

| •                            |                                    | •                                 |                            |                           |

| •                            |                                    | •                                 |                            | •                         |

| 40,41,42,43                  | -20                                | 0                                 | -15                        | -3                        |

| 44,45,46,47                  | -20                                | 0                                 | -15                        | -3                        |

| 48,49,50,51                  | -20                                | 0                                 | -16                        | 0                         |

| 52,53,54,55                  | -20                                | 0                                 | -16                        | 0                         |

| 56,57,58,59                  | -20                                | 0                                 | -16                        | 0                         |

| 60,61,62,63                  | -20                                | -4                                | -16                        | 0                         |

| 64,65,66,67                  | -20                                | -3 .                              | -16                        | 0                         |

-16

-16

-15

-15

Table 3

6

7 The code shown in FIG. 5 repeats each time the processor goes through its delay loop. Each time through, the adjustment value 8 9 is added to the number of instruction cycles in the loop to 10 offset the frequency error to zero.

-2

0

0

0

11 Using the same example described above where the 12 temperature is 20° and decreasing, the accumulated error threshold method with a threshold of -6 will be used with the 13 14 adjustment value -15.3 to show operation of the method. After 15 the first time through the delay, the system will be 3/10 of a 16 count too slow. After the second, it will be 6/10 too slow.

The accumulated error of -6 has now reached the threshold. So, the next time through the delay the adjustment value will be decremented by one and the ten's complement of its remainder will be added to the accumulated error. The output of the accumulated error after the third delay is therefore -6 + (10 + (-3)) = 1. Table 4 shows this in tabular form and the output of the process is shown in FIG. 6.

#### Table 4

| DELAY<br>LOOP | ADJUST VALUE<br>USED | REMAINDER<br>VALUE USED | ACCUMULATED<br>ERROR | THRESHOLD<br>EXCEEDED |

|---------------|----------------------|-------------------------|----------------------|-----------------------|

| 1             | -15                  | -3                      | -3                   | NO                    |

| 2             | -15                  | -3                      | -6                   | YES                   |

| · 3           | -15 -1 = -16         | -3 + 10 = 7             | · 1 ·                | NO                    |

| 4             | -15                  | -3                      | -2                   | NO                    |

| 5             | -15                  | -3                      | -5                   | NO                    |

| 6             | -15                  | -3                      | -8                   | YES                   |

| 7             | -15 -1 = -16         | -3 + 10 = 7             | -1                   | NO                    |

| 8             | -15                  | -3                      | -4                   | NO                    |

| 9             | -15                  | -3                      | -7                   | YES                   |

| 10            | -15 - 1 = -16        | -3 + 10 = 7             | 0                    | NO                    |

#### **DESIRED ADJUST VALUE = -15.3**

9.

8

-

10 This technique utilizes integer math rather than floating 11 point math in order to achieve pseudo floating point adjustments 12 in an environment that dictates the use of integer numbers, i.e. 13 a digital processor delay loop or counter/timer.

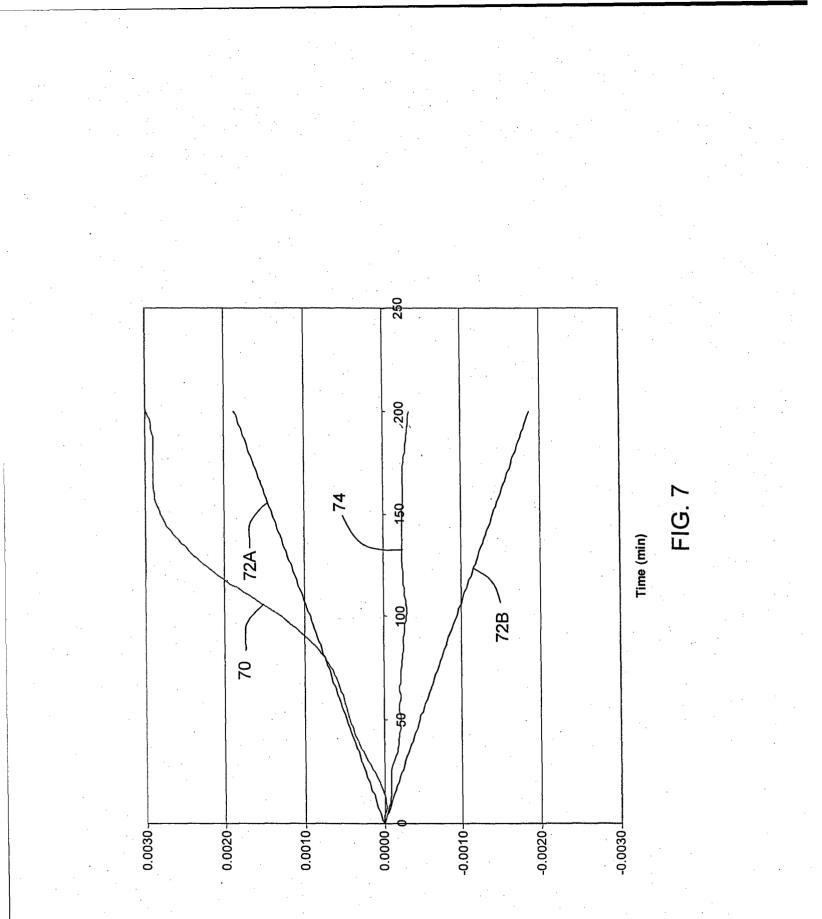

14 In theory, accumulated error thresholding proves that15 repetition interval errors will reside within the bounds of 1/20

of a count which is negligible compared to no accumulated error 1 thresholding correction. FIG. 7 provides a graph of a test 2 showing error with cycle time correction but no accumulated 3 error thresholding, identified as 70; the positive and negative 4 acceptable error limits, error within one count, are identified 5 as 72A and 72B; and error with accumulated error thresholding, 6 7 identified as 74. FIG. 7 was developed utilizing the accumulated error thresholding technique with a one second 8 repetition interval produced by a Texas Instruments TMS 5320c31 9 digital signal processor chip using the oscillator in FIG. 1A 10 (divided by four) and the same model Dallas Semiconductor 11 temperature chip in a temperature varying environment. As shown 12 13 in FIG. 7, the accumulated error of accumulated error thresholding 74 did not exceed the maximum acceptable error 14 15 bound of curves 72A and 72B. Error 74 slightly exceeded the maximum expected error for a theoretical system because of the 16 17 practicalities of the implementation. This test proves that 18 accumulated error thresholding is effective in improving the 19 performance of a timing system.

Using more digits after the decimal point can extend the precision of accumulated error thresholding. So far, accumulated error thresholding has been introduced as only using the tenths value of the adjustment value which has a resolution of 1/20 of a count. If accumulated error thresholding were to

| 1  | use both the tenths and hundredths values, the resolution would       |

|----|-----------------------------------------------------------------------|

| 2  | become a factor of 10 better or 1/200 of a count. If all digits       |

| 3  | up to the thousandths value were used, the resolution would be        |

| 4  | 1/2000 of a count. This method could be extended in a like            |

| 5  | manner to any order of resolution desired. This manuscript will       |

| 6  | refer to first order as accumulated error thresholding to the         |

| 7  | tenths, second order as accumulated error thresholding to the         |

| 8  | hundredths, and third order as accumulated error thresholding to      |

| 9  | the thousandths.                                                      |

| 10 | Equations for calculating higher order adjustment values              |

| 11 | are shown below:                                                      |

| 12 | $Adjustment \ Value" = round (Adjustment \ Value, 0) $ (4)            |

| 13 | $Remainder Value_{10} = [round(Adjustment Value,0)] \times 10 $ (5)   |

| 14 | $Remainder Value_{100} = [round(Adjustment Value,1)] \times 100 $ (6) |

| 15 | As can be seen equations 4' and 5' are very similar to equations      |

| 16 | 4 and 5. Pseudo code for the higher order algorithm is given in       |

| 17 | FIG. 8.                                                               |

| 18 | As an example to show how second order accumulated error              |

| 19 | thresholding works, assume 15.34 cycles need to be subtracted         |

| 20 | from the current code to offset the frequency error to zero.          |

| 21 | After the first delay, the tenths value will be 3/10 too slow         |

| 22 | and the hundredths value will be 4/10 too slow. After the             |

second delay, the tenths value will be 6/10 too slow and the hundredths value will be 8/10 too slow. Both of these have now reached the threshold and need to be adjusted. When the hundredths accumulated error reaches the threshold, 1 is subtracted from the tenths remainder. When the tenths value reaches its threshold, 1 is subtracted from the adjustment value. Table 5 shows this for each delay loop.

Table 5

| Delay<br>Loop | Adjust<br>Value Used | Remain_10<br>Used | Remain_100<br>Used | Acc_10 | Acc_100 | Thres_10 | Thres_100 |

|---------------|----------------------|-------------------|--------------------|--------|---------|----------|-----------|

| 1             | -15                  | -3                | -4                 | -3     | -4      | no       | no        |

| 2             | -15                  | -3                | -4                 | -6     | -8      | yes      | yes       |

| 3             | -15-1=-16            | -3+10-1=6         | -4+10=6            | 0      | -2      | no       | no        |

| 4             | -15                  | -3                | -4                 | -3     | -6      | no       | yes       |

| 5             | -15                  | -3-1=-4           | -4+10=6            | -7     | 0       | yes      | no        |

| 6             | -15-1=-16            | -3+10=7           | -4                 | 0      | -4      | no       | no        |

| - 7           | -15                  | -3                | -4                 | -3     | -8      | no       | yes       |

| - 8           | -15                  | -3-1=-4           | -4+10=6            | -7     | -2      | yes      | no        |

| 9             | -15-1=-16            | -3+10=7           | -4                 | 0      | -6      | no       | yes       |

| 10            | -15                  | -3-1=-4           | -4+10=6            | -4     | 0       | no       | no        |

| 11            | -15                  | -3                | -4                 | -7     | -4      | yes      | no        |

| 12            | -15-1=-16            | -3+10=7           | -4                 | 0      | -8      | no       | yes       |

| 13            | -15                  | -3-1=-4           | -4+10=6            | -4     | -2      | no       | no        |

| 14            | -15                  | -3                | -4                 | -7     | -6      | yes      | yes       |

| 15            | -15-1=-16            | -3+10-1=6         | -4+10=6            | -1     | 0       | no       | no        |

| 16            | -15                  | -3                | -4                 | -4     | -4      | no       | no        |

| 17            | -15                  | -3                | -4                 | -7     | -8      | yes      | yes       |

| 18            | -15-1=-16            | -3+10-1=6         | -4+10=6            | -1     | -2      | no       | no        |

| 19            | -15                  | -3                | -4                 | -4     | -6      | no       | yes       |

| 20            | -15                  | -3-1=-4           | -4+10=6            | -8     | 0       | yes      | no        |

| 21            | -15-1=-16            | -3+10=7           | -4                 | -1     | -4      | no       | no        |

| 22            | -15                  | -3                | -4                 | -4     | -8      | no       | yes       |

| 23            | -15                  | -3-1=-4           | -4+10=6            | -8     | -2      | yes      | no        |

| 24            | -15-1=-16            | -3+10=7           | -4                 | -1     | -6      | no       | yes       |

| 25            | -15                  | -3-1=-4           | -4+10=6            | -5     | 0       | no       | no        |

| 26            | -15                  | -3                | -4                 | -8     | 4       | yes      | no        |

| 27            | -15-1=-16            | -3+10=7           | -4                 | -1     | -8      | no       | yes       |

| 28            | -15                  | -3-1=-4           | -4+10=6            | -5     | -2      | no       | no        |

| 29            | -15                  | -3                | -4                 | -8     | -6      | yes      | yes       |

| 30            | -15-1=-16            | -3+10-1=6         | -4+10=6            | -2     | 0       | no       | no        |

| 31            | -15                  | 3                 | -4                 | -5     | -4      | no       | no        |

| 32            | -15                  | -3                | -4                 | -8     | -8      | yes      | yes       |

| 33            | -15-1=-16            | -3+10-1=6         | -4+10=6            | -2     | -2      | no       | no        |

| 34            | -15                  | -3                | -4                 | -5     | -6      | no       | yes       |

| 35            | -15                  | -3-1=-4           | -4+10=6            | -9     | 0       | yes      | no        |

| 36            | -15-1=-16            | -3+10=7           | -4                 | -2     | -4      | no       | no        |

| 37            | -15                  | -3                | -4                 | -5     | -8      | no       | yes       |

| 38            | -15                  | -3-1=-4           | -4+10=6            | -9     | -2      | yes      | no        |

| 39            | -15-1=-16            | -3+10=7           | -4                 | -2     | -6      | no       | yes       |

| 40            | -15                  | -3-1=-4           | -4+10=6            | -6     | 0       | yes      | no        |

| 41            | -15-1=-16            | -3+10=7           | -4                 | 1      | -4      | no       | no        |

8

| 42      | -15       | -3        | -4        | -2 | -8 | no  | yes |

|---------|-----------|-----------|-----------|----|----|-----|-----|

| 43      | -15       | -3-1=-4   | -4+10=6   | -6 | -2 | yes | no  |

| 44      | -15-1=-16 | -3+10=7   | -4        | 1  | -6 | no  | yes |

| 45      | -15       | -3-1=-4   | -4+10=6   | -3 | 0  | no  | no  |

| 46      | -15       | -3        | -4        | -6 | -4 | yes | no  |

| 47      | -15-1=-16 | -3+10=7   | -4        | 1  | -8 | no  | yes |

| 48      | -15       | -3-1=-4   | -4+10=6   | -3 | -2 | no  | no  |

| 49      | -15       | -3        | -4        | -6 | -6 | yes | yes |

| 50      | -15-1=-16 | -3+10-1=6 | -4+10=6   | 0  | 0  | no  | no  |

|         |           |           | · · · · · |    |    |     |     |

| average | -15.34    |           |           |    |    |     |     |

1

2 To prove the functionality of second order accumulated error thresholding, a simulation was run using second order 3 accumulated error thresholding, and its results are shown in 4 5 FIG. 9. The curve without accumulated error thresholding is shown as 90. The positive and negative maximum acceptable error 6 curves are 92A and 92B. This is error to within one count of 7 8 the processor. The second order accumulated error thresholding curve is shown at 94. As can be seen, curve 94 is 9 indistinguishable from the zero error axis at this scale. 10 This simulation demonstrates that second order accumulated error 11 thresholding stays within the predicted bounds and produces very 12 precise results. 13

Higher orders of accumulated error thresholding can be performed up to the accuracy requirements of the system. The error using first order accumulated error thresholding is bounded at plus or minus 1/20 of a count. The theoretical error in counts using an n-th order accumulated error threshold is bounded at:

As discussed above, in relation to FIG. 7, actual error may be greater than |e| because of the practicalities of implementation. In any case, the theoretical error can give a measure of the order of accumulated error thresholding required to give a desired accuracy.

(7)

$\pm e = \frac{10^{-n}}{2}$

1

7 When implementing accumulated error thresholding in a 8 system, the first step is collecting the frequency vs. sensor 9 data. For temperature variation, this is accomplished using an 10 environmental temperature chamber. The temperature profile 11 should be a steadily increasing/decreasing temperature at a rate 12 the system might see in the projected application. (This can be 13 similar to that of FIG. 1B).

Using the environmental chamber programmed with the desired 14 profile, the frequency and temperature are measured and 15 recorded. Those measurements are then used to calculate the 16 adjustment values and remainders, which are stored in the lookup 17 table. The lookup table is then programmed in the systems non-18 volatile memory and the above pseudo code is implemented into 19 the processor's firmware. 20

Due to the aging effect of oscillators, this process will need to be repeated periodically, dependent on the speed of the

aging and the desired accuracy of the system. Typically, this

period can be several months to several years.

3 It will be understood that various changes in the detail, 4 steps and arrangement of parts, which have been herein described 5 and illustrated in order to explain the nature of the invention, 6 may be made to those skilled in the art with the principle and 7 scope of the invention as expressed in the independent claims. 1 Attorney Docket No. 96276

2 DELAY LOOP CORRECTION FOR PROGRAMMABLE CONTROLLERS 3 4 ABSTRACT OF THE DISCLOSURE 5 An apparatus provides a correction value for an oscillator. 6 7 At least one parameter sensor measures a system parameter influencing the oscillator. A lookup table determines a cycle 8 9 adjustment value based on the system parameter. A processor 10 joined to the oscillator implements the cycle adjustment value to correct for oscillator variation. Cycle adjustment values 11 12 can be computed in both whole cycles and partial cycles through 13 accumulated error thresholding. The parameter sensor can be a 14 temperature sensor, a voltage sensor or both kinds of sensors. 15 The lookup table and processor can have additional terms to 16 account for hysteresis in the oscillator.

$\overline{\ }$

#### Temp = Chip Temp

IF Temp >= Previous Temp THEN Adjustment Value = Base Table Address + [Offset(Temp)] Remainder = Base Table Address + [Offset(Temp) + 1] ELSE IF Temp < Previous Temp THEN Adjustment Value = Base Table Address + [Offset(Temp) + 2] Remainder = Base Table Address + [Offset(Temp + 3] END IF

IF Accumulated Error > Threshold THEN Adjustment Value = Adjustment Value + 1 Remainder = Remainder - 10 ELSE IF Accumulator Error < Threshold THEN Adjustment Value = Adjustment Value - 1 Remainder = 10 + Remainder ELSE Adjustment Value = Adjustment Value

Remainder = Remainder

END IF

Accumulated Error = Accumulated Error + Remainder

Previous Temp = Temp

FIG. 5

Acc. Drift (s)

### Temp = Chip Temp

IF Temp >= Previous Temp THEN

Adjustment Value = Base Table Address + [Offset(Temp)] Remainder\_10 = Base Table Address + [Offset(Temp) + 1] Remainder\_100 = Base Table Address + [Offset(Temp) + 2] ELSE IF Temp < Previous Temp THEN

Adjustment Value = Base Table Address + [Offset(Temp) + 3] Remainder\_10 = Base Table Address + [Offset(Temp) + 4] Remainder\_100 = Base Table Address + [Offset(Temp) + 5] END IF

IF Accumulated Error\_100 > Threshold THEN Remainder\_10 = Remainder\_10 + 1

Remainder\_100 = Remainder\_100 - 10

ELSE IF Accumulator Error < Threshold THEN

Remainder\_10 = Remainder\_10 - 1

Remainder\_100 = 10 + Remainder\_100

#### ELSE

Remainder\_10 = Remainder\_10 Remainder\_100 = Remainder\_100

END IF

IF Accumulated Error\_10 > Threshold THEN Adjustment Value = Adjustment Value + 1 Remainder\_10 = Remainder\_10 - 10 ELSE IF Accumulator Error\_10 < Threshold THEN Adjustment Value = Adjustment Value - 1 Remainder\_10 = 10 + Remainder\_10 ELSE

Adjustment Value = Adjustment Value Remainder\_10 = Remainder\_10 END IF

Accumulated Error\_10 = Accumulated Error\_10 + Remainder\_10 Accumulated Error\_100 = Accumulated Error\_100 + Remainder\_100 Previous Temp = Temp

## FIG. 8

Drift (s)