Serial Number

<u>045,853</u>

Filing Date

Inventor

23 March 1998

David S. Hsu Henry F. Gray

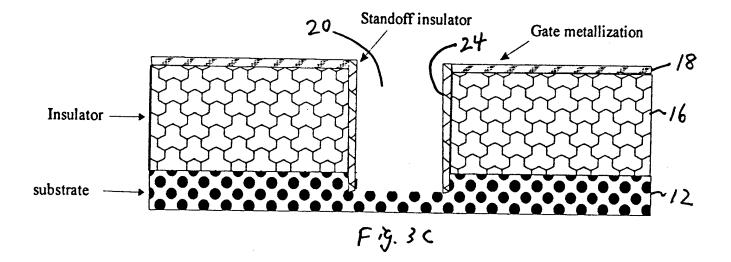

#### **NOTICE**

The above identified patent application is available for licensing. Requests for information should be addressed to:

OFFICE OF NAVAL RESEARCH DEPARTMENT OF THE NAVY CODE OOCC ARLINGTON VA 22217-5660

# 19980618 079

DISTRIBUTION STATEMENT A

Approved for public release; Distribution Unlimited

1

| 2  |                                                                                                       |

|----|-------------------------------------------------------------------------------------------------------|

| 3  | FIELD EMITTER CELL AND ARRAY WITH VERTICAL THIN-FILM-EDGE EMITTER                                     |

| 4  | ENTER THE VERTICAL THIN-FILM-EDGE EMITTER                                                             |

| 5  | Background of the Invention                                                                           |

| 6  | 1. Field of the Invention                                                                             |

| 7  | The present invention relates generally to field emitter cells and arrays and more specifically       |

| 8  | to thin-film-edge emitter cells and arrays.                                                           |

| 9  |                                                                                                       |

| 10 | 2. Description of the Background Art                                                                  |

| 11 | Very small localized vacuum electron sources which emit sufficiently high currents                    |

| 12 | for practical applications are difficult to fabricate. This is particularly true when the sources are |

| 13 | required to operate at reasonably low voltages. Presently available thermionic sources do not emit    |

| 14 | high current densities, but rather result in small currents being generated from small areas. In      |

| 15 | addition, thermionic sources must be heated, requiring special heating circuits and power supplies.   |

| 16 | Photo emitters have similar problems with regard to low currents and current densities.               |

| 17 | Field emitter arrays (FEAs) are naturally small structures which provide reasonably high              |

| 18 | current densities at low voltages. FEAs typically comprise an array of conical, pyramidal or cusp-    |

| 19 | shaped point, edge or wedge-shaped vertical structures which are electrically insulated from a        |

| 20 | positively charged extraction gate and which produce an electron beam that travels through an         |

## PATENT APPLICATION

Docket No.: N.C. 79,020 Inventor's Name: Hsu et al.

1 associated opening in the charged gate.

The classical field emitter includes a sharp point at the tip of the vertical structure and 2 opposite an extraction electrode. In order to generate electrons which are not collected at the 3 extraction electrode, but can be manipulated and collected somewhere else, an aperture is created 4 in the extraction electrode which aperture is significantly larger (e.g. two orders of magnitude) than 5 6 the radius of curvature of the field emitter. Thus, the extraction electrode is a flat horizontal surface containing an extraction electrode aperture for the field emitter. The field emitter is centered 7 8 horizontally in the extraction electrode aperture and does not touch the extraction electrode, although the vertical direction of the field emitter is perpendicular to the horizontal plane of the extraction 9 electrode. The positive charges on the edge of the extraction electrode aperture surround the field 10 emitter symmetrically so that the electric field produced between the field emitter and the extraction 11 12 electrode causes the electrons to be emitted from the field emitter in a direction such that are 13 collected on an electrode (anode) separate and distinct from the extraction electrode. A very small percentage of the electrons are intercepted by the extraction electrode. The smaller the aperture, i.e., 14 the closer the extraction electrode is to the field emitter, the lower the voltage required to generate 15 the electron beam. 16

17 It is difficult to create FEAs which have reproducibly small radius-of-curvature field emitter 18 tips of conducting materials or semiconducting materials. Furthermore, it is equally difficult to gate 19 or grid these structures where the gate-to-emitter distance is reasonably small to provide the 20 necessary high electrostatic field at the field emitter tip with reasonably small voltages. The radius

# PATENT APPLICATION

(

of curvature is typically 100-300 angstroms (Å) and the gate-to-emitter distance is typically 0.1-0.5

micrometers (μm).

Current methods of manufacturing FEAs include wet etching, reactive ion etching, and a

variety of field emitter tip deposition techniques. Practical methods generally require the use of

lithography which has a number of inherent disadvantages including the high cost of the equipment

needed. Furthermore, the high degree of spatial registration required prevents parallel processing,

i.e., the fabrication of a very large number of emitters at the same time in a single process.

8 To a large extent, these prior art problems were overcome by Hsu et al., United States Patent No. 5,584,740 and Gray et al., United States Patent No. 5,382,185, both of which are incorporated 9 10 herein by reference for all purposes in their entirety. The '740 and '185 patents describe a thin-filmedge emitter cell including a substrate having a protuberance extending therefrom, a conformally 11 deposited insulating layer over the substrate and vertical sidewall of the protuberance, an emitter film 12 conformally deposited upon the insulating layer and the vertical sidewall thereof, and a gate 13 metallization layer parallel to the vertically extending portion of the emitter film. The emitter film 14 extends vertically beyond the protuberance. U.S. Patents 5,214,347 and 5,266,155 to Gray, both are 15 which are incorporated-by-reference herein in their entirety for all purposes, describe horizontal thin-16 film edge field emitters and gated field emitters. 17

Because of the parallel orientation of the emitter film relative to the gate, the insulating layer

between these elements in those patented devices must be sufficiently thin so that, at the emitter tip,

the gate generates a field capable of extracting electrons at the tip. The dependence of the gate to

•-

۱<u>۰</u>

## PATENT APPLICATION

; -

| 1  | tip distance upon insulating film thickness requires a trade off between the reduced susceptibility to   |

|----|----------------------------------------------------------------------------------------------------------|

| 2  | pinhole defects and voltage breakdown offered by thicker insulating films and the increased voltage      |

| 3  | demands caused by the resulting additional gate to tip distance. Additionally, the parallel orientation  |

| 4  | of the gate layer creates a high capacitance. In turn, this high capacitance increases the RC time       |

| 5  | constant, reducing frequency response and power efficiency.                                              |

| 6  |                                                                                                          |

| 7  | Summary of the Invention                                                                                 |

| 8  |                                                                                                          |

| 9  | Accordingly, it is an object of this invention to provide an efficient field emitter cell that may       |

| 10 | be readily and economically fabricated.                                                                  |

| 11 | It is another object of the present invention to provide a field emitter cell having a low               |

| 12 | capacitance and good frequency response.                                                                 |

| 13 | It is a further object of the present invention to provide an efficient, low voltage, low power          |

| 14 | field emitter cell that can be fabricated in arrays without special measures to assure correct alignment |

| 15 | of the gate electrode and the emitter tip.                                                               |

| 16 | It is yet another object of the present invention to provide a field emitter cell at the lowest          |

| 17 | possible cost with the least number of processing steps.                                                 |

| 18 | It is a yet further object of the present invention to provide a field emitter cell in which the         |

| 19 | emitter is protected against oxidation and blunting.                                                     |

| 20 |                                                                                                          |

| 21 | These and additional objects of the invention are accomplished by a field emitter cell having            |

## PATENT APPLICATION

| 1  | an electrically conductive substrate. An insulating layer extends over the substrate. This insulating   |

|----|---------------------------------------------------------------------------------------------------------|

| 2  | layer has at least one perforation through it. The perforation has essentially vertical sidewalls and   |

| 3  | a bottom defined by the substrate. A conducting layer, having a perforation therein extends over the    |

| 4  | insulating layer, and serves as a gate electrode. The perforation of the conducting layer is coincident |

| 5  | with the perforation in the insulating layer. A thin-film-edge emitter layer extends upward from the    |

| 6  | perforation, normal to the gate electrode, to a height just above, just below, at, or in between, the   |

| 7  | horizontal surfaces of the gate electrode.                                                              |

| 8  | The field emitter cell of the present invention may be made by various methods using known              |

| 9  | lithographic, deposition, and etching steps. In one embodiment, the perforations in the insulating      |

| 10 | layer are made by stamping, or may be already present by virtue of the nature of the selected           |

| 11 | insulating layer.                                                                                       |

| 12 |                                                                                                         |

| 13 | Brief Description of the Drawings                                                                       |

| 14 |                                                                                                         |

| 15 | A more complete appreciation of the invention will be readily obtained by reference to the              |

| 16 | following Description of the Preferred Embodiments and the accompanying drawings in which like          |

| 17 | numerals in different figures represent the same structures or elements, wherein:                       |

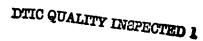

| 18 | Fig 1 shows a side view of typical field emitter cell according to the present invention.               |

| 19 |                                                                                                         |

| 20 | Fig. 2 shows a top view of the field emitter cell shown in Fig. 1.                                      |

| 21 |                                                                                                         |

# PATENT APPLICATION

.....

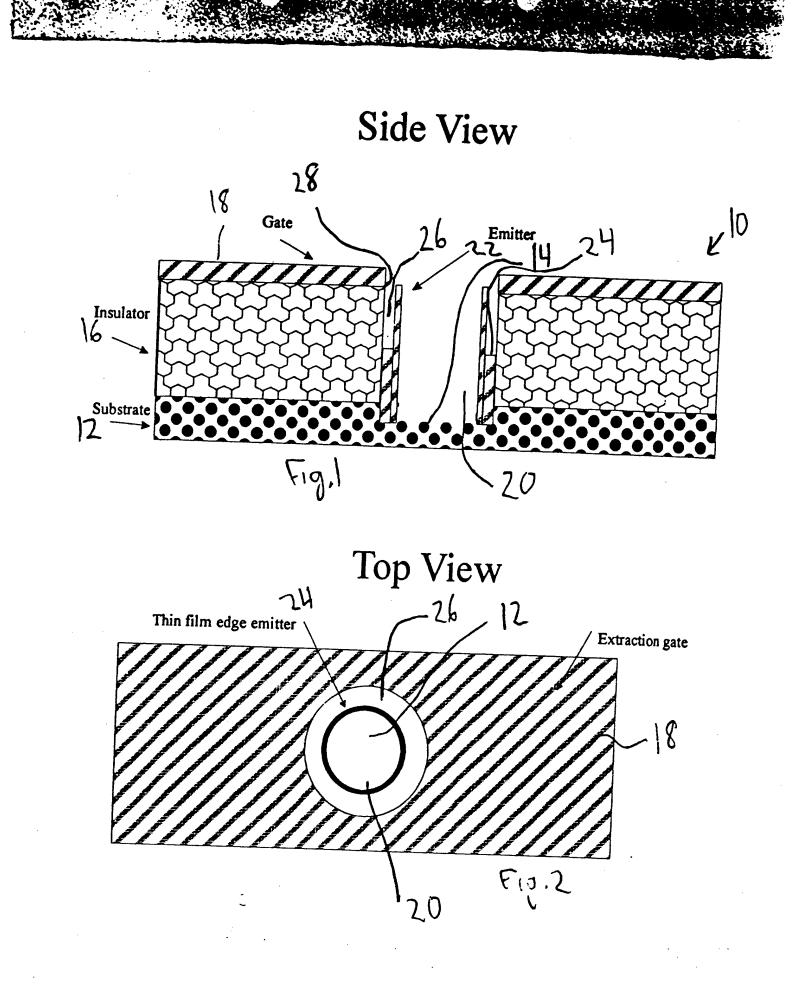

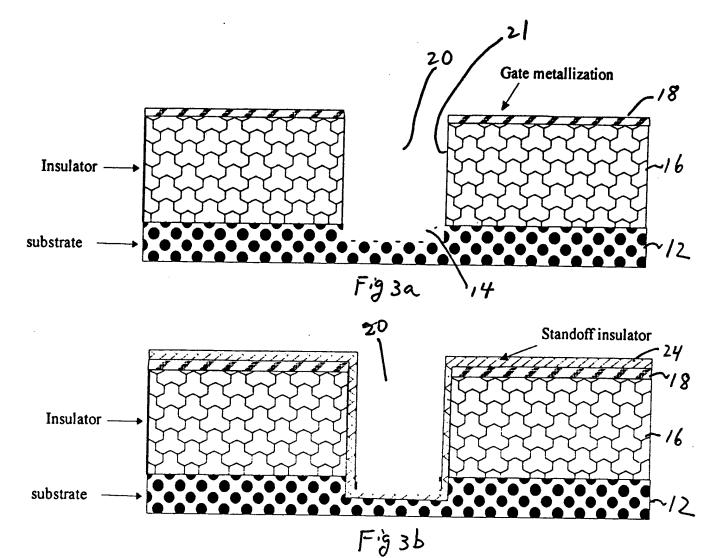

| 1          | Fig. 3a through Fig. 3g show one method of making a field emitter cell according to the               |

|------------|-------------------------------------------------------------------------------------------------------|

| 2          | present invention.                                                                                    |

| 3          |                                                                                                       |

| 4          | Fig. 4a through Fig. 4i show an alternative method of making a field emitter cell according           |

| 5          | to the present invention.                                                                             |

| 6          |                                                                                                       |

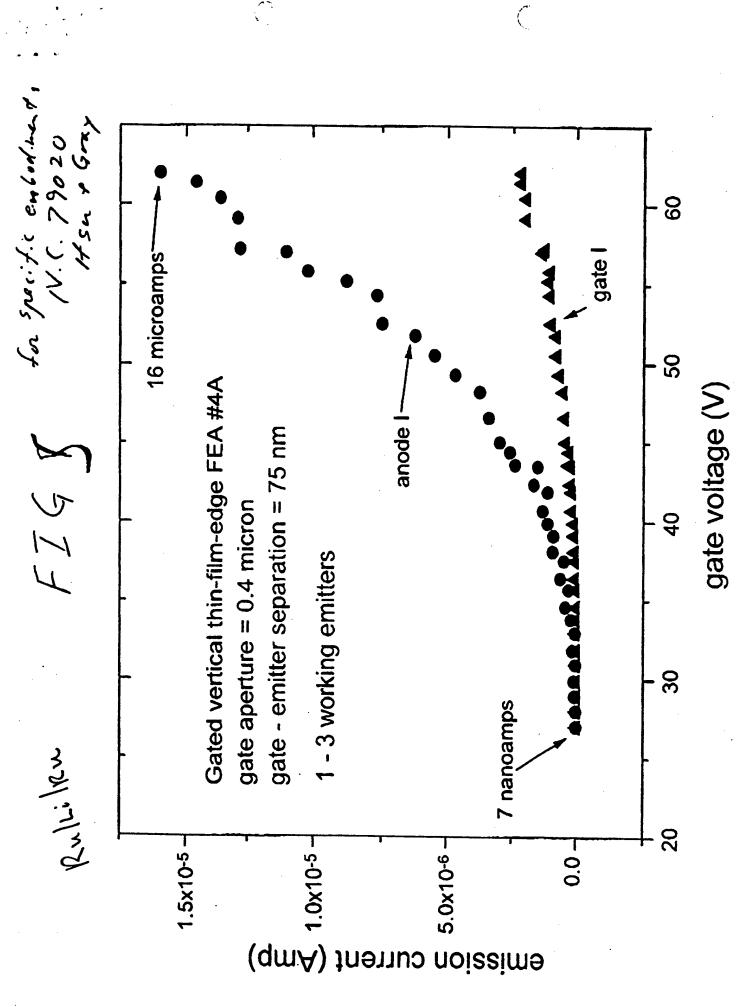

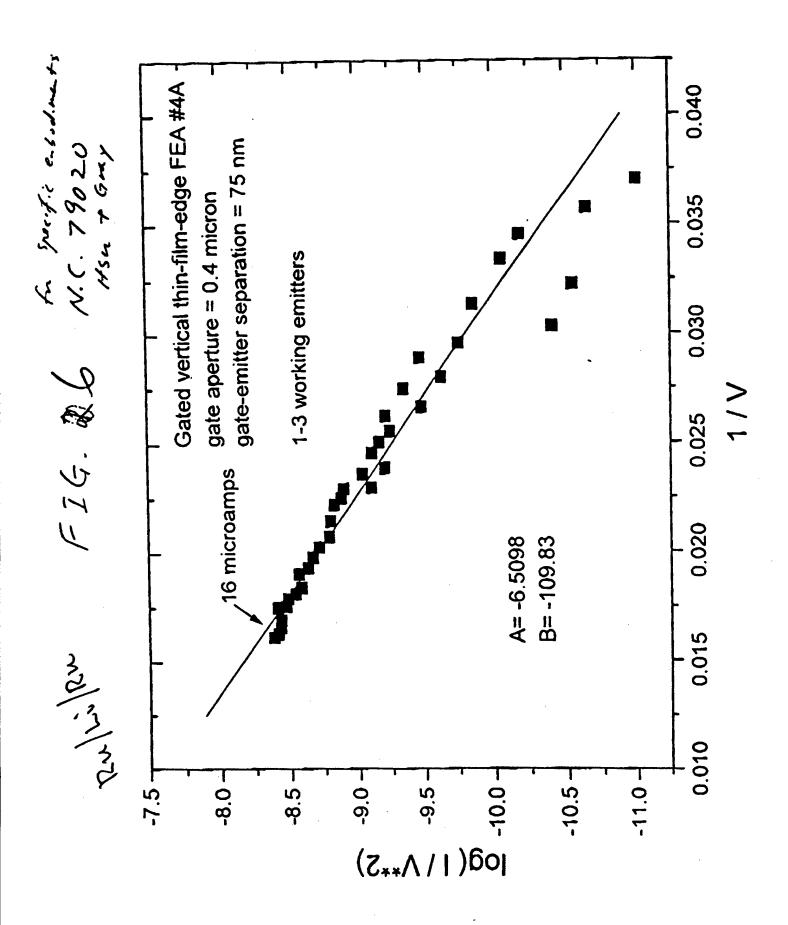

| 7          | Fig. 5 shows the typical measured current-voltage characteristics of an array of field emitter        |

| 8          | cell according to the present invention using an Ru/Li/Ru emitters.                                   |

| <b>9</b> . |                                                                                                       |

| 10         | Fig. 6 shows, in Fowler-Nordheim form, a plot of the current-voltage characteristics shown            |

| 11         | in Fig. 5.                                                                                            |

| 12         |                                                                                                       |

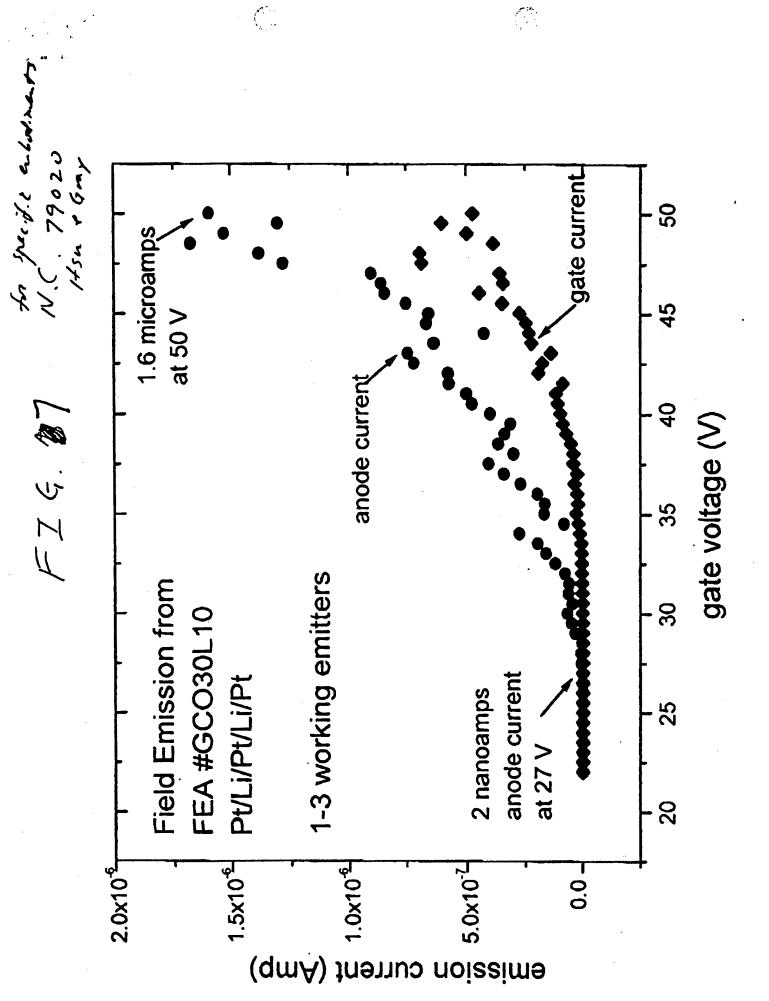

| 13         | Fig. 7 shows the typical measured current-voltage characteristics of an array of field emitter        |

| 14         | cell according to the present invention using Pt/Li/Pt/Li/Pt emitters.                                |

| 15         |                                                                                                       |

| 16         | Description of the Preferred Embodiments                                                              |

| 17         |                                                                                                       |

| 18         | The present invention includes a field emitter cell in which the thin-film-edge emitter is            |

| 19         | essentially perpendicular to the gate layer, insulation layer, and substrate. That unique arrangement |

| 20         | maximizes the distance between the gate and substrate. and minimizes the distance between the gate    |

| 21         | and the emitter, resulting in a large increase in power efficiency and a sharp reduction in the RC    |

#### PATENT APPLICATION

l constant.

2 The substrate layer can be a conductor, an n-doped semiconductor, a resistive material, a transistor, or a composite, alloy, or multilayer structure including one or more of these classes of 3 materials. The substrate layer, however, should be capable of conducting electrons. Throughout the 4 present invention and claims, the terms "conductor" and "conducting material" include both normal 5 conductors and superconductors unless otherwise stated. If a resistive layer is used, emission current 6 can be controlled or limited to prevent burnout of the emitter and to provide emission area 7 uniformity as well as a decrease in noise. A resistive material minimizes burnout by causing an IR 8 drop that results in current limiting in the field emitter cell 9 10 The insulating layer may be any electrically insulating material. Typical materials useful as 11 the insulating layer of the present invention include metal oxides, glass, and organic material (e.g., 12 organic polymers). 13 The emitter is preferably any low work function material that is protected from ready oxidation. Typically, the emitter is selected from among the same class of materials as is the 14 substrate layer. As with the substrate layer, the emitter layer should be capable of conducting 15 electrons. A preferred conducting material is lithium sandwiched between platinum layers, although 16 other materials can be readily used. Typically materials useful as the emitter include platinum, its 17 compounds and its alloys, ruthenium, its compounds and its alloys, and lithium and its alloys. The 18 emitter, like the substrate, may also be an inhomogeneous composite or a multilayer structure. 19 Typically, when the emitter is an alloy, composite (mixture or inhomogeneous) or multilayer 20

## PATENT APPLICATION

structure, at least one of the materials typically has a low work function. For examples, alloys of Li 1 with Pt and/or Ru are useful as an emitter material in the present invention. Typically, a path for 2 electron conduction should be provided between the substrate and the emitter. If a multilayer 3 structure is used, only one of the layers need to be electron conductive. The other layers can be 4 insulating, semiconducting, or hole conductors. If a resistive material is used for the emitter, the 5 emission current can be controlled to prevent emitter burnout and to provide area uniformity as well 6 as a decrease in noise. A resistive material minimizes burnout by causing an IR drop that results in 7 current limiting in the field emitter cell 8

9 In one particularly preferred embodiment, the emitter may be a noble metal/low work function material/noble metal sandwich, typically with each layer of the sandwich having a thickness 10 of about 0.005 to about 0.1 microns. For example, Ru/Li/Ru and Pt/Li/Pt sandwiches have provided 11 excellent results. Other noble metals useful as outer layers in an emitter structure for the present 12 13 invention include Pd, Au, Ir and Os. Non-noble metals, such as W, Mo, Ni, Ti, Cr, and V may also be used as the outer layers in an emitter structure for the present invention. Insulators, and/or 14 semiconductors, may also be used for the outer layers of the emitter multilayer structure, for 15 example, to protect the emitter from oxidation. Useful materials for protective outer layers on the 16 emitter include ceramics, such as AIN, TiAIN, AITiN, BN, TiN, SiN, SiC, diamond, and diamond-17 like carbon. In these embodiments, the outer layers can, but do not necessarily, protect the low work 18 function emitter material against oxidation, since only the emitting tip of the low work function 19 emitter material needs to be exposed. 20

# PATENT APPLICATION

| 1  | As stated above, the actual emitting material itself may be any low work function material.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | Typical low work function emitter materials include, and are not limited to, alkali metals such as Li,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3  | K. Na, Rb, Cs, alkaline earth metals such as Mg. Ba, Sr, Ca, transition metals such as Y and Zr, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4  | other metals such as Th and U, and alloys or compounds containing such materials.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5  | Typically, the emitter layer of the present invention has sharp tips having a radius of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6  | curvature of about 20 nm or less, and more often of about 10 nm or less and most often about 5 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7  | or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8  | The gate layer may be a single lower multitude to the single lower |

| 0  | The gate layer may be a single layer, multilayer, composite, alloy, or elemental material. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9  | gate should, however, include at least one material that is a conductor, a semiconductor, or a resistive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10 | material. A resistive gate layer or a composite including a resistive material minimizes burnout by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11 | causing an IR drop that results in current limiting in the field emitter cell. Unlike the emitter and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12 | substrate, the gate layer need not conduct electrons. That is, the gate may be a conductor by virtue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13 | of hole rather than electron mobility. The use of a p-doped semiconductor in the gate layer may be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14 | particularly advantageous, since it minimizes electrons from emitting from the gate, causing spurious                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15 | and unregulated emission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16 | The sidewalls of the perforation in the present invention should be essentially vertical.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17 | Typically, these walls extend at an angle of at least about 80° (and more often at an angle of at least                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18 | 85°) with respect to the substrate and preferably extend at an angle of substantially 90° with respect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19 | to the substrate. Because of its superior electrical and mechanical properties, a cylindrical structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20 | is most typical, but is not required for the practice of this invention. Any other d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

is most typical, but is not required for the practice of this invention. Any other shape (e.g, a shape

#### PATENT APPLICATION

1

having a square, rectangular, zig-zig, spiral, etc. cross-section) may be used.

The absolute and relative thicknesses of the various layers will depend upon the intended use 2 of the device. The best determination of these parameters for any known application may be 3 determined by routine experimentation combined with knowledge possessed by those having 4 ordinary skill in the art of field emitter cells and arrays. Nevertheless, some additional guidance is 5 offered here. A major advantage of the present invention is that the thicknesses of the various layers 6 and component dimensions, such as emitter height, gate aperture size. and gate-emitter separation, 7 8 are individually and independently selectable.

In many cases, it is desirable to have a vertical spacer layer extending between the insulator 9 layer and the emitter, extending to somewhat less than the height of the emitter. Mainly, the spacer 10 provides mechanical support for the emitter and determines the distance between the emitter and the 11 gate aperture edge. Any material may be used for the spacer. For example, the spacer layer may be 12 an insulator, a conductor, or a semiconductor. If the spacer layer is an electron-conducting material, 13 it can also serve as an electron transport medium and heat sink to the emitter. If the spacer layer is 14 a resistive material, it can serve as a control mechanism for current flow. 15

The base and the conductive part of the substrate of the invention may be any thickness. In 16 typically applications, the base and the conductive part of the substrate will each be from about 17 0.5µm to about 1000 µm, and more often about 0.5 µm to about 100 µm. Typically, the insulating 18 layer will have a thickness of about 0.1  $\mu$ m to about 10  $\mu$ m and more often about 1  $\mu$ m to about 10 19  $\mu$ m. The gate layer typically has a thickness of about 0.1  $\mu$ m to about 1 $\mu$ m. Typically, the spacer 20

#### PATENT APPLICATION

has a thickness of about 100 Å to about 1 μm. More often, the spacer has a thickness of about 100

Å to about 0.5 μm.

If desired for handling or for a specific application, the substrate/insulator/emitter/gate (with

or without spacer layer) may be supported upon a base. If used, the base may be any material,

conductor, semiconductor, or insulator, or any combination of these materials.

Also, adhesion layers may be used, if needed, between the insulating layer and the gate layer,

between the emitter layer and the spacer layer, between the insulating layer and the spacer layer,

and/or between the emitter layer and the substrate, as well as between two layers of a multilayer

component. Typical adhesion layers include Ti and TiN. The adhesion layer may be included as

a part (i.e., sublayer) of a multilayered substrate, insulating layer, spacer layer, gate layer, and/or

emitter layer. When used at the interface between two multilayered component layers, the adhesion

layer will be an outer layer of at least one of the two multilayered component layers.

Fig. 1 shows a side view of typical field emitter cell 10 according to the present invention. 13 Substrate has a depression 14, with essentially vertical sidewall, therein. Insulator layer 16 directly 14 overlays substrate 12. Gate 18 directly overlays insulator layer 16. Both insulator layer 16 and gate 15 18 have therein a perforation 20, with vertical sides, coincident with depression 14. Substrate 12 16 therefore defines the bottom of perforation 20. Emitter 22 extends, essentially vertically upward 17 from the bottom of perforation 20 to the vicinity of gate 18 (in this case, to or just below the insulator 18 layer/gate layer interface). Spacer 24 extends vertically between insulator layer 16 and emitter 22. 19 Although not required, depression 14 provide physical support and better electrical contact for 20

11 -

#### PATENT APPLICATION

emitter 22. A vacuum gap 26 exists between the upper portion of the emitter and insulator layer 16.

If desired, insulating layer 16 may be undercut at the upper part of edge 28 where insulator layer 16 defines perforation 20 and interfaces with gate layer 18 (See Fig. 3g). Such undercutting further

increases the insulation distance between the emitter and the gate, thus reducing the likelihood of

shorting along the surface between emitter 22 and gate 18. Fig. 2shows a top view of the device

shown in Fig. 1.

A field emitter cell according to the present invention, or array thereof, may be produced by 7 a variety of methods. In one typical procedure, shown in Figs. 3a through 3f, conducting substrate 8 12, with or without a base (not shown), is provided on at least its upper surface (with respect to any 9 base that may be present) with insulating layer 16 and gate layer 18 overlaying insulating layer 16. 10 The insulating layer may be provided by any means, such as bonding of a preformed insulating layer, 11 CVD deposition, CBD deposition, physical deposition such a evaporation or sputtering, oxidation 12 of the substrate layer, ion-implantation, etching, etc. Likewise, the method of providing the gate 13 layer is not particularly critical to the present invention. Methods such as melt bonding of a 14 preformed layer of conducting material, evaporative deposition, CVD (chemical vapor deposition), 15 CBD (chemical beam deposition), aqueous plating, electroplating, sputter deposition, and ion-16 17 implantation may be used.

Insulating layer 16 and gate layer 18 of the resulting laminate must then be perforated to provide perforation 20 having essentially vertical sidewalls 21. Perforation 20 forms a well that extends at least to the upper surface of the conducting substrate. A variety of methods may be used to provide the needed perforations (Fig. 3a). One particularly useful method is to reactive ion etch

#### PATENT APPLICATION

(RIE) the laminate through a mask. In one known method, perforations can be make by mechanical 1 2 stamping, using, for example, the method described by Stephen Chou, Science, Vol. 272, 5 April 1996, pages 85 through 87, the entirety of which is incorporated herein by reference. In an 3 alternative method posts, for example of Si, may be provided on the substrate, for example by RIE. 4 Then, an insulator layer is deposited over the post structure and substrate such that insulator 5 thickness is greater than the height of the post. The resulting structure is then planarized, 6 mechanically polished, or chemically-mechanically polished (CMP) to provide a flat upper surface. 7 Selectively etching the back of the insulator leaves a portion of the post protruding above the 8 insulator layer. Then, directional deposition of a gate material over the top of the post and the 9 substrate is performed. The resulting pillar or post may then be preferentially etched to provide a 10 11 hole, with essentially vertical sidewalls, through the gate layer and insulator layer.

If desired, standoff (or spacer) layer 24 may be deposited or otherwise formed directly over 12 the gate layer 18 and vertical sidewalls 21 of perforation 20 (Fig 3b). The standoff layer may be 13 deposited by any method, such as CVD and CBD. Conformality of the deposition of the standoff 14 is not critical, provided that the thickness of the vertical section of each layer along its vertical 15 sidewall is uniform. While the grain size of the standoff layer is not highly critical, it is more critical 16 in the emitter layer. Removal of the horizontal portion of standoff layer 24 by any available method 17 (e.g., by RIE, sputtering, mechanical polishing or chemical mechanical polishing) provides the 18 19 structure shown in Fig. 3c.

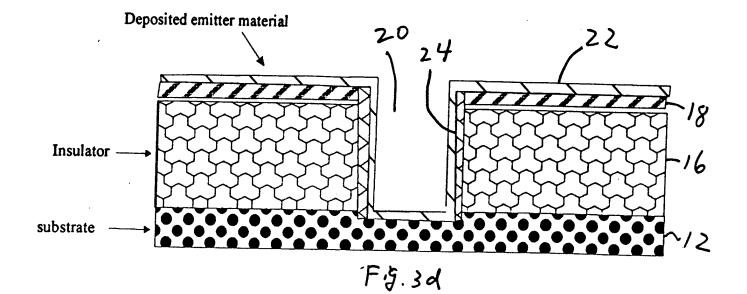

As shown in Fig. 3d, emitter layer 22 is deposited, by chemical beam deposition, on the upper

surface of gate layer 18 having perforation 20 therein. This deposition also deposits emitter layer

#### PATENT APPLICATION

22 upon the vertical sidewalls of perforation 20. Conformal CBD deposition may be done, for

example, according to the method of Hsu et al., United States Patent No. 5,246,879, the entirety of

which is incorporated herein by references for all purposes. Conformal deposition by CBD

according to the teachings of Hsu et al. '879 can readily provide thin conformal layers having fine

grain sizes. The deposition need not be conformal, however, if the portion of the vertical section of

the emitter layer along the sidewalls has an essentially uniform thickness.

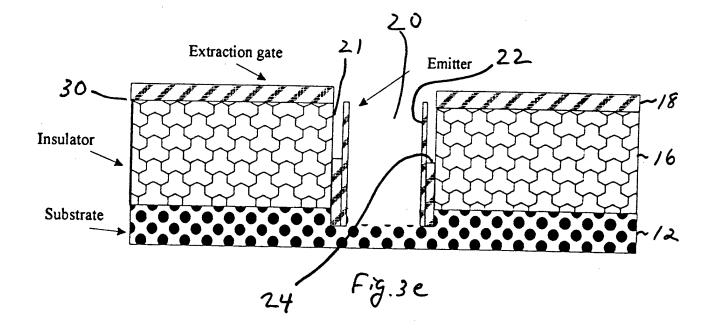

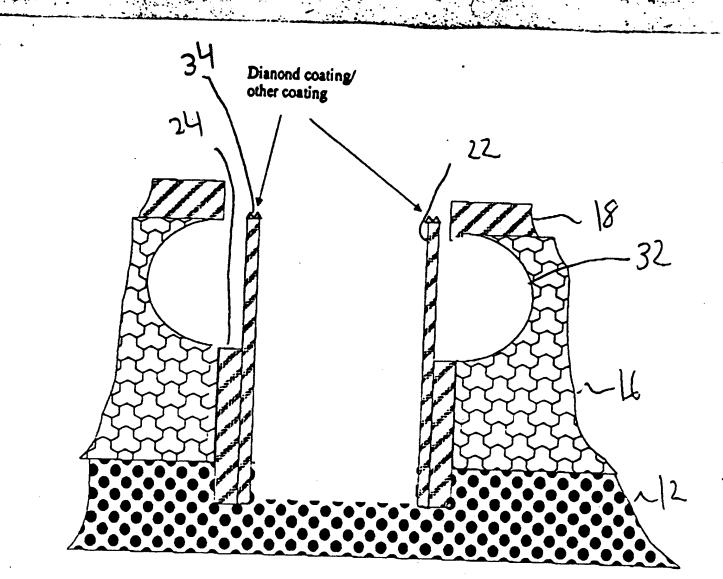

As shown in Fig. 3e, emitter layer 22 is then directionally etched to remove at least the 7 8 horizontal portion overlying gate layer 18. Removing the horizontal portion of the emitter layer 22 by etching or sputtering, rather than by mechanical polishing or CMP. avoids the need to provide a 9 fill within perforation 20 to further support the emitter structure during that and subsequent 10 11 processes. If desired, a film of diamond, or diamond-like carbon may be formed, by any known means, upon emitter layer 22 to provide a plurality of sharp points 34 for improved electron emission 12 (Fig. 3g). Additionally, even without diamond coating, sputtering or etching of the top of the vertical 13 portion of emitter layer 22 inherently provides sharp points 34 that have a small radius of curvature 14 15 for improved electron emission.

As also shown by Fig. 3e, standoff layer 24 is then selectively etched (e.g., by RIE or wet etching) to remove the top portion of the spacer layer over the perforation. A spacer layer extending from the substrate to below the insulator/gate interface 30 results.

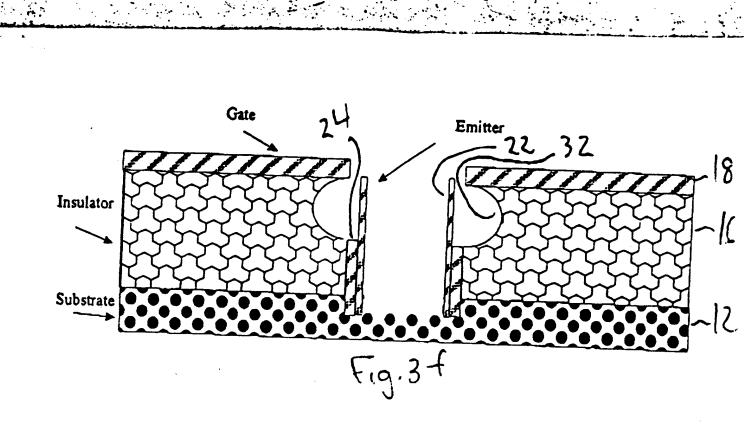

As shown in Fig. 3f, undercut 32 may be etched, by known means, at the upper portion of

insulating layer 16 and at, above, or below the upper surface of the remaining portion of standoff

layer 24.

#### PATENT APPLICATION

1 An advantage of the process shown in Figs. 33a through 3 is that the process does not require 2 planarization. Therefore, the entire fabrication process may be performed entirely in a vacuum, 3 without removing the workpiece from the vacuum chamber.

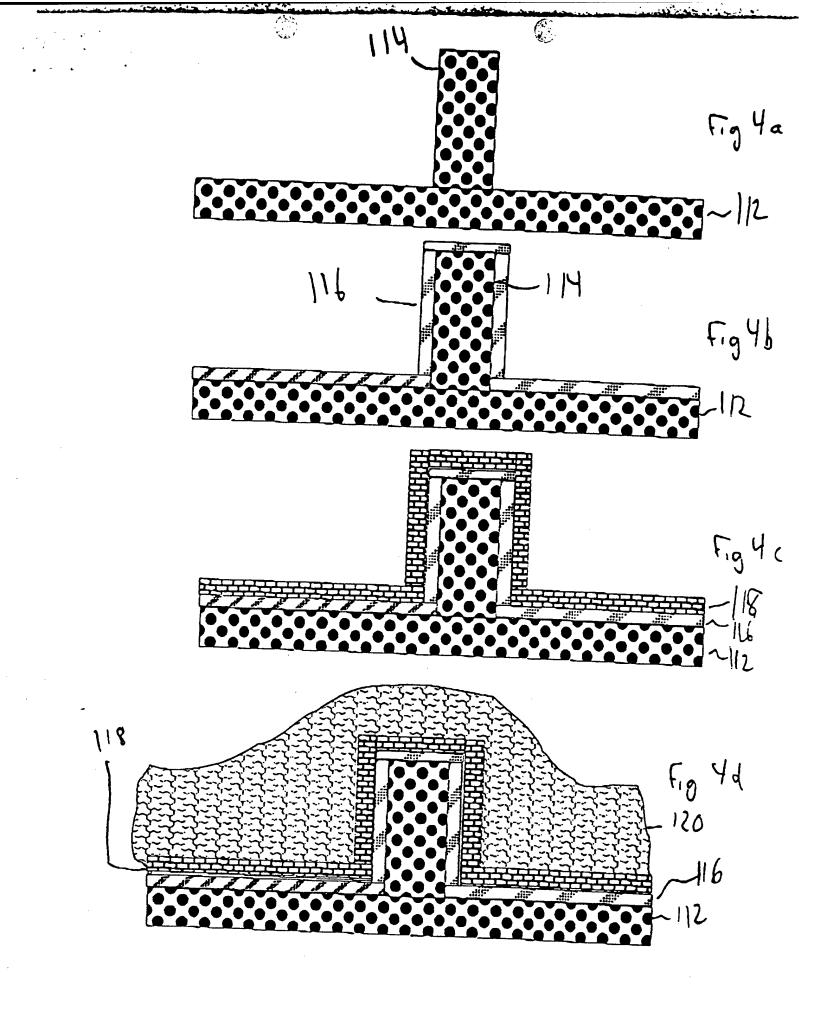

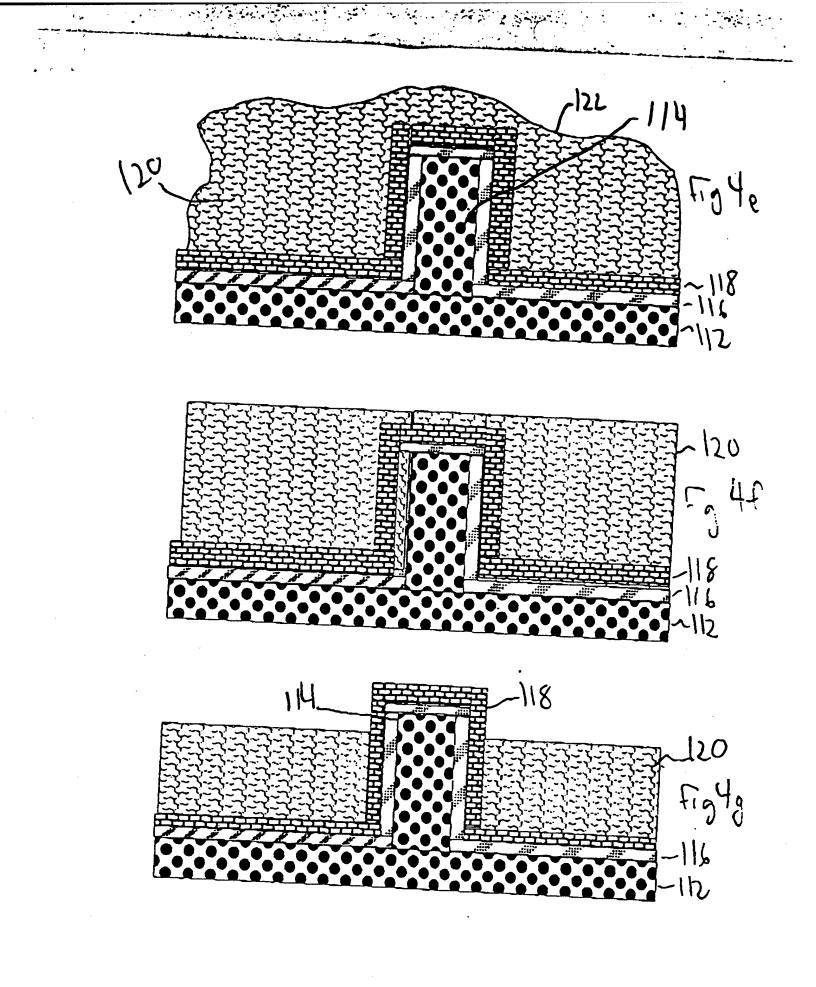

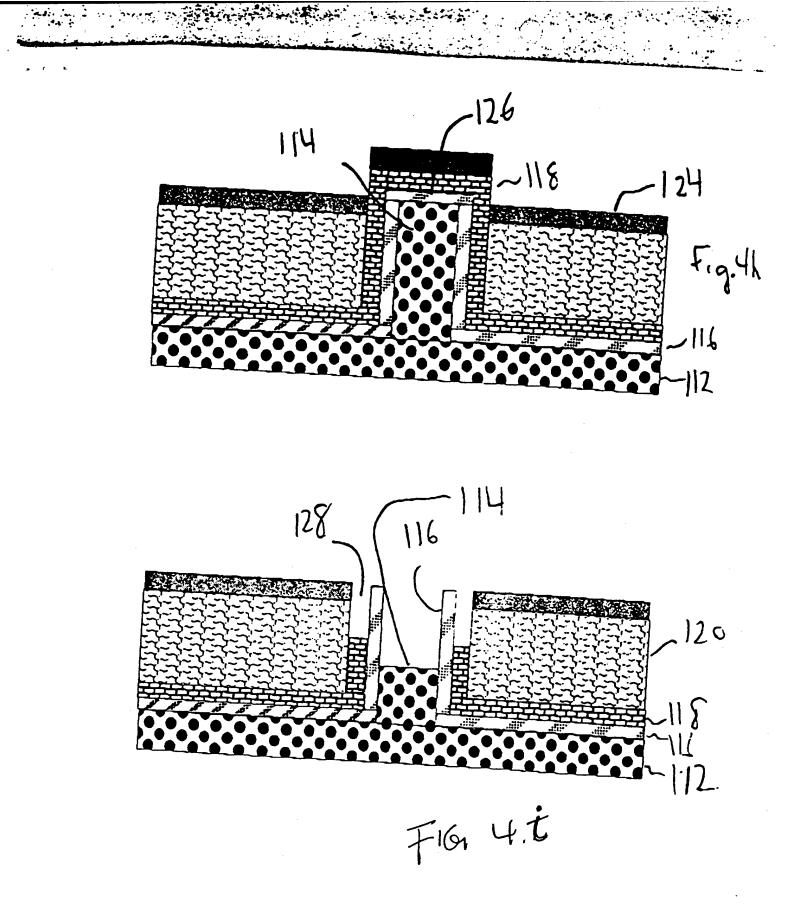

Figs. 4a through 4j show an alternative method of making a field emitter cell according to 4 the present invention. As shown in Fig. 4a, substrate 112 having protrusion 114 is provided. In Fig. 5 4b, emitter layer 116 is then deposited, by CBD for example, over substrate 112, including 6 protrusion 114. In Fig. 4c, standoff layer 118 is then provided over emitter layer 112. Then, as 7 shown in Fig. 4d, insulating layer 120 is provided, by any means, over standoff layer 118. The 8 thickness of insulating layer 120 can vary across the structure. As shown in Fig 4e, the insulating 9 layer may have, at all points, a height greater than that of the top of the portion of standoff layer 118 10 11 covering protrusion 114.

Upper surface 122 of the resulting structure is then planarized by any means, for example, either by etching, sputtering, mechanical polishing. or chemical mechanical polishing, to provide the planarized structure of Fig. 4f. Then, the upper portion of insulating layer 120 is preferentially removed (e.g., by chemical etching or RIE) from its planarized upper surface to provide the structure shown in Fig. 4g, in which the top of insulating layer 120 is below the top of protrusion 114 and the section of standoff layer 118 covering protrusion 114 is exposed.

As shown in Fig. 4h, gate layer 124 is deposited essentially directionally over insulating layer 120 and the top exposed portion of standoff layer 118, but not appreciably along the sidewalls of 20 standoff layer 118 (If necessary, small amounts of gate layer 124 on the sidewalls of standoff 118 21 can be removed, for example, by etching for a short time that removes the small amount of gate

#### PATENT APPLICATION

material on the sidewall but retains a useful thickness of gate material on the horizontal surfaces of 1 insulating layer 120 and the top exposed portion of standoff layer 118). Then, standoff layer 118 is 2 preferentially etched to uncover the upper surface 126 of the portion of emitter layer 116 covering 3 protrusion 114 and to provide a gap 128 (Fig. 4i) between insulating layer 120 and the upper portion 4 of the vertical portion of emitter layer 116. This step also removes the portion of gate layer 124 that 5 previously covered that portion 126 of standoff layer 118 and emitter layer 116. Subsequently, the 6 exposed horizontal portion of emitter layer 116 covering protrusion 114 is removed by preferential 7 or directional etching. Then, protrusion 114 is preferentially etched to below the top of the 8 9 remaining vertical portion of emitter layer 116 to provide the structure shown in Fig. 4i. 10 Having described the invention, the following examples are given to illustrate specific 11 applications of the invention including the best mode now known to perform the invention. These 12 specific examples are not intended to limit the scope of the invention described in this application. 13 14 15 **EXAMPLES** 16 17 I. STARTING HOLE STRUCTURE 18 The starting hole structure consisted of a 400nm diameter hole, having a vertical sidewall, 19 which extended downward through a 40nm Cr layer, a 100nm heavily doped p-type amorphous 20 silicon layer, a 400nm thick thermal silicon dioxide, and terminated at about 100nm deep into an 21

• .

•

# PATENT APPLICATION

$\left( \right)$

| 1          | underlying n-type Si(100) substrate. Arrays of lines of 50 holes. spaced at 5 micrometers apart. were            |

|------------|------------------------------------------------------------------------------------------------------------------|

| 2          | fabricated by electron beam lithography in combination with lift-off and reactive ion etching (RIE)              |

| 3          | methods. Each working sample consisted of three of such array of holes and was cut into 1 X 1 cm                 |

| 4          | size from 3-inch diameter wafers.                                                                                |

| 5          |                                                                                                                  |

| . <b>6</b> | II. DEPOSITION AND ETCHING OF THE SPACER LAYER                                                                   |

| 7          | A. Chemical Vapor Deposition of the Spacer SiO <sub>2</sub> layer.                                               |

| 8          |                                                                                                                  |

| 9          | The spacer silicon dioxide layer was deposited by using low-pressure chemical vapor                              |

| 10         | deposition. The starting working sample was first cleaned to remove contaminants on the surfaces,                |

| 11         | especially any passivation layers which might have been present on the sidewalls of the holes as a               |

| 12         | result of reactive ion etching. The sample was placed in a hot-walled quartz reactor tube enclosed               |

| 13         | in a tube oven. After evacuation, and subsequent heating the reactor to 395-400°C, a mixture                     |

| 14         | consisting of 0.6 Torr diethyl silane, 0.6 Torr O <sub>2</sub> and 3 Torr Ar were flowed into the reactor. After |

| 15         | 25 minutes of deposition, the gases were shut off. The resulting SiO <sub>2</sub> layer on the top horizontal    |

| 16         | surface was later measured to be about 160 nm thick. However, the deposited $SiO_2$ layer on the                 |

| 17         | sidewall of the hole appeared to be thinner.                                                                     |

| 18         |                                                                                                                  |

| 19         | B. Etch-back of the $SiO_2$ layer                                                                                |

| 20         |                                                                                                                  |

| 21         | In a commercial reactive ion etcher, the $SiO_2$ layer was etched away from the top horizontal                   |

|            |                                                                                                                  |

Ċ

# PATENT APPLICATION

(

| 1  | surface until the Cr metal was exposed. This etching step also removed the SiO <sub>2</sub> layer from the             |

|----|------------------------------------------------------------------------------------------------------------------------|

| 2  | bottom of the hole.                                                                                                    |

| 3  |                                                                                                                        |

| 4  |                                                                                                                        |

| 5  |                                                                                                                        |

| 6  | II. FABRICATION OF FEAs WITH Ru/Li/Ru THIN FILM EMITTER                                                                |