## UNCLASSIFIED

## AD NUMBER

## ADB073968

## NEW LIMITATION CHANGE

### TO

Approved for public release, distribution unlimited

## FROM

Distribution limited to U.S. Gov't. agencies only; Contractor Performance Evaluation; Aug 81. Other requests for this document must be referred to AFWAL/ADE, Wright-Patterson AFB, OH 45433.

## AUTHORITY

AFRL ltr, 26 Mar 2001.

THIS PAGE IS UNCLASSIFIED

ADB U739

AFWAL-TR-83-1084

Harris Corporation Government Information Systems Division Melbourne FL 32901

Final Technical Report

August 1981

Distribution limited to U.S. Government agencies only; Contractor Performance Evaluation; Aug 81. Other requests for this document must be referred to AFWAL/AADE, Wright-Patterson AFB, Uhio 45433.

#### SUBJECT TO EXPORT CONTROL LAWS

This document contains information for manufacturing or using munitions of war. Export of the information contained herein, or release to foreign nationals within the United States, without first obtaining : an export license, is a violation of the International Traffic-in-Arms Regulations. Such violation is subject to a penalty of up to 2 years imprisonment and a fine of \$100,000 under 22 USC 2778.

Include this notice with any reproduced portion of this document.

Avionics Laboratory Air Force Wright Aeronautical Laboratories Air Force Systems Command Wright-Patterson Air Force Base, Ohio 45433

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

This technical report has been reviewed and is approved for publication.

GEORGE A HIGH

Project Engineer

ROBERT M. WERNER, Chief VLSI Group Microelectronics Branch

FOR THE COMMANDER

STANLEY E. WAGNER Chief Microelectronics Branch Electronic Technology Division

"If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization please notify AFWAL/AADE-1, W-P AFB, OH 45433 to help maintain a current mailing list."

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

| CURITY CLASSFICATION UP CALL PAGE Anen De<br>REPORT DOCUMENTATIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       | READ INSTRUCTIONS                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                     | BEFORE COMPLETING FORM<br>3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                                  |

| AFWAL-TR-83-1084                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                          |

| TITLE (and Subtitie)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                       | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                                                                                                                       |

| Bus Interface Unit LSI Chip Deve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | elopment                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       | Final                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                                                                                                                         |

| AUTHOR(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>,</u>                                                                                                                                                                                                                                                                              | 8. CONTRACT OR GRANT NUMBER(*)                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                          |

| PERFORMING ORGANIZATION NAME AND ADDRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CC                                                                                                                                                                                                                                                                                    | F33615-77-C-1166                                                                                                                                                                                                                                         |

| Harris Corporation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .55                                                                                                                                                                                                                                                                                   | 10. PPOGRAM ELEMENT, PROJECT, TASK<br>APEA & WORK UNIT NUMBERS                                                                                                                                                                                           |

| Government Information Systems D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ivision                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                          |

| Melbourne FL 32901                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                       | 6096 41 01                                                                                                                                                                                                                                               |

| CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                       | 12. REPORT DATE                                                                                                                                                                                                                                          |

| Electronic Technology Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                       | 8 August 1981                                                                                                                                                                                                                                            |

| AFWAL/AAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                       | 13. NUMBER OF PAGES                                                                                                                                                                                                                                      |

| Wright-Patterson AFB OH 45433 MONITORING AGENCY NAME & ADDRESS(11 dille                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rent from Controlling Office)                                                                                                                                                                                                                                                         | 74<br>15. SECURITY CLASS. (of this report)                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ······································                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       | UNCLASSIFIED                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                       | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                                                                                                                                            |

| DISTRIBUTION STATEMENT (of this Report)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                       | L                                                                                                                                                                                                                                                        |

| Distribution limited to U.s. Gov<br>Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sts for this docum<br>, Ohio 45433.                                                                                                                                                                                                                                                   | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetract enter<br>SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, if different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>SUPPLEMENTARY NOTES<br>None<br>KEY WORDS (Continue on reverse side if necessary                                                                                                                                                                                                                                                                                                                                                                                                                  | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, if different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, if different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetract enter<br>SUPPLEMENTARY NOTES<br>None<br>KEY WORDS (Continue on reverse elde if necessary<br>Serial Data Bus                                                                                                                                                                                                                                                                                                                                                                                               | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, if different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse elde 11 necessary<br>Serial Data Bus<br>MIL-STD-1553B                                                                                                                                                                                                                                                                                                                                                                              | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, if different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse elde 11 necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control                                                                                                                                                                                                                                                                                                                                                           | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro                                                                                                                                                                                                               | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>SUPPLEMENTARY NOTES<br>None<br>KEY WORDS (Continue on reverse side if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control                                                                                                                                                                                                                                                                                                                                                           | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro<br>and identify by block number;<br>end identify by block number;                                                                                                                                             | ent must be referred to                                                                                                                                                                                                                                  |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>SUPPLEMENTARY NOTES<br>None<br>KEY WORDS (Continue on reverse elde if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde if necessary<br>Fhis report describes a large sca                                                                                                                                                                                                                                                                   | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro<br>and identify by block number;<br>and identify by block number;<br>ale integrated (LS                                                                                                                       | ent must be referred to<br>m Report)<br>1) circuit implementation of                                                                                                                                                                                     |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>SUPPLEMENTARY NOTES<br>None<br>KEY WORDS (Continue on reverse side if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse side if necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data but<br>all of the data bus interface fur                                                                                                                                                                                         | sts for this docum<br>, Ohio 45433.<br>end in Block 20, 11 different fro<br>and identify by block number)<br>ale integrated (LS<br>s protocol. Two con<br>nctions. Chip typ                                                                                                           | ent must be referred to<br>a Report)<br>I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync                                                                                                                     |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse elde 11 necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde 11 necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data bus<br>all of the data bus interface fun<br>generation/detection, encoding/dd                                                                                                                                                    | sts for this docum<br>, Ohio 45433.<br>end in Block 20, 11 different fro<br>and identify by block number)<br>ale integrated (LS<br>s protocol. Two cl<br>nctions. Chip type<br>ecoding, terminal                                                                                      | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress                                                                                                                                       |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse elde 11 necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde 11 necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data but<br>all of the data bus interface fun<br>generation/detection, encoding/do<br>recognition, direct memory access                                                                                                               | sts for this docum<br>, Ohio 45433.<br>end in Block 20, 11 different fro<br>and identify by block number;<br>ale integrated (LS<br>s protocol. Two cinctions. Chip type<br>ecoding, terminal<br>s (DMA) functions,                                                                    | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress<br>first level error detection.                                                                                                       |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebetrect enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse eide if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse eide if necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data bus<br>all of the data bus interface fun<br>generation/detection, encoding/do<br>recognition, direct memory access<br>and some mode code responses. The                                                                          | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro<br>and identify by block number;<br>ale integrated (LS<br>s protocol. Two ci<br>nctions. Chip typ<br>ecoding, terminal<br>s (DMA) functions,<br>his chip was produ                                            | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress<br>first level error detection,<br>ced in CMOS technology and                                                                         |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>None<br>KEY WORDS (Continue on reverse elde if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde if necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data bus<br>all of the data bus interface fun<br>generation/detection, encoding/de<br>recognition, direct memory access<br>and some mode code responses. This<br>is available from Harris Corporation                                                        | sts for this docum<br>, Ohio 45433.<br>end in Block 20, 11 different fro<br>and identify by block number)<br>ale integrated (LS<br>s protocol. Two cl<br>nctions. Chip typ<br>ecoding, terminal<br>s (DMA) functions,<br>his chip was produ<br>tion. Chip type #                      | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress<br>first level error detection,<br>ced in CMOS technology and<br>2 was concerned with the                                             |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the obstract enter<br>Supplementary notes<br>None<br>KEY WORDS (Continue on reverse elde 11 necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde 11 necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data bus<br>all of the data bus interface fun<br>generation/detection, encoding/do<br>recognition, direct memory access<br>and some mode code responses. This<br>available from Harris Corporation<br>of complex bus controller func- | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro<br>and identify by block number;<br>ale integrated (LS<br>s protocol. Two cl<br>nctions. Chip typ<br>ecoding, terminal<br>s (DMA) functions,<br>his chip was produ<br>tion. Chip type #<br>tions including co | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress<br>first level error detection,<br>ced in CMOS technology and<br>2 was concerned with the                                             |

| Evaluation; Aug 81. Other reque<br>AFWAL/AADE; Wright-Patterson AFB<br>DISTRIBUTION STATEMENT (of the ebstrect enter<br>None<br>KEY WORDS (Continue on reverse elde if necessary<br>Serial Data Bus<br>MIL-STD-1553B<br>LSI Bus Control<br>ABSTRACT (Continue on reverse elde if necessary<br>This report describes a large sca<br>the MIL-STD-1553B serial data bus<br>all of the data bus interface fun<br>generation/detection, encoding/de<br>recognition, direct memory access<br>and some mode code responses. This<br>is available from Harris Corporation                                                        | sts for this docum<br>, Ohio 45433.<br>ed in Block 20, 11 different fro<br>and identify by block number;<br>ale integrated (LS<br>s protocol. Two cl<br>nctions. Chip typ<br>ecoding, terminal<br>s (DMA) functions,<br>his chip was produ<br>tion. Chip type #<br>tions including co | I) circuit implementation of<br>hips were designed to achieve<br>e #1 is concerned with sync<br>address/subaddress<br>first level error detection<br>ced in CMOS technology and<br>2 was concerned with the<br>mmand word generation, data<br>UNCLASSIED |

Ņ

# UNCLASSIFIED

l

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

buffer address generation, time tagging of data, control codes, programmed interrupts, working registers, mode code responses, and second level error detect functions. Chip type #2 was breadboard in TTL circuits but was <u>not</u> produced in LSI silicon.

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

. .

#### TABLE OF CONTENTS

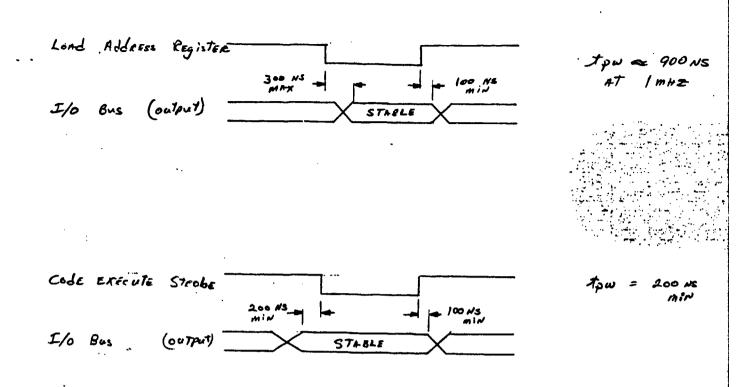

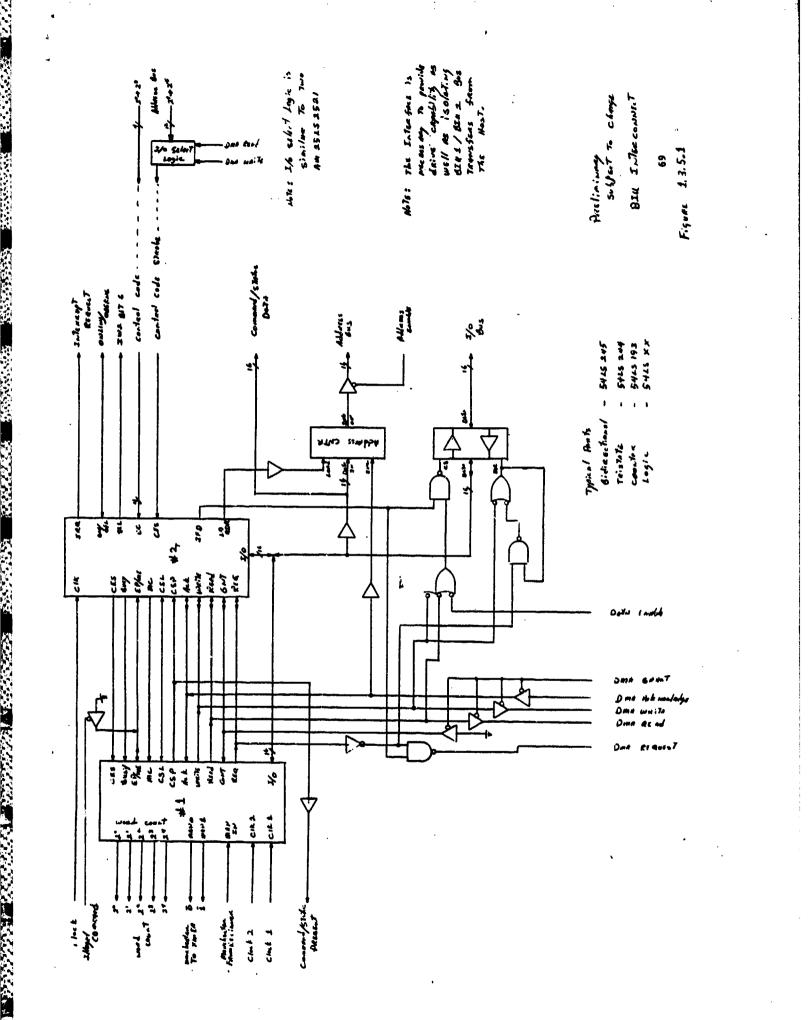

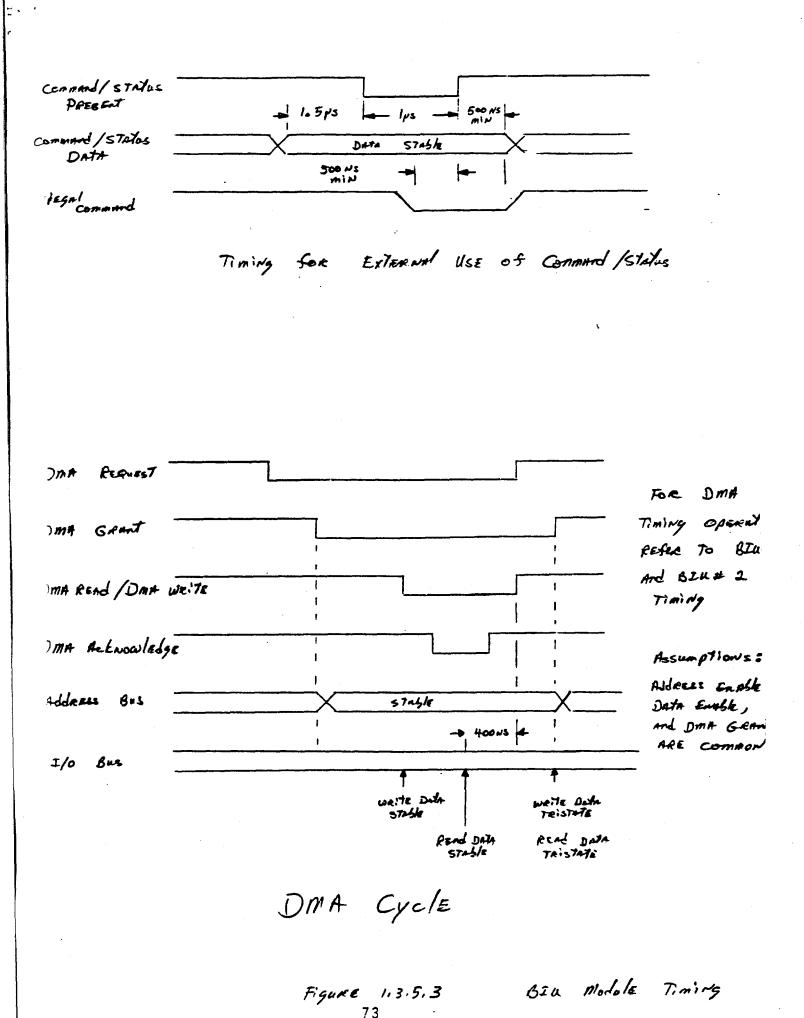

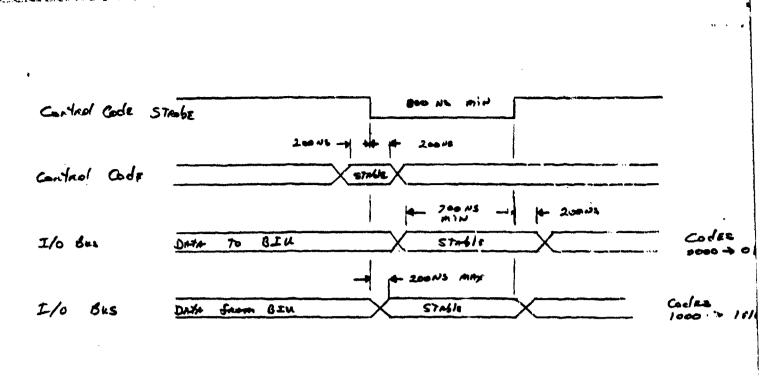

#### Paragraph No. Paragraph Heading Page\_ **BUS INTERFACE UNIT** 1.0 1 1.1 **General Description** 1.2 Detailed Description 11 1.2.1 **BIU Functional Operation** 11 1.2.1.1 Instruction Fetch and Decode 11 Mode Code Command Execution 1.2.1.2 18 1.2.1.2.1 Mode Commands as per 1553B 22 1.2.1.2.2 Mode Commands Implemented by the BIU 25 1.2.1.2.3 Mode Commands Implemented Outside the BIU 28 1.2.1.2.4 Status Word Control 29 1.2.1.3 Interrupt Generation 33 1.2.1.3.1 Interrupts Generated in the Master Controller 34 1.2.1.3.2 Interrupts Generated in the Remote Controller 40 Scenario Used in Interrupt Generation 1.2.1.3.3 41 1.3 Interface 44 1.3.1 **Electrical Characteristics** 44 1.3.2 **Pin Descriptions** 44 1.3.2.1 BIU #1 Pin Description 44 1.3.2.2 **BIU #2 Pin Description** 44 BIU #1 Timing Characteristics 1.3.3 44 BIU #2 Timing Characteristics BIU Chip Set "Module" Characteristics 1.3.4 44 1.3.5 68 1.3.5.1 Logic Considerations 68 1.3.5.2 Pin Descriptions 68 1.3.5.3 Timing Characteristics 68

#### TABLE OF FIGURES

| Figure No.                                                 | Figure Heading                                                                                                                                                                                     | Page                       |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.1-1<br>1.1-2<br>1.1-3<br>1.1-4<br>1.1-5<br>1.1-6         | System Use of the BIU<br>BIU Within the Host Box<br>Basic Block Diagram of BIU #1<br>BIU #1 Functional Pinout<br>Simple Remote Terminal<br>Interface to 8086A-Based Processor                      | 1<br>1<br>3<br>4<br>6      |

| 1.1-9<br>1.1-10<br>1.1-11                                  | BIU #2 Basic Block Diagram<br>Interconnection of BIU #1, #2, and Host<br>BIU #2 Functional Pinout                                                                                                  | 9<br>9<br>10               |

| 1.2.1.1-1 $1.2.1.1-2$ $1.2.1.1-3$ $1.2.1.1-4$ $1.2.1.1-5$  | Typical Pointer Block Used by BIU &<br>Typical Message-Data Buffer<br>Format for Instruction Word Pair<br>Connection to Host Address Bus<br>Summary of Master Controller BIU Message<br>Processing | 12<br>13<br>14<br>16<br>17 |

| 1.2.1.2-1<br>1.2.1.2-1<br>1.2.1.2.4-1<br>1.2.1.2.4-2       | Summary of Remote Controller BIU Message<br>Processing<br>Status Word Format<br>ME BIT ORed Circuit<br>TF BIT ORed Circuit                                                                         | 19<br>31<br>31             |

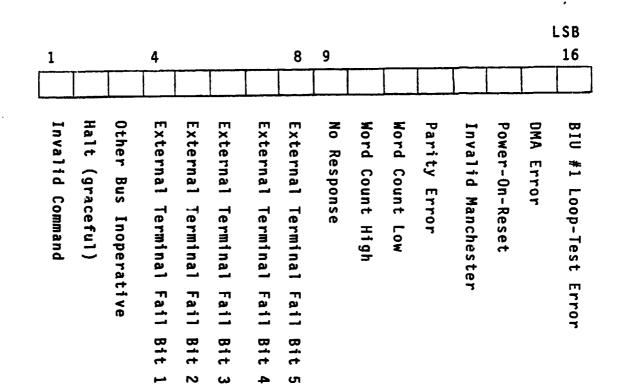

| $1.2.1.3.1-1 \\ 1.2.1.3.1-2 \\ 1.2.1.3.1-3 \\ 1.2.1.3.3-1$ | BIT Word Format<br>Internal Status Register (ISR)<br>Typical Data Bus Messages<br>Processor Control Word Format                                                                                    | 35<br>36<br>37<br>42       |

#### BUS INTERFACE UNIT (BIU)

#### 1.1

1.0

#### <u>General Description</u>

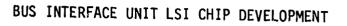

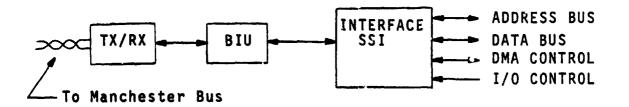

The BIU is an LSI approach to implementation of the interface between a host electronics and a manchester data bus. With such an interface, a group of up to 31 hosts can transfer information between each other on the serial data bus. Figure 1.1-1 illustrates BIU usage.

At the manchester bus interface the BIU accepts serial bi-phase data or generates serial bi-phase data. At the host electronics interface the BIU accepts instructions from the host, and by way of these instructions, transfers parallel data to and from the host. Within a host box, the BIU resides between a transmitter/receiver unit and the internal, parallel data and address buses as shown in Figure 1.1-2.

FIGURE 1.1-2 BIU WITHIN THE HOST BOX

MIL-STD-1553B forms the protocol basis for the BIU. Within 1553B, the hosts relate to each other as "remotes" or "controllers". At any one instart, one host is recognized as the controller, all the remaining hosts are considered remotes. Provision is made in 1553B and the BIU to allow for dynamic reassignment of these roles.

As a remote, the BIU is first programmed by its host through the use of I/O control transfers. Then, the BIU is capable of carrying out data transfers to and from the host memory via DMA. In this situation the BIU is stimulated by command words from the data bus.

As a controller, the BIU is first programmed by its host as above. After programming, the BIU is capable of executing the stored program code in host memory. This allows the BIU to develop the appropriate bus commands and handle data associated with these commands. This also allows the BIU to handle automatic retries and to pass interrupts to the host when retries fail or other conditions warrant.

In summary, the BIU off-loads the bus interface function from the host in either remote or controller situations and acts as an integrated DMA channel between the serial bus and host memory.

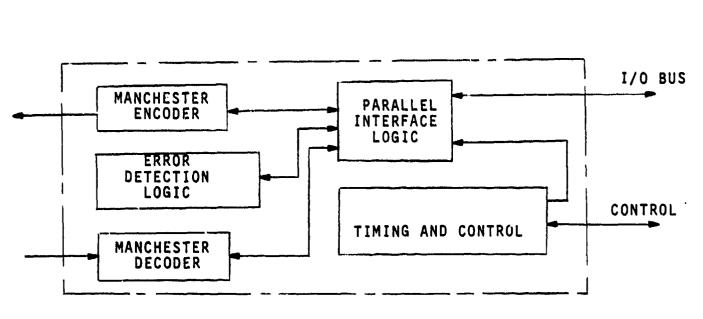

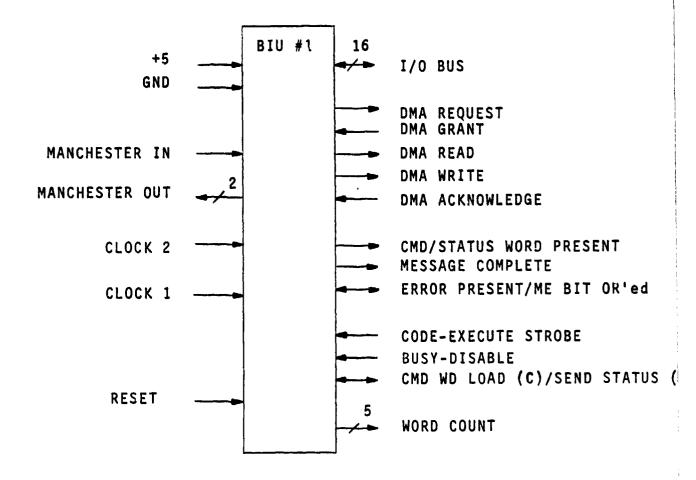

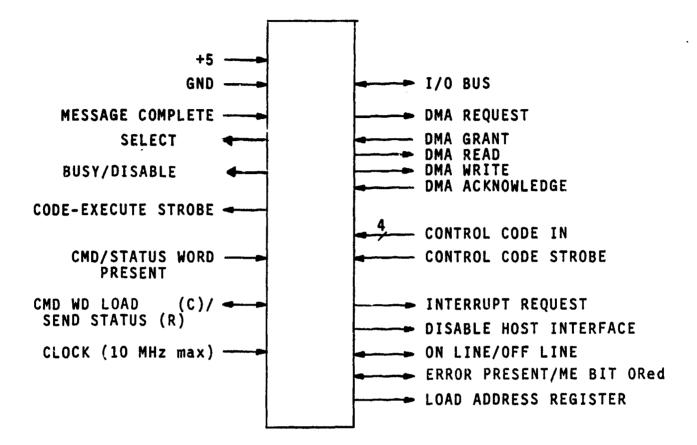

Physically, the BIU is contained in two LSI chips. In the most elemental applications, Chip #1 can be used without Chip #2. This is especially true if the selected host will never assume the role of controller. A basic block diagram of BIU #1 is given in Figure 1.1-3. Referring to the figure, some of the control lines allow for initialization and for the transfer of words (command words, status words, and error words) through the chip's I/O interface. Other control lines (the DMA controls) allow for the transfer of data words through the I/O. A functional pinout is given in Figure 1.1-4.

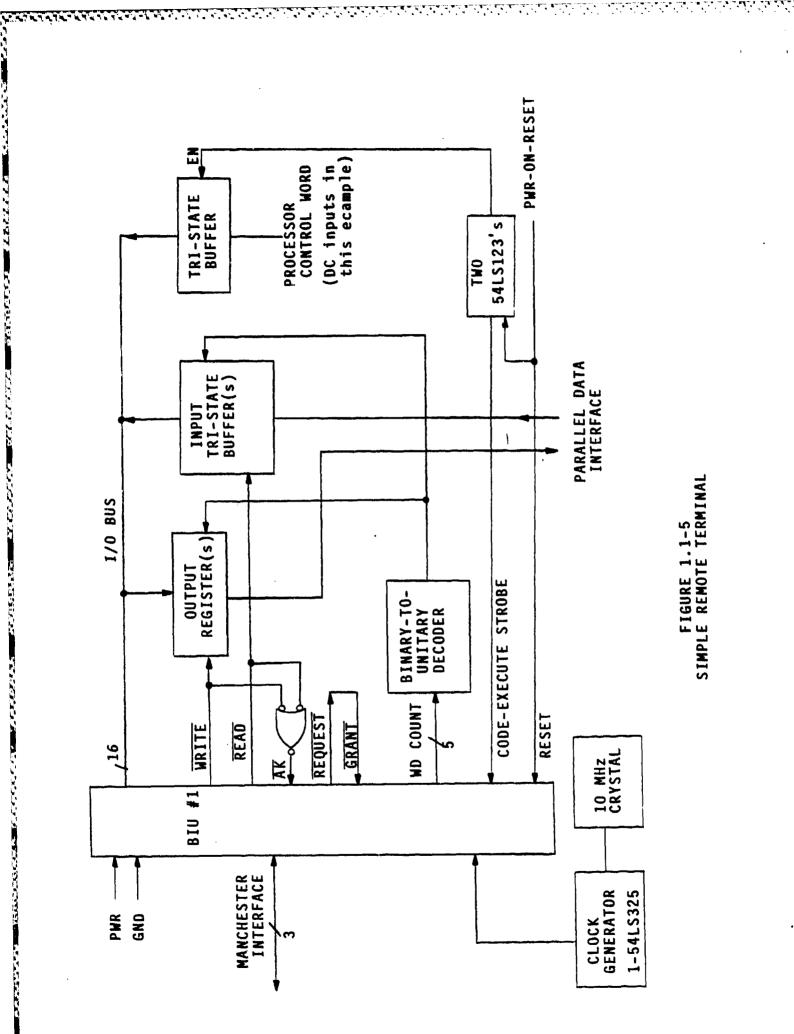

Figure 1.1-5 illustrates BIU #1 embedded in a simple host. Referring to the figure, the various logic elements are assumed CMOS compatible and connect directly to the BIU. The application is set up with output registers ready to accept data from the BIU when it outputs data on its I/O bus. Data is supplied to the BIU's I/O bus when requested through input tristate buffers. The flow of data is controlled by word count decodes and the read and write lines. The binary-to-unitary decoder (e.g., CD4028B) converts the word count into discrete lines which select both an input tri-state buffer and an output register. Input or output is then determined by an active read or active write. To satisfy the DMA handshake requirements in

2559.0

FIGURE 1.1-3 BASIC BLOCK DIAGRAM OF BIU #1

FIGURE 1.1-4 BIU #1 FUNCTIONAL PINOUT

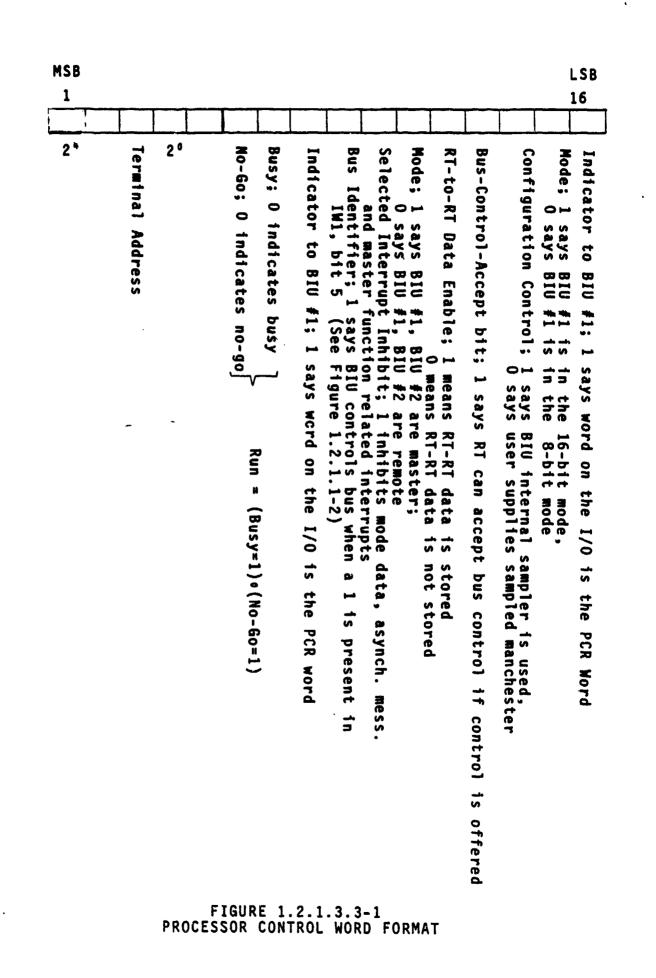

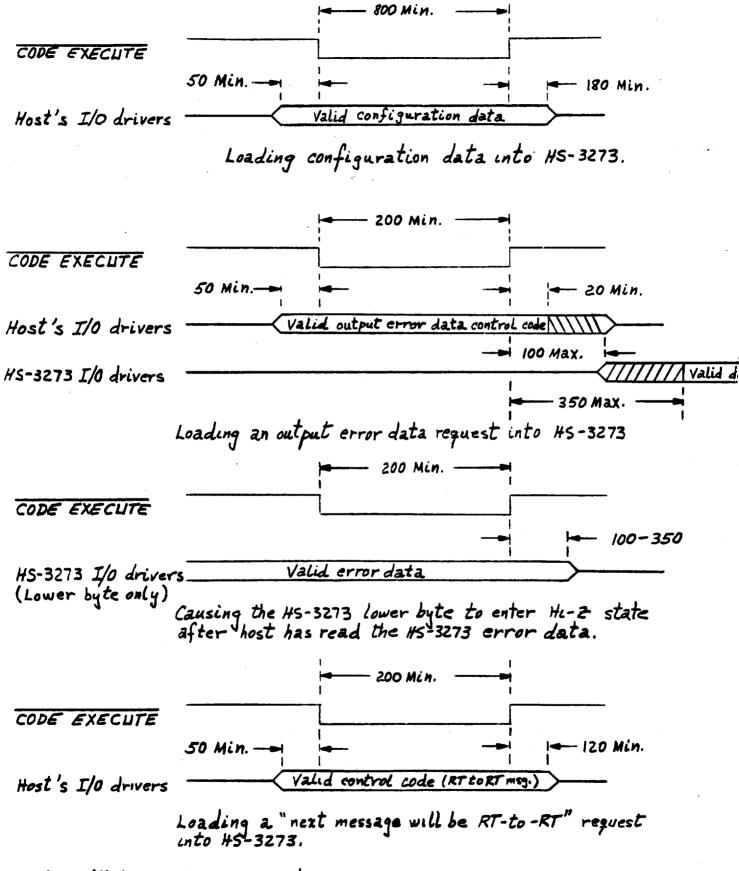

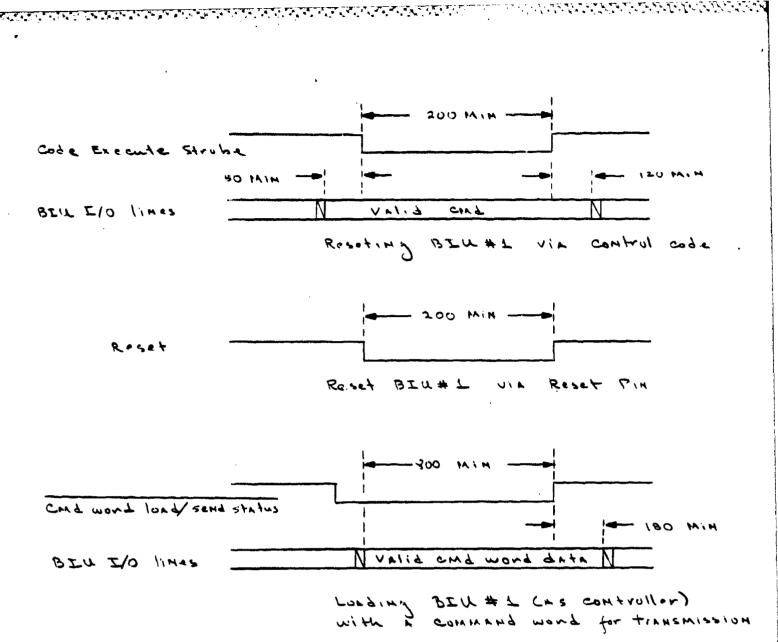

this case, request is fed into the grant input and the OR of write or read is fed into the acknowledge input. Initialization is satisfied by sending the BIU a control word through a separate tri-state buffer. Initialization occurs when the code-execute strobe goes active and  $2^{\circ}$  of the I/O bus is set high. Under these conditions, the BIU treats bits  $2^{15}$  - $2^{1}$  in a special way. The control word conveys mode information (8-bit/16-bit and controller/remote), box address, bus-accept status and manchester input configuration control. At power-up, the BIU is reset via the power-on-reset signal. This same signal strobes two of the four single-shots in the two packages of 54LS123's. One of the strobed single-shots enables the processor control word to pass through a set of tri-state buffers to the BIU; the other acts as a delay and then as a trigger to a third single-shot. The third single-shot supplies the code-execute strobe to the BIU and causes it accept the processor control word.

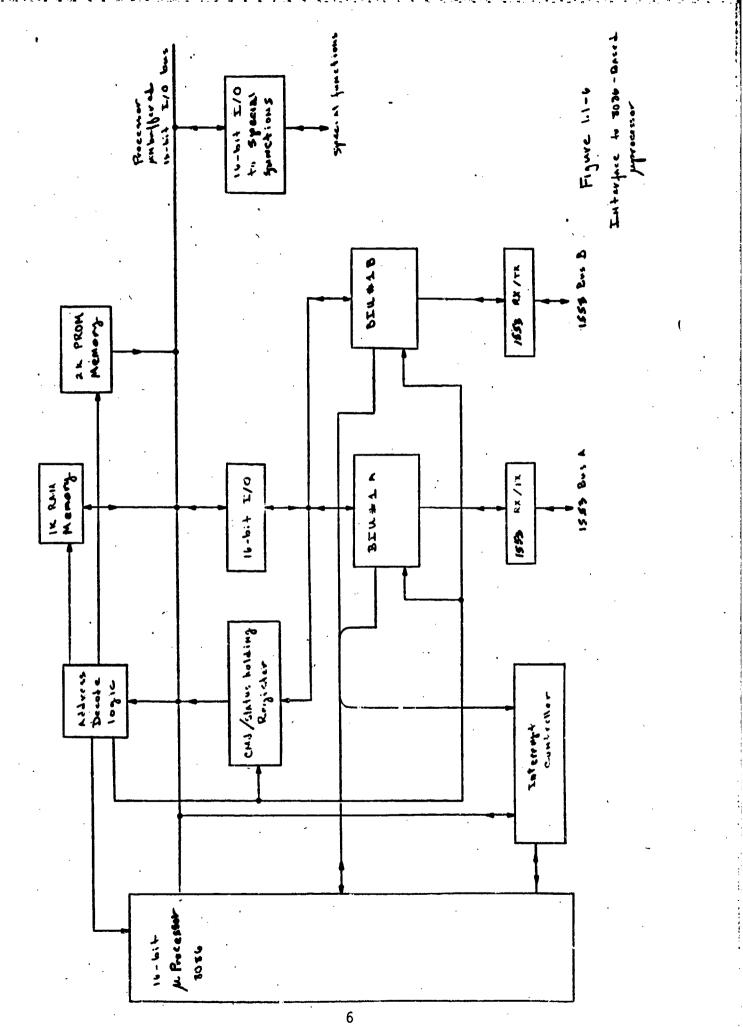

A more general application of Chip #1 without Chip #2 is given in Figure 1.1-6. In that figure, two BIU #1 Chips drive redundant buses on their serial bus side and connect together and to the 8086 I/O bus on their parallel bus side. The data path connection to the 8086 is via a set of bidirectional drivers and a register called the CMD/Status Holding Register.

In the 8086 application, communication occurs via different modes. When the 8086 communicates with the BIU Chips, it treats chip functions as memory mapped I/O's; e.g., a command word loaded into BIU #1A is sent to an address representing that function; a command word loaded into BIU #1B is sent to a different address representing that function; etc. When a BIU communicates with its host, it deposits command words and status words into the CMD/Status Holding Register; these are then available to the 8086 via memory-mapped I/O. Data word communication takes place using DMA. Service by the 8086 is linked through interrupts. A detailed block diagram of a BIU/8086 interface is given in Figure 1.1-7.

BIU #2, as was mentioned above, enhances BIU #1. BIU #2 provides controller capability such that BIU #2 can drive BIU #1 and the two chips thereby implement the bus controller function. BIU #2 contributes the following capabilities:

- Instruction-fetch via DMA,

- 2) Message-command-word generation,

- 3) Data-buffer address generation,

- 4) Time-tagging of the data stored in host memory by BIU #1,

- 5) Mode code command execution, and

- 6) Interrupt generation.

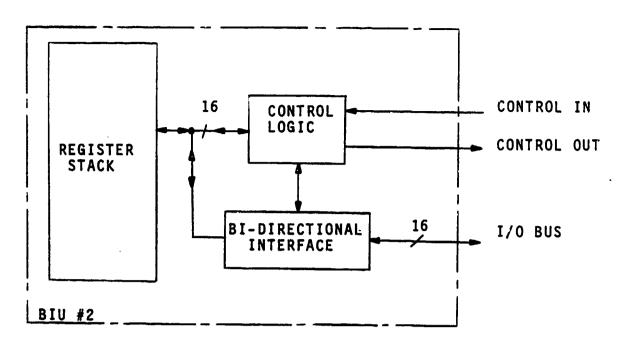

Because of the nature of BIU #2's activities, BIU #2 is basically a register stack with appropriate control logic. A basic block diagram of BIU #2 is given in Figure 1.1-9.

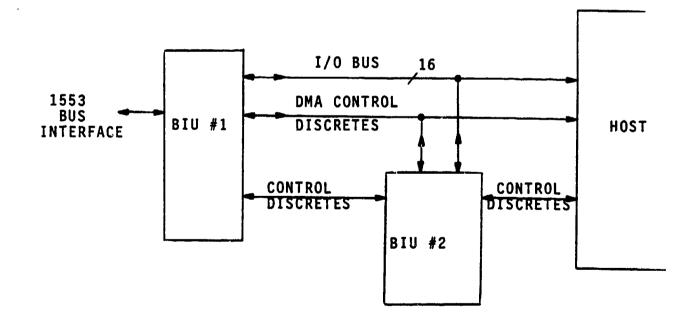

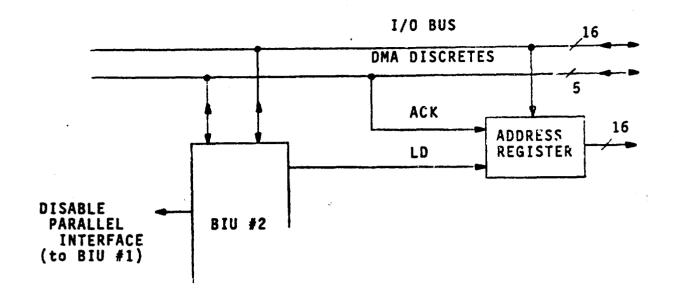

The input and output control lines are split into two groups; those to and from the host, and those to and from BIU #1. The I/O bus is shared and is tied to both host and BIU #1. The basic interconnection between BIU #1, #2, and the host is given in Figure 1.1-10.

When the hardware of Figure 1.1-10 operates in the Master Mode, BIU #2 is set up by the host. The host sends it the instruction address, a base address, and minor cycle time value. It sends both BIU #1 and #2 the processor control word. With these, BIU #2 proceeds to command generation and data buffer address generation. When command generation is completed for a given message, BIU #1 is given the command word(s) and ordered to transmit. **BIU #1 deducts whether the message is an RT-transmit or RT-receive** message or a mode command and how many words are involved in the transfer. With this information, BIU #1 proceeds with the message implementation and BIU #2 waits for control information. During the actual data transfers, BIU #1 handles the DMA operation. If errors are encountered during the message handling operation, BIU #2 is notified via a discrete control line; the nature of the error is catalogued in BIU #1's error register. Once a message is complete, BIU #2 is notified and it proceeds with appropriate action. If the message involved an error, BIU #2 decides (from information in the instruction words associated with the message) whether a re-try is appropriate and, if not, the error conditions from BIU #1 are moved into BIU #2 and an interrupt generated. If the message is error free, BIU #2 acquires the next instruction words needed to generate the command(s) and data buffer address associated with the next message.

When the hardware of Figure 1.1-10 operates in the Remote Mode, BIU #2 is set up by the host. But, in this mode, BIU #2 only requires the base address word and the control word. BIU #2 still has the task of data buffer address generation. In this situation, BIU #1 signals BIU #2 when a command word for the remote controller has arrived so that BIU #2 will prepare the buffer address. With the address generated, BIU #1 handles all the data transfers by generating the appropriate DMA control signals just as it did in the controller mode.

FIGURE 1.1-9 BIU #2 BASIC BLOCK DIAGRAM

FIGURE 1.1-10 INTERCONNECTION OF BIU #1, #2, AND HOST

The functional pin out of BIU #2 is given in Figure 1.1-11.

NAMARA TITIII DILANG DILANG TINGGAN TANANG ANALANG TANANAN TANANG TANANG TANANG TANANG TANANG TANANG TANANG TAN

FIGURE 1.1-11 BIU #2 FUNCTIONAL PINOUT

#### **Detailed Description**

1.2

This detailed description attempts to supply sufficient information to simplify application of the BIU; it concentrates on the algorithmic aspects of the chips. Following this, section 1.3 supplies a different kind of detail; it concentrates on pin descriptions, timing wave forms etc.

#### 1.2.1 BIU Functional Operation

Back in the general discussion, BIU #1 and #2 were credited with various capabilities. Considering the two chips together, the combined capabilities,

1) instruction fetch via DMA,

2) message command word generation,

3) data buffer address generation,

message data handling,

5) time tagging of the data in the data buffers,

- 6) mode command execution, and

- 7) interrupt generation, now will be covered in detail.

#### 1.3.1.1 Instruction Fetch and Decode

Five major items are covered in this section:

- 1) data buffer structure,

- 2) the fetch cycle,

- 3) command word generation,

- 4) data buffer address generation, and

- 5) time tag generation.

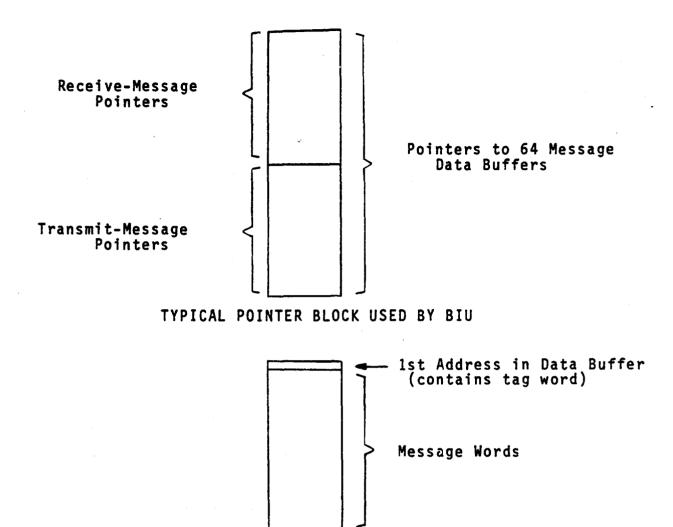

The BIU assumes all message data is packed in data buffers accessed indirectly through pointer blocks. Each buffer contains N+1 addresses so a data buffer can hold a tag word and the N message words appropriate to a particular message. The pointer which points to the first address of a given data buffer is to be found in a block of 64 pointers. Any time the BIU reads message words from or writes messages words into host memory, it must first generate the address of the pointer, acquire the pointer and then access the corresponding message-data buffer. To see how this is accomplished, let us look at how the instructions are decoded.

TYPICAL MESSAGE-DATA BUFFER

FIGURE 1.2.1.1-1

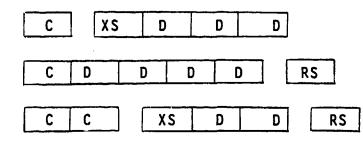

During initialization the BIU is given data for its Instruction Address Register (IAR) which points the BIU to its stored program. Instructions there are arranged in pairs; the format is given in Figure 1.2.1.1-2. The BIU is also given a Base Address Register (BAR) word; with this and the instruction words it can develop the address into the pointer block and find the data buffer. In a fetch sequence the IAR contents are placed on the 16-bit I/O bus and loaded into an external register. The first of a pair of DMA sequences occurs and the first instruction word is acquired. Again, the IAR contents (internally incremented) are placed on

| 1       | 2          | 3          | 4    | 5 | 6 | 7 | 8   | 9 | 10   | 11          | 12   | 13   | 14    | 15    | 16      |

|---------|------------|------------|------|---|---|---|-----|---|------|-------------|------|------|-------|-------|---------|

| OP<br>C | ODE        | RE         | -TRY | в | I |   | REC |   | E DE | EVICE<br>SS | REC  | EIVE | SUBAD | DRESS | /MQDE   |

|         | ORD<br>ODE | COU<br>COD |      |   | s | Т | RAN |   | T DE | VICE<br>SS  | TRAN | SMIT | SUBAD | DRESS | /MQDE . |

LSB

IW1 BIT DESIGNATION

1-2 Normal OP Codes Bit 1-2 00 = Halt BIU01 = Link (Use second word as address of next 2-word instruction) 10 = No Operation (go to next 2-word instruction) 11 = Bus Operation 3-4 Indicates number of retries (0, 1, 2, or 3) 0 = Operation is performed on Bus A 5 1 = Operation is performed on Bus B 6 1 = Interrupt processor upon successful bus operation 7-11 Receive terminal addresses 12-16 00000, 11111 = mode command operation 00001 \_\_\_\_ Receive terminal subaddress \_ \_ \_ 11101. 11110 = Asychronous message

| IW2 | BIT   | DESIGNATION                                    |

|-----|-------|------------------------------------------------|

|     | 1-5   | Word count or mode command code                |

|     | 5     | Select = Select Bit 0 = Select Output = "O"    |

|     |       | Select Bit 1 = Select Output = "1"             |

|     | 7-11  | Transmit terminal addresses                    |

|     | 12-16 | 00000, 11111 = mode command oreration $000017$ |

|     |       | Transmit terminal subaddress                   |

|     |       | 11110 = asychronous message                    |

FIGURE 1.2.1.1-2 FORMAT FOR INSTRUCTION WORD PAIR

13

FIGURE 1.2.1.1-3 CONNECTION TO HOST ADDRESS BUS

the 16 bit I/O and loaded into the external register. BIU #2 initiates a second DMA cycle and acquires the second instruction word. (The IAR is incremented again internally to prepare for the next fetch operation).

Once the two instruction words are acquired, BIU#2 can construct the command words. Referring to Figure 1.2.1.1-2 BIU #2 compares its terminal address (available from the control word (PCR word) given to it when setup by the host) with the device addresses in the instruction words. If BIU#2's address is the same as the Receive-Device Address, then the command to be generated is a transmit command to an RT. If BIU #2's address is the same as the Transmit-Device Address, then the command to be generated is a receive command to an RT. If BIU#2's address does not compare with either device address, then an RT-to-RT pair of commands is to be generated. As part of BIT, BIU#2 checks to assure the Receive-Device Address is different from the Transmit-Device Address. (Bit 5 of the Internal Status Word is set when the two are the same.)

When a command is generated, BIU #2 generates a corresponding data buffer address. As mentioned above, BIU #2 is given a Base Address Register (BAR) word. BIU #2 appends six bits (the T/R bit and the master's subaddress bits) to the LS end of the BAR word to form an address into a pointer table. The pointer, acquired from the table, points to the first address in the data buffer. This first address is reserved and the pointer to it is stored in the Pointer Register of BIU #2. The incremented value (pointing to the second address of the data buffer) is then loaded into the external address register--ready for use by BIU #1 when it executes its DMA transfers. Once the data buffer address is set up, BIU #2 is ready to transfer the command word to BIU #1 and command BIU #1 to transmit. From that point, BIU #1 handles the DMA data transfers. If the message is an RT-Receive message, the data transfers by BIU #1 complete the message process. However, if the message is an RT-Transmit message, the data transfers by BIU #1 are followed by a final DMA transfer by BIU #2 of the tag word into the first address of the data buffer. This process is summarized in Figure 1.2.1.1-4.

The discussion above assumed the BIU configured as a controller. In the remote mode, command generation doesn't apply. However, buffer address generation does. This process is summarized in Figure 1.2.1.1-5.

and the second second

- BIU #2 DMA's instruction words 1, 2 from host.

- BIU #2 compares its terminal address with those in the instruction words.

- When a compare is found, the subaddress/mode field corresponding to that device address constitutes the master's subaddress. When no compare is found, an RT-to-RT message is to be executed and the subaddress used in RT-Receive command of the 2-command sequence constitutes the master's subaddress.

- BIU #2 appends the T/R and master's subaddress bits to the LS end of the BAR word to form a 16-bit address into a pointer table:

1.00

| <br>             |     | <u>L3B</u>             |

|------------------|-----|------------------------|

| ADDRESS<br>bits) | T/R | SUBADDRESS<br>(5 bits) |

È

- BIU #2 DMA's pointer from pointer table; pointer is the location of the first address in the data buffer.

- Pointer is stored in BIU #2's Pointer Register.

- BIU #2 loads incremented value of pointer into external address register.

- BIU #2 generates command word.

- BIU #2 transfers command word to BIU #1.

- BIU #1 handles data DMAs (data storage in RT-RT messages is optional).

- When data is stored in host memory by the BIU, the final data DMA by BIU #1 is followed by a DMA by BIU #2 of the tag word into the first address of the data buffer. The tag word transferred contains the minor cycle number, word count and the data error bit:

|                              |                        | LSB |

|------------------------------|------------------------|-----|

| MINOR CYCLE NO.<br>(10 bits) | WORD COUNT<br>(5 bits) | DE  |

#### FIGURE 1.2.1.1-4 SUMMARY OF BIU CONTROLLER MODE MESSAGE PROCESSING

BIU #1 receives an RT-Transmit or an RT-Receive command.

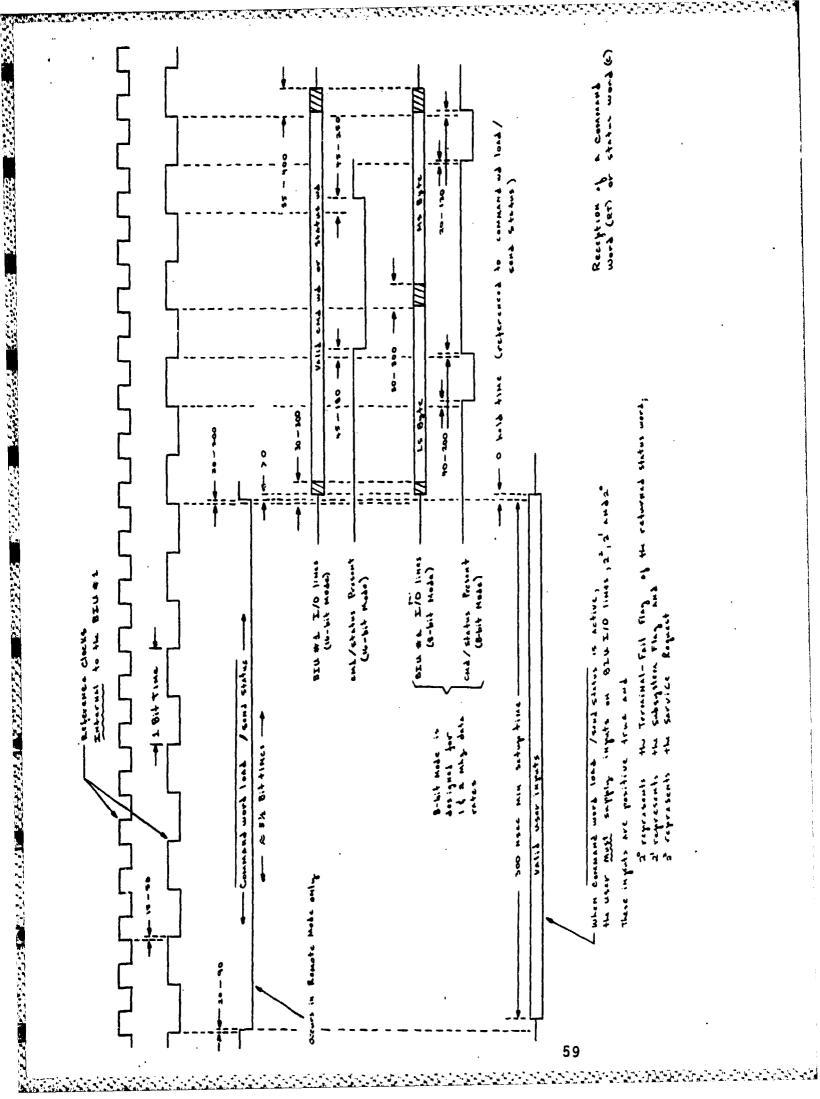

- BIU #1 signals to BIU #2 that a command word is present and passes the command word to BIU #2 via the I/O lines.

- BIU #2 determines the command is an RT-Transmit or an RT-Receive command and begins data buffer address generation.

- BIU #2 appends the T/R and subaddress bits of the command word to the LS end of a 10-bit base address to form a 16-bit address into a pointer table.

- BIU #2 DMA's pointer from pointer table; pointer is the location of the first address in the data buffer.

- Pointer is stored in BIU #2's Pointer Register.

- BIU #2 loads incremented value of pointer into external address register.

- BIU #1 handles data DMAs.

In the case of an <u>RT-Receive</u> message, the final data DMA by BIU #1 is followed by a DMA by BIU #2 of the tag word into the first address of the data buffer.

> FIGURE 1.2.1.1-5 SUMMARY OF BIU REMOTE MODE MESSAGE PROCESSING

المحتج والمعادية والمتحد والمتعاد والمتعاد والمتعاد والمعادي والمعادي والمعاد والمعاد والمعاد والمعاد

#### 1.2.1.2 MODE CODE COMMAND EXECUTION

The mode codes represent commands for action other than the simple transfer of data. Their use is primarly for data and error management. The codes are divided into two groups, those without an associated data word and those with an associated data word. The list of mode commands is given in Table 1. Codes 00000 through 01111 inclusive represent the codes without an associated data word.

#### TABLE 1

#### MODE CODES

| MODE CODE | MODE COMMAND                           | T/R BIT          |

|-----------|----------------------------------------|------------------|

| 00000     | Dynamic Bus Control                    | 1                |

| 00001     | Synchronize                            | 1                |

| 00010     | Transmit Status Word                   | 1                |

| 00011     | Initiate Self Test                     | ī                |

| 00100     | Transmitter Shutdown                   | ī                |

| 00101     | Override Transmitter Shutdown          | ĩ                |

| 00110     | Inhibit T/F Flag                       | 1                |

| 00111     | Override Inhibit T/F Flag              | ī                |

| 01000     | Reset Remote Terminal                  | 1                |

| 01001     | (Reserved)                             | -                |

| 01010     | •                                      | •                |

| 01011     | •                                      | •                |

| 01100     | •                                      | •.               |

| 01101     | •                                      | •                |

| 01110     | •                                      | •                |

| 01111     | (Reserved)                             | -                |

| 10000     | Transmit Vector Word                   | 1                |

| 10001     | Synchronize                            | 0                |

| 10010     | Transmit Last Command                  | 0<br>1<br>1<br>0 |

| 10011     | Transmit the BIT Word                  | 1                |

| 10100     | Selected Transmitter Shutdown          | 0                |

| 10101     | Override Selected Transmitter Shutdown | 0                |

| 10110     | (Reserved)                             | -                |

| •         | e                                      | •                |

| •         | •                                      | •                |

| 11111     | (Reserved)                             | -                |

|           |                                        |                  |

The MIL-STD-1553B description of the mode codes is covered in paragraph 1.2.1.2.1. This description is too broad to define BIU operation; so, paragraphs 1.2.1.2.2, 1.2.1.2.3 and 1.2.1.2.4 detail just how the BIU fits within the standard.

A CONTRACTOR OF A CONTRACTOR OF

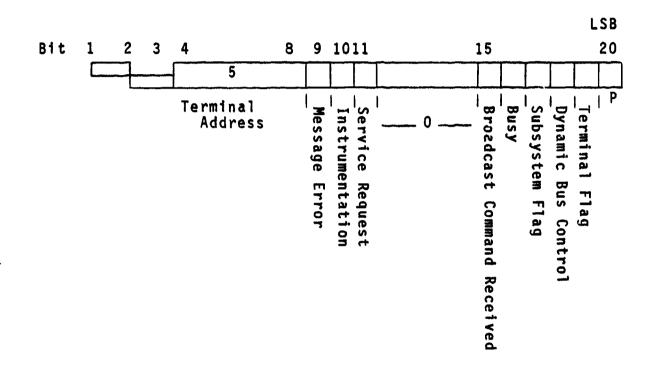

Mode codes and the status word are intimately linked, so the status word format and bit descriptions from MIL-STD-1553B are given below.

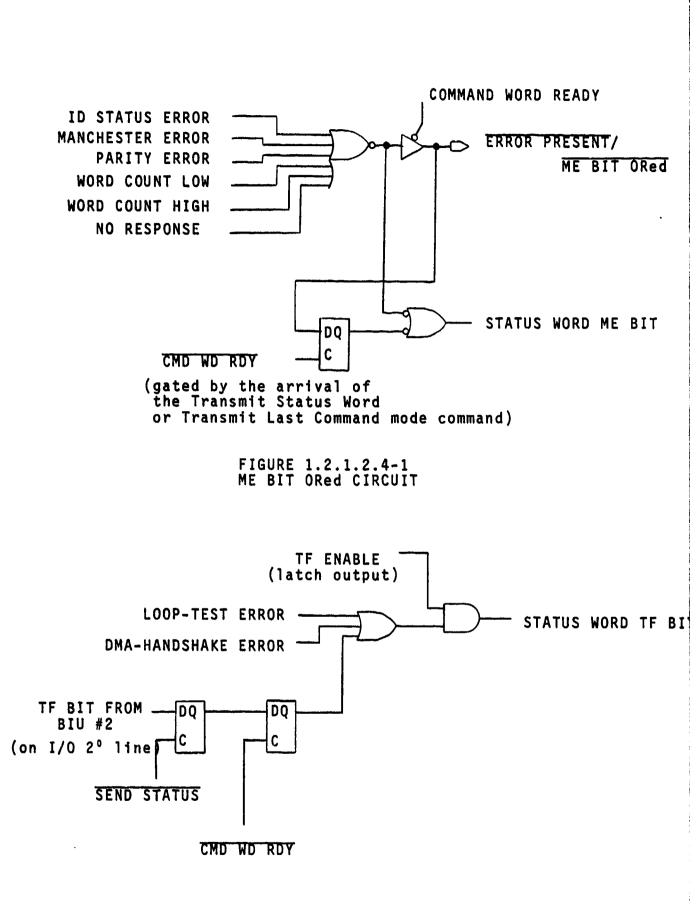

FIGURE 1.2.1.2-1 STATUS WORD FORMAT

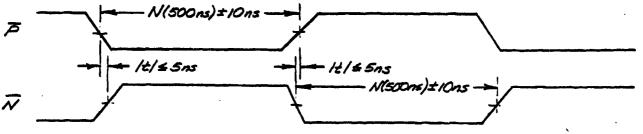

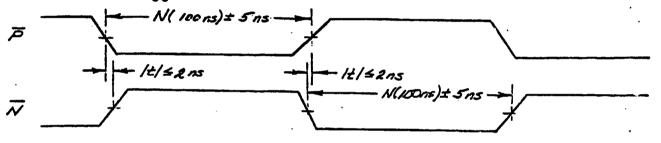

SYNC: The sync waveform shall be as specified in Figure 1.2.1.2-1.

<u>RT ADDRESS</u>: The next five bits following the sync shall contain the address of the terminal which is transmitting the status word.

MESSAGE ERROR BIT: The status word bit at bit time nine shall be utilized to indicate that one or more of the data words associated

with the preceding receive command from the bus controller has failed to pass the RT's validity tests. A Logic One shall indicate the presence of a message error, and a Logic Zero shall show its absence. All RTs shall implement the message error bit.

<u>INSTRUMENTATION BIT</u>: Bit time ten of the status word shall be reserved for the instrumentation bit and shall always be a Logic Zero. This bit is used in conjunction with a Logic One in bit time ten of the command word to distinguish between a command word and status word. The use of the instrumentation bit in this manner is optional.