## UNCLASSIFIED

## AD NUMBER

## ADB004725

## LIMITATION CHANGES

## TO:

Approved for public release; distribution is unlimited.

## FROM:

Distribution authorized to U.S. Gov't. agencies only; Test and Evaluation; DEC 1974. Other requests shall be referred to Air Force Armament Laboratory, DLJA, Eglin AFB, FL 32542.

# AUTHORITY

AFATL ltr, Feb 1977

THIS PAGE IS UNCLASSIFIED

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                           | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER 2. GOVT ACCES                                                                                                                                                                                                                                                                | SION NO. 3 RECIPIENT'S CATALOG NUMBER                                                                                  |

| AFATL-TR-74-208                                                                                                                                                                                                                                                                            |                                                                                                                        |

| TITLE (and Subtitie)                                                                                                                                                                                                                                                                       | S. TYPE OF REPORT & PERIOD COVERED                                                                                     |

| PILOT'S COCKPIT WEAPON CONTROL PANEL                                                                                                                                                                                                                                                       | Final Report - 18 Mar. 1974                                                                                            |

| TILOT 5 COCKFIT WEAFON CONTROL FANEL                                                                                                                                                                                                                                                       | to 15 September 1974                                                                                                   |

|                                                                                                                                                                                                                                                                                            | 6 PERFORMING ORG. REPORT NUMBER                                                                                        |

| AUTHOR(a)                                                                                                                                                                                                                                                                                  | 8. CONTRACT OR GRANT NUMBER(*)                                                                                         |

| Earl R. Strandt                                                                                                                                                                                                                                                                            | F08635-74-C-0090                                                                                                       |

| Douglas R. Hovda                                                                                                                                                                                                                                                                           |                                                                                                                        |

| William L. Walters<br>PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                             |                                                                                                                        |

|                                                                                                                                                                                                                                                                                            | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                         |

| Delco Electronics Division, General Motors                                                                                                                                                                                                                                                 | Corp. Project No. 2070                                                                                                 |

| 6767 Hollister Avenue<br>Goleta, California 93017                                                                                                                                                                                                                                          | Task No. 04                                                                                                            |

|                                                                                                                                                                                                                                                                                            | Work Unit No. 001                                                                                                      |

| Air Force Armament Laboratory                                                                                                                                                                                                                                                              | December 1974                                                                                                          |

| Air Force Systems Command                                                                                                                                                                                                                                                                  | 13. NUMBER OF PAGES                                                                                                    |

| Eglin Air Force Base, Florida 32542                                                                                                                                                                                                                                                        | 55                                                                                                                     |

| 4. MONITORING AGENCY NAME & ADDRESS(II different from Controlling                                                                                                                                                                                                                          |                                                                                                                        |

|                                                                                                                                                                                                                                                                                            | UNCLASSIFIED                                                                                                           |

|                                                                                                                                                                                                                                                                                            |                                                                                                                        |

|                                                                                                                                                                                                                                                                                            | 15. DECLASSIFICATION DOWNGRADING                                                                                       |

| DISTRIBUTION STATEMENT (of this Report)<br>Distribution limited to U. S. Government at<br>test and evaluation; distribution limitation<br>requests for this document must be referred<br>Laboratory (DLJA), Eglin Air Force Base, F                                                        | gencies only; this report documents<br>on applied December 1974. Other<br>d to the Air Force Armament                  |

| Distribution limited to U.S. Government at<br>test and evaluation; distribution limitation<br>requests for this document must be referred                                                                                                                                                  | gencies only; this report documents<br>on applied December 1974. Other<br>d to the Air Force Armament<br>lorida 32542. |

| Distribution limited to U.S. Government a<br>test and evaluation; distribution limitation<br>requests for this document must be referred<br>Laboratory (DLJA), Eglin Air Force Base, F                                                                                                     | gencies only; this report documents<br>on applied December 1974. Other<br>d to the Air Force Armament<br>lorida 32542. |

| Distribution limited to U. S. Government at<br>test and evaluation; distribution limitation<br>requests for this document must be referred<br>Laboratory (DLJA), Eglin Air Force Base, F<br>7. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, 11 d<br>8. SUPPLEMENTARY NOTES | gencies only; this report documents<br>on applied December 1974. Other<br>d to the Air Force Armament<br>lorida 32542. |

.

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

# UNC LASSIFIED

#### PREFACE

This program was conducted by the Delco Electronics Division of General Motors Corporation, 6767 Hollister Avenue, Goleta, California, 93017 under Contract No. F08635-74-C-0090 with the Air Force Armament Laboratory, Armament Development and Test Center, Eglin Air Force Base, Florida. Captain Glenn M. Rosander (DLJA) managed the program for the Armament Laboratory. This effort was conducted during the period from 18 March 1974 to 15 September 1974.

This technical report has been reviewed and is approved for publication.

FOR THE COMMANDER: FENDRICK J. SMITH, DR., Co onel, USAF Chief, Munitions Division

## TABLE OF CONTENTS

.

| Section |                                                                                                                                                               | Page                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| I       | INTRODUCTION<br>Background<br>Scope                                                                                                                           | 1<br>1<br>2                          |

| II      | TECHNICAL APPROACH                                                                                                                                            | 3                                    |

| III     | HARDWARE IMPLEMENTATION<br>Switch Matrix<br>Alpha-Numeric Display<br>Processor<br>External I/O<br>Interrupts<br>Built-in Test                                 | 7<br>7<br>19<br>22<br>22<br>31<br>33 |

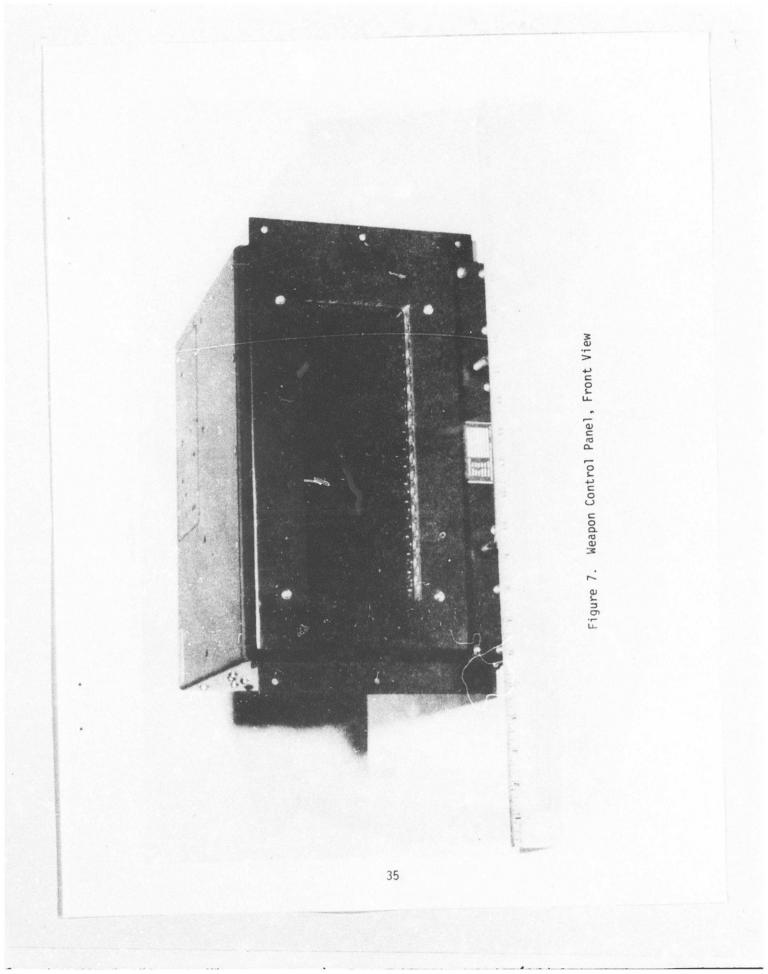

| IV      | PROCESSOR SUPPORT HARDWARE<br>Physical Description<br>Operations and Displays                                                                                 | 34<br>34<br>39                       |

| V       | SOFTWARE<br>Cross Assembler<br>Display Page Preparation Program<br>Magic 362 Operational Routines<br>Magic 362 Debug Program<br>Magic 362 Diagnostic Programs | 45<br>45<br>46<br>46<br>78           |

| VI      | RECOMMENDATIONS<br>Human Factors Considerations<br>Displays<br>Software<br>Hardware                                                                           | 50<br>50<br>51<br>51<br>52           |

## LIST OF ILLUSTRATIONS

| Fi | dure |

|----|------|

|----|------|

### Title

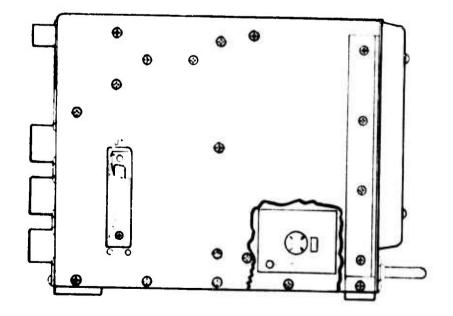

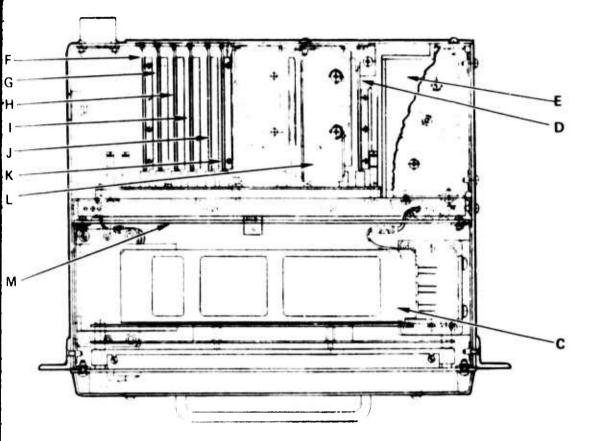

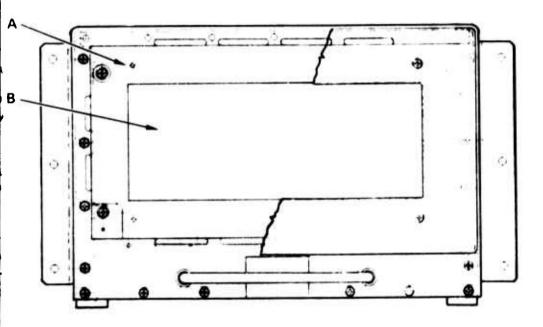

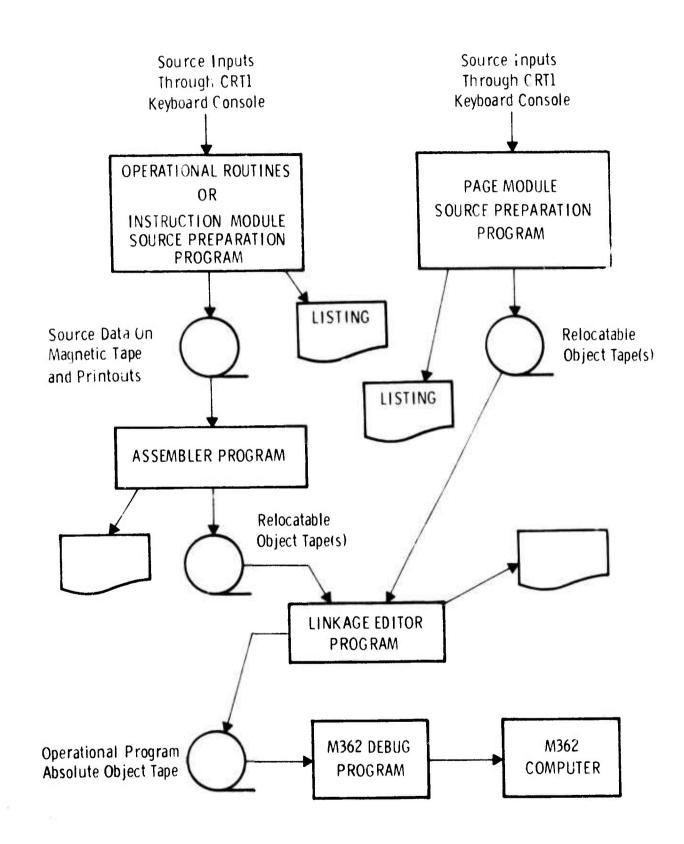

#### Page Weapon Control Panel Block Diagram WCP System Units Block Diagram, Switch Matrix Electronics Switch Matrix Frame 3 4 Modified ASCII Subset for Weapons Control Panel WCP Instruction Repertoire Weapon Control Panel, Front View Weapon Control Panel, Rear View Weapon Control Panel Layout CCU Front Panel 40 Weapons Control Panel Operational Program Generation

#### SECTION I

#### INTRODUCTION

This report documents the significant items relating to the design, development, fabrication, and test of the Pilot's Cockpit Weapons Control Panel (WCP), related support software, and processor support equipment. Although the majority of the hardware and software designs for this program were extracted from previous developments, their features are so integral to the WCP operation that a discussion of these items is also included for an overall understanding of the system concept and equipment capabilities.

#### BACKGROUND

The control facet of control and display technology has been unable to keep pace with developments in displays and electronic subsystems because there has been no satisfactory method to change the function of a switch in a way that can be easily recognized and reliably responded to by a human operator. Consequently, while visual presentations have advanced from indicator lights to numerical readouts to multiline alpha-numeric displays and on to fully formatted displays, the control function is still being handled by dedicated switches or by keyboards requiring specially coded data entry.

Meanwhile the operator control task has been expanding. As additional and more sophisticated electronics, including computers, have been added to modern weapon systems, advancing their capabilities, the operator's role has also grown because of the increased option selection available to him. At the same time, control area crowding, particularly in cockpits, is making the operator's task increasingly more taxing because of switch inaccessibility, limited prime viewing area, and non-uniform layouts between like weapon systems.

To solve the problems of restoring the operator's task to a more manageable level, reducing panel space requirements for the control function and taking full advantage of advanced display technology, an integrated, adaptively reconfigurable control and display system is required. Such a system is applicable to numerous military systems including weapon delivery systems. In recognition of the control problem, the Air Force Armament Laboratory, Eglin AFB, Florida initiated the procurement of a Pilot's Cockpit Weapon Control Panel as part of the Aircraft to Weapon Communication Control Program.

The particular problem as viewed by the Eglin AFB personnel is expressed as follows:

Current aircraft weapons control panels provide only a limited control capability. Therefore, aircraft modifications or additions are required in order to carry sophisticated weapons. The large wire bundles required to connect the control panel to the rest of the system are cumbersome and undesireable. The objective of this effort is to develop a weapons control panel utilizing advanced state-of-the-art techniques which are compatible with existing and planned weapons capabilities. This

new control panel will provide control capability throughout the spectrum of weapons and will be interfaced with the host aircraft through a multiplex system.

#### SCOPE

Under this contract, the following major engineering tasks were performed:

- Design, fabricate, test and deliver a flyable breadboard WCP (prototype).

- Fabricate, test and deliver processor support equipment.

- Design, develop, validate and deliver processor support software.

#### SECTION II

#### TECHNICAL APPROACH

The major objective of this program was to develop an integrated, multifunction control/display panel which employs multiple switches whose nomenclature and function can be legibly and logically modified under control of a small, general purpose avionics computer. The control/display panel is to feature a multi-switch array configured such that the switch functions and nomenclature could be automatically changed in a logical, straightforward manner to reflect only applicable option selections. By implementing such a system, the control aspect of weapon delivery systems will benefit from:

- A significant reduction in the number of switches, displays, and control knobs required, thus reducing prime panel space requirements.

- The need for only one primary control area which could be optimally placed for operator interface, thus increasing systems effectiveness by shortening operator reaction time.

- A simplification of the man-machine interface by presenting only pertinent, logical control options which are viable and relative to the operation in process, thus achieving increased operator proficiency and reduced operator error.

- The ability to add or delete weapon system functions without panel (cockpit) changes, thus greatly reducing modification costs.

Current computer and display technology can be applied to formulate an alphanumeric presentation which portrays an operating system mode and status and which delineates in full word form the selectable options within the mode, as well as exits from the mode. Once a selection has been made and transferred to the computer, software decisions can be made to update the display status and present the next logical set of operator options and/or transfer the selection to the appropriate weapon conditioning and control system. For example, the weapon options could be displayed based upon actual available stores (loaded less expended), with subsequent displays providing options for release/delivery method, fuzing, release quantity, release rate, etc.

A more difficult problem is the integration of the control (switch) functions such that the operator selects the appropriate option in a positive, simple, and reliable manner. From human factors considerations, the ideal solution is for the operator to physically touch the word on the display representing the desired option. This allows his action to be directed to his immediate area of concentration and no translation of the word option to an externally located switch is required. Co-location of the switch with the display also provides the equally important benefit of minimizing panel space requirements.

To integrate the switch function, the contractor chose to apply a transparent switch matrix design which had been developed to meet this type of requirements. The transparent switch matrix utilizes the electric eye concept of detecting an object by blocking a light beam. A light beam matrix is formed by locating a number of light sources at the top and right side of the display and corresponding receivers along the bottom and left side of the display. When an object is placed in the path of the beams, one or more up-down and right-left beams are blocked, thus locating the object. The matrix is essentially two-dimensional and can easily be integrated with any type of display.

This means of implementing the switch function offers significant advantages over other methods such as a conductive glass sytem or a cross-wire touch system. These other techniques require physical overlays across the display, are more susceptible to humidity and/or vibration environments, and are inherently less reliable.

The following hardware and software elements were selected to take full advantage of fully developed, available assets:

- A standard Burroughs Corporation Plasma panel, 256-character (8x32) display was selected because of availability and previous airborne applications experience with that type of display.

- The Delco Magic 362 airborne computer was selected as the processor element to simplify interface and software designs.

- The Magic 362 assembler program designed to operate on an Alpha 16 minicomputer centered on-site programming system was selected because of the linkage to a CRT terminal which could be used for display formulation.

- The Magic 362 Computer Control Console was selected as the processor support equipment since it provides the functions required and is a fully developed item.

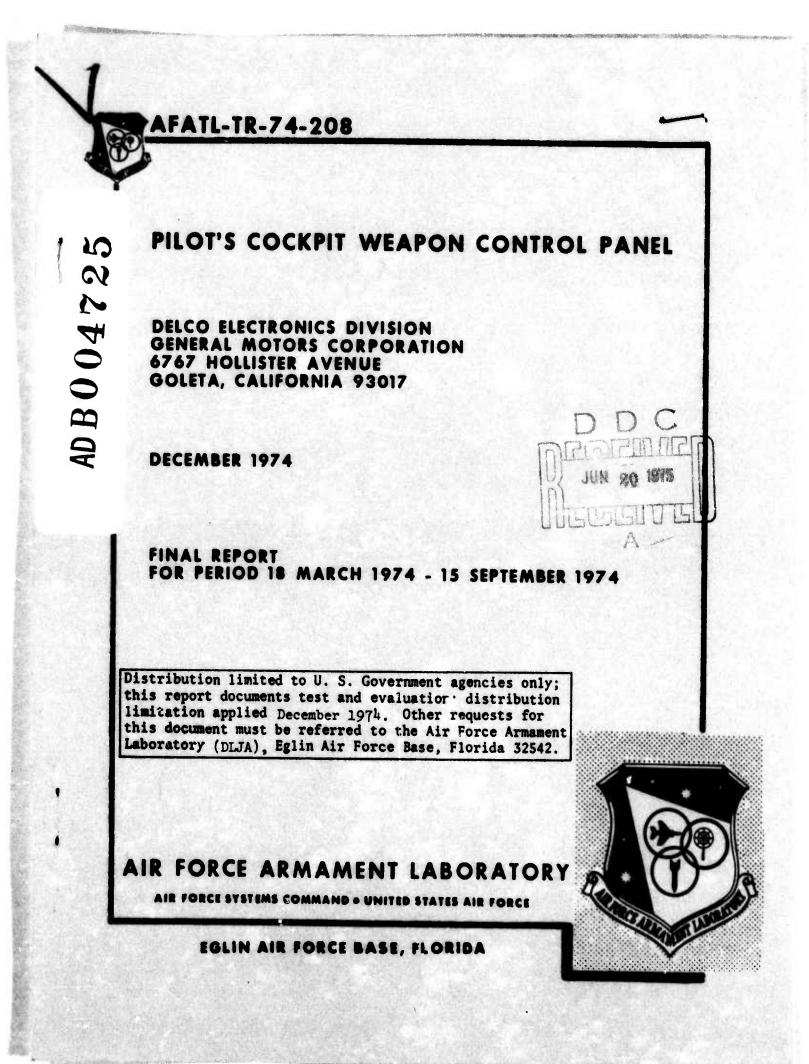

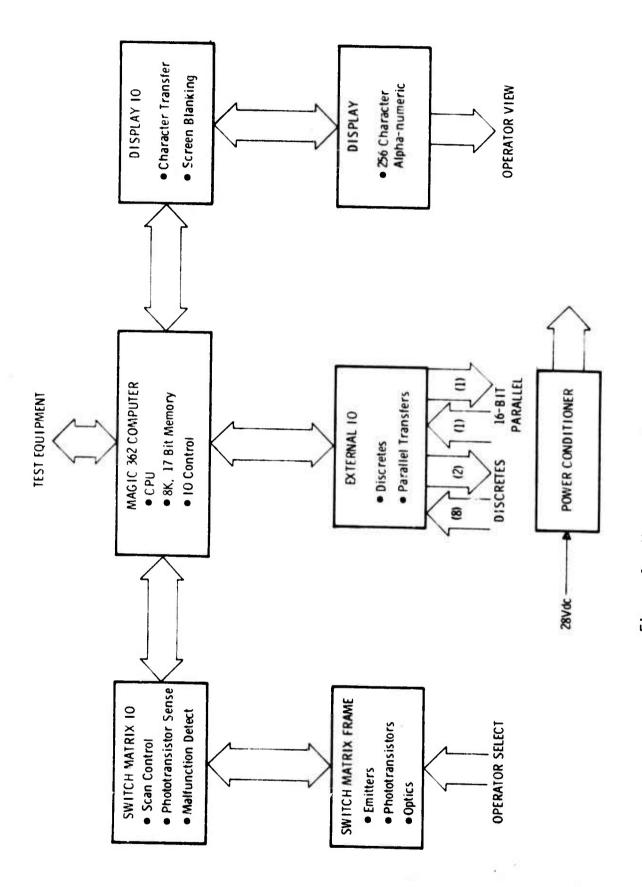

A system block diagram is shown in Figure 1. Figure 2 is a photograph of the units of the system.

#### SECTION III

#### HARDWARE IMPLEMENTATION

#### Switch Matrix

To implement a transparent switch matrix around the light beam interruption principle required tradeoff and analysis to:

- Define the pertinent characteristics required from the light emitters and detectors and characterization of available devices for appropriate selection.

- Design and evaluation of an optical system which can provide the beam focusing necessary to achieve a workable signal-to noise ratio at the receiver, while restricting crosstalk between beams.

- Development of a control/reading technique which, in detecting an object in the switch matrix plane, will be adaptive to object size, discriminate between a valid or non-valid selection, provide switch matrix self-test, and allow the matrix to fail operationally (disable a failed light path with software).

While these tasks were not performed under the auspices of this contract, their results are so significant to the basic theory and operation of the WCP that a summary is included in this report.

The first step in the development of the switch matrix was to survey available emitter and phototransistor devices to select the most likely candidates for this application without entering into a device development. Because infrared emitter spectral response is generally centered in the 900 to 940 - nanometer region and phototransistors typically peak near 900 nanometers, the emitter survey was concentrated in the IR field. The characteristics of 14 IR emitters and 17 phototransistors were compared which resulted in the tentative selection of and test of the Texas Instruments TIL31, Optron OP133, GE SSL35 and Monsanto ME7124 emitters and the Texas Instruments TIL S1 and Optron OP803 and OP805 phototransis-These device types were tested on a special fixture to obtain tors. comparative performance data with the principal characteristic of interest being the phototransistor output voltage which is the significant system application parameter. The major conclusion derived from this testing was that any of the devices evaluated could be used in the system but that some level of screening and matching would be required. The screening is necessary to ensure reasonable operating margins for the phototransistor threshold between light and no light because of the dispersion in emitter radiation (4:1 measured) and phototransistor response (3:1 measured).

The next major step in the switch matrix design was to design the optical system considering the characteristics of the devices available, background radiation, variations due to temperature, path lengths between emitters and receivers (9.6 inches in the long axis and 3.7 inches in the short axis), paths (0.28 inch). Using the general criteria of adjacent light signal-to-noise ratio and discrimination level at the phototransistor output device, circuit, or optics requirements, a theoretical analysis of the optical stantiated by test, that:

- Long axis performance would be marginal without the use of a collimating lens at the emitter end and significant improvement could be obtained in phototransistor output with simple glass plano convex lenses at both ends.

- The use of black walled light tunnels and IR filters at the phototransistor end would provide rejection of ambient light levels above those that would wash out the display itself and thus the use of baffled light tunnels or glare-shields are not required.

- The optoelectric pairs (light beam direction) should be alternated between adjacent positions to reduce crosstalk.

- The alternating of devices and the use of lenses preclude the need to mechanically align the emitter optical axis at assembly.

A complete 8 x 32 switch matrix breadboard was assembled for final validation of the concept and to evaluate detector circuits and control logic options as well as to confirm the calculated operating margins versus influencing paraemitter/phototransistor characteristics. This breadboard substantiated the validity of the design concept and confirmed that the operating margins were well in excess of circuit variations.

A detailed tradeoff study was conducted to establish the optimum control and readout modes for the panel. This study was particularly important since the basic organization of the switch matrix imposes two significant constraints. First, a true geometric assessment of an object in the switch field cannot be made. At most, the information available is which X and Y axis light beams have been interrupted which transforms into a rectangle of emitter light; thus, a failed emitter or phototransistor appears the same as an object in that path. The pertinent results of this study were:

- The most efficient switch matrix control from both electronics simplicity and power conservation considerations is provided by sequentially pulsing each emitter and reading the phototransistor output during the pulse. This provides the capability of O-Ring the X-axis and Y-axis phototransistors. thus allowing the use of 2 (one per axis) rather than 40 amplifier/detectors and reduces emitter power by a 40:1 factor.

- Little benefit is derived from knowing all of the X and Y light beams that have been interrupted since X-axis interruptions cannot be correlated with Y-axis interruptions, and the computer software is significantly complicated if 40 discretes (switches) must be tested and interpreted.

- Assuming a left-to-right X-axis scan and a top-to-bottom Y-axis scan, where the first interruption in each axis is provided to the computer as an X- and Y-axis position, the data can be used as an X, Y coordinate address which is equivalent to the upper left coordinate of the apparent object rectangle. This can be easily used by the software as an address pointer to determine the switch location.

- By incorporating a double scan, i.e., l-r, t-b, b-t, r-l, the upper left and lower right coordinates of the apparent object rectangle can be provided to the software, thus allowing a reasonableness check to be made on object size, provide means for increased resolution in determining the switch area being activated, and eliminate any sensitivity to a right or lefthanded operator.

- In the event of a light path failure, a double scan will produce two values for one axis and no values for the otner axis which can be detected as a malfunction.

- Individual software enable/disable control should be provided for each light path to allow exclusion of a failed path from the scan (fail operational) and also to allow reconfiguration of the switch point densities. This latter feature provides increased flexibility for human factors evaluation of the system concept since it allows the exclusion of certain panel areas as active switch areas and also allows reformatting from an 8x32 matrix to such configurations as 8x16, 4x15, 8x8, or 4x8.

- Logic should be provided to reject switch inputs which provide less than two complete sets of coordinates as would occur if the object entered the switch area at any time other than the start of a scan (a normal condition).

### 1. System Level Operation

The resultant switch matrix design implemented in the WCP reflected the conclusions and results from the analysis and breadboard testing. The

following provides a description of the switch matrix operation and its operational interface with the processor.

The WCP I/O provides for the recognition and encoding of any of the 256 possible switch matrix switch points where a switch point is spacially located at each of the display character locations. The switch matrix is implemented with 40 IR emitter/receiver pairs configured in 32 columns and 8 rows, thus establishing the 256 unique column/row (X/Y) intersection points. From a functional viewpoint, the operation of the switch matrix is as follows: Each emitter is individually turned on in a fixed sequence and the corresponding receiver is tested for receipt of the light energy. The emitter pulsing sequence starts with column 1 (XO1) which is the leftmost column and proceeds through each column in order, ending with column 32 (X32) which is the rightmost column. The pulsing then transfers to the Y or row axis and sequentially goes through the 8 rows starting with row 1 (YO1) which is the top row and ending with row 8 (YO8) which is the bottom row. This X-Y scan is one-half of a switch point read scan. The second half of the read scan pulses the emitters in reverse order, i.e., YO8 through YO1 and X32 through X01. A complete read scan takes 8.2 msec to execute and is repeated continuously until a switch closure is detected.

A switch closure is sensed by the condition of a pulsed emitter and no receipt of light energy by the corresponding receiver. When a switch closure is detected, the row or column number associated with the closure is stored and the emitter pulsing for the remainder of the row or column involved is terminated. If the I/O accumulates an X closure and a Y closure during each half scan of a read scan (4 data points), the scanning routine will be terminated.

If any less than 4 data points are accumulated during a read scan, the data points will be ignored and a new read scan will be initiated (see the discussion on malfunction detection for a special case).

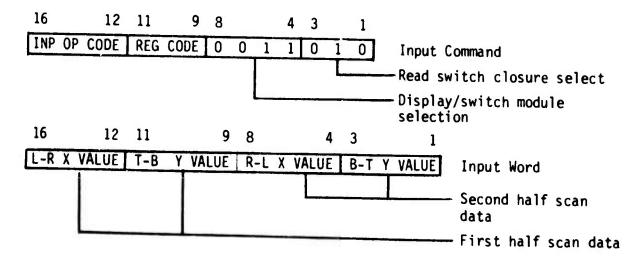

Upon accumulating four data points, the I/O will generate the switch matrix interrupt request. Within the interrupt routine the program should issue the input command to read the switch point data.

The X and Y values are the binary representation of the detected X and Y switch closures stored during the read scan. The designations (values) are associated with specific emitter/receiver pairs regardless of direction of scan with X01 (leftmost pair) having a value of 00001, X02 having a value of 00010, etc. through X32 (rightmost pair) having a value of 00000; and Y01 (top pair) having a value of 001. Y02 having a value of 010, etc. through Y08 (bottom pair) having a value of 0000. This command will not cause an instruction counter skip. Read scans will be resumed after the program has issued the RFI instruction associated with the switch matrix interrupt request.

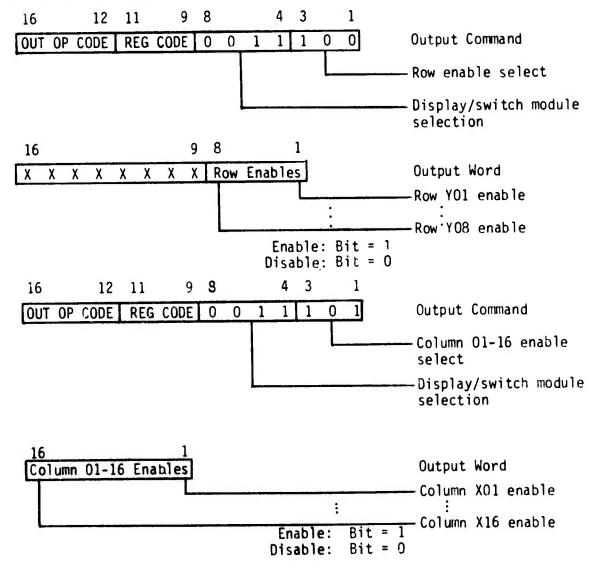

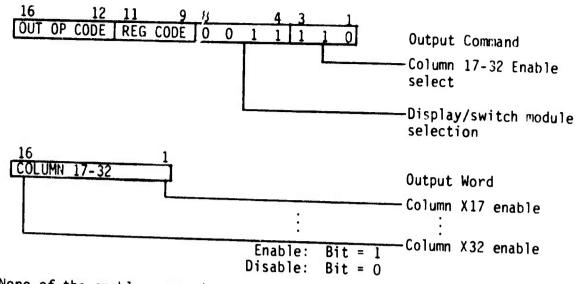

The switch matrix I/O active switch configuration is controlled by the program by three output commands. These commands provide individual enable/disable control over each of the 40 emitter/receiver pairs which is mechanized such that if any pair is disabled, the receiver output is read as no closure regardless of the actual condition. The program must set the enable/disable state for all 40 emitter/receiver pairs at power turn-on and after recovery from any power transient which caused the WCP to re-initialize and begin instruction execution at location 2000<sub>8</sub> (normal starting address).

None of the enable commands will cause an instruction counter skip.

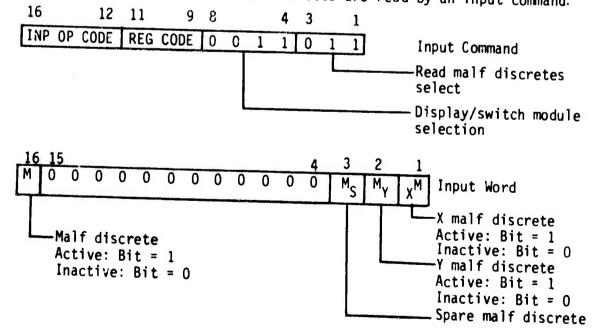

As part of the WCP built-in test hardware (BITE), the switch logic tests for a read scan which produces two X closures and no Y closures or two Y closures and no X closures. Either of these conditions infers an emitter/receiver pair failure since an inoperative path produces the same indication as a closed switch. If this condition is detected, scanning will be terminated, a switch matrix interrupt request will be generated, and two malfunction discretes will be set. Since either a normal closure or a switch path failure will produce the same interrupt request, the program should read the malfunction discretes to determine the source of the interrupt. These discretes are read by an input command.

This command will not cause an instruction counter skip.

The malf discretes are initialized in the inactive state and reset by the RFI instruction associated with the switch matrix interrupt request. To determine which switch path has failed, the program must execute a switch read input command (INP32). The corresponding data word will contain the value of the malfunctioning path in both half-scan data segments and zeroes for the value of the other axis.

2. Functional Operation

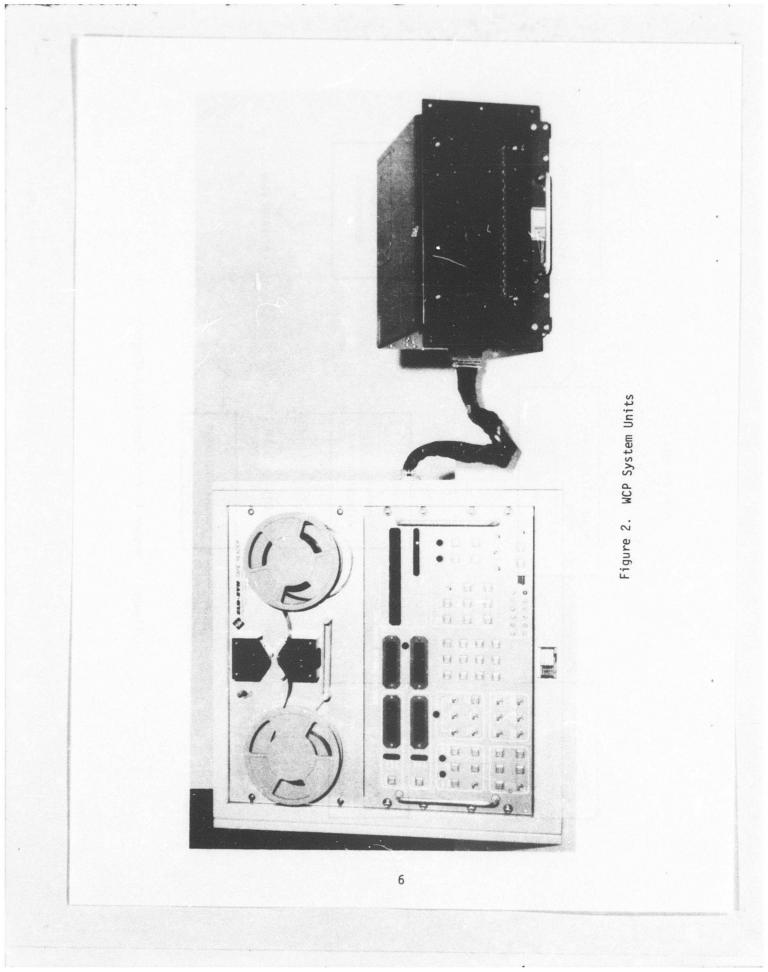

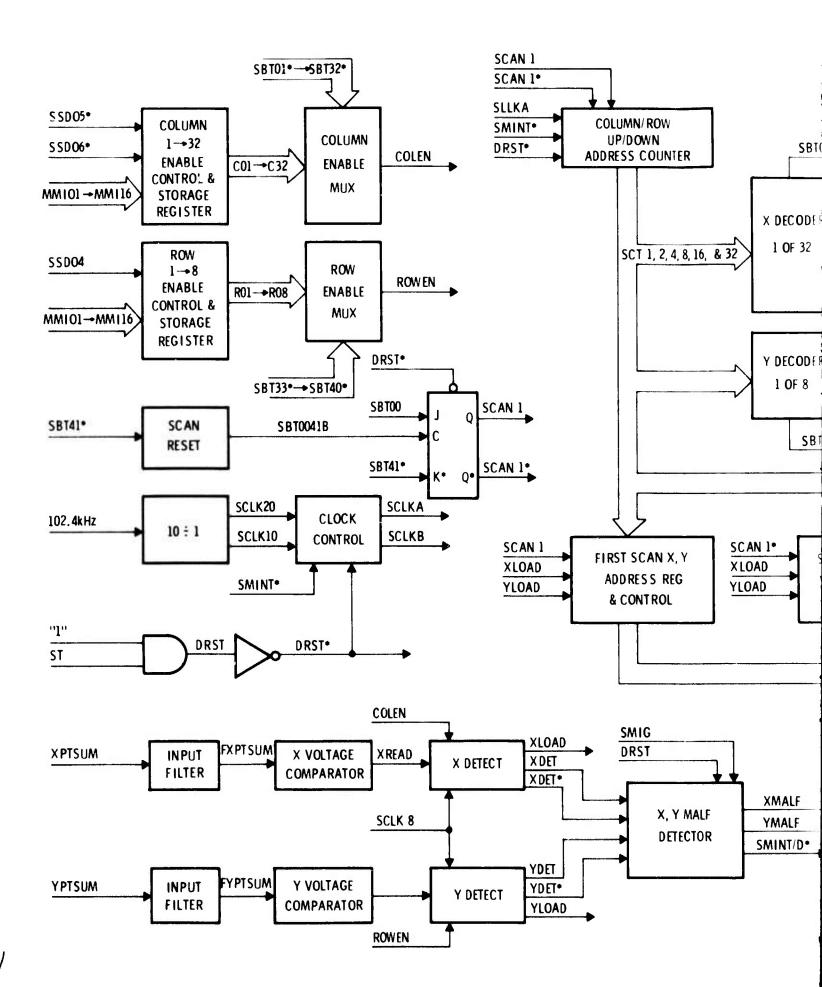

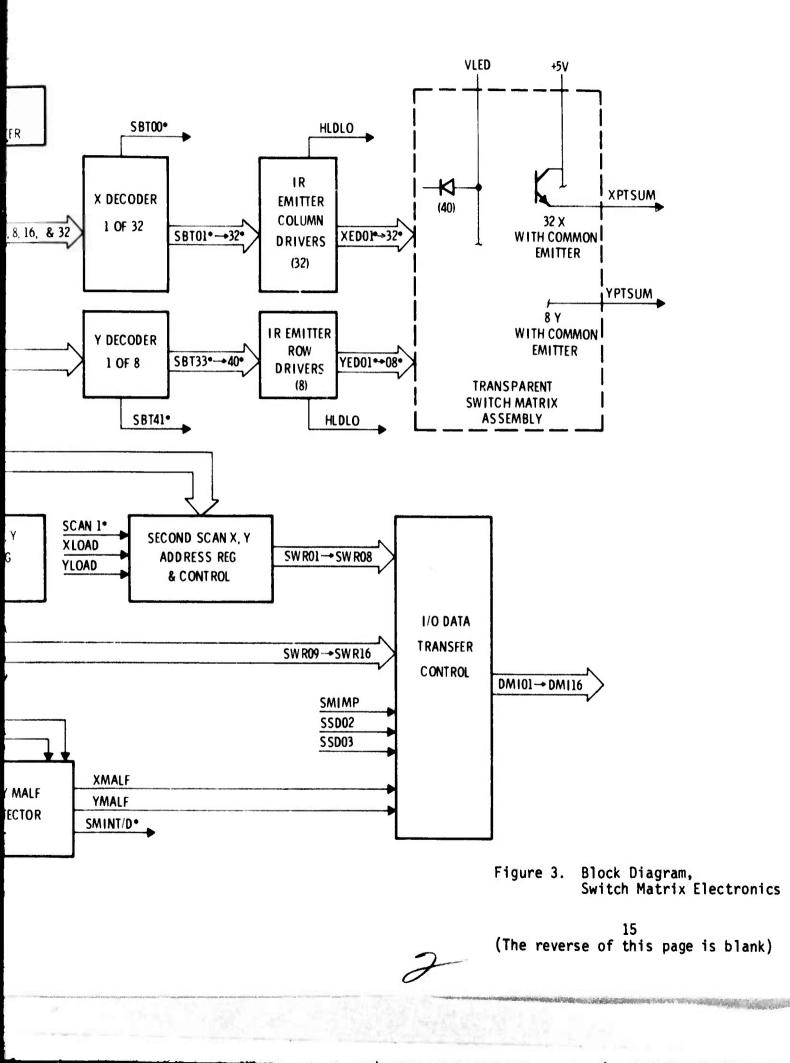

The following describes the switch matrix operations including major controls and sequencing. Figure 3 presents the switch matrix electronics in block diagram form.

The computer program issues three output commands to allow enabling/ disabling of the individual columns (32) and rows (8) emitter/receiver pair signals. If any pair is disabled by the program, the switch output is read as a no closure regardless of the actual switch condition. The program must set all rows and columns enable state to ON at power turn-on.

The program output discretes are:

OUT 34 Instruction - Enabling Rows 1 through 8 OUT 35 Instruction - Enables Columns 1 through 16 OUT 36 Instruction - Enables Columns 17 through 32

Data is transferred between the computer I/O and the Transparent Switch Electronics (TSE) by means of 16 parallel lines as follows:

MMI01 through MMI16 - Parallel data word from computer I/O to TSE DMI01 through DMI16 - Parallel data word from TSE to computer I/O

The OUT 34 instruction word is decoded by the hardware into the SSD04 discrete which, in turn, allows transfer of data on MMI01 through MMI08 into the Row Enable Storage Register.

The OUT 35 instruction is decoded into the SSD05 discrete which allows the data on MMI01 through MMI16 to be transferred to the Column 1-16 Enable Storage Register.

The OUT 36 instruction is decoded into the SSDO6 discrete which allows the data on MMI01 through MMI16 to be transferred to Column 17-32 Enable Storage Register.

DRST\* is a discrete initialize pulse (10  $\mu$ sec). DRST\* sets SCAN1 FF to "1" and the Column/Row Up/Down Address Counter to "0".

The counter enable signal, SMINTS="0" and the address counter is ready to count up with receipt of 10 KHz clock, SCLKA, (Count starts after DRST\*="1").

The Column/Row, Up/Down Address Counter counts up generating scan bit times SBT00\* through SBT41\* in sequence in the Scan X and Y Decoders.

Scanning proceeds in the spatial matrix arrangement from left to right and top to bottom in columns 1 through 32 and rows 1 through 8, respectively. A scan bit time is  $100 \ \mu$ sec wide. The output of the decoders are applied to the 32-column and 8-row IR Emitter Drivers. These in turn, one at a time, pulse their respective column and row IR emitters.

At time SBT41\*, Scan 1 FF is toggled to "O". (FF change occurs at clock pulse SBT0041B.)

This results in the C/R, U/D Address Counter down count control line being raised to a "1" and the counter now counts down. The Decoder output bit times count down from SBT40\* through SBT00\*. At bit time SBT00\*, the Scan 1 FF output is toggled again to start the address counter to counter up. This cyclic process is continuously repeated until a switch is depressed or a switch malfunction is detected. When the address counter is counting down, the scanning proceeds from Row 8 through 1 and Column 32 through 1 (i.e., B to T, R to L).

The 32 outputs of the column (X) phototransistors (XPDSUM) are wired or together and applied to the X Voltage Comparator. The output of the voltage comparator is a digital signal, XREAD.

Similarly, the 8-row phototransistors wired or output, (YPTSUM), is applied to the Y Voltage Comparator which, in turn, generates the YREAD digital signal.

The XREAD signal, with column enable, COLEN, generates a clocked XLOAD and XDET signals.

The column enable register data is multiplexed with bit times SBT01\* through SBT32\* to generate column enable signal, COLEN.

The YREAD signal with ROWEN generate a clocked YLOAD and YDET signals. The Row Enable Register data is multiplexed with bit times SBT33\* through SBT40\* to generate Row Enable signal, ROWEN.

Two consecutive XDET and YDET signals are required to generate a legal switch activation. When this condition is met, a Switch Matrix Interrupt discrete is issued (SMINT/D\*).

An XDET\* and YDET are ANDed together to generate a YONLY pulse. This, in turn, is used to generate a YMALF12 signal. YMALF12 signifies that only a Y IR beam was detected as interrupted which is not possible during normal switch activation.

Similarly XDET and YDET\* signals are used to generate an XMALF12. An XMALF12 means that only an X IR beam was interrupted. XMALF12 and/or YMALF12, when present, usually signify a failure in the emitter driver circuit. The failed position address information is transmitted to the computer I/O as a Switch Malfunction Word after a Switch Matrix Interrupt

signal is generated. The program can then disable the failed position by issuing a revised output discrete word in the proper instruction, i.e., either OUT34, OUT35 or OUT36.

Signals YMALF12\* and XMALF12\* with signal SMDET4\* generate discrete SMINT/D\*.

The XLOAD and YLOAD signals are logically combined with Scan 1 and used to clock in the present Column/Row, Up/Down counter address data into the X, Y 1st Scan Address Register. The outputs of this register are parallel signals SWR 09 through SWR 16.

The XLOAD and YLOAD signals with SCAN 1\* load the present address information of the Column/Row, Up/Down counter into the X Y 2nd Scan Address Register. The outputs of this register are parallel signals SWR 01 through SWR 08.

These outputs, SWR 01 through SWR 16, are transferred by means of the I/O Data Transfer Control logic to the computer I/O Bus on lines DMI01 through DMI16 when the following occurs:

- A Switch Matrix Interrupt SMINT is sent from the TSE electronics to the program. The computer receives the SMINT by means of the TRS instruction with an Operand Address 12048. An interrupt is generated for either or both:

- a. A malfunction has been detected.

- b. A double scan has been completed with a switch cross point depressed.

- Once in the SM interrupt routine scanning has been stopped and the SM MALF word should be input, followed by the switch word. This is done by means of the following instruction:

INP 033 Enable Input SM Malf INP 032 Enable Input SM Word

The program must signify completion of the Switch Matrix Interrupt routine by issuing an RFI instruction. When the switch interrupt routine is completed, scanning of the matrix starts over and continues until a switch is depressed or until a malfunction is detected.

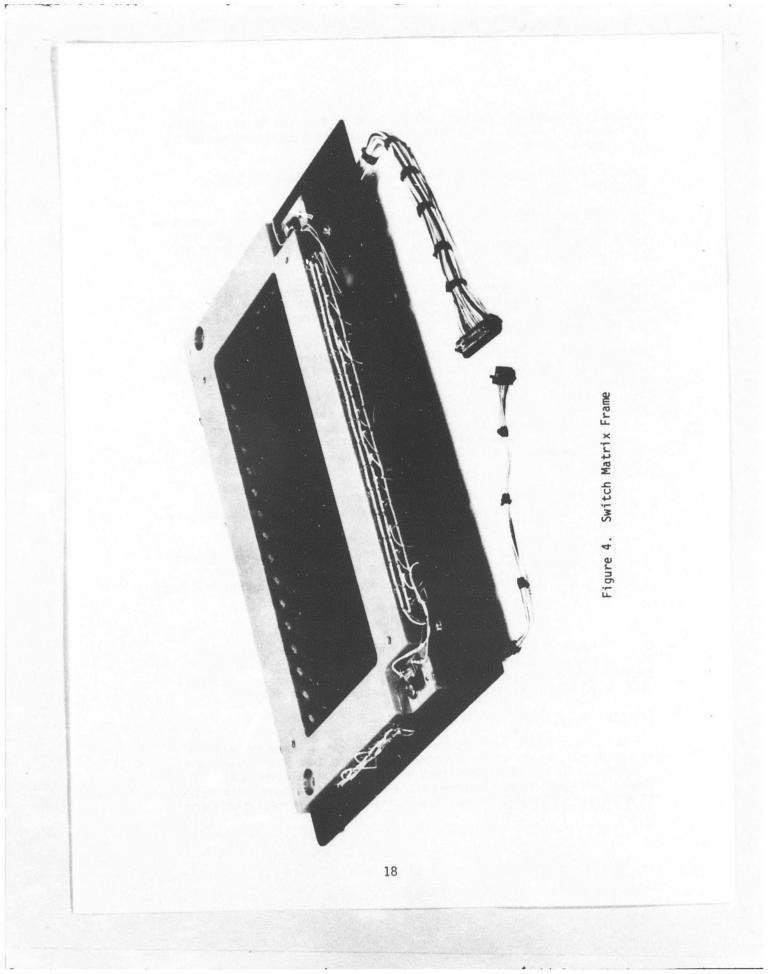

#### 3. Physical Description

The switch matrix optical system is contained in a frame as shown in Figure 4. As shown in the photograph, the long axis light paths are staggered. In addition, the light beam direction is alternated between adjacent paths to increase the separation of beams with respect to any given phototransistor. The emitters and phototransistors are

located on the outer perimeter of the frame, and the lenses are located on the inner surface with the holes through the frame serving as light tunnels.

The frame is permanently attached to the WCP front panel, forming an inseparable assembly. The wiring is connectorized to simplify assembly and enhance maintainability. At the WCP level, the frame, including a contrast enhancement filter, overlays the display, locating a switch point over each of the 256 character locations on the display. As can be seen, this technique is not constrained to a particular display, and the form factor can be adjusted for different beam-to-beam spacing as well as overall frame dimensions. Thus, the frame configuration can be made compatible with any display technology.

Alpha-Numeric Display

The display employed in the WCP is a standard Burroughs Self-Scan<sup>®</sup> Model BDS40832-200 panel display subsystem which includes a 256-character display, a character generator, a random access memory for self-contained display refresh, drive buffers and demultiplex circuitry, timing and mode control, and anode and cathode drive electronics.

The general characteristics of this subsystem are:

- Character capacity 256

- Character format 5x7 dot matrix

- Text format 32 characters per row, 8 rows

- Dot spacing 0.04 inch

- Character size 0.2 inch wide by 0.28 inch high

- Character separation 0.08 inch between characters

0.12 inch between rows

- Brightness 25 fL nominal

- Contrast ratio 20:1

- Light spectrum neon orange

- Panel scan rate 85 Hz

- Memory access time 1.75 µsec.

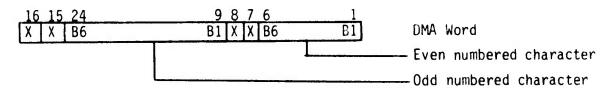

The panel is interfaced to the processor by means of special input/output circuitry. Character data to be displayed is located in 128 words in the program memory with each word containing two six-bit character bytes. The sixbit character codes are a derivation of the ASCII code as shown in Figure 5.

Included in the display I/O is the character generation logic to convert from the modified ASCII codes and the memory and scan logic to maintain the character display. Thus, for any display, the I/O need only be provided one set of 256 6-bit codes.

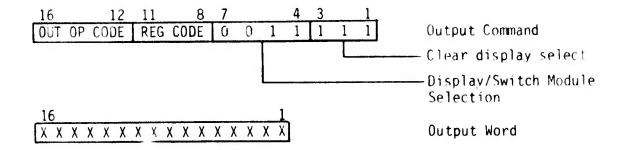

Two OUT commands are associated with the display I/O, one to clear the display and one to load 256 characters. The clear command is as follows:

| B <sub>6</sub> B <sub>5</sub> B <sub>7</sub> |                                                                                        |                                                                    |                                                                         |                                                               | 1 0                                                   | 1 1                                                           | 0                                                             | 0 1                                                           |

|----------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| BLTS                                         | B <sub>4</sub>                                                                         | <sup>В</sup> 3                                                     | B <sub>2</sub>                                                          | <sup>B</sup> 1                                                |                                                       |                                                               |                                                               | 1                                                             |

|                                              | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 2<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | SP<br>!<br>#<br>\$<br>%<br>&<br>'<br>(<br>)<br>*<br>+ | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>:<br>;<br>< | @<br>A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J<br>K<br>L | P<br>Q<br>R<br>S<br>T<br>U<br>V<br>W<br>X<br>Y<br>Z<br>[<br>~ |

|                                              | 1<br>1                                                                                 | 1                                                                  | 1<br>1                                                                  | 1<br>0<br>1                                                   | -<br>/                                                | =<br>><br>?                                                   | M<br>N<br>O                                                   | ]<br>{<br>}                                                   |

Figure 5. Modified ASCII Subset for Weapons Control Panel

The execution of this command will not cause an instruction counter skip.

The command to load the display will cause the I/O to extract the character code data from core memory by means of DMA and update the contents of the display memory. The DMA access will begin at location  $4000_8$  and end at location  $4177_8$ , with each memory access providing two 6-bit characters. The character locations within each word will be as follows:

Character data must be stored in memory locations  $4000_8$  through  $4177_8$  in a sequential fashion, i.e., characters 1 and 2 in location  $4000_8$ , characters 3 and 4 in location  $4001_8$ , characters 5 and 6 in

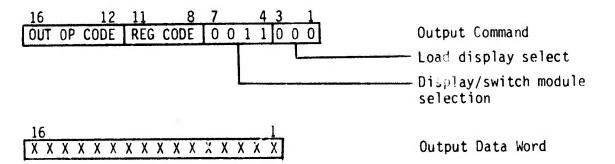

<sup>8</sup>location 4002, etc. Character numbering on the display is sequential left to<sup>8</sup>right and top to bottom starting with 1 and ending with 256, making the first character number in each row 1, 33, 65, 97, 129, 193, and 225. The output command structure for loading the display is as shown.

Once this command is issued, the I/O will proceed through the full 256 characters with the execution time being a function of the display update rate (approximately 11-3/4 msec for the total display).

If additional load display commands are issued while an update is in process, the command will be held until the in-process display formatting has been completed through all 256 characters. Execution of this command will not cause an instruction counter skip.

#### Processor

The WCP processor is a Delco Magic 362 general purpose, microprogrammed avionics computer consisting of a central processor, an 8K x 17 bit core memory and an input/output controller. The major features of the processor include:

- Binary, fixed point, two's complement arithmetic with single and double precision operations.

- 2.9 µsec Add/Subtract/Load execution time

- 16 program accessible registers

- 1.4 µsec memory cycle time

- Memory parity

The processor instruction repertoire and execution times are given in Figure 6.

External I/O

In addition to the switch matrix and display I/O, the WCP provides interfaces to external systems. Included are eight 28 VDC input discretes, two 28 VDC output discretes, a 16-bit parallel channel to another computer, and a 16-bit parallel channel from the other computer. The specific requirements for the external I/O were modified during the contract with the final configuration described below.

1. External Input Discretes

The WCP I/O wll accept up to eight 28 Vdc discretes. The discretes are input through optically coupled isolaters which are referenced individually to a discrete return signal. The input discrete channel is mechanized to generate an interrupt request when any of the eight inputs changes state from either a high to a low or from a low to a high.

A. Signal Interface Characteristics

|    | Type:                           | Double-ended                                                                        |

|----|---------------------------------|-------------------------------------------------------------------------------------|

| 2. | Voltage:                        | Logic "1"=16+6 Vdc                                                                  |

|    | Load Resistance:<br>Transients: | Logic "O"= open circuit or O+.9 Vdc<br>3.9 Kohms + 5%<br>Up to 80V per MIL-STD-704A |

| MNETIONIC | DESCRIPTION                                                                                   | COMPUTER<br>CLOCKS | EXECUTION<br>TIME (used) |

|-----------|-----------------------------------------------------------------------------------------------|--------------------|--------------------------|

|           | ARITHMETIC                                                                                    |                    |                          |

| ADD       | Add memory to A register, result in A                                                         | 12                 | 2.930                    |

| ADM       | Add A register to memory, result in memory                                                    | 18                 | 4.395                    |

| ARR       | Add register to register                                                                      | 7                  | 1.709                    |

| ADP       | Add double word in memory to A and B registers                                                | 18                 | 4.395                    |

| DIV       | Divide A and B registers by memory,<br>quotient in A                                          | 48                 | 11.719                   |

| IRI       | Increment register by operand address                                                         | 6                  | 1.465                    |

| MDP       | Multiply A and B registers by double<br>word in memory, result in A, B, X,<br>and Y registers | 141                | 34.424                   |

| MPY       | Multiply A register by memory, result in A and B                                              | 30                 | 7.324                    |

| MSK       | Mask A register with memory, result in A                                                      | 12                 | 2.930                    |

| SDP       | Subtract double word in memory from A and B                                                   | 18                 | 4.395                    |

| SRR       | Subtract register from register                                                               | 7                  | 1.709                    |

| SUB       | Subtract memory from A register, result in A                                                  | 12                 | 2.930                    |

| TCC       | Test sign of first register and carry to second register                                      | 10                 | 2.441                    |

Figure 6. WCP Instruction Repertoire

| MNEMONICDESCRIPTIONCOMPUTER<br>CLOCKSEXECUTION<br>TIME (usec)RTERotate combined A and B registers112.686 +<br>0.244NSFAShift A register92.197 +<br>0.244NSFBShift B register92.197 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>0.244NSFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLOALoad A register from memory122.930LDDLoad A register from memory122.930LRILoad register from memory122.930LRMLoad register from register71.709SRMStore register in memory122.930STDStore A and B registers in memory122.930STDStore A and B registers in memory122.930ZZero register71.709 |   |          |                                                   |      |                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|---------------------------------------------------|------|--------------------------|

| SHIFTSHIFTRTERotate combined A and B registers112.686 +<br>0.244NSFAShift A register92.197 +<br>0.244NSFBShift B register92.197 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>0.244NSFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLDALoad A register from memory122.930LDDLoad A register from memory122.930LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STDStore A and B registers in memory122.930STDStore A and B registers in memory184.395STDStore A and B registers in memory194.639                        |   | MNEMONIC | DESCRIPTION                                       |      | EXECUTION<br>TIME (µsec) |

| SFAShift A register112.686 +<br>0.244NSFAShift A register92.197 +<br>0.244NSFBShift B register92.197 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |          | SHIFT                                             |      |                          |

| SFBShift B register92.197 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>0.244NSFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLDALoad A register from memory122.930LDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register from memory122.930LRRLoad register from memory122.930LRRLoad register from memory122.930STAStore register in memory122.930STDStore A and B registers in memory122.930STDStore A and B registers in memory194.639ZZero register194.639                                   |   |          | Rotate combined A and B registers                 | 11   |                          |

| SFDShift double word in A and B registers92.197 +<br>0.244NSFDShift double word in A and B registers122.930 +<br>0.244NSFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLOALOAD/STORE122.930LDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STDStore A and B registers in memory122.930STDStore A and B registers in memory122.930STDStore A and B registers in memory194.639ZZero register194.639                                                                                 |   | SFA      | Shift A register                                  | 9    |                          |

| SFDShift double word in A and B registers122.930 +<br>0.244NSFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLOAD/STORE102.441 +<br>0.244NLDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register from memory122.930LRRLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory122.930STDStore A and B registers in memory194.639ZZero register194.639                                                                                       |   | SFB      | Shift B register                                  | 9    |                          |

| SFXShift X register102.441 +<br>0.244NSFYShift Y register102.441 +<br>0.244NLOAD/STOREI2.930LDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from memory122.930SRMStore register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory122.930ZZero register194.639                                                                                                                                                                                                    |   | SFD      | Shift double word in A and B registers            | 12   | 2.930 +                  |

| SFYShift Y register102.441 +<br>0.244NLOAD/STORELOAD/STORE2.930LDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register71.639                                                                                                                                                                                             |   | SFX      | Shift X register                                  | 10   | 2.441 +                  |

| LOAD/STORELOAD/STORELDALoad A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register71.9                                                                                                                                                                                                                                          |   | SFY      | Shift Y register                                  | 10   | 2.441 +                  |

| Load A register from memory122.930LDDLoad A and B registers from double word<br>in memory184.395LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register71.9                                                                                                                                                                                                                                                                 |   |          | LOAD/STORE                                        |      | 0.2441                   |

| LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register194.639                                                                                                                                                                                                                                                                                                                                                              |   |          | Load A register from memory                       | 12   | 2.930                    |

| LRILoad register with operand address61.465LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register194.639                                                                                                                                                                                                                                                                                                                                                              |   | LDD      | Load A and B registers from double word in memory | . 18 | 4,395                    |

| LRMLoad register from memory122.930LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory194.639ZZero register194.639                                                                                                                                                                                                                                                                                                                                                                                                         |   | LRI      | Load register with operand address                | 6    |                          |

| LRRLoad register from register71.709SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory<br>(Relative)194.639ZZero register194.639                                                                                                                                                                                                                                                                                                                                                                                                                              |   | LRM      | Load register from memory                         | 12   |                          |

| SRMStore register in memory122.930STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory<br>(Relative)194.639ZZero register1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 | LRR      | Load register from register                       | 7    |                          |

| STAStore A register in memory122.930STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory<br>(Relative)194.639ZZero register1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | SRM      | Store register in memory                          | 12   |                          |

| STDStore A and B registers in memory (Direct)184.395STDStore A and B registers in memory<br>(Relative)194.639ZZero register194.639                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | STA      | Store A register in memory                        |      |                          |

| STDStore A and B registers in memory<br>(Relative)194.639ZZero register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S | STD      | Store A and B registers in memory (Direct)        |      |                          |

| Z Zero register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 | STD      | Store A and B registers in memory                 |      |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Z |          | Zero register                                     |      |                          |

# Figure 6. WCP Instruction Repertoire (continued)

| MNEMONIC | DESCRIPTION                          | COMPUTER<br>CLOCKS | EXECUTI N<br>TIME (µs@c) |

|----------|--------------------------------------|--------------------|--------------------------|

|          | BIT ACCESS                           |                    |                          |

| RB       | Reset selected bit in memory         | 18                 | 4.395                    |

| SB       | Select bit in memory                 | 18                 | 4.395                    |

| SNS      | Skip if selected bit not set         | 12                 | 2.930                    |

| 1        | CONTROL                              |                    |                          |

| JMP      | Jump unconditionally                 | 7                  | 1.709                    |

| JOM      | Jump if register minus               | 7                  | 1.709                    |

| JOP      | Jump if register positive            | 7                  | 1.709                    |

| JOZ      | Jump if register zero                | 7                  | 1.709                    |

| RFI      | Return from interrupt                | 13 + IOW           | 3.174+10W                |

| RFS      | Return from subroutine               | 14                 | 3.418                    |

| SRG      | Skip if register greater than memory | 12                 | 2.930                    |

| TRA      | Transfer unconditionally (indirect)  | 12                 | 2.930                    |

| TRS      | Transfer to subroutine (indirect)    | 13                 | 4.395                    |

|          | INPUT/OUTPUT                         |                    |                          |

| INP      | Input to register                    | 6 + IOR            | 1.465+IOR                |

| OUT      | Output from register                 | 6 + IOW            | 1.465+IOW                |

IOR = I/O read time (minimum 0.732 microseconds)

IOW = I/O write time (minimum 0.732 microseconds)

N = Number of bits shifted

Figure 6. WCP Instruction Repertoire (concluded)

## B. Programming Interface Characteristics

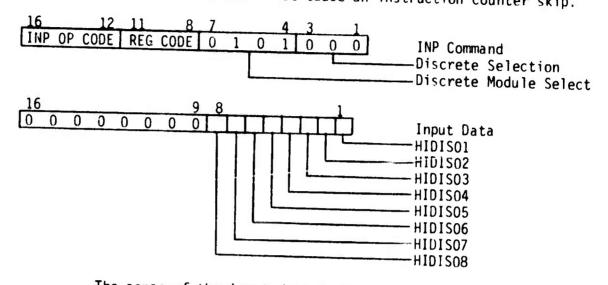

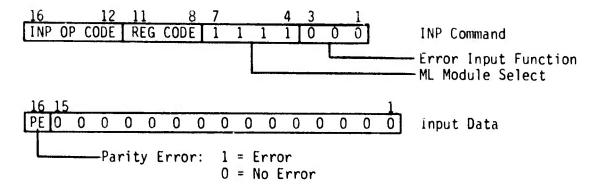

Input discretes HIDISO1 through HIDISO8 shall be available to the program from the Discrete Module. Program access shall be with an INP command whose particulars shall be as indicated below. The INP command shall not cause an instruction counter skip.

The sense of the input data is true, i.e., a logic "1" input will be represented as a one and a logic "0" input will be represented as a zero.

## 2. External Output Discretes

The WCP I/O will output two 28 Vdc discretes through optically coupled isolators. These outputs shall be powered individually from external 28 Vdc discrete voltages and referenced to individual discrete lows.

A. Signal Interface Characteristics

| 1. | Type:       | Th       | ree-wire, with power externally                         |

|----|-------------|----------|---------------------------------------------------------|

|    |             | CO       | nnected to the high and the load                        |

|    |             | 5.0      | nnected from the output to an externally pplied ground. |

| 2. | Power:      |          | ternal 28 Vdc+6 Vdc with transients to                  |

| 2  | <b>C</b>    | 80       | V Der MILSTD 704A 100 mamma                             |

| з. | Source Impe | ance: Lo | gic "1": Discrete power less                            |

|    |             |          | ansistor drop<br>gic "0": 20K to ground                 |

|    |             | LU       | gic o . zon to ground                                   |

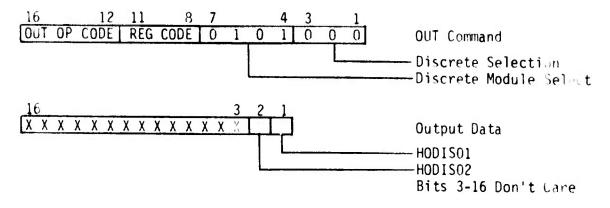

B. Programming Interface Characteristics

Output discretes HODISO1 and HODISO1 shall be controlled by the program by an OUT command to the Discrete Module. Issuance of the OUT command shall not cause an instruction counter skip.

The sense of the output data is such that the discrete is in the high (active)state when the output data bit is a one.

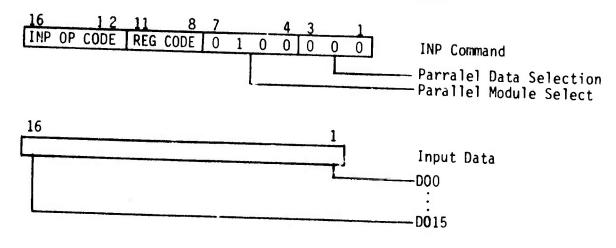

#### 3. Parallel Input Channel

The WCP I/O provides the program with an input communications from a ROLM 1602 Parallel I/O Buffer 3540 output channel. The channel consists of a 16-bit parallel information path to the WCP, a control path to the WCP, and a control path from the WCP. Control of the channel is exercised by the WCP program and by the Rolm 1602; thus, the word rates are variable.

A. Signal Interface Characteristics

The following signals comprise the Parallel Input communications channel.

| Signal                            | Source    | Definition                                                               |

|-----------------------------------|-----------|--------------------------------------------------------------------------|

| DO'N'<br>where 'N' = O through 15 | ROLM 1602 | Input data paths where DO O is the least significant bit of the transfer |

| OUT BUSY*                         | ROLM 1602 | Control path to WCP                                                      |

| EXT GATE                          | WCP       | Control path to Rolm 1602                                                |

This interface shall exhibit the following characteristics:

| 1. | Type:       | Single-ended TTL                                                                                                                                                                                                                                               |

|----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Source:     | Open collector TTL element with standard drive capability (SN5403, SN5405, or equivalent)                                                                                                                                                                      |

| 3. | Load - WCP: | 1K ohms to $V_{CC}$ and one standard TTL element.                                                                                                                                                                                                              |

| 4. | Load-1602:  | 330 ohms to $V_{CC}$ , 390 ohms to ground and one standard TTL element.                                                                                                                                                                                        |

| 5. | Sense:      | The data paths shall be true signals, i.e., a                                                                                                                                                                                                                  |

|    |             | high shall represent a logic "1". The 1602<br>control path shall be a false signal (a low<br>signifies data available on the data paths) and<br>the WCP control path shall be a true signal (a<br>positive pulse signifies that the WCP has read<br>the data). |

This interface is based upon the 3540 being wired to always enable the output data lines and to have OUT DONE set by the WCP.

In operation, OUT BUSY\* will normally be in the high (no data) state and EXT GATE will be in the low state. To initiate a transfer, the 1602 shall drop OUT BUSY\* to signify that a transfer is to be made and place the information on data lines DOO through DO15. Upon sensing the fall of OUT BUSY\*, the WCP will signal the program by generating an interrupt request. During the interrupt routine, the program will execute the INP command assigned to read the parallel channel. The RFI instruction used to terminate the routine will be sensed by the WCP I/O as a command to pulse the EXT GATE line. The fall of the EXT GATE pulse will cause the 1602 to raise the OUT BUSY\* line and to reset OUT DONE in the 1602, thus clearing the channel to allow another transmission.

The 1602 program must account for a unique case which is related to WCP signals in the event of a power interruption which would cause loss of the logic power in the WCP. The signal EXT GATE is normally low and is pulled up in the 1602. If logic control is lost in the WCP because of power loss, the 1602 circuitry will sense a high on this signal due to the pull up network under these conditions the 1602 would sense a completion of a transmission when none was intended. It should be noted that this would only be a interruption occurred before the transmission was completed and if the source of the interruption did not affect the 1602 or if a transmission was powered-up.

## B. Programming Interface Characteristics

The parallel input data is read with an INP command which should only be executed during the parallel input data interrupt subroutine. To signify that the data processed to the program is valid, the I/O shall force an instruction counter skip for OUT BUSY (data valid) and not force a skip if the INP command is executed when the input data is not valid. The parallel input interrupt subroutine should be minimized to maximize the transfer rate to the computer in that new data will not be presented until the RFI associated with the subroutine has been issued.

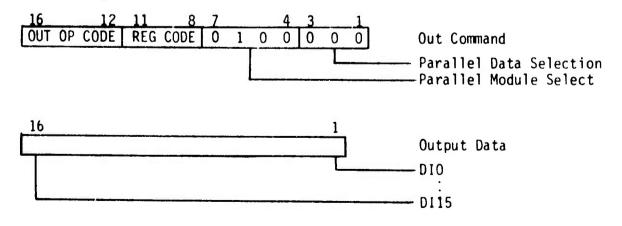

#### 4. Parallel Output Channel

The WCP I/O provides the program with an output communications channel to a Rolm 1602 Parallel I/O Buffer 3540 input channel. The channel consists of a 16-bit parallel information path from the WCP, a control path from the WCP and a control path from the 1602. Control of the channel is exercised by the WCP program and by the 1602, thus word rates are variable

#### Α. Signal Interface Characteristics

The following signals comprise the Parallel Output communications

| Signal                                                | Source             | Description                                                                                                                |

|-------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|