# INSTITUTE FOR DEFENSE ANALYSES

# An Initial Look at Alternative Computing Technologies for the Intelligence Community

Lance Joneckis - IDA

David Koester - MITRE Corporation

Joshua Alspector - IDA

January 2014

Approved for public release; distribution is unlimited.

IDA Paper P-5114 Log: H 14-000128

INSTITUTE FOR DEFENSE ANALYSES 4850 Mark Center Drive Alexandria, Virginia 22311-1882

The Institute for Defense Analyses is a non-profit corporation that operates three federally funded research and development centers to provide objective analyses of national security issues, particularly those requiring scientific and technical expertise, and conduct related research on other national challenges.

#### **About This Publication**

This work was conducted by the Institute for Defense Analyses (IDA) under contract HQ0034-14-D-0001, Project ET-2-2954.22, "Alternative Computational Technology." This research is based upon work supported by the Office of the Director of National Intelligence (ODNI), Intelligence Advanced Research Projects Activity (IARPA), via Army Contracting Command contract number W91WAW-12-C-0017. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the ODNI, IARPA, or the U.S. Government. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposed notwithstanding any copyright annotation thereon.

Copyright Notice

© 2014 Institute for Defense Analyses

4850 Mark Center Drive, Alexandria, Virginia 22311-1882 • (703)845-2000.

This material may be reproduced by or for the U.S. Government pursuant to the copyright license under the clause at DFARS 252.227-7013 (a)(16) [Sep 2011].

# INSTITUTE FOR DEFENSE ANALYSES

IDA Paper P-5114

# An Initial Look at Alternative Computing Technologies for the Intelligence Community

Lance Joneckis - IDA

David Koester - MITRE Corporation

Joshua Alspector - IDA

# **Contents**

| 1 | Executive | e Summary                                                   |  | 1             |

|---|-----------|-------------------------------------------------------------|--|---------------|

| 2 |           | and Recommendations                                         |  | <b>5</b><br>5 |

|   |           | pute model-specific solutions                               |  | 6             |

|   |           | Classical Digital Computing                                 |  | 6             |

|   |           | Neuro-Inspired.                                             |  | 9             |

|   |           | Analog                                                      |  | 10            |

|   |           | Quantum Computing                                           |  |               |

| 3 |           | Picture                                                     |  |               |

|   |           | Example of Holistic Design: Google's Compute Infrastructure |  | 13            |

|   |           | gle's Example Applied to the IC                             |  | 14            |

|   |           | Classical Digital Computing                                 |  | 21            |

|   |           | Neuro-Inspired Computation                                  |  |               |

|   |           | Analog Computing                                            |  |               |

|   |           | Quantum Digital                                             |  |               |

|   |           | clusion                                                     |  |               |

| 4 |           | Discussion: Compute Models                                  |  |               |

|   |           | damental Physical Limits on Computation                     |  |               |

|   |           | Landauer Limit.                                             |  |               |

|   |           | Bekenstein Bound                                            |  |               |

|   |           | Bremermann's Limit and the Margolus-Levitin Theorem         |  |               |

|   |           | Efficient Solution of NP-Complete Problems                  |  |               |

|   |           | ng Machine                                                  |  |               |

|   |           | Technologies                                                |  |               |

|   |           | Algorithms and Processing                                   |  |               |

|   |           | og                                                          |  |               |

|   | 4.3.1     | Theoretical Introduction                                    |  |               |

|   | 4.3.2     | Practical Introduction                                      |  |               |

|   |           | ro-Inspired                                                 |  |               |

|   |           | Description                                                 |  |               |

|   |           | Algorithms/Processing                                       |  |               |

|   |           | ntum Turing Machine (QTM)                                   |  |               |

| 5 | Detailed  | Discussion: Compute Technologies                            |  | 45            |

|   |           | OS and Beyond CMOS for Conventional CMOS Computing.         |  | 45            |

|   | 5.1.1     | Technologies                                                |  | 46            |

|   | 5.1.2     | Conventional Algorithms and Processing                      |  | 47            |

|   |           | al Cryogenic Superconducting                                |  |               |

|   |           | Technologies                                                |  |               |

|   |           | Algorithms/Processing                                       |  |               |

# CONTENTS

|   | 5.3 Ana   | log CMOS                                                        | 50 |

|---|-----------|-----------------------------------------------------------------|----|

|   | 5.4 Bion  | nolecular                                                       | 52 |

|   |           |                                                                 | 52 |

|   | 5.4.2     | Molecular-Tile Computing                                        | 53 |

|   |           |                                                                 | 55 |

|   | 5.4.4     | Neuromorphic Computing                                          | 56 |

|   | 5.5 Qua   | Intum Technologies                                              | 57 |

| 6 | Potential | l Follow-On Work: Deep Dives                                    | 59 |

|   |           |                                                                 | 60 |

|   | 6.1.1     |                                                                 | 60 |

|   | 6.1.2     |                                                                 | 60 |

|   | 6.1.3     |                                                                 | 61 |

|   | 6.1.4     |                                                                 | 61 |

|   | 6.1.5     |                                                                 | 62 |

|   | 6.1.6     | Theory and Practice of Processor-in-Memory Computing            | 62 |

|   | 6.2 Neu   | ro-Inspired Computation                                         | 63 |

|   | 6.2.1     | Silicon-Compatible Devices for Neuron, Axon, Synapse, and       |    |

|   |           | Dendrite                                                        | 63 |

|   | 6.2.2     | Interdisciplinary Understanding of Neural Structure, Computa-   |    |

|   |           | tional Model, and Algorithms                                    | 64 |

|   | 6.3 Ana   | ·                                                               | 64 |

|   |           | <b>0</b> 1                                                      | 64 |

|   | 6.3.2     | Interaction of Analog Computation with Other Computation Styles | -  |

|   |           | 64                                                              |    |

| 7 | Abbrevia  | ations                                                          | 65 |

| 8 |           |                                                                 | 67 |

| • |           | •                                                               | -  |

|   | Reference | es                                                              | 69 |

# 1 Executive Summary

We have broadly surveyed the computing landscape as it relates to the problems of interest to the intelligence community (IC). We did not find a single alternative computing technology (ACT) that is universally applicable to the wide range of IC applications, although particular solutions are suited to individual application classes. We therefore recommend that the IC consider an application-driven, holistic design approach that spans a broad range of technologies and computational models. The application classes we considered were discrete math, big data, distributed sensing and processing, scientific/numerical simulation, and robotics/autonomous systems. Holistic design could extend beyond a single technology to include integration of multiple, heterogeneous ACTs as needed to meet application/architecture requirements.

To meet mission requirements, the IC has been a leader in the development and deployment of computing and computing technologies. The computing design space in which the IC has worked runs the gamut from employing commodity components and systems to advanced special-purpose devices (SPDs). For those missions where commodity components have limited utility, the IC must question the implicit assumptions underlying current computing system design choices. This questioning must extend deeply, even to the fundamental model of computation used. Instead of asking which complementary metal oxide semiconductor (CMOS) chip we should use for a problem, we should ask about the chip we should design. Instead of what digital means of computation should we use, we might ask if we should even be solving this problem digitally. Clearly, a practice of routinely returning to fundamental questions bristles against practical concerns (such as schedule and cost), but it is the approach most likely to meet some of the unique, future needs of the IC.

The survey of the computing landscape documented in this paper extends far beyond the traditional classical digital style of computation and conventional digital CMOS technology. It even extends beyond quantum computing. By style or model of computation, we refer to how the solution to a given problem is obtained on a given computing system. The classical digital model of computation is embodied in what we might call conventional CMOS computing, ranging from the processing done in smart phones to the number-crunching done in high-performance computing (HPC) clusters. In the classical digital model data are represented digitally, and solutions to problems are computed via algorithms in a series of discrete steps. By contrast, in analog computing, data are represented by continuous values, and the solution to a problem is computed through the evolution of a dynamical system.

In the following paragraph, we describe the four fundamental styles of computing we considered: the classical digital, neuro-inspired, analog, and quantum digital. For each style of computing, we also discuss the technologies that may be used to realize a computing platform that solves problems in that style. We distinguish between technologies and platforms. For example, CMOS is a technology, while digital CMOS, with its associated infrastructure (including, for example, design and fabrication tools, and related technologies like dynamic random-access memory (DRAM)), is a device platform for realizing classical digital computing. In general, a device platform comprises the state variable (the means used to represent the computational unit), the material (the stuff that hosts the state variable), and the device (the means to manipulate state).

Classical Digital Computing: Classical digital computing, in which bits represent information and computation corresponds to sequences of elementary logic operations, dominates computing today. Conventional digital computing has, indeed, dominated the computer engineering and computer science communities for decades. We considered three platforms for conventional digital computing: CMOS and Beyond CMOS, superconducting, and biomolecular.

The CMOS and Beyond CMOS platform has been, and will continue to be, the dominant platform even after the CMOS transistor has reached its practical scaling limit, around 2024. Today, the number of transistors manufactured on a single CMOS 300-mm diameter wafer can approach one trillion. Other than biological processes, no other manufacturing process can come close to that low cost of compute element production. Industry will support the advancement of CMOS at the device (e.g., transistor) level throughout that time frame, with little need for United States Government (USG) investment. USG investment at the systems level (chip design through algorithm), however, can leverage industry's massive underlying investment and thus may have considerable impact. The two prime areas for USG investment in the CMOS and Beyond CMOS platform are holistic design and the power costs of high-bandwidth, low-latency communication. Most of the energy dissipation in CMOS is entailed in moving bits, and holistic designs that innovate across the spectrum of hardware to algorithm will be needed to obtain more efficient use of communication resources. Considering the entire technology stack can drive solutions that are optimized over the whole.

The cryogenic superconducting platform offers the potential of increasing computational power efficiency by  $10\times-1,000\times$ . CMOS and Josephson junction superconducting logic elements inherently draw comparable amounts of power, but the latter enjoys a substantial advantage in needing to expend almost no energy to move bits around. Applications that are communication intensive, which is the case for many of today's IC applications, will benefit the most from superconducting technology. USG investment will be required to move this platform forward through research to advanced development. Without eventual commercial adoption of superconducting technology, the USG will have to shoulder the burden of scaling the technology to increase performance, possibly a cost too great to bear alone.

The biomolecular platform offers the potential for power-efficient computing operating at the molecular level. While solutions to small instances of computationally hard problems have been demonstrated in this technology, extant biomolecular techniques

have poor scalability and specificity. The molecular tile approach provides for more control over the calculation but suffers from errors unless the speed of the calculation proceeds slowly. For these reasons this platform has little value for computationally hard IC problems. The biomolecular research community is currently exploring simple logic operations using a number of diverse mechanisms in vitro and in vivo, targeted not at complex calculations but rather for control of natural and synthetic biological systems. Likely application areas for these results include medicine, energy production, and environmental engineering. We recommend no IC investment at present though other parts of the USG, notably National Institute of Health (NIH) and National Science Foundation (NSF) should consider investing. The IC should monitor this area for future applicability to problems of interest.

Neuro-Inspired Computing: Neuro-inspired computing is expected to have superior performance for problems involving discrimination and pattern recognition, for example, with applicability to processing big data. This style of computing attempts to emulate the computation in animals with the goal of providing similar capabilities in engineered systems. It is motivated by the recognition that there is no transistor-based classical digital architecture, either now or foreseen for the future, that can reproduce the capabilities of the human brain while dissipating only 15 W.

The neuro-inspired compute model is currently a work in progress because we have only a limited understanding of how the brain works. Today's neuro-inspired architectures and algorithms extrapolate generously from a minimal grounding in biology. Maturing these approaches will require better characterization of the brain's processes at both the biological and algorithmic levels. We recommend an emphasis on interdisciplinary research strongly rooted in biology and computer science and complemented by other relevant disciplines.

We considered two platforms for neuro-inspired computing: analog CMOS and analog biomolecular. The CMOS platform is amply suited for realizing neuron-like devices, but it is missing an efficient synapse to be used for distributed memory and coupling neurons. Biomolecular technology, particularly in the context of synthetic biology, is at present too immature to realize neuro-inspired computing, but does offer a potentially interesting approach for the long term. Although the drivers of synthetic biology are not computation, this area should be watched for a potentially disruptive impact on neuro-inspired computing.

Analog Computing: Analog computing represents information as real-valued quantities, with computation proceeding via a set of differential equations of motion. Analog computation has low precision, making it undesirable for computations requiring exact results. *Programming* an analog system consists of mapping the problem of interest onto a dynamical system; for example, it appears to be possible to solve Boolean equations—an application of interest to the IC—by mapping the problem onto a system whose solution is given by the solution of differential equations. That done, it is unclear whether the most efficient place to solve those differential equations is on an analog computer.

Analog computing is reasonably mature, and a variety of technologies, ranging from analog CMOS to the extreme of analog computation in cells, present feasible platforms. The "programming" and set-up of the analog computation can be challenging even when running studies of similar problems. The benefits of analog computing need, however, to be established before investing in extensions to the computational platform. We recommend a small research effort to explore mappings between IC hard problems and dynamical systems.

Quantum Digital Computing: Quantum digital computing has the potential to reduce computational complexity for select problems. Shor's algorithm gives a way to shrink the number of required operations (from exponential to polynomial) for integer factoring and is the main motivation behind the desire to build a quantum computer. Simply put, a quantum computer is more powerful than a classical computer when it comes to factoring because, in principle, it has to do less work. Shor's algorithm is a particular application of a more general capability of quantum computing—a limited solution of the hidden subgroup problem, and this application has far reaching implications.

Quantum computing has explored well over a dozen candidate material systems over the last 25 years. Trapped ions, superconducting qubits, and electron-spin in solid-state materials have survived and continue to progress. Despite this investment, major challenges persist. A logical qubit, (i.e., one whose integrity is guaranteed for the duration of a calculation) remains elusive. Also, practical systems will likely comprise millions of qubits, which will need to be able to co-exist on that scale in an architecture. A worthy intermediate goal, therefore, is a scalable logical qubit. Obtaining such a qubit will require approaching the problem not only from the perspective of a technology that makes the best single qubit, but also asking what technology best supports system requirements for the desired capability. In other words, the solution should be holistically designed for a specific application. Adopting such an approach begins to move us away from a technology-centric perspective and towards a platform-centric perspective for quantum computing.

Holistic design may work to focus research to useful classes of technologies. Meanwhile, no technology that is capable of scaling to large numbers of logical qubits and adequately stable to complete a calculation has been identified. Mission capabilities implemented by quantum digital computing must be weighed against the likely substantial research investment required.

Conclusion: As computing moves into the future, solutions will necessarily become more specialized to the problem at hand. The more the solution space is expanded, the greater the potential for high-performance solutions but also the more investment that will be required. No single approach that covers the range of computational problems of interest. Because computational capabilities result in operational capabilities for the IC, investing in multiple approaches or in one approach at the expense of others is fundamentally a strategic decision that has long-term implications. Any strategic investment decision needs to carefully consider operational needs and tradeoffs.

# 2 Findings and Recommendations

### 2.1 Global Recommendations

**Finding:** With power, space, and cooling as forcing functions, computational power efficiency will become ever more important. Application-specific solutions, on which the IC has historically relied for a leg up, will be even more important for the computationally hard problems of the future. Maximum efficiencies will come from the right choice of computational style and platform.

Recommendation (G-1): Expand the design space to include a more diverse set of computational models and platforms. The IC, to preserve its edge, should extend the concept of application specificity to encompass computational styles and platforms. Innovation should not be restricted to conventional classical digital computational models realized on limited CMOS platforms. Pairing a problem to the right combination of style and platform, for example, factoring integers on a quantum computer, or using neuro-inspired processing for pattern recognition can lead to enormous gains in efficiency over conventional approaches. Hybrid systems that mix more than one style, such as embedding analog computation for certain mathematical operations, may also provide a benefit.

The dominance of digital computation has displaced analog computation historically, and this dominance presents a barrier to fully establishing alternative computational styles, such as neuro-inspired computation and the supporting hardware. Progress is further compounded by the need for these alternative computational styles to exceed capabilities of a digital solution. This situation is appreciated and several efforts are under way that address these issue. Substantial progress will require a sustained long-term and strategic commitment to these alternative computational styles.

Finding: A potentially viable alternative technology to CMOS (and its projected commercial evolution) for general-purpose, classical digital computation is superconducting, which offers the potential for an estimated one to three orders of magnitude reduction in electrical power, though this reduction in power is far from being realized. The other ACT candidates that emerged from the study—specifically neuro-inspired, analog, and quantum—represent not new technologies, but different computation styles. Each could be implemented via a range of substrates. The relevance of quantum computing to the IC is undisputed, but the potential of the other computational styles to serve IC needs is not as well understood. Neuro-inspired computing should be efficient for discrimination and pattern matching with applicability to big data. Analog computing has the potential of efficiently solving a set of first-order differential equations. ACTs may offer significant potential; however, much yet needs to be learned, and that research will require investment.

Recommendation (G-2): Algorithms are key. Historically, the big leaps in our

ability to factor numbers have come from new algorithms, with incremental assistance from progress in microelectronics. Improved algorithms have also have made important contributions in other areas, such as signal processing and machine learning. Like quantum computing, neuro-inspired and analog computing are attractive for their potential to stimulate the recasting of hard problems into forms that are more readily soluble. Also, just as efforts to realize quantum computing have required the joint contributions of mathematicians, computer scientists and physicists, the IC will need to mount interdisciplinary efforts to understand the implications of these other new computational models for its problem set.

**Finding:** The International Technology Roadmap for Semiconductors (ITRS) roadmap indicates the viability of CMOS for another 20 years. Industry is investing nearly \$50 billion yearly to sustain its trajectory. The CMOS platform will continue to advance even after CMOS reaches its practical scaling limit.

**Recommendation (G-3):** Know where to set the bar. To determine whether a candidate merits serious consideration as an alternate computing technology, the IC should compare its likely performance with the projections for CMOS on the ITRS roadmap.

**Finding:** No single alternative to CMOS can meet the ICs full range of computational needs of the IC. Quantum computing, for example, is superior for factoring integers, but neuro-inspired computation is superior for pattern matching,

**Recommendation (G-4):** Consider these preliminary findings. This study has identified benefits and limitations of ACTs. Since substantial investment will be needed to bring any individual ACT to the level of practicability, a detailed study of critical capabilities and gaps should be done before selecting or eliminating an ACT from consideration.

# 2.2 Compute model-specific solutions

# 2.2.1 Classical Digital Computing

**Finding:** The ITRS roadmap has a comprehensive strategy for emerging research material and devices. It has also defined 5 difficult challenges in the areas of memory, CMOS, Beyond CMOS, and heterogenous integration to focus the research. It is not clear that USG investment in this area will make a difference. Though the USG should closely monitor this area, and may need to make strategic investment, particularly in areas of design and architecture.

**Recommendation (C-1):** Do not invest in the CMOS Device Platform. This investment is already being adequately covered by industry. The focus of the IC should be on how to more effectively use the CMOS Device Platform for increasing computational efficiency through better design.

**Finding:** The imperative to keep costs low will drive industry to mass production of a limited set of standard central processing units (CPUs), memory, and other chips. These choices artificially constrain developer creativity and the computational model.

Recommendation (C-2): Pursue holistic co-design. To expand the application design space that CMOS can support, the USG should seek innovation throughout the CMOS technology stack. A holistic co-design paradigm will provide an efficient way to implement new algorithm research. Custom chip architectures may permit surprising efficiency gains, especially when designed along with the algorithm. The IC and USG should plan to leverage industry's scheduled advances but should also invest in expanding the possibilities for CMOS-based designs beyond those that will come from industry.

**Finding:** Moving bits in CMOS, regardless of origin or destination, is inefficient, and energy costs are not projected to decrease much in the future. Since these costs rapidly increase with distance from the CPU, communication-intensive applications, such as graph algorithms, scale poorly. The von Neumann architecture, where data and program are stored in local memory and shuttled to processor as needed, exacerbates the problem.

Recommendation (C-3): Break the von Neumann barrier. The high cost of communication in CMOS has gradually closed off solution options and constrained algorithmic creativity. The USG should go after this problem aggressively, seeking ways to lower the cost to move bits, to move fewer bits, and/or to reduce the distance the bits must travel. Solutions may involve transport technology, machine architecture, and algorithms. Likely, all three will be important, though transport technology is primarily a concern of industry. Algorithm research and subsequent holistic co-design will be the way to select which combinations of technologies to pursue.

**Finding:** Besides being more energy efficient, superconducting computers are potentially faster, with greater computational efficiency than conventional ones based on a CMOS platform; however, they also present the disadvantage of operating at 4 K. At present, superconducting is lacking a low-energy, high-performance memory, though several approaches appear promising. Many of the architectural principles developed for CMOS are applicable to the superconducting platform.

Recommendation (C-4): Experimentally demonstrate the operational advantage of the superconducting platform. Implement superconducting logic in the context of an architecture that can allow for a direct comparison with CMOS. Doing so will require addressing the current deficiencies in cryogenic memory. The Cryogenic Computing Complexity (C3) program of the Intelligence Advanced Research Project Activity (IARPA) is on the right track to implement this recommendation.

**Finding:** Superconducting logic has the advantage over CMOS for bit transport, since moving bits on superconducting lines entails no energy cost (some cost is still incurred moving bits into the processor from the outside). Communications-intensive algorithms should therefore operate more efficiently in superconducting computers than they would in CMOS-based platforms, where most of the energy is expended moving bits.

**Recommendation (C-5):** Explore superconducting communications-intensive machine architectures. Select several communications-intensive applications of interest to serve

as targets for application-specific superconducting machine architectures. Use initial computational efficiency estimates for these designs to drive subsequent technology development.

Finding: Superconducting computers generate significantly less heat than CMOS ones and so can provide a hospitable environment to host three-dimensional (3D) stacked-chip architectures, which are otherwise hard to cool. Achieving the full potential of this technology will require reducing superconducting circuit elements to smaller sizes to enable scaling and developing a novel approach to reliability that can ensure continuous operation of a 3D structure at 4 K.

**Recommendation (C-6):** Produce a roadmap for superconducting technology. The USG should charter a roadmap similar in intent to the ITRS, focused on the critical issues and challenges inherent in scaling to a smaller feature size. Publication of such a document will broadcast serious interest on the part of the government and suggest a way forward to the nascent superconducting community.

Finding: DNA computing has little practical value for tackling NP-hard problems. gates, ally, a brute force technique, the size of the space it can search is limited by the number of DNA molecules that can be simultaneously held in solution. While the technology does offer a significant speed-up over conventional computing for exhaustively searching small spaces, without the ability to scale to larger spaces, interesting problems lie beyond its reach. The molecular-tile approach gives DNA computing a way to implement logic gates; however, it has serious limitations. Instructions execute whenever they are triggered, and there is no easy way to evaluate them in a particular order. Also, to avoid contamination by stray chemical reactions, complex calculations are constrained to proceed very slowly.

Early optimism that molecular computing could offer a general-purpose computing technology using a biological substrate has given way to recognition that it will likely have utility only in a biological context. Most current research is focused on using molecular computing to address computational issues associated with enhancing or adding functionality to a biological system. The biological interactions are slow, occurring on the scale of minutes to days, but they can be exceptionally low power. Recommendation (C-7): The IC should not invest in biomolecular technology at this time. Biomolecular technology is not well suited for hard calculations. Molecular tile calculations are error prone and require slow growth rates to minimize errors. Computation based on biological processes cannot today implement either sophisticated decision logic or instruction sequences. Biomolecular computing will continue to mature without our investment for applications in medicine, fuel production, and environmental engineering. The field should be tracked for developments that might have a potential disruptive impact on general computation.

# 2.2.2 Neuro-Inspired

**Finding:** Neuro-inspired hardware computing approaches, despite their promise, are not solving problems of interest. In contrast, neuro-inspired machine learning approaches using software have shown usefulness and scalability, but they require too much digital computation and, therefore, too much compute time and power.

Recommendation (N-1): Guide hardware development with lessons from machine learning and neuroscience. Neuro-inspired computing suffers from a lack about understanding of how computation really proceeds in the brain. The USG should sponsor research that uncovers and is informed by the anatomical and biomolecular processes that make the brain so efficient. New neuromorphic hardware design efforts should incorporate findings from machine learning.

**Finding:** Neuromorphic computing is characterized by simple local processing in the "neurons," whose output affects a nearby subset of the "synapses" that form the application's distributed memory. Data do not move long distances and, therefore, computation has the potential to be extremely energy efficient. Applications in surveillance and robotics may be able to take advantage of this style of computation.

Recommendation (N-2): Fund hardware research to create energy-efficient "synapses" that can be integrated with CMOS. Creating this sort of memory architecture may be a stepping stone on the path to building a scalable neuro-inspired processor for larger problems. Current candidate chip-level building blocks are inadequate. Floating-gate structures are too large and require too much energy for updating, and memristors have a high failure rate.

**Finding:** Neuromorphic computing uses local learning algorithms to update the "synapse" values in response to data patterns at the periphery of the device. Rules based on spike-timing dependent plasticity (STDP) mimic biological synapses and can encode temporal patterns. Machine learning algorithms implemented in software are not always neuromorphic and do not generally account for temporal patterns naturally.

**Recommendation (N-3):** Fund research on hardware-friendly temporal learning algorithms. This research should be done in concert with hardware architecture research while being mindful of the progress being made in neuromorphic-style deep machine learning algorithms. Algorithms, architecture, and representations can draw inspiration from and guide hardware development in a co-design process.

**Finding:** Biomolecular methods for computing have not yet been used to create neuro-inspired architectures, but the self-assembly properties of DNA may have application to neuro-inspired computational constructs. The field of synthetic biology is advancing rapidly and may also create opportunities for advances in neuro-inspired architectures. Drivers for these technologies will come from the areas of medicine, energy production, and environmental engineering.

**Recommendation (N-4):** Watch synthetic biology advances for possible breakthroughs in creating neuro-inspired computers. Biology may produce potentially disruptive technologies for neuromorphic computation.

# 2.2.3 Analog

**Finding:** Analog computing is not well suited to traditional IC problems (like factoring) that require bit-precise calculation or high dynamic range. Analog computing is best suited to problems that allow for approximate solutions and may offer improved energy efficiency and speed over digital computing for some of those problems. It may have a niche role for accelerating the solution of IC problems that can be represented in terms of or modeled by physical systems.

**Recommendation (A-1):** Investigate the mapping of IC problems to dynamical systems. IC problems may have components that can be mapped to dynamical systems and could therefore be accelerated by analog computing. One real-world example is Boolean satisfiability, an optimization technique for which a dynamical systems approach with benefits over traditional algorithms has been demonstrated in principle [44].

# 2.2.4 Quantum Computing

**Finding:** Shor's algorithm for factoring integers has served as the overarching motivation for practical quantum computing to date. With the possible exception of quantum simulation, the other known quantum algorithms are primarily of theoretical interest or do not offer a sufficient reduction in calculation complexity to merit investment. Given the theoretical power of a computing model not limited to binary states, the dearth of interesting quantum computing algorithms is surprising and likely results from too much focus on the quantum circuit model. Our attempts to force quantum mechanics into a familiar computing construct may be limiting our ability to understand quantum computation at an intuitive level.

Recommendation (Q-1): Broaden scope of quantum models of computation and algorithms. Pursue basic research is aimed at expanding our understanding of computation in quantum systems beyond the digital circuit model. Without being too restrictive, focus attention on real problems where quantum computing can offer substantial improvement over the best classical computing approaches. Widening the applicability of quantum computing will increase industry's interest in sharing a portion of its development cost.

**Finding:** We have been on a 25-year quest for a logical qubit and are still a long way from achieving that goal. Since quantum states are fragile and protecting them from corruption by the surrounding environment is challenging, preserving computational integrity appears to hinge on effective quantum error correction. Today, some approaches are better than others, but we have no theory to say how much better they can get.

**Recommendation** (Q-2): Demonstrate a logical qubit suitable for scalable quantum computation. Focus efforts towards a practical logical qubit, that is, for which the quantum state can be maintained for the duration of the calculation and that can scale to support large computations of interest. Pursue a two-pronged strategy to

advance understanding of quantum error correction and aggressively seek a candidate physical qubit technology that is likely to meet scalability requirements.

**Finding:** It is no more likely that we will be able to have built a practical quantum computer from many of today's candidate qubit technologies than we could have built today's high-performance computers from vacuum tubes. The development of a quantum computer cannot be a linear process from qubit to system. We need to better understand the implications on system architecture of candidate qubit systems. To this end, there needs to be a symbiotic effort between qubit technology and system architecture for a scalable quantum computer. Performance stems from achieving balance over the whole system—from qubit to algorithm.

Recommendation (Q-3): Develop candidate system-level architecture for a capability quantum computer. A capability quantum computer is one that delivers a computational capability of interest to the IC and is scalable. In other words, it must have a useful performance threshold and be readily extensible to larger problems of the same type. This architecture effort needs to be symbiotic with the effort for demonstrating a logical qubit. Our current understanding of the qubit should drive the architecture and the architecture should drive the required performance of the qubit. Research needs to be application specific and consider the scalability of the calculation. The focus should be on achieving balance across the design space from qubit through algorithm.

**Table 2.1:** This table provides a summary of all the recommendations mentioned in this section. Additional detail can be found in the next chapter.

| Computing<br>Style   | Device Platform                                              | State                                      | Material                                                                          | Device                                              | State Material Device Component Node Architecture Archite                            | ecture                                                            | System<br>Architecture | Programming Algorithm<br>Model                              | Algorithm            |

|----------------------|--------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------|-------------------------------------------------------------|----------------------|

|                      | GaAs Quantum<br>dot<br>Si-Phoenhorous                        |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             |                      |

|                      | epololideo III-lo                                            |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             |                      |

| Quantum<br>Digital   | Si Quantum dot                                               | Q-2: Demons<br>logical qubit               | Q-2: Demonstrate a logical qubit                                                  |                                                     | Q-3: Develop architectures                                                           | Q-3: Develop candidate system level architectures                 | tem level              |                                                             |                      |

|                      | Superconducting                                              |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             |                      |

|                      | Trapped-ion                                                  |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             |                      |

|                      | Analog<br>Biomolecular<br>Mixed-signal                       |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             |                      |

| Anaiog               | Analog CMOS<br>Mixed-signal CMOS                             |                                            |                                                                                   |                                                     |                                                                                      |                                                                   |                        |                                                             | A-1: Map<br>problems |

| Neuro-               | Analog<br>Biomolecular<br>Mixed-signal<br>Biomolecular       | N-4: IC                                    | should attion to c                                                                | N-4: IC should watch for a application to computing | N-4: IC should watch for disruptive application to computing                         |                                                                   |                        |                                                             |                      |

| inspired             | Analog CMOS N-1: Gui<br>Mixed-signal CMOS biology<br>N-2: De | N-1: Gu<br>biology<br>N-2: De              | iide hardv<br>velop ene                                                           | vare from                                           | N-1: Guide hardware from algorithm and biology N-2: Develop energy-efficient synapse |                                                                   |                        | N-1: Neuro algorithms<br>N-3: Temporal learning             | orithms<br>learning  |

|                      | Biomolecular                                                 | C-7: IC<br>applic≀                         | should ation to c                                                                 | C-7: IC should watch for a application to computing | C-7: IC should watch for disruptive application to computing                         |                                                                   |                        |                                                             |                      |

| Classical<br>Digital | Superconducting                                              | C-4: De<br>perforn<br>C-6: ITF<br>for supe | C-4: Demonstrate performance advantage C-6: ITRS-like roadmap for superconducting | ntage<br>Imap<br>ng                                 | C-5: Explore                                                                         | communicatic                                                      | ins-intensive I        | C-5: Explore communications-intensive machine architectures | ectures              |

|                      | Beyond CMOS Digital CMOS                                     | C-1: IT<br>and Be                          | C-1: ITRS Challenges<br>and Beyond CMOS                                           | S                                                   | C-2: Pursue h<br>C-3: Break th                                                       | C-2: Pursue holistic design<br>C-3: Break the von Neumann barrier | n barrier              |                                                             |                      |

|                      |                                                              |                                            | Industry                                                                          |                                                     |                                                                                      | IC Investment                                                     |                        |                                                             | Othor I ISC          |

# 3 The Big Picture

In this chapter, we describe in more detail the "big picture" as we see it. The two chapters that follow this one contain much of the detailed analysis, with references. The final chapter presents several topics that merit further exploration than was possible in the study. These ideas are consistent with the findings and recommendations and may offer a way forward, though we caution the reader that they are preliminary and do not exhaust the possibilities. Because our foremost recommendation is the universal adoption of holistic design for the IC's compute problems, we start with perhaps the best known holistic design example: Google.

# 3.1 An Example of Holistic Design: Google's Compute Infrastructure

In the early days, Google quickly realized that the scale of computing needed was unprecedented and beyond the reach of commodity solutions. Relational databases were not large enough and were too expensive. In addition, it had to perform a non-standard calculation on a very large graph to determine page rank [90]. Google took ownership of their computing problem and crafted a solution that spanned the spectrum from algorithms to data centers. Its software approach was captured in three applications:

- Google File System is a scalable distributed file system for large distributed data-intensive applications. The file system was designed to be distributed over thousands of clusters, backup data through replication, and provide optimized sequential access for large files [50].

- MapReduce is a programming model that automatically parallelizes the computation across large-scale clusters and provides reliable operation in the presence of faults. MapReduce was primarily designed for indexing the web and now is part of Google's general computing infrastructure [36].

- **BigTable** is a distributed storage system for managing structured data, and is designed to scale to petabytes. It supports many applications including Google Search and Google Maps [30].

Google designed its own data centers to house compute clusters built from commodity components. On this end of the spectrum, Google made important innovations. For example, it noticed that standard power supplies were much less efficient than they could be and modified them (by removing (AC/DC) conversion stages and installing high-efficiency voltage regulators) to be  $\sim 25\%$  more efficient than typical power supplies. Google's data centers do not have a separate storage area

network, as would be the case with a commercial solution; rather all of the storage is contained on hard drives directly connected to processing nodes. A single web query uses hundreds of machines and completes in less than half of a second. The overall system is exceptionally fault tolerant, by design. Google's worldwide enterprise has 19 data centers and consumes 260 MW [52, 54].

Google thoroughly understood its problem and designed and implemented a solution that innovated at the machine architecture and programming model levels, leveraged the commercial market by using primarily commodity components, and could scale to unprecedented size. For example, the metric PageRank was developed to calculate an estimate of the number and quality of links referencing a web site. The iterative algorithm performs the calculations in a manner that can be implemented efficiently on a commodity cluster without expressly defining the graph structure. In addition, by designing its own compute infrastructure, Google was able to take a green energy approach at an early stage of the design process. Without this level of investment and innovation, Google might not be the company it is today.

# 3.2 Google's Example Applied to the IC

The example of Google's compute needs is not unique (see, for example, the history of D.E. Shaw's **Anton**, a special-purpose computer for studying protein folding). In fact, the example applies directly and indirectly to many government agencies, especially the IC. The Google example is an instance of data analytics—which is an important IC application. Moreover, the concepts embodied in the Google example should drive government agencies and the IC to think out-of-the-box for efficient operations.

While an approach based on commodity hardware is attractive for many reasons, it appears that a conventional CMOS-based digital approach is unlikely to scale to meet the future needs of the IC. The three overarching challenges are

- limiting electrical power consumption through increased computational efficiency,

- decreasing the high energy cost of moving bits, regardless of the origin and destination, and

- achieving application scalability for communication-intensive applications.

Computational efficiency is a measure of the useful work per Watt performed by a computing system. Large systems consume up to 10 MW of power. At a cost of \$1 million per year per MW, factors of 2 in energy efficiency have significant operational and performance impacts. Almost all of this power is consumed moving data—on chip, from local and global memory. At present, the energy cost of moving a 64-bit operand between CPU and local memory is  $50\times$  the cost to add two floating-point numbers. To move a 64-bit operand between CPU and global memory, the energy cost is  $200\times$  (the cost to add the numbers). In 2020 these costs are expected to be  $80\times$  and  $700\times$ , respectively. The consequence is that communication-intensive

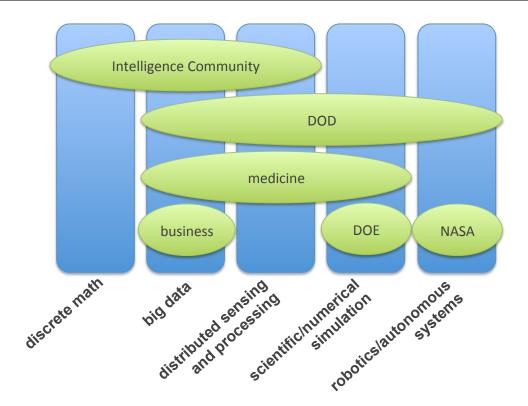

Figure 3.1: Applications of interest to the IC and others in government and the private sector.

applications scale poorly. Although memory bandwidth and access latency are slowly improving with time, they are not keeping up with increases in floating-point and integer operation capacity on a chip. The result is that it is becoming increasingly difficult to keep processors fed with data and instructions from memory [65].

Figure 3.1 shows applications of interest to the IC, the USG, and private sector. The broad application classes are discrete math, big data, distributed sensing and processing, scientific/numerical simulation, robotics/autonomous systems. The first three are of primary interest to the IC.

Within the limits of classical digital computing, we examined superconducting logic (based on Josephson junctions) and biomolecular computing and found that neither of these approaches was capable of overcoming the three challenges across the spectrum of application classes of interest to the IC.

Specifically, while superconducting technology eliminates the cost of moving bits within the superconducting domain, the cost of transferring data from the outside into the superconducting domain *does* dissipate energy at 4 K. Consequently, superconducting is expected to perform poorly on, for example, big data applications where the bulk of data is streamed from the outside into the processor. What is more, the energy cost of logic in superconducting circuits is expected to be similar to that of CMOS.

On applications for which most of the data remain in the cryogenic environment, superconducting is expected to improve computational efficiency by factors of 10–1,000 [61].

The best biomolecular algorithms for classically hard computational problems are still exponential in resources, though, in this case, the exponential resource is molecules and not time. Consequently, these algorithms scale poorly. Molecular tile computing techniques, which expand the possibilities of biomolecular computing, suffer from potentially high error rates. Optimizing the thermodynamics can reduce the error rate but at the expense of excessively slow compute speeds.

We know of no other viable candidate technology for classical digital computation except CMOS and the future evolution of CMOS, which is traditionally termed "Beyond CMOS." The ITRS describes the future of these technologies. Their development is determined by industry, with limited ability for the government to affect direction or timeline. While we did not survey Beyond CMOS technologies in detail, it is clear from the ITRS that there is no silver-bullet replacement for CMOS and that improvements will be evolutionary and incremental. At some time in the future, these incremental and evolutionary improvements may falter and a new disruptive, alternative computing technology will be required to move computing capabilities forward.

Even though CMOS device technology will advance at an incremental and predictable rate, it is less clear that we are getting all we can out of the CMOS device platform. In many cases, the design space is artificially constrained by a host of practical concerns. Software constraints include, for example, compatibility with the programming model. It is constrained at the component level by having to rely excessively on commodity chips because of the expense and time to create application-specific integrated circuits (ASICs). It is also constrained in cost and schedule by by the acquisition cycle. Industry invests 20% of its revenue, which was over \$50 billion in 2012, in research and development into silicon material systems. The future is clear—we need to get more out of the CMOS device platform (see Recommendation G-3).

Based on this and other considerations that we will discuss in detail later, we recommend that the IC consider an application-driven, holistic design approach that spans a broad range of technologies and computational models—including the integration of multiple, heterogeneous ACTs into a single system if required. Application-specific designs are not new to either the government or industry. We have described Google's approach. The government—most notably The National Security Agency (NSA) and The Department of Energy (DOE)—have a long track record of investment and innovation to develop solutions for demanding computation problems (see Recommendation G-1).

The classical digital style of computation dominates computing to such an extent that we forget about other computation styles. Table 3.1 lists the four computational styles considered in this report: classical digital, neuro-inspired, analog, and quantum

**Table 3.1:** Definition of compute style. Each compute style has a characteristic unit of information and processes to manipulate information.

| Compute<br>Style / Model | Unit of<br>Information | Description                                                                                                                                                                                             | Applications                                                                                                                                                            |

|--------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Classical Digital        | bit                    | Information is represented in binary form and manipulated by rule-based logic. Computation not governed by natural laws. Dominant computation style.                                                    | General-purpose computation of almost anything. Also used for application-specific computing.                                                                           |

| Neuro-inspired           | neuron & synapse       | Inspired by computational processes in living animals. Processing and memory are fine grained. Connection oriented. Capabilities are learned, not programmed. Computation not governed by natural laws. | Things the brain does well: pattern recognition, discrimination. Potential application to sensor processing and big data processing.                                    |

| Analog                   | real variable          | Information is represented as a real variable in a dynamical system. Computation governed by the natural laws of the system. Analog computation has limited precision.                                  | Not typically a computation<br>tool. Sometimes used in<br>control loops. Has been used<br>for controlling gunfire and<br>solving differential equations.                |

| Quantum Digital          | qubit                  | Information is represented in qubits in an analog form. Computation occurs through application of quantum gates, which are governed by the laws of quantum mechanics.                                   | Discrete math problems:<br>factoring integers, graph<br>isomorphisms, triangle<br>finding, element<br>distinctiveness. Not an<br>efficient general-purpose<br>computer. |

digital. Each style has a basic unit of information and a means of computation on that unit of information. The quantum digital circuit model, for example, represents information in qubits—two-level quantum systems—and information is processed via application of a sequence of quantum gates, which obey the laws of quantum mechanics.

Computational power—that is, the ability to make efficient progress on a problem of interest—is fundamentally related to the style in which the computer computes. Algorithms that are hard for classical digital remain hard for all ACTs and all machine architectures within the class of classical digital computation. Algorithms are intimately tied to computing style. Shor's algorithm for factoring integers is inherently a quantum algorithm and runs efficiently only on a quantum computer. Without an analysis of the alternatives that considers solving challenging problems over the different computing styles, we run the risk of less than optimal solutions or possibly, no solution at all.

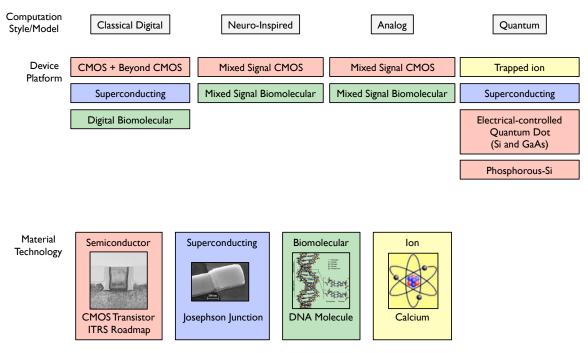

A computational style that has the potential for a significant advantage over classical digital but that cannot be reduced to practice results in little utility. Reducing a computational style to practice requires a viable device platform. Figure 3.2 shows the relationship between Computational Style, Device Platform, and Material

**Figure 3.2:** Relationship between Computational Style, Platform, and Material Technology. Colors show the relationship between the Material Technology and Device Platform.

Technology. The computational style/model is a theoretical construct that describes how information is represented and how it can be processed. The Material Technology is a broad technology base focused on a particular material system. The four material systems in this figure are Semiconductor, Superconducting, Biomolecular, and Ion. A Device Platform is the technology needed to produce the components (e.g., chips) in the system. Each material technology provides for one or more Device Platforms.

Figure 3.3 shows the organization of a classical digital computing system. The first two layers comprise the compute style and defines the unit of infomation, such as the bit for the digital computation style. The next four layers comprise the Device Platform and provide the capability of producing components for the system. For CMOS, this is the capability of producing CPU, DRAMs, and other packaged computer chips. The next three layers are the Machine Architecture organized as component, compute node, and system. The compute node provides the parts (e.g., chips) to build nodes. The compute node is, in general, capable of standalone execution of the compute model. System level scalability calability is achieved at the system level by interconnecting nodes.

At present, we do not innovate across the entire design space, and, consequently, our designs are suboptimal. Our tendency is to innovate at the node and system level. We build systems mostly out of commodity chips. Innovation at the programming model can be limited because of the need for backward compatibility with an existing software base. Opening up the design space is expensive and may also be prohibited

| Computational<br>Model/Style          | Classical<br>Digital                 | 7001001000<br>7001001000     | St                   | Defines the intrinsic nature of                                  |

|---------------------------------------|--------------------------------------|------------------------------|----------------------|------------------------------------------------------------------|

| Computational<br>Unit                 | Bit                                  | 0,1                          | Style                | the computation and the computational unit of information        |

| State<br>Variable                     | Charge<br>(electrons)                | 0.511 MeV/c² -1 1/2 electron | Dev                  | Physical entity used to represent the computational unit         |

| Material                              | Silicon                              |                              | Device Platform      | Material system for manipulating the state variable              |

| Device                                | CMOS<br>transistor<br>DRAM cell      |                              | orm                  | Devices capable of manipulating state                            |

| Component                             | CPU<br>DRAM<br>Co-Processor          | AMD                          | Machi                | Component - Computer parts made from the Device Platform         |

| Node                                  | Board<br>von Neumann<br>Architecture |                              | Machine Architecture | Node - Assembly of components capable of executing compute model |

| System                                | Global<br>Interconnect               | = 3,3                        | tecture              | System - Collection of nodes capable of sharing data             |

| Execution and<br>Programming<br>Model | MPI                                  |                              |                      | Software stack                                                   |

| Algorithm                             | LINPAC<br>Benchmark                  | <b>6</b> 500                 |                      | Application                                                      |

**Figure 3.3:** Breakdown of a system from computational model through algorithm using an HPC computer running LINPACK as an example. The first two layers define the compute style and unit of information. The next four layers (State Variable through Device) comprise the Device Platform, and the next three (Component through System) comprise the Machine Architecture.

because of practical acquisition constraints of schedule and cost. Opening up the design space requires strategic planning and investment. Having to support the entire stack, from state variable to algorithm is expensive but may not be so if extensive leveraging of existing technology is possible. Choices are important and should be grounded in compute style because, from this, stems computational power (see Recommendation G-1).

Developing a Device Platform for which there is not a Material Technology base is very expensive. Consider Semiconductor technology. In excess of \$50 billion per year is invested in this base technology, primarily focused on continuing Moore's law for CMOS semiconductors. It is by far the most developed of the four and its future is described in the ITRS. This technology base is larger than just the CMOS device platform. It also includes microelectromechanical systems (MEMS), mixed signal chips, and system on a chip. At present it is technically mature to support all of the compute styles with the exception of Quantum Digital. If a silicon-based device platform is ever developed for quantum computing, it should be an extension of the Semiconductor Material Technology base and should heavily leverage existing capabilities of semiconductor technology (see Recommendation G-3).

Biomolecular Material Technology is not particularly mature for computing. However, the driving applications for biomolecular are pharmaceutics and genomics, not computing. As such, biomolecular has the potential to be a disruptive technology for computing. The remaining two technologies we considered, superconducting and ion, are relatively immature, and have little support from industry, although they partially leverage Semiconductor for fabrication technology.

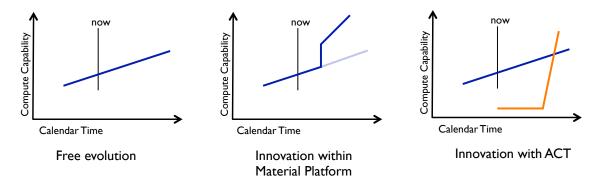

Figure 3.4 depicts the impact of different approaches to innovation on computational capability. The leftmost plot is the free evolution arising from advances in Device Platform. In the case of CMOS, this is Moore's law driven by the excess of \$50 billion annual investment in silicon. It is perhaps slightly misleading to call it free. It is only cost-free when a large user base supports research and development. The upward slope characterizes the increases in compute capability arising purely from advances in the device platform.

The middle plot in Figure 3.4 depicts innovation at the machine architecture level and above. The most effective innovation is algorithmic innovation. Finding a better algorithm leads to a discrete jump in capability, followed, in some cases, by a steeper slope because of more efficient use of computational resources. Novel and optimized machine architectures may also lead to discontinuous improvement. Machine architecture is more costly than algorithm innovation, however.

The rightmost plot in Figure 3.4 shows the impact of a novel alternative computing technology (orange line). In this case, there is a period of essentially *no* compute capability while the novel technology matures. The technology progresses through a scaling phase until it "takes off" and surpasses the conventional approach. The technology clearly needs to scale. For a limited time, the capability can scale simply

**Figure 3.4:** Scenarios resulting from different approaches to innovation in computational problems. The leftmost plot represents the "free" evolution in compute capability one obtains by allowing conventional CMOS to improve according to Moore's law due to industry investment. The middle plot represents the possible evolution resulting from directed efforts to innovate at the machine architecture level and above. The rightmost plot represents the evolution of a novel alternative compute technology (orange line) as it incubates and eventually "takes off." For the computational problem of prime factorization, the orange curve might represent quantum computing with Shor's algorithm, while the blue curve represents the evolution of a standard general number field sieve algorithm on CMOS hardware.

by letting the system get larger, but, ultimately, the Device Platform has to improve to provide for device scaling. This capability will have to be paid for by the user base, and it may be possible to offset some costs by leveraging innovations in other material systems. Supporting device level innovation, particularly if the costs of scaling also have to be carried, can rapidly become prohibitively expensive.

These observations and analysis led us to three general conclusions governing the role ACTs should play in the strategic computing landscape. The development effort required to make an ACT competitive may be considerable, and such a high cost must be considered in terms of the potential return on investment. The largest uncertainty is the future value of CMOS, particularly if the USG invests to expand its potential. Industry is willing to invest over \$50 billion per year in advancing silicon. The IC needs to leverage this investment to the maximum before resorting to an ACT. Spending upwards of \$1 billion per year on expanding the capability of silicon at the machine architecture level merits serious consideration given the cumulative investment in silicon by industry (see Recommendation G-3).

# 3.2.1 Classical Digital Computing

Classical digital computing represents information as bits and performs a sequence of logical operations on that information to compute. Although physical processes are used to compute, no natural laws govern the computation. Hence, a wide range of potential device platforms is available—everything from the standard CMOS to billiard balls. The three viable Device Platforms we examined were CMOS and Beyond CMOS, Superconducting, and Biomolecular, as shown in Figure 3.2.

In the most common form of the classical style of computing, a stored program controls execution with a von Neumann architecture. The von Neumann architecture stores the program in main memory. Program instructions and data are fetched from memory and executed in the CPU. The von Neumann architecture requires high bandwidth between the CPU and memory. The bandwidth between the CPU and memory often limits performance, and this limitation is called the von Neumann bottleneck. The introduction of multi-core CPUs without a commensurate increase in the memory bandwidth has stressed memory bandwidth even more. There are many variants on the basic von Neumann approach at the machine architecture level, and these systems also support a variety of programming models. The core ideas behind the von Neumann architecture are so ingrained in many of us that we often find it difficult to conceive of computing in any other way.

There is nothing inherently wrong with the von Neumann architecture. The problems stem mostly from limitations at the Device Platform level. Specifically, in the CMOS and Beyond CMOS platform, moving bits dissipates most of the energy, and, by its nature, the von Neumann architecture moves a lot of bits. Alternatively, the superconducting platform moves bits at 4 K, with practically no energy dissipation.

Biomolecular computing is not a von Neumann architecture, though it can have the same compute capabilities, in principle. Information is coded into molecules. Communication is performed by random mixing of molecules in solution, and processing is via chemical reactions driven by heat. Bennett has noted that this is an example of Brownian computation [20]. The computation is a random-walk driven by heat. Dissipation is necessary to prevent the chemical reaction from going in the backward direction. Dissipation of  $20 \ kT^1 \ (100 \ kT)$  gives a probability of error of  $e^{-20} \approx 2 \times 10^{-9} \ (e^{-100} \approx 4 \times 10^{-44})$ , respectively. For comparison, CMOS transistors switch at  $100,000 \ kT$  and superconducting logic is about the same, after accounting for thermal efficiency of the refrigerator need to cool a superconducting computer to 4 K. Hence, biomolecular computing offers the possibility of extremely low-power computation (though one should also include the power required to run the associated laboratory equipment used in the calculation). Table 3.2 presents an overview of our recommendations for the Classical Digital style of computing.

#### CMOS and Beyond CMOS

A global market for semiconductors of more than \$300 billion annually [4] drives more than \$50 billion annually [1] into research and development of the Silicon Material System and the CMOS Device Platform. The IC needs to leverage industry's investment to the greatest extent possible.

The ITRS roadmap predicts that the CMOS transistor will reach its practical scaling limit in 2024 and that that limit will be only  $3\times$  worse than the theoretical

$<sup>^{1}</sup>kT$  is the thermal energy of a degree of freedom of a system at temperature T. At room temperature (300 K),  $kT = 4.1 \times 10^{-21}$  J.

Table 3.2: Recommended investment strategy "map" for CMOS and Beyond CMOS. The technology stack, from state variable to algorithm is listed at the top of each column. Individual device technologies are listed in each row. Our recommended investment strategy for each portion of the map (i.e., each combination of technology and location in the technology stack) is labeled by reference to a particular recommendation from Section 2 in the format C-N.

| Computing<br>Style   | Device Platform           | State              | Material                                        |                  | Component<br>Architecture                                         |              | System<br>Architecture | Programming<br>Model | Algorithm |  |

|----------------------|---------------------------|--------------------|-------------------------------------------------|------------------|-------------------------------------------------------------------|--------------|------------------------|----------------------|-----------|--|

|                      | Biomolecular              |                    | Should ation to d                               |                  | r disruptive                                                      |              |                        |                      |           |  |