# A QUANTUM COMPUTING APPROACH TO MODEL CHECKING FOR ADVANCED MANUFACTURING PROBLEMS

UNIVERSITY OF SOUTHERN CALIFORNIA – INFORMATION SCIENCES INSTITUTE

JULY 2014

FINAL TECHNICAL REPORT

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

STINFO COPY

# AIR FORCE RESEARCH LABORATORY INFORMATION DIRECTORATE

#### NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report is the result of contracted fundamental research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated 10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09. This report is available to the general public, including foreign nationals. Copies may be obtained from the Defense Technical Information Center (DTIC) (http://www.dtic.mil).

AFRL-RI-RS-TR-2014-193 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH ASSIGNED DISTRIBUTION STATEMENT.

FOR THE DIRECTOR:

/ **S** /

STEVEN L. DRAGER

Work Unit Manager

/S/

MARK H. LINDERMAN

Technical Advisor, Computing &

Communications Division

Information Directorate

This report is published in the interest of scientific and technical information exchange, and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

### **REPORT DOCUMENTATION PAGE**

Form Approved OMB No. 0704-0188

The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number.

PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| a. REPORT<br>U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | b. ABSTRACT<br>U            | c. THIS PAGE<br>U | UU                                  | 67                                  | 19b. TELEPH<br><b>N/A</b>               | IONE NUMBER (Include area code)                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|-------------------------------------|-------------------------------------|-----------------------------------------|---------------------------------------------------------------------------|--|

| ABSTRACT OF PAGES STEVEN I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |                   | F RESPONSIBLE PERSON FOR L. DRAGER  |                                     |                                         |                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   | r, Model Checkir<br>Abstraction Ref |                                     | nconstrai                               | ned Binary Optimization, Integer Linear                                   |  |

| 15. SUBJECT T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ERMS                        |                   |                                     |                                     |                                         |                                                                           |  |

| into a Model Checking (MC) approach based on Counter-example Guided Abstraction Refinement (CEGAR). The computational bottleneck of this approach is the solution of certain combinatorial optimization problems for which the D-Wave processor was specifically designed. We developed a set of tools to sidestep the restrictions imposed by the limited connectivity of the processor, performed a set of benchmarking tests of the device, and implemented a proof of concept example that integrated the quantum processor with regular model checking techniques. |                             |                   |                                     |                                     |                                         |                                                                           |  |

| This project s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | studied the fea             |                   |                                     |                                     |                                         | iabatic quantum annealing processor                                       |  |

| 14. ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |                   |                                     |                                     |                                         |                                                                           |  |

| 13. SUPPLEME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NTARY NOTES                 |                   |                                     |                                     |                                         |                                                                           |  |

| Approved for exempt from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Public Relea public affairs | security and p    | n Unlimited. This                   | ccordance with                      |                                         | ontracted fundamental research deemed<br>R memorandum dated 10 Dec 08 and |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   |                                     |                                     |                                         | AFRL-RI-RS-TR-2014-193                                                    |  |

| Air Force Research Laboratory/RITA<br>525 Brooks Road<br>Rome NY 13441-4505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |                   |                                     | 11. SPONSOR/MONITOR'S REPORT NUMBER |                                         |                                                                           |  |

| Air Force Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | search Labora               | atory/RITA        |                                     |                                     |                                         | AFRL/RI                                                                   |  |

| 9. SPONSORIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | G/MONITORING                | AGENCY NAME       | (S) AND ADDRESS                     | S(ES)                               |                                         | 10. SPONSOR/MONITOR'S ACRONYM(S)                                          |  |

| University of Southern California – Information Sciences Institute 4676 Admiralty Way, Suite 1001 Marina del Rey, CA 90292-6601                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   |                                     |                                     |                                         |                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   | D ADDRESS(ES)                       | Institute                           | 1                                       | 8. PERFORMING ORGANIZATION REPORT NUMBER                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   | 5f. WORI                            | 5f. WORK UNIT NUMBER<br>QC          |                                         |                                                                           |  |

| Federico M. Spedalieri, John Damoulakis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |                   |                                     |                                     | 5e. TASK NUMBER<br>SL                   |                                                                           |  |

| 6. AUTHOR(S)  Fodorico M. Spedalieri, John Demoulekia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |                   |                                     | 5d. PROJECT NUMBER HACM             |                                         |                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   |                                     | 5c. PROGRAM ELEMENT NUMBER 62303E   |                                         |                                                                           |  |

| ADVANCED MANUFACTURING PROBLEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                   |                                     | 5b. GRANT NUMBER N/A                |                                         |                                                                           |  |

| A QUANTUM COMPUTING APPROACH TO MODEL CHECKING FOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |                   |                                     |                                     | 5a. CONTRACT NUMBER<br>FA8750-13-2-0035 |                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JLÝ 2014                    | <u> </u>          | FINAL TECHN                         | NICAL REPOR                         | RT NOV 2012 – JAN 2014                  |                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TE (DD-MM-YY)               | (Y) 2. REP        | ORT TYPE                            |                                     |                                         | 3. DATES COVERED (From - To)                                              |  |

### TABLE OF CONTENTS

| Section | Page |

|---------|------|

|---------|------|

| List o | of Figures                                                                          | .iii |

|--------|-------------------------------------------------------------------------------------|------|

| List o | of Tables                                                                           | .iii |

| 1 S    | UMMARY                                                                              | 1    |

| 2 IN   | NTRODUCTION                                                                         | 4    |

| 2.1    | D-Wave Two (DW2) adiabatic quantum optimization processor overview                  | 4    |

| 2.1.1  | The Physical Principles of the D-Wave Quantum Computer                              | 6    |

| 2.1.2  | Programming and Using the D-Wave Quantum Computer                                   | 7    |

| 2.1.3  | Counterexample guided abstraction refinement                                        | 8    |

| 2.1.4  | Refining the Abstraction                                                            | 9    |

| 2.1.5  | Minimal Separating Set                                                              | 11   |

| 3 N    | METHODS, ASSUMPTIONS, AND PROCEDURES                                                | 13   |

| 3.1    | Feasibility study of using DW2 for Bounded Model Checking and Binary Decis Diagrams |      |

| 3.2    | Benchmarking of DW2 performance on MAX-2-SAT against classical sol MaxWalkSAT       |      |

| 3.2.1  | MAX-2-SAT                                                                           | 13   |

| 3.2.2  | MaxWalkSAT                                                                          | 14   |

| 3.2.3  | Instance ensemble                                                                   | 14   |

| 3.2.4  | Benchmarking strategy                                                               | 15   |

| 3.3    | Development of heuristic embedding algorithm                                        | 15   |

| 3.3.1  | Iterative heuristic embedding                                                       | 16   |

| 3.4    | Integration of CEGAR approach with DW2                                              | 18   |

| 3.4.1  | Converting SAT to ILP                                                               | 19   |

| 3.4.2  | Converting ILP to QUBO                                                              | 19   |

| 3.5    | Implementation of Model Checking example                                            | 21   |

| 4 R    | RESULTS AND DISCUSSION                                                              | 22   |

| 4.1    | Feasibility study of using DW2 for Bounded Model Checking and Binary Decis Diagrams |      |

| 4.1.1  | Creating propositional formulas in BMC                                              | 22   |

| 4.1.2 Mapping of propositional formulas for BMC into DW2                   | 23     |

|----------------------------------------------------------------------------|--------|

| 4.1.3 Results of the suitability study for Bounded Model Checking          | 23     |

| 4.1.4 Implementation of Binary Decision Diagrams using DW2                 | 24     |

| 4.1.5 Binary Decision Diagrams                                             | 24     |

| 4.1.6 Model checking algorithms                                            | 25     |

| 4.1.7 Issues with casting computation of extremal BDD as optimization prob | olem25 |

| 4.1.8 Results of BDD implementation using DW2                              | 26     |

| 4.2 Benchmarking of DW2 on MAX-2-SAT versus MaxWalkSAT                     | 26     |

| 4.2.1 Analysis of the benchmarking results                                 | 27     |

| 4.3 Implementation of a heuristic embedding tool                           | 28     |

| 4.3.1 Code structure                                                       | 28     |

| 4.4 Integration of DW2 into CEGAR loop                                     | 31     |

| 4.4.1 Verifying the validity of abstract counterexamples                   | 31     |

| 4.4.2 Refining the model                                                   | 33     |

| 4.4.3 CEGAR Implementation                                                 | 35     |

| 4.4.4 ILP Problems                                                         | 36     |

| 4.5 Implementation of CEGAR based model checking example                   | 36     |

| 4.5.1 Verification summary                                                 | 37     |

| 4.5.2 Detailed transcript                                                  | 37     |

| 4.6 Evidence for quantum behavior in the DW2 processor                     | 52     |

| 4.6.1 Quantum signature                                                    | 53     |

| 4.6.2 Evidence of entanglement                                             | 53     |

| 5 CONCLUSIONS                                                              | 54     |

| 6 REFERENCES                                                               | 56     |

| 7 APPENDIX A – Publications and Presentations                              | 58     |

| 8 APPENDIX B – Description of CEGAR-DW2 integration code                   | 59     |

| 9 LIST OF SYMBOLS, ABBREVIATIONS, AND ACRONYMS                             | 60     |

### LIST OF FIGURES

| Figure | Page                                                                               |

|--------|------------------------------------------------------------------------------------|

| 1      | D-Wave One connectivity graph6                                                     |

| 2      | Schematic representation of the compound superconducting loops used to realize the |

|        | qubits in the D-Wave processor7                                                    |

| 3      | Energy profile of a superconducting flux qubit                                     |

| 4      | Example of abstracted model10                                                      |

| 5      | Spurious counter example                                                           |

| 6      | CEGAR loop                                                                         |

| 7      | Benchmarking results for MAX-2-SAT27                                               |

|        |                                                                                    |

|        | LIST OF TABLES                                                                     |

| Table  | Page                                                                               |

| 1      | Truth table for Boolean OR and energies of associated 2-qubit Hamiltonian          |

#### 1 SUMMARY

The goal of the Quantum Computing Approach to Model Checking for Advanced Manufacturing Problems (QCHECK) research project was to determine if it is feasible in the future to speed up a Model Checking (MC) approach based on Counter-example Guided Abstraction Refinement (CEGAR) by using a D-Wave open system, adiabatic quantum annealing processor. These are specialized computing devices that solve spin Ising models, which are equivalent to Quadratic Unconstrained Binary Optimization (QUBO). We focused on two aspects of the CEGAR approach that involved solving integer linear programs (ILPs) and Boolean satisfiability (SAT) problems. The project was divided in five tasks:

- **Task1:** Study feasibility of using a D-Wave to solve Bounded Model Checking (BMC) problems and implementing Binary Decision Diagrams (BDD) based techniques.

- **Task 2:** Compare the performance of a second generation D-Wave (DW2) on MAX-2-SAT problems native to its architecture, versus the heuristic solver MaxWalkSat.

- **Task 3:** Develop a heuristic embedding algorithm for the DW2 to get around the limited connectivity of the processor.

- **Task 4:** Integrate the CEGAR approach with the DW2 processor.

- **Task 5:** Implement examples.

#### Results:

**Task 1:** It was found that even though in principle the required BMC problems could be cast as QUBO problems, the probabilistic nature of the processor (that provides no guarantees that the best possible solution has been found) made the approach susceptible to false negatives: a SAT formula could be proclaimed "unsatisfiable" because the best solution found by DW2 does not satisfy the formula, while a better solution might exist that proves the formula satisfiable. With regards to implementing BDD based approaches using DW2, it was concluded that encoding such a problem as an optimization problem, though possible, would not scale well with system size.

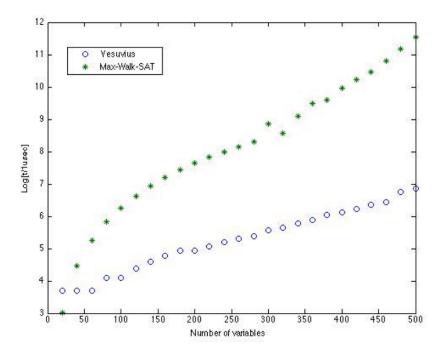

- **Task 2:** The comparison was performed on a set of random instances of MAX-2-SAT that are native to the DW2 processor's architecture, for different numbers of variables. The performance of DW2 was shown to be better than that of MaxWalkSat, with the caveat that MaxWalkSat was not optimized for the DW2 architecture. The issue of DW2's performance vs. that of classical solvers remains (as this report is being written) an open and very contested research topic.

- **Task 3:** A tool to perform heuristic embeddings was created. It allowed us to implement QUBO problems that had a different connectivity graph than the native DW2 architecture. This tool is useful for optimization problems, but suffers the same limitations found in Task 1 for decision problems (i.e., SAT) due to the lack of a guarantee that the solution found is the best possible. The tool needs further optimization, and alternative approaches need to be investigated.

- **Task 4:** Several issues arose that made this task more challenging than was anticipated:

- 1. Off-the-shelf model checking packages do not provide access to internal data such as the ILP needed to be solved during the CEGAR implementation. We contacted the developers but they were reluctant to give us access to the source code.

- 2. Many simple models that we studied generated trivial ILPs during the CEGAR implementation, i.e., the solution could be found by simple inspection. It took some time to learn from these models what properties of the system will lead to non trivial ILPs.

- 3. In order to have access to the ILPs we ended up writing a small model checking package using publicly available libraries. We used the And-Inverter Graph (AIG) format, allowing us to generate small, non-trivial ILPs (on the order of tens of linear constraints and binary variables).

**Task 5:** We found an example from the literature of a flight control system and checked a safety property that requires two exclusive flight modes not to be engaged at the same time. We implemented this problem integrating the AIG-based model checker with the DW2, ran the CEGAR approach starting with an abstraction that had 33 hidden variables. Our integrated code proved the system to be safe by making visible only 14 of the 33 hidden variables.

#### Main lessons learned during the execution of this project

The current programing paradigm of the DW2 processor requires either heuristic embeddings or approximate embeddings to implement QUBO problems that do not have connectivity native to the processor. This step leads to a loss of certainty about whether the optimal solution to the original problem is the same as the optimal solution to the embedded problem. This feature potentially results in false negatives when solving decision problems with DW2. For example, if the best answer provided by the processor corresponds to a negative result for the decision problem (e.g., a SAT formula is not satisfiable), yet there exists a better solution to the original decision problem that gives a positive answer (i.e., the SAT formula may be satisfiable). Note that there are no false positives, since a positive answer provides that the corresponding assignment can be checked efficiently.

Optimization problems are better suited for the current programming toolbox. Even though we may not find the optimal solution to a problem, both the heuristic and approximate embedding approaches provide "good solutions", which can still be very valuable if they can be found faster than with other methods. The heuristic embedding tool developed in this project is designed to generate a sequence of improving solutions, although there is no guarantee that the optimal solution will be found (although additional information about the problem may help identify when optimal solutions are found).

The question of speed up with respect to classical algorithms is very hard to answer. A benchmarking against a particular classical algorithm will not preclude the existence of another, more efficient algorithm. Since we can only estimate the scaling behavior of the runtime performance of the DW2 processor by benchmarking it on a given set of instances, the problem is translated into finding a particular set of instances that show speedup over some set of classical algorithms. Even how to pose the question of speedup has been the subject of intense research. At this point in time, there is no conclusive evidence that the DW2 provides any speedup, but this has only been tested up to 500 variables. New processors with up to 2000 qubits are expected to be available in the next two years.

Although not directly related to this project, very important results have been obtained regarding the quantum nature of the DW2 processor. Even though it is designed to operate in a quantum

mechanical regime, it is not easy to experimentally confirm this feature. During the execution of this project we also performed research aimed at resolving this issue. Two approaches were devised: one provided evidence of a quantum signature by analyzing the statistics of the output of the DW2 processor when solving a carefully designed problem involving 8 qubits. The second approach, implemented in collaboration with the company D-Wave, gave a definitive answer regarding the quantum nature of the device by showing that entanglement is present during the quantum annealing evolution. Whether this entanglement can provide a computational speedup is still an open question.

In terms of the integration of the CEGAR model checking approach and the DW2 processor, the proposed approach was shown to be very straightforward. The obstacles encountered were not related to the fundamental idea of the approach, but rather to the technical limitations of the software tools required (lack of access to the inner workings of the CEGAR implementation available in the different publicly available model checking packages). Any model checking package that provides the required information (i.e., the ILPs to be solved in CEGAR) could be easily integrated to interface with the DW2 processor.

#### 2 INTRODUCTION

The goal of the QCHECK project was to analyze the feasibility of exploiting the computational capabilities of the DW2 adiabatic quantum processor in order to speedup and improve the solution of model checking problems. The DW2 device is designed to solve combinatorial optimization problems by exploiting quantum mechanical effects of an array of Superconducting Quantum Interference Devices (SQUIDs) [1].

One of the main drivers of the computational hardness of model checking problems is the extremely large size of the state space that needs to be considered [2]. The different algorithms and techniques that have been developed to solve model checking problems need to implement in one way or another, a mitigation strategy for this problem. One of the approaches that have been proposed and developed is based on abstractions. The main idea is to replace the system that needs to be checked by an abstraction that has a much smaller state space, with the feature that if a property is found to be true in the abstraction it is automatically true in the original system. Since the size of the abstracted state space is smaller, the algorithms employed to address the abstract problem require much less computational resources.

The abstraction based approach however, comes with a price: a property may be proven wrong in the abstraction when it is actually true in the original system (false negative). To avoid this problem, every counterexample to a property found in the abstraction must be verified as valid, i.e., a corresponding counterexample must exist in the original system. When such a counterexample cannot be produced, we say that the abstraction generated a spurious counterexample, and the truth or falsehood of the property remains unknown.

To solve this issue an approach known as Counterexample Guided Abstraction Refinement has been developed [3]. The basic idea is to use the structure of the spurious counterexample to generate a finer abstraction that would get rid of it. A finer abstraction has a larger state space and so it is important to find a refinement that increases the size of the state space the least. This process continues until the property is proven to hold, or a valid counterexample in the original system is found. We have identified an approach to CEGAR in which combinatorial optimization problems of the form that can be solved by the DW2 processor are a central part of the algorithm: one is to check whether an abstract counterexample corresponds to an actual counterexample in the original system which requires solving an instance of a Boolean Satisfiability problem; the other is at the root of finding the smallest abstraction refinement that can get rid of a spurious counterexample and requires solving and Integer Linear Program.

#### 2.1 D-Wave Two (DW2) adiabatic quantum optimization processor overview

The DW2 adiabatic quantum computer solves a Quadratic Unconstrained Binary Optimization. This optimization consists in finding the vector of binary variables that minimizes the quadratic objective function

$$f(x_1, ..., x_n) = \operatorname{Min}_{[\underline{x}]} \{ \sum_{[i < j; i=1, ..., n; j=1, ..., i-1]} Q_{ij} x_i x_j \}$$

(1)

where  $\underline{x} = (x_1, x_2, ..., x_n)$ ,  $x_i \in \{0,1\}$ , and  $Q_{ij}$  is a matrix of real numbers that determines the objective function. This problem is equivalent (through a simple linear transformation of the variables  $x_i \to s_i = 2x_i - 1$ ) to the *Ising model*. The *Ising* model represents a set of interacting spin magnets with an energy given by:

$$\boldsymbol{E}(s_1, \ldots, s_n) = \sum_{\text{fi} < i; i=1, \ldots, n} \boldsymbol{J}_{ii} s_i s_i + \sum_{\text{fi} = 1, \ldots, n} \boldsymbol{h}_i s_i$$

(2)

where the spin variables,  $s_j$ 's, now take the values  $\{+1,-1\}$ , the parameters  $J_{ij}$  represent the interactions between two spins, and the parameters  $h_i$  correspond to local magnetic fields. Solving the *Ising* model consists in finding the spin configuration that minimizes the energy, E. This problem is known to be NP-hard [4], and many important combinatorial problems can be reduced to it [5].

DW2 implements a quantum version of the *Ising* model, where each spin variable is replaced by a Pauli operator  $\sigma_z$ , representing the state of a qubit (quantum bit) that is associated with the magnetic flux of a superconducting quantum interference device (flux-SQUID). The *Ising* Hamiltonian, given by

$$H_{\text{Ising}} = \sum_{[i=1,...,N]} \{ \sum_{[j=1,...,N]} [J_{ij}\sigma_i^z \sigma_j^z] \} + \sum_{[j=1,...,N]} h_i \sigma_i^z$$

(3)

characterizes the quantum mechanical system of spins. The device allows for tunable interactions between the different qubits (i.e., tunable parameters  $J_{ij}$ ), as well as tunable local biases (parameters  $h_i$ ).

Quantum annealing in the D-Wave processor proceeds as follows: initially a transverse field is applied such that the lowest energy state has all the spins pointing in the same transverse direction, a quantum superposition of +1 and -1. The parameters are then slowly varied in order to transform the Hamiltonian into  $H_{\text{Ising}}$ , whose ground state encodes the solution to the optimization problem. The adiabatic theorem of quantum mechanics assures us that, provided this parameter change is slow enough, the final state of the system corresponds to the ground state of the final Hamiltonian [6], i.e., the spin configuration that minimizes the energy function. The values of the spins are obtained by measuring the flux of each qubit at the end of the annealing. In reality, due to the probabilistic nature of this quantum mechanical system, this process must be repeated several times in order to expect to identify the lowest energy configuration.

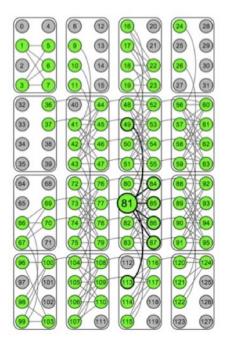

Our initial D-Wave One (DW1) system had 128 qubits, depicted as green and gray circles in Figure 1. They are arranged in a 4 x 4 array of 8-qubit tiles. In each tile, the qubits are separated in two groups of 4 and connected in a bipartite fashion [7] (each qubit is only connected to all the qubits in the other group). Some qubits in each tile have extra connections to qubits in other tiles, such that the graph is connected (but not fully connected). The connectivity graph is called the Chimera graph [8]. The DW2 processor used in the latter part of the project has 512 qubits. It is composed of a 16 x 16 array of 8-qubit tiles connected in a similar way as in Figure 1.

Figure 1. D-Wave One connectivity graph

This connection topology is dictated by constraints imposed by the underlying technology, but the design is scalable up to many thousands of qubits. The lack of full connectivity between all the qubits in the chip prevents a straightforward mapping of an arbitrary *Ising* Hamiltonian (or, equivalently, an arbitrary quadratic function) into the processor. However, although constructing and optimizing this embedding is not a trivial issue, several heuristics have already been developed.

#### 2.1.1 The Physical Principles of the D-Wave Quantum Computer

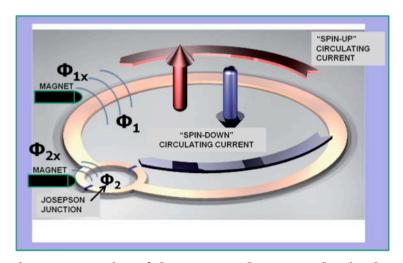

The basic building block of the DW2 quantum annealing chip is a superconducting flux qubit, (rf-SQUID flux qubit) as depicted in Figure 2. The simplified version consists of two superconducting loops having two Josephson junctions [9]. Each loop is subject to externally-biased magnetic fields ( $\Phi_{1x}$  and  $\Phi_{2x}$ ) that are used to control the properties of the qubit. The quantum states are associated with the quantized magnetic flux  $\Phi_1$ .

Figure 2. Schematic representation of the compound superconducting loops used to realize the qubits in the D-Wave processor

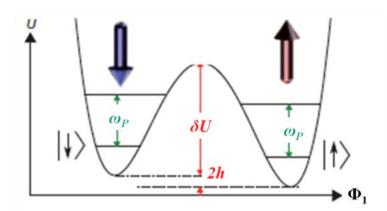

For low temperatures, it is a good approximation to only consider the two lowest states corresponding to flux pointing up and flux pointing down. The energy profile that describes the system is a double-well potential, represented in Figure 3. The bias fluxes  $\Phi_{1x}$  and  $\Phi_{2x}$  are used to adjust the height of the energy barrier  $\delta U$ , and the energy difference between the two states, 2h. The actual qubits in the quantum computing element chip have extra loops that are used to compensate for undesirable effects due to fabrication manufacturing variations and provide more uniformity in their properties.

Figure 3. Energy profile of a superconducting flux qubit

#### 2.1.2 Programming and Using the D-Wave Quantum Computer

Programming of the DW2 involves setting the values of the local magnetic fields, and the coupling coefficients for each super-conducting qubit, which determine the desired final (*Ising*)

Hamiltonian. The DW2 is housed in an integrated environment able to be programmed by either desktop computers connected directly to the DW2, or remotely via a local area network, or other remotely-accessed communication networks, to which the desktop computers are connected.

To program the DW2, a user needs to provide the chip with the values of J and h that satisfy the constraints discussed above. Casting a given problem into the Ising form and respecting the constraints on J and h is part of the "art" of programming DW2. For many discrete optimization problems there are known mappings to the Ising model, but those often result in matrices J with more connectivity than what is currently available on DW2. One way is to map such J into the chip by using certain qubits to simulate more connections, but the price paid is that these qubits are not available to encode the solution. There are also heuristic approaches that aim at approximating a given unconstrained J with another matrix J' that satisfies the constraints of the chip and has the same minimum of the energy function.

Programming of, and readout from the DW2 occurs through an application-programming interface consisting of function libraries that make calls to the optimization capability of the DW2. These libraries are available in Matlab and Python, and can be used to access the machine's functionalities directly from the programmer's code. These software tools, in conjunction with the machine's circuitry, translate the description of the *Ising* Hamiltonian into the time-dependent classical controlling signals that make the qubits evolve following the required adiabatic evolution. After the qubits are measured, the results are also available through a software interface.

#### 2.1.3 Counterexample guided abstraction refinement

One of the main computational bottlenecks in model checking is related to what is known as the "state space explosion": even for moderately sized systems, the state space needed to describe them is intractably large (a system with  $10^{100}$  states is not uncommon). Developing techniques to deal with this issue is central in model checking. One popular technique is based on the use of Binary Decision Diagrams, a very compact data structure that allows for a succinct description of the state space and the transition system [10]. Another approach is based on abstractions: a smaller system is constructed in such a way that properties proven true in the abstraction are guaranteed to be also true in the original system [11]. The abstraction can then be checked using regular model checking tools (like BDDs for example), which are computationally more efficient since they are applied to a much smaller system.

If an abstraction is not sufficient to prove a given formula, the model checking tool used on the abstraction must provide a counter-example (CE), a path in state-space that violates the formula. This CE can be *real* or *spurious*: a real CE can be mapped to an actual CE in the original (concrete) model, hence disproving the formula; a spurious CE is an artifact of the abstraction and "disappears" when mapped to the original model. To determine which one is the case, we can "simulate" the CE in the original system. This can be posed as finding a satisfying assignment for a Boolean formula. DW2 implements these Boolean *satisfiability* problems by fabricating an energy function that achieves a minimum, when all clauses are satisfied. If the formula is *not satisfiable*, the lowest energy configuration obtained with DW2 will represent an assignment of the Boolean variables that will not satisfy the formula. This can be efficiently checked from DW2's output.

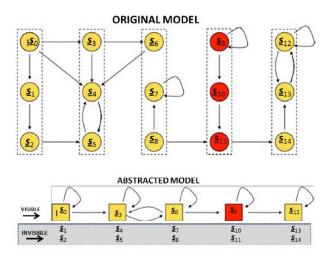

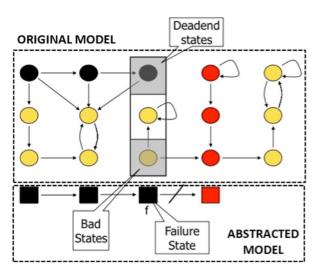

In order to determine if an abstract CE corresponds to an actual CE in the original system (and hence a proof that the property is not satisfied), we need to translate the sequence of transitions that form the abstract CE into a sequence of transitions in the original system. The central question that we need to ask is: given a transition in the abstract system does a corresponding transition exist in the original system? It should be remembered that in an existential abstraction, an abstract transition between two abstract states exists, even if only one pair of original states (each mapped to a different abstract state) has a transition (see Figure 4, where the transition between states  $s_3$  and  $s_6$  in the original system induces a transition between the second and third states of the abstraction).

For example, consider an abstract CE,  $\hat{T}$ , given by a sequence of abstract states  $\langle \hat{s_1}, ..., \hat{s_n} \rangle$ . Given an abstract state  $\hat{s}$ , the abstraction function h maps states in the original system into the abstract system. The set of states that are mapped into  $\hat{s}$  are the ones that satisfy  $h(s) = \hat{s}$ . If we denote by  $R(s_i, s_j)$  the characteristic function of the transitions in the original system (i.e.,  $R(s_i, s_j) = 1$  if and only if there is a transition between states  $s_i$  and  $s_j$ , and 0 otherwise), then a path  $\langle s_1, ..., s_n \rangle$  is a concrete representation of the abstract CE  $\hat{T}$ , if the Boolean formula

$$\Lambda_{i=1}^{n}(h(s_{i}) = \widehat{s}_{i}) \wedge \Lambda_{i=1}^{n-1} R(s_{i}, s_{i+1})$$

(4)

is satisfied, where the first AND operator assures that the states  $s_i$  are mapped into the corresponding abstract states  $\hat{s}_i$ , while the second AND operator assures that there exists a transition in the original system between the states  $s_i$  and  $s_{i+1}$ . We will show later that finding a satisfying assignment of a Boolean formula can be cast as a 0-1 Integer Linear Program, and this ILP can be mapped into QUBO form implemented by DW2.

#### 2.1.4 Refining the Abstraction

If the CE is spurious, the satisfiability problem presented above identifies an abstract state that causes the violation of the formula being checked. This is due to having clustered together "<u>dead end</u>" states (that do not provide a path to an error state) and "<u>bad</u>" states (that provide a path to an error state). We can illustrate this behavior with the following diagrams that represent a system and its abstraction (see Figure 4).

Figure 4. Example of abstracted model

Consider the set of states and their transitions depicted in the original model of Figure 4. Here,  $\underline{s}_0$  is the initial state, and the states colored red are error states. Consider a possible abstraction of this system in which all the states inside each dotted-lined rectangle are mapped to the same abstract state. The transition diagram for such an abstraction is given in the lower part of Figure 4. From these diagrams, we can see why a spurious CE may arise. In the original system, it is clear that if we start in the initial state  $\mathbf{I}$ , we will never reach the "error" states (red states in the diagram). However, by looking at the transition diagram for the abstraction, we can see that starting in the abstract initial state we may eventually reach an "error" state. This is easier to see in the diagram of Figure 5.

Figure 5. Spurious counter example

The states in black in Figure 5 represent a possible path that the system can take. Note that in the original system that path cannot reach any "error" states. The farthest the system can go is the "dead end" state. However, in the abstraction, the "dead end" state is mapped to the same abstract state as a "bad" state, i.e., a state that can eventually transition into an "error" state, so a spurious transition is created that causes the system to have a valid path from the initial state to an "error" state. In the diagram, we note as a "failure" state the abstract state that is causing a spurious counter-example to appear, because it maps together "dead end" and "bad" states. To refine the abstraction, these states need to be separated and assigned to different abstract states. Therefore, in order to construct viable abstractions, one must follow the steps outlined below:

- 1. **Minimal Separating Set** Generate an abstraction where "dead end" and "bad" states are clearly separated. This results in an ILP that the DW2 can solve as an *Ising* problem.

- 2. **Satisfiability** Regardless of the approach used to generate abstractions, any CE needs to be verified, if it is real or spurious. This invokes the processing of satisfiability, which is executed in DW2 as an *Ising* model.

The sections below discuss how these steps are formulated and mapped to the DW2 quantum annealer.

#### 2.1.5 Minimal Separating Set

This can be constructed by identifying which of the "invisible" variables should be made "visible" to distinguish "dead end" and "bad" states. The goal is to separate these two sets exactly (i.e., no mistakes allowed) using the smallest number of invisible variables possible, in order to keep the size of the refined abstraction from growing too much. For this, we use the following definitions, assuming that there are 2 sets of states  $S = (s_1, s_2, ..., s_m)$  and  $T = (t_1, t_2, ..., t_n)$  that need to be separated (S can represent the "dead-end" states and T can represent the "bad" states). Let T0 be the set of variables required to specify all states in the original system.

**Definition-1**: A set of variables  $U = (u_1, u_2, ..., u_k) \subseteq W$ , separates S from T if for each pair of states  $(s_i, t_i), s_i \in S$  and  $t_i \in T$ , there exists a variable  $u_r$  such that  $s_i(u_r) \neq t_i(u_r)$ .

**Definition-2**: Given 2 sets S and T per Definition-1, find the smallest set of variables  $U = (u_1, u_2, ...., u_k) \subseteq W$ , that separates S from T. The set U is called the *minimal separating set*.

We can assign a binary variable  $v_i$  to each variable  $u_i$ , that will represent whether that variable is included in the separating set or not: if  $u_i$  is in the separating set, then  $v_i = 1$ ; otherwise is zero (the corresponding variable is excluded). The conditions are that for each  $(s_i, t_j)$  pair at least one of the variables that distinguish between the two states must be selected. Thus, there is a total of mxn conditions. Under this formulation, the minimal separating set can be solved using integer linear programming in a conventional computer to attain an exact solution.

Minimize

$$\Sigma_{[j=1,...,k]} v_j$$

with each  $v_i = 0$  or 1 (5)

Subject to:  $(\forall s \in S) \ (\forall t \in T) \ \Sigma_{[i=1,...,k]} v_i \ge 1 \text{ for } s(u_i) \ne t(u_i)$

Assuming that S represents the "dead end" states and T the "bad" states, the objective function aims to minimize the count on the number of new variables we are including, while the

constraints express the fact that every pair of "dead end"-"bad" states has to be distinguished by at least one of the new variables we are including.

We refer now to the case that the sets S and T represent the "bad" and "dead-end" states denoted by  $S_B$  and  $S_D$ . The following lemma from formal methods apply:

<u>Lemma</u> – Let U be the set of variables separating the "dead-end",  $S_D$ , and "bad",  $S_B$ , states. Let an abstraction function h' correspond to the visible set V' of variables realizing the abstraction. Also, let V represent the entire set of the original visible variables; then the following applies: V' =  $V \cup U$ . The abstraction function h' maps  $S_D$  and  $S_B$  on to different states in the abstract model.

This lemma implies the following: 1) the number of visible variables have increased from |V| to |V'|=|V|+|U|; and 2) using this augmented set of visible variables the abstraction function will map  $S_B$  &  $S_D$  to different abstract states, which do need to be considered. As said above, the model checking tool will check if the property of interest is valid in the abstraction. If it is valid, then the procedure is over; if it is not and it generates a spurious CE, the process needs to be repeated until a set of visible variables is identified on which that property holds or a valid CE is found.

#### 3 METHODS, ASSUMPTIONS, AND PROCEDURES

# 3.1 Feasibility study of using DW2 for Bounded Model Checking and Binary Decision Diagrams

The analysis of the suitability of DW2 to address BMC problems and to implement BDD-based model checking approaches was a theoretical exercise, and no particular assumptions were required. We will present the details of the problem setup together with the results of this investigation in Section 4.1.

## 3.2 Benchmarking of DW2 performance on MAX-2-SAT against classical solver MaxWalkSAT

The main goal of this task was to benchmark the performance of the DW2 processor on a native problem, against a classical heuristic solver. The rational for this task was that benchmarking up to that point was performed against classical exact solvers, in particular AK-MAXSAT [12]. Since this solver provides a guarantee of optimality, it requires more resources (i.e., run time). The DW2 processor is a probabilistic solver (solution is provided with a finite probability and no optimality guarantee is given), and so it is not fair to compare it with exact solvers.

#### 3.2.1 MAX-2-SAT

The choice of MAX-2-SAT is based on the fact that this problem can be trivially written as an Ising problem that is native to the DW2 processor.

<u>Definition of MAX-2-SAT</u>: given a Boolean formula in conjunctive normal form with 2 literals per clause, find the maximum number of clauses that can be simultaneously satisfied.

The key point in implementing this problem using the DW2 processor is to notice that for each 2-literal clause, we can construct a Hamiltonian of Ising form whose ground state is composed by the satisfying assignments for the clause. For example, consider the 2-literal clause  $(x_i \lor x_j)$ . This clause is satisfied if any of the two variables is TRUE. To map this problem into an Ising form we will associate to each variable the state of a qubit, with  $x = \text{TRUE} \rightarrow |+1\rangle$  and  $x = \text{FALSE} \rightarrow |-1\rangle$ . Consider then the 2-qubit Hamiltonian

$$H = \frac{1}{4}(1 - \sigma_i - \sigma_j + \sigma_i \otimes \sigma_j)$$

(6)

where the  $\sigma_i$  is the Pauli operator associated with qubit i, and  $\{|+1\rangle, |-1\rangle\}$  are its corresponding eigenvectors. Table 1 shows the truth table of the 2-literal clause, and the energies of the associated states.

Table 1. Truth table for Boolean OR and energies of associated 2-qubit Hamiltonian

| Xi | X <sub>j</sub> | $x_i \vee x_j$ | $\sigma_i$ | $\sigma_j$ | Н |

|----|----------------|----------------|------------|------------|---|

| F  | F              | F              | -1         | -1         | 1 |

| F  | T              | T              | -1         | +1         | 0 |

| T  | F              | Т              | +1         | -1         | 0 |

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED

We can see that all satisfying assignments are associated with states of energy 0, while the only non-satisfying assignment corresponds to a state with energy 1. Hence, the ground state of the Hamiltonian H is composed exactly by all the satisfying assignments of the 2-literal clause. If any of the variables appear negated in the formula, we just need to flip the sign of the corresponding Pauli operator on the Hamiltonian.

If we have a conjunction of many clauses  $C_1 \land ... \land C_M$ , we just need to add the corresponding Hamiltonians  $H = H_1 + ... + H_M$ . For any possible truth assignment to the Boolean variables, the energy of the state will be increased by 1 for every unsatisfied clause. Then the energy of the ground state of H will be the *minimal* number of unsatisfied clauses, from which we can trivially infer the *maximum* number of satisfied clauses, i.e., the objective of the MAX-2-SAT problem. It is then clear that we can look at MAX-2-SAT as a native problem to the DW2 processor. Even though the decision problem 2-SAT is known to have a polynomial-time solution, the optimization problem MAX-2-SAT is NP-hard (i.e., a polynomial-time algorithm for it would imply the existence of a polynomial-time algorithm for all problems in NP).

#### 3.2.2 MaxWalkSAT

We chose the MaxWalkSAT [13] solver as the classical algorithm for the benchmarking. This solver applies heuristic methods to provide an approximate solution to a MAX-2-SAT instance. Since it is not required to provide any guarantees of optimality (as exact solvers do) it can run much faster on many instances. We considered that this provided a better comparison between classical solvers and the DW2 processor.

MaxWalkSAT is a variant of WalkSAT, a heuristic SAT solver. In its more general form, MaxWalkSAT solves the weighted SAT problem, in which each clause is given a weight and the goal is to maximize the total weight of all simultaneously satisfied clauses. In our case, we set the weights to 1. The algorithm for WalkSAT starts with a random truth assignment for all the variables, then randomly selects an unsatisfied clause and a variable within that clause is flipped. This variable can be chosen either at random, or as the variable whose flipping minimizes the number of already satisfied clauses becoming unsatisfied. So in a sense, it is a mixture of deterministic local search and random jumps.

#### 3.2.3 Instance ensemble

In order to implement this comparison we generated MAX-2-SAT instances that were native to the architecture of the DW2 processor. We generated problems with N variables, for N = 20,40,...,500. The number of clauses was chosen to be 2N, since it is known that this ratio of clauses to variables generates instances that are typically hard to solve.

The ensemble was composed of 1000 instances for each value of N. The instances were constructed in the following way. For each value of N, we chose N qubits that formed a connected subset of the processor (to avoid assigning variables to qubits that were not connected to other qubits of the set). Then we randomly picked M=2N of the available couplers associated with the set of qubits to represent the 2-literal clauses. Finally, for each clause we randomly (probability ½) negated the literals. This construction assured us that all clauses were distinct, and hence the total number of clauses was indeed 2N.

#### 3.2.4 Benchmarking strategy

To compare the performance of the classical and quantum solvers we implemented the following strategy. First, by using the exact solver AK-MAXSAT, we found the optimal value of the objective function for every instance in the ensemble. This value was later used to estimate the probability of success of each solver on each given instance.

Quantum solver (DW2): we ran each instance a thousand times, using an annealing cycle of 20 microseconds. We compared the value of the objective obtained in each run with the known optimal value, and used this information to compute the probability of success for each given instance. Then we used this information to compute the expected number of repetitions (or runs) needed to obtain the optimal value at least once with at least 99% probability. This number of repetitions times the annealing time used (20 microseconds) was the performance figure we used for each instance. We then averaged this value over all instances with the same number of variables N, and used it to compare with the classical solver.

Classical solver (MaxWalkSAT): the classical algorithm MaxWalkSAT requires another input parameter called the "cutoff", that gives an upper limit on the number of iterations performed before stopping. Clearly, if the cutoff is small, the algorithm will be faster but we may not find the optimal solution. On the other hand if the cutoff is very large, the algorithm will take more time but will have a better chance of finding the optimal solution. There is then a tradeoff between the value of the cutoff and the time it would take the algorithm to find the optimal solution with probability at least 99%. We ran every instance with different values of the cutoff in order to find a value that will reach the optimal solution with 99% probability in the fastest run time. We then averaged these values over all of the instances with the same number of variables N. All the instances were run on a Mac Pro with a 2.6 GHZ processor and 48Gb of RAM.

#### 3.3 Development of heuristic embedding algorithm

The main goal of this task was to develop a tool that would allow us to embed problems that do not match the processor's connectivity. As discussed in Section 2, the DW2 processor has a very particular connectivity graph called the Chimera graph that is the result of design compromises between scalability and algorithmic power. The connectivity graph is sparse, and each is qubit connected to at most 6 other qubits.

This design feature has an impact on the type of problems that can be embedded in the processor. A general Ising model will have an underlying graph of couplings, and if this graph is not a subset of the Chimera graph we need to implement alternative ways of embedding the problem. Even if a given instance was a subgraph of the Chimera graph, finding the appropriate mapping is an instance of Subgraph Isomorphism, another combinatorial optimization problem that may be as hard as the original Ising instance. Hence, with the current design of the processor we have no choice but to develop alternative methods to embed problems. It is important to point out that this issue is not particular to the D-Wave processors. For any implementation of adiabatic quantum optimization, the connectivity of the processor will be associated with some physical interaction between qubits. These interactions tend to be local and thus require that the qubits are close to each other. This will put a limit to the number of interactions a given qubit can represent, since the number of local neighbors in any reasonable architecture will be limited and much smaller than the total number of qubits. Hence the problem of embedding is central to the adiabatic quantum optimization approach and not just a D-Wave issue.

Since most Ising problems of interest will not fit directly into the Chimera graph, it is necessary to develop techniques to go around this issue. We have already mentioned that an exact embedding requires solving a hard problem and does not seem to be a scalable solution. Hence, we need to apply some kind of *approximate embedding*. This requires discarding some of the information (i.e., the couplings) that defines the problem in order to generate a related Ising problem that can be fit into the Chimera graph. This approach has been used by Google and D-Wave in an image recognition application [14], where they reduced the training of a strong classifier to a QUBO problem. Their approximate embedding scheme followed a greedy algorithm, that aimed at keeping the largest couplings (in absolute value) with the rational that these couplers will be more important in determining the structure of the best solutions. It is important to note that this step requires a certain preprocessing of the input instance that increases the computational resources required. Also, there are no theoretical results that would guide this process or give any guarantees on the quality of the solutions obtained.

#### 3.3.1 Iterative heuristic embedding

In order to address the drawbacks of the approximate embedding method, we considered a different approach that aims at taking advantage of the sampling capabilities of the DW2 processor. The idea comes from an approach to optimization problems known as "Probability collectives" [15]. The main idea is to replace an optimization problem with a sampling problem. Given an objective function over binary strings G(x), one approach to find its minimum will be to sample from its Gibbs distribution, which is given by

$$P(\mathbf{x}) = \exp(-\beta * G(\mathbf{x})) / Z \tag{7}$$

where beta is the inverse temperature, and Z is the partition function, which is defined as  $Z = \Sigma \exp(-\beta * G(\mathbf{x}))$ , where the sum runs over all binary strings. It is clear that this distribution is biased towards configurations that have a small value of  $G(\mathbf{x})$  due to the exponential factor. So if we had access to a machine or algorithm that generated samples following this distribution, with high probability we would obtain the minimum configuration.

The key point is to consider the DW2 processor as a *parameterized sampler*, where the parameters are the local fields and the couplings  $(h_i, J_{ij})$ , and the output is a distribution over the set of binary strings. The goal is then to find a set of parameters that produce an output distribution that is "close" to the Gibbs distribution associated with the objective function  $G(\mathbf{x})$ . This sets up an iterative procedure:

- 1. Initialize the set of parameters  $(h_i, J_{ii})$ .

- 2. Sample the output of the DW2 processor using these parameters.

- 3. Compute measure of "closeness" between this output distribution and  $P(\mathbf{x})$ .

- 4. Update the parameters  $(h_i, J_{ij})$  in order to decrease the measure of "closeness".

- 5. Go back to Step 2.

This process continues until a termination criterion is reached. Every time we sample the processor, we can compute the value of the objective function G on all samples and keep track of the one that gives us the minimum.

As a measure of "closeness" we chose the relative entropy (or Kullback-Leibler divergence) between the two distributions [16]. This measure has the property of being non-negative, and vanishing if and only if the two distributions are identical. If we call  $Q(\mathbf{x}; h_i J_{ij})$  the output distribution of the quantum processor (that depends on the parameters  $(h_i J_{ij})$ ), the relative entropy between Q and P is defined by

$$D(Q||P) = \sum Q(\mathbf{x}; h_i, J_{ii}) \log \left( Q(\mathbf{x}; h_i, J_{ii}) / P(\mathbf{x}) \right)$$

(8)

where the sum is taken over all binary strings. Our goal then is to find the values of the parameters  $(h_i, J_{ij})$  that minimize the relative entropy. This is an optimization problem of a continuous function over a set of continuous variables, so we chose a gradient descent method.

In order to compute the components of the gradient of the relative entropy, we would need to know the functional form of  $Q(\mathbf{x}; h_i, J_{ij})$ . However, this functional form is not available to us, and we can only sample from the distribution  $Q(\mathbf{x}; h_i, J_{ij})$ . To move forward, we made the assumption that  $Q(\mathbf{x}; h_i, J_{ij})$  was the Gibbs distribution associated with the Ising energy, that is

$$Q(\mathbf{x}; h_i, J_{ij}) = \exp(-\beta E_{\text{Ising}}(\mathbf{x}; h_i, J_{ij})) / Z_Q$$

(9)

where  $Z_Q(h_iJ_{ij}) = \Sigma$  exp(- $\beta$ \* $E_{Ising}$  ( $\mathbf{x}$ ;  $h_iJ_{ij}$ )) is a normalization constant that depends on the parameters  $(h_iJ_{ij})$ , and the sum is over all binary strings. By making this assumption we can explicitly compute the components of the gradient and obtain

$$\nabla_{J} = -\beta \left\{ \left\langle (2x_{i} - 1)(2x_{j} - 1) \log(\mathbf{Q}(\mathbf{x}; h_{i}, J_{ij}) / \exp(-\beta * \mathbf{G}(\mathbf{x}))) \right\rangle - \left\langle (2x_{i} - 1)(2x_{j} - 1) \right\rangle \right.$$

$$\left\langle \log(\mathbf{Q}(\mathbf{x}; h_{i}, J_{ij}) / \exp(-\beta * \mathbf{G}(\mathbf{x}))) \right\rangle \right\}$$

$$\nabla_{h} = -\beta \left\{ \left\langle (2x_{i} - I) \log(\mathbf{Q}(\mathbf{x}; h_{i}, J_{ij}) / \exp(-\beta * \mathbf{G}(\mathbf{x}))) \right\rangle - \left\langle (2x_{i} - I) \right\rangle \left\langle \log(\mathbf{Q}(\mathbf{x}; h_{i}, J_{ij}) / \exp(-\beta * \mathbf{G}(\mathbf{x}))) \right\rangle \right\}$$

$$(10)$$

The expectation values that appear in the gradient are taken with respect to the distribution  $\exp(-\beta E_{Ising}(\mathbf{x}; h_i, J_{ij})) / Z_Q$ , i.e., the Gibbs distribution associated with the Ising model implemented on the processor. Even though we know it's functional form, this expression is hard to compute because it requires summing over all binary strings to obtain the normalization constant  $Z_Q$ , and this sum has exponentially many terms, making it impractical for large problems. In order to get around this obstacle, we will make another approximation and use the sample averages to compute the expected values. The sample averages can be obtained by evaluating the expressions on the samples produced by the processor. Since we will only generate a fixed number of samples, this computation can be done efficiently.

Note that the algorithm makes two approximations: first, it assumes that the output distribution from the DW2 processor is a Gibbs distribution in order to compute the gradient of the relative entropy; and second, it replaces the expected values over this Gibbs distribution by the sample averages.

#### 3.4 Integration of CEGAR approach with DW2

The CEGAR algorithm is a means of tackling the state space explosions that often arise in model-checking. In CEGAR, one initially computes an *abstraction* of the original model that can be model-checked more easily than the full model. This must be an abstraction that is *conservative*, in a sense we describe below. One then checks the abstracted model to see if the property holds in the abstracted model. If it holds, we are done; the system passes the test. Here is where the conservative nature of the abstraction is critical: it must be the case that if the system passes the check the property is, in fact, safe (the check must be *sound*); however, CEGAR admits false positives (where the check fails, although the system is safe – the check is not *complete*). Typically the CEGAR algorithm is applied to reachability problems, where the safety property states that the system must not reach some undesirable state. A conservative abstraction is used which increases the set of reachable states, so that the check will be sound.

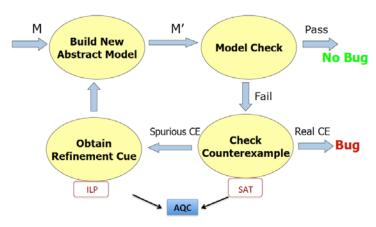

If we find an abstract counterexample, we commence the part of the process that gives the algorithm its name. First we must *check* to see if the counterexample is sound. We do this by "replaying" the counterexample in the full model, instead of the abstraction. If the counterexample is found to be sound, we are done: the system is unsafe, and must be corrected. On the other hand, if the counterexample is unsound, we must *refine* the abstraction and repeat the process. A simple diagram of the CEGAR procedure is presented in Figure 6. The abstraction refinement is counter-example guided in the sense that we find a place in the counter-example trace where the abstract counterexample cannot be followed. In this case, what must have happened is that the abstract counter-example progresses from abstract state  $as_i$  to  $as_{i+1}$  but there is no way to progress from a corresponding concrete state  $h^{-1}(as_i)$  to  $h^{-1}(as_{i+1})$  ( $h^{-1}$  is the inverse of the abstraction, so  $h^{-1}(as_i)$  is the set of concrete states that correspond to the abstract state  $as_i$ .) To refine the abstract state, we find the set of concrete states that satisfy the description of abstract state i,  $h^{-1}(as_i)$ , and the set of concrete states from which  $h^{-1}(as_{i+1})$  is reachable, and refine by adding state features that separate these two sets. The first set of states is called the "dead end states," and the second set is called the "bad states."

Figure 6. CEGAR loop

In the QCHECK project, we experimented with applying the D-wave quantum computer to two steps of the CEGAR process:

- 1. Checking the soundness of the abstract counter-example and

- 2. Finding an (approximately) optimal refinement to separate the dead-end from the bad states.

The first step involved solving a SAT problem that encoded the existence of an actual counter example associated with the abstract counterexample. The second involved solving an ILP in order to find the smallest set of hidden variables that needed to be made visible in order to get rid of the spurious counterexample. These two problems (SAT and ILP) are special cases of combinatorial optimization problems, and can both be cast as QUBO problems that can be solved with DW2. Actually, SAT can be cast as a particular instance of ILP as we show below.

#### 3.4.1 Converting SAT to ILP

In a Boolean satisfiability problem, we have a set of Boolean variables  $\{x_i\}$ , and a set of clauses formed by combining a number of those variables and their negations with the logic operator OR. For example, a clause can take the form

$$C = x_1 \vee x_2 \vee \overline{x_3} \tag{11}$$