# MULTI-CORE PROGRAMMING DESIGN PATTERNS: STREAM PROCESSING ALGORITHMS FOR DYNAMIC SCENE PERCEPTIONS

UNIVERSITY OF MISSOURI

MAY 2014

FINAL TECHNICAL REPORT

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

STINFO COPY

# AIR FORCE RESEARCH LABORATORY INFORMATION DIRECTORATE

### NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report is the result of contracted fundamental research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated 10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09. This report is available to the general public, including foreign nationals. Copies may be obtained from the Defense Technical Information Center (DTIC) (http://www.dtic.mil).

AFRL-RI-RS-TR-2014-142 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH ASSIGNED DISTRIBUTION STATEMENT.

FOR THE DIRECTOR:

/S/ STANLEY LIS Work Unit Manager /S/

MARK H. LINDERMAN

Technical Advisor, Computing & Communications Division

Information Directorate

This report is published in the interest of scientific and technical information exchange, and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

# REPORT DOCUMENTATION PAGE

U

U

U

Form Approved OMB No. 0704-0188

The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number.

PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YYYY)          | 2. REP   | PORT TYPE         |                  |             | 3. DATES COVERED (From - To)             |  |  |  |  |  |

|--------------------------------------|----------|-------------------|------------------|-------------|------------------------------------------|--|--|--|--|--|

| MAY 2014 FINAL TECHNICAL REPO        |          |                   |                  | RT          | NOV 2010 – NOV 2013                      |  |  |  |  |  |

| 4. TITLE AND SUBTITLE                |          |                   |                  |             | 5a. CONTRACT NUMBER                      |  |  |  |  |  |

|                                      |          |                   |                  |             | FA8750-11-1-0073                         |  |  |  |  |  |

| MULTI-CORE PROGRAMMING I             |          |                   |                  | 5h GRA      | 5b. GRANT NUMBER                         |  |  |  |  |  |

| PROCESSING ALGORITHMS FO             | OR DY    | NAMIC SCENE       | PERCEPTION       | Job. Olta   | N/A                                      |  |  |  |  |  |

|                                      |          |                   |                  |             |                                          |  |  |  |  |  |

|                                      |          |                   |                  | 5c. PRO     | GRAM ELEMENT NUMBER                      |  |  |  |  |  |

|                                      |          |                   |                  |             | 62788F                                   |  |  |  |  |  |

| 6. AUTHOR(S)                         |          |                   |                  | 5d. PRO     | JECT NUMBER                              |  |  |  |  |  |

|                                      |          |                   |                  |             | T2MC                                     |  |  |  |  |  |

| Kannappan Palaniappan                |          |                   |                  | Fo TACI     | Z NUMPED                                 |  |  |  |  |  |

|                                      |          |                   |                  | Se. I ASI   | K NUMBER<br>MI                           |  |  |  |  |  |

|                                      |          |                   |                  |             | IVII                                     |  |  |  |  |  |

|                                      |          |                   |                  | 5f. WOR     | K UNIT NUMBER                            |  |  |  |  |  |

|                                      |          |                   |                  |             | SS                                       |  |  |  |  |  |

| 7. PERFORMING ORGANIZATION NAM       | E(S) AN  | D ADDRESS(ES)     |                  |             | 8. PERFORMING ORGANIZATION               |  |  |  |  |  |

| University of Missouri               | _(-, , , |                   |                  |             | REPORT NUMBER                            |  |  |  |  |  |

| 316 University Hall                  |          |                   |                  |             |                                          |  |  |  |  |  |

| Columbia, MÓ 65211-3020              |          |                   |                  |             |                                          |  |  |  |  |  |

| ·                                    |          |                   |                  |             |                                          |  |  |  |  |  |

| 9. SPONSORING/MONITORING AGENC       | Y NAME   | E(S) AND ADDRESS  | S(ES)            |             | 10. SPONSOR/MONITOR'S ACRONYM(S)         |  |  |  |  |  |

|                                      |          | -(0,1             | (==)             |             | , ,                                      |  |  |  |  |  |

| Air Force Research Laboratory/RI     | ITB      |                   |                  |             | AFRL/RI                                  |  |  |  |  |  |

| 525 Brooks Road                      |          |                   |                  |             | 11. SPONSOR/MONITOR'S REPORT NUMBER      |  |  |  |  |  |

| Rome NY 13441-4505                   |          |                   |                  |             |                                          |  |  |  |  |  |

|                                      |          |                   |                  |             | AFRL-RI-RS-TR-2014-142                   |  |  |  |  |  |

| 12. DISTRIBUTION AVAILABILITY STAT   |          |                   | roport is the re | ocult of o  | ontracted fundamental research deemed    |  |  |  |  |  |

|                                      |          |                   |                  |             | ontracted fundamental research deemed    |  |  |  |  |  |

| AFRL/CA policy clarification mem     |          |                   |                  | I SAF/AQ    | R memorandum dated 10 Dec 08 and         |  |  |  |  |  |

| , ,                                  | oranuc   | uni dated 16 Jan  | 09.              |             |                                          |  |  |  |  |  |

| 13. SUPPLEMENTARY NOTES              |          |                   |                  |             |                                          |  |  |  |  |  |

| 14. ABSTRACT                         |          |                   |                  |             |                                          |  |  |  |  |  |

|                                      | lidated  | l and henchmark   | ed a scalable r  | arallel im  | plementations of the integral histogram  |  |  |  |  |  |

|                                      |          |                   |                  |             | bject searching, motion analysis and     |  |  |  |  |  |

|                                      |          |                   |                  |             | sing CUDA optimizations for many core    |  |  |  |  |  |

|                                      |          |                   |                  |             | using the StarSs programming model in    |  |  |  |  |  |

|                                      |          |                   |                  |             | luding Cell/B.E., GPU and SMP. The       |  |  |  |  |  |

|                                      |          |                   |                  |             | 6 bins for a 640x480 image reaches 160   |  |  |  |  |  |

|                                      |          |                   |                  |             | ost 200 fr/sec but critically depends on |  |  |  |  |  |

|                                      |          |                   |                  |             | aster than the sequential CPU version    |  |  |  |  |  |

|                                      |          |                   |                  |             | reaching 194 fr/sec. The implemented     |  |  |  |  |  |

| code has been delivered to AFRL      |          |                   |                  |             | ,                                        |  |  |  |  |  |

| 15. SUBJECT TERMS                    |          | •                 |                  |             |                                          |  |  |  |  |  |

| parallel multicore algorithms, integ | gral his | stogram, compute  | er vision, graph | ics proce   | essing unit (GPU), IBM Cell Broadband    |  |  |  |  |  |

| Engine, StarSs                       |          |                   |                  |             |                                          |  |  |  |  |  |

|                                      |          |                   |                  |             |                                          |  |  |  |  |  |

| 16. SECURITY CLASSIFICATION OF:      |          | 17. LIMITATION OF |                  |             | OF RESPONSIBLE PERSON                    |  |  |  |  |  |

|                                      |          | ABSTRACT          | OF PAGES         |             | NLEY LIS                                 |  |  |  |  |  |

| a. REPORT b. ABSTRACT c. THIS F      | PAGE     |                   | 41               | 19b. TELEPI | HONE NUMBER (Include area code)          |  |  |  |  |  |

41

N/A

UU

# Contents

| 1 | Sun                                                    | nmary                                                                         | 1  |  |  |  |  |  |  |  |  |  |

|---|--------------------------------------------------------|-------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

| 2 | Inti                                                   | roduction and Architecture Background                                         | 2  |  |  |  |  |  |  |  |  |  |

|   | 2.1                                                    | Multicore Programming Design Patterns                                         | 2  |  |  |  |  |  |  |  |  |  |

|   | 2.2                                                    | Dynamic Scene Analysis Using Integral Histograms                              | 3  |  |  |  |  |  |  |  |  |  |

|   | 2.3                                                    | Integral Histogram Using Star Superscalar (StarSs) for Parallel Architectures | 4  |  |  |  |  |  |  |  |  |  |

|   | 2.4                                                    | GPU Architecture Consideration                                                | 5  |  |  |  |  |  |  |  |  |  |

| 3 | Me                                                     | Iethods, Assumptions and Procedures                                           |    |  |  |  |  |  |  |  |  |  |

|   | Integral Histogram Computation for Vision Applications | 6                                                                             |    |  |  |  |  |  |  |  |  |  |

|   | 3.2                                                    | Parallel Integral Histogram in StarSs                                         | 8  |  |  |  |  |  |  |  |  |  |

|   | 3.3                                                    | Reference Implementation on the Cell/B.E                                      | 12 |  |  |  |  |  |  |  |  |  |

|   | 3.4                                                    | GPU Kernel Optimization for Integral Histogram                                | 15 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 3.4.1 GPU Aware Data Structure Design                                         | 15 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 3.4.2 GPU Parallelization Using Parallel Prefix-Sum (Exclusive Scan)          | 15 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 3.4.3 Parallel Prefix Sum Operation on the GPU                                | 16 |  |  |  |  |  |  |  |  |  |

|   | 3.5                                                    | GPU-based Transpose Kernel                                                    | 17 |  |  |  |  |  |  |  |  |  |

|   | 3.6                                                    | Data Structure and Implementation Strategy                                    | 17 |  |  |  |  |  |  |  |  |  |

| 4 | Res                                                    | sults and Discussion                                                          | 19 |  |  |  |  |  |  |  |  |  |

|   | 4.1                                                    | Experimental Results for Integral Histograms Using StarSs                     | 19 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 4.1.1 CellSs - StarSs for Cell/B.E                                            | 19 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 4.1.2 Cell/B.E. Intrinsics                                                    | 21 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 4.1.3 StarSs for SMP                                                          | 22 |  |  |  |  |  |  |  |  |  |

|   |                                                        | 4.1.4 StarSs for GPUs                                                         | 22 |  |  |  |  |  |  |  |  |  |

|   | 4.2                                                    | Summary for StarSs Integral Histogram                                         | 23 |  |  |  |  |  |  |  |  |  |

|   | 4.3                                                    | Experimental Results for Integral Histograms Using GPUs                       | 26 |  |  |  |  |  |  |  |  |  |

|   | 4.4                                                    | Summary for GPU Integral Histogram                                            | 27 |  |  |  |  |  |  |  |  |  |

| 5 | Cor                                                    | nclusions                                                                     | 29 |  |  |  |  |  |  |  |  |  |

| 6 | Ref                                                    | ferences                                                                      | 31 |  |  |  |  |  |  |  |  |  |

| 7 | List                                                   | t of Symbols, Abbreviations and Acronyms                                      | 34 |  |  |  |  |  |  |  |  |  |

# List of Figures

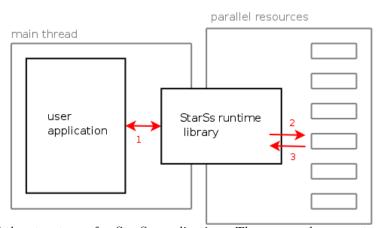

| 1  | Overview of the structure of a StarSs application. The user code generates tasks according to the sequential program (1), the runtime records the tasks into a TDG, schedules tasks to resources (2) and removes finished tasks from the TDG (3)                                                                                                                                                                                                |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

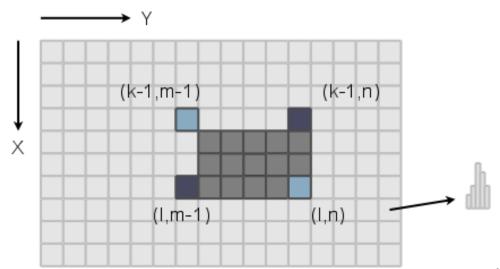

| 2  | Intersection or computation of the histogram for the region in grey, defined by the pixels $\{(k, m), (k, n), (l, m), (l, n)   k < l, m < n\}$ .                                                                                                                                                                                                                                                                                                |

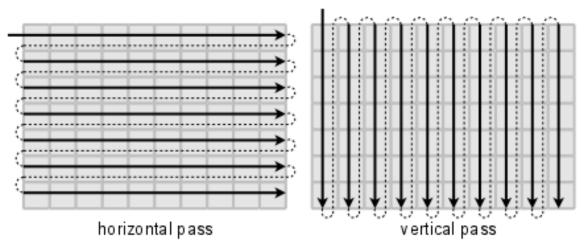

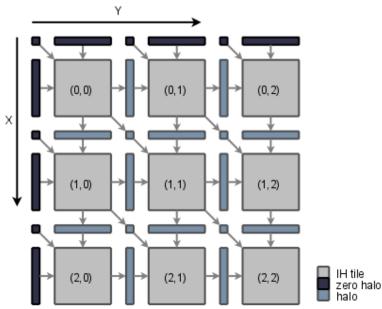

| 3  | The two passes for the cross-weave scan                                                                                                                                                                                                                                                                                                                                                                                                         |

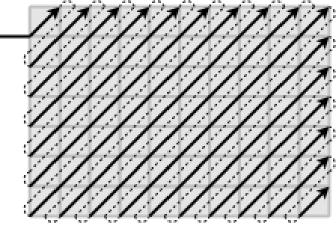

| 4  | The wavefront scan                                                                                                                                                                                                                                                                                                                                                                                                                              |

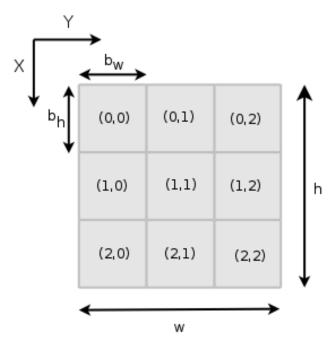

| 5  | Block data layout for a $w \times h$ image and integral histogram. Each tile contains $b_w \times b_h$ pixels or histograms.                                                                                                                                                                                                                                                                                                                    |

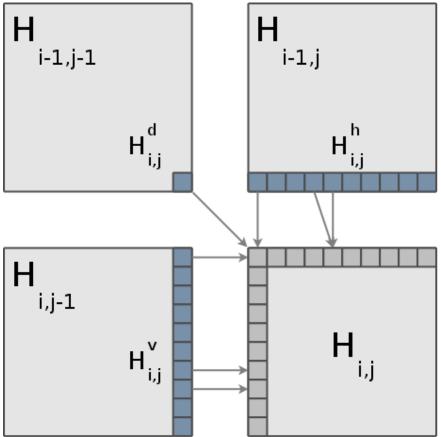

| 6  | Inter-block dependencies for block $H_{i,j}$ with halos for propagation between tiles. The arrows specify the inter-block dependencies for some selected histograms on the borders of $H_{i,j}$ 10                                                                                                                                                                                                                                              |

| 7  | Block data layout for the integral histogram. Each block contains $b_w \times b_h$ histograms. Block borders are duplicated in the halos and serve to pass histograms to the neighboring blocks 11                                                                                                                                                                                                                                              |

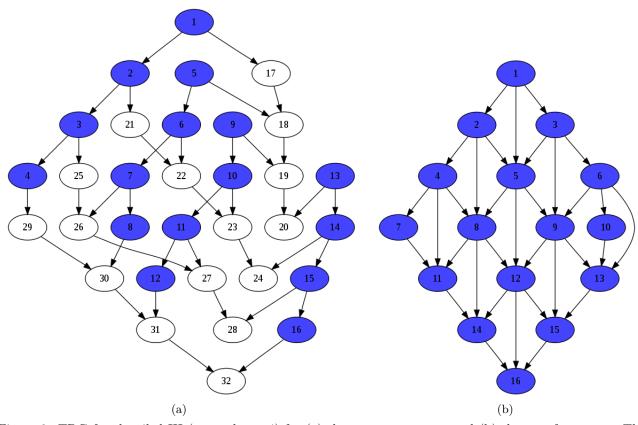

| 8  | TDG for the tiled IH ( $w_B = h_B = 4$ ) for (a) the cross-weave scan and (b) the wavefront scan. The tasks are numbered according to program order, which is identical to the scan order in our implementation in StarSs. The color of a node represents the task type                                                                                                                                                                         |

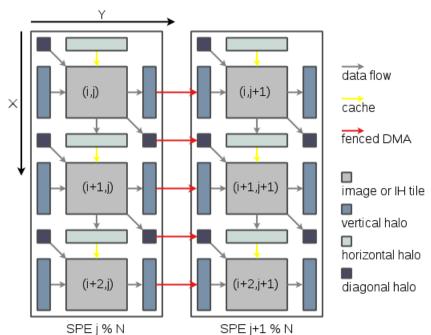

| 9  | Schedule and data flow for the reference implementation of the wavefront scan on the Cell/B.E 13                                                                                                                                                                                                                                                                                                                                                |

| 10 | (a) Tight lock-step between SPEs $n$ and $n+1$ due to the presence of one output buffer for the produced halos. (b) The synchronization between the SPEs becomes less stringent by providing two output buffers. As a result the processing of the four blocks speeds up                                                                                                                                                                        |

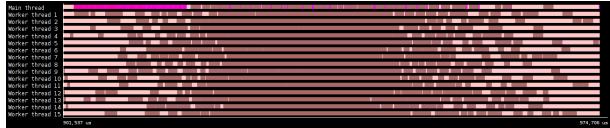

| 11 | Lack of potentially parallel tasks at the beginning and the end of the wavefront scan on SMP. The horizontal axis represents execution time and an entry on the vertical axis corresponds to a thread. The dark phases mark task execution whereas the threads idle during the lighter phases. In this Paraver trace we clearly distinguish a computation-intensive middle part centered between two regions where the threads are less active. |

| 12 | Integral histogram tensor represented as 3-D array data structure (left), and equivalent 1-D array mapping (right)                                                                                                                                                                                                                                                                                                                              |

| 13 | Parallel prefix sum operation, commonly known as exclusive scan or prescan. <sup>1</sup> Top: Up-sweep or reduce phase applied to an 8-element array. Bot: Down sweep phase                                                                                                                                                                                                                                                                     |

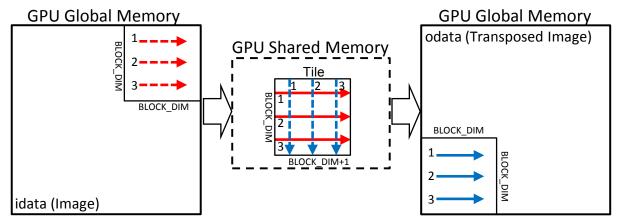

| 14 | Data flow between GPU global memory and shared memory while computing the coalesced transpose kernel; stage 1 in red, stage 2 blue, reads are dashed lines, writes are solid lines                                                                                                                                                                                                                                                              |

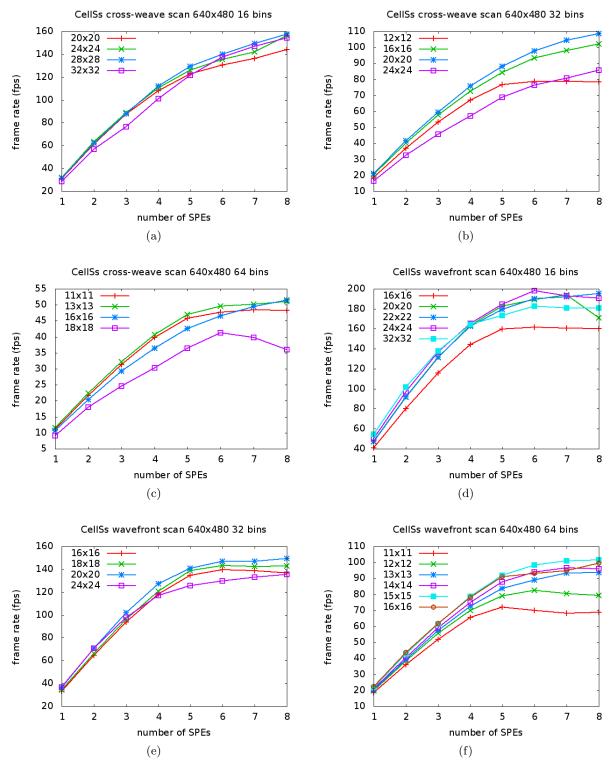

| 15 | Performance of the cross-weave (a,b,c,d) and wavefront scan (e,f,g,h) in CellSs on an 640x480 image for different block sizes and different numbers of bins                                                                                                                                                                                                                                                                                     |

| 16 | Speedup for the wavefront scan for 32 bins and different block sizes. One kernel has been vectorized ("v"), the other not ("nv")                                                                                                                                                                                                                                                                                                                |

| 17 | Performance of the cross-weave (a) and wavefront scan (b) on SMP for a 640x480 image for different block sizes and 64 bins                                                                                                                                                                                                                                                                                                                      |

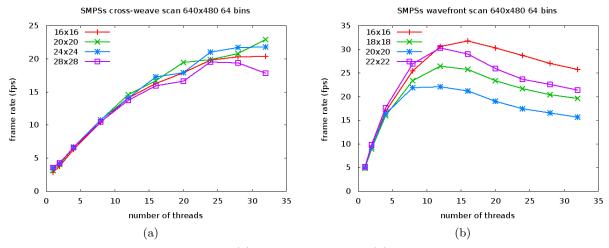

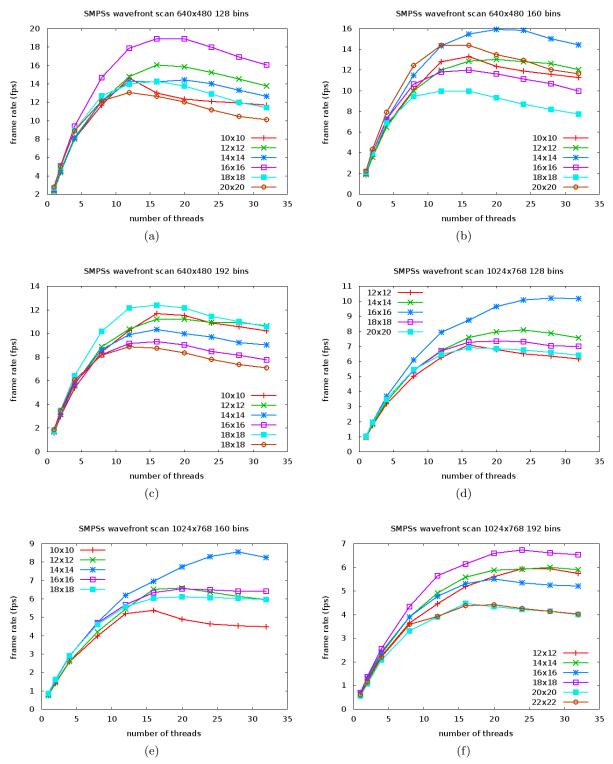

| 18 | Performance of the wavefront scan on SMP for a $640 \times 480$ image (top row) and a $1024 \times 768$ image for different block sizes and $128,160$ and $192$ bins                                                                                                                                                                                                                                                                            |

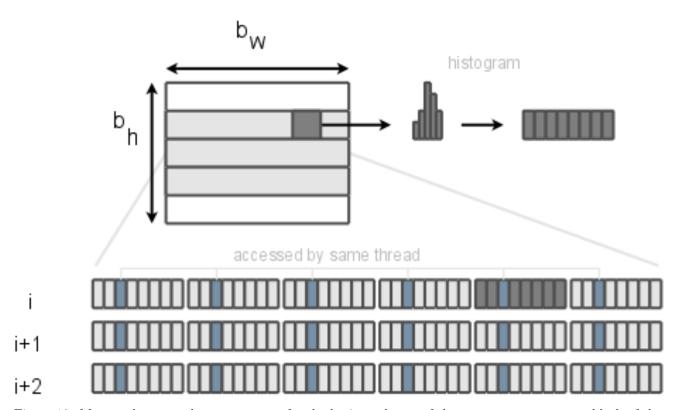

| 19 | Memory layout and access pattern for the horizontal pass of the cross-weave scan on a block of the integral histogram. The block contains $b_w \times b_h$ histograms or $b_w \times b_h \times b_c$ individual bins. Each thread updates a single bin in one or more rows                                                                                                                                                                      |

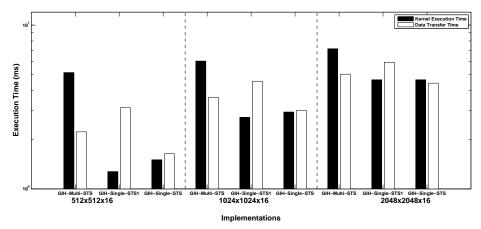

| 20 | Kernel execution time versus data transfer time for different image sizes                                                                                                                                                                                                                                                                                                                                                                       |

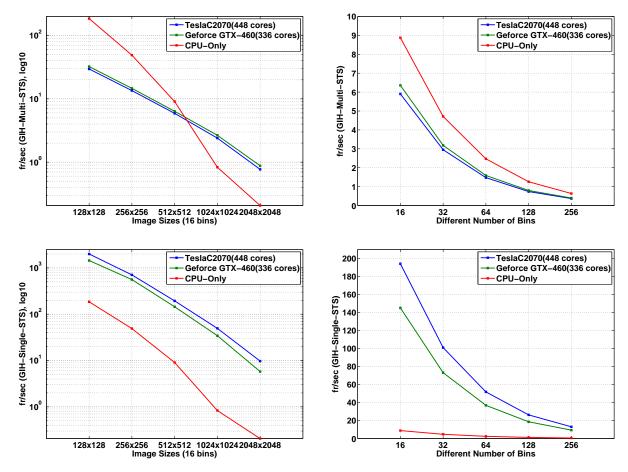

| 21 | Frame rate of GIH-Multi-STS, GIH-Single-STS and CPU-only integral histogram implementations: (UL) GIH-Multi-STS frame rate for different image sizes, (UR) GIH-Multi-STS frame rate for different number of bins, (LL) GIH-Single-STS frame rate for different image sizes, (LR) GIH-Single-STS frame rate for different number of bins for 512x512 image size                                                                          | 27 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

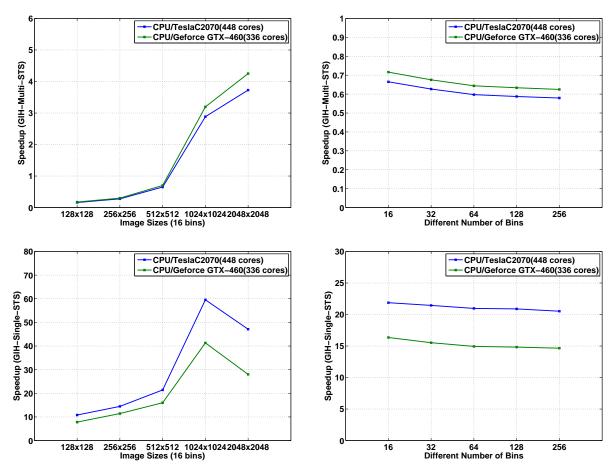

| 22 | Speedup of the two GPU designs over CPU on two NVIDA graphic cards: (UL) Speedup of GIH-Multi-STS (with respect to CPU-only) with different image sizes, (UR) Speedup of GIH-Multi-STS with varying number of bins, (LL) Speedup of GIH-Single-STS for different image sizes, (LR) Speedup of GIH-Single-STS with varying number of bins for 512x512 image size                                                                         | 28 |

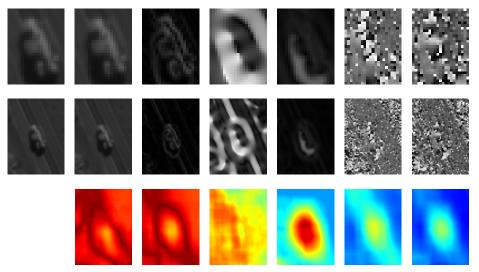

| 23 | Top row shows the car template and associated raw target features for intensity, gradient magnitude, Hessian shape index, normalized curvature index, Hessian eigenvector orientations, and oriented gradient angles. Row 2 shows the predicted search window and associated raw features. Row 3 shows the corresponding likelihood maps combining target template with the associated search window features using integral histogram. | 29 |

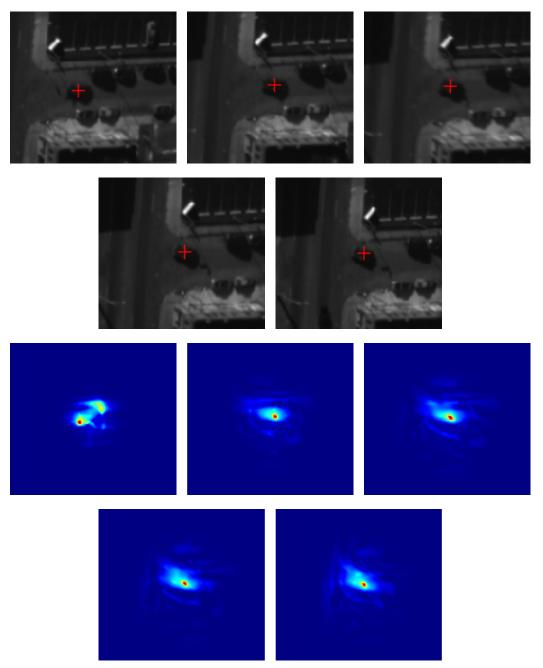

| 24 | LOFT tracking results are shown for the first five frames for car C4_1_0 from CLIF aerial wide-area motion imagery. <sup>2</sup> Top row shows the tracked car locations and the bottom row shows the fused likelihood maps used by LOFT <sup>3</sup> to determine the best target location in each corresponding frame                                                                                                                 | 30 |

# List of Tables

| 1 | Comparison between IH in CellSs (Section 3.2), using the Cell SDK and LS-to-LS transfers (Section                                |    |

|---|----------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.3) and using the Cell SDK with LS-to-memory transfers. Development time and code size are                                      |    |

|   | normalized to the CellSs result. Performance is reported on a $640 \times 480$ -image for $16,32$ and $64$                       |    |

|   | bins                                                                                                                             | 22 |

| 2 | Framerate (fps) for images of $512 \times 512$ , $640 \times 480$ , $1024 \times 1024$ , $1920 \times 1080$ elements and 16, 32, |    |

|   | 64 and 128 bins, for 1 or 2 GPUs and using different grouping factors                                                            | 25 |

#### 1. SUMMARY

The University of Missouri (MU) completed the parallel implementations of several core computer vision algorithms including the integral histogram for fast subwindow object searching that is scalable to large images and large subwindow sizes using Compute Unified Device Architecture (CUDA) for many core Graphics Processing Units (GPU) with various kernel optimizations. The integral histogram algorithm was also parallelized for the Cell Broadband Engine (Cell/B.E.) architecture jointly with the Barcelona Supercomputing Center. These algorithms and code implementations have been delivered to AFRL for transition to other AFRL programs including Command, Control, Communications, Computers, Intelligence, Surveillance and Reconnaissance (C4ISR) Enterprise to the Edge (CETE), Multi-INT Enhanced Exploitation and Analysis Tools (E2AT) and Next Generation Wide Area Motion Imagery (WAMI). An initial implementation of the 3D spatiotemporal median filter for background model-based fast motion detection, using integral histograms, was also tested.

The rapid succession of powerful and innovative architectures has rekindled an interest in programming models such as CUDA or OpenCL. Parallel programming practice traditionally tends towards thread or streaming models. Threads and streams deliver good performance if the application can be expressed as a set of cooperating parallel resources or restrictions on data access are honored, respectively. We compare this tradition to an approach inspired by the Instruction-Level Parallelism (ILP) in superscalar processors, as found in Star Superscalar<sup>4</sup> (StarSs) and StarPU.<sup>5</sup> These models use a standard, sequential programming language and rely on data dependence analysis to execute the workload in parallel. This results in good portability and simplifies code development. We illustrate these features and describe a parallel implementation of the integral histogram in StarSs. This report provides performance results for the portable implementation of an efficient integral histogram computation in StarSs for symmetric multiprocessing (SMP), the Cell Broadband Engine (Cell/B.E.) and GPU.

We have completed the GPU parallel multicore implementation of the integral histogram which is an extension of the integral image computation for full motion video processing. Several different kernels were implemented that tradeoff compute intensive versus communication intensive approaches. We are characterizing these kernels and are continuing evaluating the performance of the algorithms on different sized images.

The integral histogram for images is an efficient preprocessing method for speeding up diverse computer vision algorithms including object detection, appearance-based tracking, recognition and segmentation. We have completed an efficient GPU implementation based on cross-weave scans implemented using parallel prefix-sums and image transposition. Our proposed Graphics Processing Unit (GPU) implementation uses parallel prefix sums on row and column histograms in a cross-weave scan with high GPU utilization and communication-aware data transfer between CPU and GPU memories.

Parallel implementations of the integral histogram computation were developed, for the multicore Cell/B.E. and many core GPU using CUDA. The Cell/B.E. implementation using cross-weave scan and 16 bins for a 640x480 image reaches 160 fr/sec using 8 Synergistic Processing Elements (SPEs). The wavefront scan for the same parameters reaches almost 200 fr/sec but is more critically dependent on the block size.

Several GPU CUDA kernels for the integral histogram were implemented, tested and evaluated. Two different data structures and communication models were evaluated in these three kernels. A 3-D array to store binned histograms for each pixel and an equivalent linearized 1-D array, each with distinctive data movement patterns. Using the 3-D array with many kernel invocations and low workload per kernel was inefficient, highlighting the necessity for careful mapping of sequential algorithms onto the GPU. We characterized the dependence on image size, tile size, histogram bin size, memory utilization, thread utilization, and data transfer times. We compared the efficiency of the BSC StarSs programming model to extend the integral histogram to SMP and GPU architectures compared to manually optimized GPU CUDA implementations of the integral histogram.

The reorganized 1-D array with a single data transfer to the GPU with high GPU utilization, was 60 times faster than the sequential CPU version for a 1K x 1K image reaching 49 fr/sec and 21 times faster for 512 x 512 images reaching 194 fr/sec. With larger image sizes data transfer communication time dominates a larger percent of the total time taken for the integral histogram task. The integral histogram module is applied as part of the likelihood of features tracking (LOFT) system for video object tracking using fusion of multiple cues.

We have extended the integral histogram approach to design and implement an initial version of the 3D spatiotemporal median filter algorithm for fast motion detection in full motion video. We characterized the performance of the spatiotemporal adaptive x-y-t median operator for moving object detection in complex electrooptical and infrared video sequences. Initial results of the GPU implementation are promising showing performance improvements similar to the integral histogram speedup. We characterized performance of the parallel 3D median filter for different image sizes and varying number of histogram bins and evaluated motion detection performance on real video sequences.<sup>6</sup>

Future work will include integration of these parallel computer vision algorithms with wide area motion imagery and full motion video multitarget tracking systems. We are also working on extending the integral histogram for axis aligned bounding boxes to support oriented bounding boxes.

This report based on several publications written as part of the project deliverables.<sup>6–9</sup> The StarSs programming model is shown to be very efficient for rapid prototyping of portable parallel versions of image processing and computer vision algorithms. However, for best performance manual code tuning and optimization are still necessary at the expense of additional development time and cost.

#### 2. INTRODUCTION AND ARCHITECTURE BACKGROUND

#### 2.1 Multicore Programming Design Patterns

The Cell Broadband Engine (Cell/B.E.) multicore processor developed by IBM and other companies, incorporates the verb—POWER5— processor as the Power Processor Element (PPE), one of the early general purpose multicore processors, where it cooperates with 8 single instruction multiple data (SIMD) cores or Synergistic Processing Elements (SPEs) to deliver an power efficient single-precision peak performance of more than 256 GFlops. Substantially more raw power became available later, when nVIDIA released the first version of CUDA together with its line of Tesla GPUs. Over the course of the past decade, we have witnessed the rise of homogeneous and heterogeneous multicore processors. These parallel architectures offer affordable and power efficient computing resources for computer vision algorithms in constrained environments. However, programming models for these parallel hardware architectures have not kept pace.

Architectural innovations as these, that affect Thread-Level Parallelism (TLP) or Data-Level Parallelism (DLP), invariably trigger changes in the way we write programs. In the same vein as the development of SMP lead to Open Multi-Processing (OpenMP) and clusters inspired the use of the Message Passing Interface (MPI), the multicore architectures sparked an interest in suitable programming models. Cilk $++^{10}$  for example, implements the nested threading model of Cilk<sup>11</sup> for multicores. OoOJava<sup>12</sup> adheres to the same fork-join model and performs automatic dependence analysis during compilation and execution. Its compiler conservatively estimates dependencies in order to build run-time queues of threads. Light-weight checks then enforce a correct schedule of the threads at run-time. CUDA<sup>13</sup> models the computation as a sequence of two-dimensional thread grids. Each thread grid consists of three-dimensional, independent thread blocks. The threads in a thread block execute the same kernel in parallel. Computations and data transfers can be ordered by defining streams and the CUDA interface provides explicit control over the memory hierarchy. BrookGPU<sup>14</sup> implements the Brook stream programming language for GPUs. A stream identifies a collection of elements and has a shape or dimensionality. A kernel applies a function to each element of the stream in parallel. Brook has a reduction construct and is able to infer the size of an output stream based on the kernel's input streams. The OpenCL<sup>15</sup> framework publishes the hardware resources of a heterogeneous system via a uniform interface. Programs written in OpenCL can therefore call kernels that execute in a CPU, GPU or multicore.

These programming models impose an explicit parallel structure on the computation. A thread model exposes individual execution contexts and in that capacity it ties in closely with the underlying hardware. The low level of the thread interface delivers the full computational power of the hardware, but exposes its complexity and quirks as well. Nested thread models further restrict the structure of the computation to the spawn tree of the parallel threads, but not all applications lend themselves to a description in terms of recursive calls to threads. Unless the application exhibits massive amounts of unstructured parallelism one must also provide synchronization between the threads. This requirement stems from the order among the data accesses of the application, whereas the thread model is designed around the (parallel) capacity to process the data. The

former fundamentally characterizes the computation itself, whereas the latter is an artefact of the particular programming model. Parallel computing by definition requires the availability of multiple resources, but in the presence of this cheap commodity the limiting factor is *data dependence*. Streaming models on the contrary make no assumptions about the available resources but they limit the permissible data dependencies. Specifically, kernels process the elements of a stream in parallel, which precludes the existence of data dependencies among the elements.

In the threading model and the stream model the user consequently must understand the data dependencies that govern the computation and take appropriate measures. Either the algorithm must be restructured to avoid synchronization or one must add synchronization primitives, as both models support the fundamental property of data dependence only indirectly. This observation did not in the least prevent the widespread and successful use of these models. The lack of data dependence analysis and enforcement creates the freedom to craft efficient programs tailored for a specific architecture, although the effort involved can be prohibitive. Alternatively the parallel programming model itself can define the computation directly in terms of the data dependencies. StarSs (Section 2.3), StarPU<sup>5</sup> and PLASMA<sup>17,18</sup> are exponents of this trend. Instead of code that explicitly unveils DLP, be it via threads or streams, the aforementioned programming models resort to a sequential description, which identifies tasks or units of parallel computation. StarSs supports standard C and Fortran, for example. The data dependencies present in the sequential code define task dependencies. These are recorded in a Task Dependency Graph (TDG) or a similar data structure during execution. The runtime library schedules tasks from the TDG to the parallel resources and enforces the partial order on the tasks. DAGuE<sup>19</sup> is a distributed scheduler for MAGMA<sup>20</sup> that uses a compact and problem-size independent format for the TDG called Job Definition Format (JDF). Like the Parameterized Task Graph, <sup>21</sup> the JDF representation can be used at run time to determine task dependencies without unrolling the TDG of the application and without a centralized arbiter.

Such parallel programming models typically reduce the programming effort, as dependence analysis, scheduling and resource synchronization are handled by the compiler or the runtime instead of by the user. The resulting code also is more readily portable, as the program description (e.g. standard C for a StarSs application) is architecture-independent. This form of organizing a parallel computation bears a striking resemblance to the instruction-level parallelism in superscalar processors. In both cases the workload consists of a sequential stream of tasks or instructions. A superscalar processor tracks the dependencies for a window of instructions and issues instructions without outstanding dependencies. Independent instructions execute in parallel, given the availability of sufficient resources.<sup>22,23</sup>

In this report we describe a parallel implementation of the integral histogram<sup>24</sup> (IH) using the StarSs programming model. It is not our intention to make a case for one programming model or the other. Rather, to evaluate the merits of our implementation, we demonstrate the portability of IH in StarSs by executing the same source code on three different platforms, including SMP, the Cell Broadband Engine (Cell/B.E.) and a GPU platform. Section 4.1 discusses the performance on each architecture. For the Cell/B.E. we compare IH in StarSs with an optimized, hand-coded version (Section 3.3) to get an idea of the relative performance or efficiency of a StarSs application. First we give an overview of StarSs (Section 2.3) and briefly discuss IH (Section 3.1) together with related work on the topic (Section 2.2), followed by the parallel implementation of IH in StarSs (Section 3.2). Section 4.2 formulates some conclusions and hints at future work.

#### 2.2 Dynamic Scene Analysis Using Integral Histograms

Histograms limited to an image segment (or regional histograms) are widely used in a variety of computer vision tasks. Their application extends from object recognition and image content-based retrieval to segmentation, detection and tracking. Sliding-window search methods can use histogram measures to produce high-quality results but the computational cost is immense. The integral histogram<sup>24</sup> is a recently proposed preprocessing technique that abates said cost. It allows for histogram construction of arbitrary rectangular gridded regions (i.e. images or volumes) in constant time. Preprocessed images are suitable for exhaustive global search using sliding window-based histogram optimization measures, yield high-quality results<sup>25</sup> and still obey real-time bounds. Fast histogram computation using the integral histogram (IH) speeds up the sequential implementation by up to five orders of magnitude. However, the overall cost remains prohibitive for real-time applications with large images, large search window sizes and a large number of histogram bins. For example, a  $512 \times 512$  image

search using a 1000-bin feature histogram requires about 1 gigabyte (GB) of memory and takes about one second.<sup>26</sup> The computation of such dense confidence maps remains infeasible for these types of applications. A parallel implementation of the IH would enable methods using global optimization of histogram measures to be competitive with or faster than other approaches in terms of speed. There are a variety of commodity multicore architectures currently available for the parallelization of image- and video-processing algorithms, including IBM's Cell/B.E., GPUs from NVidia and AMD and many-core CPUs from Intel.<sup>27</sup> The vast growth of digital video content has been a driving force behind active research into exploiting heterogeneous multi-core architectures for computationally intensive, multimedia analysis tasks. These include real-time (and super-real-time) object recognition, object tracking in multi-camera sensor networks, stereo vision, information fusion, face recognition, biometrics, image restoration, compression, etc.<sup>28–34</sup>

Data dependence and implicit parallelism are central ideas in StarSs and its runtime controls the scheduling of tasks and data transfer of task arguments. Then the implementations of these aspects in StarSs critically affect the performance of an application. Dynamic dependence analysis can be limited to blocks or more complete based on linear representations.<sup>35</sup> The scheduler is distributed and uses job stealing<sup>16</sup> or speculative techniques<sup>36</sup> for good scalability and to avoid bottlenecks. Dependence tracking and scheduling cooperate to exploit temporal locality.<sup>37</sup> This ability is crucial to circumvent memory bandwidth limitations on multicore- and GPU architectures. In particular, the implementation of StarSs for GPU<sup>38</sup> is able to manage CUDA streams for overlapping communication and computation.

#### 2.3 Integral Histogram Using Star Superscalar (StarSs) for Parallel Architectures

The StarSs programming model<sup>4, 39, 40</sup> provides an environment for the development of portable parallel applications for a variety of architectures. In this report we use the implementations of StarSs for SMP, Cell/B.E. and NVIDIA GPU, referred to respectively as SMPSs, CellSs and GPUSs. The programming model advocates the development of code in a standard, sequential language, such as C or Fortran. On the user's side there are no explicit parallel constructs, like threads or streams. It generally suffices that the user adds pragmas to the original code to mark the code intended to execute on the parallel resources, referred to as tasks, typically corresponding to functions or inline code blocks. The StarSs source-to-source compiler converts these pragmas into calls to the StarSs runtime library. As the application advances the StarSs runtime executes the tasks in parallel as dictated by the data dependencies present in the original program (Figure 1).

Figure 1: Overview of the structure of a StarSs application. The user code generates tasks according to the sequential program (1), the runtime records the tasks into a TDG, schedules tasks to resources (2) and removes finished tasks from the TDG (3).

In practice the main thread of a StarSs application executes the sequential code and switches to the StarSs library when it encounters code marked with a pragma. The library or runtime does not immediately execute the task. Instead it analyzes the task arguments to find the true dependencies that define task precedence. StarSs avoids output dependencies and anti-dependencies by renaming arguments. The main thread returns control to the user application and the StarSs runtime records the task in the Task Dependence Graph (TDG).

Simultaneously the runtime schedules **ready tasks** (or tasks without outstanding dependencies in the TDG) to the multiple resources. The resources in turn remove finished tasks from the TDG and update the state of dependent tasks. Ultimately this pruning of dependencies updates dependent tasks to ready tasks that again become scheduling candidates.

In StarSs dependence analysis, renaming, scheduling and updates to the TDG take place concurrently during execution. This combination converts a sequential stream of tasks generated by a single thread into a TDG into a parallel execution of tasks on multiple resources. The concept has a strong resemblance to dynamic scheduling in superscalar processors, where the pipeline decodes instructions in order but schedules them to multiple units in parallel. In both cases the ability to track data dependencies drives the parallel execution. The StarSs model hides the underlying hardware and frees the user from the tedious requirements that traditionally accompany parallel programming (synchronization, scheduling, decomposition, load balancing,...). The first aspect ensures that StarSs applications are portable and the second reduces the turnaround time for code development. The high-level interface of StarSs nevertheless translates to good performance for a wide variety of applications. To this end the run-time libraries incorporate techniques that e.g. improve temporal locality, increase the degree of parallelism, pipeline tasks, cache data, and so forth.

#### 2.4 GPU Architecture Consideration

We summarize some of the important aspects of the GPU architecture and its programmability that is pertinent to the efficient use of GPU kernels and structuring the flow of the integral histogram computation for large images.

Massive parallelism and programmability NVIDIA GPUs consist of several Streaming Multiprocessors (SMs), each containing a set of in-order cores. In the Fermi architecture, each SM comprises either 32 or 48 cores. For example, the Tesla C2070 card consists of fourteen 32-core SMs, for a total of 448 cores. The advent of the Compute Unified Device Architecture (CUDA) has greatly improved the programmability of NVIDIA GPUs. With CUDA, the computation is organized in a hierarchical fashion, wherein threads are grouped into thread blocks. Each thread block is mapped onto a different SM, whereas different threads are mapped to cores and executed in SIMD units, called warps. Threads within the same block can communicate using shared memory, whereas threads within different thread blocks are fully independent. Therefore, CUDA exposes to the programmer two degrees of parallelism: fine-grained parallelism within a thread block and coarse-grained parallelism across multiple thread blocks. GPU utilization is maximized when threads belonging to the same warp do not present divergent control flows, and when the kernel launch configuration (number of threads and thread blocks) is such to fully utilize the underlying cores.

**GPU** memory hierarchy GPUs have a heterogeneous memory organization consisting of high latency off-chip global memory, low latency read-only constant memory (which resides off-chip but is cached), low-latency on-chip read-write shared memory, and texture memory. GPUs adopting the Fermi architecture, such as those used in this work, are also equipped with a two-level cache hierarchy. Judicious use of the memory hierarchy and of the available memory bandwidth is essential to achieve good performances.

The global memory can be accessed via 32-, 64- or 128- bytes transactions. Multiple memory accesses to contiguous memory locations can be automatically coalesced into a single memory transaction: memory coalescing is fundamental to optimize the memory bandwidth utilization. Further, context-switch among threads can be used to hide high latency global memory accesses. Finally, the use of shared memory and caches can be used to reduce the accesses to global memory.

The shared memory can be configured either as a software- or as a hardware-managed cache. The first configuration is typical of highly optimized code. In this case, within kernel functions, threads will first load the data from global memory to shared memory, then process the data into shared memory, and finally move the results into global memory. Since shared memory does not impose the same coalescing rules as global memory, it can allow efficient irregular access patterns. In order to achieve high bandwidth, shared memory is divided into equally sized banks. Memory requests directed to different banks can be served in parallel, whereas requests to the same bank are serialized. Therefore, avoiding bank conflicts is essential to optimize shared memory access.

#### 3. METHODS, ASSUMPTIONS AND PROCEDURES

#### 3.1 Integral Histogram Computation for Vision Applications

We define an image as a function f over a two-dimensional Cartesian space  $\mathbb{R}^2$  such that  $\mathbf{x} \to f(\mathbf{x})$  for a pixel  $\mathbf{x} \in \mathbb{R}^2$ . The binning function  $Q(f(\mathbf{x}), b)$  evaluates to 1 if  $f(\mathbf{x}) \in b$  for the bin b, otherwise its value equals 0. For a set  $B = \{b_0, b_1, \dots, b_n\}$  of intervals or bins the histogram b evaluates the binning function b0 over the pixels in the domain of b1:

$$h(b) = \sum_{\mathbf{x}} Q(f(\mathbf{x}), b) \quad b \in B$$

(1)

In general, IH associates a histogram with each pixel of the image. For a sequence of pixels  $S = (\mathbf{x}^0, \mathbf{x}^1, \dots, \mathbf{x}^p)$  and a subsequence  $S_{\mathbf{x}^p} \subseteq S$  the integral histogram H at  $\mathbf{x}^p$  for a bin b is defined as

$$H(\mathbf{x}^p, b) = \sum_{\mathbf{x} \in S_{\mathbf{x}^p}} Q(f(\mathbf{x}), b)$$

(2)

S forms the scan order. This definition states that the value for a bin b at a pixel  $\mathbf{x}^p$  in H can be found by applying the binning function to a subset of the pixels preceding  $\mathbf{x}^p$  in the scan order. The computation essentially propagates pixel values through the image f. To emphasize the two-dimensional nature of f we can identify the pixel  $\mathbf{x}$  with its spatial coordinates (i,j). This carries over to H and f, that become H(i,j,b) and f(i,j) in this notation. We assume that H and f are respectively a vector and a scalar associated with a pixel, although in practice two separate data structures are used to represent the image and the integral histogram.

Figure 2: Intersection or computation of the histogram for the region in grey, defined by the pixels  $\{(k, m), (k, n), (l, m), (l, n) | k < l, m < n\}$ .

Specifically, IH uses an efficient scan order, that limits the number of visits to each pixel, such that the computation of the histogram for a rectangular region T of f becomes computationally inexpensive. In that context the computation of H, or **propagation**, precedes the computation of the histogram or **intersection**. We only consider scan orders that result in

$$H(i,j,b) = \sum_{x=0}^{i} \sum_{y=0}^{j} Q(f(x,y),b)$$

(3)

This means that H at pixel (i,j) summarizes the values of the pixels above and to the left of (i,j). The intersection for the region (Figure 2) delimited by the points  $\{(k,m),(k,n),(l,m),(l,n)|k< l,m< n\}$  then

reduces to a linear combination of four histograms from H:

$$h(T,b) = H(k-1, m-1, b) + H(l, n, b) - H(k-1, n, b) - H(l, m-1, b)$$

(4)

Propagation initializes H(i, j, b) to 0 for all pixels (i, j) and bins b. We describe two scan orders. A scan order, by definition, imposes a strict order on the pixels and histograms. But if the computation at an element (i, j) requires only a proper subset of the histograms computed previously, the scan order can be relaxed to a partial order.

Figure 3: The two passes for the cross-weave scan.

The **cross-weave scan** requires two passes over H as it processes each dimension separately (Figure 3). In the Y-direction it visits the pixels and histograms from left to right and top to bottom. At each element (i,j) the algorithm propagates H(i,j,b) to (i,j+1) in order to compute H(i,j+1,b). As a result the propagation in the Y-direction can advance in parallel for different rows, in spite of the strict order suggested by the horizontal pass. In the X-direction the cross-weave scan processes H from top to bottom and left to right. The histogram at H(i,j,b) passes on to pixel (i+1,j) to compute H(i+1,j,b). Now columns can be processed in parallel. The cross-weave scan thus allows the propagation for rows (step 1) and columns (step 2) to advance in parallel, while the operations in each row or column are strictly ordered:

(1)

$$H(i, j, b) = 0$$

(2)  $H(i, j, b) = Q(f(i, j), b) + H(i, j - 1, b) \quad j > 0$

(3)  $H(i, j, b) = H(i, j, b) + H(i - 1, j, b) \quad i > 0$

The wavefront scan performs a single pass over the input image and orders the pixels according to the antidiagonals, starting from the upper left corner down to the lower right corner (Figure 4). Propagation according to the wavefront scan computes H(i, j, b) using H(i, j-1, b), H(i-1, j, b), H(i-1, j-1, b). Applied recursively, the propagation at (i, j) thus occurs after the algorithm has computed all H(i-x, j-y, b),  $x = 1, \ldots, i, y = 1, \ldots, j$ above and to the left of (i, j):

(1)

$$H(i, j, b) = 0$$

(2)  $H(i, j, b) = H(i - 1, j, b) + H(i, j - 1, b) - H(i - 1, j - 1) + Q(f(i, j), b)$

Remark that, again, the wavefront scan does not strictly order the accesses to the elements. Its definition only requires that the computation of H(i,j,b) precedes the computation of  $\{H(i+i,j+j,b)\}, i,j>0$ , as the latter uses the values computed by the former.

Figure 4: The wavefront scan.

A possible implementation of the wavefront scan advances an anti-diagonal wavefront over the input image. It first computes the histogram at the pixel  $D_0 = \{(0,0)\}$ , followed by the histograms at the pixels in  $D_1 = \{(1,0),(1,1),(1,0)\},\ldots$  until all the anti-diagonals have been visited. The histograms at each  $D_i$  can be computed in parallel, because the histograms of all the (direct) upper and left neighbors have been computed in  $D_{i-1}$ . Alternatively an implementation can process the pixels from left to right and from top to bottom, under the restriction that only one element can be processed at a time.

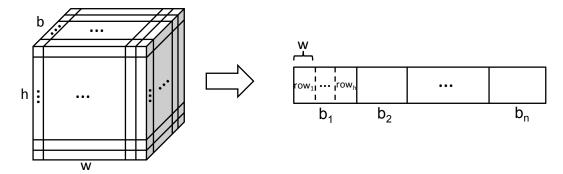

Figure 5: Block data layout for a  $w \times h$  image and integral histogram. Each tile contains  $b_w \times b_h$  pixels or histograms.

#### 3.2 Parallel Integral Histogram in StarSs

The cross-weave nor the wavefront scan impose a strict order on the computations (Section 3.1), hence IH can be parallelized. To this end we formulate a tiled or blocked version. Blocking subdivides the image f and the integral histogram H, and naturally divides the computation into smaller units or tasks. This design is scalable and general, and readily adapts to different target architectures. The implementation in StarSs expresses the

tiled algorithm in a traditional, sequential programming language such as C. At run-time StarSs tracks read and write accesses to the tiles, derives the dependencies between the tasks performing the accesses and schedules tasks to the parallel resources (Section 2.3).

Figure 5 illustrates the tiled or block data layout for f and H. We preserve the usual coordinate system, but now a coordinate pair identifies a tile instead of an individual pixel or histogram. An image of dimensions  $w \times h$  defines H with  $(w \times h) \times b_c$  bins, with  $b_c$  the number of bins in a histogram. It admits a division into blocks of  $b_w \times b_h$  pixels, whereas H can be decomposed in tiles of  $b_w \times b_h$  histograms. Conversely, each tile of H holds  $b_w \times b_h \times b_c$  bins. The original image can be padded to eliminate boundary conditions. In the block data layout f as well as H consist of  $w_B \times h_B$  blocks with  $w_B = \lceil w/b_w \rceil$  and  $h_B = \lceil h/b_h \rceil$ . We distinguish between blocks and individual elements using a slightly different notation. Blocks  $f_{i,j}$  and  $H_{i,j}$  correspond to the tiles at row i and column j in the block data layout of the image and the integral histogram, respectively, while (i,j) designates a pixel or a histogram depending on the context.

We define the propagation on a single block as a task. For the cross-weave scan this results in two different types of tasks, one for the horizontal and one for the vertical pass. The wavefront scan uses only one type of task. There is a one-to-one map between tasks (of the same type) and blocks in f or H. Task  $t_{i,j}$  uses block  $f_{i,j}$  in the propagation for a block  $H_{i,j}$ . Parallel computation then derives from concurrent execution of tasks without dependencies. For a GPU, intra-task parallelism can be achieved by dividing the computation of the elements of a block  $H_{i,j}$  over the threads in a thread block (Section 4.1.4). On the Cell/B.E. and for SMP a parallel resource is single-threaded. Hence  $H_{i,j}$  can be computed with a sequential version of the cross-weave or wavefront scan, restricted to a single block. In both scan orders the tasks access the pixels of  $f_{i,j}$ , and for each pixel  $(x,y) \in f_{i,j}$  it updates the bins of the associated histogram (x,y) in  $H_{i,j}$ . For example, the task for the wavefront scan in our implementation processes the pixels from left to right and from top to bottom as suggested in Section 3.1:

Similarly, the task for the horizontal pass of the cross-weave scan copies the histogram at  $(x,y) \in H_{i,j}$  to the histogram at (x,y+1) and increments the bin b for which Q(f(x,y)) = 1. The vertical scan adds the histogram at  $(x-1,y) \in H_{i,j}$  to the histogram at (x,y). For both scan orders most of the computations in a tile  $H_{i,j}$  use updated elements from  $H_{i,j}$  as input. However, in the wavefront task, the computation of the histograms at  $(0,y), y=0,\ldots,b_w$  and  $(x,0), x=0,\ldots,b_h$  for a block  $H_{i,j}$  requires histograms that belong to  $H_{i-1,j}, H_{i,j-1}$  and  $H_{i-1,j-1}$ . The horizontal pass of the cross-weave scan computes the elements (x,0) of  $H_{i,j}$  using the histograms on the border of  $H_{i,j-1}$  and the vertical pass requires the lower border of H(i-1,j) for the propagation of the (0,y) in  $H_{i,j}$ . Propagation on blocks exhibits the same characteristics as propagation on individual elements. In a tiled formulation, IH propagates histograms from one block to another block at block boundaries. We restrict our attention to the wavefront scan from here on. The development of the algorithm for the cross-weave scan is analogous.

Figure 6: Inter-block dependencies for block  $H_{i,j}$  with halos for propagation between tiles. The arrows specify the inter-block dependencies for some selected histograms on the borders of  $H_{i,j}$ .

The aforementioned dependence between  $H_{i,j}$  stems from the data dependence between the elements they contain. Figure 6 identifies three sets or **halos** for a tile  $H_{i,j}$ , namely  $H_{i,j}^d$ ,  $H_{i,j}^h$  and  $H_{i,j}^v$ . The subscript identifies the tile whose edges require the histograms in these sets. The singleton  $H_{i,j}^d$  contains the histogram  $(b_h - 1, b_w - 1)$  of the diagonally opposite block  $H_{i-1,j-1}$ , while  $H_{i,j}^v = \{(l, b_w - 1) \in H_{i,j-1} | l = 0, \dots, b_h - 1\}$  and  $H_{i,j}^h = \{(b_h - 1, l) \in H_{i-1,j} | l = 0, \dots, b_w - 1\}$ . Element (0,0) of  $H_{i,j}$  depends on  $H_{i,j}^d$ , elements  $(x,0), x = 0, \dots, b_h - 1$  need  $H_{i,j}^v$  and finally the propagation for elements  $(0,y), y = 0, \dots, b_w - 1$  uses  $H_{i,j}^h$ . The map between tasks and blocks defines task precedence via the data dependencies on the blocks:  $t_{i,j}$  is eligible for execution if all tasks  $t_{x,y}$  with x < i, y < j have been computed. Or  $t_{i,j}$  depends on  $t_{i-1,j}$  via  $H_{i,j}^h$ , on  $t_{i,j-1}$  via  $H_{i,j}^v$  and on  $t_{i-1,j-1}$  through  $H_{i,j}^d$ .

The halos correspond to definitions of sets of histograms, rather than effective data structures, that make the data dependencies between  $H_{i,j}$  explicit. These blocks have fixed dimensions, while the propagation in IH extends over the entire input and spills from one block to the next. Our implementation replicates the halos and allocates separate physical buffers, as in Figure 7, which are considered blocks as well. This duplication allows us to express the data accesses by a task  $t_{i,j}$  in terms of full blocks, instead of subsets of blocks:  $t_{i,j}$  accepts as input arguments the block  $f_{i,j}$  and the halos  $H^h_{i,j}$ ,  $H^v_{i,j}$  and  $H^d_{i,j}$ . Its output consists of  $H_{i,j}$  and the halos  $H^h_{i+1,j}$ ,  $H^v_{i,j+1}$  and  $H^d_{i+1,j+1}$ . These chains of halo production and consumption establish the required data dependencies. The data dependencies as exposed via the task arguments completely define the task precedence, which simplifies and speeds up the dependence analysis in StarSs \*. Figure 8 depicts the TDG for IH for a small image size for both scan orders. The cross-weave scan

<sup>\*</sup>Although this is not a strict requirement. $^{35}$

Figure 7: Block data layout for the integral histogram. Each block contains  $b_w \times b_h$  histograms. Block borders are duplicated in the *halos* and serve to pass histograms to the neighboring blocks.

visits each tile  $H_{i,j}$  twice, once during the horizontal pass and next in the vertical pass, and generates twice as many tasks as the wavefront scan.

The halos  $H^v_{i,j}$  occupy an additional  $h_B \times b_h \times w_B \times b_c$  bins, the halos  $H^h_{i,j}$  take up  $w_B \times b_w \times h_B \times b_c$  bins and the  $H^d_{i,j}$   $h_B \times w_B \times b_c$  bins. These storage requirements can be reduced by noting that the horizontal halos can be recycled per row, the vertical halos per column and the diagonal halos per diagonal. The lifetime of  $H^h_{i,j}$  ends before  $H^h_{i+1,j}$  is produced because task  $t_{i,j}$  executes and finishes before  $t_{i+1,j}, \forall j=0,\ldots,w_B-1$ . The task precedence for this application guarantees that the accesses to  $H^h_{i,j}$  do not overlap in time for fixed j. Similar observations hold for the vertical and diagonal halos. Hence there is no reason to separate the input and output halos of a task:  $H^h_{i,j}, H^v_{i,j}$  and  $H^d_{i,j}$  can occupy the same memory as  $H^h_{i+1,j}, H^v_{i,j+1}$  and  $H^d_{i+1,j+1}$  respectively. With this reduction the horizontal halos occupy  $w_B \times b_w \times b_c$  additional bins, the vertical halos  $h_B \times b_h \times b_c$  bins and the diagonal halos ( $w_B + h_B - 1$ )  $\times b_c$  bins. As a side-effect the task can be defined with fewer parameters, because the halos that are read and written are the same. At run-time this translates to fewer arguments per StarSs task, less dependence analysis and less runtime overhead.

With the block data layout in place IH can be implemented in a straightforward manner in StarSs. The main function is a simple sequential description of the scan order. For the wavefront scan the code steps through the diagonals parallel to the minor diagonal of the blocked H. This generates the sequence of tasks  $t_{0,0},t_{1,0},t_{0,1},t_{2,0},t_{1,1},t_{0,2},...$  The StarSs library builds the TDG at execution time and schedules the tasks to the resources (Section 2.3). For SMP and the Cell/B.E. the task for the wavefront scan resorts to the sequential, left-to-right variant for propagation (Section 3.1). The main function for the cross-weave scan looks as follows:

```

// im[i][j] = image block (i,j)

// ih[i][j] = integral histogram block (i,j)

// vhalos[i] = vertical halo for row i

// hhalos[i] = horizontal halo for column i

int main(int argc, char *argv[]) {

...

// horizontal scan

for (int i=0; i<imheight; i++) {</pre>

```

Figure 8: TDG for the tiled IH ( $w_B = h_B = 4$ ) for (a) the cross-weave scan and (b) the wavefront scan. The tasks are numbered according to program order, which is identical to the scan order in our implementation in StarSs. The color of a node represents the task type.

```

for (int j=0; j<imwidth; j++) {

hscan(...,im[i][j],vhalos[i],ih[i][j]);

}

// vertical scan

for (int j=0; j<imwidth; j++) {

for(int i=0; i<imheight; i++) {

vscan(..,hhalos[j],ih[i][j]);

}

}

...

}</pre>

```

#### 3.3 Reference Implementation on the Cell/B.E.

To evaluate the quality of IH in StarSs we implemented the wavefront scan directly on the Cell/B.E. using the same general design as in Section 3.2, albeit with a flat data layout (as opposed to a block data layout). The rows of a block do not occupy consecutive locations in main memory, but we process f and H by blocks: the SPEs use Direct Memory Access (DMA) lists to perform scatter and gather operations on the data. For fair comparison, we reuse the code of the StarSs tasks in this reference implementation.

The data dependencies for the wavefront scan are characteristic of its blocked formulation, not of a particular

Figure 9: Schedule and data flow for the reference implementation of the wavefront scan on the Cell/B.E.

implementation. As the wavefront scan on the Cell/B.E. uses the same tasks as for the CellSs version, the task dependencies are identical (Figure 8(b)). The regularity of the task dependencies suggests that a static task schedule is feasible. We simply hard-code the trend we observed in the schedules from CellSs for the wavefront scan and assign task  $t_{i,j}$  to SPE j%N, with N the number of available SPEs. Each (block) column in  $f_{i,j}$  or  $H_{i,j}$  is processed by the same SPE from top to bottom, in order, and the set of columns is divided over the SPEs in a round-robin fashion. As a result the halos  $H^h_{i,j}$ ,  $i=0,\ldots,h_B-1$  are accessed by the same SPE j%N. They can be cached in the local store (LS) between tasks  $t_{i,j}$  and  $t_{i+1,j}$ . From the schedule it further follows that the halos  $H^v_{i,j+1}$  and  $H^d_{i,j+1}$  have to be transferred from SPEs j%N to (j+1)%N. We arrange for the former SPE to push the produced data to the latter via LS-to-LS DMA transfers. SPE N-1, the last one in the pipeline of SPEs, copies the vertical and diagonal halos to main memory. To close the cycle, SPE 0 transfers those halos from main memory to its LS when it processes the corresponding tiles. For the remainder of the report we drop the modulo notation, as the distribution of tasks to SPEs should be clear.

The stand-alone implementation must enforce the proposed schedule, which requires synchronization. We do not use a scheduler for this purpose, but rather implement a distributed mechanism with tokens that piggy-back onto the DMA transfers of blocks between SPEs. Remark that the schedule defines a producer-consumer relation between SPE j and j+1 (wrapping around from N-1 to 0). Hence SPE j+1 must postpone the execution of  $t_{i,j+1}$  until SPE j has produced the required halos  $H_{i,j+1}^h$  and  $H_{i,j+1}^d$ . Reciprocally, SPE j must synchronize with j+1 in order not to flood the consumer with halos and exceed the limited storage of the LS. We conclude that the SPEs must work in lock-step.

The task dependencies dictate that  $t_{i,j}$  must precede  $t_{i+1,j}, t_{i,j+1}$  and  $t_{i+1,j+1}$ . The schedule trivially settles the first dependency. For the last two dependencies we arrange an explicit means of synchronization that takes advantage of the properties of the DMA transfers between each pair of SPEs. If the dependency  $t_{i,j} \to t_{i,j+1}$  (on SPE j and (j+1) respectively) is satisfied, then so is  $t_{i,j} \to t_{i+1,j+1}$ , because  $t_{i,j+1}$  precedes  $t_{i+1,j+1}$  on SPE (j+1) per definition of the schedule. We can therefore concentrate on the synchronization for the transfer of the vertical halos between a pair of SPEs to enforce the correct task precedence. We synchronize SPE (j+1), as a consumer of  $H_{i,j+1}^v$ , with the producer, SPE j, by transferring a token together with each  $H_{i,j+1}^v$ . After  $t_{i,j}$  finishes, SPE j starts the DMA transfer of  $H_{i,j+1}^v$  to SPE j+1 with tag t, followed by the transfer of a token  $t_{i,j+1}^v$  to SPE  $t_{i,j+1}^v$  to SPE

DMA transfers with the same tag are ordered with respect to SPE j+1. When SPE j+1 detects the arrival of  $T_p$ ,  $H_{i,j+1}^v$  will be present in its LS. For the wrap-around case, between SPE N-1 and SPE 0, the detection of  $T_p$  by SPE 0 signals that the DMA transfer of the vertical halo from the LS of SPE N-1 to main memory has finished. The consumer, SPE 0, can then set up a DMA transfer to bring the halo to its LS.

The same mechanism prevents that an SPE produces halos faster than its neighbor is able to consume. "Faster" in this context means that the producer uses up all the available buffers in the LS of the consumer, before the latter consumes the halos kept in the buffers. SPE j cannot advance unrestrictedly and flood the limited storage in SPE j+1 with vertical and diagonal halos. At some point SPE j much check whether it can reuse buffers in the LS of SPE j+1 to store the halos it produces. To this end SPE j+1 transfers a token  $T_c$  to SPE j. SPE j uses the value of  $T_c$  to check the amount of available buffers in SPE j+1. A buffer b becomes available again when the halo it contains can be overwritten, i.e. when it has been successfully transferred from SPE j+1 to SPE j+1. After SPE j+1 starts the DMA transfer of b to SPE b with tag b, it reuses b for a fenced DMA transfer of b to SPE b has finished, and that it can overwrite b with a new halo.

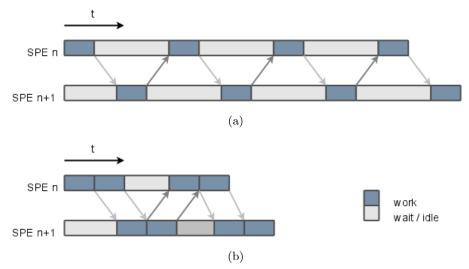

In summary, SPE j must wait for  $T_p$  from SPE j-1 before executing the associated task and for  $T_c$  in order not to overwrite the corresponding buffer in SPE j+1. This type of tight synchronization is very sensitive to delays and overly restricts the computation and interaction between SPEs. Instead of providing one single LS buffer for the halos, the image tile or the integral histogram tile, an SPE creates multiple buffers for each. And instead of using dimensionless tokens, our implementation uses arrays of counters to implement  $T_p$  and  $T_c$ . These provisions enable multi-buffering and relax the lock-step between the SPEs. The details are out of scope for this report, but hopefully Figure 10 illustrates the idea clearly.

Figure 10: (a) Tight lock-step between SPEs n and n+1 due to the presence of one output buffer for the produced halos. (b) The synchronization between the SPEs becomes less stringent by providing two output buffers. As a result the processing of the four blocks speeds up.

In Figure 10(a) SPE n disposes of a single output buffer per halo, which hold the produced halos. SPE n must wait for the acknowledgement ( $T_c$ ) from SPE n+1 before it advances and overwrites these buffers, as their contents must have reached SPE n+1. This results in a tight lock-step between the SPEs involved and SPE cycles are wasted waiting for the halos to arrive or clear the LS. In Figure 10(b) the SPEs have two output buffers per halo. SPE n can then execute two tasks and produce two sets of halos before it has to synchronize with SPE n+1, waiting for a buffer to free up. The additional buffer and the more refined synchronization protocol give the SPEs more freedom to advance before having to synchronize with its neighbors. The resulting decoupling reduces the time spent in synchronization and hence improves performance.

Figure 11: Lack of potentially parallel tasks at the beginning and the end of the wavefront scan on SMP. The horizontal axis represents execution time and an entry on the vertical axis corresponds to a thread. The dark phases mark task execution whereas the threads idle during the lighter phases. In this Paraver trace we clearly distinguish a computation-intensive middle part centered between two regions where the threads are less active.

#### 3.4 GPU Kernel Optimization for Integral Histogram

In this section we describe the details of the GPU integral histogram implementation. We first describe the integral histogram data structure and its layout in GPU memory and then present different optimization strategies. In our first implementations,<sup>7</sup> we reuse existing parallel kernels from the NVIDIA Software Development Kit (SDK); we refer to these as generic kernels. We point out the limitations of such an approach, and progressively refine our implementation in order to better utilize the architectural features of the GPU. This leads to the evolution of four techniques to compute the integral histogram on GPUs that trade-off productivity with efficiency and a discussion of how the performance of the proposed implementations reflect their utilization of the underlying hardware. The first three implementations perform cumulative sums on row and column histograms in a cross-weave (CW) fashion, whereas the fourth one performs a wavefront (WF) scan.

#### 3.4.1 GPU Aware Data Structure Design

An image with dimensions  $h \times w$  produces an integral histogram tensor of dimensions  $b \times h \times w$ , where b is the number of bins in the histogram. This tensor can be represented as a 3-D array, which in turn can be mapped onto a 1-D row major ordered array as shown in Figure 12. It is well known that the PCI-Express connecting CPU and GPU is best utilized by performing a single large data transfer rather than many small data transfers. Therefore, whenever the 1-D array representing the integral histogram fits in the available GPU global memory, we transfer it between GPU and CPU using a single memory transaction. The computation of larger integral histograms is tiled along the bin-direction and distributed between available GPUs: portions of the 1-D array corresponding to the maximum number of bins that fit the GPU capacity are transferred between GPU and CPU in single transaction units. For all the considered image sizes a single bin fits the GPU memory; however, our implementation can be easily extended to images exceeding the GPU capacity by tiling the computation also column-wise. Finally, we experimentally verified that initializing the integral histogram on GPU is more efficient than initializing it on CPU and then transferring it from CPU to GPU. Therefore, in all our GPU implementations, we initially transfer the image from CPU to GPU, then initialize and compute the integral histogram on GPU, and finally transfer it back from GPU to CPU.

#### 3.4.2 GPU Parallelization Using Parallel Prefix-Sum (Exclusive Scan)