# Effect of Interface States on the Performance of Antimonide nMOSFETs

Ashkar Ali, *Student Member, IEEE*, Himanshu Madan, *Student Member, IEEE*, Michael J. Barth, J. Brad Boos, *Member, IEEE*, Brian R. Bennett, and Suman Datta, *Fellow, IEEE*

Abstract—Antimonide (Sb) quantum-well MOSFETs are demonstrated with an integrated high- $\kappa$  dielectric (1-nm Al<sub>2</sub>O<sub>3</sub>/10-nm HfO<sub>2</sub>). The effect of interface trap density  $D_{\rm it}$ on the dc drive current and transconductance  $g_m$  is studied in detail using split C-V/G-V, pulsed I-V, and radio-frequency measurements. Pulsed I-V measurements show improved ON current, transconductance, and subthreshold slope due to reduced charge trapping in the dielectric at high frequencies. The long-channel Sb nMOSFET exhibits effective electron mobility of 6000 cm<sup>2</sup>/V · s at high field (2 × 10<sup>12</sup>/cm<sup>2</sup> of charge density  $N_s$ ), which is 15× higher than Si NMOS inversion layer mobility, and one of the highest values reported for III–V MOSFETs. The short-channel Sb nMOSFET ( $L_G = 150$  nm) exhibits a cutoff frequency  $f_T$  of 120 GHz, an  $f_T \times L_G$  product of 18 GHz ·  $\mu$ m, and a source-side injection velocity  $v_{\rm eff}$  of 2.7 × 10<sup>7</sup> cm/s at a drain bias  $V_{\rm DS}$  of 0.75 V and a gate overdrive of 0.6 V.

Index Terms—Antimonide MOSFET, high- $\kappa$  dielectric, InAsSb, interface states.

# I. INTRODUCTION

N antimony-based  $InAs_xSb_{1-x}$  quantum-well (QW) heterostructure with high electron mobility, integrated with high hole mobility strained  $In_xGa_{1-x}Sb$  QW, can potentially enable III–V CMOS and share the same metamorphic buffer on silicon [1]. In this letter, we report  $InAs_{0.8}Sb_{0.2}$  nMOSFETs with an integrated high- $\kappa$  dielectric, which exhibit recordhigh long-channel electron mobility, short-channel electron velocity, and high-frequency small-signal performance. The effect of interface trap density  $D_{it}$ , which degrades the dc drive current and transconductance  $g_m$ , is studied in detail using split C-V/G-V, pulsed I-V, and radio-frequency (RF) measurements.

Manuscript received December 4, 2012; accepted December 21, 2012. Date of publication January 14, 2013; date of current version February 20, 2013. This work was supported by the Focus Center Research Program for Materials, Structures, and Devices sponsored by the Semiconductor Research Corporation and the Defense Advanced Research Projects Agency, and the Office of Naval Research. The review of this letter was arranged by Editor G. (GE) Meneghesso.

A. Ali was with the Pennsylvania State University, University Park, PA 16802 USA. He is now with Intel Corporation, Hillsboro, OR 97124 USA (e-mail: AshkarAli@psualum.com).

H. Madan, M. J. Barth, and S. Datta are with the Pennsylvania State University, University Park, PA 16802 USA.

J. B. Boos and B. R. Bennett are with the Naval Research Laboratory, Washington, DC 20375 USA.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2236881

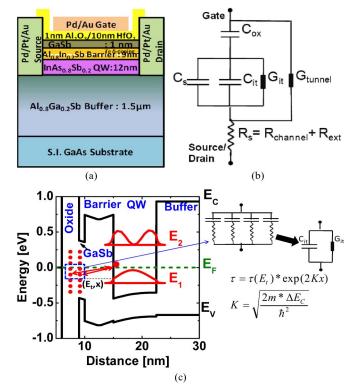

Fig. 1. (a) Schematic of the Sb nMOSFET with a 1-nm Al<sub>2</sub>O<sub>3</sub>/10-nm HfO<sub>2</sub> dielectric. (b) Equivalent-circuit model for the QW MOSFET with traps at the dielectric–GaSb interface:  $C_{\rm ox}$  is the oxide capacitance;  $C_s$  is the semiconductor capacitance, which is the series combination of barrier and QW capacitance values;  $C_{\rm it}$  and  $G_{\rm it}$  are the interface trap capacitance and conductance, respectively;  $G_{\rm tunnel}$  is the leakage conductance; and  $R_s$  is the series resistance. (c) Band diagram under the gate showing traps at the GaSb–dielectric interface exchanging carriers with the QW through tunneling.  $C_{\rm it}$  and  $G_{\rm it}$  are modeled using a distributed network of traps physically extending into the dielectric from the GaSb–dielectric interface.

### II. DEVICE LAYER DESIGN AND FABRICATION

Fig. 1(a) shows the schematic of an InAs<sub>0.8</sub>Sb<sub>0.2</sub> nMOSFET with a 1-nm Al<sub>2</sub>O<sub>3</sub>/10-nm HfO<sub>2</sub> high- $\kappa$  gate dielectric. We obtained Hall mobility of 13 500 cm<sup>2</sup>/V·s at a carrier density of  $2.2 \times 10^{12}$ /cm<sup>2</sup> for the as-grown device layers without the dielectric. The devices were fabricated using a process detailed in [2], with gate lengths of 20  $\mu$ m, 450 nm, 300 nm, and 150 nm.

The equivalent small-signal model for the QW MOSFET is shown in Fig. 1(b). The traps in antimonide MOSFETs not only exist at the interface but also physically extend into the dielectric (border traps) or the transition layer between the high*kappa* dielectric and the antimonide (defect-induced gap states, DIGS). A distributed network of traps physically extending into the dielectric from the GaSb–dielectric interface was used to model the effects of these border traps/DIGS [see Fig. 1(c)].

| <b>Report Documentation Page</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |                              |                         | Form Approved<br>OMB No. 0704-0188          |                         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|-------------------------|---------------------------------------------|-------------------------|--|

| Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number.                                                                                                                                                                      |                               |                              |                         |                                             |                         |  |

| 1. REPORT DATE<br>MAR 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               | 2. REPORT TYPE               |                         | 3. DATES COVE<br>00-00-2013                 | ered<br>3 to 00-00-2013 |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |                              |                         | 5a. CONTRACT NUMBER                         |                         |  |

| Effect of Interface States on the Performance of Antimonide nMOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |                              |                         | 5b. GRANT NUMBER                            |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                              |                         | 5c. PROGRAM ELEMENT NUMBER                  |                         |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                              |                         | 5d. PROJECT NUMBER                          |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                              |                         | 5e. TASK NUMBER                             |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                              |                         | 5f. WORK UNIT NUMBER                        |                         |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>Naval Research Laboratory,Electronic Science and Technology<br>Division,Washington,DC,20375                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                              |                         | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER |                         |  |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                              |                         | 10. SPONSOR/MONITOR'S ACRONYM(S)            |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                              |                         | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)   |                         |  |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT<br>Approved for public release; distribution unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |                              |                         |                                             |                         |  |

| 13. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                              |                         |                                             |                         |  |

| 14. ABSTRACT<br>Antimonide (Sb) quantum-well MOSFETs are demonstrated with an integrated high-κ dielectric<br>(1-nm Al2O3/10-nm HfO2). The effect of interface trap density Dit on the dc drive current and<br>transconductance gm is studied in detail using split C?V/G?V, pulsed I?V, and radio-frequency<br>measurements. Pulsed I?V measurements show improved ON current, transconductance, and<br>subthreshold slope due to reduced charge trapping in the dielectric at high frequencies. The long-channel<br>Sb nMOSFET exhibits effective electron mobility of 6000 cm2/V ? s at high field (2 ? 1012/cm2 of charge<br>density Ns), which is 15? higher than Si NMOS inversion layer mobility and one of the highest values<br>reported for III?V MOSFETs. The short-channel Sb nMOSFET (LG = 150 nm) exhibits a cutoff frequency<br>fT of 120 GHz, an fT ? LG product of 18 GHz ? μm and a source-side injection velocity veff of 2.7 ?<br>107 cm/s at a drain bias VDS of 0.75 V and a gate overdrive of 0.6 V. |                               |                              |                         |                                             |                         |  |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                              |                         |                                             |                         |  |

| 16. SECURITY CLASSIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17. LIMITATION OF<br>ABSTRACT | 18. NUMBER                   | 19a. NAME OF            |                                             |                         |  |

| a. REPORT<br>unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | b. ABSTRACT<br>unclassified   | c. THIS PAGE<br>unclassified | Same as<br>Report (SAR) | OF PAGES<br>3                               | RESPONSIBLE PERSON      |  |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std Z39-18

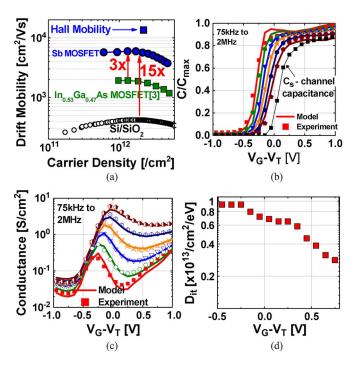

Fig. 2. (a) Extracted electron drift mobility versus  $N_s$  showing record high mobility. (b) and (c) Measured split C-V/G-V characteristics along with self-consistently modeled C-V/G-V based on the equivalent-circuit method. The value of  $C_{\rm ox}$  used for the modeling is 2.3  $\mu$ F/cm<sup>2</sup>, and  $C_{\rm max}$  is 0.8  $\mu$ F/cm<sup>2</sup>. (d)  $D_{\rm it}$  extracted from self-consistent equivalent-circuit modeling of C-V/G-V.

# III. EQUIVALENT-CIRCUIT MODELING AND INTERFACE STATE CHARACTERIZATION

The equivalent-circuit modeling technique relies on selfconsistently solving the capacitance and conductance contributions from interface states, without needing information about the location of conductance peaks. The fitting procedure minimizes the error between the measured admittance (C-V) and G-V) and the simulated admittance for the device over the entire frequency range while solving for  $D_{it}$ , the trap time constant, and the semiconductor capacitance. The procedure is explained in detail in our earlier publication [4]. Traps extending until 1 nm deep into the oxide/transition layer have been considered for the C-V/G-V model, with the trap profile exponentially decaying into the oxide as given by  $N_{\rm it}(x) =$  $N_{\rm it}(0) \exp(-x/x_{\rm DIGS})$  [5]. The characteristic decay length  $x_{\text{DIGS}}$  was used as a fitting parameter and was defined to be 1 Å for this modeling. As traps extend into the oxide, their response time exponentially increases as  $\tau = \tau_0(E_t) \exp(2kx)$ , where  $\tau_0(E_t)$  is the response time of traps at x = 0 at a given energy level  $E_t$  [6]. The wave vector for the electrons tunneling from the conduction band in the InAsSb QW to the traps at the GaSb/high- $\kappa$  dielectric interface  $(k = \sqrt{2m * \Delta Ec/\hbar^2})$  is estimated to be  $\sim 0.13$ /Å using  $\Delta Ec = 1.3$  eV [5], [6]. The effect of these traps on the electron mobility is studied next using detailed split C-V/G-V modeling.

Fig. 2(a) shows the electron drift mobility extracted from the output conductance and measured C-V characteristics. We report a record-high effective electron mobility value of  $6000 \text{ cm}^2/\text{V} \cdot \text{s}$  at  $2 \times 10^{12}/\text{cm}^2$  of  $N_s$ , which is  $15 \times$  higher than Si NMOS inversion layer mobility and  $3 \times$  higher than that of InGaAs NMOS [3]. The extracted drift mobility is

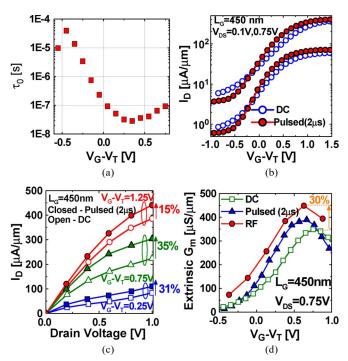

Fig. 3. (a) Response time of the traps at the GaSb/high- $\kappa$  dielectric interface at x = 0 extracted from self-consistent equivalent-circuit modeling of C-V/G-V. (b) Pulsed  $I_D-V_G$  measurements showing improved  $I_{\rm ON}$  and subthreshold slope compared with dc. (c) Pulsed  $I_D-V_D$  characteristics showing significant enhancement in  $I_{\rm ON}$  over dc. (d) Extrinsic RF  $g_m$  showing 30% enhancement over dc  $g_m$  due to less charge trapping in RF.

lower than the Hall mobility partly due to the overestimation of charge from split C-V measurements due to the effect of interface states  $D_{it}$ . Fig. 2(b) and (c) shows the measured split C-V/G-V characteristics of the  $L_G = 20 \ \mu m$  device. The frequency dispersion in the C-V/G-V characteristics is due to  $D_{\rm it}$ . The measured C-V and G-V data are modeled using the equivalent-circuit method in [4] based on the model in Fig. 1(b), including the effects of border traps [5]-[7]. The measured and modeled C-V/G-V curves are in excellent agreement with each other, as shown in Fig. 2(b) and (c). Fig. 2(d) shows the extracted  $D_{it}$  from the equivalent-circuit modeling. The  $D_{it}$ shown in Fig. 2(d) is the net integral of traps at the GaSb/high- $\kappa$  dielectric interface (interface traps) and those extending into the oxide (border traps) at a given energy level. Charging and discharging of interface traps give rise to stretch out in the measured split C-V. Hence, the inversion charge obtained from the measured C-V is overestimated, resulting in a lower value for drift mobility obtained using output conductance  $q_{\rm DS}$  and  $N_s$  from split C-V.

Fig. 3(a) shows the trap time constant extracted from the C-V/G-V modeling. The time constant shown in Fig. 3(a) is the response time of the traps at the GaSb/high- $\kappa$  dielectric interface at x = 0 ( $\tau_0$ ). At each gate bias, the time constant of the traps would follow  $\tau = \tau_0(E_t) \exp(2kx)$ , and the trap density follows  $N_{it}(x) = N_{it}(0) \exp(-x/x_{\text{DIGS}})$ , depending on the depth x. The net trap response would then be driven by the physical depth of the traps into the oxide,  $\tau(x)$ , and  $N_{it}(x)$ . To demonstrate the impact of traps on the device performance, pulsed I-V measurements (2- $\mu$ s pulsewidth) and RF measurements were performed. Pulsed measurements show a significant improvement (by 35% at a 0.75-V gate overdrive)

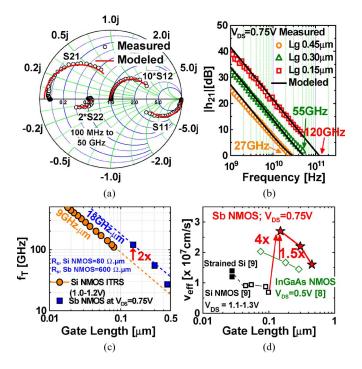

Fig. 4. (a) Measured and modeled S-parameters of the 150-nm  $L_G$  Sb NMOS at  $V_G - V_T = 0.6$  V and  $V_{\rm DS} = 0.75$  V. (b) Measured and modeled  $|h_{21}|$ . (c)  $f_T$  versus  $L_G$ . (d) Extracted source injection velocity.

in  $I_{\rm ON}$  and subthreshold slope [see Fig. 3(b) and (c)] of these devices compared with the dc measurements. The 35% gain in the ON-state current measured at a high overdrive indicates that majority of the traps contributing to drive degradation exist deeply within the oxide and have time constants > 2  $\mu$ s. Fig. 3(d) shows extrinsic  $g_m$  comparing dc, pulsed I-V, and RF measurements. Peak extrinsic RF  $g_m$  improves by 30% compared with dc  $g_m$  for a gate overdrive of 0.6 V. This improvement is due to reduced charge trapping in the dielectric at very high frequencies. This confirms that the reduction in FET mobility compared with Hall mobility is partly due to the overestimation of charge from split C-V, and the actual electron mobility in the Sb MOSFET should be higher than the measured dc value of 6000 cm<sup>2</sup>/V · s.

# IV. RF CHARACTERIZATION

Fig. 4(a) shows the measured and modeled scattering parameters (S-parameters) of the 150-nm  $L_G$  device from 100 MHz to 50 GHz. An excellent agreement between the measured and simulated S-parameters confirms the extracted circuit element values. Fig. 4(b) shows the measured and modeled small-signal current gain  $|h_{21}|$  versus frequency for  $L_G = 150$ , 300, and 450 nm. The devices have cutoff frequencies of 120, 55, and 27 GHz, respectively. From the extracted parameters from small-signal modeling, we evaluate the source-side injection velocity  $v_{\text{eff}}$  of these devices as  $g_m/\text{slope}$  ( $C_{qs}$  versus  $L_G$ ). Fig. 4(c) and (d) benchmarks the  $f_T$  and  $v_{\rm eff}$  of the Sb NMOS devices with state-of-the-art Si and III–V NMOS. The 150-nm  $L_G$  Sb NMOS exhibits a  $v_{\rm eff}$  of 2.7 × 10<sup>7</sup> cm/s and an  $f_T \times L_G$  product of 18 GHz ·  $\mu$ m. The measured  $f_T$  and  $f_T \times L_G$  are 2× higher, and  $v_{\rm eff}$  is 4× higher than Si NMOS (1.0–1.2 V  $V_{\rm DD}$ ) at similar  $L_G$ .

### V. CONCLUSION

Long-channel Sb NMOS devices are demonstrated with high field effective electron mobility of 6000 cm<sup>2</sup>/V · s. Shortchannel Sb NMOS devices exhibit a cutoff frequency  $f_T$  of 120 GHz, an  $f_T \times L_G$  product of 18 GHz ·  $\mu$ m, and a sourceside injection velocity  $v_{eff}$  of 2.7 × 10<sup>7</sup> cm/s at 0.75-V  $V_{DS}$  and 0.6-V gate overdrive. The measured  $f_T$  and  $f_T \times L_G$  are 2× higher, whereas  $v_{eff}$  is 4× higher than Si NMOS (1.0–1.2 V  $V_{DD}$ ). The 150-nm  $L_G$  device exhibits a drive current of 450  $\mu$ A/ $\mu$ m at  $V_{DS}$  of 0.75 V. Charging and discharging of  $D_{it}$  give rise to stretch out in the measured split C-V curves, resulting in a lower value for extracted drift mobility. Pulsed I-V and RF measurements show enhanced  $I_{ON}$ , subthreshold slope, and  $g_m$  compared with dc measurements due to reduced trap charging effects at high frequencies.

### REFERENCES

- M. K. Hudait, S. Datta, J. T. Kavalieros, M. L. Doczy, and R. S. Chau, "Sb-based CMOS devices," U.S. Patent 7 429 747, Sep. 30, 2008.

- [2] A. Ali, H. Madan, A. Agrawal, I. Ramirez, R. Misra, J. B. Boos, B. R. Bennett, J. Lindemuth, and S. Datta, "Enhancement-mode antimonide quantum-well MOSFETs with high electron mobility and gigahertz smallsignal switching performance," *IEEE Electron Device Lett.*, vol. 32, no. 12, pp. 1689–1691, Dec. 2011.

- [3] S. H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, "Enhancement technologies and physical understanding of electron mobility in III–V n-MOSFETs with strain and MOS interface buffer engineering," in *Proc. IEDM*, Dec. 2011, pp. 13.4.1–13.4.4.

- [4] A. Ali, H. Madan, S. Koveshnikov, S. Oktyabrsky, R. Kambhampati, T. Heeg, D. Schlom, and S. Datta, "Small-signal response of inversion layers in high-mobility In<sub>0.53</sub>Ga<sub>0.47</sub> As MOSFETs made with thin high-κ dielectrics," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 742–748, Apr. 2010.

- [5] K. Iizuka, T. Hashizume, and H. Hasegawa, "Small-signal response of interface states at passivated InGaAs surfaces from low frequencies up to microwave frequencies," *Solid State Electron.*, vol. 41, no. 10, pp. 1463– 1468, Oct. 1997.

- [6] F. P. Heiman and G. Warfield, "The effects of oxide traps on the MOS capacitance," *IEEE Trans. Electron Devices*, vol. ED-12, no. 4, pp. 167– 178, Apr. 1965.

- [7] H. Preier, "Contributions of surface states to MOS impedance," *Appl. Phys. Lett.*, vol. 10, no. 12, pp. 361–363, Jun. 1967.

- [8] M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, "Advanced high-κ gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications," in *Proc. IEDM*, 2009, pp. 1–4.

- [9] D. A. Antoniadis and A. Khakifirooz, "MOSFET performance scaling: Limitations and future options," in *Proc. IEDM*, 2008, pp. 1–4.