### Operating System Support for Shared Hardware Data Structures

#### by Gedare Bloom

B.S. in Computer Science and Mathematics, May 2005, Michigan Technological University M.S. in Computer Science, August 2012, The George Washington University

#### A Dissertation submitted to

the Faculty of School of Engineering and Applied Science of The George Washington University in partial satisfaction of the requirements for the degree of Doctor of Philosophy

January 31, 2013

Dissertation directed by

Bhagirath Narahari

Professor of Engineering and Applied Science and of Engineering Management & Systems

Engineering

and

Rahul Simha

Professor of Engineering and Applied Science

| Report Docume                                                                                                                                                                                                                                                                                                                                                                                           | entation Page                                                                                                                                                                                                                                                                                                  | Form Approved<br>OMB No. 0704-0188                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for the collection of information is estimated to maintaining the data needed, and completing and reviewing the collect including suggestions for reducing this burden, to Washington Headqu VA 22202-4302. Respondents should be aware that notwithstanding at does not display a currently valid OMB control number.                                                          | ion of information. Send comments regarding this burden estimate arters Services, Directorate for Information Operations and Reports                                                                                                                                                                           | or any other aspect of this collection of information,<br>, 1215 Jefferson Davis Highway, Suite 1204, Arlington                                                                                  |

| 1. REPORT DATE 31 JAN 2013                                                                                                                                                                                                                                                                                                                                                                              | 2. REPORT TYPE                                                                                                                                                                                                                                                                                                 | 3. DATES COVERED <b>00-00-2013 to 00-00-2013</b>                                                                                                                                                 |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                | 5a. CONTRACT NUMBER                                                                                                                                                                              |

| <b>Operating System Support for Shared</b>                                                                                                                                                                                                                                                                                                                                                              | Hardware Data Structures                                                                                                                                                                                                                                                                                       | 5b. GRANT NUMBER                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                | 5c. PROGRAM ELEMENT NUMBER                                                                                                                                                                       |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                | 5d. PROJECT NUMBER                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                | 5e. TASK NUMBER                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                | 5f. WORK UNIT NUMBER                                                                                                                                                                             |

| 7. PERFORMING ORGANIZATION NAME(S) AND AE The George Washington University,Fa Applied Science,Washington,DC,20052                                                                                                                                                                                                                                                                                       | culty of School of Engineering and                                                                                                                                                                                                                                                                             | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                                                                                                                                                      |

| 9. SPONSORING/MONITORING AGENCY NAME(S) A                                                                                                                                                                                                                                                                                                                                                               | ND ADDRESS(ES)                                                                                                                                                                                                                                                                                                 | 10. SPONSOR/MONITOR'S ACRONYM(S)                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)                                                                                                                                                        |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT Approved for public release; distribution                                                                                                                                                                                                                                                                                                                       | on unlimited                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |

| 13. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

| A fundamental problem in computing utilized. Architecture features like cachenefit software with temporal or spat that relies on fine-grained access to darkerives little benefit from these features approach to improve memory performs structure with operations that leverage times, but only supports an exclusive dethesis proposes operating system (OS) even when its capacity is less than the | he, prefetching, out-of-order execution locality, or instruction-level or tast with structural locality, such as poss. The importance of these data structure. A hardware data structure (He parallelism and structural locality that structure small enough to fit the support for HWDSs so that application. | on, and multiprocessing only sk-level parallelism. Software inter-based data structures, ctures motivates a new WDS) implements a data o reduce data structure access capacity of the HWDS. This |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

c. THIS PAGE

unclassified

16. SECURITY CLASSIFICATION OF:

b. ABSTRACT

unclassified

a. REPORT

unclassified

17. LIMITATION OF ABSTRACT

Same as

Report (SAR)

18. NUMBER OF PAGES

137

19a. NAME OF RESPONSIBLE PERSON The School of Engineering and Applied Science of The George Washington University certifies that Gedare Bloom has passed the Final Examination for the degree of Doctor of Philosophy as of November 19, 2012. This is the final and approved form of the dissertation.

### Operating System Support for Shared Hardware Data Structures

#### Gedare Bloom

#### Dissertation Research Committee:

Bhagirath Narahari, Professor of Engineering and Applied Science and of Engineering Management & Systems Engineering, Dissertation Co-Director Rahul Simha, Professor of Engineering and Applied Science, Dissertation Co-Director Gabriel Parmer, Assistant Professor of Computer Science, Committee Member Evan Drumwright, Assistant Professor of Computer Science, Committee Member Guru Prasadh Venkataramani, Assistant Professor of Engineering and Applied Science, Committee Member

© Copyright 2013 by Gedare Bloom All Rights Reserved

# Dedication

For my grandfather Laird, who inspired me to seek higher education.

For my wife Veronica, who inspires me to better myself.

For my daughter Annalise, who inspires me to better the world.

# Acknowledgments

Thank you Veronica, for challenging me to improve in all aspects of life. I love you.

No one is an island. I am grateful for all the assistance I have received throughout my life. A dissertation is the culmination of a long journey, an epic quest of self-discovery that starts when the young mind is planted with the seed of introspection. Along the way, many hands help to sow the seed and till its soil, and to the people whose hands have helped me, I am grateful.

To my parents, Uno and Jodi, for encouraging academic success, praising hard work and good grades, permitting my obsessive reading, and for chasing their dreams. To my siblings, Jeni and Adam for enduring and passing lessons learned, and to Ric and Ben for following and providing me with retrospective. To my grandparents, Laird and Marcia Heal, Elsa Bloom, and Beulah Huff, whose memories I treasure, for instilling in me the virtue of being studious, wholesome, and hard-working: mens sana in corpore sano.

To my aunts and uncles: to Dicky for embodying sisu; to Sandy Martin for introducing me to science, to Kathy Soderbloom for a larger world of politics and religion, to Diana Anderson for intellectual challenges and inspirations; to David, Andy, and Loren Heal for introducing the digital world to me, to Bud Heal for maintaining some of the old world, and to Kim Rosser, who always seems positive to me.

To all the wonderful teachers and professors who are *there* for their students.

To Mrs. Weber, my 5th grade science teacher who first introduced me to controlled scientific experimentation.

To Mr. Wang, my 7th and 8th grade math teacher, for seeing in me a skill for math

and encouraging me to develop it beyond the course material, and for the occasional pickup basketball game, in which I got to socialize with a teacher outside the confines of the classroom—a new development.

To Mr. Stelmaszak, my affable but demanding Calculus teacher, for encouraging students to think about and prepare for the future.

To Mr. Kedigh, for introducing me to programming and computer science.

To Dr. Dave Poplawski, for sponsorship of the student ACM and programming competitions at Michigan Tech.

To Dr. Steve Seidel, for introducing me to the world of research and academe through the MTU UPC seminar.

To Dr. Soner Önder, for teaching me enough of compilers and architecture that I have hardly needed a book or refresher since, a truly amazing skill of a great teacher; I will always remember that I "cannot bribe God."

To Dr. Abdou Youssef, for being an inspiration both in the classroom and out.

To Dr. Poorvi Vora, for your passion for students and teaching.

To Dr. Jonathan Stanton, for introducing me to the world of systems and some of the realities of academic life.

To my advisors, Bhagi and Rahul, for taking me under wing and giving me the freedom to explore.

To Stefan Popoveniuc, for being a great sounding board and working with me on my first paper.

To Eugen Leontie, for being in the trenches with me; our successes have been great and I am glad to have worked with you.

To Joe Zambreno, for useful advice about my career and research. You have helped me to see the world through a different lens.

To Gabe Parmer, for your excitement and input about my research. Our conversations about systems has been great for my intellectual growth.

To Guru, you endorsed my work when I was uncertain in the early stages, which helped me to stay positive and on track.

Friends have a lot to do with how a mind is shaped and grows. Some friends grow and learn with you, teach you, and inspire you to work hard: Dan Mayo, thank you for being such a friend—I am better for having known you.

To Rob Weller, Brandon Wilson, and David Deane, for the boring nights and the exciting, for inviting me out despite my proclivity toward unpredictability and wildness.

To Dan Clark, Justin Ter Avest, and Adam Shirey for 8.31 and all the rest.

To Joe Vaillancourt, for helping to drag me along at times.

To Nick Young and Jeremy Koenen, for broomball, sake, and puyo puyo.

To my friends in grad school who helped lessen some of the burdens of graduate student life, thank you Darby Thompson, Rim Yazigi, Darakshan Mir, Kevin Henry, Amin Teymorian, Liran Ma, Kerry McKay, and Olga Gelbart.

To my lab mates Scotty Smith and James Marshall, for attending more than their share of presentations on my work, and to James for encouraging me to ride my bicycle more, and Scotty for putting up with our bicycle talk.

To the great folks who work with RTEMS, especially Joel Sherrill, Chris Johns, and Sebastian Huber, for the support over the past few years.

To Gary Kreger and Curtis Schoolman, for teaching me that working hard is just working.

To my department and university, and to industry and government for funding my research directly and indirectly through grants, fellowships, and awards. My academic career so far has been supported in part by Hewlett-Packard (through the MTU UPC), the

US National Science Foundation (NSF grants CNS-1117243, CNS-0934725, ITR-025207, CNS-0831149), the Air Force Office of Scientific Research (AFOSR grants FA9550-09-1-0194 and FA955006-1-0152), and the George Washington University (teaching fellowships, travel awards, and summer dissertation fellowship).

To the rest, for surely I missed some, I give thanks.

Surely there must be a less primitive way of making big changes in the [memory] store than by pushing vast numbers of words back and forth through the von Neumann bottleneck. Not only is this tube a literal bottleneck for the data traffic of a problem, but, more importantly, it is an intellectual bottleneck that has kept us tied to word-at-a-time thinking instead of encouraging us to think in terms of the larger conceptual units of the task at hand. Thus programming is basically planning and detailing the enormous traffic of words through the von Neumann bottleneck, and much of that traffic concerns not significant data itself but where to find it.

— John Backus, 1977

Advances in microelectronics have made the realization of "smart" data structures a practical reality.

— Charles Leiserson, 1979

Indeed, I believe that virtually *every* important aspect of programming arises somewhere in the context of sorting or searching!

— Don Knuth

${\bf Sisu.}$

### Abstract of Dissertation

### Operating System Support for Shared Hardware Data Structures

A fundamental problem in computing is that processors cannot access memory fast enough to stay fully utilized. Architecture features like cache, prefetching, out-of-order execution, and multiprocessing only benefit software with temporal or spatial locality, or instruction-level or task-level parallelism. Software that relies on fine-grained access to data with structural locality, such as pointer-based data structures, derives little benefit from these features. The importance of these data structures motivates a new approach to improve memory performance. A hardware data structure (HWDS) implements a data structure with operations that leverage parallelism and structural locality to reduce data structure access times, but only supports an exclusive data structure small enough to fit the capacity of the HWDS. This thesis proposes operating system (OS) support for HWDSs so that applications can use and share a HWDS even when its capacity is less than the data structure's size.

The priority queue and map data structures demonstrate the appeal of an OS-HWDS union. A GPS benchmark with real-world data executes 24% faster using a HWDS instead of a software data structure, even though the data exceeds the hardware's capacity. Compared to software implementations, a 128-node HWDS achieves over 50% faster mean access time to a 512-node priority queue, and 15% faster mean search time in a 512-node read-mostly map. When sharing a HWDS among four maps of power-of-2 sizes between 64 and 512, a 128-node HWDS achieves 35% faster searches than a splay tree. These performance improvements are made possible by the OS support for HWDSs proposed in this thesis.

# Table of Contents

| D             | edica  | ation                                         | iv           |

|---------------|--------|-----------------------------------------------|--------------|

| A             | ckno   | wledgments                                    | $\mathbf{v}$ |

| A             | bstra  | act of Dissertation                           | x            |

| Ta            | able ( | of Contents                                   | xv           |

| $\mathbf{Li}$ | st of  | Figures                                       | xvi          |

| $\mathbf{Li}$ | st of  | Tables                                        | xx           |

| $\mathbf{Li}$ | st of  | Acronyms                                      | xxi          |

| G             | lossa  | ry of Terms                                   | xxii         |

| 1             | Intr   | roduction                                     | 1            |

|               | 1.1    | Impact                                        | 5            |

|               | 1.2    | Overview                                      | 7            |

|               |        | 1.2.1 Overflow handling                       | 9            |

|               |        | 1.2.2 Sharing HWDS resources: HWDS assignment | 9            |

|               | 1.3    | Contributions                                 | 11           |

|               | 1.4    | Scope                                         | 13           |

|               | 1.5    | Outline                                       | 14           |

| 2             | Lite   | erature Review                                | 15           |

|               | 2.1    | Design and Implementation of HWDSs            | 15           |

|     | 2.1.1  | HWDSs for network routing                    | 15 |

|-----|--------|----------------------------------------------|----|

|     | 2.1.2  | HWDSs for real-time scheduling               | 16 |

|     | 2.1.3  | HWDSs for reconfigurable computing with Java | 16 |

|     | 2.1.4  | Systolic Priority Queues                     | 16 |

|     | 2.1.5  | Abstract Datatype Processors                 | 17 |

|     | 2.1.6  | Content-addressable memory (CAM)             | 17 |

|     | 2.1.7  | Scratchpad memory (SPM)                      | 18 |

|     | 2.1.8  | Reconfigurable computing data structures     | 19 |

|     | 2.1.9  | String matching                              | 19 |

| 2.2 | Fine-g | grained Parallelism                          | 19 |

|     | 2.2.1  | Carbon                                       | 20 |

|     | 2.2.2  | Ne-XVP                                       | 20 |

|     | 2.2.3  | Asynchronous Direct Messages                 | 21 |

|     | 2.2.4  | HAQu                                         | 21 |

|     | 2.2.5  | Loop accelerators                            | 22 |

|     | 2.2.6  | Scalable Cores                               | 23 |

| 2.3 | Shipp  | ing Code to Data                             | 23 |

|     | 2.3.1  | Data structure co-processing                 | 23 |

|     | 2.3.2  | Processor-in-memory                          | 24 |

|     | 2.3.3  | Processor-in-disk                            | 24 |

| 2.4 | Linke  | d Prefetching                                | 25 |

| 2.5 | Capal  | bility- and Object-based Systems             | 26 |

| 2.6 | Transa | actional Memory                              | 26 |

| 27  | Summ   | pary of Related Work                         | 27 |

| 3 | $\mathbf{os}$ | Suppo   | ort for HWDSs: Generalities                              | 28 |

|---|---------------|---------|----------------------------------------------------------|----|

|   | 3.1           | Overfl  | ow Handling                                              | 28 |

|   | 3.2           | HWD     | S Assignment                                             | 29 |

|   | 3.3           | Exper   | imental Infrastructure                                   | 31 |

| 4 | Pric          | ority C | Queue HWDS                                               | 32 |

|   | 4.1           | Priori  | ty Queue: an Example HWDS                                | 32 |

|   |               | 4.1.1   | Software priority queues                                 | 33 |

|   |               | 4.1.2   | Hardware priority queues                                 | 34 |

|   | 4.2           | Handl   | ing Overflow with a Priority Queue HWDS                  | 36 |

|   | 4.3           | Exper   | iments                                                   | 37 |

|   |               | 4.3.1   | Discrete event simulation                                | 38 |

|   |               | 4.3.2   | Planning algorithms                                      | 44 |

|   | 4.4           | Summ    | nary                                                     | 49 |

| 5 | Maj           | p HW    | DS                                                       | 50 |

|   | 5.1           | Softwa  | are-based Search                                         | 50 |

|   | 5.2           | Map I   | HWDS                                                     | 51 |

|   |               | 5.2.1   | CAM-based map HWDS                                       | 51 |

|   |               | 5.2.2   | Overflow handling                                        | 52 |

|   |               | 5.2.3   | Least recently used (LRU) spilling and fill-after-search | 52 |

|   |               | 5.2.4   | Size checks                                              | 52 |

|   |               | 5.2.5   | Dynamic eviction                                         | 53 |

|   | 5.3           | Exper   | iments                                                   | 53 |

|   |               | 5.3.1   | Overflow handling for large maps                         | 56 |

|   |               | 5.3.2   | LRU spilling and fill-after-search                       | 57 |

|   |     | 5.3.3             | Eviction                                          | 59 |

|---|-----|-------------------|---------------------------------------------------|----|

|   |     | 5.3.4             | Sharing for multiple maps                         | 60 |

|   | 5.4 | Summ              | ary                                               | 62 |

| 6 | Sha | red H             | WDSs for Hard Real-Time Systems                   | 63 |

|   | 6.1 | Real-t            | ime Considerations for HWDSs                      | 63 |

|   |     | 6.1.1             | Overflow handling                                 | 63 |

|   |     | 6.1.2             | Sharing                                           | 65 |

|   | 6.2 | Respo             | nse Time Analysis                                 | 65 |

|   |     | 6.2.1             | Notation                                          | 65 |

|   |     | 6.2.2             | Standard response time analysis                   | 66 |

|   |     | 6.2.3             | Response time analysis with HWDSs                 | 66 |

|   |     | 6.2.4             | Response time analysis with a priority queue HWDS | 68 |

|   | 6.3 | HWD               | S Assignment for Real-time Systems                | 69 |

|   | 6.4 | Exper             | iments                                            | 72 |

|   |     | 6.4.1             | Schedulability                                    | 74 |

|   |     | 6.4.2             | Real-world Applications                           | 77 |

|   | 6.5 | Summ              | ary                                               | 81 |

| 7 | Fut | ure W             | ork and Conclusion                                | 82 |

|   | 7.1 | Policie           | es for Accessing Memory                           | 82 |

|   | 7.2 | HWD               | S Assignment                                      | 82 |

|   | 7.3 | Data S            | Sharing                                           | 83 |

|   | 7.4 | OS O <sub>l</sub> | ptimizations for HWDSs                            | 83 |

|   | 7.5 | Integr            | ation with Programming Languages and Libraries    | 84 |

|   | 7.6 | Hardw             | vare Improvements                                 | 85 |

|              |       | 7.6.1   | Other HWDSs                         | 85  |   |

|--------------|-------|---------|-------------------------------------|-----|---|

|              |       | 7.6.2   | Improved processor pipeline support | 85  |   |

|              |       | 7.6.3   | HWDS support for instructions       | 85  |   |

|              |       | 7.6.4   | Prefetching                         | 86  |   |

|              |       | 7.6.5   | Multicore considerations            | 87  |   |

|              | 7.7   | Conclu  | usion                               | 87  |   |

| Bi           | bliog | graphy  |                                     | 88  |   |

| $\mathbf{A}$ | STI   | . Profi | ling: Containers and Comparators    | 108 | } |

|              | A.1   | Maps    | in the C++ STL                      | 108 |   |

|              | A.2   | Object  | t comparison code                   | 110 | ı |

|              | A 3   | Summ    | arv                                 | 111 |   |

# List of Figures

| 1-1 | The adv  | vantage of hardware is parallelism                    | 3  |

|-----|----------|-------------------------------------------------------|----|

| 1-2 | Limited  | hardware resources create disadvantages for HWDSs     | 4  |

|     | (a)      | A full HWDS cannot accept new nodes                   | 4  |

|     | (b)      | Data structures cannot share the HWDS                 | 4  |

| 1-3 | Progran  | n code changes when using a HWDS                      | 8  |

|     | (a)      | Insertion code for a software binary heap             | 8  |

|     | (b)      | Insertion code for a priority queue HWDS              | 8  |

| 1-4 | HWDS     | architecture overview                                 | 8  |

|     | (a)      | Computer organization                                 | 8  |

|     | (b)      | Multicore computer organization                       | 8  |

| 1-5 | Handlin  | g limited hardware capacity with HWDSs                | 10 |

|     | (a)      | Spilling to handle overflow                           | 10 |

|     | (b)      | Filling to handle underflow                           | 10 |

| 1-6 | HWDS     | sharing with a HWDS context switch                    | 10 |

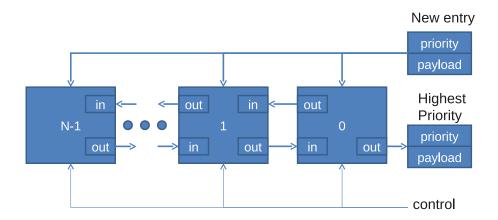

| 4-1 | A priori | ity queue implemented in hardware.                    | 35 |

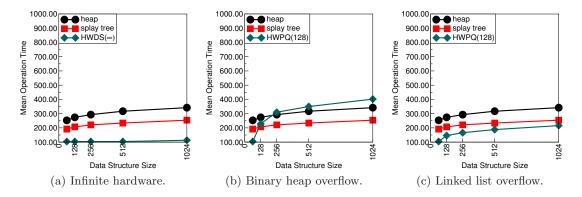

| 4-2 | Overflov | w data structure implementation matters               | 39 |

|     | (a)      | Infinite hardware.                                    | 39 |

|     | (b)      | Binary heap overflow                                  | 39 |

|     | (c)      | Linked list overflow                                  | 39 |

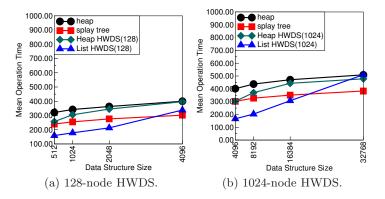

| 4-3 | Overflov | w with 4,096 operations with 128- and 1024-node HWDSs | 40 |

|     | (a)      | 128-node HWDS                                         | 40 |

|     | (b)      | 1024-node HWDS                                        | 40 |

| 4-4 | Priority | queue benchmark with 16 384 hold operations           | 41 |

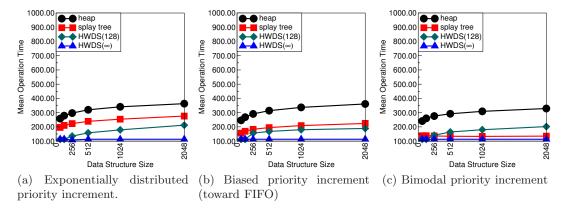

|     | (a)        | Exponentially distributed priority increment                             | 41 |

|-----|------------|--------------------------------------------------------------------------|----|

|     | (b)        | Biased priority increment (toward FIFO)                                  | 41 |

|     | (c)        | Bimodal priority increment                                               | 41 |

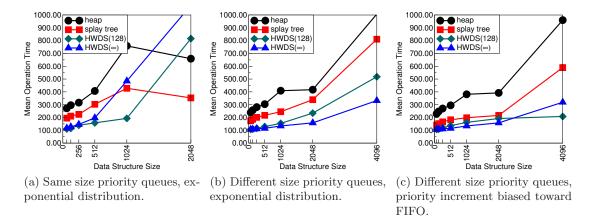

| 4-5 | Four tas   | sks sharing a hardware priority queue with 1024 hold operations          | 42 |

|     | (a)        | Same size priority queues, exponential distribution                      | 42 |

|     | (b)        | Different size priority queues, exponential distribution                 | 42 |

|     | (c)        | Different size priority queues, priority increment biased toward FIFO.   | 42 |

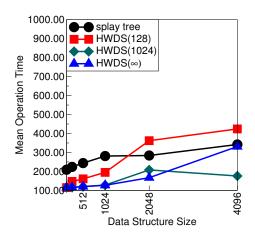

| 4-6 | Multitas   | sk sharing of same-sized priority queues with 4096 hold operations and   |    |

|     | three size | zes of HWDS                                                              | 43 |

| 4-7 | Multitas   | sk sharing of same-sized priority queues with 4096 hold operations and   |    |

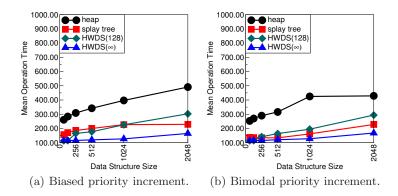

|     | varying    | priority increment distributions                                         | 44 |

|     | (a)        | Biased priority increment                                                | 44 |

|     | (b)        | Bimodal priority increment                                               | 44 |

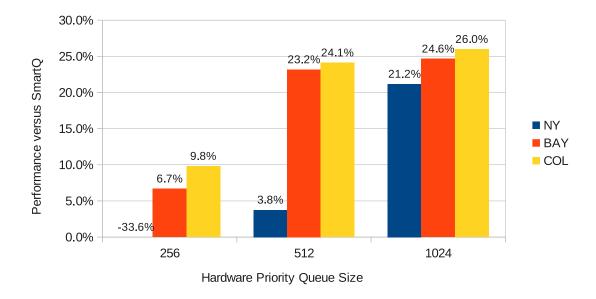

| 4-8 | Perform    | ance of priority queue HWDS on modified DIMACS GPS benchmarks .          | 47 |

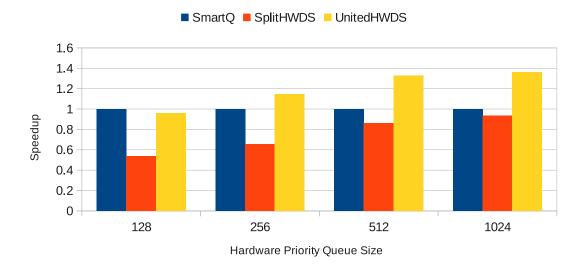

| 4-9 | Compar     | ison of United HWDS with Split HWDS                                      | 48 |

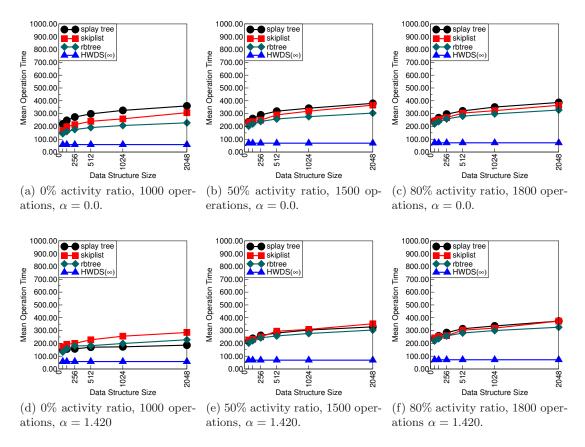

| 5-1 | Infinite   | HWDS and software search results with and without skew                   | 55 |

|     | (a)        | 0% activity ratio, 1000 operations, $\alpha = 0.0.$                      | 55 |

|     | (b)        | 50% activity ratio, 1500 operations, $\alpha = 0.0.$                     | 55 |

|     | (c)        | 80% activity ratio, 1800 operations, $\alpha = 0.0.$                     | 55 |

|     | (d)        | $0\%$ activity ratio, $1000$ operations, $\alpha = 1.420$                | 55 |

|     | (e)        | 50% activity ratio, 1500 operations, $\alpha = 1.420.\dots$              | 55 |

|     | (f)        | 80% activity ratio, 1800 operations $\alpha = 1.420.$                    | 55 |

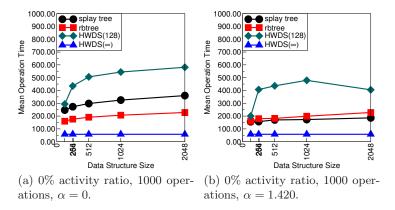

| 5-2 | Overflow   | w handling of search benchmark with extract-last spilling                | 56 |

|     | (a)        | $0\%$ activity ratio, $1000$ operations, $\alpha = 0. \dots \dots \dots$ | 56 |

|     | (b)        | $0\%$ activity ratio, 1000 operations, $\alpha = 1.420, \ldots, \ldots$  | 56 |

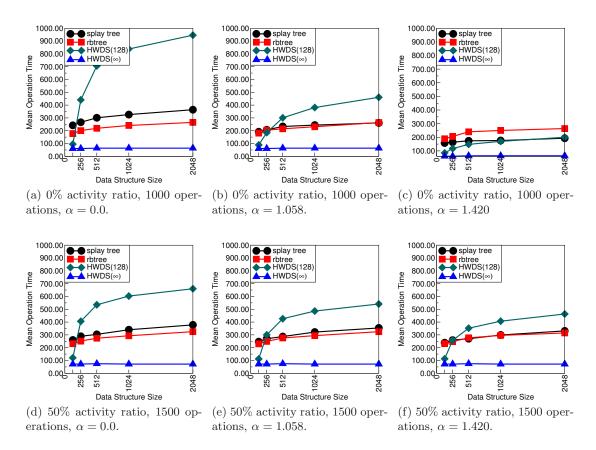

| 5-3 | Map ove  | erflow with LRU and fill-after-search, 1000 search operations             | 57 |

|-----|----------|---------------------------------------------------------------------------|----|

|     | (a)      | 0% activity ratio, 1000 operations, $\alpha = 0.0.$                       | 57 |

|     | (b)      | 0% activity ratio, 1000 operations, $\alpha = 1.058.$                     | 57 |

|     | (c)      | 0% activity ratio, 1000 operations, $\alpha = 1.420 \ldots \ldots \ldots$ | 57 |

|     | (d)      | 50% activity ratio, 1500 operations, $\alpha = 0.0.$                      | 57 |

|     | (e)      | 50% activity ratio, 1500 operations, $\alpha = 1.058.$                    | 57 |

|     | (f)      | 50% activity ratio, 1500 operations, $\alpha = 1.420.\dots$               | 57 |

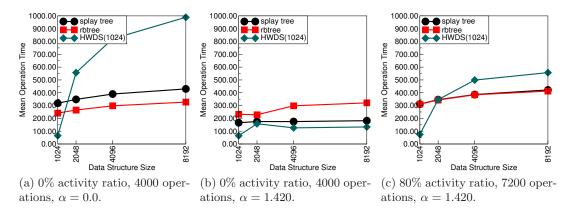

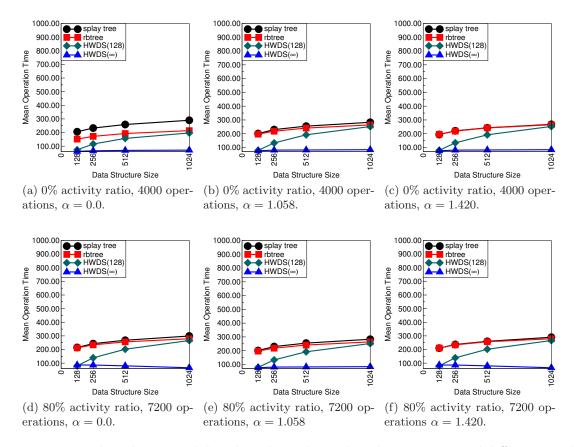

| 5-4 | Map ove  | erflow, 1024-node HWDS, 4000 search operations                            | 58 |

|     | (a)      | 0% activity ratio, 4000 operations, $\alpha = 0.0.$                       | 58 |

|     | (b)      | 0% activity ratio, 4000 operations, $\alpha = 1.420$                      | 58 |

|     | (c)      | 80% activity ratio, 7200 operations, $\alpha = 1.420.\dots$               | 58 |

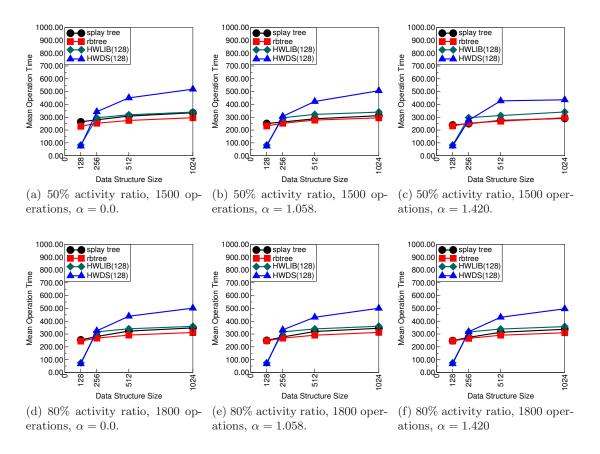

| 5-5 | Map HV   | WDS overflow handling with HWDS assignment to software upon first         |    |

|     | EXTRACT  | Γ                                                                         | 59 |

|     | (a)      | 50% activity ratio, 1500 operations, $\alpha = 0.0.$                      | 59 |

|     | (b)      | 50% activity ratio, 1500 operations, $\alpha = 1.058.$                    | 59 |

|     | (c)      | 50% activity ratio, 1500 operations, $\alpha = 1.420.\dots$               | 59 |

|     | (d)      | 80% activity ratio, 1800 operations, $\alpha = 0.0.$                      | 59 |

|     | (e)      | 80% activity ratio, 1800 operations, $\alpha = 1.058.$                    | 59 |

|     | (f)      | 80% activity ratio, 1800 operations, $\alpha = 1.420$                     | 59 |

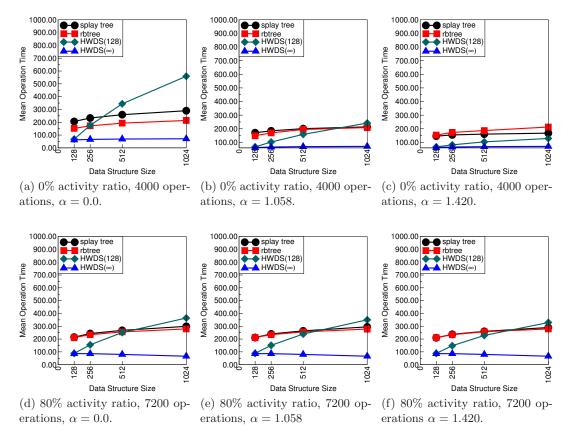

| 5-6 | Multitas | sking search with overflow and different-sized priority queues            | 60 |

|     | (a)      | 0% activity ratio, 4000 operations, $\alpha = 0.0.$                       | 60 |

|     | (b)      | 0% activity ratio, 4000 operations, $\alpha = 1.058$                      | 60 |

|     | (c)      | 0% activity ratio, 4000 operations, $\alpha = 1.420.\dots$                | 60 |

|     | (d)      | 80% activity ratio, 7200 operations, $\alpha = 0.0.$                      | 60 |

|     | (e)      | 80% activity ratio, 7200 operations, $\alpha = 1.058$                     | 60 |

|     | (f)       | 80% activity ratio, 7200 operations $\alpha = 1.420.$                  | 60  |

|-----|-----------|------------------------------------------------------------------------|-----|

| 5-7 | Multitas  | sking search benchmarks with size-based assignment and different-sized |     |

|     | priority  | queues                                                                 | 61  |

|     | (a)       | $0\%$ activity ratio, 4000 operations, $\alpha = 0.0.$                 | 61  |

|     | (b)       | $0\%$ activity ratio, 4000 operations, $\alpha = 1.058$                | 61  |

|     | (c)       | $0\%$ activity ratio, 4000 operations, $\alpha = 1.420.\dots$          | 61  |

|     | (d)       | 80% activity ratio, 7200 operations, $\alpha = 0.0.$                   | 61  |

|     | (e)       | 80% activity ratio, 7200 operations, $\alpha = 1.058$                  | 61  |

|     | (f)       | 80% activity ratio, 7200 operations $\alpha = 1.420.$                  | 61  |

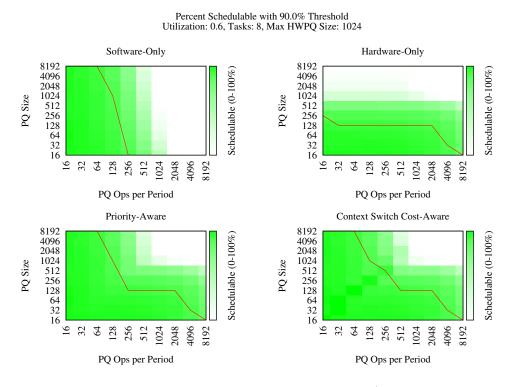

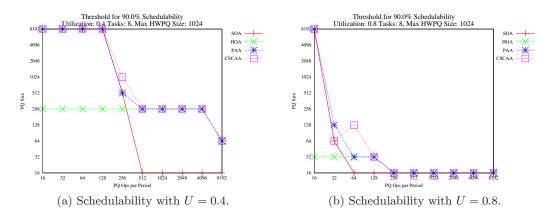

| 6-1 | Schedul   | ability of random task sets with HWDSs                                 | 75  |

| 6-2 | Schedul   | ability of random task sets as utilization changes                     | 76  |

|     | (a)       | Schedulability with $U=0.4.$                                           | 76  |

|     | (b)       | Schedulability with $U=0.8.$                                           | 76  |

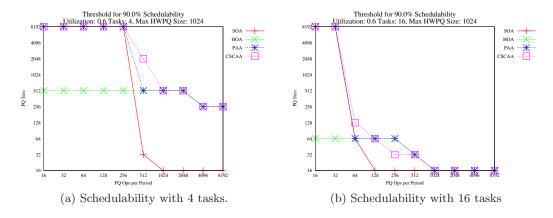

| 6-3 | Schedul   | ability of random task sets as number of tasks changes                 | 77  |

|     | (a)       | Schedulability with 4 tasks                                            | 77  |

|     | (b)       | Schedulability with 16 tasks                                           | 77  |

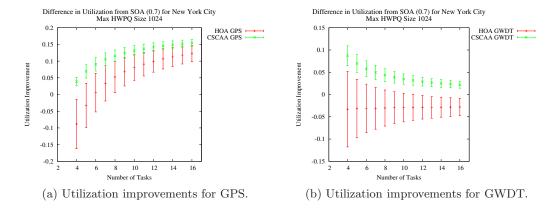

| 6-4 | Utilizati | ion improvements for GPS and GWDT applications                         | 80  |

|     | (a)       | Utilization improvements for GPS                                       | 80  |

|     | (b)       | Utilization improvements for GWDT                                      | 80  |

| A-1 | observe   | ers man consumes 3.5% of Chromium startup/shutdown time                | 111 |

# List of Tables

| 4-1 | Priority queue behavior in selected DIMACS GPS benchmarks | 46  |

|-----|-----------------------------------------------------------|-----|

| 6-1 | Priority queue behavior in real-world applications        | 79  |

| A-1 | STL container use of 21 open-source C++ programs          | 108 |

| A-2 | STL map use profiling                                     | 109 |

# List of Acronyms

**API:** application programming interface

**BST:** binary search tree

CAM: content-addressable memory

CSCAA: context switch cost-aware assignment

**FIFO:** first-in, first-out

**HOA:** hardware-only assignment

**HWDS:** hardware data structure

I/O: input/output

**ISA:** intruction set architecture

LIFO: last-in, first-out

LRU: least recently used

**OS:** operating system

PAA: priority-aware assignment

RAM: random-access memory

RC: reconfigurable computing

RTEMS: Real-Time Executive for Multiprocessor Systems

RTOS: real-time operating system

${f SOA:}$  software-only assignment

**SPM:** scratchpad memory

STL: Standard Template Library

**TLB:** translation lookaside buffer

**TLP:** task-level parallelism (or thread-level parallelism)

TM: transactional memory

VMA: virtual memory address

WCET: worst-case execution time

# Glossary of Terms

**container:** An abstract data type in the C++ STL.

- exception-based HWDS: A HWDS that permits direct access but raises exceptions when the HWDS cannot satisfy a request. See also: interposition-based HWDS.

- heap: A data structure containing key-value pairs that orders nodes within a tree according to a rule that a parent node's key is greater than or equal (equivalently less than or equal for a max heap) to its children nodes' keys. See also: priority queue.

- **HWDS assignment:** Problem of determining whether a data structure uses a HWDS or a software implementation.

- **HWDS context:** HWDS registers and data associated with a data structure. See also: HWDS context switch

- **HWDS context switch:** Saving one HWDS context and restoring another. See also: HWDS context.

- interposition-based HWDS: A HWDS that is accessed through a software library which avoids making invalid requests to the HWDS by checking every access. See also: exception-based HWDS.

- locality: The tendency of memory accesses to occur in clusters. See also: spatial locality, structural locality, temporal locality.

- map: A data structure that contains key-value pairs and supports an efficient mechanism to lookup (search) nodes by key. Also known as: associative array, dictionary, or search tree.

- multitasking: OS-mediated processor sharing for multiple execution contexts. See also: scheduler, task, thread.

- **node:** A storage unit for a data structure comprising one or more data and link (pointer) fields.

- **priority queue:** A data structure that contains key-value pairs sorted by a priority stored in the key.

- red-black tree: A balanced tree data structure named for the node coloring rules that ensure a bounded height imbalance. See also: map

- scheduler: Entity that controls access to hardware resources. Commonly used for sharing processor time or access to devices.

- simultaneous multithreading: Hardware-supported processor sharing for multiple execution contexts simultaneously in parallel. See also: thread, multitasking.

- **skip list:** A list-of-lists data structure that stores all nodes in the last (bottom) list, and the number of links (height) any given node has is randomized. *See also: map*

- **spatial locality:** Tendency of memory accesses to be located near each other in the memory address space. *See also: locality.*

- **splay tree:** A self-adjusting binary search tree named for the splay operation, which moves recently accessed nodes to the root for faster access. *See also: map.*

- **split HWDS:** HWDS that uses an overflow data structure which ignores the mechanisms of the HWDS. See also: united HWDS.

- **stable:** A property of a priority queue or map data structure that dequeues of nodes of the same key is in FIFO order.

**structural locality:** Tendency of memory accesses to follow an ordered pattern. *See also:* locality.

task: A schedulable software execution context. Also known as: thread or process.

temporal locality: Tendency of recent memory accesses to recur. See also: locality.

thread: execution context. See also: simultaneous multithreading, task.

united HWDS: HWDS that uses an overflow data structure which relies on the HWDS to improve performance. See also: split HWDS.

**Zipf's distribution:** A skewed probability distribution generated with Zipf's law, which states the probability the i'th key out of n keys will be accessed is inversely proportional to i.

# Chapter 1 – Introduction

Throughout the history of computing, processors have outperformed main memory [130]. Indeed, the performance gap has steadily increased since the 1980s, leading Wulf and Mc-Kee [136] to coin the term *memory wall* to describe the bottleneck caused by the gap. The memory wall arises from processor performance improving faster than memory bandwidth and latency.

One technique to delay the impact of the memory wall is caching. But even with an infinite size cache that (pre)fetches data at full memory bandwidth, the gap between processor speed and bandwidth means cache misses are inevitable—enough data cannot move into the cache fast enough to satisfy the processor. When the cache misses, the memory access time depends on latency to get the first byte, and bandwidth to get the rest. Patterson [99] states that latency lags bandwidth: a historical trend indicates that latency improves slower than bandwidth. Yet latency dominates bandwidth in determining the performance of memory accesses for small sizes, such as a cache line. Poor memory latency means that cache misses become more expensive relative to processor cycle times as technology improves. Ten years ago, a 1 GHz processor with DDR-200 RAM had a memory latency around 52 CPU cycles. Five years ago, a 4 GHz processor with DDR2-800 RAM had a memory latency around 220 CPU cycles.

Meanwhile Moore's law abides: a prediction that a new chip can be produced with double the transistors—potential performance—compared with chips made less than two years prior. As transistor density increases, power and heat dissipation has become a critical factor in chip design and manufacture. The answer from the architecture community has been the chip multiprocessor, or multicore: Excess transistors are devoted either to increased cache or to more processing cores. A fundamental assumption of multicore is

that applications can or will exploit sufficient parallelism among multiple cores to achieve speedup. Unfortunately, parallel programming remains hard, despite years of research that has yielded promising technologies such as transactional memory [54] and lock-free data structures [32]. While multicore processors delay the growing gap between latency and performance by processing at lower frequencies, latency still dominates bandwidth, and the memory wall remains.

Scaling the memory wall drives research in both computer architecture and compilers. Computer architects introduced hardware prefetching to reduce miss rates, and techniques to hide cache misses when sufficient work is available—for example non-blocking cache, out-of-order execution, and *simultaneous multithreading*. Compilers play a role in controlling how software accesses the cache and can reduce miss rates using techniques such as software prefetching, instruction reordering, memory compaction, and loop optimizations. Most compiler solutions work well on statically known or easily profiled applications such as software with bounded loops and fixed-size arrays. But many high-level programs are written in terms of data structure (or object) operations and interfaces, and not in terms of loops and arrays.

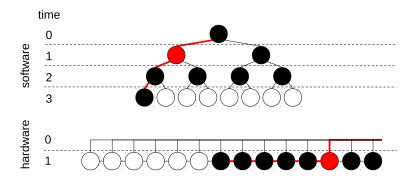

This thesis improves the state-of-the-art by supporting the use of excess transistors to improve application performance through a fundamental programming construct that spans both processor and memory: the data structure. A hardware data structure (HWDS) is an implementation of a data structure that is supported by hardware mechanisms to improve data structure operations. By organizing the memory hierarchy in terms of data structure operations, instead of cache line fetches, HWDSs permit rethinking how processors access memory. More important, hardware mechanisms exploit parallelism to reduce the algorithmic complexity of data structure operations, which can yield substantial performance benefits compared with software implementations; see Figure 1-1, which shows how

Figure 1-1: The advantage of hardware is parallelism. Here, an insert in a software binary search tree requires traversing at most the entire depth of the tree, whereas hardware can insert in two steps by broadcasting and comparing the new value in parallel.

hardware can insert to a sorted structure faster than software because of the advantage of parallel comparisons.

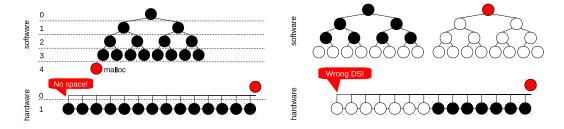

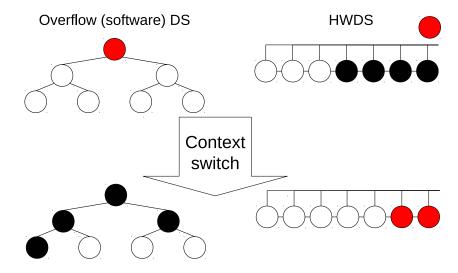

HWDSs are not without disadvantages however, most of which stem from limited hardware resources. Chip space allocated to the HWDS steals from other features such as cache and on-chip communications, so minimizing the HWDS size is important. The main disadvantage of HWDSs is the limited hardware capacity that can be devoted to supporting data structure operations; see Figure 1-2a. Limited hardware capacity precludes using one HWDS for each software data structure, so sharing the HWDS resources in *multitasking* environments is important; see Figure 1-2b, which depicts two data structures attempting to use a HWDS simultaneously. The *HWDS context* is the set of control registers and data belonging to the data structure that is loaded in a HWDS.

Hardware support for specific data structures has been proposed in the past (see Chapter 2), but so far the interface between the HWDS and programmer has been ignored. Most existing HWDSs have limited interactions with operating system (OS) and application software, with much of the prior work allowing only one data structure with a known

- (a) A full HWDS cannot accept new nodes.

- (b) Data structures cannot share the HWDS.

Figure 1-2: Limited hardware resources create disadvantages for HWDSs.

maximum size (less than HWDS capacity) to use the HWDS; a notable exception is the work of Chandra and Sinnen [27], which is reviewed in Section 2.1 and compared with the approach of this thesis in Section 4.3.2. Sharing a HWDS among arbitrarily-sized data structures requires extra support in both hardware and software.

This thesis shows that OS, application, and HWDS interactions are crucial to realizing efficient HWDSs that arbitrarily-sized data structures can share. Architecture features enable OS and application use of HWDSs. OS support extends the capabilities of HWDSs beyond prior art with support for arbitrary-sized structures and sharing a HWDS among tasks. (Throughout this dissertation, task denotes a software context and thread denotes a hardware context.) HWDSs can also improve the performance of OS data structure operations, and contribute knowledge about task behavior with respect to data structure usage.

Yesterday's data structures were written together with application code. Today's data structures come in optimized, portable, mature libraries. Tomorrow's data structures should ship with the hardware support to use them well. This thesis shows the promise of HWDSs as a new interface between software and memory.

## 1.1 Impact

Niklaus Wirth wrote that "Algorithms + Data Structures = Programs," a maxim that has gained strength as software has become more complex and data structures more important. Modern programmers can choose data structures from optimized libraries such as the Standard Template Library (STL) or Boost in C++, and the Java collections framework. These libraries stress both performance and flexibility, but their performance is often limited to an  $O(\log n)$  algorithmic factor—and the dynamic nature of these structures lessens the benefits of prefetching and caching. This thesis shows that HWDSs can improve performance by reducing that algorithmic factor to O(1) for common operations in ideal cases, and when the ideal is not met then extra support from the OS helps to maintain performance improvements.

The following examples demonstrate the potential for improvement from data structures implementing the two abstract data types considered in this thesis, the *priority queue* and *map*:

- Planning algorithms. Two popular algorithms that use priority queues are Dijkstra's shortest-path algorithm and the A\* planning algorithm. Experiments show that Dijkstra's algorithm often spends 50–60% of its execution time in the priority queue [81]. Our own experiments on real-world maps taken from the DIMACS shortest path implementation challenge benchmarks [26] show the benchmark spends up to 29% of its time inside the priority queue.

- Image analysis. The grey-weighted distance transform on 3D images uses a software priority queue [82]. Measurements show the priority queue accounts for over 30% of the application's execution time; see Section 6.4.

- Discrete event simulation. A priority queue organizes pending events in a discreteevent simulation (such as a queueing network or integrated circuit simulation), and has been a popular test case for priority queue implementations [61, 105]. Such simulations spend up to 40% of execution time managing the queue [105].

- Fine-grained multitasking. Carbon [73] uses hardware queues to improve fine-grained multitasking for Recognition, Mining, and Synthesis. Compared to software approaches, Carbon can achieve 68% faster execution time for loop-level parallelism, and 109% for task-level parallelism.

- Real-time task scheduling. In prior work, I have shown that a hardware priority queue reduces scheduling overheads and improves predictability [16]; others have shown that a hardware priority queue can reduce task scheduler overhead from 18% in software to less than 0.5% [72].

- Web browsers. The Chromium web browser makes extensive use of the C++ STL map container, which often is implemented as a red-black tree. Profiling (see Appendix A) of this code shows that—even for a short session of starting, loading a blank page, and stopping—Chromium creates 1907 maps and executes 49,483 find operations that consume 436,758,391 cycles of map execution time, or approximately 12% of overall execution time.

- Programming languages. Interpreted languages need to look up strings frequently, as do systems that monitor memory accesses. For example, Akritidis et al. [7] use a splay tree—a self-adjusting binary search tree (BST)—referent object checker and evaluated it on the Olden and SPECINT 2000 benchmarks—for Olden the time overhead of using the checker was 30% on average (excluding two benchmarks); for SPECINT 2000 the overhead was on average 900% and exceeded 100% for all benchmarks.

- OS search trees. Pfaff [100] evaluates implementations of BSTs—including random BSTs, self-balancing BSTs (AVL and red-black), and splay trees—in the context of systems usage. The systems applications used to evaluate the BSTs are virtual memory address (VMA) mapping in Linux, IP peer caching, and index cross-reference collation. With real-world data, a splay tree implementation of VMA mapping improves performance of Mozilla, VMware, and Squid test sets by 23% to 40%. Other uses of balanced search trees in Linux include: input/output (I/O) schedulers, optical device driver, high-resolution timers, ext3 filesystem directory entries, and cryptographic keys [1].

- Key-value stores Key-value stores implement straightforward searching with keys that are often either strings or integers. Search benchmarks model the application processing of key-value stores; OS processing time of key-value stores can be substantial—when requests are small memcached spends up to 80% of its time in OS code primarily for network packet processing [20].

These applications are just a sample of the uses for priority queues and maps. OS support for HWDS use in these applications can eliminate much of the time spent processing data structure operations.

### 1.2 Overview

In using a data structure, an application "reads" (searches or iterates) and "writes" (inserts or removes) nodes. A data structure's read/write operations abstract the lower level load/store operations that comprise a processor's interface to memory. By supporting the high-level abstraction of data structure operations, HWDSs enable applications to extract fine-grained parallelism from their data structures.

```

void bubble_up(int i) {

while (i > 1 && heap[i]->key <

heap[PARENT(i)]->key) {

swap_entries (i, PARENT(i));

i = PARENT(i);

}

void heap_insert(int key,int val) {

int s = ++heap_current_size;

heap[s] = alloc_init_node(keyval);

bubble_up(s);

}

(a) Insertion code for a software binary heap.

(b) Insertion code for a priority queue HWDS.

```

Figure 1-3: Program code changes when using a HWDS.

Figures 1-3a and 1-3b demonstrate the expressive power of a HWDS abstraction with the insert code of a software priority queue implemented as a binary heap, and the insert code of a priority queue using a HWDS respectively.

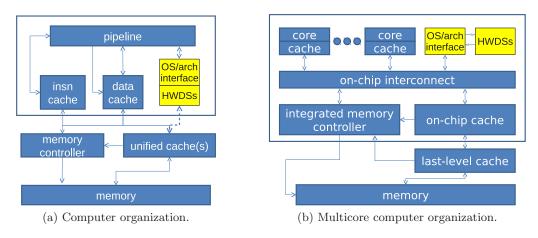

Figure 1-4a shows how a HWDS can fit with other computer hardware in a uniprocessor setting; multicore chips introduce complications for sharing and communication, and one possible configuration is shown in Figure 1-4b. Design space exploration for both uni- and multi-processing with HWDSs is interesting future work.

Figure 1-4: HWDS architecture overview.

This thesis makes it possible to use a HWDS even when the application's data needs exceed the HWDS capacity, or when multiple data structures attempt to share the HWDS concurrently. I demonstrate the benefit of OS support for HWDSs with use cases and synthetic benchmarks that are executed using cycle-accurate simulation.

### 1.2.1 Overflow handling

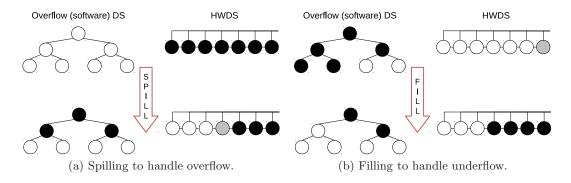

Generic applications require support for data structures of arbitrary size. Since hardware has a fixed capacity, arbitrarily large data sets eventually will cause overflow. A HWDS is like a write-back cache: it must save dirty nodes to backing storage or else the updated data would be lost. This is in opposition to a write-through or read-only cache, which can handle overflow by simply removing nodes from the hardware unit's storage because the backing storage already contains the up-to-date node's data.

The specifics of overflow handling depends on the implementation of the HWDS, but the general concept is universal. To deal with overflow, HWDS control logic and software (for example, the OS) spill data out of the HWDS and into an overflow data structure in secondary storage (main memory); see Figure 1-5a. Conversely, control logic and software fill data from the overflow data structure when the HWDS needs to access nodes that it previously spilled; see Figure 1-5b. Section 3.1 describes HWDS overflow handling in greater detail.

## 1.2.2 Sharing HWDS resources: HWDS assignment

Multiple data structures might share a HWDS, for example when two applications execute concurrently and use the hardware for different data structures. Sharing is a traditional OS problem of how to manage contention for a limited hardware resource: The usual solution is scheduling. This thesis turns the sharing problem into that of *HWDS assignment*, which

Figure 1-5: Handling limited hardware capacity with HWDSs.

Figure 1-6: HWDS sharing with a HWDS context switch.

is the problem of determining whether a data structure uses a HWDS or a software-only implementation. When two data structures do share a HWDS, the OS supports the HWDS with a HWDS context switch—spilling the nodes for the current HWDS context and filling nodes for the requested data structure; see Figure 1-6. Section 3.2 further illuminates the problem of sharing HWDS resources and its solution, HWDS assignment.

### 1.3 Contributions

This thesis explores the hardware-software interface of HWDSs with a holistic approach that has many contributions including:

- Operation-level interface for applications to use HWDSs. An interface between HWDSs and software gives applications access to HWDS resources and improves program performance. The programming interface is at the level of data structure operations, and the implementation is at the instruction set architecture (ISA) level so that future improvements in the hardware microarchitecture do not affect the interface.

- Effective use of parallelism compared to conventional architectures. Explicitly parallel architectures require a programmer to partition and synchronize shared data accesses. HWDSs use implicit parallelism to achieve high-performance parallel computing without burdening the programmer with consistency and tasking models. Implicit parallelism improves software performance at little cost to the programmer.

- Spilling HWDS overflow data. Hardware and software work together to support large data structures that overflow hardware capacity. Although some performance is lost, the HWDS approach remains competitive with software-only solutions. Compared to software implementations, a 128-node HWDS achieves over 50% faster mean access time to a 512-node priority queue, and 15% faster mean search time in a 512-node read-mostly map.

- HWDS Assignment for sharing a HWDS. HWDS assignment is supported by the OS to share and restrict available HWDS resources among multiple data structures. When sharing a HWDS among four maps of power-of-2 sizes between 64 and 512, a 128-node HWDS achieves 35% faster searches than a *splay tree*. Eviction

of oversized HWDSs enables the OS to make dynamic assignment decisions to limit performance loss; when a 128-node HWDS is used for a 512-node map that is updated and searched, an eviction policy yields 16% performance loss, but performance loss without eviction is 64%. Prior art does not offer any solutions for HWDS assignment, so these performance improvements are made possible solely by the OS support for HWDSs proposed in this thesis.

- Support for many kinds of data structures. The priority queue and map are examples of HWDSs that improve the performance of sorting and searching, two fundamental problems in computing. The policies and solutions of this thesis apply to both kinds of data structures, and future work can investigate others such as string-based or hashing structures.

- Increased real-time schedulability. HWDSs can benefit real-time systems by reducing worst-case execution times (WCETs) even when multiple data structures share a HWDS or when data structure sizes exceed HWDS capacity.

- Evaluation with cycle-accurate timing, real systems, and real-world data.

Real applications and synthetic benchmarks validate the HWDS approach using cycle-accurate fully-functional simulation. OS support is designed and implemented in the Real-Time Executive for Multiprocessor Systems (RTEMS) real-time operating system (RTOS), so real OS overheads are included in the experiments. The simulator executes HWDS operations and accounts for operation latency as part of the cycle time. Experiments are conducted using applications and microbenchmarks that use data structures with both software and HWDS implementations.

With respect to prior art, an experiment using a GPS benchmark with real-world data is conducted that compares overflow handling with the exception-based *united HWDS*

proposed by this thesis with the interposition-based *split HWDS* proposed by others [27]; see section 4.3.2. When using the united HWDS, the benchmark executes 24% faster than when using a software implementation, even though the data structure size exceeds the hardware's capacity. The benchmark using the split HWDS *never does better than software* in the presence of overflow.

The OS support for HWDSs presented in this thesis bears some resemblance to policies and mechanisms for cache and translation lookaside buffer (TLB) management, but the structural locality, operation diversity, and design and implementation multiplicity of HWDSs demand new solutions. Memory cache is a reflection of a flat array of storage, and leverages the independence between cache lines for fast, effective fetching and replacing. A HWDS has connections between nodes that must be preserved, which would require complex hardware to implement structure-preserving overflow. HWDSs support common data structure operations that encode high-level abstractions in low-level mechanisms, whereas cache and TLB are limited to the load/store memory interface. Extant solutions to hardware overflow and sharing that rely on hardware mediation are not useful across multiple kinds of HWDSs, and hardware management for any given HWDS implementation would drive up its cost and complexity in terms of both development and hardware resources. The structural locality, operational richness, and design diversity motivate software management of HWDSs. This thesis shows that software—more flexible, fixable, and forwardcompatible than hardware—can manage HWDSs efficiently to provide performance gains for applications and systems software.

### 1.4 Scope

Investigation of HWDSs is an open-ended area of research. Limits on the scope of this thesis delineate what is and is not investigated.

This thesis investigates: architectural support for HWDSs with Simics/GEMS, OS support with RTEMS in a uniprocessor setting, representative data structures (priority queue and map) and applications, HWDSs in real-time systems, and the performance of HWDSs versus software-only solutions.

This thesis does not investigate: real hardware or general purpose OS (e.g. Linux) implementations, design space exploration for HWDS interfaces or implementations, compiler support for HWDS, sharing a HWDS among multiple tasks with a single data structure, OS optimizations that use the knowledge about applications gleaned from HWDS behavior, multiprocessor architectures, and metrics related to power, reliability, or usability. All of these areas are possible directions for future work.

### 1.5 Outline

This thesis is organized as follows. Chapter 2 reviews the related work in the field. Chapter 3 describes the generic OS support for HWDSs necessary for overflow handling and HWDS assignment. Chapter 4 describes an example of a HWDS that implements a priority queue, refines the generic overflow handling support, and presents experimental results that demonstrate the performance of overflow handling and HWDS assignment for two important priority queue applications: discrete event simulation and path planning. Chapter 5 proposes a HWDS implementation of a map for efficient searching, and presents experimental results from a synthetic search benchmark. Chapter 6 shows how real-time systems can use HWDSs to improve the schedulability of task sets by reducing WCETs; I evaluate four HWDS assignment algorithms using experiments and benchmarks modeled from real-world applications. Chapter 7 identifies possibilities for future work and concludes.

# Chapter 2 – Literature Review

The work most closely related to this thesis are in the areas of design of HWDSs, hardware support for fine-grained parallelism, shipping code to data, linked prefetching, object-based systems, and transactional memory. The following reviews each of these in turn.

## 2.1 Design and Implementation of HWDSs

### 2.1.1 HWDSs for network routing

Hardware support for scheduling has been an area of interest in the queuing hardware of packet-switched networks. Moon et al. [87] compare four approaches to hardware priority queues for high-speed networks and introduce an approach that melds two of the previous solutions. Kim and Shin [65] describe an architecture for EDF scheduling for ATM switch networks and introduce deadline folding to circumvent limitations in the range of priority values. Bhagwan and Lin [14] introduce a heap-based hardware priority queue with pipelined stages of the enqueue and dequeue operations. Morton et al. [89] describe a hardware priority queue that does not require hardware comparators.

How this thesis differs Although packet-switched routers can benefit from hardware priority queues, software has no interface to access the priority queues—they are only useful for sorting network packets. This study enables software to use the priority queues by exposing an interface to the hardware so that software can benefit from the hardware acceleration while remaining flexible to implement different algorithms using functional memory.

### 2.1.2 HWDSs for real-time scheduling

Approaches for hardware-based packet scheduling have been extended for task scheduling in RTOSs. The goals of hardware support for real-time scheduling are to minimize scheduling latency and provide highly predictable multiprocessing. The Spring Scheduling Coprocessor (SSCoP) [24] is one of the first examples of a hardware task scheduler and introduces simple queues for the set of scheduled tasks. Others have implemented hardware scheduling using some form of custom logic and a hardware priority queue [108, 71, 69, 16, 72, 115].

How this thesis differs In contrast to the prior work, which focuses on hardware support for a single fixed-size priority queue, this thesis allows arbitrarily-large priority queues to share a hardware priority queue.

#### 2.1.3 HWDSs for reconfigurable computing with Java

Chandra and Sinnen [27] investigate HWDSs in the context of integrating a high-level language, Java, with reconfigurable computing. In addition to the usual priority queue operations, the authors investigate how to increase the queue length, use non-integer priority values, and add new operations.

How this thesis differs Chandra and Sinnen do not consider how HWDSs are shared and scheduled among multiple consumers. Their approach, a split *interposition-based HWDS*, does not handle overflow well; see Section 4.3.2.

#### 2.1.4 Systolic Priority Queues

Leiserson [77] describes systolic HWDS implementations including priority queue, multiqueue, and tree. He suggests that overflow be handled by the OS, and that pairing an insert with an extract can handle refilling the HWDS. How this thesis differs Leiserson focuses on the hardware design of systolic HWDSs with only cursory examination given to the software-side of the HWDS-OS equation. This thesis demonstrates that intelligent software support is necessary to achieve good performance from HWDSs in the presence of overflow and sharing.

### 2.1.5 Abstract Datatype Processors

Kim [67] and Wu et al. [134] share the vision of raising the abstraction of hardware to that of software; their work proposes and evaluates abstract datatype processors, which accelerate data types with mechanisms and performance similar to HWDSs. Abstract datatype instructions can reduce instruction fetch times by 21–48% and data read/write times by 22–40%. The datatypes they investigated are the sparse vector and hash table, and hardware support is modeled with a content-addressable memory (CAM).

How this thesis differs Abstract datatype instructions currently ignore capacity and sharing problems, but the similarity between these instructions and HWDSs indicates similar problems exist due to hardware size limitations.

### 2.1.6 Content-addressable memory (CAM)

Hardware can search small sets of records with numerical keys efficiently with a CAM. Ternary CAMs [97] can implement approximate search for some applications, such as longest prefix matching.

A common use for CAM in modern computing is as a read-only cache for page tables—the virtual-to-physical address translation map that underlies page-based virtual memory systems. This cache is called the TLB, and its purpose is to cache translations for fast lookup. Tagged TLBs permit cached entries from multiple page tables to share the TLB. TLB overflow is handled by dropping entries; since the TLB is a read-only cache, the

backing data remains in memory. However if the page table is modified, the TLB needs to be refreshed or invalidated.

How this thesis differs CAMs do not permit searching with arbitrary-sized or multiple data sets because of limited hardware capacity, but the solutions posed in this thesis may be used with CAMs to implement a map HWDS.

The primary difference between the page table-TLB and the HWDSs employed in this thesis is that the TLB acts as a read-only cache for the page table, whereas this thesis uses HWDSs like a write-through cache for the overflow data structure. Although subtle, this difference is important. Other differences include: a TLB does not export a SEARCH function; a task or process only gets to use one page table at a time; TLBs do not in general support arbitrary search keys—the address translation relies on the size of pages in the page table to divide the search space.

### 2.1.7 Scratchpad memory (SPM)

An alternative to caching in the embedded domain is a scratchpad memory (SPM) [101]. SPMs can provide predictable access times and software control over code [133] and data [125]. SPMs are software-managed: applications and compilers control the data (and code) residing in the SPM. Co-mingling SPMs with custom hardware can provide further benefits such as intelligent object-based allocation [129, 128].

How this thesis differs Software that uses a SPM still executes serially to access data structures. HWDSs execute in parallel and require different management than scratch-pads because of the increased hardware complexity in HWDS logic. Combining the two approaches to use a HWDS with a SPM as the backing store may be useful for overflow handling.