NPS62-79-015PR

# NAVAL POSTGRADUATE SCHOOL

Monterey, California

Analog-to-Digital Signal Processing in a Prototype SATCOM Signal Analyzer

John E. Ohlson William B. Zell, Jr.

December 1979

Project Report

Approved for public release; distribution unlimited

Prepared for: Naval Electronic Systems Command

PME-106-1

Washington, D.C. 20360

20091105039

TK 5104 036

## NAVAL POSTGRADUATE SCHOOL Monterey, California

Rear Admiral T. F. Dedman Superintendent

Jack R. Bosting Provost

The work reported herein was supported in part by the Naval Electronic Systems Command, PME-106-1.

Reproduction of all or part of this report is authorized.

This report was prepared by:

OHN E. OHLSON

Professor of Electrical Engineering

WILLIAM B. ZELL,

Lieutenant, United States Navy

Reviewed by:

DONALD E. KIRK, Chairman

Department of Electrical

Engineering

Released by:

WILLIAM M. TOLLES

Dean of Research

1. REPORT NUMBER

NPS62-79-015PR

4. TITLE (and Subtitle)

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

REPORT DOCUMENTATION PAGE

| Analog-to-Digital Signal Processing in a                                                          | Project Report                                                 |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Prototype SATCOM Signal Analyzer                                                                  | 6. PERFORMING ORG. REPORT NUMBER                               |

| 7. AUTHOR(s)                                                                                      | 8. CONTRACT OR GRANT NUMBER(+)                                 |

| John E. Ohlson                                                                                    |                                                                |

| William B. Zell, Jr.                                                                              |                                                                |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                                       | 10. PROGRAM ELEMENT PROJECT TASK                               |

|                                                                                                   | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| Naval Postgraduate School                                                                         | N0003980WR09137                                                |

| Monterey, California 93940                                                                        |                                                                |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                           | 12. REPORT DATE                                                |

| Naval Electronic Systems Command                                                                  | December 1979                                                  |

| PME-106-1                                                                                         | 103                                                            |

| Washington, D.C. 20360 14. MONITORING AGENCY NAME & ADDRESS(It ditterent from Controlling Office) | 15. SECURITY CLASS. (of this report)                           |

|                                                                                                   | Unclassified                                                   |

|                                                                                                   |                                                                |

|                                                                                                   | ISA. DECLASSIFICATION/DOWNGRADING SCHEDULE                     |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                       |                                                                |

| Approved for public release; distribution                                                         | unlimited.                                                     |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

| 17. DISTRIBUTION STATEMENT (of the obstrect entered in Block 20, if different fro                 | om Report)                                                     |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

| 18. SUPPLEMENTARY NOTES                                                                           |                                                                |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

|                                                                                                   |                                                                |

| 19. KEY WORDS (Continue on reverse elde if necessary and identify by block number                 | )                                                              |

|                                                                                                   |                                                                |

| Satellite Communications                                                                          |                                                                |

| Analog to Digital Conversion                                                                      |                                                                |

|                                                                                                   |                                                                |

| 20. ABSTRACT (Continue on reverse side if necessary and identify by block number)                 |                                                                |

| A prototype SATCOM Signal Analyzer (SSA) h                                                        | has been designed which                                        |

| performs spectral analysis on transponder                                                         | signals from the Navy's                                        |

| UHF communications satellites. As an inte                                                         | egral part of the SSA, the                                     |

| Analog to Digital Control and Conversion s                                                        | subsystem converts four                                        |

| channels to baseband analog signals into e<br>sentations while operating at variable same         | equivalent digital repre-                                      |

| either twelve or eight bits of resolution                                                         | of the analog signal                                           |

| The digital data thus derived is presented                                                        | to an array processor                                          |

| DD FORM 1473 EDITION OF 1 NOV 65 IS OBSOLETE                                                      |                                                                |

| S/N 0102-014-6601                                                                                 | UNCLASSIFIED                                                   |

| SECURITY OF                                                                                       | SSIBIL ATION OF THIS WACE /When Hale Entered                   |

READ INSTRUCTIONS BEFORE COMPLETING FORM

S. TYPE OF REPORT & PERIOD COVERED

2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER

## UNCLASSIFIED SIFICATION OF THIS PAGE(When Data Entered)

| for Fast F<br>the design<br>Conversion | ourier Trnasf<br>and construc<br>subsystem. | orm proce | ssing.<br>he Analo | This<br>g to | report d<br>Digital | ocuments<br>Control and |

|----------------------------------------|---------------------------------------------|-----------|--------------------|--------------|---------------------|-------------------------|

|                                        |                                             |           |                    | ,            |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

|                                        |                                             |           |                    |              |                     |                         |

#### ABSTRACT

A prototype SATCOM Signal Analyzer (SSA) has been designed which performs spectral analysis on transponder signals from the Navy's UHF communications satellites. As an integral part of the SSA, the Analog to Digital Control and Conversion subsystem converts four channels of baseband analog signals into equivalent digital representations while operating at variable sampling rates and offering either twelve or eight bits of resolution of the analog signal. The digital data thus derived is presented to an array processor for Fast Fourier Transform processing. This report documents the design and construction of the Analog to Digital Control and Conversion subsystem.

## TABLE OF CONTENTS

| I.   | INT | RODUC | CTION | ·              |       |      |      |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 12 |

|------|-----|-------|-------|----------------|-------|------|------|------|-----|-----|------------|----|----|----|----|----|----|----|

|      | A.  | BACK  | GROU  | ND -           |       |      |      |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 12 |

|      | В.  | PROT  | COTYP | E SYS          | TEM ( | GOAI | s -  |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 12 |

|      | C.  | SCO   | PE OF | THIS           | REP   | ORT  |      |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 13 |

|      | D.  | THE   | PROT  | OTYPE          | SSA   | SYS  | TE   | M -  | -   | -   | -          | -  | -  | -  | -  | -  | -  | 13 |

|      | E.  |       |       | O-DIG          |       |      |      |      |     |     |            |    |    |    |    | -  | -  | 15 |

| II.  | DES | IGN C | CONSI | DERAT          | IONS- |      |      |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 17 |

|      | A.  | BASI  | C DE  | SIGN           | CONS  | IDEF | TAS  | IONS | 5-  | -   | -          | -  | -  | -  | -  | -  | -  | 17 |

|      | В.  |       |       | ERSUS<br>CONVE |       |      |      |      |     |     |            |    |    |    | -  | -  | -  | 17 |

|      |     | 1.    | Samp  | ling           | Requ  | irem | ien  | ts-  | -   | -   | -          | -  | -  | -  | -  | -  | -  | 18 |

|      |     | 2.    | Hard  | lware          | Requ  | irem | en   | ts-  | -   | -   | -          | -  | -  | -  | -  | -  | -  | 18 |

|      |     | 3.    | Imag  | e and          | Zer   | o Fr | eq   | uen  | су  | Co  | ns         | id | er | at | ic | ns | ;- | 19 |

|      |     | 4.    | Syst  | em Co          | mpat  | ibil | lity | y -  | -   | -   | -          | -  | -  | -  | -  | -  | -  | 19 |

|      | C.  | EQU   | IPMEN | T SEL          | ECTI  | ON-  |      |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 20 |

|      |     | 1.    | Samp  | ole Ra         | te R  | equi | re   | men  | ts  | -   | -          | -  | -  | -  | -  | -  | -  | 20 |

|      |     | 2.    | Bit   | Resol          | utio  | n Re | equ. | ire  | mer | nts | ; <b>–</b> | -  | -  | -  | -  | -  | -  | 21 |

|      |     | 3.    | Equi  | pment          | Sel   | ecti | lon- |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 21 |

| III. | DET | AILEI | OPE   | ERATIO         | N -   |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 23 |

|      | A.  | INT   | RODUC | CTION          |       |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 23 |

|      | В.  | ADC   | BOAF  | sp             |       |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 23 |

|      |     | 1.    | Intr  | oduct          | ion   |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 23 |

|      |     |       | a.    | Funct          | ions  |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 23 |

|      |     |       | b.    | Input          | .s -  |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 26 |

|      |     |       | c.    | Outpu          | ts-   |      | -    |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 26 |

|      |     |       | d.    | Imple          | ment  | atio | on · |      | -   | -   | -          | -  | -  | -  | -  | -  | -  | 28 |

|    |     | e.   | DC Board Sections                        |       |       | -    |      | -       | - | 30 |

|----|-----|------|------------------------------------------|-------|-------|------|------|---------|---|----|

|    | 2.  | Sync | ronization Sectio                        | n     |       | -    |      | -       | - | 30 |

|    |     | a.   | Introduction                             |       |       | -    |      | -       | - | 30 |

|    |     | b.   | Master Pulse                             |       |       | -    |      | -       | - | 30 |

|    |     | c.   | Sample-Command Pul                       | se -  |       | -    |      | -       | - | 33 |

|    |     | d.   | start-Convert Puls                       | e     |       | -    |      | -       | - | 33 |

|    |     | e.   | II/LOW-SELECT Sign<br>Inversion          |       |       |      | g a: | nd<br>- | - | 34 |

|    | 3.  | Samp | e-and-Hold Sectio                        | n     |       | -    |      | -       | - | 35 |

|    |     | a.   | introduction                             |       |       | -    |      | -       | - | 35 |

|    |     | b.   | M-318 Operational                        | Amp]  | Lifie | er · |      | -       | - | 35 |

|    |     | C.   | ower and Overvolt                        | age I | Prote | ect. | ion  | -       | - | 35 |

|    |     | d.   | Sample-and-Hold Mo<br>JH                 | dule, | , DAT | EL.  | -SHI | - M     | - | 37 |

|    | 4.  | Anal | g-to-Digital Conv                        | ersio | on Se | ect  | ion  | -       | - | 37 |

|    |     | a.   | Introduction                             |       |       | -    |      | -       | - | 37 |

|    |     | b.   | Low Speed Analog-t<br>Converter, DATEL A |       |       |      |      | -       | - | 38 |

|    |     | c.   | ligh Speed Analog-<br>Converter, TRW TDC |       |       |      |      | -       | - | 42 |

|    | 5.  | Digi | al-Data-Selection                        | Sect  | tion  | -    |      | -       | - | 45 |

|    |     | a.   | Introduction                             |       |       | -    |      | -       | - | 45 |

|    |     | b.   | Output Formats                           |       |       | -    |      | -       | - | 45 |

|    |     | c.   | Data Latching                            |       |       | -    |      | -       | - | 47 |

|    |     | d.   | Oata Multiplexing-                       |       |       | _    |      | -       | - | 48 |

| C. | ADC | CONT | ROL BOARD                                |       |       | -    |      | -       | - | 49 |

|    | 1.  | Intr | oduction                                 |       |       | -    |      | -       | - | 49 |

|    |     | a.   | Tunctions                                |       |       | -    |      | -       | - | 49 |

|    |     | b.   | Inputs                                   |       |       | -    |      | -       | - | 49 |

|    |     |      |                                          |       |       |      |      |         |   |    |

|        |       |       | · .   | outputs                                 |    |   |   | 72         |

|--------|-------|-------|-------|-----------------------------------------|----|---|---|------------|

|        |       |       | đ.    | Implementation                          | -  | - | - | 50         |

|        |       |       | e.    | ADC Control Board Sections              | -  | - | - | 52         |

|        |       | 2.    | Puls  | e Forming/Power Protection Sect         | io | n | - | 52         |

|        |       |       | a.    | Introduction                            | -  | - | - | 52         |

|        |       |       | b.    | SAMPLE-ENABLE Signal                    | _  | _ | - | 52         |

|        |       |       | c.    | Pulse Generation                        | -  | - | - | 55         |

|        |       |       | d.    | Reference Signals                       | -  | _ | - | 56         |

|        |       | 3.    | Divi  | der Network                             | _  | - | - | 56         |

|        |       |       | a.    | Introduction                            | _  | - | - | 56         |

|        |       |       | b.    | Sample-Frequency Generation             | _  | - | - | 56         |

|        |       | 4.    | Freq  | quency-Selection Section                | -  | _ | - | 60         |

|        |       |       | a.    | Introduction                            | -  | - | - | 60         |

|        |       |       | b.    | Sample-Frequency Selection              | _  | _ | - | 60         |

|        |       |       | c.    | HI/LOW-SELECT Signal                    | -  | - | - | 65         |

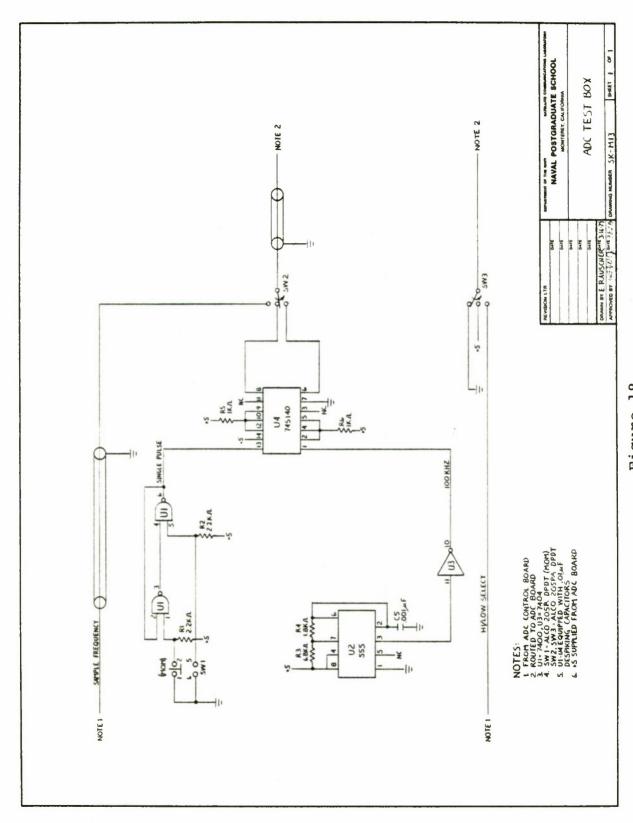

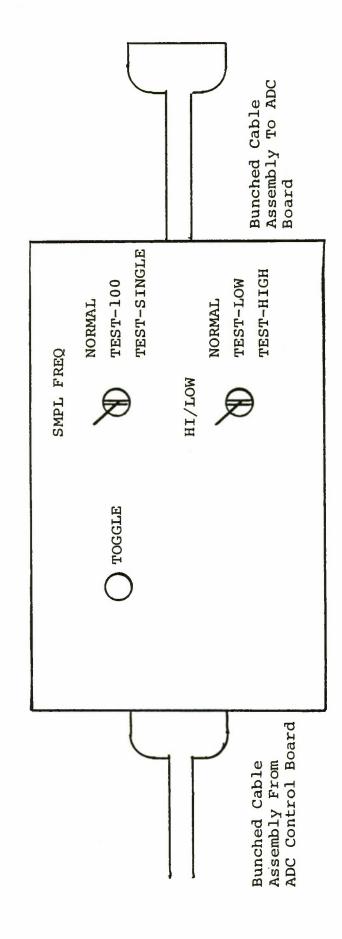

|        | D.    | ADC   | TEST  | BOX                                     | -  | - | - | 65         |

|        |       | 1.    | Intr  | oduction                                | -  | - | - | 65         |

|        |       | 2.    | Inpu  | its/Outputs                             | -  | - | - | 66         |

|        |       | 3.    | Impl  | ementation                              | -  | - | - | 66         |

|        |       | 4.    | Oper  | ation                                   | -  | - | - | 68         |

|        |       |       | a.    | HI/LOW Test Mode                        | -  | - | - | 68         |

|        |       |       | b.    | SAMPLE-FREQUENCY Test Mode              | -  | - | - | 70         |

| IV.    | FUT   | JRE I | DESI  | ON CONSIDERATIONS                       | -  | - | - | 73         |

| v.     | CON   | CLUS  | ION - |                                         | -  | - | - | <b>7</b> 5 |

| APPENI | OIX A |       |       | CHANNEL ANALOG-TO-DIGITAL ERSION THEORY | -  | _ | - | 76         |

| APPENI | OIX I | 3 - 8 | SPEC  | FICATION TABLES                         | -  | - | - | 79         |

|        |       |       |       |                                         |    |   |   |            |

| APPENDIX | C -   | CALI  | BRAT | CIO | N PI | ROC | EL | UF | ŒS | 5- | *** | _ | - | _ | - | _ | _ | _ | _ | 83  |

|----------|-------|-------|------|-----|------|-----|----|----|----|----|-----|---|---|---|---|---|---|---|---|-----|

| APPENDIX | Z D - | PIN   | COM  | NEC | TIOI | NS  | -  | -  | -  | -  | -   | - | - | - | - | - | - | - | - | 86  |

| APPENDIX | E -   | COMP  | PONE | T   | LIST | rs  | -  | -  | -  | -  | -   | - | - | - | - | - | - | - | - | 97  |

| LIST OF  | REFE  | ERENC | CES- | -   |      | -   | -  | -  | _  | -  | -   | - | _ | - | - | - | - | - | - | 102 |

| INITIAL  | DIST  | RIBUI | CION | LI  | ST-  | -   | _  | _  | _  | _  | _   | _ | _ | _ | _ | _ | _ | _ | _ | 103 |

## LIST OF FIGURES

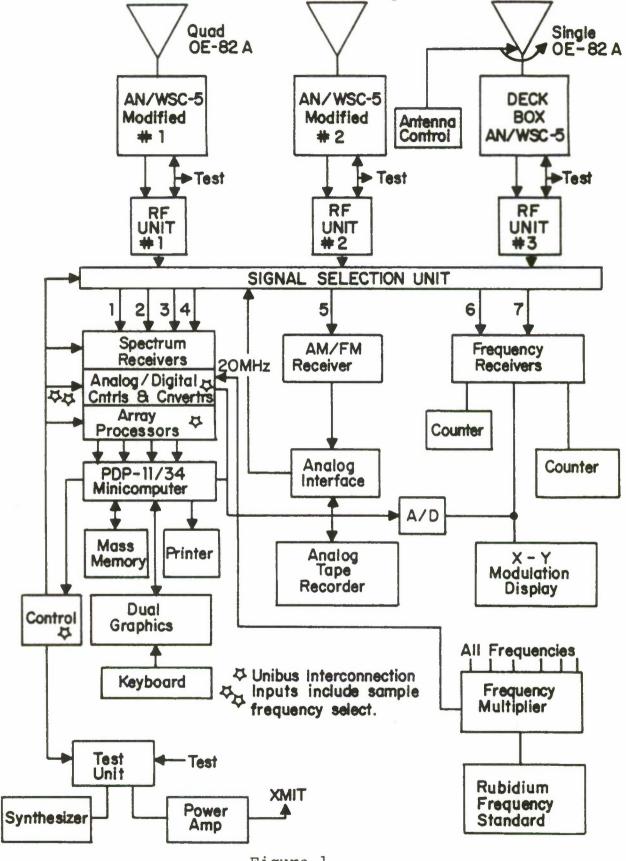

| 1.  | Block Diagram of the Prototype SATCOM Signal Analyzer                   | 14 |

|-----|-------------------------------------------------------------------------|----|

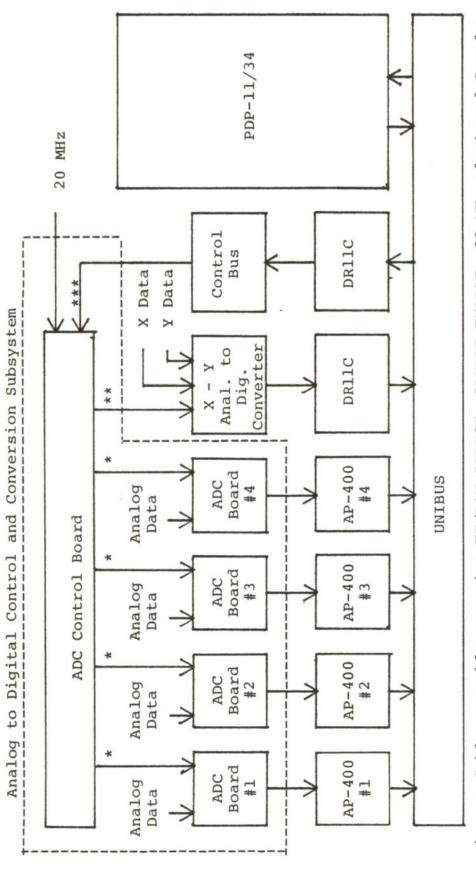

| 2.  | Block Diagram of the Analog-to-Digital Control and Conversion Subsystem | 24 |

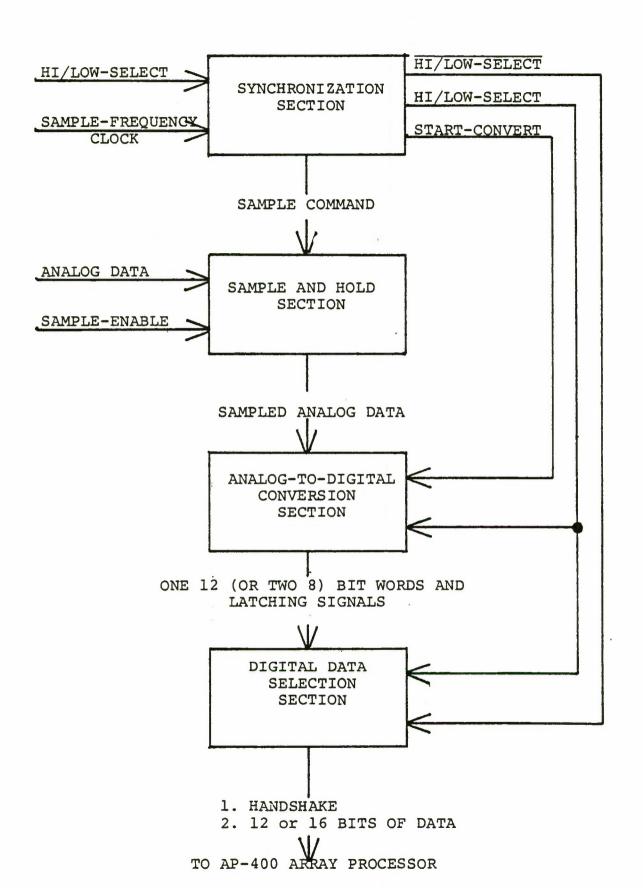

| 3.  | Block Diagram of ADC Board Operation                                    | 27 |

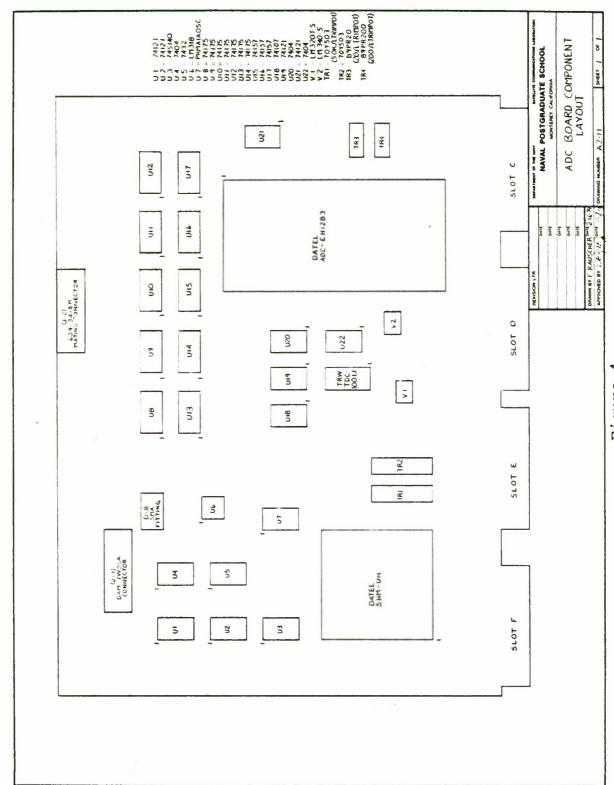

| 4.  | ADC Board Component Layout                                              | 29 |

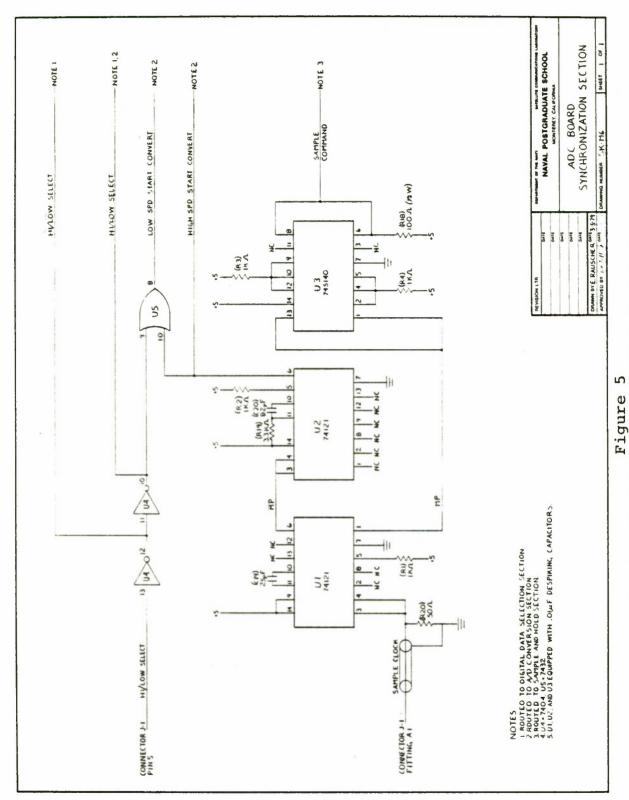

| 5.  | Synchronization Section Circuit Diagram                                 | 31 |

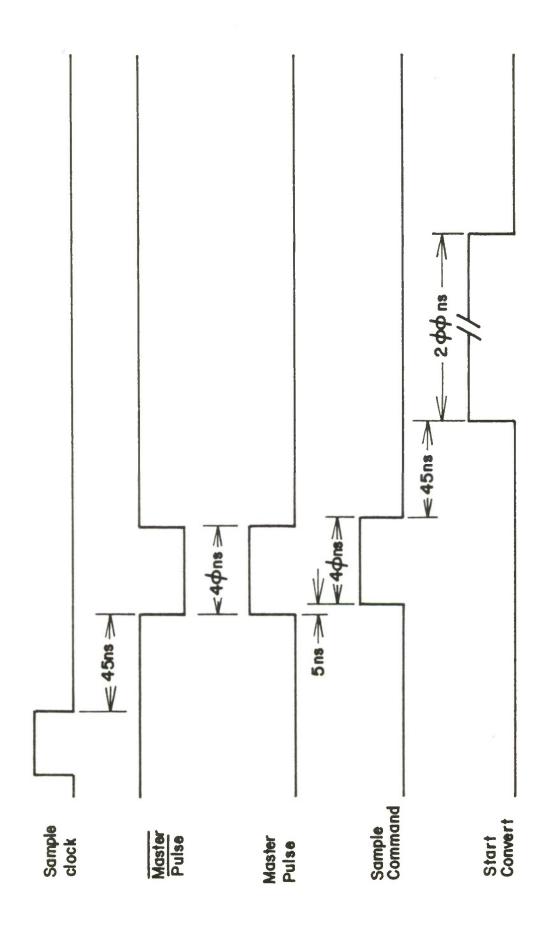

| 6.  | Synchronization Section Timing Diagram                                  | 32 |

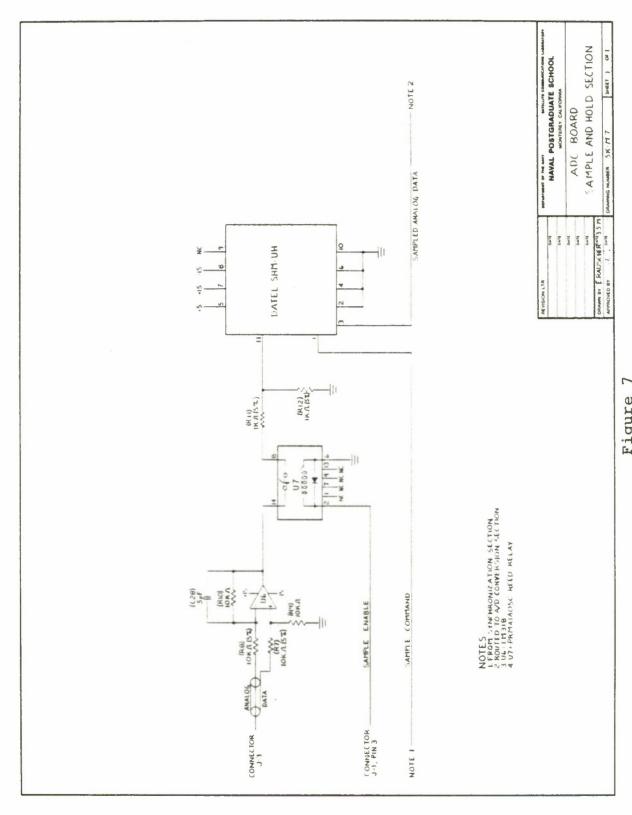

| 7.  | Sample-and-Hold Section Circuit Diagram                                 | 36 |

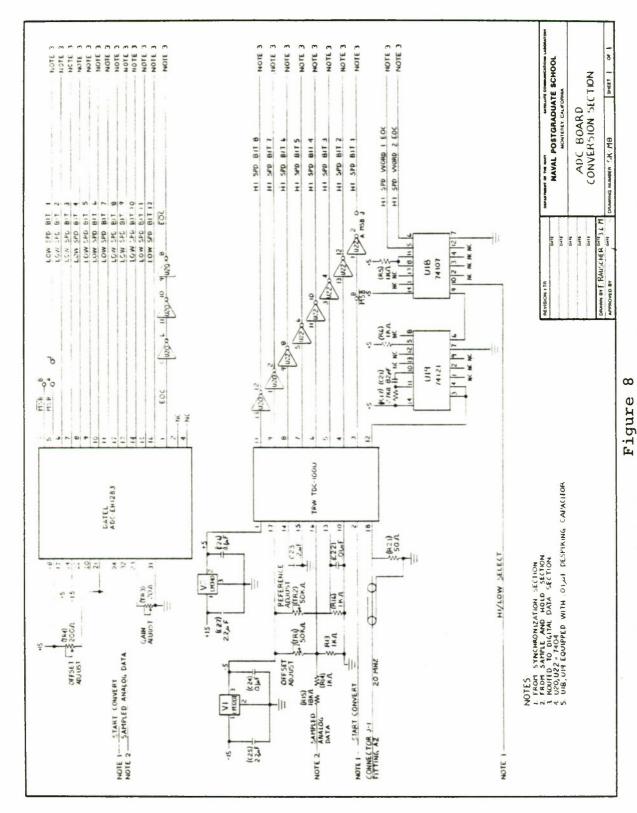

| 8.  | Analog-to-Digital Conversion Section Circuit Diagram                    | 39 |

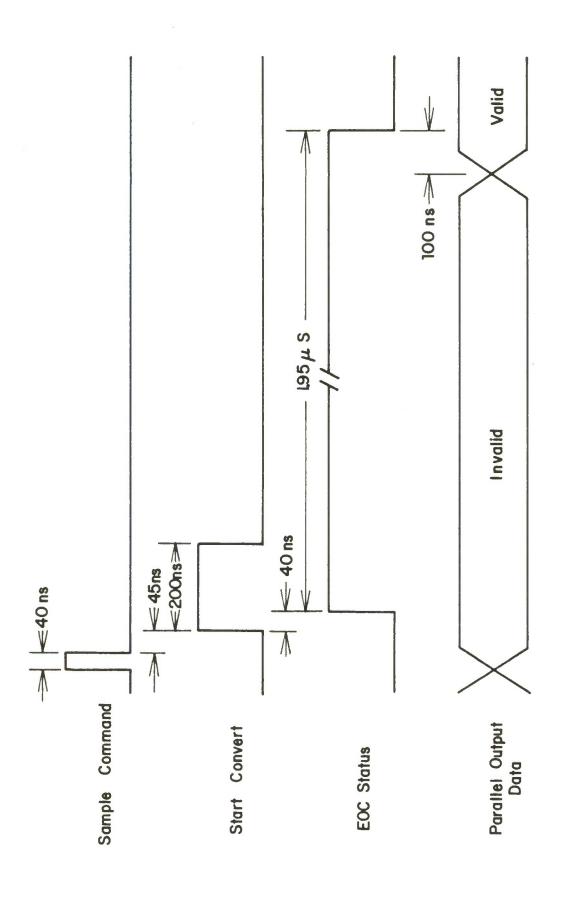

| 9.  | Low-Speed Analog-to-Digital Conversion Timing Diagram                   | 40 |

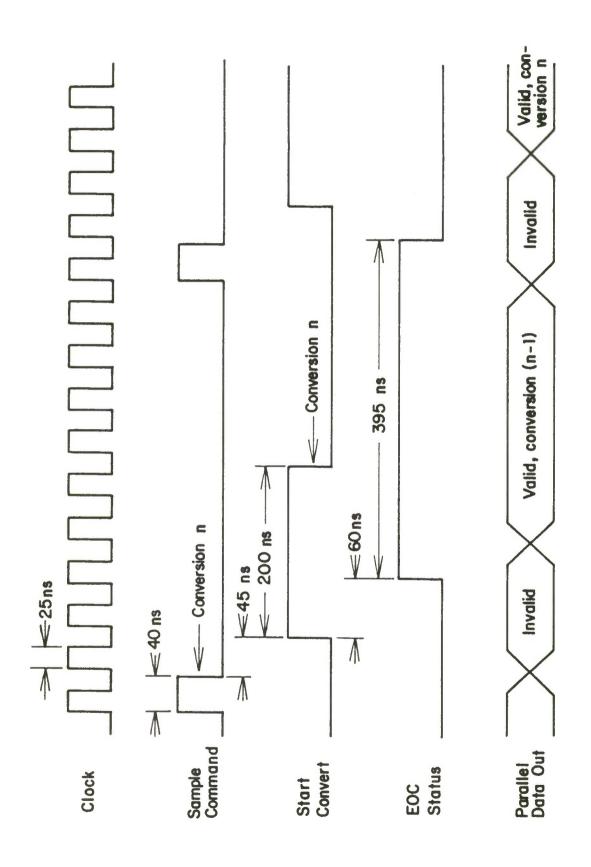

| 10. | High-Speed Analog-to-Digital Conversion Timing Diagram                  | 44 |

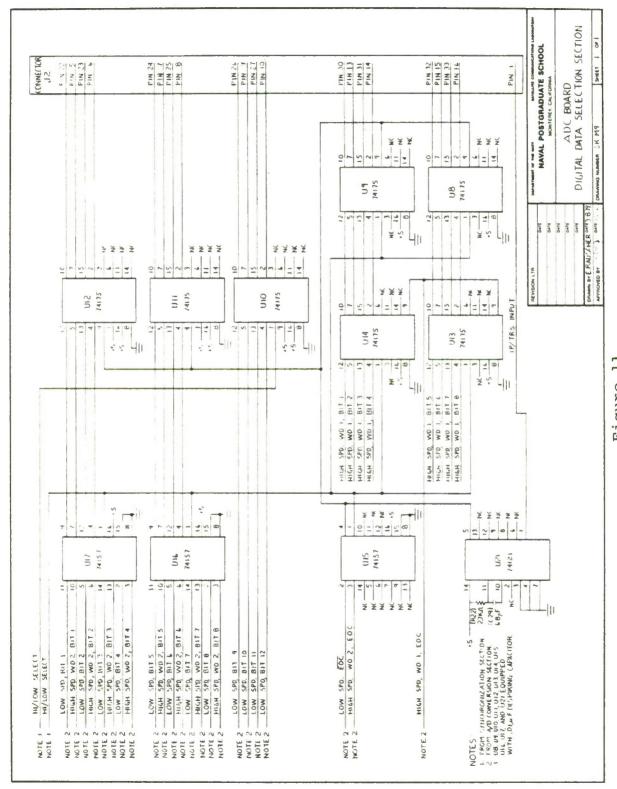

| 11. | Digital-Data-Selection Section Circuit Diagram                          | 46 |

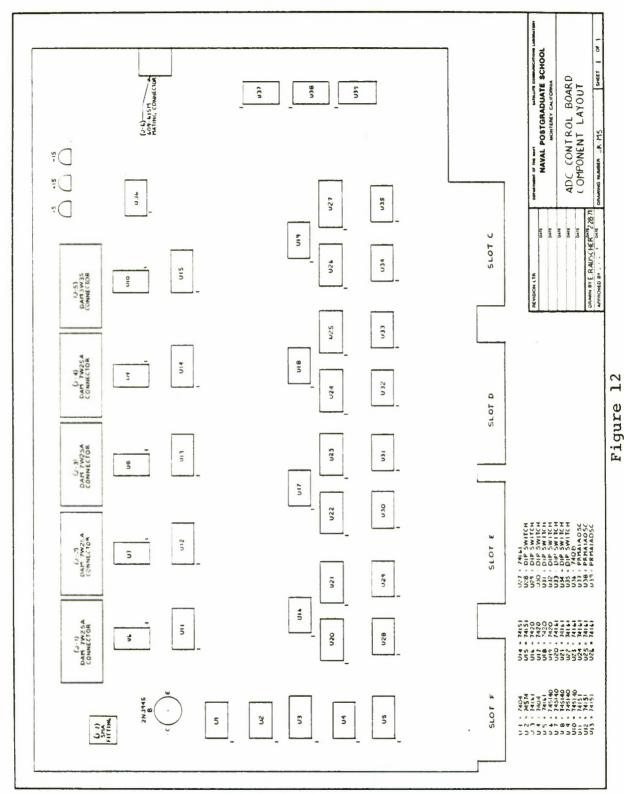

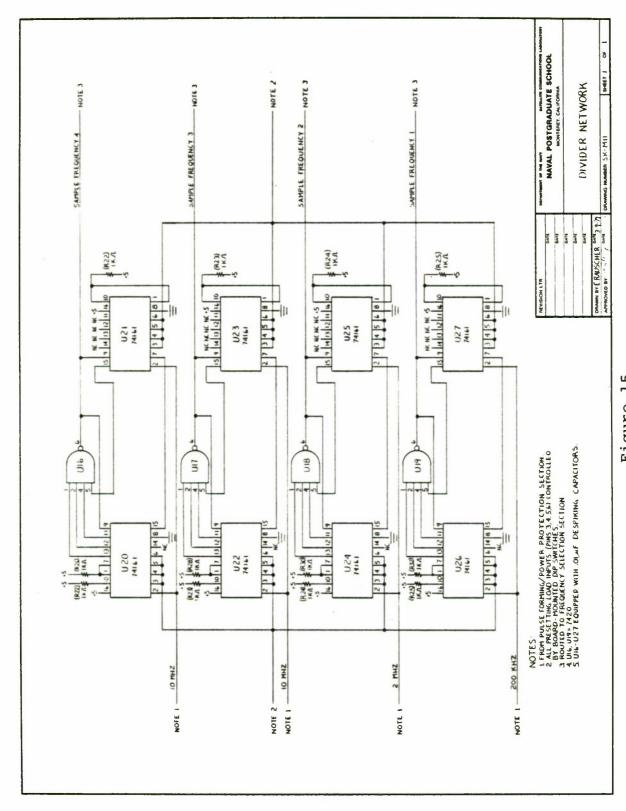

| 12. | ADC Control Board Component Layout                                      | 51 |

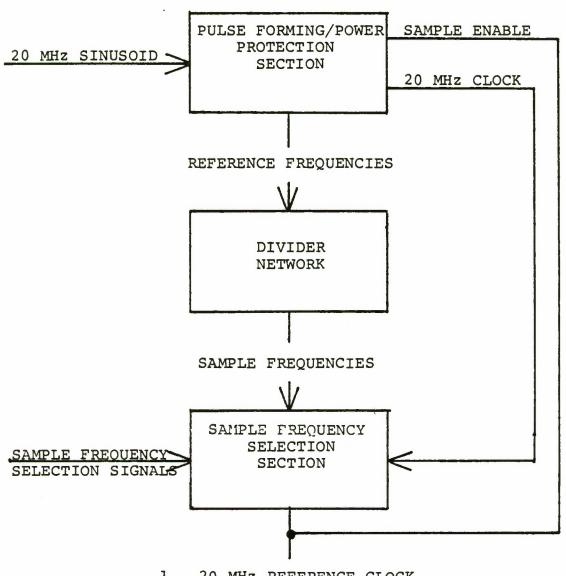

| 13. | Block Diagram of ADC Control Board Operation                            | 53 |

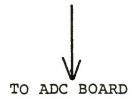

| 14. | Power Protection/Pulse Forming Section Circuit Diagram                  | 54 |

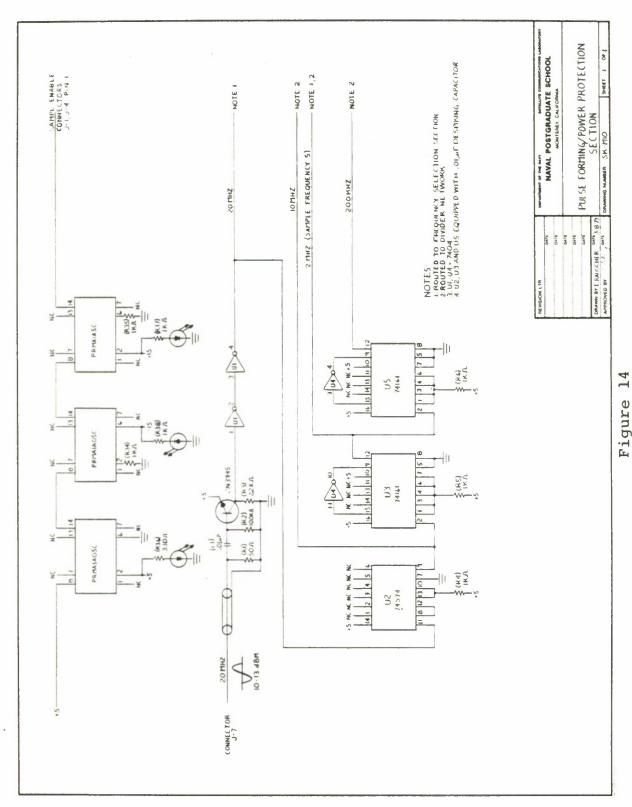

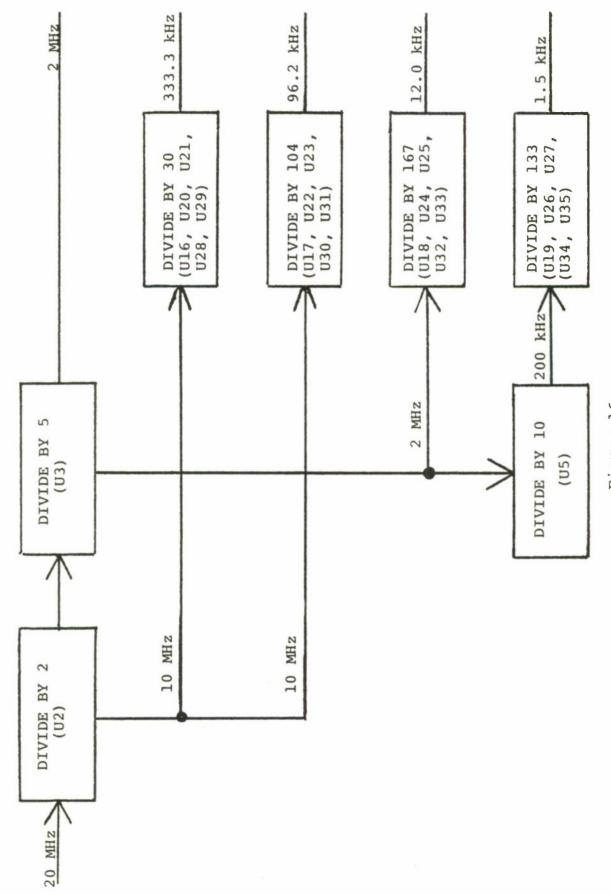

| 15. | Divider Network Circuit Diagram                                         | 57 |

| 16. | Block Diagram of Sample-Frequency Generation                            | 58 |

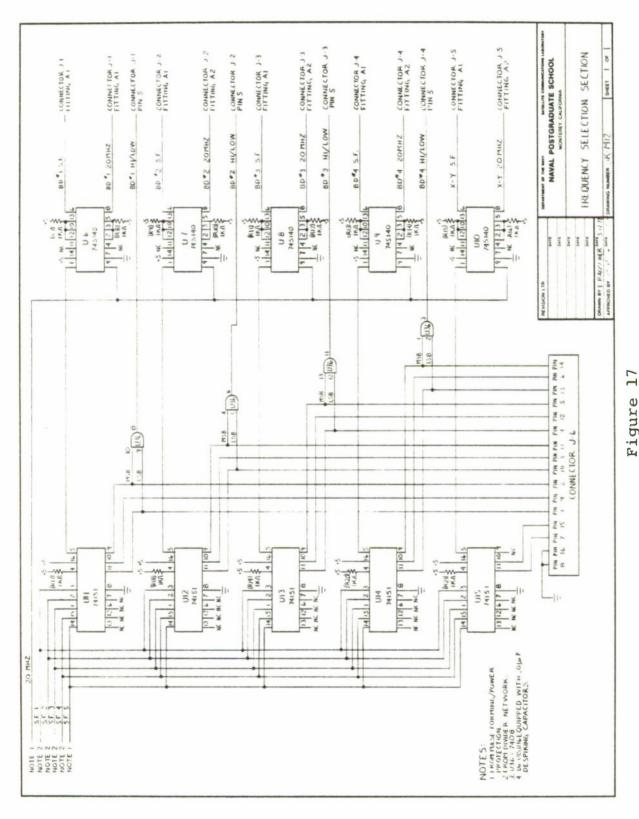

| 17. | Frequency-Selection Section Circuit Diagram                             | 62 |

| 18. | ADC Test Box Circuit Diagram                                            | 67 |

| 19. | ADC Test Box                                                            | 69 |

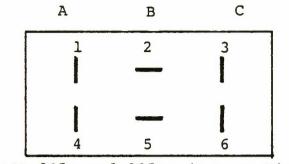

| 20. | Switch Configurations                                                   | 71 |

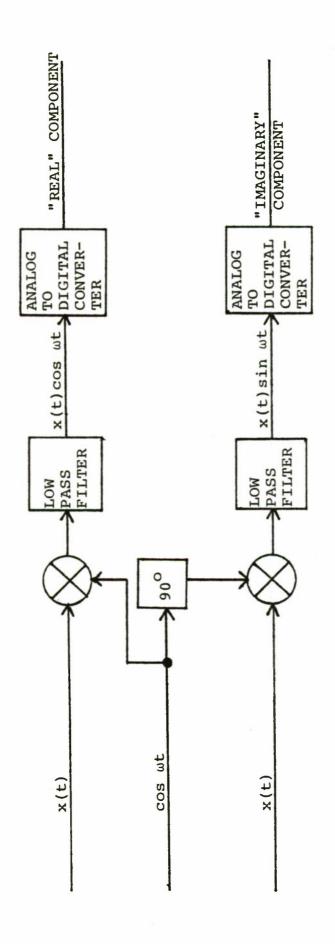

| 21. | Block Diagram of Dual Channel Analog-to-Digital Conversion              | 77 |

## LIST OF TABLES

| I.    | Analog-to-Digital Control and Conversion Subsystem Input/Output Specifications | 25  |

|-------|--------------------------------------------------------------------------------|-----|

| II.   | Offset Binary and Two's Complement Data Formats                                | 41  |

| III.  | Switch Settings for Tentative Sampling Frequencies                             | 61  |

| IV.   | Sample Frequency Selection                                                     | 64  |

| V.    | DATEL SHM-UH Specifications                                                    | 80  |

| VI.   | DATEL ADC-EH12B3 Specifications                                                | 81  |

| VII.  | TRW TDC-1001J Specifications                                                   | 82  |

| VIII. | ADC Control Board Pin Connections                                              | 87  |

| IX.   | ADC Board Pin Connections                                                      | 93  |

| Х.    | ADC Control Board Components List                                              | 98  |

| XI.   | ADC Board Components List                                                      | 99  |

| XTT.  | ADC Test Box Components List                                                   | 101 |

This page intentionally blank.

## I. INTRODUCTION

#### A. BACKGROUND

This project is one of a series of research projects concerning Navy UHF satellite communications (SATCOM) undertaken by the Satellite Communications Laboratory at the Naval Postgraduate School (NPS). Previous research efforts include, but are not limited to, the preparation and evaluation of a shipboard Radio Frequency Interference (RFI) measurement package (Refs. 1-3), the design and construction of the development model SATCOM Signal Analyzer (Refs. 4-6), and the measurement of transponder oscillator drift of the GAPFILLER satellite (Ref. 7). The project which constitutes the basis of this report had its beginning in late 1978 when this laboratory was funded by PME 106-1 of the Naval Electronic Systems Command (NAVELEX) to develop a prototype version SATCOM Signal Analyzer (SSA) system. Upon successful completion and field testing of the prototype, production models will replace the existing monitoring systems at various Naval Communications Stations (NAVCOMMSTA's) and will be used to perform various measurements on Navy UHF communications satellite transponders while operating in orbit.

### B. PROTOTYPE SYSTEM GOALS

The development of the prototype is based on the provision

of all equipment necessary to make real-time measurements at NAVCOMMSTA's. This equipment must have the capability to:

1) perform high speed spectral analyses and frequency measurements in the UHF (240-320 MHz) band using digital techniques; 2) monitor authorized users of the Navy SATCOM system, including the GAPFILLER and FLTSATCOM series satellites;

3) perform selective monitoring when the NAVCOMMSTA is in the footprint of multiple satellites; 4) characterize RFI signals through the use of an X-Y modulation display; and 5) operate in either manual or automatic (computer control) modes.

### C. SCOPE OF THIS REPORT

Figure 1 is a block diagram of the prototype SSA system.

This report documents the design and construction of the Analog-to-Digital Control and Conversion subsystem.

#### D. THE PROTOTYPE SSA SYSTEM

The prototype SSA system has been designed around a PDP-11/34 minicomputer. Standard peripherals have been provided which made the system self sufficient and readily adaptable to existing NAVCOMMSTA power transceiver and antenna systems. Four identical and independent receiver paths have been incorporated to enable the system to continue operation in the event of component failures in any of these channels. High speed digital processing of signal data is accomplished through the use of an Analogic AP-400 array processor which operates under control of the PDP-11/34.

Figure 1

Block Diagram Of The Prototype SATCOM Signal Analyzer

The primary interface with the system operator is the dual graphics subsystem, consisting of two 17-inch, 60-Hz (non-interleaved), raster scan displays. Each of these units has the capability to display a single spectrum or nine separate spectra arranged in a three by three matrix format. Provisions have been made for hard copy reproduction of the information being displayed.

### E. ANALOG-TO-DIGITAL CONTROL AND CONVERSION SUBSYSTEM

As may be observed in Figure 1, the Analog-to-Digital Control and Conversion subsystem is the interface between the Spectrum Receivers and the Array Processor. Within each of the four signal paths in the Spectrum Receiver, an incoming analog signal is downconverted to baseband frequency and bandwidth limited to a bandwidth appropriate to the desired spectral resolution. The Analog-to-Digital Control and Conversion subsystem converts this baseband signal into an equivalent digital "word" which in turn is presented to the AP-400 for array processor Fast Fourier Transform (FFT) processing.

In order to accomplish the above task, and to provide a high degree of flexibility in the spectral processing capabilities of the prototype SSA, design considerations required that the Analog-to-Digital Control and Conversion subsystem be capable of the following operations:

- Sample-and-hold an analog signal at a maximum 2 MHz clock rate;

- 2. Analog-to-digital convert the sampled signal at a

maximum 2 MHz rate with eight bits of resolution, or a maximum 500 kHz rate with twelve bits of resolution;

- Select sampling frequency rates for analog-to-digital conversion (ADC) under control of the PDP-11/34;

- Select sampling frequency rates for the X-Y modulation display under control of the PDP-11/34;

- 5. Provide an interrupt of the ADC process in the event of failure of any of the power supplies;

- 6. Generate appropriate "handshake" signals to the AP-400 array processor; and

- 7. Be compatible in all respects with standard PDP-11/34 hardware and software.

Initial attempts to obtain an ADC system which would meet the above requirements revealed that no such units were commercially available. Accordingly, the Analog-to-Digital Control and Conversion subsystem was designed and constructed in this laboratory. The completed subsystem consists of five printed circuit (PC) boards: 1) four identical ADC boards (one per receiver signal path) which perform the actual analog-to-digital conversions; 2) one ADC Control Board which controls each of the ADC Boards and is in turn controlled by the Control Bus (also designed at NPS) which is driven by a DRIIC via the UNIBUS; and 3) an ADC Test Box to enable limited testing of any of the ADC Boards.

## II. DESIGN CONSIDERATIONS

#### A. BASIC DESIGN CONSIDERATION

The prototype SSA system as depicted in Figure 1 was designed to be completely contained (with the exception of OE-82A antenna and AN/WSC-S transceivers) within five standard 19 inch racks. This represents a dramatic space reduction when compared with the SATCOM Signal Analyzer (developmental version) which performs the same functions (see references 4-6) as the prototype system but occupies 13 racks. Analogously, the Data Acquisition Unit of the SSA (developmental version) occupies one-half of a rack while the Analog-to-Digital Control and Conversion subsystem of the SSA prototype is wholly contained on five PC boards. Much of the reduction of space was obtained by performing the analog-to-digital conversions in the single vice dual channel mode.

B. SINGLE VERSUS DUAL CHANNEL ANALOG-TO-DIGITAL CONVERSION

As described in Appendix A, dual channel analog-to-digital conversion involves the simultaneous mixing (down-conversion) of an RF or IF signal with two equal magnitude,

quadrature phase related local oscillator frequencies. The

two down-converted signals are thus in phase quadrature with

each other so that after analog-to-digital conversion, may

be thought of as representing the "real" and "imaginary"

components of a complex waveform. On the other hand, single

channel analog-to-digital conversion involves the mixing of an RF or IF signal with a single local oscillator frequency. Analog-to-digital conversion of this down converted signal results in a representation of the "real" component of a waveform. Each of these conversion schemes offers advantages to the system designer.

## 1. Sampling Requirements

Nyquist sampling theory states that an analog signal may be completely reconstructed from sampled values if the sampling rate is at least twice the highest frequency component contained within the signal. For spectral analysis this implies that each resolution unit (frequency line) requires two samples values. Dual channel conversion inherently provides these two values in the form of a "real" and "imaginary" component for each resolution unit, and sampling may thus be carried out at a rate equal to the highest frequency component within the analog signal. Therefore, for a given analog-to-digital converter, dual channel conversion offers the opportunity to either examine twice the bandwidth or operate at one-half the rate as in the single channel case. Inasmuch as the technology exists to adequately support the higher sampling rates required in single channel conversion, this limitation was considered acceptable in the design of the Analog-to-Digital Control and Conversion subsystem.

## 2. Hardware Requirements

Dual channel analog-to-digital conversion requires two identical processing channels (sample-and-hold modules,

analog-to-digital converters, supporting circuitry) to simultaneously convert the quadrature related analog signals into the "real" and "imaginary" components of a complex data point. Single channel conversion requires only one processing channel, thereby reducing the number of components by one-half. This was considered highly advantageous in light of the space limitations imposed on the SSA prototype design.

## 3. Image and Zero Frequency Considerations

Performing spectral analysis by the dual channel technique results in a displayed spectrum which may contain misleading information. As explained in Appendix A, dual channel conversion results in a D.C. value in the baseband signal which represents the component of the RF signal at the local oscillator frequency. This appears in the spectral display as a signal at D.C. or zero frequency. Similarly, image frequencies may appear in the spectral display due to imbalances in the gains of the processing channels in the dual channel case. Either zero or image frequencies could lead the unsuspecting system operator to erroneously conclude that the R.F. signal contained components that are not in fact present. The fact that neither of these phenomena are present in single channel conversion, coupled with the fact the production versions of the SSA may eventually be operated by unsophisticated operators, make the latter technique both advantageous and desirable.

## 4. System Compatibility

Both conversion techniques are easily adaptable to

digital processing. However, dual channel conversion requires double the amount of computer interface for adequate control and monitoring and may restrict the flexibility of the host computer. Additionally, the single channel conversion technique lends itself readily to audio monitoring (and recording) of the baseband signal. This capability does not exist in the dual channel case as a result of the prebaseband division of the analog signal.

#### C. EQUIPMENT SELECTION

## 1. Sample Rate Requirements

The minimum acceptable sampling rate for the Analogto-Digital Control and Conversion subsystem is the Nyquist rate (see Section II. B. 1.). When this criterion is applied to a baseband signal, the sampling rate equals twice the bandwidth of that signal. However, if the bandwidth is taken, as is usually the case, as the half-power (or 3 dB) bandwidth, consideration must be given to aliasing. Aliasing results from the fact that a rectangular bandpass filter (BPF) is virtually impossible to implement and that a signal passed through such a BPF will have sloping, rather than abrupt, leading and trailing edges. If this signal is then sampled at the Nyquist rate, considerable distortion in the resultant spectrum may occur. The solution to aliasing is to sample at a rate based on a wider bandwidth, i.e., the 30 dB down bandwidth, where the effects of aliasing are not as significant. In the design of the Analog-to-Digital Control and Conversion subsystem, a rate of 2 MHz was considered

adequate to successfully sample the satellite's wideband transponder channel while a rate below 500 kHz was deemed appropriate for sampling the narrowband channels.

## 2. Bit Resolution Requirements

The analog-to-digital conversion of any signal results in the generation of quantization noise which is added onto the noise of the input signal. The quantization noise effect is 6 dB of SNR per bit of resolution. Determination of the number of bits used in the digital representation of the analog signal is thus a tradeoff between the desired dynamic range of the analog-to-digital converter and tolerable levels of quantization noise. Experience gained in this laboratory while operating the developmental SATCOM Signal Analyzer (see references 4-6) indicated that eight bits of resolution were adequate for the wideband channel and were within the realm of existing technology. Similarly, 12 bits of resolution were considered adequate for the representation of signals in the narrowband channels.

## 3. Equipment Selection

The major functional components of the Analog-to-Digital Control and Conversion subsystem are the sample-and-hold module and two analog-to-digital converters. For purposes of clarification, the remainder of this thesis will refer to the high-speed analog-to-digital converter as that converter which operates at a 2 MHz rate and provides eight bits of resolution; the low-speed analog-to-digital converter as the converter which operates at or below a 500 kHz rate

providing 12 bits of resolution. Selection of the components to be used to fulfill the design requirements involved comparisons of existing hardware based on the following factors:

- a. Specifications;

- b. Cost;

- c. Power supplied required;

- d. Power dissipation; and,

- e. Size

Based on the above criteria, the sample-and-hold module and low-speed analog-to-digital converter selected were the DATEL SHM-UH and DATEL ADC-EH12B3, respectively. In the case of the high-speed analog-to-digital converter, three units were selected for laboratory evaluation—the DATEL ABC-VH8B3, the TRW TDC-1001J, and the DDC (Digital Devices Corporation) ADC-1210. In each case the evaluation consisted of implementing the device, its supporting circuitry and power supplies on SK-10 breadboards and then applying signals similar to those which would be encountered in the operating system. Upon completion of the evaluations the TRW TDC-1001J was selected as the high-speed analog-to-digital converter.

## III. DETAILED OPERATION

#### A. INTRODUCTION

The Analog-to-Digital Control and Conversion subsystem receives a baseband analog signal from each of the four channels of the Spectrum Receiver. Within the subsystem these four analog signals are independently analog-to-digital converted at various sampling rates determined by the system operator. The resultant digital representations of the analog inputs are then presented to a bank of four array processors for Fast Fourier Transform processing (see Figure 2). The subsystem consists of four identical printed circuit (PC) boards (ADC Boards) containing the analog-to-digital conversion circuitry and one PC board (ADC Control Board) containing the requisite circuitry to control the four ADC Boards and the X-Y display analog-to-digital converter. The system operator may perform limited testing on any of the ADC Boards through the use of the ADC Test Box in conjunction with the ADC Control Board. Table I provides the required external inputs and outputs of this subsystem.

#### B. ADC BOARD

#### 1. Introduction

#### a. Functions

Each of the four ADC Boards perform the following functions: 1) sample-and-hold an incoming signal at a maximum

Cable assembly carrying HI/LOW-SELECT, SAMPLE-ENABLE, 20 MHz clock and Sample Frequency clock

Cable assembly carrying Sample Frequency and 20 MHz clocks Ribbon cable carrying Sample-Frequency-Select signals \*\*\* \*\*

Analog-to-Digital Control and Conversion Subsystem Block Diagram Figure 2

#### TABLE I

## ANALOG TO DIGITAL CONTROL AND CONVERSION SUBSYSTEM INPUT/OUTPUT SPECIFICATIONS

Power Supplies: +5 volts, + 15 volts (provided by chassis connections)

Analog Inputs:

Number 4 (1 per Spectrum Receiver

channel)

Voltage Range + 10 volts

Maximum input Voltage + 15 volts

Reference Input: 20 MHz @ 13 dBm (sine wave)

Sampling Rates:

High Speed 2 MHz

Low Speed Range 781 Hz - 500 kHz (selectable)

Selection Control 3 bits per analog input

Digital Outputs:

Format Two's complement or offset

binary (selectable)

Low Speed One 12 bit word

High Speed Two 8 bit words (successive

sample values) in parallel

Handshake 150 nanosecond positive pulse

(AP-400 compatible)

Clock Outputs for X-Y ADC:

Reference 20 MHz square wave

Sample Frequency Range 781 Hz - 96.2 kHz

Selection Control 2 bits

2 MHz clock rate; 2) analog-to-digital convert the sampled signal at one of five sampling rates; 3) output digital data in a format compatible with the AP-400 (array processor); and, 4) generate "handshake" signals to the AP-400. As previously mentioned, each of the ADC Boards operates in conjunction with one channel of the Spectrum Receiver subsystem. Inasmuch as the ADC Boards are identical, future reference in this thesis to "the" board may be taken to mean any one of the ADC Boards. A generalized block diagram of the operation of the ADC Board is provided as Figure 3.

## b. Inputs

The ADC Board receives all operating and control signals from the ADC Control Board. These signals are as follows:

- Sample-Frequency Clock;

- (2) HI/LOW-SELECT Signal;

- (3) SAMPLE-ENABLE Signal; and,

- (4) 20 MHz reference Clock

These signals and their functions will be explained in detail later in this thesis. The ADC Board also receives the baseband analog signal from the corresponding channel of the Spectrum Receiver.

## c. Outputs

The ADC Board generates a 12 bit digital representation of the input analog signal while operating in the low-speed mode and an eight bit representation in the high-speed mode. The appropriate digital signals to the mode of

Figure 3

ADC BOARD OPERATION

operation and the "handshake" signal are routed to the AP-400 array processor. Additional outputs include a +5 volt signal which is provided to the ADC Test Box and a common GROUND signal provided to the ADC Control Board.

### d. Implementation

The ADC Board is wholly contained on a standard PDP-11 QUAD size printed circuit (see Figure 4). Design layout and basic board construction were accomplished through the use of the facilities of the Etching Laboratory at NPS. The ADC Boards are designed to be mounted vertically on, and draw all power (+5 volts, +5 volts, GROUND) from, a standard PDP-11 backplane contained within a PLESSEY PM-1150/5 power chassis. Inputs from the ADC Control Board are brought onto the board via a CANNON DAM-7W25A Connector assembly which has provisions for two coaxial fittings and five standard pin connections. The signals carried by coaxial cable (20 MHz reference clock and Sample Frequency clock) are routed to their destinations via cable on the component side of the board. The analog signal interfaces with the ADC Board through a standard SMA Bulkhead fitting. Outputs from the ADC Board to the AP-400 exit the board via an ANSLEY 609-615M 34 pin ribbon cable mating connector. The GROUND and +5 volt outputs (to the ADC Control Board and ADC Test Box, respectively) are routed via the CANNON 7W25A connector. Pin connections for all connectors and backplane slots may be found in Appendix D.

Figure 4

ADC Board Component Layout

#### e. ADC Board Sections

The ADC Board has been subdivided into five functional sections. This division not only simplifies discussion of board operation but also represents an orderly progression in the signal processing which occurs on the board. The four sections are the Synchronization section, the Sample-and-Hold section, the Analog-to-Digital Conversion section and the Digital-Data-Selection section. An in-depth discussion of ADC Board operation will be accomplished by considering the operations performed within each section. The reader is advised to familiarize himself with Figure 3 prior to the reading of the following sections.

## 2. Synchronization Section

#### a. Introduction

The Syncrhonization section performs the following functions: 1) generation of the Sample-Command signal;

2) generation of the Start-Convert signals for both analogto-digital converters; 3) buffering and inversion of the HI/

LOW-SELECT signal; and, 4) selective enabling of the low-speed

Start-Convert signal. The schematic diagram for this section

is given in Figure 5, while Figure 6 depicts the time relationship among the various pulses generated in this section.

#### b. Master Pulse

The 40 nanosecond positive-going Master Pulse (MP) and its complement  $(\overline{MP})$  are generated by Ul, a 74121 monostable multivibrator. Triggering information is provided by the trailing edge of the Frequency clock which arrives

Synchronization Section Circuit Diagram

Figure 6 Synchronization Section Timing Diagram

directly at pins 3 and 4 via the center conductor of a coaxial cable. The braid of the cable is grounded adjacent to the integrated circuit and a 50 ohm impedance matching resistor is placed across the braid and center conductor. The width of the Master Pulse is determined by the internal resistor/25 picofarad capacitor combination and was selected to meet the 35 nanosecond (± 10 nanosecond) requirement of the sample-and-hold module with tolerance for variations in capacitor and resistor values.

## c. Sample-Command Pulse

The sample-and-hold module (DATEL SHM-UH) requires a Sample-Command signal of the previously mentioned width which is capable of sourcing 100 milliamperes of current. Accordingly, the complement of the Master Pulse (MP) is simultaneously provided to pins 1 and 13 of U3, a 74S140 dual 50 ohm line driver. All other inputs to U3 are held high so that the negative going pulse (MP) results in a positive pulse at the outputs. These outputs are combined, and, in conjunction with a 100 ohm pull up resistor, provide the Sample-Command pulse which is of correct width and current sourcing capability to drive the sample-and-hold module.

#### d. Start-Convert Pulse

A 200 nanosecond positive going pulse is used as the Start-Convert pulse for both analog-to-digital converters. This width was selected to exceed the minimum requirements (high speed converter--50 nanoseconds, low speed--100 nanoseconds) and to provide adequate tolerance for resistor/

capacitor values. The pulse is generated by U2, a 74121 monostable multivibrator with the width controlled by a 3.3 kilohm/82 picofarad combination across pins 10, 11 and 14. Triggering is supplied by the trailing edge of the Master Pulse, applied to pins 3 and 4. Use of this pulse for triggering provides approximately 85 nanoseconds of delay from the beginning of the sampling evolution until the analog-to-digital conversions begin, thus assuring that the acquisition time of the sample-and-hold (50 nanoseconds) has elapsed.

e. HI/LOW-SELECT Signal Buffering and Inversion The HI/LOW-SELECT signal and its complement are the most widely used control signals in the analog-to-digital conversion process. Because of the number of loads it drives on the ADC Board, it is buffered by double inversion at U4, a HEX Inverter. The complement (HI/LOW-SELECT) is generated by a single stage of inversion. In the Synchronization section, the HI/LOW-SELECT signal is used to enable the lowspeed Start-Convert signal. This enabling is required due to the low-speed analog-to-digital converter having a maximum conversion rate to 500 kHz. The use of a common Start-Convert signal to both converters implies that in the highspeed mode (conversion rate = 2MHz), the low-speed converter would be driven at four times its maximum rate. To avoid this situation, the low-speed Start-Convert pulse-train is logically OR-ed with the HI/LOW-SELECT signal (at U5), producing a constant "high" output and thereby disabling the lowspeed converter.

## 3. Sample-and-Hold Section

#### a. Introduction

In the Sample-and-Hold section the analog signal from the associated channel of the Spectrum Receiver is sampled at the desired sample rate. The section is designed around the DATEL SHM-UH sample-and-hold module and associated protection circuitry. The schematic diagram for this section is given in Figure 7.

## b. LM-318 Operational Amplifier

As shown in Figure 6, the baseband analog signal is applied to a unity gain LM-318 Operational Amplifier (OP-AMP) designed to operate in the differential mode. This configuration reduces ground loop noise. Laboratory experimentation revealed that operation in this mode with  $\pm$  15 volt power supplied results in a saturation voltage of  $\pm$  14 volts, which exceeds the input overvoltage protection range of the SHM-UH. The solution to this potential problem will be discussed in the following section.

#### c. Power and Overvoltage Protection

Experience in the operation of the SHM-UH in this laboratory has demonstrated that it is susceptible to failure if an analog signal is applied to the module without all power supplies operating. In order to avoid this occurrence, a CLARE PRMAlA05C reed relay was placed between the LM-318 OP-AMP and the analog input of the SHM-UH. The controlling voltage for this relay is the SAMPLE-ENABLE signal which is generated on the ADC Control Board. As previously mentioned,

Figure 7 Sample And Hold Section Circuit Diagram

the input overvoltage protection range of the SHM-UH ( $\pm$  10 volts) is less than the saturation voltage of the LM-318 OP-AMP. In order to protect against over-voltage inputs, a two-to-one divider network has been implemented immediately prior to the reed relay which ensures that the maximum input voltage to the SHM-UH is approximately  $\pm$  7 volts.

d. Sample-and-Hold Module, DATEL SHM-UH

The analog baseband signal from the Spectrum Receiver is sampled by the DATEL SHM-UH sample-and-hold module. It is controlled by the 40 nanosecond Sample-Command input generated in the Synchronization section and has a ± 5 volt full scale input range. The device is capable of operation at a sampling rate of 10 MHz which is well in excess of the maximum rate employed in this system. The output sampled values are noninverted ± 5 volt levels which are directly compatible with the input of the low-speed analog-to-digital converter and require reduction and offset to ensure compatibility with the high-speed converter input range. The SHM-UH has an internal offset trimpot which is adjusted according to the instructions contained in Appendix C. Detailed specifications of the SHM-UH may be found in Appendix B.

# 4. Analog-to-Digital Conversion Section

### a. Introduction

The Analog-to-Digital Conversion section performs two functions: 1) analog-to-digital conversion of the sampled analog data with eight or twelve bits of resolution;

2) generation or conditioning of End-of-Convert (EOC) signals

to ultimately be used as latch commands. The section was designed around the DATEL ADC-EH12B3 and TRW TDC-100lJ analog-to-digital converters and all supporting circuitry. Figure 8 is a schematic diagram for this section.

b. Low-Speed Analog-to-Digital Converter, DATEL ADC-EH12B3

Sampled analog signal values from the SHM-UH are routed directly to the DATEL ADC-EH12B3. This device provides a 12 bit representation of the input signal value and is capable of operation at a maximum rate of 500 kHz. It is controlled by the 200 nanosecond Start-Convert pulse generated in the Synchronization section. As demonstrated in Figure 9, the parallel output data and EOC signal are available approximately 2 microseconds after the leading edge of the Start-Convert pulse. The twelve bits of parallel output data is available in offset binary or two's complement format. The preferred option is selected through the use of a jumper wire on the reverse side of the ADC Board. Connecting the cable between pads J and A provides the offset binary format while connecting the wire between pads J and B provides the two's complement format (see Table II). The EOC signal is a negative-going pulse which occurs 100 nanoseconds after the conversion is complete. This signal is then triple inverted by the inverters in U20 and provided to the Digital-Data-Selection section for use as a latching signal. tions for the adjustment of the external 20 ohm trimpot (GAIN ADJUST) and 200 ohm trimpot (OFFSET ADJUST) are located in Appendix C, while Appendix B provides detailed operating

Analog-to-Digital Conversion Section Circuit Diagram

Figure 9 Low Speed Analog-To-Digital Conversion Timing Diagram

TABLE II

OFFSET BINARY AND TWO'S COMPLEMENT DATA FORMATS

## LOW-SPEED CONVERSION FORMATS

| Analog Input Voltage |      | t Bina<br>Connec | ry<br>tion)* |      | Compl<br>Connec |      |

|----------------------|------|------------------|--------------|------|-----------------|------|

| +5.00 volts          | 1111 | 1111             | 1111         | 0111 | 1111            | 1111 |

| +2.50 volts          | 1100 | 0000             | 0000         | 0100 | 0000            | 0000 |

| 0.00 volts           | 1000 | 0000             | 0000         | 0000 | 0000            | 0000 |

| -2.50 volts          | 0100 | 0000             | 0000         | 1100 | 0000            | 0000 |

| -5.00 volts          | 0000 | 0000             | 0000         | 1000 | 0000            | 0000 |

<sup>\*</sup>Pads A, B and J are located adjacent to pin 1 of the ADC-EH12B3 module.

## HIGH-SPEED CONVERSION FORMATS

| Analog Input Voltage | Offset E | Binary<br>nnection)* |      | omplement<br>nection) * |

|----------------------|----------|----------------------|------|-------------------------|

| 0.000 volts          | 1111     | 1111                 | 0111 | 1111                    |

| 125 volts            | 1100     | 0000                 | 0100 | 0000                    |

| 250 volts            | 1000     | 0000                 | 0000 | 0000                    |

| 375 volts            | 0100     | 0000                 | 1100 | 0000                    |

| 500 volts            | 0000     | 0000                 | 1000 | 0000                    |

<sup>\*</sup>Pads A, B and J are located adjacent to pin 1 of U22.

specifications of the ADC-EH12B3.

c. High-Speed Analog-to-Digital Converter, TRW TDC-1001J

The TRW TDC-1001J analog-to-digital converter provides an eight bit representation of the analog input value and is capable of operation at a maximum rate of 2.5 The input analog voltage range is + .25 volts around a center value of -.25 volts, which requires an offset and range adjustment of the sampled values originating at the SHM-UH sample-and-hold module. The range adjustment was accomplished by a twenty-to-one voltage division of the analog signal and offset adjustment was similarly accomplished by ten-to-one voltage division of the -5 volt power supply. Instructions for the requisite adjustment of the 50 kilohm trimpot to obtain the offset value are found in Appendix C. Laboratory experimentation revealed that this module is highly susceptibel to instabilities in the + 5 volt power supplies. much as -5 volts is not available on the PDP-11 backplane, and to provide essentially ripple free supply voltages, it was decided to provide these supplies by + 5 volt regulators. The reference input (-5 volts) applied to pin 13 is obtained by a ten-to-one division of the -5 volt regulator output through the use of a fixed 1 kilohm resistor and a 50 kilohm trimpot. Appendix C contains instructions for this adjustment. The 20 MHz reference clock required by this module is applied directly to pin 18 via the center conductor of a coaxial cable which is terminated across a 50 ohm impedance matching resistor. The output of the TDC-1001J is eight bits of parallel

data presented in inverted offset binary format, i.e., the more negative full scale value (-.5 volts) appears as eight logical "ones". Converting this output to a true offset binary format is accomplished through the use of inverters in U20 and U22. The output of these inverters may be converted into two's complement or offset binary format by making the same pad/jumper cable connections as in the low-speed case (see Table II). The EOC signal is used to control the output latch register internal to the device and thus occurs approximately 110 nanoseconds prior to the output data being available at pins 3-9 and 11 (see Figure 10). The disparity in time, and the unique output format from the ADC Board to the AP-400 while operating in the high-speed mode, make this EOC signal unsuitable for use in the Digital-Data-Selection section which requires two separate latching signals during high-speed operation (see Section III, B.5.). Accordingly, the TDC-1001J EOC signal is applied as the triggering signal to Ul9, a 74121 monostable multivibrator, generating a 150 nanosecond positive-going pulse. This pulse is in turn applied as the clock signal to a negative edge triggered J-K flip-flop (contained in Ul9) which is configured in the toggle mode. The use of the trailing edge of the pulse generated in Ul9 as the clock signal to Ul8 ensures that the positive transitions occurring at either the Q or  $\overline{\mathbb{Q}}$  outputs are sufficiently delayed to act as latching commands. flip-flop is enabled by the HI/LOW-SELECT signal and thus is disabled during operation in other than the high-speed mode.

Figure 10 High Speed Analog-to-Digital Conversion Timing Diagram

The Q output of the J-K flip-flop makes a positive transition upon the completion of the first conversion after the high-speed mode is selected (and all subsequent odd numbered conversions) and hence is referred to as HIGH-SPEED-WORD-ONE-EOC. Similarly the  $\overline{\mathbb{Q}}$  output makes a positive transition upon completion of the second conversion (and all subsequent even numbered conversions) and is referred to as HIGH-SPEED-WORD-TWO-EOC.

# 5. Digital-Data-Selection Section

#### a. Introduction

The Digital-Data-Selection section performs three functions: 1) multiplexing of digital data and latching commands to the output latches; 2) latching the output data; and, 3) generation of the "handshake" signal to the AP-400. The schematic of this section is shown in Figure 11.

## b. Output Formats

The outputs from the Digital-Data Selection section are provided directly to the AP-400 array processor.

This device accepts up to 24 bits of data at a maximum 1 MHz rate, and is capable of processing these data bits (under PDP-11/34 control) as either one "word" or two "words" (of 16 and eight bit lengths). The AP-400 may be programmed to read any number of these bits in either format. In the low-speed mode of operation the 12 bits of output data are routed to the AP-400 inputs reserved for the 16 bit "word" and all nondata inputs are ignored. In the high speed mode two eight bit "words" are "packed" into the first eight inputs of the 16

Figure 11 Digital Data Selection Section Circuit Diagram

bit "word" and all eight inputs of the eight bit "word", and the array processor is programmed to read these 24 bits as one "word" but to interpret them as two separate sample values. This technique allows the analog-to-digital conversions to be performed at a 2 MHz rate with the digital outputs being processed at a 1 MHz rate with no inherent loss of data. The required "handshake" signal to the array processor (IP/TRS INTERRUPT) is a 150 nanosecond positive-going pulse indicating that data is ready at the processor inputs. This signal is generated by U21, a 74121 monostable multivibrator, with a 2.7 kilohn resistor/68 picofarad capacitor combination across pins 10, 11 and 14. During low-speed operation, triggering is provided by the ADC-EH12B3 EOC signal while in the high-speed mode the trigger is provided by the HIGH-SPEED-WORD-TWO-EOC.

### c. Data Latching

As demonstrated in Figure 11, output data from the Digital-Data-Selection section is made available to the AP-400 at various combinations of five 74175 quad memory latches (U8-U12). In the low-speed mode of operation, the 12 output bits appear at the outputs of U10-U12, with latching commands supplied by the positive transition of the ADC-EH12B3 EOC signal. The unused output latches (U8, U9) are disabled by the application of the HI/LOW-SELECT signal to pin one of both IC's. During high-speed operation, the eight digital data bits of the first conversion are applied to two intermediate latches (U13, U14) with latching commands to these

latches by the HIGH-SPEED-WORD-ONE EOC signal. Upon completion of the second high-speed conversion, these eight bits and the eight bits from the second conversion are latched directly into U8, U9, Ull and Ul2, respectively, with latching commands supplied by the HIGH-SPEED-WORD-TWO-EOC signal. In the high-speed mode of operation the unused output latch (Ul0) is disabled by the HI/LOW-SELECT signal applied to pin one of that latch. Therefore, during high-speed operation the eight output bits of the first conversion are double latched and all 16 bits are applied to the output latches simultaneously. In both high-speed and low-speed modes the "handshake" signal appears at the output approximately 40 nanoseconds after the digital data appears at the outpus of the appropriate latches. This delay is attributable to the propagation time of the monostable multivibrator (U21) generating this signal.

## d. Data Multiplexing

In order to minimize the number of components utilized, the first eight data bits of the low speed mode and the eight bits from the second conversion in the high-speed mode utilize the same output latches (Ull, Ul2). These 16 bits of data are multiplexed prior to the output latches by two 74157, quad two-to-one multiplexers (Ul6, Ul7), with selection commands provided by the HI/LOW-SELECT signal. The latching commands to the five output latches (ADC-EH12B3 EOC and HIGH-SPEED-WORD-TWO-EOC) are similarly multiplexed through an additional 74157 (Ul5) which also has selection commands supplied by the HI/LOW-SELECT signal.

#### C. ADC CONTROL BOARD

# 1. Introduction

#### a. Functions

The ADC Control Board is designed to provide all control signals to each of the four ADC Boards. Accordingly, it performs the following functions: 1) conversion of a 20 MHz sinusoid into a 20 MHz pulse-train; 2) generation of all five Sample-Frequency-Clock signals; 3) generation of the SAMPLE-ENABLE signal; and, 4) generation of the HI/LOW-SELECT signal.

## b. Inputs

The Master Control Bus of the PDP-11/34 provides all operating signals to the ADC Control Board. These signals include three ADC Sample-Frequency-Selection signals for each of the ADC Boards and two Sample-Frequency-Selection signals for the X-Y modulation display. All operating frequencies in the SSA Prototype system are based on a 5 MHz rubidium standard. The 20 MHz sinusoidal input to the ADC Control Board is generated by the up conversion of the 5 MHz sinusoid in the frequency multiplication unit (see Figure 1). Additionally, the ADC Control Board shares a common GROUND with each of the ADC Boards, the analog-to-digital converter of the X-Y Modulation Display, the Master Control Bus, and, when appropriate, the ADC Test Box.

#### c. Outputs

The ADC Control Board outputs the following signals to each of the ADC Boards:

- (1) 20 MHz reference clock;

- (2) Sample frequency clock;

- (3) SAMPLE ENABLE signal;

- (4) HI/LOW SELECT signal.

Additionally, both of the clock signals are provided to the analog-to-digital converter of the X-Y Modulation Display.

## d. Implementation

The ADC Control Board was designed for implementation on a standard PDP-11 QUAD size printed circuit board with a two inch extension in the direction of slot B (see Figure 12). Use was made of the facilities of the NPS Etching Lab in the design layout and basic construction of the ADC Control Board. Inputs from the Master Control Bus arrive at this board via a ANSLEY 609-615M 16-pin ribbon cable mating connector which is equipped with a polarizing key to avoid incorrect mounting. The 20 MHz sinusoid is applied via coaxial cable to a standard SMA Bulkhead fitting. Outputs to each of the four ADC Boards are routed via four CANNON 7W25A connectors which, as mentioned previously, have provisions for two coaxial fittings and five standard pin connections. The two clock signals for the X-Y Modulation Display exit the board via the outer two (of three) coaxial fittings on a CANNON 3W3S connector. The ADC Control Board will be mounted adjacent to the four ADC Boards within the PLESSEY power chassis and will draw all power supplies (+5 volts, +15 volts, GROUND) from appropriate connections on the PDP-11 backplane. Appendix D provides a listing of pin connections for all

ADC CONTROL BOARD COMPONENT LAYOUT

connectors and backplane slots.

#### e. ADC Control Board Section

As in the case of the ADC Boards, the ADC Control Board has been divided into functional sections to facilitate discussion of board operations. The operations performed within each of these areas will be presented in the following sections of this thesis. The three sections are the Pulse Forming/Power Protection section, the Divider Network, and the Frequency-Selection section. Figure 13 is provided as a generalized block diagram of the operation of the ADC Control Board.

## 2. Pulse Forming/Power Protection Section

#### a. Introduction

The Pulse Forming/Power Protection section performs three functions: 1) conversion of the 20 MHz sinusoid into a 20 MHz pulse-train; 2) generation of all reference frequencies for use in the divider network; and, 3) generation of the SAMPLE-ENABLE signal. The schematics of this section are presented in Figure 14.

## b. SAMPLE-ENABLE Signal

As mentioned in Section III.A.3., the application of an analog signal to the SHM-UH sample-and-hold module with one or more power supplies not operating is a failure condition for this device. Accordingly, each of the three power supplies required for SHM-UH operation is provided to the input of a CLARE PRMA 1A05C to pull in the relay of that device. An internal protection diode in each reed relay requires

- 1. 20 MHz REFERENCE CLOCK

- 2. SAMPLE FREQUENCY CLOCK

- 3. HI/LOW SELECT

- 4. SAMPLE ENABLE

- 5. GROUND

Figure 13 ADC CONTROL BOARD OPERATION

Pulse Forming/Power Protection Section Circuit Diagram

that the more positive signal be applied to pin 2 and that the ±15 volt inputs be routed through current limiting resistors (1 kilohm). A +5 volt signal is then passed in series through the three relays and is routed to the ADC Boards as the SAM-PLE-ENABLE signal. Should one of the power supplied malfunction, the corresponding relay would open causing the SAMPLE-ENABLE signal to go "OFF" and open the relay which passes the analog signal to the SHM-UH. Three Light-Emitting-Diodes (LED's) are mounted at the upper edge of the ADC Control Board for quick visual reference to power supply status. The normal, power-on, condition is indicated by an illuminated LED.

#### c. Pulse Generation

The 20 MHz sinusoid from the frequency multiplication unit is converted to a 20 MHz pulse train by application to the base of a 2N3945 high power NPN transistor configured as shown in Figure 14. Double inversion of the collector output at Ul provides TTL compatible levels as well as a 50% duty cycle. The collector and base resistor values were determined to provide flexibility in the transistor types which could be employed in this circuit. Laboratory testing of three different transistors (2N3501, 2N3118, 2N3945) yielded satisfactory formation of the pulse train. The input sinusoid is designed to have a +13 dBm level; the circuit as designed works satisfactorily with sinusoidal input levels as low as +6 dBm, indicating that a 75% decrease in input level is tolerable. The 20 MHz pulse train is routed to the ADC Boards and X-Y Modulation Display where it serves as the reference clock for

the high-speed analog-to-digital converters.

## d. Reference Signals

The ADC Control Board is capable of producing one high-speed and four low-speed Sample-Frequency clock signals. The range of frequencies available provides a great deal of flexibility in resolution capability in the spectral analyses to be performed. Accordingly, this section of the board provides three reference signals (10 MHz, 2 MHz, 200 kHz) to the Divider Network where the low-speed sampling frequencies are generated (Note: 2 MHz is also the high-speed sampling frequency). As demonstrated in Figure 14, the 20 MHz pulse train is applied to U2, a D flip-flop designed to divide by two. This 10 MHz output signal is then routed to U3, a 74161 configured to divide by five. Finally, the resultant 2 MHz signal is divided by ten at U5, another 74161. These three reference frequencies are then routed to the Divider Network.

# 3. Divider Network

#### a. Introduction

As previously mentioned, the Divider Network generates the low-speed sampling frequencies to be used in the spectral analyses by performing various divisions on the three reference frequencies. Figure 15 is a schematic of this section while Figure 16 provides a block diagram of the sample frequency generation process.

## b. Sample Frequency Generation

Each of the reference frequencies generated in the Pulse Forming/Power Protection section is routed to a

Figure 15 Divider Network Circuit Diagram

Figure 16 Sample Frequency Generation

variable modulo (up to 256) divider combination consisting of a 7420 dual input NAND gate, two 74161 divide-by-16 counters and two board-mounted, quad DPDT switches. This combination of components offers a great deal of flexibility in the selection of sampling frequencies (by making available all prime number in the 0-256 range) and simplifies the implementation of predetermined sampling frequencies. The 10 MHz reference frequencies may be converted into sampling frequencies in the 39.1 kHz to 10 MHz range through the application of such a combination. Similarly, the 2 MHz reference frequency could be converted into sampling frequencies in the 7.8 kHz to 2 MHz range; the 200 kHz reference input into sampling frequencies in the 781 to 200 kHz range. Control of the exact sampling frequency desired is accomplished by manipulation of the two quad switch packages which in turn control the preset load inputs to the divider I.C.'s. Implementation of a particular sampling frequency is accomplished by first determining which of the above ranges is appropriate to the desired frequency. The divider modulo number is then determined by division of the corresponding reference frequency by the desired sampling frequency (round-off may be required). The programming of the eight DPDT switches within each combination is determined by subtracting the modulo division number from 255 and converting the result to a base two representation. switches in each combination represent ascending powers of the base two  $(2^0, 2^1 \dots)$ , reading from left to right. The UP position on each switch places a logical "1" on that switch's output while the DOWN position places a logical "0" on the output. Using this technique, the binary representation of the result of the (255-modulo division number) subtraction is placed on the eight switches and the desired frequency is generated at pin nine of the right most 74161 in the combination. As demonstrated in Figure 15, the tentative values of the five sampling frequencies are 1.5 kHz, 12.0 kHz, 96.2 kHz, 333.3 kHz and 2.0 MHz (all values rounded to nearest tenth) and are designated sample frequencies 1-5 respectively. Table III lists the switch settings utitlized to obtain the low speed sampling frequencies. The sample frequencies thus generated are routed to the Frequency Selection section.

# 4. Frequency-Selection Section

## a. Introduction

The Frequency-Selection section performs three functions: 1) selection of the desired sampling frequency for each ADC Board and the X-Y Modulation Display; 2) selective disabling of each ADC Board and X-Y Modulation Display; 3) generation of HIGH/LOW-SELECT signal. The schematic representation of this section is provided as Figure 17.

### b. Sample-Frequency Selection

The selection of the sample frequency for each ADC Board and the X-Y Modulation Display is accomplished through the use of five 74151 eight-to-one multiplexers (U-11 through U15). The five sampling frequencies generated in the Divider Network are applied to the multiplexer for each of the ADC Boards (U11 - U14) while the multiplexer for the X-Y

TABLE III

SWITCH SETTINGS FOR TENTATIVE SAMPLING FREQUENCIES

| C4                 | 0       | 0        | 1        | 1         |

|--------------------|---------|----------|----------|-----------|

| C3                 | ٦       | 1        | 0        | 7         |

| C2                 | ٦       | 0        | 0        | 1         |

| SWIT<br>C1         | ٦       | ٦        | 7        | 0         |

| RIGHT SWITCH CI CZ | U35     | U33      | U31      | U29       |

| C4                 | 1       | П        | 0        | 0         |

| C3                 | 0       | 0        | Т        | 0         |

| H<br>C2            | Н       | 0        | 1        | 0         |

| LEFT SWITCH        | 0       | 0        | Т        | 7         |

| LEFT               | U34     | U32      | 030      | U28       |

| FREQUENCY          | 1.5 kHz | 12.0 kHz | 96.2 kHz | 333.3 kHz |

"0" = DOWN, "1" = UP

Frequency Selection Section Circuit Diagram

Modulation Display receives only Sample Frequencies 1-3. Design of this section includes the provision for the selective disabling of any of the ADC Boards and/or the X-Y Modulation Display. The disabling signal is a logical "0" placed on the Sample-Frequency coaxial cable to the board being disabled. This signal is obtained by the application of a logical "1" (+5 volts) to the DO input of each multiplexer (pin 4), and is designated Sample Frequency 0. This value is inverted by the corresponding 74S140 dual 50 ohm line device thereby creating the disabling signal. Selection of the desired sampling frequency is controlled by the Sample-Frequency-Selection signals received from the Master Control Bus of the PDP-11/34. The multiplexer controlling the output frequency to each of the ADC Boards receives a three bit selection signal which allows for the selection of all six sample frequencies. Inasmuch as the multiplexer for the X-Y Modulation Display has only four possible sample frequency options, it receives a two bit selection signal. correlates the Sample-Frequency-Selection signals to the resultant output signals. As previously mentioned, each output sample frequency, as well as the 20 MHz reference clock, is applied to a 74S140 component to provide sufficient current sourcing for transmission via coaxial cable. All output signals to ADC Boards one through four exit the ADC Control Board via connectors J-1 through J-4, respectively. Connector J-5 is the interface for the two clock signals routed to the X-Y Modulation Display.

TABLE IV

SAMPLE FREQUENCY SELECTION

| Signal | (to | quency Select<br>each 74151)<br>10 Pin 11 | Sample Frequency<br>Number | Sample Frequency<br>Value |

|--------|-----|-------------------------------------------|----------------------------|---------------------------|

| 0      | 0   | 0                                         | 0                          | None, wired to +5 volts   |

| 0      | 0   | 1                                         | 1                          | 1.5 kHz                   |

| 0      | 1   | 0                                         | 2                          | 12.0 kHz                  |

| 0      | 1   | 1                                         | 3                          | 96.0 kHz                  |

| 1      | 0   | 0                                         | 4*                         | 333.3 kHz                 |

| 1      | 0   | 1                                         | 5*                         | 2.0 MHz                   |

<sup>\* --</sup> not available to multiplexer for X-Y Modulation Display (Ul5)

### c. HI/LOW-SELECT Signal