## **AFRL-RI-WP-TR-2008-1529**

# TERA-OP RELIABLE INTELLIGENTLY ADAPTIVE PROCESSING SYSTEM (TRIPS) IMPLEMENTATION

Stephen W. Keckler, Doug Burger, Kathryn S. McKinley, Steve Crago, and Richard Lethin The University of Texas at Austin

**SEPTEMBER 2008 Final Report**

Approved for public release; distribution unlimited.

See additional restrictions described on inside pages

#### STINFO COPY

AIR FORCE RESEARCH LABORATORY

INFORMATION DIRECTORATE

WRIGHT-PATTERSON AIR FORCE BASE, OH 45433-7334

AIR FORCE MATERIEL COMMAND

UNITED STATES AIR FORCE

#### NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report was cleared for public release by the Defense Advanced Research Projects Agency's Public Affairs Office and is available to the general public, including foreign nationals. Copies may be obtained from the Defense Technical Information Center (DTIC) (http://www.dtic.mil).

AFRL-RI-WP-TR-2008-1529 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH THE ASSIGNED DISTRIBUTION STATEMENT.

\*//Signature//

ALFRED SCARPELLI

Project Engineer Embedded Information Sys Engineering Branch Advanced Computing Division

//Signature//

JAMES S. WILLIAMSON, Chief Embedded Information Sys Engineering Branch Advanced Computing Division

This report is published in the interest of scientific and technical information exchange and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

<sup>\*</sup>Disseminated copies will show "//signature//" stamped or typed above the signature blocks.

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YY)              | 2. REPORT TYPE    |                       | 3. DATES COV | /ERED (From - To)                           |

|----------------------------------------|-------------------|-----------------------|--------------|---------------------------------------------|

| September 2008                         | Final             |                       | 25 April     | 2003 – 30 September 2008                    |

| 4. TITLE AND SUBTITLE                  |                   |                       |              | 5a. CONTRACT NUMBER                         |

| TERA-OP RELIABLE INTELLIG              | F33615-03-C-4106  |                       |              |                                             |

| (TRIPS) IMPLEMENTATION                 |                   |                       |              | 5b. GRANT NUMBER                            |

|                                        |                   |                       |              | 5c. PROGRAM ELEMENT NUMBER                  |

|                                        |                   |                       |              | 62712E                                      |

| 6. AUTHOR(S)                           |                   | 5d. PROJECT NUMBER    |              |                                             |

|                                        |                   |                       | _            | P366                                        |

| Stephen W. Keckler, Doug Burger,       | Kathryn S. McKii  | nley, Steve Crago, ar | nd           | 5e. TASK NUMBER                             |

| Richard Lethin                         |                   |                       |              | 41                                          |

|                                        |                   |                       |              | 5f. WORK UNIT NUMBER                        |

|                                        |                   |                       |              | P3664106                                    |

| 7. PERFORMING ORGANIZATION NAME(S) AN  | ND ADDRESS(ES)    |                       |              | 8. PERFORMING ORGANIZATION                  |

|                                        |                   |                       |              | REPORT NUMBER                               |

| The University of Texas at Austin      |                   |                       |              |                                             |

| Department of Computer Sciences        |                   |                       |              |                                             |

| 1 University Station, C0500            |                   |                       |              |                                             |

| Austin, TX 78712-0233                  |                   |                       |              |                                             |

| 9. SPONSORING/MONITORING AGENCY NAM    | IE(S) AND ADDRESS | (ES)                  |              | 10. SPONSORING/MONITORING AGENCY ACRONYM(S) |

| Air Force Research Laboratory          |                   | DARPA/IPTO            |              | AFRL/RITA                                   |

| Information Directorate                |                   | 3701 Fairfax Driv     | -            | 11. SPONSORING/MONITORING                   |

| Wright-Patterson Air Force Base, C     | OH 45433-7334     | Arlington, VA 22      | 2203-1714    | AGENCY REPORT NUMBER(S)                     |

| Air Force Materiel Command             |                   |                       |              | AFRL-RI-WP-TR-2008-1529                     |

| United States Air Force                |                   |                       |              |                                             |

| 12. DISTRIBUTION/AVAILABILITY STATEMEN | Т                 |                       |              |                                             |

Approved for public release; distribution unlimited.

#### 13. SUPPLEMENTARY NOTES

PAO case number 12927, 03 Mar 2009. Document contains color.

The Tera-op Reliable Intelligently Adaptive Processing System (TRIPS) is a novel computer system designed to address technology scaling challenges, to provide high performance through concurrency, and to demonstrate mechanisms for hardware polymorphism. The team has constructed a full-system TRIPS prototype including a new Explicit Data Graph Execution (EDGE) instruction set architecture, custom application-specific integrated circuit (ASIC) chips, system circuit boards, a custom compiler with new optimization capabilities, a software development kit, and support for multithreaded parallel programs. Consisting of approximately 170 million transistors in a 130nm technology, the TRIPS chip includes two coarse grained processors, each with 16 ALUs (including floating-point units) that execute in parallel. TRIPS systems of up to 20 chips have been deployed at UT-Austin, ISI-East, and the Air Force Research Laboratory (AFRL). The prototype demonstrates per-processor performance (measured in cycles) of up to three times better than leading commercial products. Performance analysis results have led to follow-on architectures that employ dynamic polymorphism to tailor the capabilities of the hardware to the demands of the software.

#### 15. SUBJECT TERMS

Scalable Architectures, Compilers, Polymorphous Computing, Parallel Software

| 16. SECURITY CLASSIFICATION OF: |  |                              | <b>-</b> □          |                 | 19a. NAME OF RESPONSIBLE PERSON (Monitor)                   |  |

|---------------------------------|--|------------------------------|---------------------|-----------------|-------------------------------------------------------------|--|

| a. REPORT Unclassified          |  | c. THIS PAGE<br>Unclassified | OF ABSTRACT:<br>SAR | OF PAGES<br>112 | Al Scarpelli  19b. TELEPHONE NUMBER (Include Area Code) N/A |  |

## **Table of Contents**

| Li | st of F    | Figures                                                      | vi   |

|----|------------|--------------------------------------------------------------|------|

| Li | st of T    | Tables                                                       | vii  |

| Ac | know       | vledgement                                                   | viii |

| 1  | Exec       | cutive Summary                                               | 1    |

| 2  | Intro      | oduction                                                     | 2    |

| 3  | EDG        | GE Architectures                                             | 4    |

|    | 3.1        | Background                                                   | 4    |

|    | 3.2        | Explicit Data Graph Execution (EDGE) ISAs                    | 4    |

|    |            | 3.2.1 Block-atomic Execution                                 | 4    |

|    |            | 3.2.2 Direct Instruction Communication with Explicit Targets | 4    |

|    | 3.3        | TRIPS ISA Specification                                      | 5    |

|    |            | 3.3.1 Predication                                            | 7    |

|    | 3.4        | Code Examples                                                | 8    |

|    | 3.5        | Summary                                                      | 11   |

|    |            | ·                                                            |      |

| 4  | TRI        | PS Microarchitecture                                         | 13   |

|    | 4.1        | Processor Microarchitecture                                  | 13   |

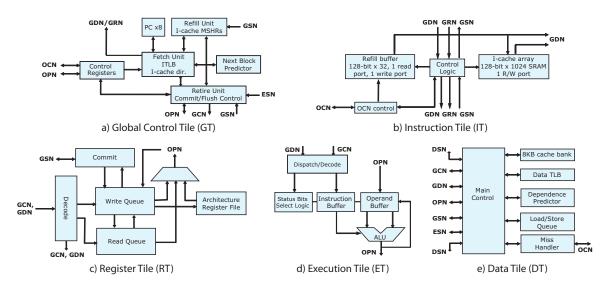

|    |            | 4.1.1 Global Control Tile (GT)                               | 14   |

|    |            | 4.1.2 Instruction Tile (IT)                                  | 15   |

|    |            | 4.1.3 Register Tile (RT)                                     | 15   |

|    |            | 4.1.4 Execution Tile (ET)                                    | 16   |

|    |            | 4.1.5 Data Tile (DT)                                         | 16   |

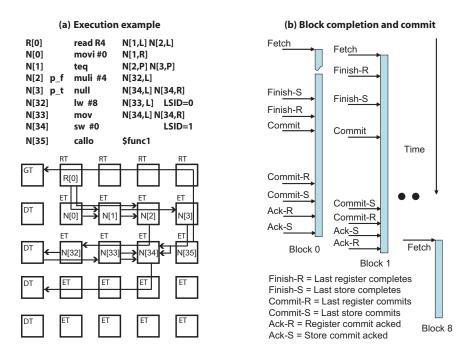

|    | 4.2        | Distributed Microarchitectural Protocols                     | 16   |

|    |            | 4.2.1 Block Fetch Protocol                                   | 16   |

|    |            | 4.2.2 Distributed Execution                                  | 17   |

|    |            | 4.2.3 Block/Pipeline Flush Protocol                          | 18   |

|    |            | 4.2.4 Block Commit Protocol                                  | 18   |

|    | 4.3        | Overheads of Distributed Microarchitecture                   | 19   |

|    |            | 4.3.1 Area Overheads                                         | 19   |

|    |            | 4.3.2 Distributed Protocol Overheads                         | 20   |

|    | 4.4        | Non-Uniform Level-2 Cache System                             | 21   |

|    |            | 4.4.1 TRIPS Physical Address Space                           | 22   |

|    |            | 4.4.2 Memory Tile Design                                     | 22   |

|    |            | 4.4.3 Configuration                                          | 23   |

|    | 4.5        | Summary                                                      | 24   |

| _  | TDI        | DC Deceloture Control                                        | 25   |

| 5  |            | PS Prototype System  TDIPS Chia Landau antation              | 25   |

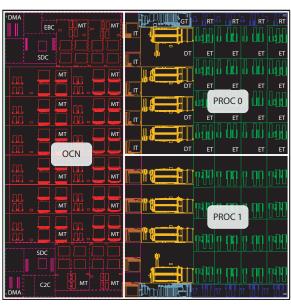

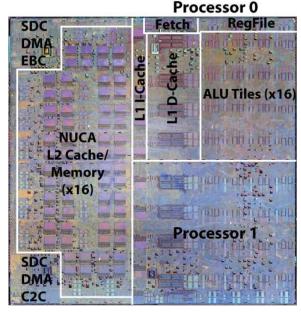

|    | 5.1        | TRIPS Chip Implementation                                    | 25   |

|    |            | 5.1.1 Floorplan                                              | 26   |

|    |            | 5.1.2 Physical Design                                        | 26   |

|    |            | 5.1.3 Verification                                           | 27   |

|    | 5.0        | 5.1.4 Timing                                                 | 28   |

|    | 5.2        | TRIPS System Design                                          | 28   |

|    |            | 5.2.1 Motherboard                                            | 30   |

|    | <i>5</i> 2 | 5.2.2 Daughtercard                                           | 31   |

|    | 5.3        | Summary                                                      | 32   |

| 6 | TRI                 | S Compiler                                                                                                                                                                                                                                                                          | 33                                           |

|---|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

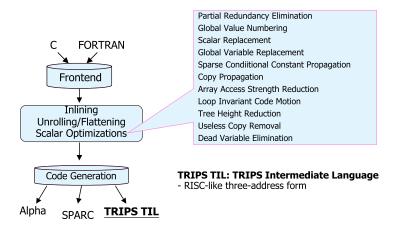

|   | 6.1                 | Compiler Structure                                                                                                                                                                                                                                                                  | 34                                           |

|   | 6.2                 | Frontend Scalar Optimizations                                                                                                                                                                                                                                                       | 34                                           |

|   | 6.3                 | TRIPS Intermediate Language Form                                                                                                                                                                                                                                                    | 34                                           |

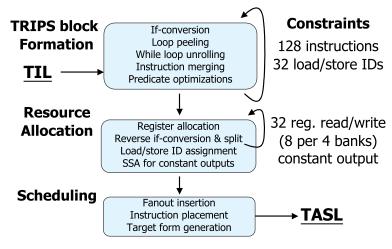

|   | 6.4                 | Compiler Backend Approach                                                                                                                                                                                                                                                           | 36                                           |

|   | 6.5                 | Satisfying Resource Constraints                                                                                                                                                                                                                                                     | 37                                           |

|   | 6.6                 | TRIPS Block Formation                                                                                                                                                                                                                                                               | 38                                           |

|   | 6.7                 | Banked Register Allocation                                                                                                                                                                                                                                                          | 38                                           |

|   | 6.8                 | Instruction Scheduling                                                                                                                                                                                                                                                              | 39                                           |

|   |                     | 6.8.1 Spatial Path Scheduling                                                                                                                                                                                                                                                       | 39                                           |

|   |                     | 6.8.2 Refining the SPS Cost Function using Learning                                                                                                                                                                                                                                 | 40                                           |

|   | 6.9                 | Summary                                                                                                                                                                                                                                                                             | 41                                           |

|   |                     |                                                                                                                                                                                                                                                                                     |                                              |

| 7 |                     | S Software Development Kit                                                                                                                                                                                                                                                          | 42                                           |

|   | 7.1                 | Runtime Libraries                                                                                                                                                                                                                                                                   | 42                                           |

|   | 7.2                 | Binary Utilities                                                                                                                                                                                                                                                                    | 42                                           |

|   | 7.3                 | Software Simulators and Debuggers                                                                                                                                                                                                                                                   | 43                                           |

|   |                     | 7.3.1 Functional Simulator                                                                                                                                                                                                                                                          | 44                                           |

|   |                     | 7.3.2 Timing Simulator                                                                                                                                                                                                                                                              | 44                                           |

|   |                     | 7.3.3 System Simulator                                                                                                                                                                                                                                                              | 44                                           |

|   |                     | 7.3.4 System call support                                                                                                                                                                                                                                                           | 44                                           |

|   |                     | 7.3.5 Critical path analysis                                                                                                                                                                                                                                                        | 44                                           |

|   |                     | 7.3.6 Debugger                                                                                                                                                                                                                                                                      | 45                                           |

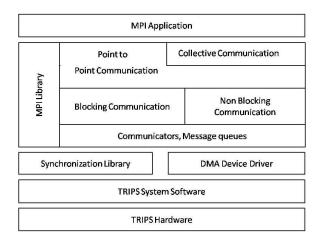

|   | 7.4                 | System Software                                                                                                                                                                                                                                                                     | 45                                           |

|   |                     | 7.4.1 System software components                                                                                                                                                                                                                                                    | 45                                           |

|   |                     | 7.4.2 Board Software                                                                                                                                                                                                                                                                | 46                                           |

|   |                     | 7.4.3 Resource Manager                                                                                                                                                                                                                                                              | 47                                           |

|   | 7.5                 | Summary                                                                                                                                                                                                                                                                             | 47                                           |

| 8 | Soft                | are Support for Parallelism                                                                                                                                                                                                                                                         | 48                                           |

| o | 8.1                 | Message Passing Interface                                                                                                                                                                                                                                                           | 48                                           |

|   | 0.1                 | 8.1.1 Simplifications to MPI library                                                                                                                                                                                                                                                | 48                                           |

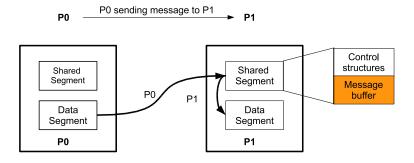

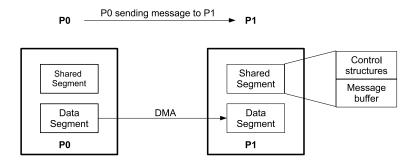

|   |                     | 8.1.2 Message passing on TRIPS                                                                                                                                                                                                                                                      | 49                                           |

|   |                     | 8.1.3 Placement of Message Queues                                                                                                                                                                                                                                                   | 49                                           |

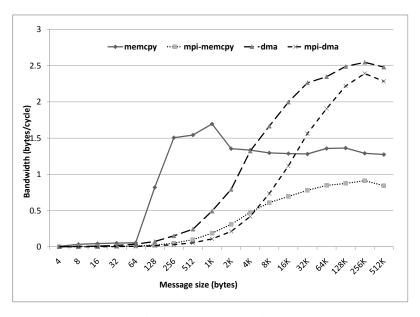

|   |                     | 8.1.4 Data Transfer Modes                                                                                                                                                                                                                                                           | 50                                           |

|   |                     |                                                                                                                                                                                                                                                                                     |                                              |

|   |                     | č                                                                                                                                                                                                                                                                                   | 51                                           |

|   | 0.2                 | 8.1.6 Summary                                                                                                                                                                                                                                                                       | 52                                           |

|   | 8.2                 | Stream Compilation for TRIPS                                                                                                                                                                                                                                                        | 53                                           |

|   |                     | 8.2.1 R-Stream Overview                                                                                                                                                                                                                                                             | 53                                           |

|   |                     | 8.2.2 R-Stream Compilation Strategy for TRIPS                                                                                                                                                                                                                                       | 54                                           |

|   |                     | 8.2.3 TRIPS Machine Model                                                                                                                                                                                                                                                           | 54                                           |

|   |                     |                                                                                                                                                                                                                                                                                     | ~ ~                                          |

|   |                     | 8.2.4 Mapping Matrix Multiplication to TRIPS                                                                                                                                                                                                                                        | 55                                           |

|   |                     | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60                                           |

|   |                     | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60<br>61                                     |

|   |                     | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60                                           |

| 9 | Eval                | 8.2.5       Achievement and Current Status          8.2.6       High-Level Optimization for Polymorphous Computing Architectures          8.2.7       Future Research Opportunities                                                                                                 | 60<br>61                                     |

| 9 | <b>Eva</b> l<br>9.1 | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60<br>61<br>61                               |

| 9 |                     | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60<br>61<br>61                               |

| 9 | 9.1                 | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60<br>61<br>61<br><b>63</b>                  |

| 9 | 9.1                 | 8.2.5 Achievement and Current Status                                                                                                                                                                                                                                                | 60<br>61<br>61<br><b>63</b><br>63<br>64      |

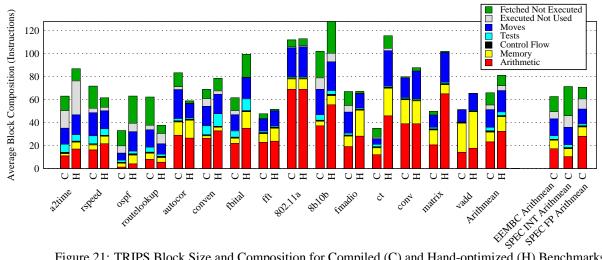

| 9 | 9.1                 | 8.2.5 Achievement and Current Status  8.2.6 High-Level Optimization for Polymorphous Computing Architectures  8.2.7 Future Research Opportunities  ation of TRIPS System  Evaluation Methodology  ISA Evaluation  9.2.1 TRIPS Block Size and Composition                            | 60<br>61<br>61<br><b>63</b><br>64<br>65      |

| 9 | 9.1                 | 8.2.5 Achievement and Current Status  8.2.6 High-Level Optimization for Polymorphous Computing Architectures  8.2.7 Future Research Opportunities  action of TRIPS System  Evaluation Methodology  ISA Evaluation  9.2.1 TRIPS Block Size and Composition  TRIPS ISA versus PowerPC | 60<br>61<br>61<br>63<br>63<br>64<br>65<br>66 |

|         | 9.3.1   | Filling a 1K Instruction Window                 | 68 |

|---------|---------|-------------------------------------------------|----|

|         | 9.3.2   | Feeds and Speeds                                | 69 |

|         | 9.3.3   | ILP Evaluation                                  | 70 |

| 9.4     | Applica | ation Performance Evaluation                    | 72 |

|         | 9.4.1   | Simple Benchmarks                               | 72 |

|         | 9.4.2   | SPEC CPU2000                                    | 72 |

| 9.5     | Applica | ation Study - DGEMM                             | 73 |

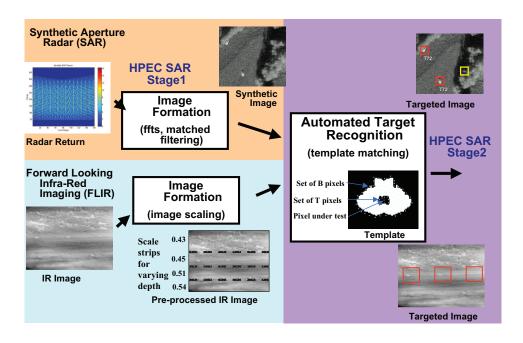

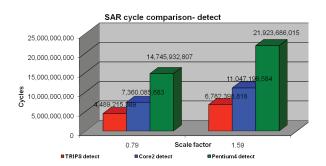

| 9.6     | Applica | ation Study - SAR                               | 74 |

| 9.7     | TRIPS   | Power Evaluation                                | 77 |

|         | 9.7.1   | Hardware Power Measurement                      | 77 |

|         | 9.7.2   | Architectural Power Models and Validation       | 78 |

|         | 9.7.3   | Power Analysis and Comparison                   | 79 |

| 0 Scala | ble and | Configurable Systems                            | 83 |

|         |         | sable Lightweight Processors                    | 83 |

|         | -       | Overview of TFlex Operation                     | 84 |

|         |         | Composable Instruction Fetch                    | 85 |

|         |         | Composable Control-flow Prediction              | 85 |

|         |         | Composable Instruction Execution                | 87 |

|         |         | Composable Memory Disambiguation                | 88 |

|         | 10.1.6  | Composable Dependence Prediction                | 88 |

|         |         | TFlex Performance                               | 88 |

| 10.2    |         | Architecture and Microarchitecture Enhancements | 89 |

|         | 10.2.1  | Predicate Prediction                            | 89 |

|         | 10.2.2  | Alternate Dataflow Graph Mappings               | 89 |

|         | 10.2.3  | Operand Network Optimizations                   | 90 |

| 10.3    | Summa   | ıry                                             | 90 |

| 1 Sum   | narv    |                                                 | 91 |

|         |         |                                                 |    |

| 2 Reco  | mmend   | ations                                          | 92 |

| 3 Refe  | rences  |                                                 | 93 |

|         |         | ns, Abbreviations, and Symbols                  | 97 |

# **List of Figures**

| 1              | The TRIPS Instruction Set Architecture (ISA)                                                   | 6  |

|----------------|------------------------------------------------------------------------------------------------|----|

| 2              | Predication in the TRIPS ISA                                                                   | 7  |

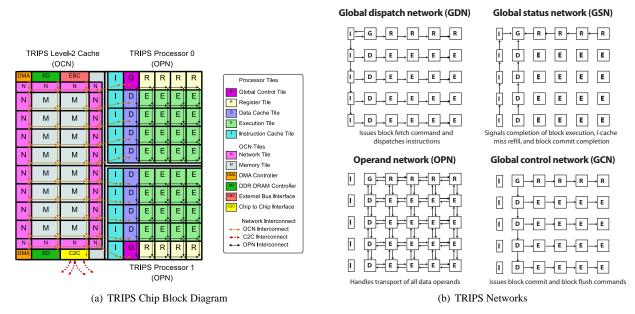

| 3              | TRIPS Chip Block Diagram and Networks                                                          | 14 |

| 4              | TRIPS Tile-Level Designs                                                                       | 15 |

| 5              | TRIPS Operational Protocols                                                                    | 18 |

| 6              | TRIPS Prototype Chip Specifications                                                            | 25 |

| 7              | TRIPS Prototype Chip Block Diagram and Die Photo                                               | 26 |

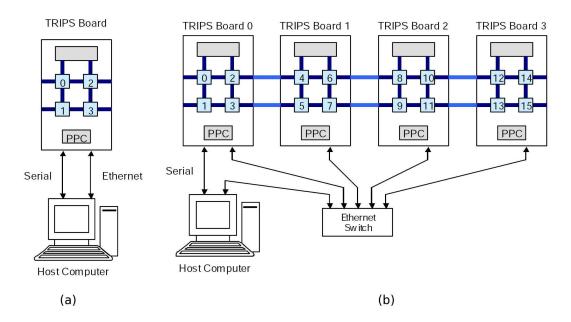

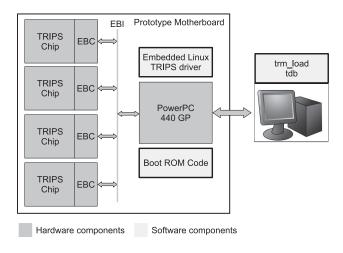

| 8              | TRIPS System Designs                                                                           | 29 |

| 9              | TRIPS Rack-based System                                                                        | 29 |

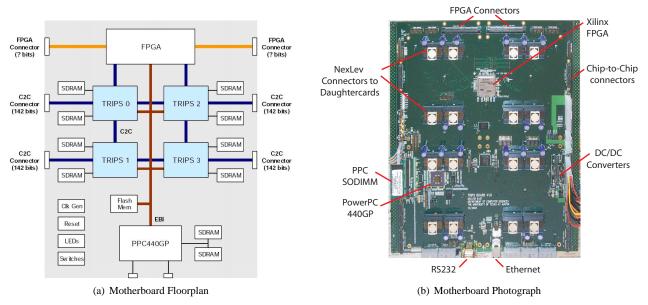

| 10             | TRIPS Motherboard                                                                              | 30 |

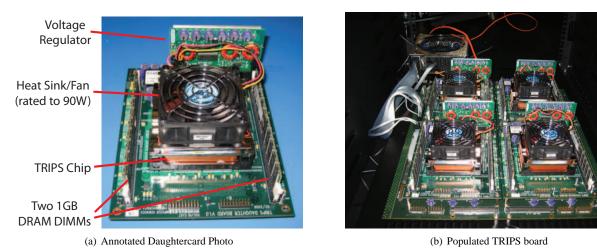

| 11             | TRIPS Daughtercards                                                                            | 32 |

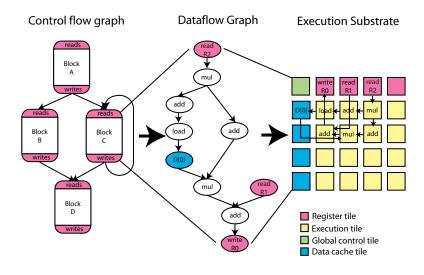

| 12             | Block control flow graph and mapping of instructions on to a $4\times4\times8$ TRIPS Processor | 33 |

| 13             | TRIPS Compiler Front End                                                                       | 35 |

| 14             | TRIPS Compiler Back End                                                                        | 35 |

| 15             | TRIPS Assembly Code Examples                                                                   | 36 |

| 16             | System Software Components                                                                     | 46 |

| 17             | MPI on the TRIPS System Software Stack                                                         | 48 |

| 18             | Transferring Data with Buffering in a Shared Segment (Using memcopy)                           | 50 |

| 19             | Transferring Data without Buffering in a Shared Segment (Using DMA)                            | 51 |

| 20             | MPI Bandwidth                                                                                  | 52 |

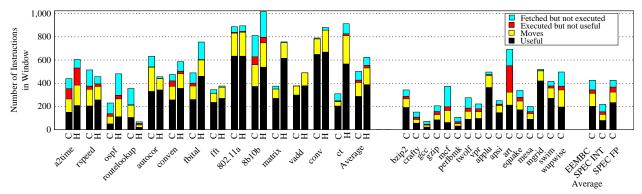

| 21             | TRIPS Block Sizes                                                                              | 65 |

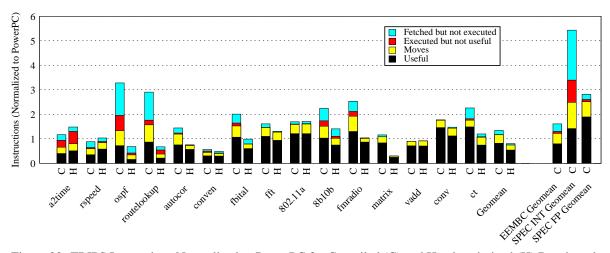

| 22             | TRIPS and RISC Instruction Counts                                                              | 66 |

| 23             | TRIPS and RISC Register and Memory Accesses                                                    | 67 |

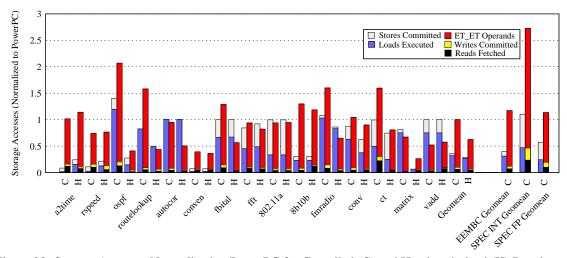

| 24             | In flight Instructions in TRIPS                                                                | 68 |

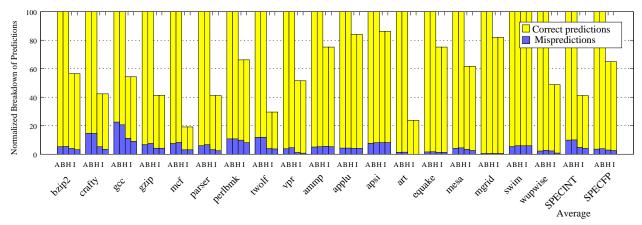

| 25             | TRIPS Block Prediction Accuracy                                                                | 69 |

| 26             | Memory and Network Feeds and Speeds                                                            | 70 |

| 27             | TRIPS Instruction Throughput                                                                   | 71 |

| 28             | Idealized Instruction Throughput                                                               | 71 |

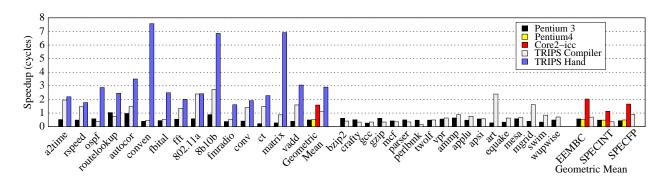

| 29             | TRIPS Versus Commercial Chips                                                                  | 72 |

| 30             | SAR End-to-End Application Description                                                         | 74 |

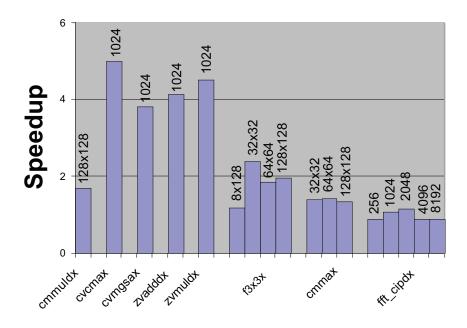

| 31             | Library Performance Relative to PowerPC                                                        | 75 |

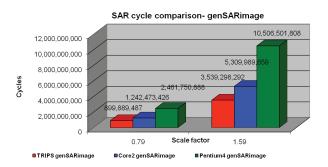

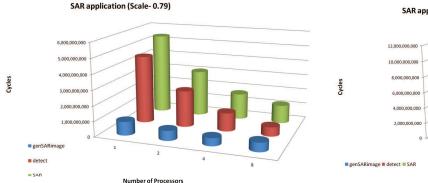

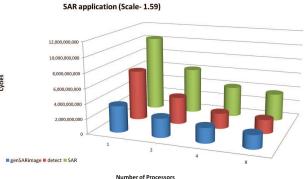

| 32             | SAR Performance on TRIPS and Intel Architectures                                               | 76 |

| 33             | SAR MPI Performance on TRIPS                                                                   | 76 |

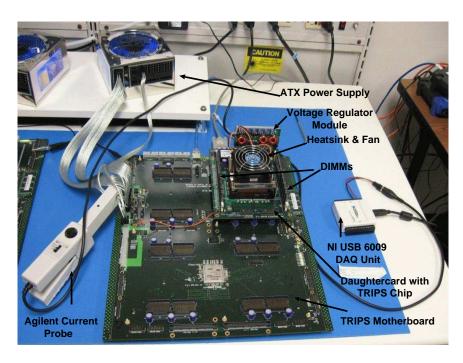

| 34             | TRIPS Hardware Power Measurement Infrastructure                                                | 77 |

| 35             | TRIPS Architectural Power Modeling                                                             | 78 |

| 36             | TRIPS and Alpha Power Consumption                                                              | 80 |

| 37             | TRIPS and Alpha Power Efficiency                                                               | 80 |

| 38             | TRIPS Power Breakdown                                                                          | 81 |

| 39             | Alpha Power Breakdown                                                                          | 81 |

| 40             | Three Dynamically Assigned CLP Configurations                                                  | 83 |

| 41             | TFlex Execution Stages                                                                         | 85 |

| 42             | TFlex Core Microarchitecture                                                                   | 86 |

| 43             | TFlex Interleaving and Inter-core Communication                                                | 87 |

| <del>4</del> 3 | TFlex Performance - 2 to 32 Cores                                                              | 88 |

|                |                                                                                                |    |

## **List of Tables**

| 1  | TRIPS Control and Data Networks                            | 20 |

|----|------------------------------------------------------------|----|

| 2  | Network Overheads and Preliminary Performance of Prototype | 21 |

| 3  | TRIPS NUCA Memory Latencies in Cycles                      | 23 |

| 4  | TRIPS Chip Area Breakdown                                  | 27 |

| 5  | TRIPS Tile Specifications                                  | 28 |

| 6  | Comparison of L2 and SRF Modes                             | 49 |

| 7  | MPI Latency Comparison                                     | 51 |

| 8  | Evaluation Reference Platforms                             | 64 |

| 9  | TRIPS Benchmark Suites                                     | 64 |

| 10 | Performance counter statistics for SPEC                    | 73 |

| 11 | Comparison of Matrix Multiply (DGEMM) Results              | 73 |

| 12 | TRIPS Power Consumption Summary                            | 78 |

| 13 | TRIPS and Alpha 21264 Simulation Parameters                | 79 |

## Acknowledgments

The authors gratefully acknowledge the support of DARPA/IPTO and the Air Force Research Laboratory under contract F33615-03-C-4106.

In addition, all of the members of the TRIPS team made substantial and crucial contributions to the success of this project. These contributors include the scientists, students, and staff members at UT-Austin, IBM Microelectronics, the Information Sciences Institute of the University of Southern California, and Reservoir Laboratories.

## 1 Executive Summary

Semiconductor technology trends are presenting substantial challenges to the design and implementation of computer systems. Power and scaling constraints have brought an end to the continuous improvements of conventional uniprocessor designs. Further, power requirements in many deployment domains demand performance and power efficiencies unattainable by conventional general purpose processors. Polymorphous Computing Architectures (PCAs), architectures that can adapt to application and environmental requirements, are an attractive option for deployment in high-performance embedded systems. The present solution, in the absence of effective polymorphous systems, is to deploy multiple computers, with each one tailored to a particular anticipated task or class of tasks. While replacing many systems with a single one is a worthy goal, to date no suitable polymorphous systems exist.

In Phase 1 of the DARPA PCA program, completed in 2004, the Tera-Op Reliable Intelligently Adaptive Processing System (TRIPS) project developed and evaluated major advances in processor and memory system architectures that are scalable to deep-submicron fabrication technology and are adaptable to application demands. Phase 2 (TRIPS Implementation, described in this report), had four primary objectives: (1) implement a TRIPS hardware prototype to demonstrate capabilities of scalable and morphable systems, (2) implement a software development kit (SDK) for both internal and external users to port, author, and debug applications for TRIPS, (3) evaluate the TRIPS system and compare to existing commercial alternatives, and (4) develop and evaluate new architecture concepts based on the lessons learned from the prototype evaluation. The TRIPS team, composed of personnel from the University of Texas at Austin, USC Information Sciences Institute, Reservoir Laboratories, and IBM Microelectronics has reached each of these objectives.

The TRIPS hardware prototype design includes a custom ASIC consisting of approximately 170 million transistors in a 336mm<sup>2</sup> chip fabricated in IBM's Cu-11 technology, a 130nm bulk technology with copper wiring. The TRIPS chip includes two coarse grained processors, each with 16 ALUs (including floating-point units) that execute in parallel. The processors execute an instruction set belonging to a new class of instruction set architectures (ISAs) called Explicit Data Graph Execution (EDGE). The chip also includes an implementation of a Non-Uniform Cache Architecture (NUCA), which is also designed for large, scalable, and configurable caches. TRIPS chips are assembled onto custom circuit boards with prototype system sizes ranging up to 32 chips (which includes a total of 64 processors and 1024 floating-point units). TRIPS systems of up to 20 chips have been deployed at UT-Austin, ISI-East, and AFRL. The software development kit (SDK) includes a custom optimizing compiler, a debugger, performance analysis tools, and support for multithreaded parallel programs. The compiler includes many new algorithms required for EDGE architectures, including optimizing instruction placement to reduce inter-instruction communication delays.

The evaluation of the TRIPS prototype system demonstrates per-processor performance (measured in cycles) of up to three times better than leading commercial products. Furthermore, the EDGE instruction set and execution model eliminates many of the power-hungry structures and operations in conventional computer systems. At 366MHz, a TRIPS processor consumes approximately 10 Watts, which gives the prototype a potential power efficiency advantage of a factor of three over conventional designs, with the opportunity for substantially more power optimizations beyond the scope of the prototype. On a synthetic aperture radar (SAR) benchmark, TRIPS outperformed conventional architectures by a factor of 1.5–1.8, depending on program phase. Based on measurements using the prototype, the team has developed both architecture optimizations to TRIPS and new composable core architectures that can adjust the processor granularity on the fly to meet the instantaneous parallelism demands of an application. This configurable lightweight processor (CLP) system is a substantial step forward in meeting the goals of truly polymorphous hardware systems.

The technical and educational impact of the TRIPS project has been profound, with scores of papers appearing in premier journals and conferences, best paper awards, numerous citations in papers authored by other researchers, and several projects at other universities derived directly from TRIPS observations and inventions. Concepts originating from the TRIPS non-uniform cache architectures (NUCA) for both single and multicore chips are making their way into the memory systems of commercial designs; we are likely to see products with NUCA-oriented caches in the near future. To date, the influence of the TRIPS processor technologies on commercial or COTS products have been more muted. Because TRIPS relies on a new instruction set architecture, convincing companies to adopt the TRIPS processor designs has been more difficult. At present, nearly all commercial systems are investing heavily in multicore system designs, despite the uncertainty in whether software can be developed to exploit the parallel cores. We anticipate that difficulties with that software transition will motivate a closer look in the future at the scalable processor architectures of TRIPS.

#### 2 Introduction

TRIPS was conceived to solve many of the fundamental problems arising as semiconductor processes advance. Left unaddressed, these problems will inhibit the effective use of commercial components in military systems [1, 26]. Mission-critical applications will benefit from the advanced polymorphous capabilities of the TRIPS system, which include numerous malleable hardware components for ultra-flexible application mapping, resource oblivious scheduling for rapid application prototyping and deployment, environmental adaptivity for resilience in hostile environments, and dynamic performance adaptation for changing and unpredictable field constraints. The TRIPS system is intended to provide a single interface to applications that will allow them to run on a wide spectrum of SWEPT (Size, Weight, Energy, Power, and Time) implementations, including lightweight, battery-operated field systems, resilient but powerful base station systems, and ultra-high-performance back-room systems. Most important, TRIPS is intended to be extremely scalable with technology, and addresses many of the long-term problems that will emerge as devices scale down to 35 nanometers and below.

Phase 1 of the TRIPS project, concluded in 2004, developed proof-of-concept technologies that met the scalability and adaptivity goals described above [29]. To that end, the TRIPS team developed novel processor microarchitectures and on-chip memory system architectures that are both technology scalable and amenable to different types of applications. The processor core design employs an Explicit Data Graph Execution (EDGE) instruction set that enables different types of programs to be efficiently mapped to a spatial computation substrate. For the proof of concept, we developed architecture specifications, simulators, and prototype compilers to evaluate and refine the architecture concepts.

Phase 2 (described in this report), had four primary objectives intended to determine the feasibility and future of the technology developed in phase one: (1) implement a TRIPS hardware prototype to demonstrate capabilities of scalable and morphable systems, (2) implement a software development kit for both internal and external users to port, author, and debug applications for TRIPS, (3) evaluate the TRIPS system and compare to existing commercial alternatives, and (4) develop and evaluate new architecture concepts based on the lessons learned from the prototype evaluation. The TRIPS team, composed of personnel from the University of Texas at Austin, USC Information Sciences Institute, Reservoir Laboratories, and IBM Microelectronics has reached each of these objectives.

The TRIPS hardware prototype design includes a custom ASIC chip consisting of approximately 170 million transistors in a 130nm IBM fabrication technology. The TRIPS chip contains two coarse grained processors that execute in parallel, each with 16 ALUs (including floating-point units). The processors execute a new EDGE instruction set architecture designed for the distributed arrays of ALUs. The chip also includes an implementation of a Non-Uniform Cache Architecture, which is also designed for large scalable and configurable caches. TRIPS chips are assembled onto custom circuit boards with prototype system sizes ranging up to 32 chips (which includes a total of 64 processors and 1024 floating-point units). TRIPS systems of up to 20 chips have been deployed at UT-Austin, ISI-East, and AFRL. The SDK includes a custom optimizing compiler, a debugger, performance analysis tools, and support for multithreaded parallel programs. The compiler includes many new algorithms required for EDGE architectures, including optimizing instruction placement to reduce inter-instruction communication delays.

The evaluation of the TRIPS prototype system demonstrates per-processor performance (measured in cycles) of up to 3 times better than leading commercial products. Furthermore, the EDGE instruction set and execution model eliminates many of the power-hungry structures and operations in conventional computer systems including register renaming, instruction reordering, and register file reads and writes. At 366MHz, a TRIPS processor consumes approximately 10 Watts, which gives the prototype a potential power efficiency advantage of a factor of three over conventional designs, with the opportunity for substantially more power optimizations beyond the scope of the prototype. On a synthetic aperture radar (SAR) code, TRIPS outperformed conventional architectures by a factor of 1.5–1.8, depending on program phase. Based on observations and measurements with the prototype, the team has developed both architecture optimizations to TRIPS, as well as a new composable core architecture that can adjust the processor granularity on the fly to meet the instantaneous parallelism demands of an application. This configurable lightweight processor (CLP) system represents a substantial step forward in meeting the goals of truly polymorphous hardware systems.

The technical and educational impact of the TRIPS project has been profound. From the academic perspective, the TRIPS project has resulted in more than 11 journal articles or book chapters, more than 40 refereed papers presented at leading

technical conferences, more than 20 workshop papers, and 4 best paper awards. Just since 2002, these papers have garnered more than 1500 citations by other technical papers, demonstrating a dramatic influence on computer architecture research. Numerous follow-on research papers have been published based on our foundational work on NUCA. Our work has also inspired new research efforts in data-driven computer architectures. For example, the TRIPS software development kit was made available to other researchers upon request; to date, over 65 different researchers or research groups have obtained the tools.

Ten of the graduate students who have worked on TRIPS have graduated with doctoral degrees and some have taken their experience and insight to jobs at IBM, Intel, and AMD. Three of the graduates are on the faculty at leading universities including the University of Wisconsin, Columbia University, and Texas A&M University. More than twelve undergraduate students have worked on aspects of TRIPS, and many of these have gone on to pursue graduate degrees in computer science at leading U.S. universities.

To date, the influence of the TRIPS technologies on commercial or COTS products have been more muted. Concepts originating from the TRIPS NUCA for both single and multicore chips is making its way into the memory systems of commercial designs and we are likely to see products with NUCA-oriented caches in the near future. However, because TRIPS relies on a redesign of the instruction set architecture, convincing companies to adopt the TRIPS processor designs has been more difficult. At present, nearly all commercial systems are investing heavily in multicore system designs, despite the uncertainty in whether software can be developed to exploit the parallel cores. We anticipate that the difficulty associated with that software transition will motivate a closer look in the future at the scalable processor architectures of TRIPS.

Section 3 describes the TRIPS EDGE instruction set architecture in detail, including refinements made during the design of the TRIPS mircroarchitecture in phase two. Sections 4 and 5 detail the TRIPS prototype hardware design and implementation, including the TRIPS chips, boards, and systems. Sections 6–8 describe the TRIPS compiler, including the novel algorithms required for distributed processor architectures, and the tools that compose the software development kit (SDK). Section 9 recounts a performance evaluation of TRIPS, focusing primarily on the novel elements of the TRIPS processor and memory systems. Section 10 gives an overview of potential next generation polymorphous computing systems that consist of computational and memory elements that can be assembled dynamically to form logical processors, conforming to the concurrency needs of an applications. Section 11 provides a summary and Section 12 give recommendations for further study and use of TRIPS technologies.

#### 3 EDGE Architectures

#### 3.1 Background

The original first goal of the TRIPS project was to develop several new technologies for scalable processor and memory system architectures. Given the massive investment in conventional RISC and CISC architectures, and the attendant difficulties in parallelizing them for many applications. we developed a new class of instruction set architectures, called Explicit Data Graph Execution architectures. This new class of architectures addresses the scalability of the microprocessor core, permitting polymorphism, high performance, and high energy efficiency.

#### 3.2 Explicit Data Graph Execution (EDGE) ISAs

EDGE ISAs combine the capabilities of the classic dataflow architectures with the support required to execute conventional imperative languages, such as C, Fortran, Java, or C++. They support design-productive tiled microarchitectures, wide issue out-of-order execution, and the exposure of large regions of computation to the hardware without the attendant circuit complexity of conventional superscalar processors that employ RISC or CISC ISAs.

EDGE ISAs have two main characteristics: (1) a program is partitioned into atomically executed blocks of instructions which have a single entry-point and no internal branching, and (2) instructions within a block execute in dataflow order according to their true data dependences. These two features permit efficient and polymorphous execution on a microarchitecture that supports them. In the case of the TRIPS prototype, the TRIPS chip fetches and executes individual blocks sequentially, but as an optimization the chip speculatively fetches and executes multiple subsequent blocks concurrently with the non-speculative block. In the TRIPS chip prototype, this method opens up an instruction window of up to 1024 instructions, providing the opportunity to exploit concurrency from different regions of the executing program.

#### 3.2.1 Block-atomic Execution

Similar to the concept of transactions (although not visible to the programmer), an EDGE ISA specifies that its instruction blocks must commit atomically and in program order. Each block, which in the TRIPS system can contain up to 128 normal instructions, is fetched as a single logical unit, mapped to the hardware, and, when complete, is committed as one unit, with all of its outputs (stores, register writes, and one branch) logically committed to memory at once. This block-atomic model greatly reduces the overheads for supporting high-performance execution, such as wide instruction fetch and branch prediction. It also supports distributed execution by reducing the frequency at which control decisions must be made. Finally, having atomically committing instruction blocks that are of finite size reduces the scope of the dataflow execution, bounding the size of the instruction pointers required for the explicit data graph execution, as described below.

While we are not the first to discuss the notion of atomic instruction blocks, the combination of unusually large atomic blocks with dataflow semantics, as described below, creates a powerful capability not previously seen in computer architecture research.

#### 3.2.2 Direct Instruction Communication with Explicit Targets

Within each block, execution proceeds directly from instruction to instruction, rather than through a shared register file. For non-memory instructions, producer-consumer relationships are explicit, with each instruction containing the instruction numbers of the instructions within a block that consumes its result (a "push" model). Conventional RISC and CISC ISAs specify their source operands as register names in the instructions, and are thus a "pull" model. When each EDGE instruction executes, it sends its result to its consumers, waking them up for execution as necessary. This model thus effectively encodes a statically formed dataflow graph, expressed through the ISA, to the hardware for each block.

The hardware maps these static graphs onto the execution units, and typically executes them in dataflow order. Each block reads from a number of architectural registers to commence its execution, and writes to a number of registers to communicate to other subsequent blocks. By stitching together a number of these blocks at runtime, a microarchitecture can create a larger instruction window, with the dynamically tracked dataflow arcs found at runtime through store/load pairs and inter-block register communication. This model eliminates a majority of the accesses to the shared register file, and in the common case of one ALU operation communicating with another, removes a significant amount of the execution energy associated with out-of-order execution. Sequential memory semantics are still obeyed, since the hardware must produce the same result as if each instruction was executed in the original program order. Since there is no ordering of non-memory instructions within a block other than dataflow order, each load and store contains a load/store identifier to convey its original program order to the memory system, which then guarantees correct execution.

#### 3.3 TRIPS ISA Specification

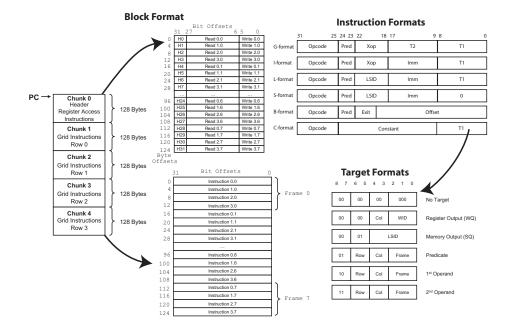

The TRIPS prototype instruction set is the first instantiation of an EDGE architecture. Figure 1 shows the current definition of the TRIPS prototype's ISA. Each block contains a 128-byte block header, which specifies the number of block outputs, as well as the registers that are read from and written to by the block. The rest of the block consists of four 128-byte instruction "chunks," each of which supplies 32 32-bit instructions to a row. Each row contains 4 nodes with 8 instructions per node.

The ISA provides the six instruction formats shown in Figure 1, which differ based on instruction function and number of distinct instruction targets. The major difference between the TRIPS EDGE instructions and conventional RISC instructions is that each instruction contains no source operand specifiers, but instead contains the name(s) of its consumer instructions. These consumer names are called targets; one or two per value-producing instruction are provided. If an instruction has more targets in a block than can be specified in the instruction format, extra instructions must be inserted to forward the value to the additional targets, resulting in a software fan-out tree. This "push" model permits the compiler to schedule dataflow-like execution within a block on the underlying substrate. Communication among different blocks must still occur through registers. As shown in Figure 1, targets in the TRIPS ISA consist of nine bits. Seven of the bits specify the target instruction number, which corresponds either to a physical reservation station in the execution array, or as a block output to one of the 128 architectural registers. Physical reservation stations are identified using row, column, and frame coordinates. The frame represents a specific buffer location at the ALU indicated by < row, column >. A  $4 \times 4$  TRIPS processor with 128 reservation stations (one reservation station for each instruction in the block) requires 8 frames. The remaining two bits specify whether each target is an architectural register or is in the block, and if it is in the block, whether it is the left, right, or predicate operand of the consuming instruction.

In addition to the standard immediate and extended opcode fields, there are several other non-standard fields in the instruction set. Loads and stores have tags (LSIDs) to specify their program order to the memory system. Branches contain tags to assist the block-level branch predictor. Each instruction also contains a two-bit predicate field, which specifies whether the instruction should execute as soon as its operands arrive, or whether it should wait for a predicate operand to arrive before firing. In the latter case, the instruction fires only if the arriving predicate matches its predicate type (true or false). Having binary predicate values reduces the number of overhead instructions needed to invert predicates.

The predicate bits are used to implement predication in an EDGE ISA. Predication can convert control flow (branches) into data flow (predicate values) that guard instructions executed in case they belong to a non-taken path. Elimination of branches allows multiple EDGE instruction blocks to be combined into a single atomic instruction block, which exposes concurrency to software and reduces block management control overheads. Creating larger blocks improves the effectiveness and performance of EDGE architectures.

#### Instructions

|       | Load and Store Instructions     |   |  |

|-------|---------------------------------|---|--|

| LB    | Load Byte                       | L |  |

| LH    | H Load Halfword                 |   |  |

| LW    | Load Word                       | L |  |

| LD    | Load Doubleword                 | L |  |

| SB    | Store Byte                      | S |  |

| SH    | Store Halfword                  | S |  |

| SW    | Store Word                      | S |  |

| SD    | Store Doubleword                | S |  |

|       | Integer Arithmetic Instructions |   |  |

| ADD   | Add                             | G |  |

| ADDI  | Add Immediate                   | I |  |

| SUB   | Subtract                        | G |  |

| SUBI  | Subtract Immediate              | I |  |

| MUL   | G                               |   |  |

| MULI  | Multiply Immediate              | I |  |

| DIVS  | Divide Signed                   | G |  |

| DIVSI | Divide Signed Immediate         | I |  |

| DIVU  | Divide Unsigned                 | G |  |

| DIVUI | Divide Unsigned Immediate       | I |  |

|       | Integer Logical Instructions    |   |  |

| AND   | Bitwise AND                     | G |  |

| ANDI  | Bitwise AND Immediate           | I |  |

| OR    | Bitwise OR                      | G |  |

| ORI   | Bitwise OR Immediate            | I |  |

| XOR   | Bitwise XOR                     | G |  |

| XORI  | Bitwise XOR Immediate           | I |  |

| Integer Shift Instructions |                                       |   |  |  |  |

|----------------------------|---------------------------------------|---|--|--|--|

| SLL                        | Shift Left Logical                    | G |  |  |  |

| SLLI                       | LLI Shift Left Logical Immediate      |   |  |  |  |

| SRL                        | Shift Right Logical                   | G |  |  |  |

| SRLI                       | SRLI Shift Right Logical<br>Immediate |   |  |  |  |

| SRA                        | Shift Right Arithmetic                | G |  |  |  |

| SRAI                       | Shift Right Arithmetic<br>Immediate   | I |  |  |  |

|                            | Integer Extend Instructions           |   |  |  |  |

| EXTSB                      | Extend Signed Byte                    | G |  |  |  |

| EXTSH                      | Extend Signed Halfword                | G |  |  |  |

| EXTSW                      | Extend Signed Word                    | G |  |  |  |

| EXTUB                      | EXTUB Extend Unsigned Byte            |   |  |  |  |

| EXTUH                      | XTUH Extend Unsigned Halfword         |   |  |  |  |

| EXTUW Extend Unsigned Word |                                       | G |  |  |  |

|                            | Integer Test Instructions             |   |  |  |  |

| TEQ                        | Test EQ                               | G |  |  |  |

| TEQI                       | Test EQ Immediate                     | I |  |  |  |

| TLT                        | Test LT                               | G |  |  |  |

| TLTI                       | Test LT Immediate                     | I |  |  |  |

| TLE                        | Test LE                               | G |  |  |  |

| TLEI                       | Test LE Immediate                     | I |  |  |  |

| TLTU                       | Test LT Unsigned                      | G |  |  |  |

| TLTUI                      | Test LT Unsigned Immediate            | I |  |  |  |

| TLEU                       | Test LE Unsigned                      | G |  |  |  |

| TLEUI                      | Test LE Unsigned Immediate            | I |  |  |  |

| Floating-Point Arithmetic Instructions |                                       |    |  |  |  |

|----------------------------------------|---------------------------------------|----|--|--|--|

| FADD                                   | G                                     |    |  |  |  |

| FSUB                                   | FSUB FP Substract                     |    |  |  |  |

| FMUL                                   | FP Multiply                           | G  |  |  |  |

| FDIV                                   | FP Divide                             | G  |  |  |  |

|                                        | Floating-Point Test Instructions      |    |  |  |  |

| FEQ                                    | FP Test EQ                            | G  |  |  |  |

| FLT                                    | FP Test LT                            | G  |  |  |  |

| FLE                                    | FP Test LE                            | G  |  |  |  |

|                                        | Floating-Point Conversion Instruction | ns |  |  |  |

| FITOD                                  | Convert Integer to Double FP          | G  |  |  |  |

| FDTOI                                  | Convert Double FP to Integer          | G  |  |  |  |

| FSTOD                                  | FSTOD Convert Single FP to Double FP  |    |  |  |  |

| FDTOS                                  | G                                     |    |  |  |  |

|                                        | Control Flow Instructions             |    |  |  |  |

| BR                                     | Branch                                | В  |  |  |  |

| BRO                                    | Branch with Offset                    | В  |  |  |  |

| CALL                                   | Call                                  | В  |  |  |  |

| CALLO                                  | Call with Offset                      | В  |  |  |  |

| RET                                    | Return                                | В  |  |  |  |

| SCALL                                  | System Call                           | В  |  |  |  |

|                                        | Miscellaneous Instructions            |    |  |  |  |

| NULL                                   | Nullify Output                        | G  |  |  |  |

| MOV                                    | Move                                  | G  |  |  |  |

| MOVI                                   | Move Immediate                        | I  |  |  |  |

| GENS                                   | Generate Signed Constant              | С  |  |  |  |

| GENU                                   | Generate Unsigned Constant            | С  |  |  |  |

| APP                                    | Append Constant                       | С  |  |  |  |

| NOP                                    | No Operations                         | С  |  |  |  |

Figure 1: The TRIPS Instruction Set Architecture (ISA)

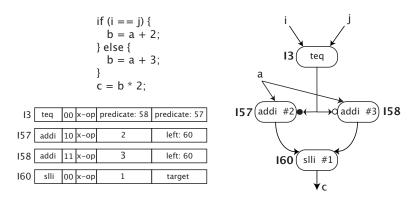

Figure 2: Predication in the TRIPS ISA

#### 3.3.1 Predication

Figure 2 shows an example of a simple C-code fragment of an if-then-else and a diagram representing its if-converted dataflow graph. The right-most field in the instruction is the target identifier, which specifies the consumer of the instruction's result. The TRIPS ISA allows up to 128 instructions within each block.

The TRIPS ISA but must follow a number of rules to produce well-formed, predicated blocks:

- 1. Any instruction (except for a few specific data movement and constant generation instructions) may be predicated. A two-bit predicate field indicates whether an instruction is predicated and on what polarity of the arriving predicate the instruction should be executed.

- 2. For a predicated instruction to fire and execute, it must receive all of its data operands and a matching predicate operand. A matching predicate is one that matches the polarity of the waiting instruction. For example, an instruction waiting for a "false" predicate will only fire when a "false" predicate arrives.

- 3. Multiple instructions may target the predicate operand of an instruction, but at most one may deliver a matching predicate. This capability permits aggressive instruction merging.

- 4. To deliver a predicate to multiple predicated instructions, the compiler must construct the necessary fanout tree using a series of multi-target move instructions.

- 5. The predicated dataflow graphs must preserve the exception behavior of an unpredicated program, meaning that the same exceptions must be detected at the TRIPS block boundaries.

Dataflow predication provides the ability to compute compound predicates efficiently, while also exploiting early mispredication detection and implicit predication. The overheads of dataflow predication, as instantiated in TRIPS, require a two-bit field per instruction and fanout instructions for routing predicates to more than two predicate consumers. Previous architectures also had significant overheads for predication. Partially predicated dataflow ISAs added extra split and merge instructions. VLIW architectures required larger per-instruction fields (e.g. six bits) to specify predicate registers.

Figure 2 also illustrates predicate generation. The test instruction (teq) receives i and j, computes a predicate, and sends it to the two addi instructions. Note that the addi instructions are predicated on opposite polarities; the black circle indicates predication on true, while the white circle indicates predication on false. When the addi instructions receive both a and the predicate, the instruction with the matching predicate fires and delivers the result to the subsequent shift (slli) instruction. Since only one addi instruction fires, the shift will receive only one token representing the updated value of b.

Figure 2 also shows the encodings of the four instructions. The instruction fields include opcode (7 bits), predicate (2 bits), extended opcode (5 bits), immediate or target 2 (9 bits), and target 1 (9 bits). The predicate field specifies whether the instruction is predicated on a true predicate (PR = 11), predicated on a false predicate (PR = 10), or unpredicated (PR = 10). In this example, the unpredicated teq instruction, which has a PR field of 00, produces a "true" predicate, in which the low-order bit of the value routed to the consumers is equal to one. The teq has two targets, 57 and 58, which correspond to the predicate operands of the two addi instructions respectively. Each addi instruction has only one target as the second target field is needed to encode the immediate value.

#### 3.4 Code Examples

Substantial refinements were made to the concept of EDGE architectures as part of the Phase 2 support. In addition to many of the predication features, the TRIPS ISA was defined in detail. In this section, we show four examples of how a simple routine is successively lowered into an EDGE ISA encoding.

**Vector Add loop:** We demonstrate EDGE-related transformations using a vector add loop example, since it is relatively simple to follow. Below we show a snippet of C code for the loop in which each vector is 1024 elements long.

```

for (i = 0; i < 1024; i++)

{

C[i] += (A[i] + B[i]);

}</pre>

```

**Unrolled Vector Add example:** As discussed later in this report, the TRIPS compiler unrolls frequently iterated loops to fill out each instruction block. In this example, vagaries of the TRIPS EDGE ISA (i.e., the limit of no more than 32 loads and/or stores per block) limit the number of iterations from the above loop that may be packed into a single block. The loop body is replicated eight times, as shown below, expanded to fill a single instruction block as much as possible.

```

C[i] += A[i] + B[i]

C[i+1] += A[i+1] + B[i+1]

C[i+2] += A[i+2] + B[i+2]

C[i+3] += A[i+3] + B[i+3]

C[i+4] += A[i+4] + B[i+4]

C[i+5] += A[i+5] + B[i+5]

C[i+6] += A[i+6] + B[i+6]

C[i+7] += A[i+7] + B[i+7]

i+=8

test i < 1024

```

TIL Vector Add code: The below code represents the vector-add output of the compiler before assembly and instruction identifier assignment. We defined a RISC-like intermediate compiler form called the TRIPS Intermediate Language, or TIL. This form is readable by the compiler, and is significantly easier to manually tune than TRIPS Assembly Language (TASL). Since TIL is generated by the compiler after block formation, each block contains a .bbegin and a .bend identifier. There are a number of read instructions in each block that read global registers and identify which instructions in the block need those register values to commence execution. At the end of the block, there are multiple write registers to preserve values other than memory values. The code below has not yet been lowered into target format, meaning that instructions still specify abstract source and destination registers within the block. However, load/store IDs are specified in the instructions. Near the end of the block, note the two branch instructions, which are predicated on opposite predicate values, guaranteeing that only one of the two will execute when the block is executed.

```

.bbegin vadd$1

read $t0, $g70

read $t1, $g71

read $t2, $g72

read $t3, $q73

$t4, ($t1) L[0]

ld

ld

$t5, ($t2) L[1]

ld

$t6, ($t3) L[2]

fadd $t7, $t5, $t6

fadd $t8, $t4, $t7

($t1), $t8 S[3]

sd

ld

$t9, 8($t1) L[4]

ld

$t10, 8($t2) L[5]

ld

$t11, 8($t3) L[6]

fadd $t12, $t10, $t11

fadd $t13, $t9, $t12

8($t1), $t13 S[7]

sd

ld

$t14, 16($t1) L[8]

$t15, 16($t2) L[9]

ld

ld

$t16, 16($t3) L[10]

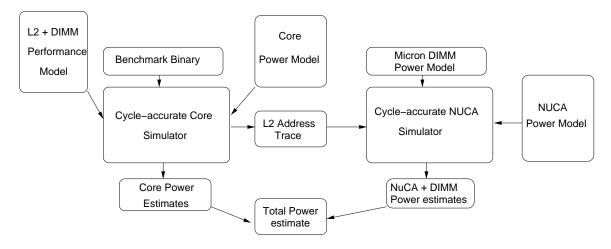

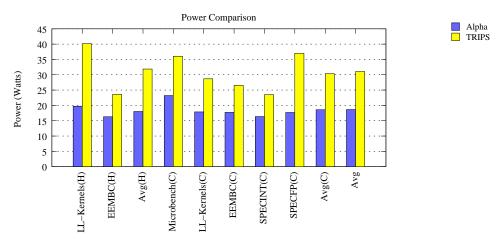

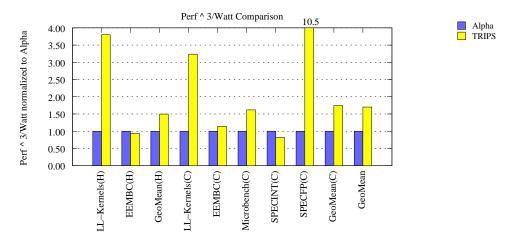

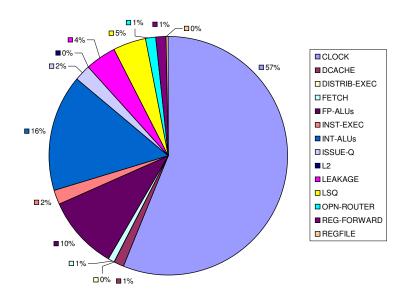

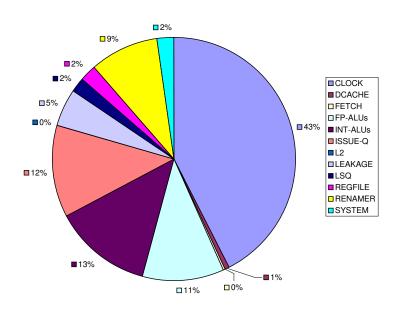

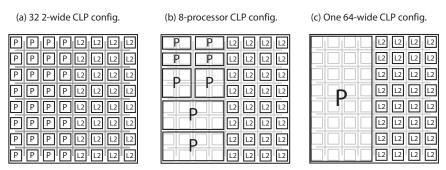

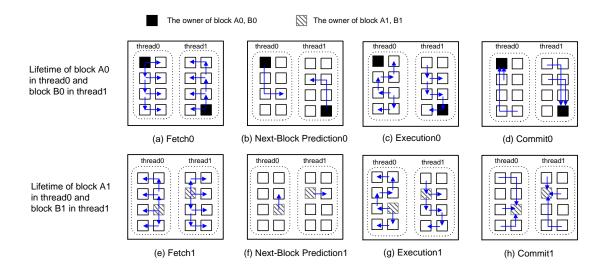

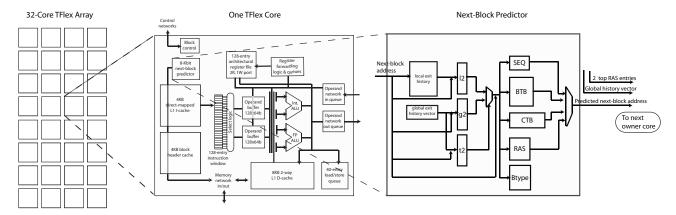

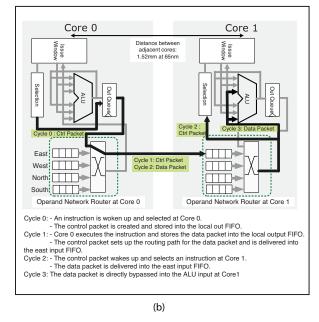

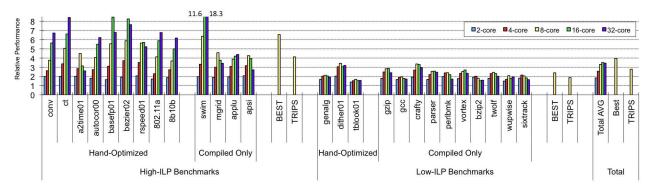

fadd $t17, $t15, $t16