# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

# MODELING AND SIMULATION OF A NON-COHERENT FREQUENCY SHIFT KEYING TRANSCEIVER USING A FIELD PROGRAMMABLE GATE ARRAY (FPGA)

by

Konstantinos Voskakis

September 2008

Thesis Advisor: Thesis Co-Advisor: Second Reader: Frank Kragh Peter Ateshian Roberto Cristi

Approved for public release; distribution is unlimited

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         |                                                                                                                        | Form Approv                                                                                                                                                                        | ved OMB No. 0704-0188                                                                                                                                                                                           |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Public reporting burden for this colle<br>searching existing data sources, gath<br>comments regarding this burden estin<br>Washington headquarters Services, D<br>22202-4302, and to the Office of Mar                                                                                                                                                                 | ering and maintaining the<br>nate or any other aspect of<br>irectorate for Information C<br>agement and Budget, Paper                                                                                                                                                                                                                      | data needed, and con<br>this collection of info<br>perations and Reports<br>work Reduction Proje                                                                                                                                        | npleting an<br>ormation, in<br>, 1215 Jeff<br>ct (0704-01                                                              | nd reviewing the concluding suggestion<br>ncluding suggestion<br>ferson Davis Highw<br>(188) Washington D                                                                          | bllection of information. Send<br>as for reducing this burden, to<br>ay, Suite 1204, Arlington, VA<br>C 20503.                                                                                                  |  |

| 1. AGENCY USE ONLY (Leave                                                                                                                                                                                                                                                                                                                                              | Ś                                                                                                                                                                                                                                                                                                                                          | September 2008                                                                                                                                                                                                                          | 3. RE                                                                                                                  | PORT TYPE AND DATES COVERED<br>Master's Thesis                                                                                                                                     |                                                                                                                                                                                                                 |  |

| <ul> <li>4. TITLE AND SUBTITLE Mo<br/>Frequency Shift Keying Transceir<br/>(FPGA).</li> <li>6. AUTHOR(S) Konstantinos V</li> </ul>                                                                                                                                                                                                                                     | ver Using a Field Program                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                         |                                                                                                                        | 5. FUNDING N                                                                                                                                                                       | IUMBERS                                                                                                                                                                                                         |  |

| <ul> <li>7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br/>Naval Postgraduate School<br/>Monterey, CA 93943-5000</li> </ul>                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         |                                                                                                                        | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                                                                                                                                        |                                                                                                                                                                                                                 |  |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         | . ,                                                                                                                    | AGENCY R                                                                                                                                                                           | NG/MONITORING<br>EPORT NUMBER                                                                                                                                                                                   |  |

| <b>11. SUPPLEMENTARY NOTE</b><br>or position of the Department of I                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         | ose of the                                                                                                             | author and do no                                                                                                                                                                   | ot reflect the official policy                                                                                                                                                                                  |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT         Approved for public release; distribution is unlimited.                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         | 12b. DISTRIBUTION CODE                                                                                                 |                                                                                                                                                                                    |                                                                                                                                                                                                                 |  |

| Keying (BFSK) receiver-transmi<br>Coherent BFSK demodulation<br>environment of choice is Mathwe<br>design is downloaded to a Virtex<br>The receiver is Non-C<br>feedback circuit is responsible t<br>match filters instead of low pas<br>experiences that were gained dur<br>In Appendix A, we eva<br>Software Defined Radio. These<br>Processors and Application Spec | cipals of Software Defin<br>tter in a Field Programm<br>implemented at the reco<br>orks <sup>?®</sup> Simulink and Xili<br>-4 FPGA.<br>oherent (NC) in the sen<br>for both packet and bit<br>s filters which would b<br>ing the learning process a<br>aluate different technolog<br>options include Digital<br>ific Integrated Circuits an | nable Gate Array (F<br>eiver, the design o<br>nx <sup>®</sup> System Genera<br>se that the receiver<br>synchronization. A<br>e easier, but would<br>are discussed.<br>gical options in imp<br>Signal Processors,<br>nd a comparison bet | FPGA). A<br>f transmit<br>tor, a dedi<br>need not<br>lso, the re-<br>d degrade<br>lementing<br>Field Pre-<br>ween thes | fter introducing t<br>tter and receiver<br>icated library for<br>know the phase<br>eceiver is impler<br>the performance<br>g communication<br>ogrammable Gate<br>e choices is made | is illustrated. The design<br>Mathworks' Simulink. The<br>of the incoming signal. A<br>nented using non-coherent<br>. Finally, some interesting<br>modulating techniques and<br>e Arrays, General Purpose<br>2. |  |

| 14. SUBJECT TERMS Softward<br>Processing Chip, Application Spe<br>System Generator                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         |                                                                                                                        |                                                                                                                                                                                    | 15. NUMBER OF<br>PAGES<br>125<br>16. PRICE CODE                                                                                                                                                                 |  |

| 17. SECURITY                                                                                                                                                                                                                                                                                                                                                           | 18. SECURITY                                                                                                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                                                      | ). SECUF                                                                                                               | RITV                                                                                                                                                                               | 20. LIMITATION OF                                                                                                                                                                                               |  |

| CLASSIFICATION OF<br>REPORT                                                                                                                                                                                                                                                                                                                                            | CLASSIFICATION<br>PAGE                                                                                                                                                                                                                                                                                                                     | OF THIS C<br>A                                                                                                                                                                                                                          | LASSIFI<br>BSTRAC                                                                                                      | CATION OF                                                                                                                                                                          | ABSTRACT                                                                                                                                                                                                        |  |

| Unclassified<br>NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                   | Unclassif                                                                                                                                                                                                                                                                                                                                  | ied                                                                                                                                                                                                                                     | Unc                                                                                                                    | classified Stand                                                                                                                                                                   | UU<br>ard Form 298 (Rev. 2-89)                                                                                                                                                                                  |  |

Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited

# MODELING AND SIMULATION OF A NON-COHERENT FREQUENCY SHIFT KEYING TRANSCEIVER USING A FIELD PROGRAMMABLE GATE ARRAY (FPGA)

Konstantinos Voskakis Lieutenant Junior Grade, Hellenic Navy B.S., Hellenic Naval Academy, 1999

Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

# NAVAL POSTGRADUATE SCHOOL September 2008

Author: Konstantinos Voskakis

Approved by: Frank Kragh Thesis Advis

Thesis Advisor

Peter Ateshian Thesis Co-Advisor

Roberto Cristi Second Reader

Jeffrey Knorr Chairman, Department of Electrical and Computer Engineering

# ABSTRACT

In this thesis, the principals of Software Defined Radio are demonstrated by implementing a Binary Frequency Shift Keying (BFSK) receiver-transmitter in a Field Programmable Gate Array (FPGA). After introducing the theory behind the Non-Coherent BFSK demodulation implemented at the receiver, the design of both transmitter and receiver is illustrated. The design environment of choice is Mathworks'<sup>®</sup> Simulink and Xilinx<sup>®</sup> System Generator, a dedicated library for Mathworks' Simulink. The design is downloaded to a Virtex-4 FPGA.

The receiver is Non-Coherent (NC) in the sense that the receiver need not know the phase of the incoming signal. A feedback circuit is responsible for both packet and bit synchronization. Also, the receiver is implemented using non-coherent match filters instead of low pass filters which would be easier, but would degrade the performance. Finally, some interesting experiences that were gained during the learning process are discussed.

In Appendix A, we evaluate different technological options in implementing communication modulating techniques and Software Defined Radio. These options include Digital Signal Processors, Field Programmable Gate Arrays, General Purpose Processors and Application Specific Integrated Circuits and a comparison between these choices is made.

# **TABLE OF CONTENTS**

| I.   | INT       | RODUCTION                                      |     |

|------|-----------|------------------------------------------------|-----|

|      | A.        | BACKGROUND ON SOFTWARE DEFINED RADIO           | 1   |

|      | В.        | GOALS OF RESEARCH AND CONCEPTS                 |     |

|      | C.        | METHODOLOGY AND SCOPE OF THE RESEARCH          | 2   |

|      | D.        | BENEFITS OF THE RESEARCH                       |     |

|      | Е.        | ORGANIZATION OF THE THESIS                     | 3   |

| II.  | BIN       | ARY FREQUENCY SHIFT KEYING MODULATION SCH EME  | AND |

|      |           | NVOLUTIONAL ENCODING                           |     |

|      | A.        | BFSK MODULATION                                | 5   |

|      | В.        | CONVOLUTIONAL ENCODING                         | 9   |

| III. | DES       | SIGN ENVIRONMENT                               | 13  |

| -    | <b>A.</b> | SYSTEM GENERATOR                               |     |

|      | В.        | ISE PROJECT MANAGER                            | 15  |

|      | C.        | AVNET BOARD                                    |     |

| IV.  | DES       | IGN FLOW                                       | 19  |

| 1    | A.        | TRANSMITTER                                    |     |

|      | 1 1.      | 1.   Preamble Subsystem                        |     |

|      |           | 2. Data Input Subsystem                        |     |

|      |           | 3. Modulation Subsystem                        |     |

|      | B.        | RECEIVER                                       |     |

|      | 27        | 1. Non-Coherent Matched Filter Subsystem       |     |

|      |           | 2. Timing Circuit                              |     |

|      |           | 3. Decoding Subsystem                          |     |

| V.   | DES       | SIGN VALIDATIONS, RESULTS AND TROUBLESHOOTING  |     |

| ••   | A.        | SYSTEM GENERATOR                               |     |

|      | B.        | TROUBLESHOOTING AND LESSONS LEARNED            |     |

|      | 2.        | 1. Transmitter                                 |     |

|      |           | 2. Receiver                                    |     |

| VI.  | CON       | NCLUSIONS                                      | 45  |

| • 10 | A.        | SUMMARY OF THE WORK                            |     |

|      | B.        | SIGNIFICANT RESULTS                            |     |

|      | C.        | SUGGESTIONS FOR FUTURE WORK                    |     |

|      |           | 1. Limitation of the Design                    |     |

|      |           | 2. Suggestions                                 |     |

| APP  | ENDIX     | <b>X A. BACKGROUND ON FPGA AND TECHNOLOGIC</b> |     |

|      |           | CKGROUND                                       |     |

|      | A.        | BRIEF DESCRIPTION OF AN FPGA                   |     |

|      | B.        | ADVANTAGES AND APPLICATIONS OF FPGAS           |     |

|      | C.        | FPGA VS. GPP                                   |     |

|      | D.        | FPGA VS. DSP                                   |     |

|      |           |                                                |     |

| Е.        | FPGA VS. ASIC                                           | 56     |

|-----------|---------------------------------------------------------|--------|

| F.        | DSP-ENHANCED FPGAS                                      |        |

| G.        | THE ROLE OF FPGAS IN SDR – HOW TO COMBINE DSP           | -F PGA |

|           | COPROCESSOR                                             | 59     |

| H.        | <b>BEYOND THESE TECHNOLOGIES, WHAT NEXT?</b>            | 62     |

| I.        | LIMITATIONS                                             | 64     |

| APPENDIX  | <b>X B. IN DE PTH PARAMETER ANALYSIS OF BFSK TRANSC</b> | EIVER  |

| DES       | IGN                                                     |        |

| А.        | TRANSMITTER (TOP LEVEL)                                 | 65     |

| В.        | PREAMBLE SUBSYSTEM                                      | 67     |

| C.        | DATA INPUT SUBSYSTEM                                    | 69     |

| D.        | MODULATION SUBSYSTEM                                    | 71     |

| Е.        | RECEIVER (TOP LEVEL)                                    | 74     |

| F.        | MATCHED FILTER SUBSYSTEM                                |        |

| G.        | CORRELATOR'S SUBSYSTEM                                  |        |

| Н.        | DECISION CIRCUIT                                        |        |

| I.        | DECODING SUBSYSTEM                                      | 86     |

| APPENDIX  | <b>C. MATLAB VERIFICATION CODE</b>                      | 91     |

| LIST OF R | EFERENCES                                               | 97     |

| INITIAL D | ISTRIBUTION LIST                                        | 105    |

# LIST OF FIGURES

| Figure 1    | Block diagram of a NCBFSK receiver (From: [5]).                                     | 6   |

|-------------|-------------------------------------------------------------------------------------|-----|

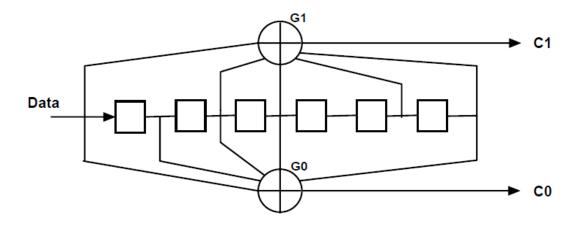

| Figure 2    | Convolutional Encoder Block Diagram of code rate $r = \frac{1}{2}$ and $\kappa = 7$ | .10 |

| Figure 3    | Example of the environment and the blocks offered by Sysgen                         | .14 |

| Figure 4    | Project Navigator Main Window                                                       | .16 |

| Figure 5    | Transmitter's schematic diagram designed in Simulink/Sysgen                         |     |

|             | environment.                                                                        | .19 |

| Figure 6    | Preamble Subsystem.                                                                 | .20 |

| Figure 7    | Data Input Subsystem.                                                               | .21 |

| Figure 8    | Modulation Subsystem                                                                | .22 |

| Figure 9    | Receiver's schematic diagram designed in Simulink environment.                      | .24 |

| Figure 10   | Non-Coherent Matched filter subsystem (one of two).                                 | .25 |

| Figure 11   | Correlator's Subsystem (one of two).                                                |     |

| Figure 12   | Decision Circuit.                                                                   |     |

| Figure 13   | Decoding Subsystem                                                                  |     |

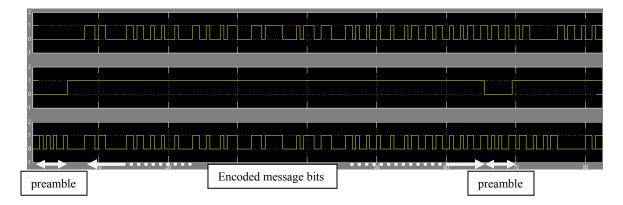

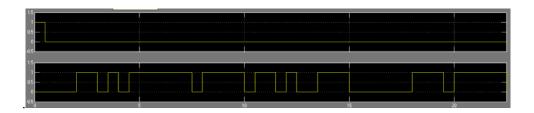

| Figure 14   | Plots of the encoded bits, the 'read_enable' and the channel bits (top to           |     |

| e           | bottom).                                                                            | .34 |

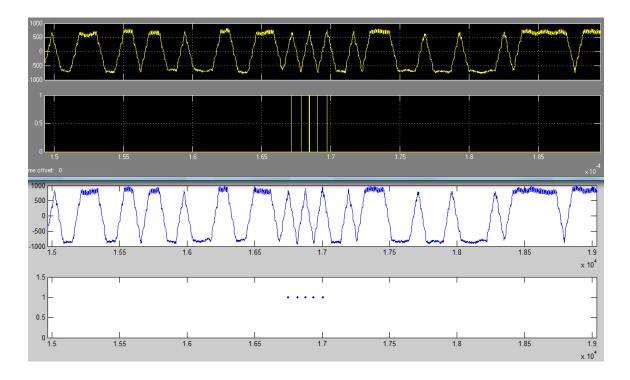

| Figure 15   | Results captured from the 'Scope 3' (Figure 36) in Simulink and results as          |     |

| e           | plotted by the equivalent Matlab Code (from top to bottom).                         | .35 |

| Figure 16   | Matlab code to align output of Transmitter and Receiver and calculate               |     |

| 0           | number of errors                                                                    | .36 |

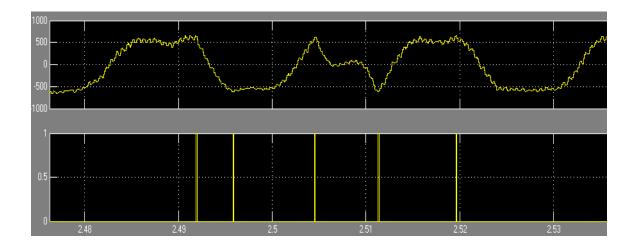

| Figure 17   | Plot of the 'empty' output signal and the 'din' input signal of the FIFO            |     |

| 0           | memory in the beginning of the simulation.                                          | .40 |

| Figure 18   | Plot of the 'empty' output signal and the 'din' input signal of the FIFO            |     |

| 0           | memory at the end of the simulation                                                 | .40 |

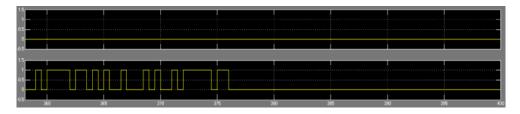

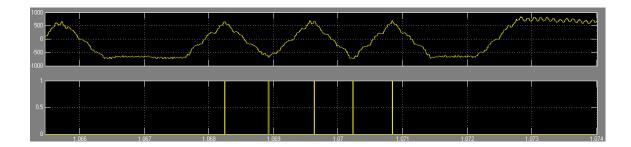

| Figure 19   | Example of a preamble acquisition with initial values for 'DDS clock                |     |

| 0           | rate.' Top plot shows the decision signal and bottom plot shows the                 |     |

|             | successive peak identification made by the timing circuit                           | .41 |

| Figure 20   | Example of a preamble acquisition with final values for 'DDS clock rate.'           |     |

| 0           | Top plot shows the decision signal and bottom plot shows the successive             |     |

|             | peak identification made by the timing circuit.                                     | .42 |

| Figure 21   | FIR custom block                                                                    |     |

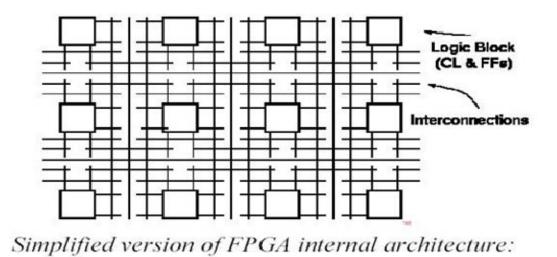

| Figure 22   | Simplified Version of FPGA Internal Architecture (From: [32])                       |     |

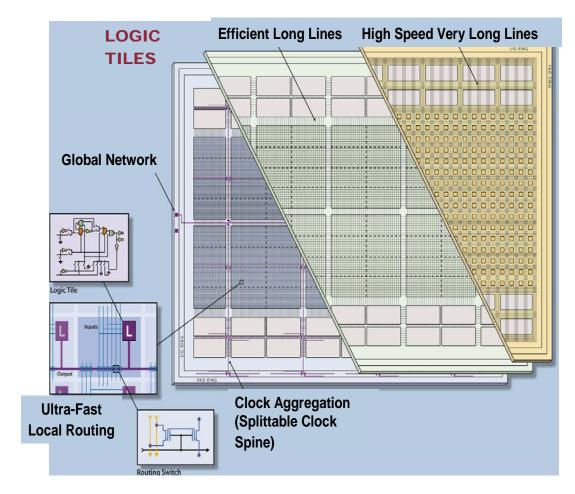

| Figure 23   | Typical FPGA architecture (From: [33]).                                             |     |

| Figure 24   | Internal Structure of a DSP48E cell. (From: [58])                                   |     |

| Figure 25   | Different Functions Assigned to GPPs, FPGAs, and DSPs (From: [65])                  |     |

| Figure 26   | Illustration of the concept behind eASIC's structured ASICs (From: [72])            |     |

| Figure 27   | PicoArray Concept (From: [75])                                                      |     |

| Figure 28   | Transmitter's schematic diagram designed in Simulink/Sysgen                         |     |

| - 1941 0 20 | environment.                                                                        | 65  |

| Figure 29   | Preamble Subsystem.                                                                 |     |

| Figure 30   | Data Input Subsystem                                                                |     |

| - 19410 20  |                                                                                     | ,   |

| Figure 31 | A block diagram of a convolutional encoder. (From: [13])              | 69 |

|-----------|-----------------------------------------------------------------------|----|

| Figure 32 | Modulation Subsystem                                                  | 71 |

| Figure 33 | Receiver's schematic diagram designed in Simulink/Sysgen environment. | 74 |

| Figure 34 | NC Matched filter subsystem (one of two).                             | 76 |

| Figure 35 | Correlator's Subsystem (one of two).                                  | 78 |

| Figure 36 | Initialization block.                                                 | 78 |

| Figure 37 | Decision Circuit.                                                     | 79 |

| Figure 38 | Decoding Subsystem.                                                   | 86 |

# LIST OF TABLES

| Table 1. | Results of multiple runs with different input sequence and constant input                                                              |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|          | delay (value set to zero).                                                                                                             |  |

| Table 2. | Results of multiple runs with constant input sequence and variable input delay. All runs made after first execution of command a =rand |  |

|          | (1,1900)<5                                                                                                                             |  |

| Table 3. | Device utilization summary.                                                                                                            |  |

## **EXECUTIVE SUMMARY**

Software Defined Radio (SDR) is a new and fascinating idea having its roots in the early'90's. Technologic constraints prevented this idea from becoming a reality at the beginning, but the development of powerful Field Programmable Gate Arrays (FPGAs) has increased interest in the SDR concept. FPGAs combine versatility, reconfigurability and upgradability that is hard to find in any other device.

A simple way to make Software Defined Radio a reality is to store transceiver designs for many modulation schemes in memory and download the selected one to an FPGA as needed. This goal is accomplished when transceivers for all modulation schemes and services of choice are designed and synthesized for the target FPGA. Starting this procedure, a Binary Frequency Shift Keying transmitter and receiver design is the main purpose of this thesis.

BFSK is the modulation that uses two different frequencies for the binary 0 and binary 1 symbols of the input stream. This modulation is simple but there are still many challenges for the timing synchronization of the receiver. A non-coherent receiver was chosen to eliminate the need for phase synchronization. The description of such a receiver along with the timing issue is addressed in Chapter II. Given that Forward Error Correction is used in the transceiver design, an introduction of convolutional encoding is also given in Chapter II.

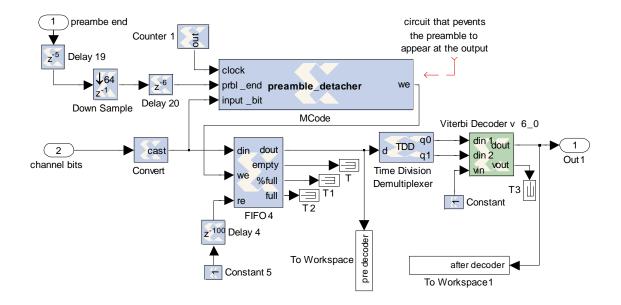

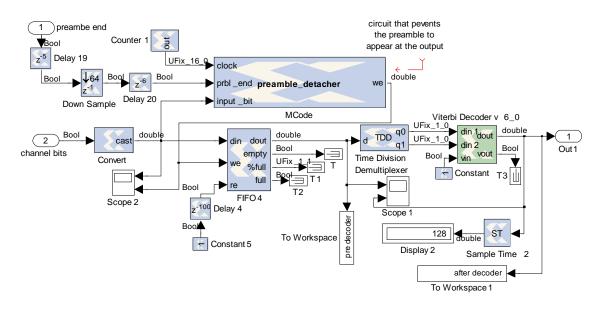

To make a good design, the proper software must support the effort. System Generator is a program available by Xilinx to help the designing of a project, offering an environment familiar to most engineers, namely Mathworks' Simulink with a complete library of synthesizable blocks. This program is supported by the Integrated Software Environment (ISE) Design Suite, which is the Xilinx software that accepts the code generated by System Generator and continues the task of implementing the design to the FPGA and testing the resulting downloaded design. A more complete description is included in Chapter III. The transmitter and receiver design made under System Generator is presented in Chapter IV. A preamble is attached before each packet to facilitate the synchronization of the receiver. Before that happens, the message bits are encoded using convolutional encoding. Then output bits of these procedures are transmitted based on the general rule of the BFSK modulation scheme where binary zeros and ones correspond to two different frequencies. The receiver uses non-coherent matched filters to extract the transmitted bits from the received waveform. Also, there exists a timing circuit that provides the bit and packet synchronization. Finally, the preamble is stripped off and the remaining bits are inserted to a Viterbi decoder that yields the message bits.

The verification of the design follows in Chapter V. This is carried out in the System Generator environment, by examining the signal at different points in the design, and in using Matlab code that simulates part of the receiver. The results are shown and the design can be considered successful. The problems that were encountered during the design are also addressed in the second half of this chapter.

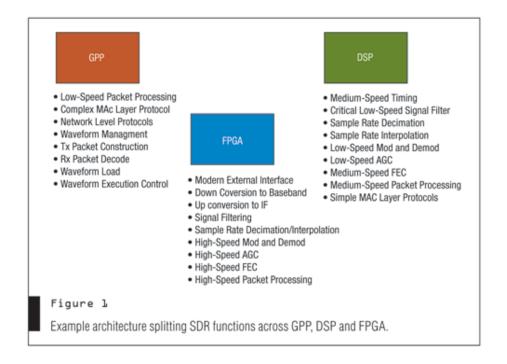

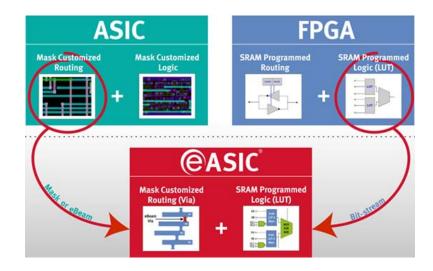

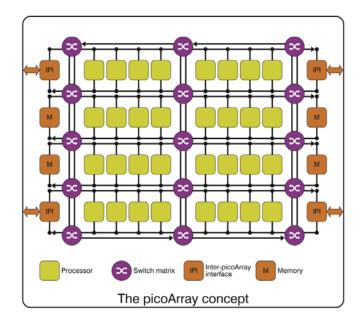

A closer look at current FPGA technology is included in Appendix A. Different technological options in implementing communication modulating techniques and Software Defined Radio are discussed. These options include Digital Signal Processors (DSP), Field Programmable Gate Arrays, General Purpose Processors (GPP) and Application Specific Integrated Circuits (ASICS) and a comparison between these choices is made. The results of the comparison are that a heterogeneous design that includes all three of a DSP, a GPP and an FPGA can provide the maximum performance and versatility. DSPs are better performing in sequential logic, whereas FPGAs are more efficient in executing parallel tasks. GPP are used in supporting the different network protocols and other similar tasks.

A lower level description compared to the design flow of Chapter IV of each block is included in Appendix B. The reason for many choices made in the parameters window of every block is mentioned next to the actual value of the parameter. In this way, the rebuilding of the design can be made solely based on this appendix. In the same time, further insight into the dependence of the desired results upon the chosen parameters is provided. In Appendix C, the Matlab code that helped the verification of the receiver design is included.

# ACKNOWLEDGMENTS

I would like to thank my advisor, Assistant Professor Frank Kragh, my Co-Advisor, Instructor Peter Ateshian and my Second Reader, Professor Roberto Cristi for their help to make my design work. They offered me their knowledge and their valuable time to help me overcome many of the difficulties I encountered. I would also like to thank Professor Alexander Julian for his advice on using System Generator, a program that he has mastered.

# I. INTRODUCTION

#### A. BACKGROUND ON SOFTWARE-DEFINED RADIO

A *software radio* is a radio which uses programmable hardware. Software is used to configure the hardware to meet different communication scheme specifications as well as to support several different services. According to J. Mitola (1993) "a *software radio* (SR) is a set of Digital Signal Processing (DSP) primitives, a metalevel system for combining the primitives into communications systems functions (transmitter, channel model, receiver . . .) and a set of target processors on which the software radio devices implemented in specific hardware, which provide a limited capability of switching between modulation schemes and services, mainly due to the static hardware used. An ideal SR receiver directly samples the antenna output. A *software-defined radio* (SDR) is a practical version of an SR. The received signals are sampled after a suitable band selection filter and frequency down conversion [2].

The flexibility and reconfigurability demonstrated by the SDR have become a reality largely due to the evolution of digital electronics processes defined in software instead of using static and application specific integrated circuits such as mixers, filters, amplifiers, modulators, demodulators, and detectors.

The concept of SDR has progressed further because of the advancement of Field Programmable Gate Arrays (FPGAs) and is currently a field of intensive research, even though the FPGAs are not the only platform upon which SDR can be based. General Purpose Processors (GPPs) and dedicated Digital Signal Processing (DSP) chips provide an alternative to FPGAs, having their own pros and cons. Nevertheless, the versatility that FPGAs demonstrate makes them unique in many aspects.

#### B. GOALS OF RESEARCH AND CONCEPTS

Recent technological advancements have allowed FPGAs to transform from an auxiliary device to a signal processing engine. Nowadays, not only can FPGAs compete

with dedicated circuits, but also they give life to sectors of science that need their versatility. They have enhanced the Software Defined Radio concept, which is a great advancement versus the normal Radio concept.

The main goal of this research is the design of a Binary Frequency Shift Keying (BFSK) transmitter and receiver. The BFSK modulation is used for the illustration of the techniques in designing a communication system in FPGAs. The reason is that BFSK is a simple, but robust modulation that can be received non-coherently. The design process also helps acquiring a greater experience in the design of FPGAs using some of the easier to use but powerful schematic, synthesis and place and route tools available today.

The second goal of the research is to track the advancements made in the field of FPGAs and inform on the usefulness and possible implementations of FPGAs.

# C. METHODOLOGY AND SCOPE OF THE RESEARCH

Xilinx's System Generation 10.1 SP2 is the schematic tool used to design a BFSK transceiver. After verifying that the design worked correctly, the code of the design was automatically generated by System Generator and the code was loaded into the Integrated Software Environment (ISE<sup>TM</sup>) to be synthesized, placed and routed, and finally downloaded to the target FPGA, which is a Xilinx's Virtex-4. Nevertheless, the verification of the implementation on the chip was not done due to time constraints.

The main challenge to the design is to achieve the synchronization required in order for the receiver to be able to distinguish the beginning and end of different packets of incoming data. The length of the packet was chosen to be fixed at 128 bits and the first 8 bits compose the preamble that facilitates the bit synchronization and packet detection.

#### D. BENEFITS OF THE RESEARCH

The concept of Software Defined Radio is fascinating but complex. Designing different modulation schemes that can be downloaded to an FPGA is an easy way to design a simple Software Defined Radio. On the other hand, all digital modulations share

the same basic principles; thus, synchronization techniques from one modulation can be borrowed and modified to work with another modulation scheme. A fully working digital BFSK transceiver is simulated in this thesis.

The research made regarding FPGAs unveiled the fact that while technology is changing, some arguments, like power consumption, that were once against the use of FPGAs, may be today their strong point. The system designer must always be up-to-date and adaptive regarding new technologies since FPGAs are going to be used more extensively in the future [3].

#### E. ORGANIZATION OF THE THESIS

Chapter II includes background regarding Binary Frequency Shift Keying. A Non-Coherent BFSK receiver is presented in order to facilitate the understanding of the design that was implemented in an FPGA. Also, the concept of convolutional encoding is introduced.

Chapter III contains the description of the design environment used, namely Xilinx's System Generator, ISE and ChipScope Pro along with the characteristics of the board used for the design. The high level of maturity and the friendly interface of the software product played a key role in the successful completion of the whole project.

Chapter IV gives a detailed description of the software design of a BFSK transmitter and receiver. The description includes the logic for the design choices that were made, the reason behind the choice of specific components, and the explanation of the function of many blocks.

Chapter V discusses the results taken by simulation in the design environment. Input and output are compared using Matlab and the correctness of the results is discussed.

Chapter VI includes an outline of the work made, the significant results taken, the limitations of the design, and recommendations for future work.

In Appendix A, an extensive background regarding FPGAs is given, explaining that they are well suited for Software Defined Radios. FPGA's positive and negative aspects are mentioned and are compared with General Purpose Processors, Digital Signal Processors and Application Specific Integrated Circuits.

In Appendix B, a detailed description of the design is given in a per figure and per block basis. Reading Appendix B in parallel with Chapter IV provides a better understanding of the blocks and the reason they were used.

In Appendix C, the Matlab code used to verify the results taken by System Generator is shown.

In this chapter, the concept of Software Defined Radio was introduced. The idea of SDR is realized by building a BFSK transceiver using an FPGA. In order to provide a solid background to facilitate understanding the design, the next chapter discusses BFSK modulation and demodulation and convolutional encoding.

# II. BINARY FREQUENCY SHIFT KEYING MODULATION SCHEME AND CONVOLUTIONAL ENCODING

BFSK is a basic digital modulation scheme. Its concept is not presented in depth, but can be found in any introductory textbook concerning communications. The textbook used as a reference for this brief introduction is [4, p. 198] along with [5], which both include a detailed description of the BFSK modulation scheme and a BFSK receiver. An introduction to convolutional encoding is also given at the end of this chapter.

#### A. BFSK MODULATION

In BFSK, two distinct frequencies are chosen to represent the two possible values of a bit. The equation that describes the transmission signal *s* of the  $i^{th}$  bit that is produced by this modulation technique is the following [5]:

$$s(t) = \sqrt{2}A_c \cos\left[2\pi \left(f_c + b\left(t\right) \cdot \frac{\Delta f}{2}\right)t + \theta_i\right], \quad \text{for } iT_b \ge t \ge (i-1)T_b \tag{2.1}$$

where  $T_b$  is the bit duration,  $A_c$  is the carrier's amplitude,  $f_c$  is the mean signaling frequency in Hz, b(t) is the value of the transmitted bit in bipolar form where 1 corresponds to bit 1 and -1 corresponds to bit 0,  $\Delta f$  is the frequency separation of the two frequencies, and  $\theta_i$  is the *i*<sup>th</sup> bit phase.

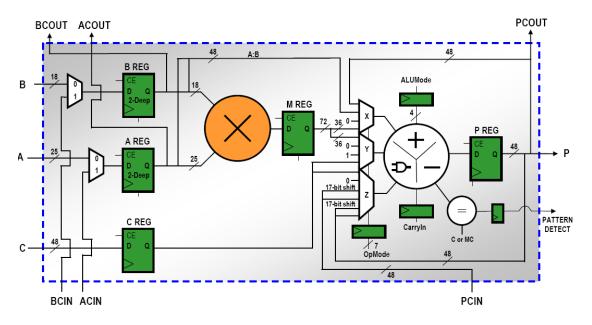

A BFSK receiver is distinguished by coherent or non-coherent depending if the knowledge of the phase information of the received signal is prerequisite for the receiver to work properly. In this thesis, the receiver of choice is non-coherent which decreases the complexity of the receiver circuit, eliminating the need for an extra circuit that would acquire the phase information. The configuration that allows the realization of a Non-Coherent (NC) reception is the energy detector. A diagram of a NC BFSK receiver is shown in Figure 1 [5].

$$s(t) = \sqrt{2} A_c \cos\left[(\omega_c \pm \Delta \omega/2)t + \theta_i\right]$$

$$s(t) = \sqrt{2} A_c \cos\left[(\omega_c \pm \Delta \omega/2)t + \theta_i\right]$$

$$\frac{s(t) = \sqrt{2} A_c \cos\left[(\omega_c \pm \Delta \omega/2)t + \theta_i\right]}{\left[\frac{1}{L_b}\int_0^{T_b}(\bullet)dt + \frac{1}{L_b}\int_0^{T_b}(\bullet)dt + \frac{1}{L_b}\int_$$

Figure 1 Block diagram of a NCBFSK receiver (From: [5]).

The received signal is distributed in two distinct paths, one for each frequency. To each path, the signal is further divided among two branches; one branch is configured to detect the in-phase (I) signal and the other branch the quadrature (Q) signal of the respective frequency. Each branch consists of a mixer, an integrator and the squaring function. Both branches and the summer at their end consist of a non-coherent matched filter. The term non-coherent matched filter means that this filter does not try to match the carrier phase, but only the envelope of the signal [5, pp. 256-258].

The structure is self similar, thus, the analysis made for the case of bit '1' transmitted is exactly inverse to the case of bit '0' transmitted. For a bit '1' transmitted, the input to the integrator of the top path is given by [5]:

$$r_{l_{i}}(t) = 2s(t)\cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t\right]$$

$$= 2\sqrt{2}A_{c}\cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right] \cdot \cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t\right]$$

$$= \sqrt{2}A_{c}\left\{\cos\left(\theta_{i}\right) + \cos\left[2\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right]\right\}.$$

(2.2)

Similarly, the input to the other integrator in the top non-coherent matched filter is

$$r_{1q}(t) = 2s(t)\sin\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t\right]$$

$$= 2\sqrt{2}A_{c}\cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right] \cdot \sin\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t\right]$$

$$= \sqrt{2}A_{c}\left\{-\sin\left(\theta_{i}\right) + \sin\left[2\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right]\right\}.$$

(2.3)

The integrator outputs for the two branches of the top path are:

$$X_{1_{i}}(T_{b}) = \sqrt{2}A_{c}\left\{\cos\theta_{i} + \frac{R_{b}}{4\pi\left(f_{c} + \Delta f/2\right)} \cdot \left[\cos\theta_{i} \cdot \sin\left[4\pi\left(f_{c} + \Delta f/2\right)T_{b}\right] + \sin\theta_{i}\left\{\cos\left[4\pi\left(f_{c} + \Delta f/2\right)T_{b}\right] - 1\right\}\right]\right\} (2.4)$$

for the I channel, and

$$X_{1_{q}}(T_{b}) = \sqrt{2}A_{c}\left\{-\sin\theta_{i} + \frac{R_{b}}{4\pi(f_{c} + \Delta f/2)} \left\{ \cos\theta_{i}\left\{\cos\left[4\pi(f_{c} + \Delta f/2)T_{b}\right] + \cos\theta_{i}\left\{\cos\left[4\pi(f_{c} + \Delta f/2)T_{b}\right] - 1\right\} \right\} \right\}$$

(2.5)

for the Q channel.

If the right conditions are met, the above expressions are simplified. Thus, when  $f_c$  is chosen to be an integer multiple of half the bit rate  $R_b$  and  $\Delta f$  is chosen to be an integer multiple of the bit rate  $R_b$ , where  $R_b = \frac{1}{T_b}$ , only the first terms of the above expressions are non-zero. These conditions are known as *orthogonal* signaling [3, pp. 200-204]. Following that restriction, the outputs of the integrators of the top NCMF are:

$$X_{1_i}(T_b) = \sqrt{2}A_c \cdot \cos\theta_i \tag{2.6}$$

and

$$X_{1_q}(T_b) = -\sqrt{2}A_c \cdot \sin\theta_i \,. \tag{2.7}$$

The outputs of the squaring block are

$$V_{l_i}(T_b) = 2A_c^2 \cdot \cos^2 \theta_i \tag{2.8}$$

and

$$V_{1_a}(T_b) = 2A_c^2 \cdot \sin^2 \theta_i \,. \tag{2.9}$$

Summing the outputs of the two branches yields

$$V_1(T_b) = 2A_c^2 (\sin^2 \theta_i + \cos^2 \theta_i) = 2A_c^2$$

(2.10)

as the output of the top path. The output of the I-channel mixer in the bottom NCMF in Figure 1 is

$$r_{2_{i}}(t) = 2s(t)\cos\left[\left(\omega_{c} - \frac{\Delta\omega}{2}\right)t\right]$$

$$= 2\sqrt{2}A_{c}\cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right] \cdot \cos\left[\left(\omega_{c} - \frac{\Delta\omega}{2}\right)t\right]$$

$$= \sqrt{2}A_{c}\left[\cos\left(\Delta\omega \cdot t + \theta_{i}\right) + \cos\left(2\omega_{c}t + \theta_{i}\right)\right].$$

(2.11)

The output of the Q-channel mixer in the bottom NCMF in Figure 1 is

$$r_{2q}(t) = 2s(t)\sin\left[\left(\omega_{c} - \frac{\Delta\omega}{2}\right)t\right]$$

$$= 2\sqrt{2}A_{c}\cos\left[\left(\omega_{c} + \frac{\Delta\omega}{2}\right)t + \theta_{i}\right] \cdot \sin\left[\left(\omega_{c} - \frac{\Delta\omega}{2}\right)t\right]$$

$$= \sqrt{2}A_{c}\left[-\sin\left(\Delta\omega \cdot t + \theta_{i}\right) + \sin\left(2\omega_{c}t + \theta_{i}\right)\right].$$

(2.12)

The outputs of the integrators of the bottom NCMF are

~

$$X_{2_{i}}(T_{b}) = \frac{\sqrt{2}A_{c}R_{b}}{2\pi} \begin{cases} \frac{\cos\theta_{i}}{\Delta f}\sin(2\pi\Delta f \cdot T_{b}) + \frac{\sin\theta_{i}}{\Delta f}\left[\cos(2\pi\Delta f \cdot T) - 1\right] + \\ \frac{1}{2f_{c}}\left\{\cos\theta_{i} \cdot \sin(4\pi f_{c}T_{b}) + \sin\theta_{i}\left[\cos(4\pi f_{c}T_{b}) - 1\right]\right\} \end{cases}$$

(2.13)

for the I-channel, and

$$X_{2_{q}}(T_{b}) = \frac{\sqrt{2}A_{c}R_{b}}{2\pi} \begin{cases} -\frac{\sin\theta_{i}}{\Delta f}\sin\left(2\pi\Delta f\cdot T_{b}\right) + \frac{\cos\theta_{i}}{\Delta f}\left[\cos\left(2\pi\Delta f\cdot T\right) - 1\right] + \\ \frac{1}{2f_{c}}\left\{\sin\theta_{i}\cdot\sin\left(4\pi f_{c}T_{b}\right) - \cos\theta_{i}\left[\cos\left(4\pi f_{c}T_{b}\right) - 1\right]\right\} \end{cases}$$

(2.14)

for the Q-channel.

If orthogonal signaling is chosen, i.e.,  $\Delta f = mR_b$  and  $f_c = n\frac{R_b}{2}$  where *n* and *m* are integers, the outputs of the integrators in the bottom NCMF simplify to  $X_{2_i}(T_b) = 0$  and  $X_{2_q}(T_b) = 0$ . This in turn yields

$$V_2(T_b) = 0 (2.15)$$

and using equation (2.10) and (2.15) the output of the subtraction of the paths is

$$V_1 - V_2 = 2A_c^2. (2.16)$$

For the case that bit '0' is transmitted, the whole process is inverted and the respective outputs of the two paths would be  $v_1(T_b) = 0$ , and  $v_2(T_b) = 2A_c^2(\sin^2\theta_i + \cos^2\theta_i) = 2A_c^2$ . Hence, the output of the subtraction of the two paths is now  $-2A_c^2$ . Sampling the final output at the end of the duration of each bit reveals the value of the transmitted bit.

It is obvious that this implementation relies heavily on proper bit synchronization, which means that the receiver should know the exact duration of each bit and when each bit ends. To acquire this information an extra circuit is needed and when the timing information is incorrect, severe degradation of the performance of the receiver may result. Many Time Error Detectors (TEDs) for discrete time implementations are presented in [6], including the Early-Late TED, the Zero Crossing TED, and the Gardner TED.

In summary, the energy of the two branches of each path are added and compared to the energy of the other path. The decision made about the received bit is in favor of the bit that corresponds to the frequency of the path with the highest energy. In order to minimize the cross product of energies, the frequencies used must be orthogonal which implies a tone spacing that is a multiple of the bit rate and a center frequency that is a multiple of half the bit rate [5].

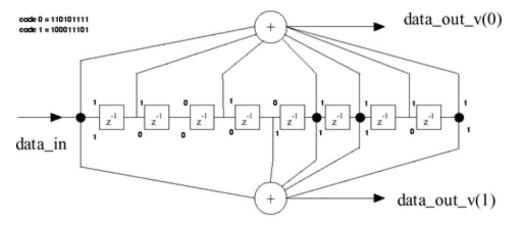

#### **B. CONVOLUTIONAL** ENCODING

Encoding in digital communications is used for forward error correction. The convolutional codes are one of the two most commonly used along with block codes. They were introduced in 1955 by Elias [7].

Convolutional codes are characterized by the *code rate*  $r = \frac{k}{n}$ , where k is the length of the input word and n is the length of the output word, and by the memory order

*m*. The memory order *m* is the number of memory elements that are included in the encoder and is a crucial parameter of the performance of a code. Each code can be uniquely described by a matrix with octal numbers as elements. The number of columns in this matrix corresponds to the *n* parameter and the number of rows to the *k* parameter. The actual value of the octal number reveals the interconnections that yield the respective output, counting in binary from right to left. In the example taken from [8], in Figure 2, we can identify an  $r = \frac{1}{2}$  code with a convolutional code array of [133,171]. The number 133 is the octal equivalent of binary 1011011 and corresponds to output  $C_0$ . This specific code is an industry standard code for m = 6. The constraint length  $\kappa$  for the case of k = 1 is  $\kappa = m+1$ . In this thesis, the industry standard convolutional code for  $r = \frac{1}{2}$  and  $\kappa = 3$ , namely [7 5], is used.

Figure 2 Convolutional Encoder Block Diagram of code rate  $r = \frac{1}{2}$  and  $\kappa = 7$ .

Convolutional encoded streams are usually decoded by Viterbi decoders, invented by Viterbi [9]. Viterbi decoders implement maximum likelihood decoding with a slight performance penalty due to finite decoder memory [10]. This chapter has explained the fundamental principles required to understand the NCBFSK transmitter and receiver design detailed in the remainder of this document. The next chapter describes the software and hardware design tools used in this design effort.

## III. DESIGN ENVIRONMENT

Xilinx offers a full suite of programs that provides an integrated development environment for its FPGAs. This suite is named Integrated Software Environment (ISE) Design Suite and the main programs that are included are System Generator for DSP, ISE Project Navigator, ChipScope Pro Tool, PlanAhead and AccelDSP Synthesis Tool [11]. Not all of these tools were used because each program has a very specific functionality, some of which were not needed. System Generator was used as the main design entry and simulation program and ISE Project Navigator as the program that implements the design into the targeted Xilinx device.

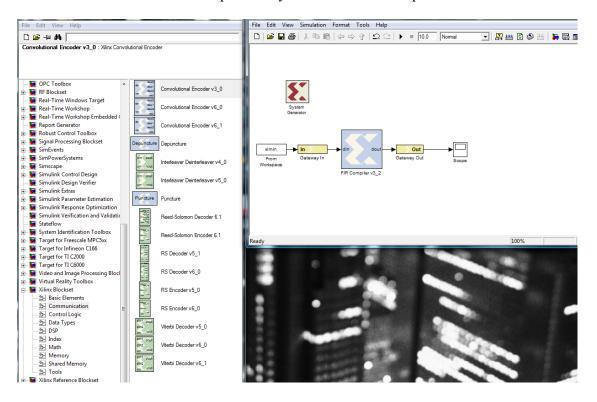

## A. SYST EM GENERATOR

System Generator is a FPGA design program that offers the necessary libraries of blocksets, making use of the Mathworks' Simulink design environment. Simulink is a schematic tool that is part of Matlab and is known for its efficiency and ease of use among engineers. For this reason, System Generator (Sysgen) chose this environment to offer the system modeling, making available the mixing of components from Simulink and Sysgen for simulation purposes (Figure 3). Sysgen also provides automatic code generation that can be then downloaded to Xilinx's FPGAs. The Hardware Description Language (HDL) that is used during code generation can be chosen from the Sysgen token and is either VHDL or Verilog [12].

The blocks offered by Sysgen are guaranteed to be synthesizable, solving a great problem for the designer. Blocks are schematic components that implement primitive functions and offer the option of default along with customizable inputs and outputs that can be interconnected. More complex blocks exist as well, yielding the opportunity to construct a complex design without much effort. A full list and description of all the available blocks is included in [13] and a more technical description of the Intellectual Properties blocks is included in [14]. Most of these blocks are DSP related and only a few are dedicated to communications. In the later case, an extra license is usually needed in order for them to integrate into the design. Their color is green by default and is clearly shown in Figure 3. The block 'System Generator' is mandatory to every design and the blocks 'Gateway In' and 'Gateway Out' define the limits of the design that are going to be translated in an FPGA circuit. The current version of Sysgen is 10.1 with Service Pack 2.

Figure 3 illustrates a very simple example, where a Finite Impulse Response (FIR) Filter is designed. The input is supplied by Matlab and the output is viewed by double clicking on the 'Scope.' The parameters of the single Xilinx block used are defined in the respective window that appears when the FIR block is selected. Neither of the Simulink blocks, 'From Workspace' and 'Scope,' are synthesizable. They are only used during the design phase for simulation purposes.

Other parameters that are common to many Sysgen blocks are the format and width of the output values [13, p. 44]. There are blocks dedicated to manipulate the data type and alter their internal structure. For example, the Enable and Reset signal are only allowed to be Boolean, thus an unsigned one bit integer must be reinterpreted as a Boolean number. This is accomplished by the blocks 'Reinterpret' or 'Convert.'

Figure 3 Example of the environment and the blocks offered by Sysgen.

Another block of special use is 'MCode' [13, p. 239]. It allows writing a program in Matlab and saving it in the block. Then, Sysgen is responsible for synthesizing this program. There are many constraints regarding the commands that can be used in such a program. As an example, the division by a number different from a power of two is not supported. Nevertheless, this block is very useful to describe state machines, and as such, it has been used many times in the BFSK design.

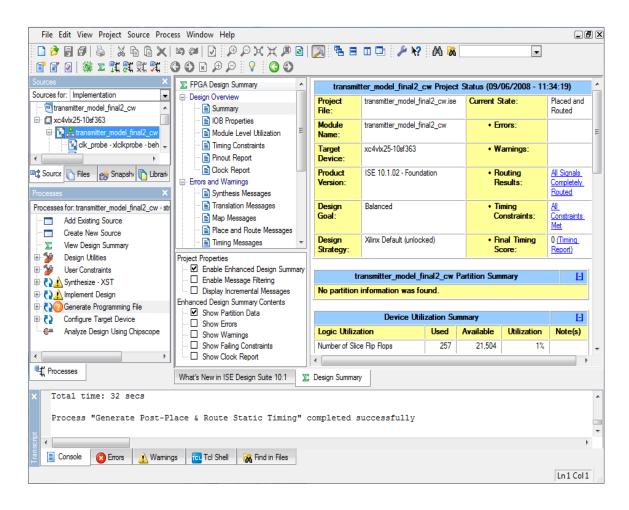

## **B. ISE PROJECT MANAGER**

After finishing with the design and generating the code for the HDL language of choice via Sysgen, the source file is loaded into the ISE Project Manager as a project. This Manager is responsible for the synthesis, implementation, and verification of the design and the target device configuration [15].

After loading a project created by Sysgen, source files can be added, created or modified. Other available processes under the Processes Window, as shown in the left column in Figure 4, are as follows:

- Add timing constraints or define Input Output (IO) pins under User Constraints choice.

- Synthesize the project or generate post-synthesis simulation under Synthesize –XST. At this step HDL programs are converted to netlist files that are used by the implementation step.

- Translate the logical design (netlist file) to a physical file format, to make the mapping of the design to the FPGA, and to place and route the mapping to the FPGA of choice under Implement Design choice. The placement step includes the decision made by the program regarding where to place the logic elements given the internal structure of the target device. Then, routing is responsible for finding the optimized connecting paths between these placed components.

- Generate the programming file that will be installed into the FPGA under Generate Programming File,

- Configure Target Device, and

- Use the ChipScope Pro program to verify the actual implementation into the FPGA under Analyze Design Using Chipscope. Every step of the implementation process described above has its own tools for testing and simulating the design. ChipScope is responsible to check the functionality of the final design installed into the FPGA.

Figure 4 Project Navigator Main Window.

#### C. AVNET BOARD

The mainboard to be used for the project is designed by AVNET and is called the Xilinx<sup>®</sup> Virtex<sup>™</sup>-4 LX LC Development Kit interconnected with the Analog to Digital (A/D) and Digital to Analog (D/A) Converter P160 provided by Avnet as well.

The mainboard's key features are the Virtex XC4VLX25 FPGA, 10/100 Ethernet interface and 64 MB Double Date Rate (DDR) Synchronous Dynamic Random Access Memory (SDRAM). The Virtex XC4VLX25 is a low entry FPGA of the Virtex-4 family and contains 24,192 logic cells and 48 dedicated DSP cells called XtremeDSP (18-bits x 18-bits, two's complement, signed Multiplier). It is manufactured using the 90nm Copper CMOS Process and it has no possibility of using the embedded soft processor PowerPC 405 core, due to size constraints [16]. The Analog Module P160 features two 12-bit 53 Msps A/D converters and two 12-bit 165 Msps D/A converters yielding much flexibility for the design [17]. Nevertheless, this module has not been used in any test in this research, mainly due to time constraints. The description of its pins and interfaces is in [18].

The literature recommended for the Sysgen and ISE is limited to the Xilinx Manuals. These manuals are included in a help guide offered by Xilinx as an internet-accessible Acrobat file [19]. For System generator there is also a manual that includes introductory labs and block and program reference manuals in its support page under the documentation tab and the Design Tool choice [20]. Extensive documentation of the most complex blocks is given in the same page under the IP Cores choice [21]. For the ISE project manager the documentation can be reached through the help guide stated above after choosing 'ISE Help' [15].

Sysgen and ISE Project Manager were extensively used for the design and the generation of the programming file of the non-coherent Binary Frequency Shift Keying Transmitter-Receiver presented in the next chapter. The plethora of tools offered by these programs made the design straight-forward, compared to writing directly to an HDL language. Xilinx is also supporting its programs online, making the troubleshooting easier.

THIS PAGE INTENTIONALLY LEFT BLANK

# **IV. DESIGN** FLOW

In this chapter, the logic flow of the design is discussed in detail. The basic principles of the BFSK transmitter and receiver illustrated in Chapter II are implemented in Simulink using Xilinx's blocks. The transmitter and receiver are separated into two different designs. The design is further exemplified in a per figure and per block basis in the Appendix B, where key parameters and Matlab code, where applicable, are also given.

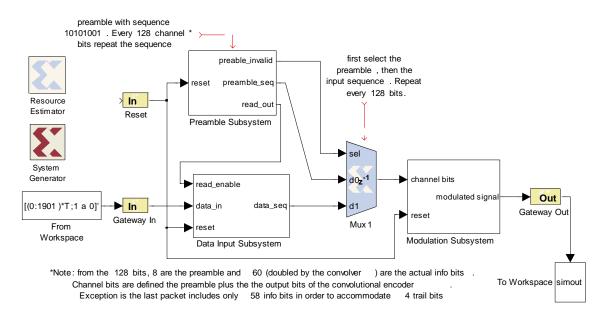

## A. TRANSMITTER

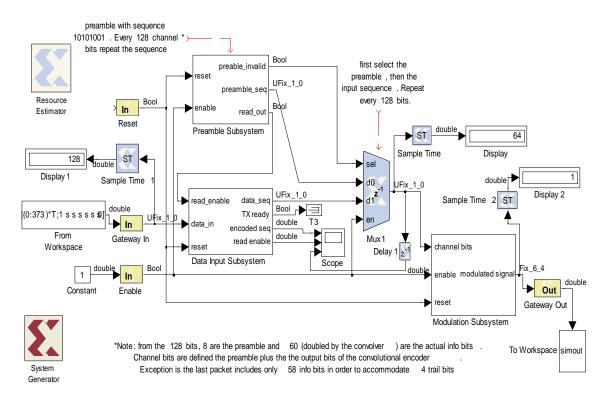

The transmitter, illustrated in Figure 5, is the combination of three distinct parts: the preamble, the data input and the modulation circuitry. The data is transmitted in blocks of 120 bits. An eight bit preamble with pattern 10101001 is attached in front of every packet to facilitate packet synchronization at the receiver. For simulation purposes, Simulink's blocks 'From Workspace' and 'To Workspace' were used to supply the design with input bits and store them, respectively. The results were also visually verified at each stage using 'Scope' blocks.

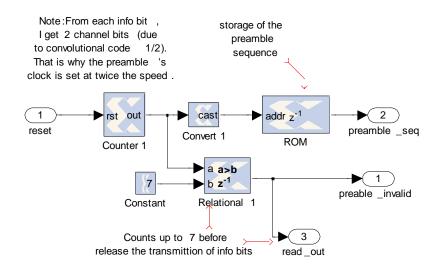

# 1. Preamble Subsystem

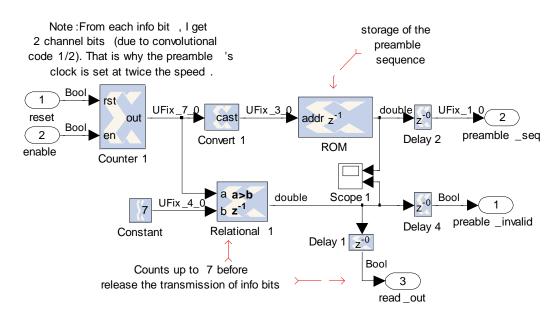

The Preamble Subsystem (Figure 6) is responsible for the attachment of the preamble at the start of each packet. This subsystem is also responsible for the blocking of data bits whenever the preamble is transmitted and controlling the multiplexer 'Mux 1' in Figure 5, which selects the data or the preamble.

The counter drives two blocks. It counts up to 127 and restarts from 0. While the counters output is seven or less, the preamble is valid and is read out to the modulation subsystem via the multiplexer 'Mux1' in Figure 5. The 'read\_out' and 'preamble\_invalid' are low and the output of the counter is directly translated to an address in the 'ROM' block. The content of this address appears at 'ROM' output and again through the 'Mux1' in Figure 5 to the Modulation Subsystem. 'Mux1' is switched in the correct position by 'preamble\_invalid' signal. 'Read\_out' is responsible to block the message bits and let them be stored in a memory while the preamble is transmitted. The signals 'preamble\_invalid' and 'read\_out' take the same values and have different names merely for illustration purposes.

Figure 6 Preamble Subsystem.

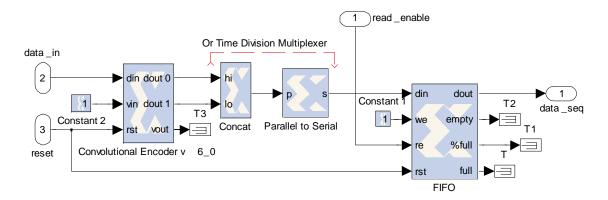

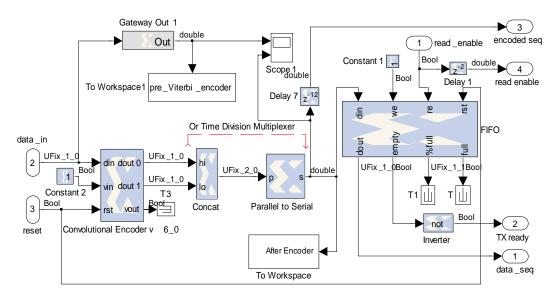

## 2. Data Input Subsystem

The Data Input Subsystem (Figure 7) is responsible for the convolutional encoding of the input sequence with a rate  $r = \frac{1}{2}$  code and the subsequent storage of the encoded bit in a First In First Out (FIFO) memory. The two streams created by the 'Convolutional Encoder' block merge back into one stream by the 'Concat' and 'Parallel to Serial' blocks. It should be noted that these two last blocks can be replaced by a 'Time Division Multiplexer' block. The bit period of the final stream is half the period of the message bits due to the encoding with rate  $r = \frac{1}{2}$ . In the 'Convolutional Encoder' parameters window, the constraint length was set to 3, meaning that the encoder is using a register of two flip-flops. The encoding vector of choice was [7 5], as explained in Section B in Chapter II.

Figure 7 Data Input Subsystem.

After being stored in the 'FIFO' memory, the data waits for the enable signal of the Preamble Subsystem in order to exit. At the same time, the multiplexer 'Mux1' in Figure 5 is switched to the correct position to allow the promulgation of the input data to the last subsystem. Each bit produces an FSK symbol of duration 64 samples in the Modulation Subsystem. This parameter can generally be adjusted from the panel of the blocks under the title 'Explicit sample period.'

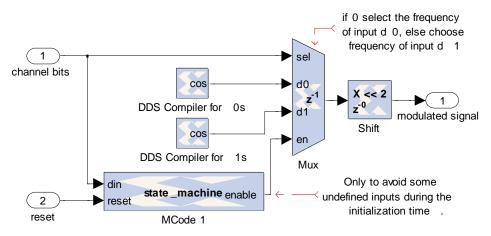

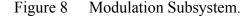

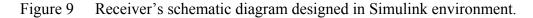

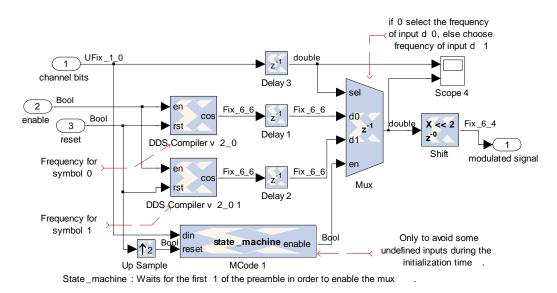

#### 3. Modulation Subsystem

The modulation subsystem, illustrated in Figure 8, uses each bit that appears at its entrance to choose between the two frequencies. This is accomplished by a multiplexer 'Mux,' where the selection pin (sel) is driven by the forwarded bits and the multiplexer data inputs are driven by two Direct Digital Synthesizers (DDSs). Each DDS generates a sine wave at one of the two frequencies for the BFSK signal. The DDS is a digital sinusoid generator and can produce frequencies up to half the frequency at which the DDS core will be clocked, i.e., the DDS clock rate, in order not to exceed the Nyquist frequency [22]. For the Xilinx Virtex-4, which can achieve clock speeds of 500 Mhz [23], the limit for the output frequency of the DDS is 250 Mhz when the DDS clock rate is set to the maximum possible frequency. Nevertheless, much lower frequencies were used and the frequencies for 1 and 0 are 45 MHz and 40 MHz, respectively. Given that the encoded bit rate of choice is R = 1.5625 Mbps, the two frequencies are not orthogonal based on the definition given in Section A in Chapter II. Even though this design choice may degrade the performance in a noisy environment, it does not have any noticeable impact in the noiseless analysis that follows. The 'Shift' block plays the role of amplification, multiplying the signal before transmission by a factor of four. Pulse shaping is not used in this design.

State\_machine : Waits for the first 1 of the preamble in order to enable the mux

The 'Mcode 1' in Figure 8 is used for initiation. During the beginning of the simulation, many signals inside the blocks start in undefined states and other blocks, like the multiplexer, cannot propagate these kinds of signals. A block that would enable the multiplexer after the propagation of the undefined signals was needed, without affecting the overall performance of the designs. Usually, a constant enable signal is used along with a delay measured exactly to overcome this problem. A very simple Matlab program was written that takes advantage of the fact that the first bit of the preamble is 1. Upon detection of the first 1 to the channel, the 'MCode 1' enables the multiplexer without any further interruption. It should be noticed that the command  $xfix({xlBoolean}, 0)$  was used in the program in order to avoid the use of a 'Convert' block. Otherwise, any value assigned as 0 or 1 in a Matlab Code is translated to an unsigned integer and cannot be used as it is to drive the enable port (en) of the 'Mux.' The xfix() command explicitly converts to the type described as the first argument. In this case, the value 0 is assigned as a Boolean type and not as an integer [13, p. 243].

# **B. RECEIVER**

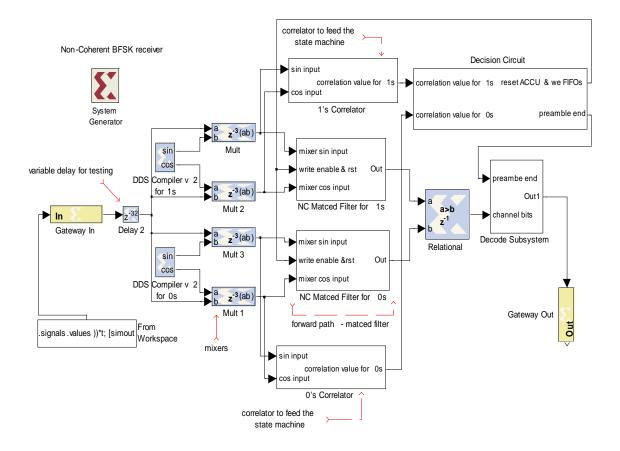

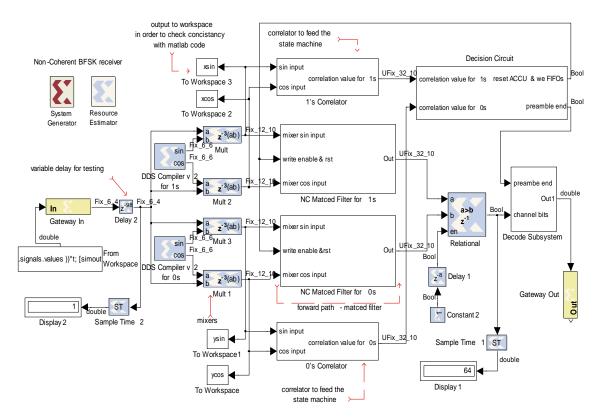

The non-coherent BFSK receiver is illustrated in Figure 9. The choice of a Non-Coherent (NC) receiver design was made to eliminate any need for an extra circuit that would extract the phase information from the received signal. The receiver consists of the following subsystems: the two Correlators, the Decision Circuit, the Timing Circuit, the two Non-Coherent Matched Filters and the Decoding Subsystem. The Correlators [24] and the Timing Circuit form the feedback path and the Non-Coherent Matched Filters and the Decoding Subsystem form the feed-forward path. The mixers are parts of both paths and are shown explicitly in the figure. The 'Relational' block compares the non-coherent matched filters' outputs and decides the value of the received bit. The circuit designed closely matches the theoretical diagram found in the Introduction of BFSK scheme in Figure 1 in Chapter II, with the addition of a time synchronization circuit and a Decode Subsystem.

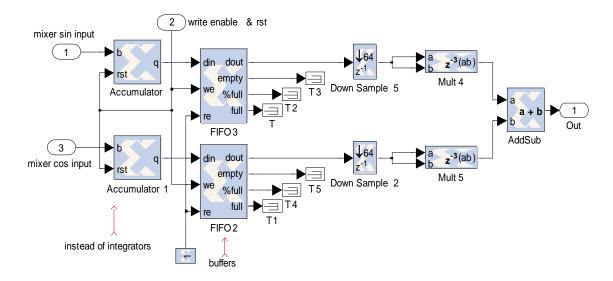

#### 1. Non-Coherent Matched Filter Subsystem

A non-coherent matched filter is introduced in Section A in Chapter II. The implementation of this filter in the BFSK receiver includes an integrator that integrates the input signal over the duration of a bit period  $T_b$ . Thus, correct timing for the specific design means the correct identification of the beginning of each bit in order to integrate over the correct time frame. This fact generates the need for a timing feedback circuit that will make this information available.

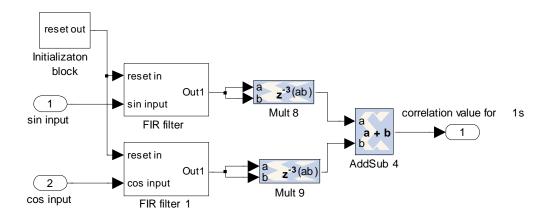

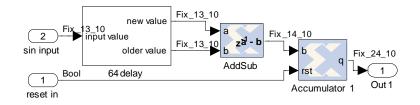

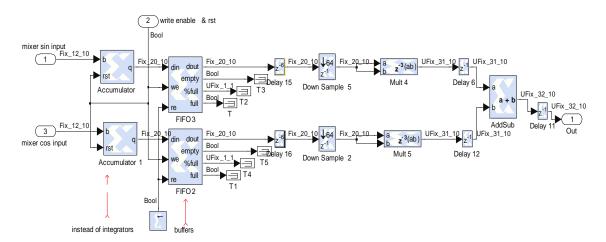

The NC Matched Filter Subsystem in Figure 10 has two filters where each one consists of two branches. The two branches correspond to the sine and the cosine at the symbol frequency. Each branch consists of a mixer (illustrated in Figure 9 before NC Matched Filter Subsystem), an accumulator, and a squaring block. Then, the two branches' outputs are added together to give the final output of each filter. The output

values of the two filters are compared in order to decide which frequency was transmitted. The frequency that was transmitted corresponds to the filter with the highest output value.

The accumulator included in the NC Matched Filter Subsystem is the followed discrete time equivalent of an integrator and it adds 64 consecutive values of the input signal before it is reset by the feedback timing circuit. Every accumulator is followed by a FIFO memory, which only reads the output of the accumulator just before the accumulator's reset signal is raised. In this way, the memory captures only the last value of the respective sum. The rest of the block is straight forward, with a squaring block and an adder that adds the signals of the two branches, yielding a single output from the subsystem. The downsample implemented in all branches between the FIFO memory and the squaring blocks is used in order to downgrade the unneeded computational load. After the accumulation of the correct 64 samples of a bit and the subsequent storage of this value to a FIFO memory element, the memory yields the same output for 64 consecutive time units. Thus, it is not necessary to do the computations for all values.

Figure 10 Non-Coherent Matched filter subsystem (one of two).

## 2. Timing Circuit

Synchronization circuits are categorized as data-aided and non data-aided (or blind) and the latter require no training data sequence [25]. As was mentioned previously in the transmitter description in Chapter IV, this design uses a data-aided circuit for the acquisition of the bit synchronization. The preamble is a known pattern that will help to identify not only the start time of each bit, but the commencement of each packet as well.

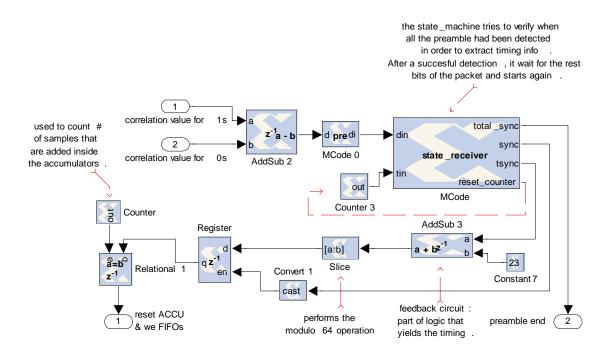

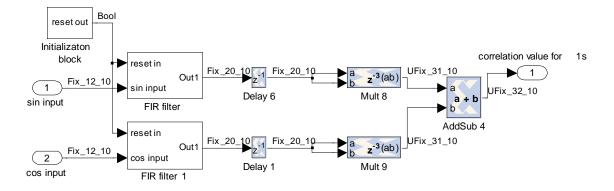

In this design, the feedback synchronization circuit is separated into three subsystems, the two Correlators and the Decision Circuit. The Correlators (Figure 11) work similarly to the NC Matched Filter Subsystem with the main difference being that accumulators have been replaced by Finite Impulse Response (FIR) filters. These filters constitute sliding window accumulators of the last 64 samples. In order to make a decision regarding the beginning and end of a bit, a circuit that updates its output at every received sample is needed. The correct timing is going to be extracted by the maxima and minima of this output. In contrast, the feed-forward path with the non-coherent matched filters need only accumulate the proper values and then yield a different output once every 64 samples and not every sample.

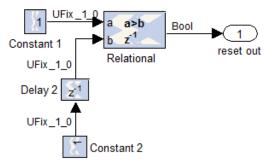

In Figure 11, the FIR is shown to be a custom FIR filter and not an off-the-shelf block provided by Xilinx. The reason is going to be analyzed in the troubleshooting section, but for the moment, it can be thought as an FIR filter with impulse response  $h(n) = \sum_{n=0}^{63} \delta(n-n_0)$ , where  $\delta(n) = \begin{cases} 1 & \text{if } n=0 \\ 0 & \text{if } n\neq 0 \end{cases}$ . The initialization block, as in the case of the block 'Mcode1' of the transmitter, is used only to prevent the undefined initial signals from propagating and to suppress errors during the simulation. It consists of a comparator that has two delayed versions of 1 in its inputs; thus, propagating an initial reset high signal once at the beginning of the simulation.

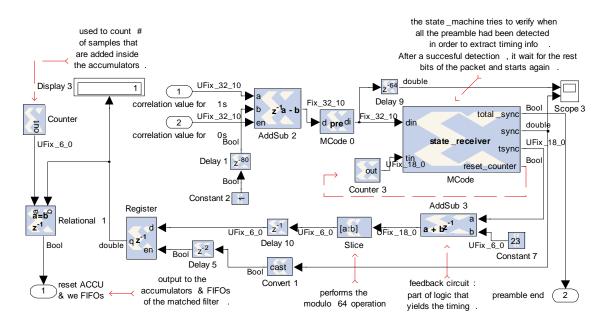

The difference of the outputs of the two correlators is the input to a logic block ('Mcode' block in Figure 12) that searches for maxima and minima of the input waveform. Given that the correlator yields a maximum when the correct 64 samples of a bit have been added, the expectation is that the 1's correlator will output a much higher

value than the 0's correlator when the whole first bit of the preamble has just been received. The opposite is expected at the second bit of the preamble, because it has the frequency corresponding to the 0 bit. Thus, the difference waveform is expected to be a maximum after receiving a 1 at the exact moment that all 64 samples of that 1 have entered the filter. Following the same reasoning, the difference waveform is expected to be a minimum after receiving a 0 at the exact moment that all 64 samples of that 0 have entered the filter. However, when two consecutive equal bits are received, the result is different. The output of the filter will reach an extremum at the moment that all the 64 samples of the first bit have entered the filter, and then remain at that extremum for the following 64 samples, corresponding to the second bit. Therefore, the filter output displays a plateau effect, which is less useful for symbol synchronization. After the identification of maxima and minima, a state machine tries to verify when the correct pattern of the preamble has been received. When this is the case, the timing of the bits is well known and this information is supplied to the accumulators of the NC Matched Filter Subsystem. This part is included in the Decision Circuit shown in Figure 12.