# SUPERCONDUCTING TECHNOLOGY ASSESSMENT

National Security Agency Office of Corporate Assessments

**AUGUST 2005**

| Report Documentation Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                          | Form Approved<br>OMB No. 0704-0188 |                   |                                             |                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------|-------------------|---------------------------------------------|-----------------------------------------------------------------|

| Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. |                                                                          |                                    |                   |                                             | is collection of information,<br>Highway, Suite 1204, Arlington |

| 1. REPORT DATE     2. REPORT TYPE       AUG 2005     N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                          |                                    |                   | 3. DATES COVERED                            |                                                                 |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                          |                                    |                   | 5a. CONTRACT NUMBER                         |                                                                 |

| Superconducting T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Cechnology Assessme                                                      | ent                                |                   | 5b. GRANT NUM                               | <b>IBER</b>                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |                                    |                   | 5c. PROGRAM E                               | LEMENT NUMBER                                                   |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |                                    |                   | 5d. PROJECT NU                              | JMBER                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |                                    |                   | 5e. TASK NUMB                               | ER                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |                                    |                   | 5f. WORK UNIT NUMBER                        |                                                                 |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>NSA Office of Corporate Assessments 9800 Savage Road, Suite 6468 For<br>George G. Meade, Maryland 20755                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |                                    | Suite 6468 Fort   | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER |                                                                 |

| 9. SPONSORING/MONITO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSOR/MONITOR'S ACRONYM(S) |                                    |                   |                                             |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |                                    |                   | 11. SPONSOR/M<br>NUMBER(S)                  | ONITOR'S REPORT                                                 |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT<br>Approved for public release, distribution unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          |                                    |                   |                                             |                                                                 |

| 13. SUPPLEMENTARY NOTES<br>The original document contains color images.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                                    |                   |                                             |                                                                 |

| 14. ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14. ABSTRACT                                                             |                                    |                   |                                             |                                                                 |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |                                    |                   |                                             |                                                                 |

| 16. SECURITY CLASSIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ATION OF:                                                                |                                    | 17. LIMITATION OF | 18. NUMBER                                  | 19a. NAME OF                                                    |

| a. REPORT<br><b>unclassified</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | b. ABSTRACT<br>unclassified                                              | c. THIS PAGE<br>unclassified       | - ABSTRACT<br>SAR | OF PAGES<br><b>257</b>                      | RESPONSIBLE PERSON                                              |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std Z39-18

# Superconducting Technology Assessment Letter of Promulgation

#### Background

This Superconducting Technology Assessment (STA) has been conducted by the National Security Agency to address the fundamental question of a potential replacement for silicon complementary metal oxide semiconductor (CMOS) in very high-end computing (HEC) environments. Recent industry trends clearly establish that design tradeoffs between power, clock and metrology have brought CMOS to the limits of its scalability. All microprocessor firms have turned to multiple cores and reduced power in efforts to improve performance. Increased parallelism on a chip permits some architectural innovation, but it also increasingly shifts issues of performance gains into software application environments, where there are already many practical limits to scalability of performance. For many demanding applications in the U. S. national security, scientific, medical and industrial sectors, availability of higher-performance components in well-balanced HEC environments is essential. Alternatives to CMOS must therefore be found.

The Semiconductor Industry Association (SIA) International Technology Roadmap for Semiconductors (ITRS) has identified Superconducting Rapid Single Flux Quantum (RSFQ) technology as the most promising technology in the continuing demand for faster processors. There has been steady progress in research in this technology, though with somewhat weaker efforts at development and industrialization. This assessment is an in-depth examination of RSFQ technologies with the singular objective of determining if a comprehensive roadmap for technology development is possible, aiming for industrial maturity in the 2010-2012 timeframe. The goal would be an RSFQ technology set sufficient to support development of true petaflop-scale computing at the end of this decade.

#### Methodology

A team of national experts in superconducting technologies was empanelled to conduct this assessment. It was chaired by Dr. John Pinkston, former Chief of Research, NSA. Membership is shown in Appendix B and included experts in processor architectures, several types of memories, interconnects, design and manufacturing in these technologies. The panel heard from academic, industrial and government experts in the field and reviewed available superconducting documentation. The panel also had the benefit of presentations and discussions with two leading HEC architects on system-level issues that could conceivably impact the use of RSFQ technologies. The panel had lengthy internal discussions on the mutual dependencies of various superconducting components. Availability, technical issues, development schedules and potential costs were discussed at length. The resulting roadmap represents a consensus of views with no substantial dissension among panel members. The panel was enjoined from examining HEC architectural issues and systems-level options, other than those bearing directly on technology envelopes (e.g., is a 50 Ghz clock a sufficient goal?).

#### Summary of Findings

The STA concluded that there were no significant outstanding research issues for RSFQ technologies. Speed, power and Josephson Junction density projections could be made reliably. Areas of risk have been identified and appropriately dealt with in the roadmap, with cautionary comments on mitigation or alternatives. Memories are clearly one such area, but this report concludes that the field suffers more from lack of research than available alternatives. The assessment, in fact, identifies several memory alternatives, each of which should be pursued until technology limits are clearly understood. Development of RSFQ technologies to sufficient levels of maturity, with appropriate milestones, could be achieved in the time frame of interest but would require a comprehensive and sustained government funded program of approximately \$100M/yr. The panel concluded that private sector interests in superconducting RSFQ would not be sufficient to spawn development and industrialization.

It is, of course, NSA's role to turn these STA findings into specific actions in partnership with national security community and other federal HEC users having extreme high end computing needs and the vision to pursue the performance goals that superconducting RSFQ appears to offer.

The undersigned government members of this study would like to commend our industry and academia participants for the balanced and constructive assessment results.

Ferrad Beloa

Dr. Fernand Bedard

George R. Cotter

T Tenksti

Dr. John T. Pinkston

Dr. Nancy K. Welker

Michael A. Escavage

# **TABLE OF CONTENTS**

# **EXECUTIVE SUMMARY**

| Assessment Objective and Findings | 01 |

|-----------------------------------|----|

| Limitations of Current Technology | 02 |

| Panel Tasked                      | 02 |

| RSFQ Technology Is Viable         | 03 |

| Roadmap Created                   | 04 |

| Government Investment Crucial     | 05 |

| Technical Issues                  | 05 |

| Conclusions                       | 05 |

|                                   |    |

# **CHAPTER 01: INTRODUCTION**

| 1.1   | NSA Dependent on High-End Computing                           | 07 |

|-------|---------------------------------------------------------------|----|

| 1.2   | Limitations of Conventional Technology for High-End Computing | 08 |

| 1.2.1 | Conventional Silicon Technology Not the Answer                | 08 |

| 1.2.2 | Supercomputing RSFQ a Viable Alternative                      | 08 |

| 1.3   | What is RSFQ Circuitry?                                       | 09 |

| 1.3.1 | Josephson Junctions                                           | 09 |

| 1.3.2 | RSFQ Attributes                                               | 10 |

| 1.4   | Summary of Panel's Efforts                                    | 10 |

| 1.4.1 | RSFQ Ready for Investment                                     | 11 |

| 1.4.2 | RSFQ Can Leverage Microprocessor Technology                   | 11 |

| 1.5   | Roadmap Created and Government Investment Needed              | 11 |

| 1.5.1 | Funding                                                       | 13 |

| 1.6   | Technical Issues                                              | 13 |

| 1.6.1 | Supercomputing System Constraints on the Use of RSFQ          | 13 |

| 1.6.2 | Fast, Low Latency Memory                                      | 15 |

| 1.6.3 | High-Speed Input/Output                                       | 15 |

| 1.6.4 | CAD Tools                                                     | 15 |

| 1.6.5 | Refrigeration                                                 | 15 |

| 1.7   | State of the Industry                                         | 15 |

| 1.8   | Contents of Study                                             | 16 |

| 1.9   | Chapter Summaries                                             | 16 |

## CHAPTER 02: ARCHITECTURAL CONSIDERATIONS FOR SUPERCONDUCTOR RSFQ MICROPROCESSORS

| 2.1   | Superconductor Microprocessors–Opportunities, Challenges, and Projections                 | 25 |

|-------|-------------------------------------------------------------------------------------------|----|

| 2.2   | Microprocessors – Current Status of RSFQ Microprocessor Design                            | 28 |

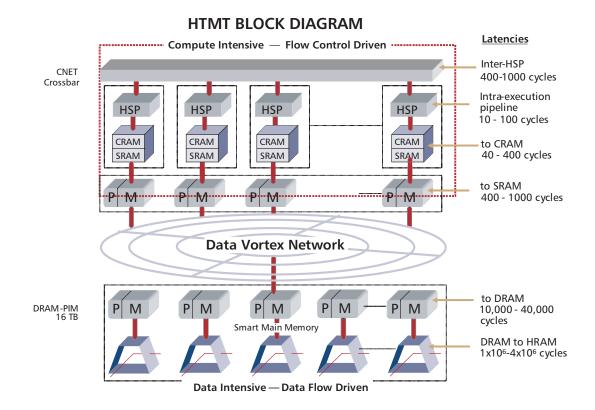

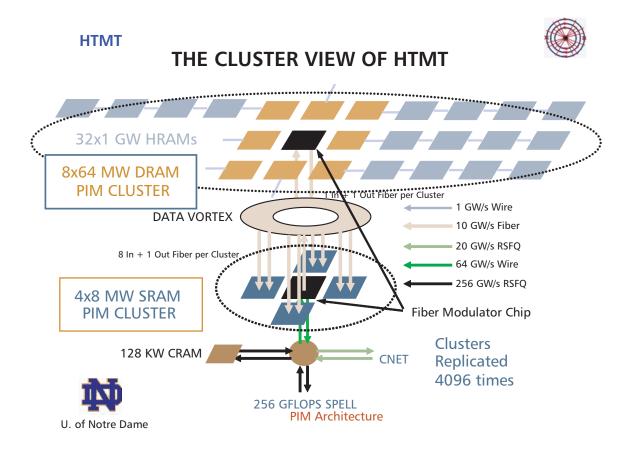

| 2.2.1 | SPELL Processors for the HTMT Petaflops System (1997-1999)                                | 28 |

| 2.2.2 | 20-GHz, 8-bit FLUX-1 Microprocessor (2000-2002)                                           | 29 |

| 2.2.3 | CORE1 Bit-serial Microprocessor Prototypes (2002-2005)                                    | 30 |

| 2.2.4 | Proposal for an RSFQ Petaflops Computer in Japan (est. 2005-2015)                         | 30 |

| 2.3   | Microprocessors – Readiness                                                               | 32 |

| 2.4   | Microprocessors – Issues and Concerns                                                     | 33 |

| 2.4.1 | Clocking for 50 GHz RSFQ Processors                                                       | 33 |

| 2.4.2 | Long Processing Pipelines                                                                 | 33 |

| 2.4.3 | On-chip Interconnect, Chip Area Reachable in a Single Cycle, and Register File Structures | 33 |

| 2.4.4 | Memory Hierarchy for Superconductor Processors and Systems                                | 34 |

| 2.4.5 | Memory Latency Tolerant Architectures                                                     | 35 |

| 2.5   | Microprocessors – Conclusions and Goals                                                   | 36 |

| 2.6   | Microprocessors – Roadmap and Milestones                                                  | 37 |

| 2.7   | Microprocessors – Funding                                                                 | 38 |

|       |                                                                                           |    |

# CHAPTER 03: SUPERCONDUCTIVE RSFQ PROCESSOR AND MEMORY TECHNOLOGY

| 3.1   | RSFQ Processors                                  | 43 |

|-------|--------------------------------------------------|----|

| 3.1.1 | RSFQ Processors – Status                         | 43 |

| 3.1.2 | RSFQ Processors – Readiness for Major Investment | 47 |

| 3.1.3 | RSFQ Processors – Roadmap                        | 49 |

| 3.1.4 | RSFQ Processors – Investment Required            | 50 |

| 3.1.5 | RSFQ Processors – Issues and Concerns            | 51 |

| 3.1.6 | RSFQ Processors – Projected Future Capability    | 52 |

| 3.2   | Memory                                           | 52 |

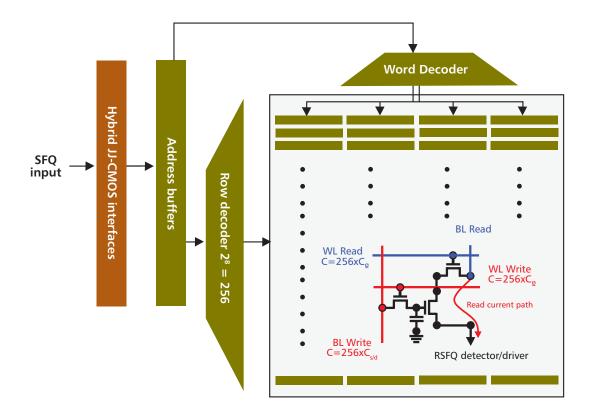

| 3.2.1 | Memory – Hybrid Josephson-CMOS RAM               | 54 |

| 3.2.2 | Memory – Single-Flux Quantum Memory              | 56 |

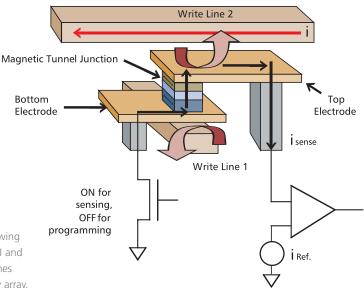

| 3.2.3 | Memory – MRAM                                    | 59 |

| 3.2.4 | Memory – Summation                               | 66 |

| 3.3   | CAD Tools and Design Methodologies               | 67 |

| 3.4   | Summary                                          | 72 |

# CHAPTER 04: SUPERCONDUCTIVE CHIP MANUFACTURE

| 78 |

|----|

| 79 |

| 82 |

| 83 |

| 84 |

| 84 |

| 85 |

| 86 |

| 87 |

| 89 |

| 90 |

| 90 |

| 92 |

|    |

# CHAPTER 05: INTERCONNECTS AND SYSTEM INPUT/OUTPUT

| 5.1   | Optical Interconnect Technology                                                | 99  |

|-------|--------------------------------------------------------------------------------|-----|

| 5.1.1 | Optical Interconnect Technology – Status                                       | 100 |

| 5.1.2 | Optical Interconnect Technology – Readiness                                    | 101 |

| 5.1.3 | Optical Interconnect Technology – Projections                                  | 102 |

| 5.1.4 | Optical Interconnect Technology – Issues and Concerns:                         | 103 |

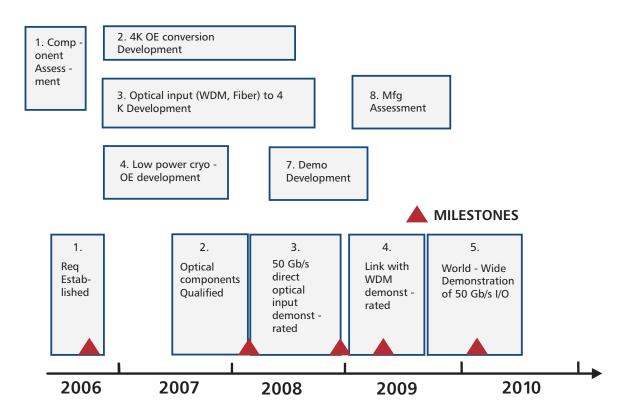

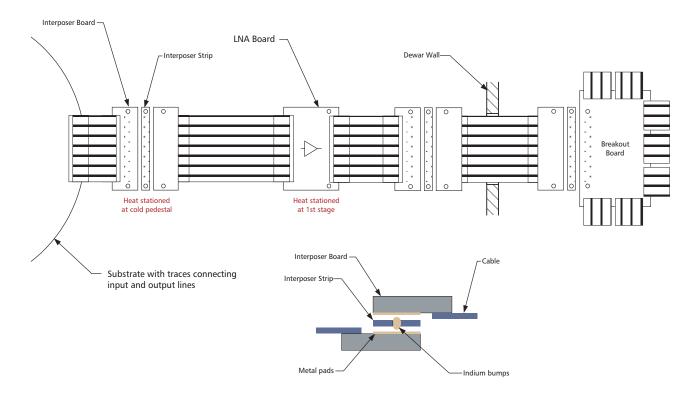

| 5.2   | Input: Data and Signal Transmission from Room Temperature to 4 K               | 103 |

| 5.2.1 | Input: Room Temperature to 4 K – Status                                        | 104 |

| 5.2.2 | Input: Room Temperature to 4 K – Issues and Concerns                           | 104 |

| 5.2.3 | Input: Room Temperature to 4 K – Roadmap                                       | 104 |

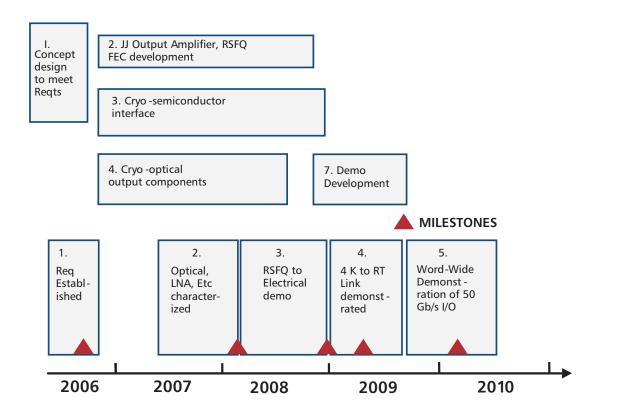

| 5.3   | Output: 4 K RSFQ to Room Temperature Electronics                               | 105 |

| 5.3.1 | Output: 4 K RSFQ to Room Temperature Electronics – Status                      | 105 |

| 5.3.2 | Output: 4 K RSFQ to Room Temperature Electronics – Readiness and Projections   | 106 |

| 5.3.3 | Output: 4 K RSFQ to Room Temperature Electronics – Issues and Concerns         | 107 |

| 5.3.4 | Output: 4 K RSFQ to Room Temperature Electronics – Roadmap and Funding Profile | 108 |

| 5.4   | Data Routing: 4 K RSFQ to 4 K RSFQ                                             | 108 |

| 5.4.1 | Data Routing: 4 K RSFQ to 4 K RSFQ – Status                                    | 109 |

| 5.4.2 | Data Routing: 4 K RSFQ to 4 K RSFQ – Readiness                                 | 110 |

| 5.4.3 | Data Routing: 4 K RSFQ to 4 K RSFQ – Issues and Concerns                       | 110 |

| 5.4.4 | Data Routing: 4 K RSFQ to 4 K RSFQ – Roadmap and Funding                       | 111 |

|       |                                                                                |     |

# **CHAPTER 06: SYSTEM INTEGRATION**

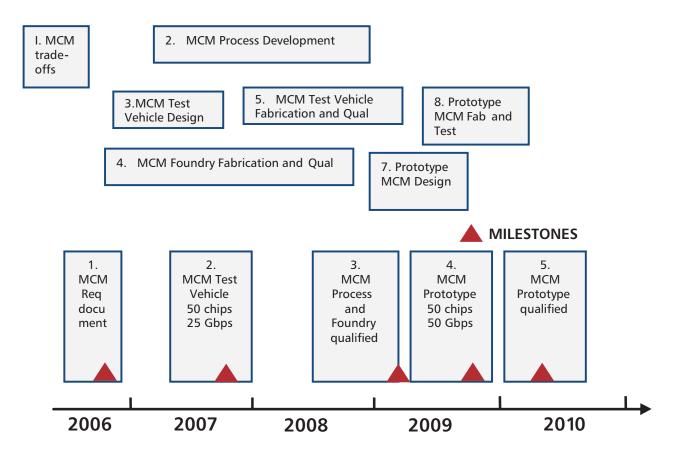

| 6.1   | Multi-chip Modules and Boards                       | 114 |

|-------|-----------------------------------------------------|-----|

| 6.1.1 | Multi-chip Modules and Boards – Status              | 114 |

| 6.1.2 | Multi-chip Modules and Boards – Readiness           | 115 |

| 6.1.3 | Multi-chip Modules and Boards – Projections         | 116 |

| 6.1.4 | Multi-chip Modules and Boards – Issues and Concerns | 116 |

| 6.1.5 | Multi-chip Modules and Boards – Roadmap and Funding | 117 |

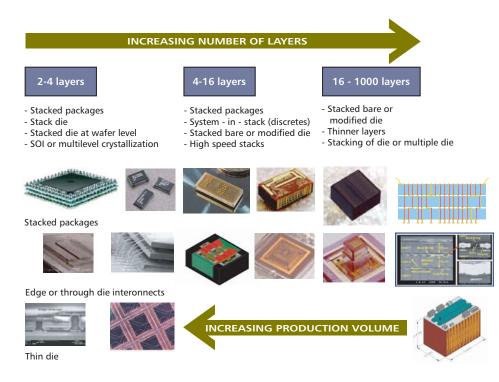

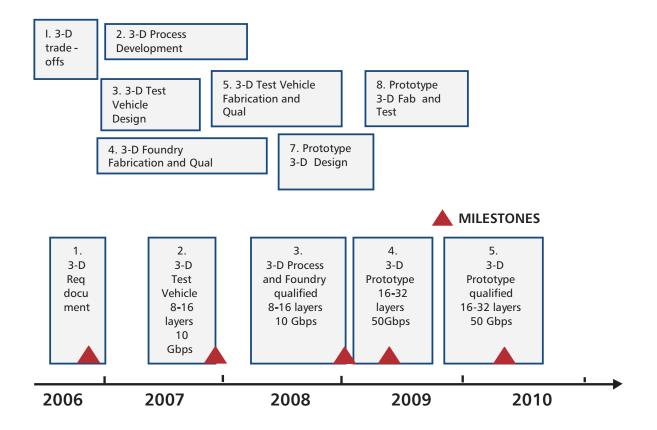

| 6.2   | 3-D Packaging                                       | 118 |

| 6.2.1 | 3-D Packaging – Status                              | 118 |

| 6.2.2 | 3-D Packaging – Readiness                           | 119 |

| 6.2.3 | 3-D Packaging – Issues and Concerns                 | 120 |

| 6.2.4 | 3-D Packaging – Roadmap and Funding                 | 120 |

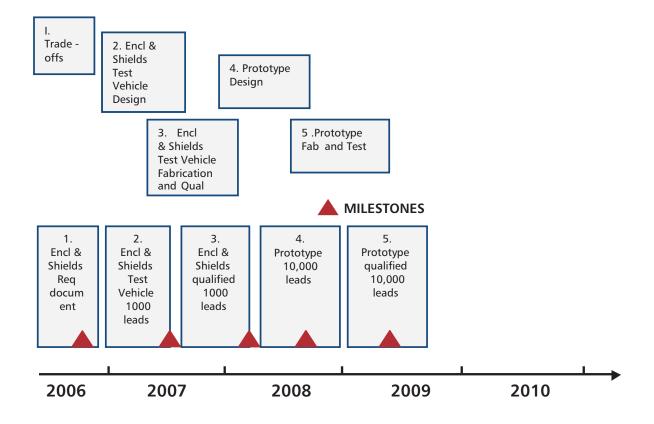

| 6.3   | Enclosures and Shields                              | 121 |

| 6.3.1 | Enclosures and Shields – Status                     | 121 |

| 6.3.2 | Enclosures and Shields – Readiness                  | 122 |

| 6.3.3 | Enclosures and Shields – Projections                | 122 |

| 6.3.4 | Enclosures and Shields – Issues and Concerns        | 122 |

| 6.3.5 | Enclosures and Shields – Roadmap and Funding        | 123 |

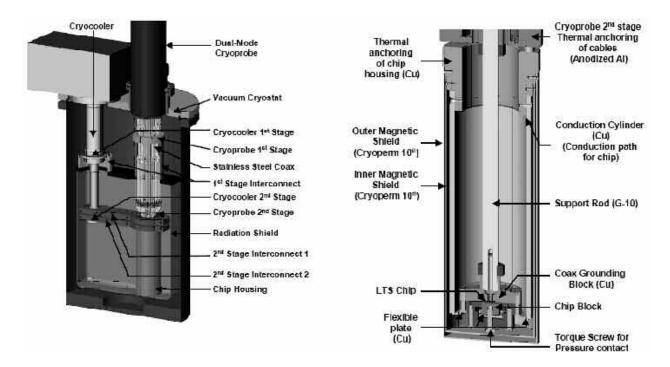

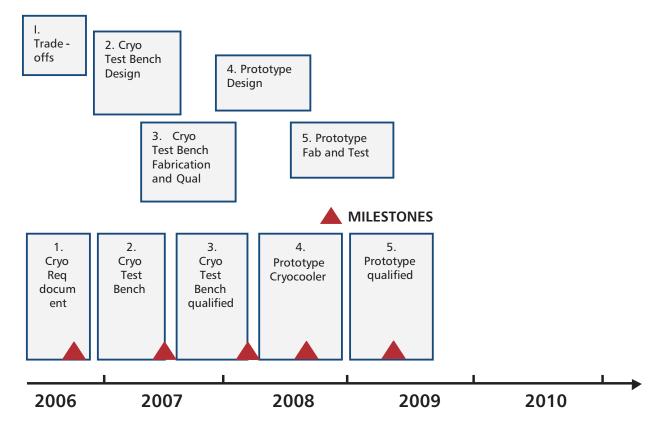

| 6.4   | Cooling                                             | 123 |

| 6.4.1 | Cooling – Status                                    | 124 |

| 6.4.2 | Cooling – Readiness                                 | 125 |

| 6.4.3 | Cooling – Issues and Concerns                       | 125 |

| 6.4.4 | Cooling – Roadmap and Funding                       | 126 |

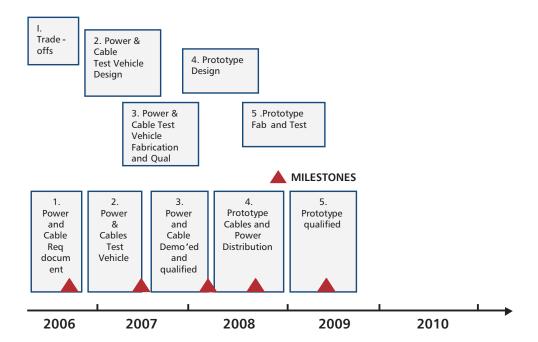

| 6.5   | Power Distribution and Cables                       | 127 |

| 6.5.1 | Power Distribution and Cables – Status              | 127 |

| 6.5.2 | Power Distribution and Cables – Readiness           | 129 |

| 6.5.3 | Power Distribution and Cables – Projections         | 129 |

| 6.5.4 | Power Distribution and Cables – Issues and Concerns | 129 |

| 6.5.5 | Power Distribution and Cables – Roadmap and Funding | 130 |

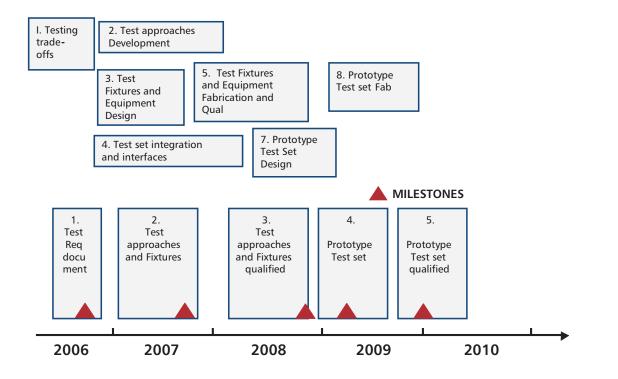

| 6.6   | System Integrity and Testing                        | 131 |

| 6.6.1 | System Integrity and Testing – Status               | 131 |

| 6.6.2 | System Integrity and Testing – Readiness            | 131 |

| 6.6.3 | System Integrity and Testing – Issues and Concerns  | 131 |

| 6.6.4 | System Integrity and Testing – Roadmap and Funding  | 132 |

| APPENDIX A: TERMS OF REFERENCE                                                             | 135 |

|--------------------------------------------------------------------------------------------|-----|

| APPENDIX B: PANEL MEMBERS                                                                  | 139 |

| APPENDIX C: GLOSSARY                                                                       | 143 |

| APPENDIX D: INTRODUCTION TO SUPERCONDUCTOR<br>SINGLE FLUX QUANTUM CIRCUITRY                | 147 |

| (The appendices below can be found on the attached CD but are not printed in this report.) |     |

| APPENDIX E: SOME APPLICATIONS FOR RSFQ                                                     | 155 |

| APPENDIX F: SYSTEM ARCHITECTURES                                                           | 161 |

| APPENDIX G: ISSUES AFFECTING RSFQ CIRCUITS                                                 | 169 |

| APPENDIX H: MRAM TECHNOLOGY FOR RSFQ HIGH-END COMPUTING                                    | 177 |

| APPENDIX I: SUPERCONDUCTOR INTEGRATED CIRCUIT<br>FABRICATION TECHNOLOGY                    | 185 |

| APPENDIX J: CAD                                                                            | 203 |

| APPENDIX K: DATA SIGNAL TRANSMISSION                                                       | 213 |

| APPENDIX L: MULTI-CHIP MODULES AND BOARDS                                                  | 227 |

# **INDEX OF FIGURES**

# **CHAPTER 01: INTRODUCTION**

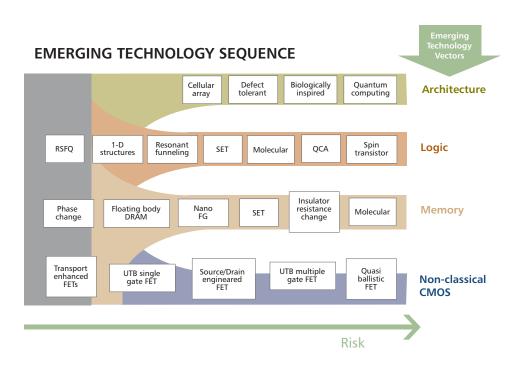

| 1-1 | 2004 ITRS update shows RSFQ as the lowest risk potential emerging technology for processing beyond silicon | 09 |

|-----|------------------------------------------------------------------------------------------------------------|----|

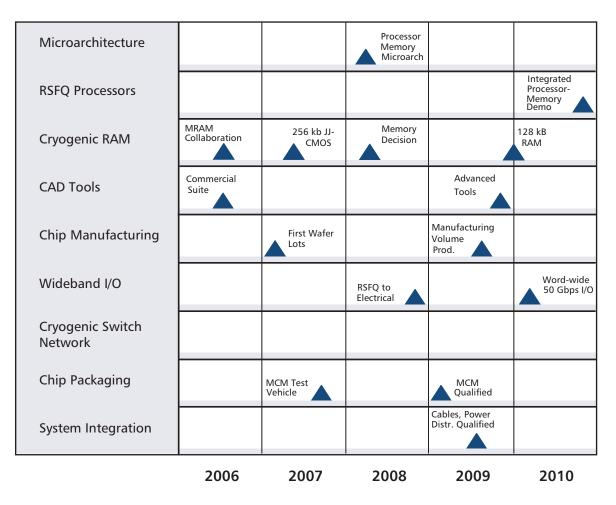

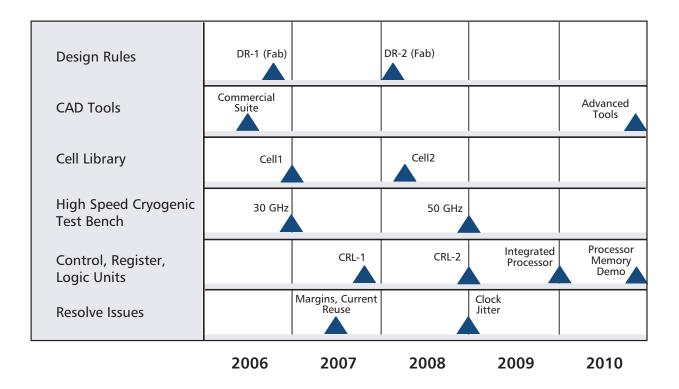

| 1-2 | Roadmap for RSFQ technology tools and components                                                           | 12 |

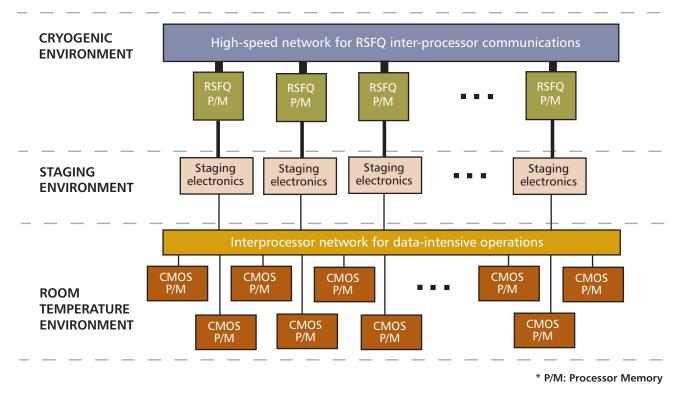

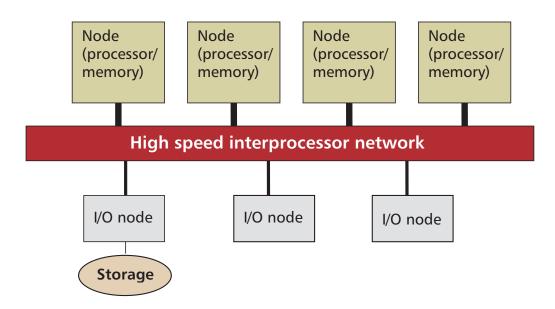

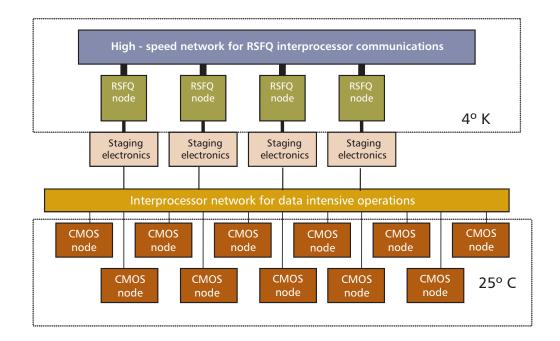

| 1-3 | Conceptual architecture                                                                                    | 14 |

# CHAPTER 02: ARCHITECTURAL CONSIDERATIONS FOR SUPERCONDUCTOR RSFQ MICROPROCESSORS

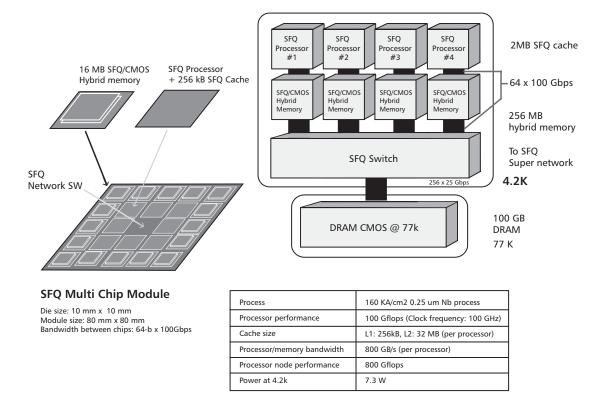

| 2-1 | 8-processor node of the proposed Japanese superconductor petaflops system | 31 |

|-----|---------------------------------------------------------------------------|----|

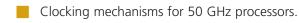

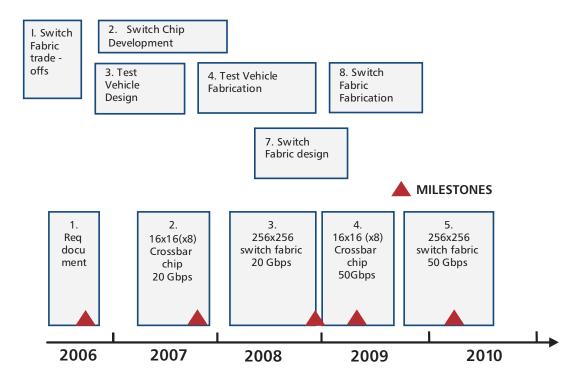

| 2-2 | 50-GHz multi-chip processor microprocessor design roadmap                 | 37 |

# CHAPTER 03: SUPERCONDUCTIVE RSFQ PROCESSOR AND MEMORY TECHNOLOGY

| 3.1-1 Roadmap and major milestones for RSFQ processors                                                   | 43 |

|----------------------------------------------------------------------------------------------------------|----|

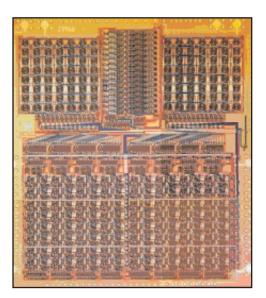

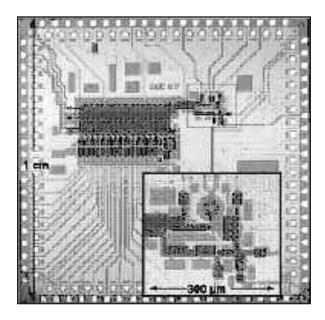

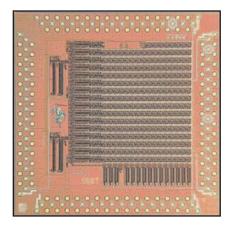

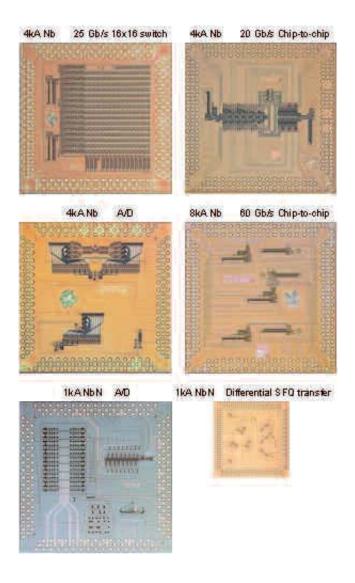

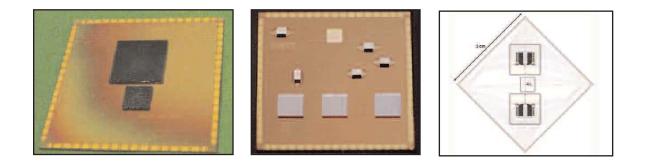

| 3.1-2 Photograph of 1-cm <sup>2</sup> Flux-1 63K JJ microprocessor chip                                  | 44 |

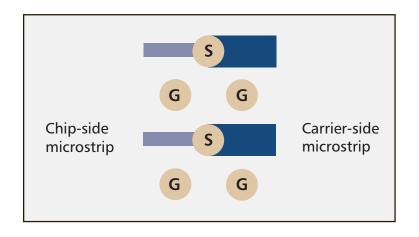

| 3.1-3 Signal and ground pad geometry used on Flux-1                                                      | 47 |

| 3.2-1 Hybrid Josephson-CMOS RAM operates at 4 K                                                          | 54 |

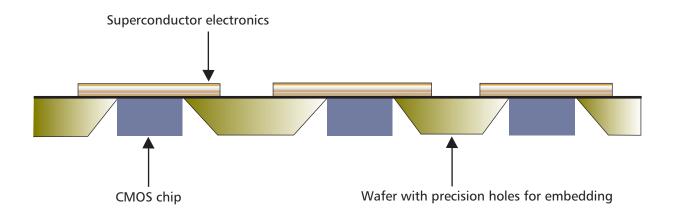

| 3.2-2 Wafer with embedded CMOS memory chips for direct wiring of Josephson peripheral circuits           | 55 |

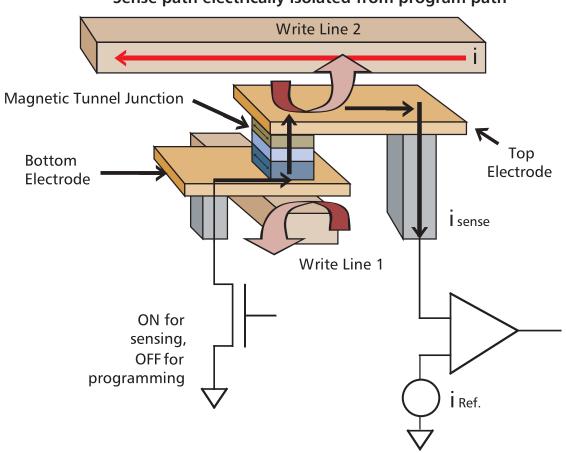

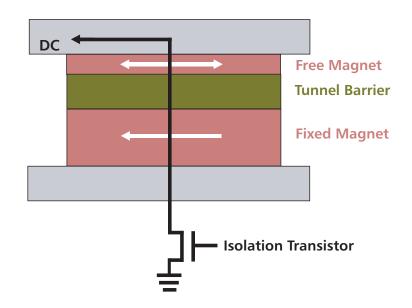

| 3.2-3 Diagram of FS-TMR cell                                                                             | 61 |

| 3.2-4 Cryogenic RAM roadmap                                                                              | 66 |

| 3.3-1 ADC chip containing about 6,000 JJs                                                                | 68 |

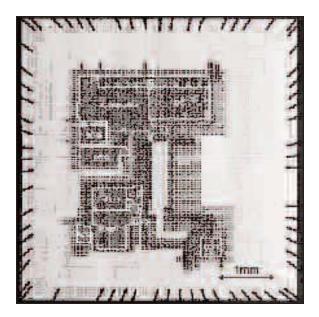

| 3.3-2 A bit-serial superconductor microprocessor featuring 6,300 JJs, 7 instructions, and a 16 GHz clock | 68 |

# **CHAPTER 04: SUPERCONDUCTIVE CHIP MANUFACTURE**

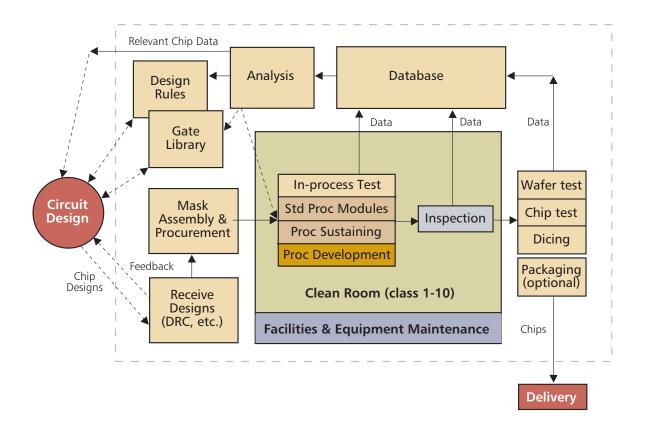

| 4-1        | Schematic diagram of functions included in IC chip manufacture                                                                                                                                   | 78       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

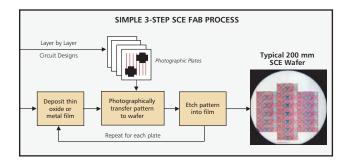

| 4-2        | Fabrication of RSFQ ICs is accomplished using semiconductor equipment and processes                                                                                                              | 79       |

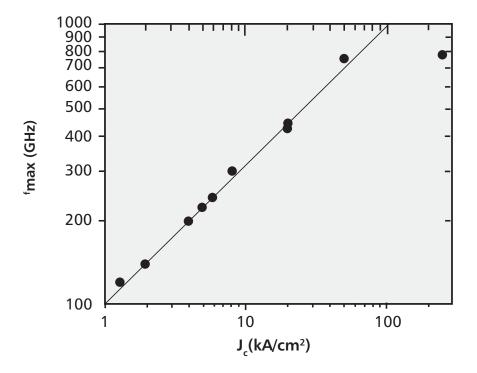

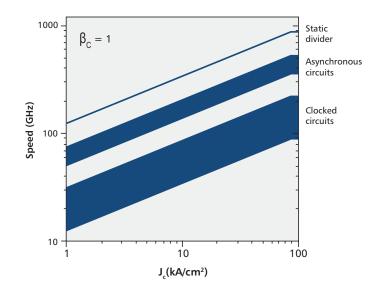

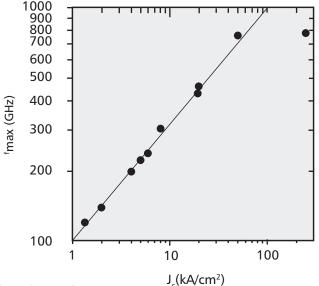

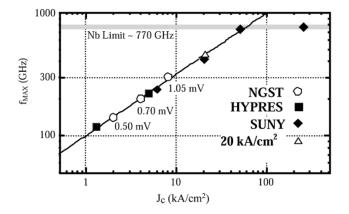

| 4-3        | Demonstrations of RSFQ circuit speed with increasing Jc                                                                                                                                          | 80       |

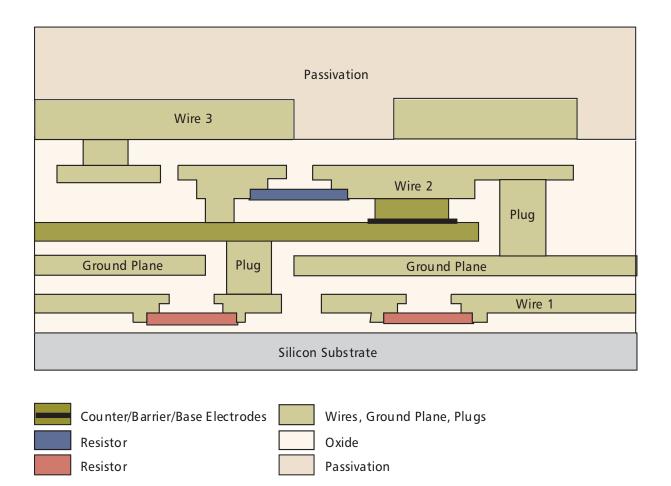

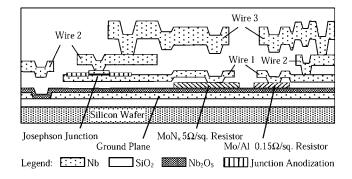

| 4-4        | Notional cross-section of the superconductive IC chip fabrication process illustrating salient features of an advanced process which includes four interconnect levels, planarization, and plugs | 85       |

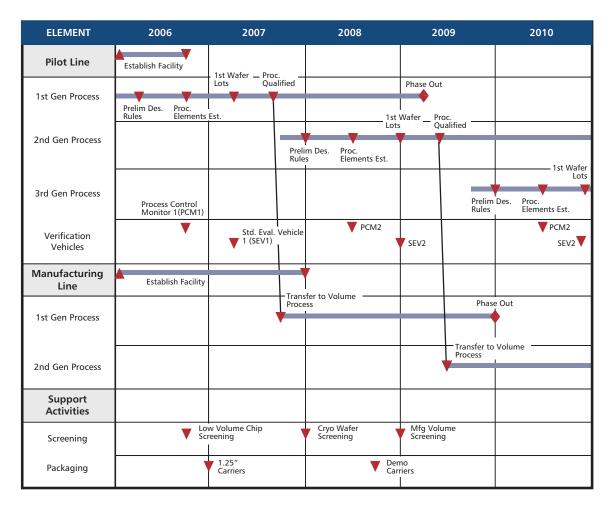

| 4-5<br>4-6 | Projections of RSFQ circuit speeds with increasing Jc<br>Timeline for development of SCE manufacturing capability                                                                                | 87<br>92 |

# CHAPTER 05: INTERCONNECTS AND SYSTEM INPUT/OUTPUT

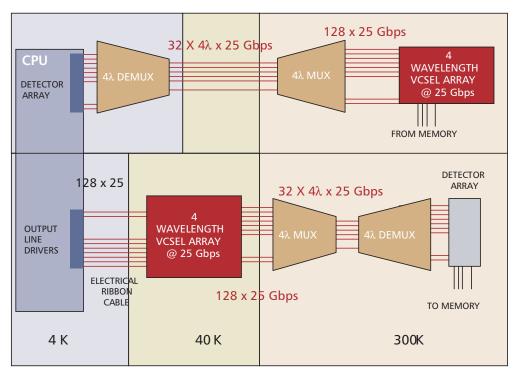

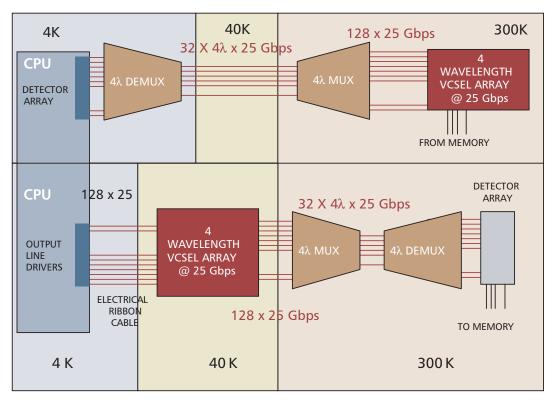

| 5-1 | A 64-fiber, 4-wavelength, 25-Gbps CWDM System for bi-directional transmission totaling 6.4 Tbps between a superconducting processor at 4 K and high speed mass memory at 300 K | 100 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

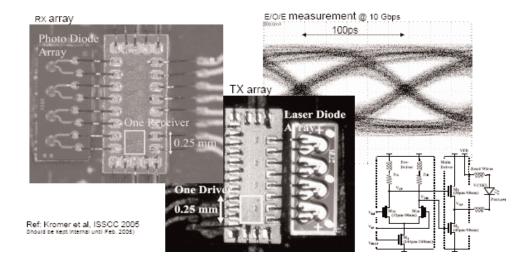

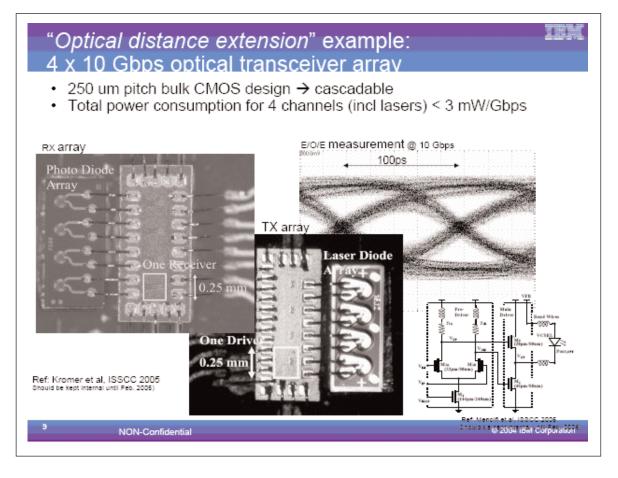

| 5-2 | Four channel transceiver arrays operating at 10 Gbps/channel produced by IBM/Agilent                                                                                           | 101 |

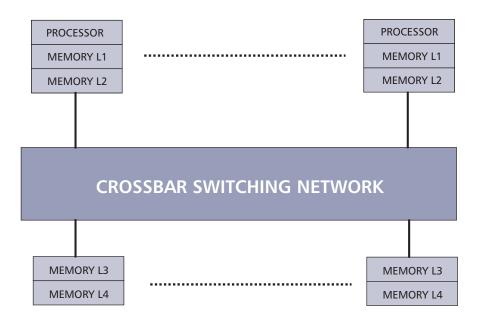

| 5-3 | The use of crossbar switching in supercomputers                                                                                                                                | 109 |

| 5-4 | Superconducting 16x16 crossbar switch with 14,000 junctions on a 5x5 mm chip                                                                                                   | 110 |

# **CHAPTER 06: SYSTEM INTEGRATION**

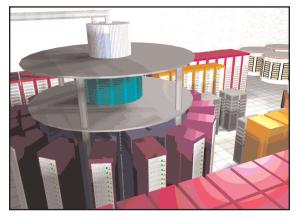

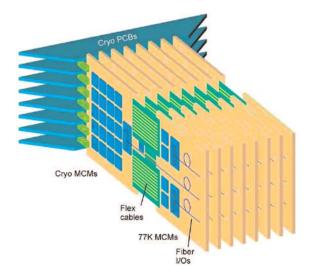

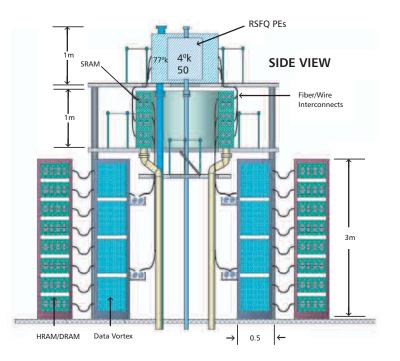

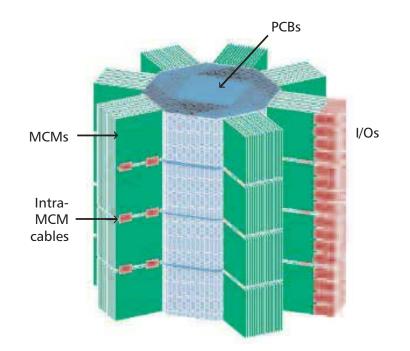

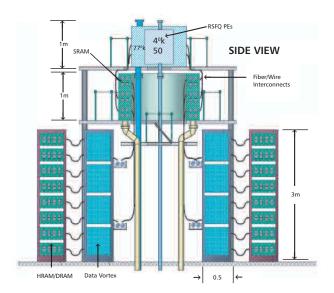

| 6-1a | System installation concept for petaflops HTMT system                                | 113 |

|------|--------------------------------------------------------------------------------------|-----|

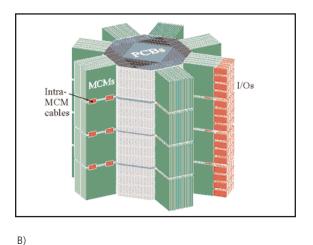

| 6-1b | Packaging concept for HTMT SCP                                                       | 113 |

| 6-2  | HTMT conceptual packaging for cryogenic processing and data communications           | 114 |

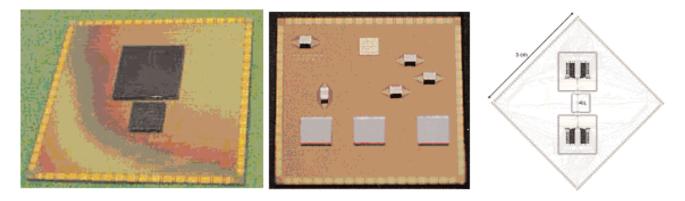

| 6-3  | Multi-chip module with SCE chips                                                     | 115 |

| 6-4  | Categorization of 3D packaging approaches                                            | 119 |

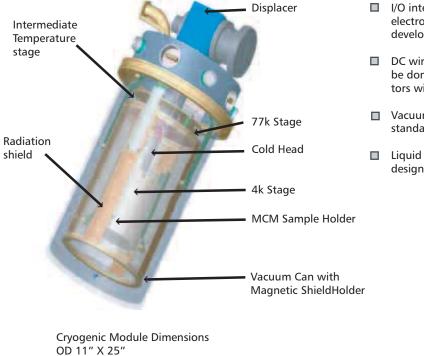

| 6-5  | Construction details of a typical enclosure designed for operation at 4 K            | 121 |

| 6-6  | Concept for a large-scale system including cryogenic cooling unit for supercomputers | 125 |

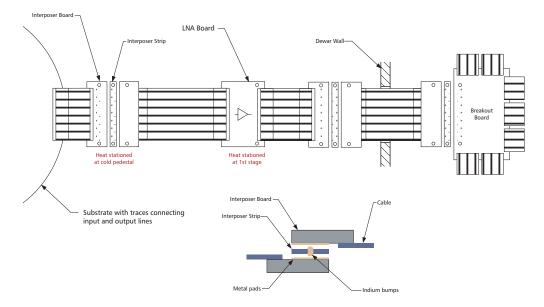

| 6-7  | High-speed flexible ribbon cable designed for modular attachment                     | 128 |

| APPENDIX A: TERMS OF REFERENCE | (none) |

|--------------------------------|--------|

| APPENDIX B: PANEL MEMBERS      | (none) |

| APPENDIX C: GLOSSARY           | (none) |

# APPENDIX D: INTRODUCTION TO SUPERCONDUCTOR SINGLE FLUX QUANTUM CIRCUITRY

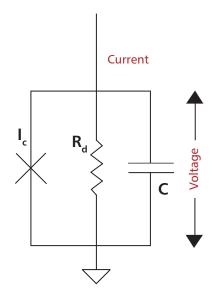

| Figure 1: Equivalent circuit of Josephson junction. I <sub>C</sub> represents the nonlinear switch | 147 |

|----------------------------------------------------------------------------------------------------|-----|

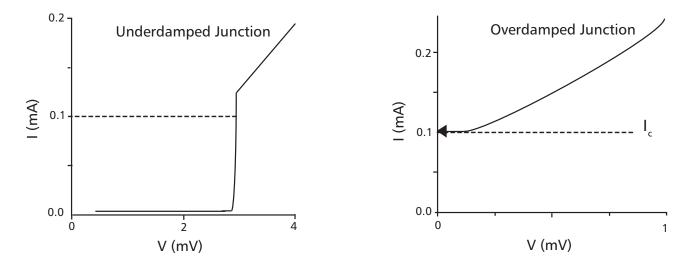

| Figure 2a: DC electrical characteristics of voltage-state latching junctions                       | 148 |

| Figure 2b: DC electrical characteristics of SFQ non-latching junctions                             | 148 |

| Figure 3: Measured speed of static dividers varies as $J_{C}^{1/2}$                                | 149 |

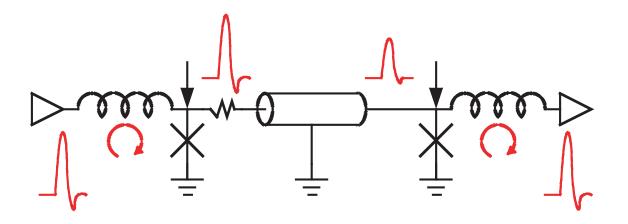

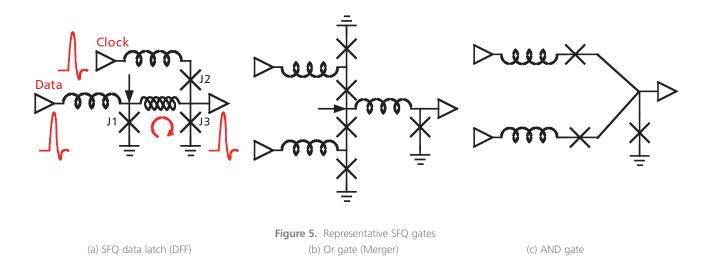

| Figure 4: Passive transmission lines can propagate picosecond SFQ pulses without dispersion        | 150 |

| at the speed of light in the line                                                                  |     |

| Figure 5: Representative SFQ gates                                                                 | 151 |

(The appendices below can be found on the attached CD but are not printed in this report.)

| APPENDIX E: SOME APPLICATIONS FOR RSFQ | (none) |

|----------------------------------------|--------|

| APPENDIX F: SYSTEM ARCHITECTURES       | (none) |

# **APPENDIX G: ISSUES AFFECTING RSFQ CIRCUITS**

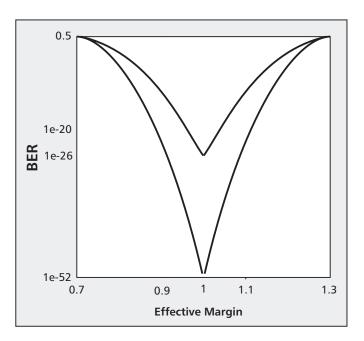

| Figure 1: Calculated BER of a 2-JJ comparator as a function of operating margin | 169 |

|---------------------------------------------------------------------------------|-----|

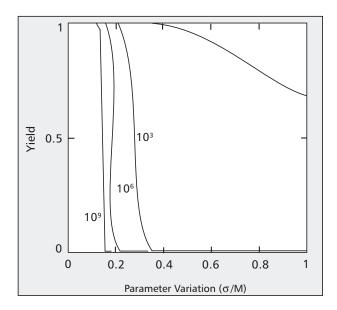

| Figure 2: Yield as a function of process variations                             | 171 |

# APPENDIX H: MRAM TECHNOLOGY FOR RSFQ HIGH-END COMPUTING

| Figure 1: Schematic of a 1T-1MTJ MRAM cell structure showing the sense path and programming lines                            | 177 |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Schematic of a proposed SMT MRAM cell structure showing the common current path for sense and program operations   | 178 |

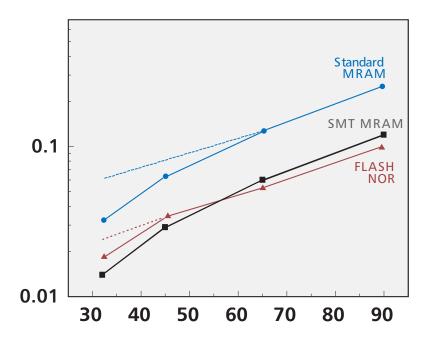

| Figure 3: Estimated cell sizes for the two MRAM technologies compared to NOR Flash for IC technology nodes from 90nm to 32nm | 179 |

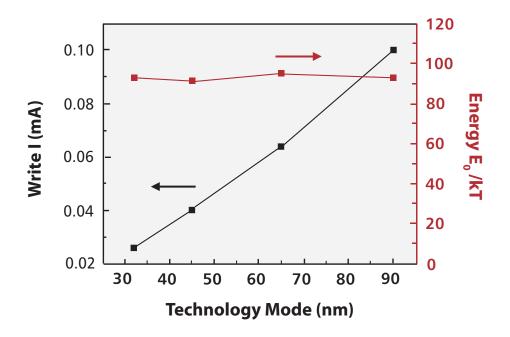

| Figure 4: Estimated switching currents for SMT devices at various lithography nodes                                          | 182 |

# APPENDIX I: SUPERCONDUCTOR INTEGRATED CIRCUIT FABRICATION TECHNOLOGY

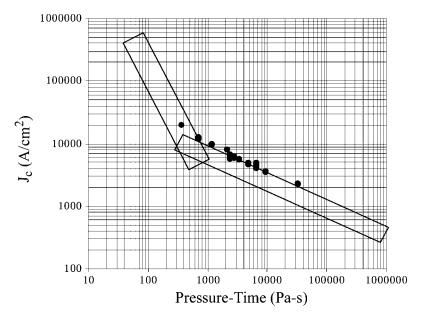

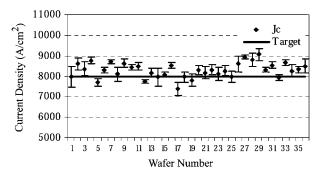

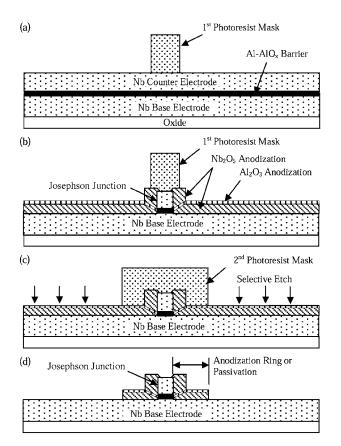

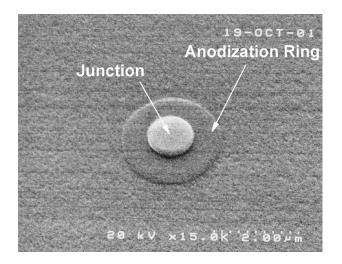

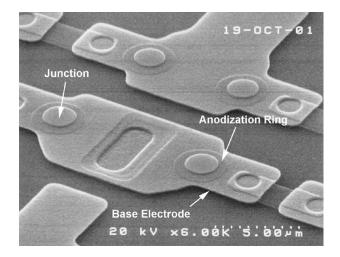

| Figure 1: Cross section of NGST's 8-kA/cm <sup>2</sup> niobium-based 14-mask step integrated circuit process<br>Figure 2: Current density versus oxidation pressure-time product for Jc of 2-20 kA/cm <sup>2</sup><br>Figure 3: Trend chart of current density<br>Figure 4: Junction fabrication process showing key features<br>Figure 5: SEM photograph of a 1.0 µm junction and self-aligned anodization ring on base electrode<br>Figure 6: SEM photograph of a partially completed T-flip flop stage showing junction,<br>anodization ring and base electrode | 1519<br>1521<br>1521<br>1522<br>1523<br>1523 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

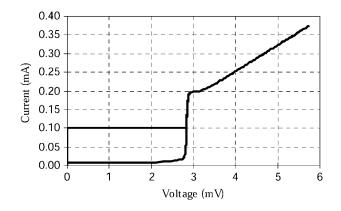

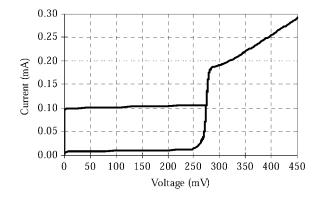

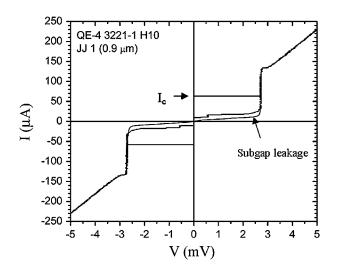

| Figure 7: Typical current-voltage characteristics of a 8-kA/cm <sup>2</sup> 1.25-µm diameter junction<br>Figure 8: Typical current-voltage characteristics of a series array of<br>one hundred 8-kA/cm <sup>2</sup> 1.25-µm diameter junctions                                                                                                                                                                                                                                                                                                                     | 1523<br>1523                                 |

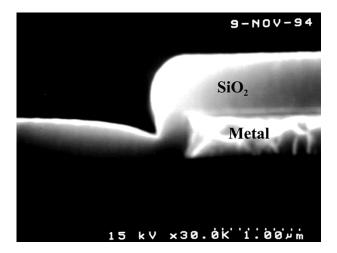

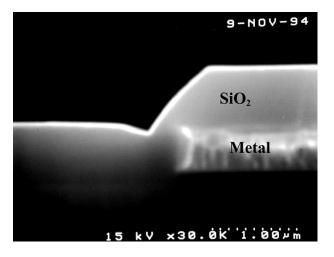

| Figure 9: SEM photograph showing the reentrant step coverage of sputter-deposited SiO <sup>2</sup> over a 500-nm metal step                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1524                                         |

| Figure 10: SEM photograph showing the improvement in step coverage of SiO <sup>2</sup> over a 500-nm metal step with substrate bias applied during deposition                                                                                                                                                                                                                                                                                                                                                                                                      | 1525                                         |

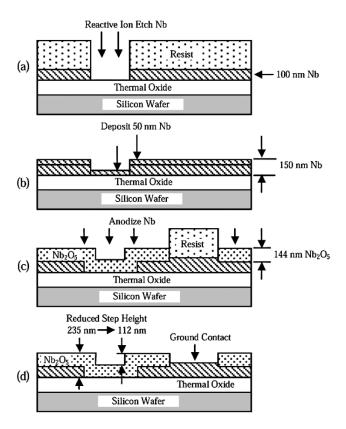

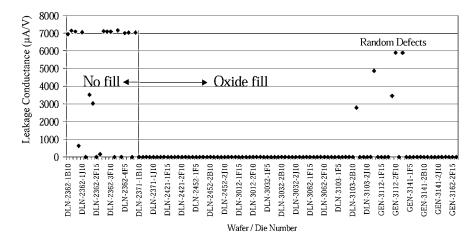

| Figure 11: Ground plane planarization process<br>Figure 12: Trend chart of leakage conductance for comb-to-meander structure showing<br>that oxide fill eliminates shorts between adjacent comb-to-meander wires over ground<br>etch meander in PCM test structure                                                                                                                                                                                                                                                                                                 | 1526<br>1527                                 |

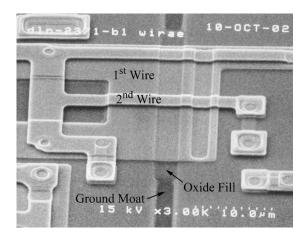

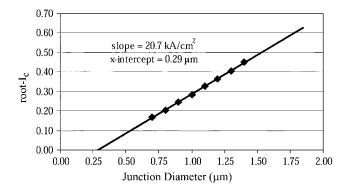

| Figure 13: SEM picture of first and second wiring layers crossing ground moat filled with oxide<br>Figure 14: Maximum reported TRFF divider speed<br>Figure 15: Typical current-voltage characteristics of a 20-kA/cm <sup>2</sup> , 0.90-µm junction<br>Figure 16: Plot and linear fit of the square-root-lc versus drawn junction diameter for a series<br>of 20-kA/cm <sup>2</sup> junctions ranging in diameter                                                                                                                                                | 1527<br>1528<br>1529<br>1529                 |

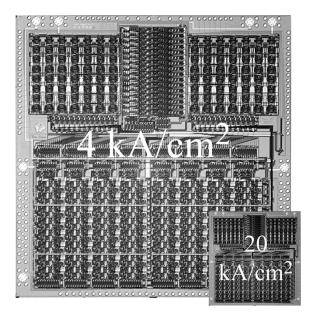

| Figure 17: Photograph of the FLUX-1r1 microprocessor chip fabricated in NGST's 4-kA/cm <sup>2</sup> process                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1530                                         |

# **APPENDIX J: CAD**

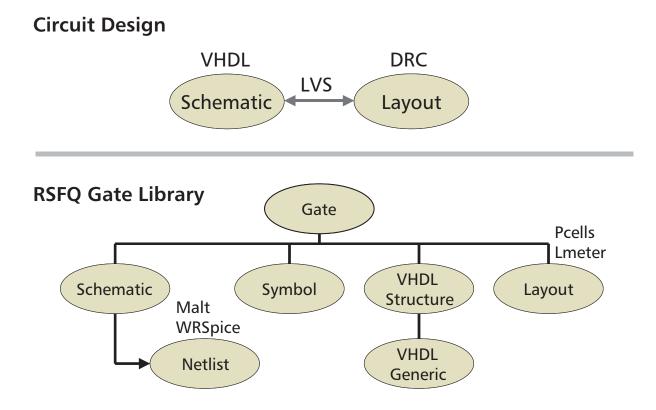

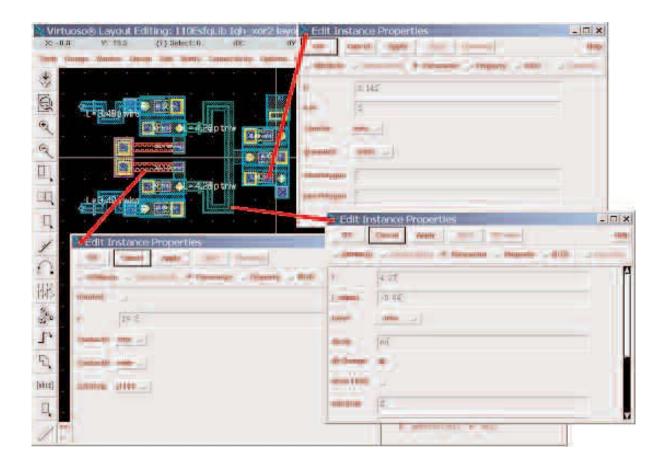

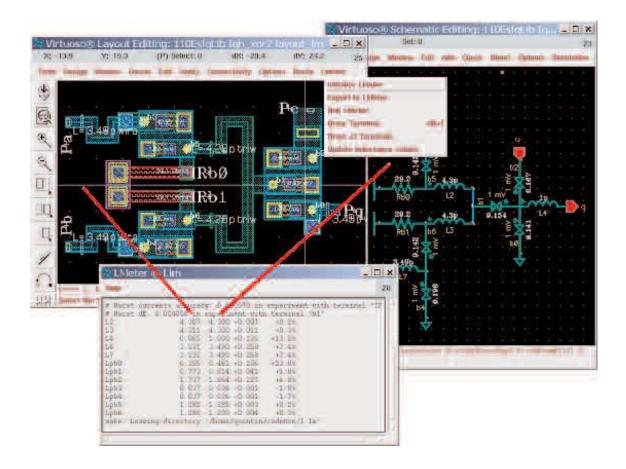

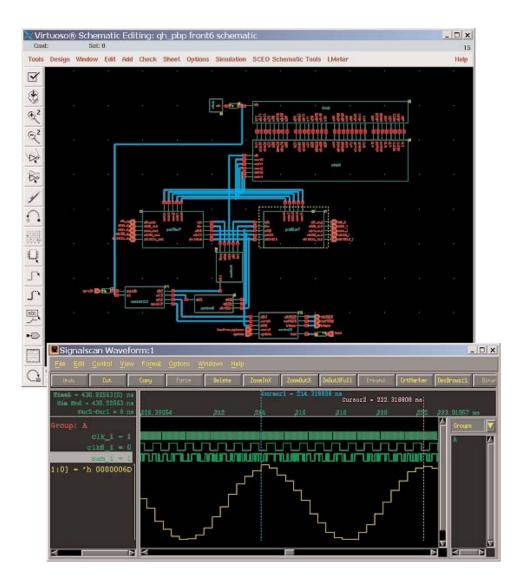

| Figure 1: Circuit design and verification                                           | 203 |

|-------------------------------------------------------------------------------------|-----|

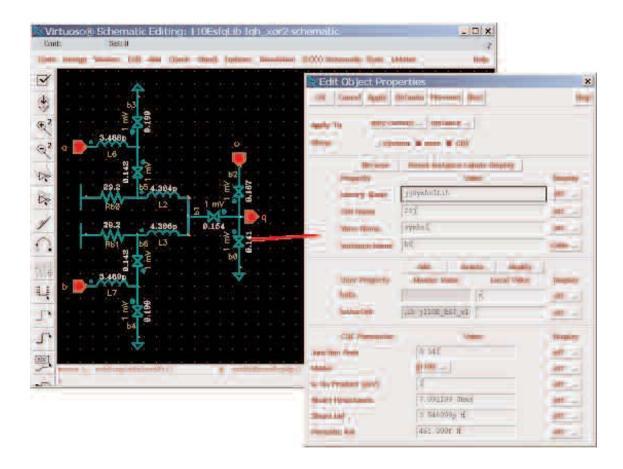

| Figure 2: Schematic view                                                            | 204 |

| Figure 3: Symbol view                                                               | 205 |

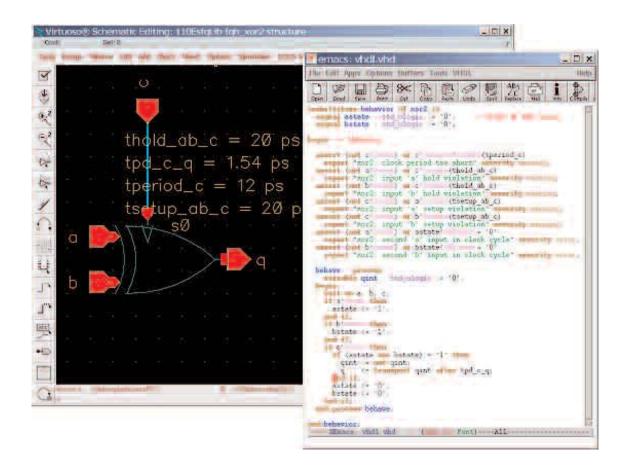

| Figure 4: VHDL view                                                                 | 206 |

| Figure 5: Physical layout view                                                      | 207 |

| Figure 6: LMeter is specialized software that extracts the inductance value         | 208 |

| of an interconnect from the physical layout                                         |     |

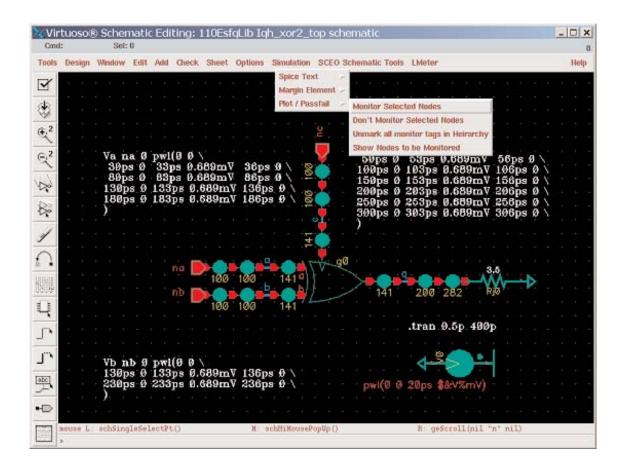

| Figure 7: VHDL simulation performed on a large, mixed signal superconductor circuit | 209 |

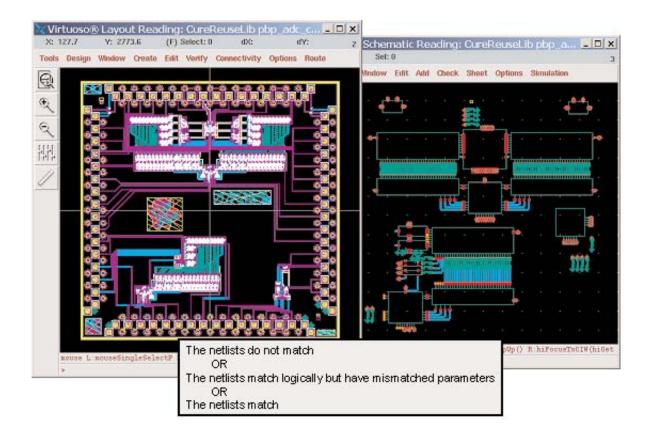

| Figure 8: Layout-versus-Schematic verification on the chip level for a large chip   | 210 |

| Figure 9: First-pass success is routine for circuits of up to a few thousand JJs    | 211 |

# **APPENDIX K: DATA SIGNAL TRANSMISSION**

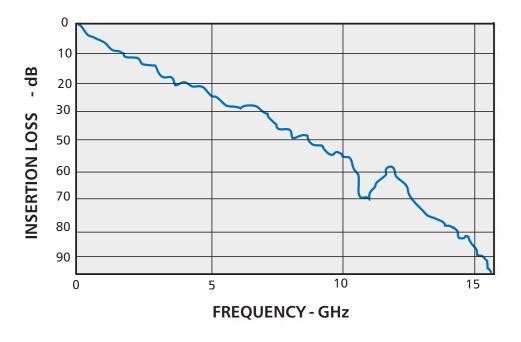

| Figure 1: Channel loss for 50 cm electrical link                                                                                                                                       | 214 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Long path data signal transmission requirements for one proposes petaflop architecture                                                                                       | 215 |

| Figure 3: Four channel transceiver arrays produced by the IBM/Agilent effort funded by DARPA                                                                                           | 216 |

| Figure 4: A 64-fiber, 4-wavelength, 25-Gbps CWDM system for bidirectional transmission totaling 6.4 Tbps between a superconductive processor at 4 K and high speed mass memory at 300K | 220 |

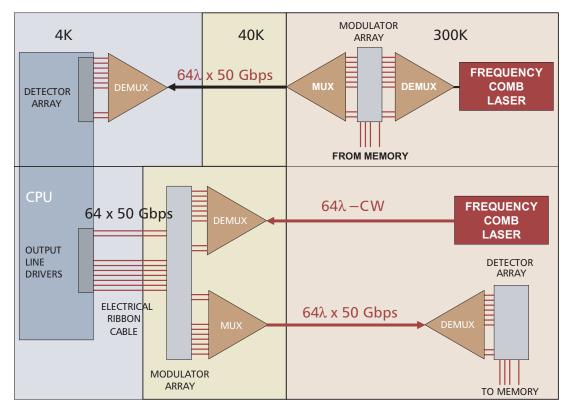

| Figure 5: A 3-fiber, 64-wavelength, 50-Gbps DWDM system for bidirectional transmission totaling 6.4 Tbps between a superconductive processor at 4 K and high speed mass memory at 300K | 221 |

# APPENDIX L: MULTI-CHIP MODULES AND BOARDS

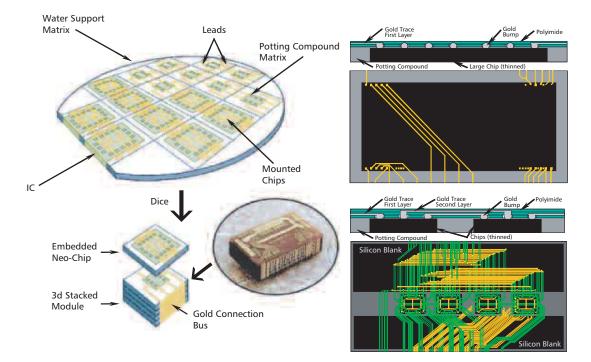

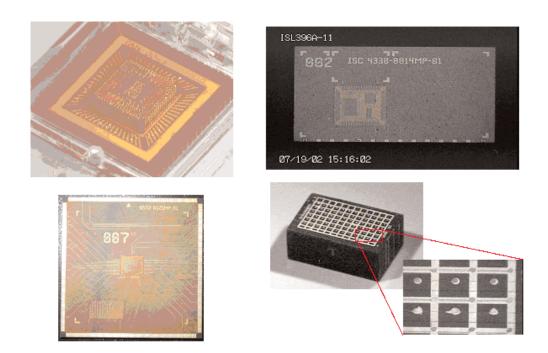

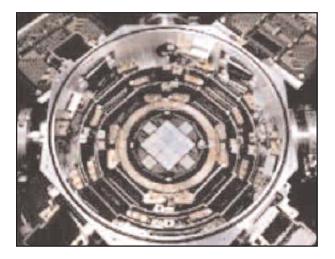

| Figure 1: Packaging concept for HTMT SCP<br>Figure 2: A multi-chip module with SCE chips<br>Figure 3: Lead inductance vs. bond length or height for different attach techniques<br>Figure 4: Heterogeneous stacking technology for system-in-stack<br>Figure 5: Stacks containing superconducting electronics circuits were cycled<br>from RT to 4 K several times                                                                           | 227<br>228<br>229<br>232<br>232        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

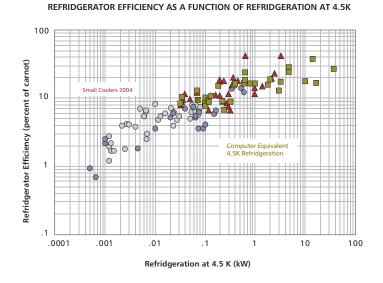

| Figure 6: A prototype cryo enclosure for operation at 4 K<br>Figure 7: A typical cryocooler enclosure designed for communication applications<br>Figure 8: A rack mounted cryocooler enclosure example<br>Figure 8: Northrop Grumman's high-efficiency cryocooler unit<br>Figure 9: Refrigerator efficiency of various cooling systems<br>Figure 10: Concept for a large-scale system including cryogenic<br>cooling unit for supercomputers | 233<br>234<br>234<br>236<br>237<br>237 |

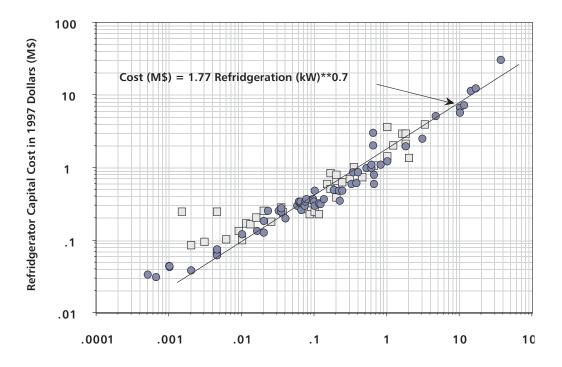

| Figure 11: The cost of various refrigerators as a function of refrigeration<br>Figure 12: A high-speed flexible ribbon cable designed for modular attachment                                                                                                                                                                                                                                                                                 | 239<br>240                             |

# **CONTENTS OF CD**

EXECUTIVE SUMMARY

CHAPTER 01: INTRODUCTION CHAPTER 02: ARCHITECTURAL CONSIDERATIONS FOR SUPERCONDUCTOR RSFQ MICROPROCESSORS CHAPTER 03: SUPERCONDUCTIVE RSFQ PROCESSOR AND MEMORY TECHNOLOGY CHAPTER 04: SUPERCONDUCTIVE CHIP MANUFACTURE CHAPTER 05: INTERCONNECTS AND SYSTEM INPUT/OUTPUT CHAPTER 06: SYSTEM INTEGRATION

APPENDIX A: TERMS OF REFERENCE APPENDIX B: PANEL MEMBERS APPENDIX C: GLOSSARY APPENDIX D: INTRODUCTION TO SUPERCONDUCTOR SINGLE FLUX QUANTUM CIRCUITRY APPENDIX E: SOME APPLICATIONS FOR RSFQ APPENDIX F: SYSTEM ARCHITECTURES APPENDIX G: ISSUES AFFECTING RSFQ CIRCUITS APPENDIX H: MRAM TECHNOLOGY FOR RSFQ HIGH-END COMPUTING APPENDIX I: SUPERCONDUCTOR INTEGRATED CIRCUIT FABRICATION TECHNOLOGY APPENDIX J: CAD APPENDIX K: DATA SIGNAL TRANSMISSION APPENDIX L: MULTI-CHIP MODULES AND BOARDS

All financial figures throughout the report are listed in millions of dollars (\$M); all financial figures in chapter summaries are rounded to the nearest million.

# **EXECUTIVE SUMMARY**

# **ASSESSMENT OBJECTIVE AND FINDINGS**

The government, and particularly NSA, has a continuing need for ever-increasing computational power. The Agency is concerned about projected limitations of conventional silicon-based technology and is searching for possible alternatives to meet its future mission-critical computational needs.

This document presents the results of a Technology Assessment, chartered by the Director of NSA, to assess the readiness of ultra-high-speed superconductive (SC) Rapid Single Flux Quantum (RSFQ) circuit technology for application to very-high-performance (petaflops-scale) computing systems. A panel of experts performed this assessment and concluded that:

- RSFQ technology is an excellent candidate for petaflops-scale computers.

- Government investment is necessary, because private industry currently has no compelling financial reason to develop this technology for mainstream commercial applications.

- With aggressive federal investment (estimated between \$372 and \$437 million over five years), by 2010 RSFQ technology can be sufficiently matured to allow the initiation of the design and construction of an operational petaflops-scale system.

- Although significant risk issues exist, the panel has developed a roadmap that identifies the needed technology developments with milestones and demonstration vehicles.

| TABLE E-1. REASONS TO DEVELOP SUPERCONDUCTIVE COMPUTER TECHNOLOGY                      |                                                                                |  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Technological                                                                          | Financial                                                                      |  |

| NSA's computing needs are outstripping conventional technology.                        | Market forces alone will not drive private industry to develop SC technology.  |  |

| RSFQ technology is an excellent candidate for higher-performance computing capability. | The federal government will be the primary end user of SC computer technology. |  |

| RSFQ technology has a clear<br>and viable roadmap.                                     | Other federal government missions will benefit from advances in SC technology. |  |

# LIMITATIONS OF CURRENT TECHNOLOGY

#### **Circuit Speeds Facing Limits**

The government is observing increased difficulty as industry attempts to raise the processing performance of today's silicon-based supercomputer systems through improvements in circuit speeds. In the past several decades, steady decreases in circuit feature sizes have translated into faster speeds and higher circuit densities that have enabled ever-increasing performance. However, conventional technology has a limited remaining lifetime and is facing increasing challenges in material science and power dissipation at smaller feature sizes.

There are already signs that the major commodity device industry is turning in other directions. The major microprocessor companies are backing away from faster clock speeds and instead are fielding devices with multiple processor "cores" on a single chip, with increased performance coming from architectural enhancements and device parallelism rather than increased clock speed.

While the Semiconductor Industry Association (SIA) International Technology Roadmap for Semiconductors (ITRS) projects silicon advances well into the next decade, large-scale digital processing improvements will almost certainly come from increased parallelism, not raw speed.

#### Commercial and Government Interests Diverging

Over the past two decades, High-End Computing (HEC) systems have improved by leveraging a large commodity microprocessor and consumer electronics base. However, future evolution of this base is projected to diverge from the technology needs of HEC for national security applications by supporting more processors rather than faster ones. The result will be limitations in architecture and programmability, for implementations of HEC based on the traditional commodity technology base.

#### Power Requirements Swelling

For supercomputers, continuing reliance on this technology base means a continuation of the trend to massively parallel systems with thousands of processors. However, at today's scale, the electrical power and cooling requirements are bumping up against practical limits, even if ways were found to efficiently exploit the parallelism. For example, the Japanese Earth Simulator system, which has been ranked number one on the list of the top 500 installed HEC, consumes approximately 6 megawatts of electrical power.

#### **PANEL TASKED**

A panel of experts from industry and academia, augmented by Agency subject matter experts, was assembled to perform this study, bringing expertise from superconducting materials, circuitry, fabrication, high-performance computer architecture, optical communications, and other related technologies. The panel:

- Assessed RSFQ technology for application to high-performance computing systems available after 2010, based on current projections of material science, device technology, circuit design, manufacturability, and expected commercial availability of superconductive (SC) technology over the balance of the decade.

- Identified roadmaps for the development of the essential components, including microprocessor circuits, memory, and interconnect, for high-end computer architectures by 2010.

# **RSFQ TECHNOLOGY IS VIABLE**

| TABLE E-2. RSFQ SUMMARY                   |                                                                                                   |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| Technical Advantages                      | Technical Challenges                                                                              |  |

| The most advanced alternative technology. | Providing high-speed and low-latency memory.                                                      |  |

| Combines high speed with low power.       | Architecting systems that can tolerate significant memory access latencies.                       |  |

| Ready for aggressive investment.          | Providing very high data rate communications between room temperature technology and cooled RSFQ. |  |

#### Most Advanced Alternative Technology

The ITRS 2004 update on Emerging Research Devices lists many candidate technologies, presently in the research laboratories, for extending performance beyond today's semiconductor technology. Superconducting RSFQ is included in this list and is assessed to be at the most advanced state of any of the alternative technologies.

#### Ready for Aggressive Investment

In the opinion of the panel, superconducting RSFQ circuit technology is ready for an aggressive, focused investment to meet a 2010 schedule for initiating the development of a petaflops-class computer. This judgment is based on:

- An evaluation of progress made in the last decade.

- Projection of the benefits of an advanced very-large-scale integration (VLSI) process for RSFQ in a manufacturing environment.

- A roadmap for RSFQ circuit development coordinated with VLSI manufacturing and packaging technologies.

#### Can Leverage Semiconductor Technology Base

Although RSFQ circuits are still relatively immature, their similarity in function, design, and fabrication to semiconductor circuits permits realistic extrapolations. Most of the tools for design, test, and fabrication are derived directly from the semiconductor industry, although RSFQ technology will still need to modify them. Significant progress has already been demonstrated on limited budgets by companies such as Northrop Grumman and HYPRES, and in universities such as Stony Brook and the University of California, Berkeley.

#### High Speed with Low Power

Individual RSFQ circuits have been demonstrated operating at clock rates in the hundreds of GHz, and system clocks of at least 50GHz seem quite attainable, with faster speeds possible. In addition, RSFQ devices have lower power requirements than other systems, even after cooling requirements are included. Extremely low RSFQ power enables compact systems with greatly increased computational capability for future government needs, but with no increase in overall power requirements beyond today's high-end systems.

#### State of the Industry

Today, expertise in digital SC technology resides in only a handful of companies and institutes. The U.S. base is shrinking:

| TABLE E-3. DIGITAL RSFQ TECHNOLOGY'S CURRENT STATE OF THE INDUSTRY |                                    |                                                                                                                                                                                                   |

|--------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Country                                                            | Entity                             | Status                                                                                                                                                                                            |

|                                                                    | ISTEC/SRL                          | <ul> <li>Joint government/industry center, probably doing the most<br/>advanced work in digital RSFQ anywhere in the world today.</li> <li>Responsible for the Earth Simulator system.</li> </ul> |

|                                                                    | HYPRES                             | <ul> <li>Private company focused entirely on SC digital electronics.</li> <li>Has operated the only full-service commercial foundry<br/>in the U.S. since 1983.</li> </ul>                        |

|                                                                    | Northrop<br>Grumman                | <ul> <li>Had the most advanced foundry and associated design capability until suspended last year.</li> <li>Still has a strong cadre of experts in the field.</li> </ul>                          |

|                                                                    | Stony Brook U,<br>UC Berkeley, JPL | <ul> <li>Currently conducting academic research.</li> </ul>                                                                                                                                       |

|                                                                    | Chalmers U<br>of Technology        | <ul> <li>Currently conducting academic research.</li> </ul>                                                                                                                                       |

|                                                                    | NSA, NIST                          | – Have resident expertise.                                                                                                                                                                        |

#### **ROADMAP CREATED**

This report presents a detailed RSFQ technology roadmap, defining the tools and components essential to support RSFQ-based high-end computing by 2010. The end point of this roadmap includes:

- An RSFQ processor of approximately 1-million gate complexity, operating at a 50 GHz clock rate.

- A design capability:

- consisting of an RSFQ cell library and a complete suite of computer-aided design (CAD) tools.

- allowing a competent ASIC digital designer with no background in superconductor electronics to design high-performance processor units.

- An RSFQ chip manufacturing facility with an established stable process operating at high yields.

## **GOVERNMENT INVESTMENT CRUCIAL**

There is no foreseeable commercial demand for SC digital technology products sufficient to justify significant private industry investment in developing that technology. For this reason, government funding is crucial to this technology's development. Besides its use to NSA, SC will likely have applications for other government missions as well. Once it has been sufficiently developed, SC may also prove to have commercial applications.

While the panel finds RSFQ technology very promising as a base for future HEC systems, this technology will still require significant developmental effort and an investment of between \$372 and \$437 million over five years in order to be ready for design and construction of operational systems.

## **TECHNICAL ISSUES**

Many technical problems remain to be solved on the path to maturing RSFQ technology. This report presents sequences of experiments and developmental steps that would address the major issues critical to the success of this effort. Those issues, which must be addressed aggressively by any developmental program, are:

- Providing high-speed/low-latency memory.

- Architecting systems that can tolerate significant memory access latencies.

- Providing very-high-data-rate communications into and (particularly) out of the cryogenic environment.

Other technical issues—considered to be reasonably low risk, although still in need of development work—include:

- Providing powerful CAD tools for the designers.

- Achieving a stable fabrication process.

- Refrigeration.

#### **CONCLUSIONS**

RSFQ technology is ready for a major development program culminating in demonstration vehicles that will open the door to operational systems. This can be accomplished in five years with an aggressive, government funded program. Without such government investment, this development will not happen.

# 01

This document presents the results of a Technology Assessment, chartered by the Director of NSA, to assess the readiness of an ultra-high-speed circuit technology, superconductive Rapid Single Flux Quantum (RSFQ), for use in very-high-performance (petaflops-scale) computing systems.

# **INTRODUCTION**

The request for this assessment was motivated by the government's assessment that conventional technology for high-end computing (HEC) systems is finding it more and more difficult to achieve further increases in computational performance. A panel of experts in superconductive electronics, high-performance computer architectures, and related technologies was formed to conduct this study. The composition of the panel is presented in Appendix B.

In summary, the charge to the panel was to:

"...conduct an assessment of superconducting technology as a significant follow-on to silicon for component use in high performance computing systems available after 2010. The assessment will examine current projections of material science, device technology, circuit design, manufacturability, and general commercial availability of superconducting technology over the balance of the decade, identify programs in place or needed to advance commercialization of superconducting technology if warranted by technology projections, and identify strategic partnerships essential to the foregoing. First order estimates of the cost and complexity of government intervention in technology evolution will be needed. The assessment will not directly investigate potential high-end computer architectures or related non-superconducting technologies required by high-end computers other than those elements essential to the superconducting technology projections."

The full text of the formal charge to the panel is given in Appendix A.

# **1.1 NSA DEPENDENT ON HIGH-END COMPUTING**

The NSA mission is dependent on HEC for cryptanalysis, natural language processing, feature recognition from image analysis, and other intelligence processing applications. NSA applications touch the extremes of supercomputing resource use: numerically intensive computation, high-volume data storage, and high bandwidth access to external data. As the use of electronic communications increases, so too does the volume of data to be processed and the sophistication of encryption mechanisms; thus, the need for HEC escalates.

NSA's mission is dependent on high-end computing; its applications touch the extremes of supercomputing resource use:

- Numerically intensive computation.

– High-volume data storage.

- High-bandwidth access to external data.

For the past two decades, HEC systems have evolved by leveraging a large commodity microprocessor and consumer electronics base. However, there is now increased concern about the divergence of this base and the government's HEC technology needs. There are many other potential government and private sector applications of HEC. Some of these are discussed in Appendix E: Some Applications for RSFQ. (The full text of this appendix can be found on the CD accompanying this report.)

## **1.2 LIMITATIONS OF CONVENTIONAL TECHNOLOGY FOR HIGH-END COMPUTING**

In 1999, the President's Information Technology Advisory Committee (PITAC) wrote the following in its Report to the President-Information Technology Research: Investing in Our Future (Feb 1999): "...Ultimately, silicon chip technology will run up against the laws of physics. We do not know exactly when this will happen, but as devices approach the size of molecules, scientists will encounter a very different set of problems fabricating faster computing components."

## **1.2.1 CONVENTIONAL SILICON TECHNOLOGY NOT THE ANSWER**

NSA experts in HEC have concluded that semiconductor technology will not deliver the performance increases that the government's computing applications demand. Complementary metal oxide semiconductors (CMOS) is becoming less a performance technology—vendors such as Intel are voicing reluctance to seek 10 GHz clock speeds—and more a capability technology, with transistor counts of several hundred million per chip. The high transistor counts make it possible to put many functional units on a single processor chip, but then the on-chip functional units must execute efficiently in parallel. The problem becomes one of extracting parallelism from applications so that the functional units are used effectively.

Unfortunately, there are applications for which on-chip parallelism is not the solution; for such applications, blazing speed from a much smaller number of processors is required. For supercomputers, continuing reliance solely on a CMOS technology base means a continuation of the trend to massively parallel systems with thousands of processors. The result will be limitations in efficiency and programmability.

In addition, at today's scale, the electrical power and cooling requirements are facing practical limits, even if ways were found to efficiently exploit the parallelism. For example, the Japanese Earth Simulator system, which has been ranked number one on the list of the top 500 installed HEC, consumes over 6 megawatts of electrical power.

# **1.2.2 SUPERCOMPUTING RSFQ A VIABLE ALTERNATIVE**

The Silicon Industry Association (SIA) International Technology Roadmap for Semiconductors (ITRS) 2004 update on Emerging Research Devices has many candidate technologies presently in the research laboratories for extending performance beyond today's semiconductor technology. Superconducting Rapid Single Flux Quantum (RSFQ) is included in this list and is assessed to be at the most advanced state of any of the alternative technologies. RSFQ technology has the potential to achieve circuit speeds well above 100 GHz with lower power requirements than complementary metal oxide semiconductor (CMOS), making it attractive for very-high-performance computing, as shown in Figure 1-1.

Superconducting RSFQ is assessed to be at the most advanced state of any of the alternative technologies.

Digital superconducting electronics RSFQ technology has the potential, as identified in the 2003 and 2004 SIA roadmaps, to be a "successor" technology to CMOS for high-performance applications. The 2004 Update to this roadmap stated the problem as:

"One difficult challenge related to logic in both near- and the longer-term is to extend CMOS technology to and beyond the 45 nm node sustaining the historic annual increase of intrinsic speed of high-performance MPUs at 17%. This may require an unprecedented simultaneous introduction of two or more innovations to the device structure and/or gate materials. Another longer-term challenge for logic is invention and reduction to practice of a new manufacturable information and signal processing technology addressing 'beyond CMOS' applications. Solutions to the first may be critically important to extension of CMOS beyond the 45 nm node, and solutions to the latter could open opportunities for microelectronics beyond the end of CMOS scaling."

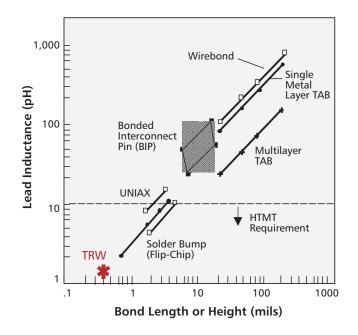

Figure 1-1. 2004 ITRS update shows RSFQ as the lowest risk (highest maturity) potential emerging technology for processing beyond silicon.

# **1.3 WHAT IS RSFQ CIRCUITRY?**

Rapid Single Flux Quantum (RSFQ) is the latest generation of superconductor circuits based on Josephson junction devices. It uses generation, storage, and transmission of identical single-magnetic-flux-quantum pulses at rates approaching 1,000 GHz. Small asynchronous circuits have already been demonstrated at 770 GHz, and clocked RSFQ circuits are expected to exceed 100 GHz.

#### **1.3.1 JOSEPHSON JUNCTIONS**

The Josephson junction (JJ) is the basic switching device in superconductor electronics. Josephson junctions operate in two different modes: switching from zero-voltage to the voltage-state and generating single-flux quanta. The early work, exemplified by the IBM and the Japanese Josephson computer projects of the 1970's and 1980's, exclusively used logic circuits where the junctions switch between superconducting and voltage states and require AC power. RSFQ junctions generate single-flux-quantum pulses and revert to their initial superconducting condition. RSFQ circuits are DC powered.

## **1.3.2 RSFQ ATTRIBUTES**

Important attributes of RSFQ digital circuits include:

- Fast, low-power switching devices that generate identical single-flux-quantum data pulses.

- Loss-less superconducting wiring for power distribution.

- Latches that store a magnetic-flux quantum.

- Low loss, low dispersion integrated superconducting transmission lines that support "ballistic" data and clock transfer at the clock rate.

- Cryogenic operating temperatures that reduce thermal noise and enable low power operation.

- RSFQ circuit fabrication that can leverage processing technology and computer-aided design (CAD) tools developed for the semiconductor industry.

Additional discussion of RSFQ technology basics can be found in Appendix D.

# **1.4 SUMMARY OF PANEL'S EFFORTS**