# RADIATION HARDENED LOW POWER DIGITAL SIGNAL PROCESSOR

Michael E. Fleming, William Spiller, and Mike Yee

Digital Signal Processing Architectures Inc. 10306 NE 85<sup>th</sup> Circle Vancouver, WA 98662

15 April 2005

**Final Report**

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED.

AIR FORCE RESEARCH LABORATORY

Space Vehicles Directorate

3550 Aberdeen Ave SE

AIR FORCE MATERIEL COMMAND

KIRTLAND AIR FORCE BASE, NM 87117-5776

#### AFRL-VS-PS-TR-2005-1045

DTIC COPY

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data, does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report has been reviewed by the Public Affairs Office and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nationals.

If you change your address, wish to be removed from this mailing list, or your organization no longer employs the addressee, please notify AFRL/VSSE, 3550 Aberdeen Ave SE, Kirtland AFB, NM 87117-5776.

Do not return copies of this report unless contractual obligations or notice on a specific document requires its return.

This report has been approved for publication.

//signed//

CASEY D. MCCOY, 2Lt, USAF

Project Manager

//signed//

KIRT S. MOSER, DR-IV

Chief, Spacecraft Technology Division

## REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing this collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1904, Aflington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YYYY)                                     | 2. REPORT TYPE             | 3. DATES COVERED (From - To)             |

|-----------------------------------------------------------------|----------------------------|------------------------------------------|

| 15/04/2005                                                      | Final Report               | 15/04/2004 to 15/04/2005                 |

| 4. TITLE AND SUBTITLE                                           | 5a. CONTRACT NUMBER        |                                          |

| Radiation Hardened Low Power Digital Signal Processor           |                            | FA9453-04-M-0097                         |

|                                                                 |                            |                                          |

|                                                                 |                            | 5b. GRANT NUMBER                         |

|                                                                 |                            |                                          |

|                                                                 |                            | 5c. PROGRAM ELEMENT NUMBER               |

|                                                                 |                            | 65502F                                   |

| 6. AUTHOR(S)                                                    |                            | 5d. PROJECT NUMBER                       |

| Michael E. Fleming, William (Kelly)                             | 3005                       |                                          |

|                                                                 |                            | 5e. TASK NUMBER                          |

|                                                                 |                            | VP                                       |

|                                                                 |                            | 5f. WORK UNIT NUMBER                     |

|                                                                 |                            | HD                                       |

| 7. PERFORMING ORGANIZATION NAME(                                | S) AND ADDRESS(ES)         | 8. PERFORMING ORGANIZATION REPORT NUMBER |

| Digital Signal Processing                                       |                            |                                          |

| Architectures Inc.                                              |                            |                                          |

| 10306 NE 85 <sup>th</sup> Circle                                |                            |                                          |

| Vancouver, WA 98662                                             | ( NAME(O) AND ADDRESS (50) | 40.0001/000//1001/000/0000/////          |

| 9. SPONSORING / MONITORING AGENCY<br>Air Force Research Laborat |                            | 10. SPONSOR/MONITOR'S ACRONYM(S)         |

| Space Vehicles Directorate                                      | -                          |                                          |

| <del>-</del>                                                    |                            | 44 ODONOOD/MONITODIO DEDODT              |

| 3550 Aberdeen Ave., SE                                          |                            | 11. SPONSOR/MONITOR'S REPORT             |

| Kirtland AFB, NM 87117-577                                      | 6                          | NUMBER(S)                                |

|                                                                 |                            | AFRL-VS-PS-TR-2005-1045                  |

#### 12. DISTRIBUTION / AVAILABILITY STATEMENT

Approved for public release; distribution is unlimited.

#### 13. SUPPLEMENTARY NOTES

#### 14. ABSTRACT

Report developed under SBIR contract for topic AF04-020.

This program develops a unique digital signal processing chip architecture based around four on-chip elements; a large multi-use memory, a RISC microprocessor, a fast FFT based vector processor, and a re-configurable Field Programmable Gate Array (FPGA).

These four elements are synchronized and blended on-chip to form a powerful signal and image processor. This processor, called the Transform Concentric Signal Processor (TCSP), meets and exceeds many of the current DoD on-board processing requirements.

Scalability is a major strength of the TCSP, multiple TCSP chips can be cascaded on a board, or in an MCM, to efficiently address even the most demanding signal and image processing requirements.

A significant windfall of this approach is a substantial reduction in software Engineering due to the TCSP's advanced data flow, ultra low latency, and high radix techniques.

#### 15. SUBJECT TERMS

SBIR Report, DSP, FFT, polyphase, radar, image processing, digital filtering, CFAR, matched filtering, convolution, pattern recognition

| 16. SECURITY CLASSIFICATION OF: |                             | 17. LIMITATION<br>OF ABSTRACT | 18. NUMBER<br>OF PAGES | 19a. NAME OF RESPONSIBLE PERSON Lt. Casey McCoy |                                                          |

|---------------------------------|-----------------------------|-------------------------------|------------------------|-------------------------------------------------|----------------------------------------------------------|

| a.REPORT<br>Unclassified        | b. ABSTRACT<br>Unclassified | c.THIS PAGE<br>Unclassified   | Unlimit <sup>,</sup>   | ed<br>60                                        | 19b. TELEPHONE NUMBER (include area code) (505) 846-5811 |

### **Table of Contents**

| AF04-020 Solicitation, P | hase 1 Objective List ———————————————————————————————————— | Page 1  |

|--------------------------|------------------------------------------------------------|---------|

| Phase 1 Objective (1)    |                                                            | Page 2  |

| Phase 1 Objective (2)    |                                                            | Page 6  |

| Phase 1 Objective (3)    |                                                            | Page 7  |

| Phase 1 Objective (4)    |                                                            | Page 8  |

| Phase 1 Objective (5)    |                                                            | Page 11 |

| Phase 1 Objective (6)    |                                                            | Page 20 |

| Phase 1 Objective (7)    |                                                            | Page 21 |

| Phase 1 Objective (8)    |                                                            | Page 22 |

| Phase 1 Objective (9)    |                                                            | Page 25 |

| Phase 1 Objective (10)   |                                                            | Page 27 |

| Phase 1 Objective (11)   |                                                            | Page 28 |

| Phase 1 Objective (12)   |                                                            | Page 45 |

| Phase 1 Objective (13)   |                                                            | Page 48 |

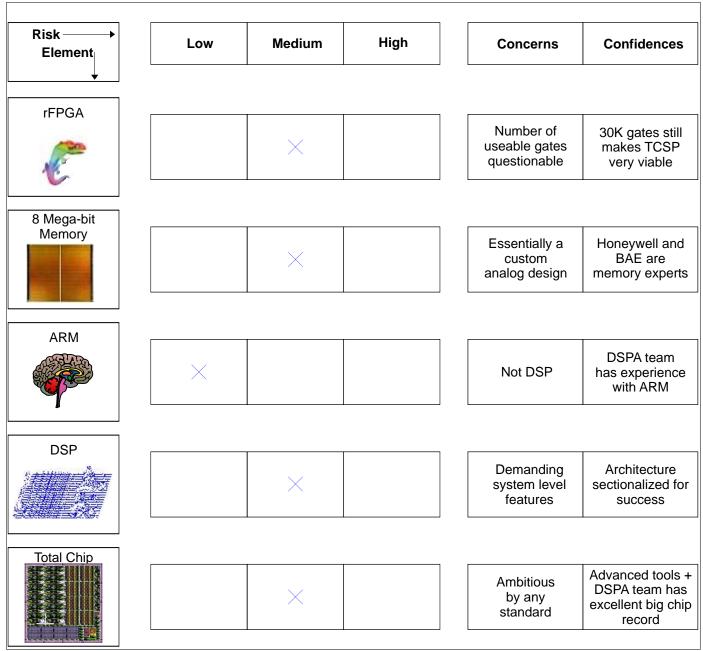

| Risk Matrix              |                                                            | Page 51 |

## List of Figures

| Figure 1.0 Transform Concentric Signal Processor (TCSP) Program ————————————————————————————————————       |  |

|------------------------------------------------------------------------------------------------------------|--|

| Figure 1.1 Transform Concentric Signal Processor (TCSP) Block Diagram ———————————————————————————————————— |  |

| Figure 2.0 TCSP Size and Placement —                                                                       |  |

| Figure 3.0 Motorola G6 Microprocessor —                                                                    |  |

| Figure 4.0 Odd Radix 3-D image Processing Impact                                                           |  |

| Figure 5.0 Six TCSP I/O Chip Ports and Data Flow                                                           |  |

| Figure 6.0 Scalable Core DSP Module —                                                                      |  |

| Figure 7.0 Cascaded Core Modules                                                                           |  |

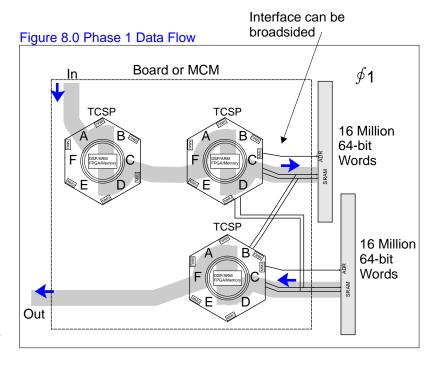

| Figure 8.0 Phase 1 Data Flow                                                                               |  |

| Figure 9.0 Phase 2 Data Flow                                                                               |  |

| Figure 10.0 Four TCSP's Back to Back Data Flow                                                             |  |

| Figure 11.0 Same Instruction Multiple Data (SIMD)                                                          |  |

| Figure 12.0 Direct Input 1                                                                                 |  |

| Figure 13.0 Direct Input 2                                                                                 |  |

| Figure 14.0 Cascade (Phase 1)                                                                              |  |

| Figure 15.0 Cascade (Phase 2)                                                                              |  |

| Figure 16.0 Double Buf Coef 1 (Phase 1)                                                                    |  |

| Figure 17.0 Double Buf Coef 1 (Phase 2)                                                                    |  |

| Figure 18.0 Double Buf Coef 2 (Phase 1)                                                                    |  |

| Figure 19.0 Double Buf Coef 2 (Phase 2)                                                                    |  |

| Figure 20.0 Double Buf Coef 2 (Phase 3)                                                                    |  |

| Figure 21.0 Double Buf Coef 2 (Phase 4)                                                                    |  |

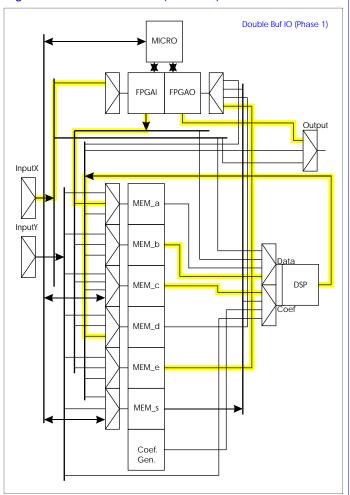

| Figure 22.0 Double Buf IO (Phase 1)                                                                        |  |

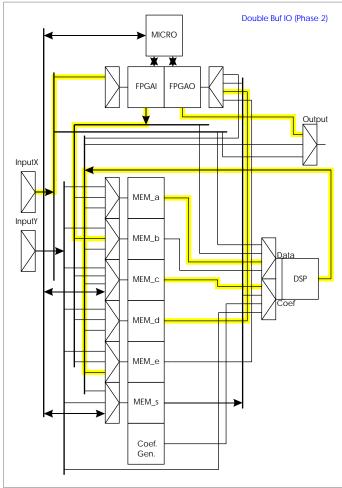

| Figure 23.0 Double Buf IO (Phase 2)                                                                        |  |

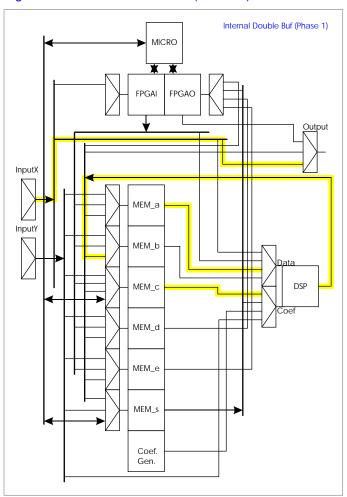

| Figure 24.0 Internal Double Buf (Phase 1)                                                                  |  |

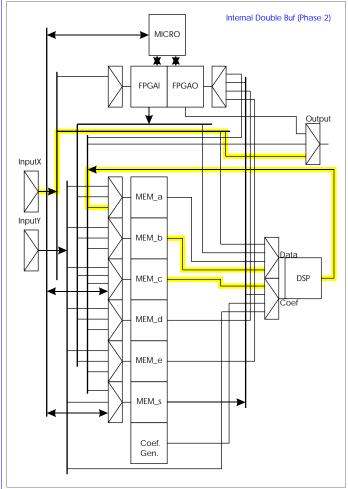

| Figure 25.0 Internal Double Buf (Phase 2)                                                                  |  |

| Figure 26.0 ARM Core sizes                                                                                 |  |

| Figure 27.0 40-bit Block Floating Point PSD ( 32-bit Binary + 8 bit Exponent)                              |  |

| Figure 28.0 IEEE 32-bit Floating Point PSD ( 40-bit Binary + 8 bit Exponent Converted ) ———                |  |

| Figure 29.0 16-bit Block Floating Point PSD —                                                              |  |

| Figure 30.0 24-bit Block Floating Point PSD —                                                              |  |

|                                                                                                            |  |

## List of Figures (cont.)

| Figure 31.0 Weak Signal Search ————————————————————————————————————                          | ——— P 24 |

|----------------------------------------------------------------------------------------------|----------|

| Figure 32.0 Weak Signal Search—                                                              | p 24     |

| Figure 33.0 on chip Coefficient Generator (CG)                                               | —— p 25  |

| Figure 34.0 Compression Inputs                                                               | —— p 26  |

| Figure 35.0 Current RHDSP24 Development Tools                                                | p 27     |

| Figure 36.0 1024 Point FFT with no Window                                                    | —— p 28  |

| Figure 37.0 1024 Point FFT with Hamming Window                                               | p 28     |

| Figure 38.0 FFT with Remez Filter coefficients in place of the window function               | —— p 29  |

| Figure 39.0 8K Channel Polyphase Digital Filter Example ———————————————————————————————————— | p 30     |

| Figure 40.0 Doppler Processing using the Short Time Fourier Transform (STFT)                 | p 31     |

| Figure 41.0 Doppler Processing using the STFT - Results                                      | p 33     |

| Figure 42.0 Illustration of Frequency Domain Pulse Compression                               | p 34     |

| Figure 43.0 Radar Display —                                                                  | —— p 35  |

| Figure 44.0 CFAR Algorithm ————————————————————————————————————                              | p 35     |

| Figure 45.0 Realtime Fast Convolution Filter Output                                          | —— p 36  |

| Figure 46.0 Filter Output on Top Of Input Signal —                                           | p 36     |

| Figure 47.0 Subtracted Signals —                                                             | p 37     |

| Figure 48.0 Two dimensional CFAR Realtime Filter                                             | p 38     |

| Figure 49.0 Sampled Image                                                                    | p 39     |

| Figure 50.0 Image PSD                                                                        | p 39     |

| Figure 51.0 Inverse FFT Resulting Image————————————————————————————————————                  | —— p 40  |

| Figure 52.0 Blurred Image                                                                    | —— p 45  |

| Figure 53.0 Point Spread Function PSF                                                        | —— p 45  |

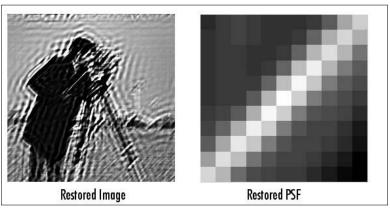

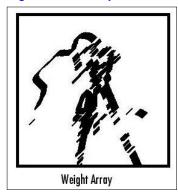

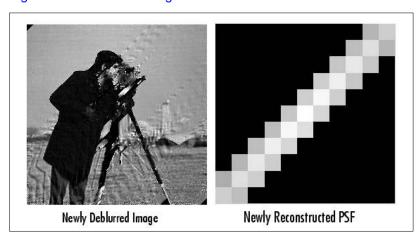

| Figure 54.0 Restored Image and Restored PSF                                                  | —— p 45  |

| Figure 55.0 Newly Created Array                                                              | —— p 46  |

| Figure 56.0 Deblurred Image and its PSF                                                      | —— p 46  |

| Figure 57.0 Eight Point Complex FFT                                                          | —— p 48  |

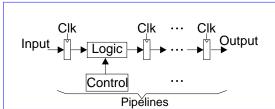

| Figure 58.0 Pipelined Logic                                                                  |          |

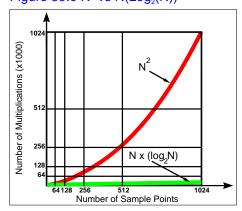

| Figure 59.0 N² vs N(Log <sub>2</sub> (N))                                                    | —— p 49  |

| Figure 60.0 Free Window Multiply and Free Coefficient Multiply on Fast Convolution           | p 50     |

| Figure 61.0 Risk Matrix —                                                                    | P 51     |

AF04-020 TITLE: Radiation Hardened, Low Power Digital Signal Processors

TECHNOLOGY AREAS: Information Systems, Sensors, Electronics, Battlespace

OBJECTIVE: Develop a low cost and low power Digital Signal Processor (DSP) architecture for use with high performance space applications.

PHASE I: Identify a highly efficient, hardened architecture. Simulate and model performance effects of the processor in different environments. Model the efficiency and throughput characteristics with radar processing algorithms, including Space Time Adaptive Processing (STAP) and Space Frequency Adaptive Processing (SFAP). Using state-of-the-art, space qualified (or qualifiable) integrated circuit processors, develop a scalable and programmable DSP element architecture. A large amount of on-chip memory is desirable for achieving highly efficient, backend signal processing (e.g., radar signal processing). Future ISR systems will require in excess of 5 GFLOPS/s (32-bit floating point arithmetic) per Watt for functions like STAP, Doppler processing, image formation, Constant False Alarm Rate (CFAR), and target position estimation.

#### Phase 1 Objectives:

- 1. Address market needs through on going customer interaction to produce a sound implementation maximizing synergy between the commercial, military, and space requirements. Illustrate the capabilities of the proposed architecture for currently available and soon to be available rad hard chip geometries.

- 2. Investigate new algorithms such as odd radix FFT and multi-tap FIR functions for the proposed architecture that will maintain its software heritage.

- 3. Determine whether the current 5 port, 24-bit two's complement complex I/O bus structure is sufficient, and if there needs to be more ports or additional types of ports.

- 4. Maintain the high throughput, latency insensitive approach across all the proposed hardware and software additions.

- 5. Determine how much memory can be included on chip for the proposed architecture, and how it should be best sectionalized, particularly for adaptive algorithms.

- 6. Determine whether it is technically possible and within the abilities of DSP Architectures Inc. to support adding FPGA capability on board the proposed chip.

- 7. Investigate an on-chip microprocessor, how capable, and what on chip microprocessor. Determine the software advantages of different on chip microprocessors and how much on-chip microprocessor memory is possible.

- 8. Measure the impact of increasing resolution. This includes the cost of a dedicated fixed point to and from IEEE floating point conversion and moving the architecture from 24-bits complex binary to 32-bits complex binary. Determine whether full IEEE floating point or boundary conversion is needed for the target set of applications and whether it can be added effectively to the TCSP chip.

- 9. In an effort to reduce overall application chip count, investigate moving memory management capability onto the proposed chip (in the form of the MMU24) along with on-chip twiddle factor generation.

- 10. Determine whether the entire chip and/or board system should be simulated with an integrated approach and/or what needs to be done to tie multiple vendor IP support tools together to form a whole.

- 11. Investigate how efficiently applications such as polyphase channelization, SAR radar, GMTI radar, wideband communications, and vision systems, can be performed by the proposed architecture.

- 12. Determine how well the proposed architecture will scale when applied to larger applications. Determine whether it will offer the economy of scale necessary to reduce the power and mass of future spacecraft reducing the ongoing cost of point solution ASICs.

- 13. Investigate chip design techniques and tools that are good candidates to allow the proposed architecture to achieve the maximum performance/watt.

Phase 1 Objective (1.) Address market needs through on going customer interaction to produce a sound implementation maximizing synergy between the commercial, military, and space requirements. Illustrate the capabilities of the proposed architecture for currently available and soon to be available rad hard chip geometries.

DSPA addressed this new chip architecture by reviewing all of its commercial, military, and space marketing information for the last nine years.

Additionally, DSPA consulted, in detail, with our OEM board manufactures as to what they would most like to see in a high end digital signal processing chip architecture.

Consistently at the forefront of these requirements were a programmable FFT based DSP, a large on chip flexible data memory, re-configurable fast FPGA logic, and a standard RISC microprocessor for maintaining an ongoing portable software library.

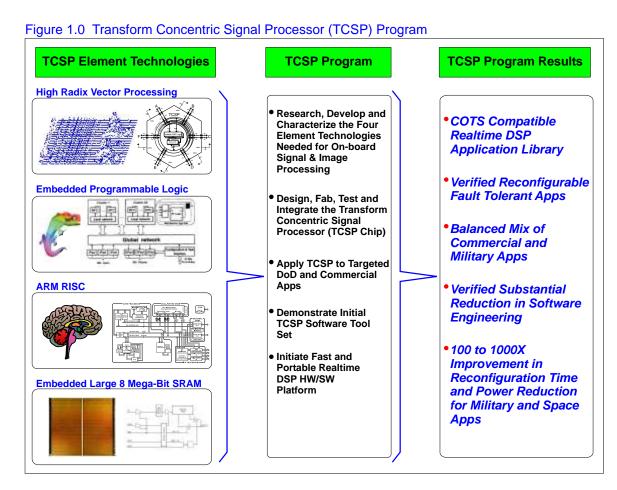

As shown in Figure 1.0, this program integrates the four element technologies of a innovative vector processor, a fast reconfigurable FPGA fabric, a standard RISC microprocessor, and a large internal memory to form, what we believe to be, a uniquely capable chip.

Since the architecture presented here is centered around a COTS chip implementation of the FFT, that has been refined for the last 20 years, it is named the Transform Concentric Signal Processor (TCSP).

As will be discussed, foremost in the design of this chip architecture are the requirements of low power and scalability. The TCSP employs several techniques to minimize power dissipation and maximize the sustained sample rate of demanding high end real time signal and image processing. The rad hard TCSP hardware and software scales from stand alone "black box" applications to the most demanding multi-processor applications in the industry.

A byproduct of the on chip vector processor and advanced data flow techniques is a substantial reduction in software engineering.

Phase 1 Objective (1.) Address market needs through on going customer interaction to produce a sound implementation maximizing synergy between the commercial, military, and space requirements. Illustrate the capabilities of the proposed architecture for currently available and soon to be available rad hard chip geometries.

#### The TCSP Chip Offers These Highlights:

- 0.15 micron rad hard, ultra low power SOI process, over 64-bits of internal precision, >>>10 GigaFlop/Watt

- Fully parallel FFT's, matrix math, complex math, FIRs, complex magnitude, etc. optimized in hardware Over 8 Million bits of multi-use SRAM -- I/O, memory, ARM, DSP, and rFPGA fabric all run concurrently

- Advanced rFPGA fabric targeted to contain equivalent of 200K useable ASIC gates, fast reconfiguration

- Six on-chip high end, 32-bit address range, DSP Memory Management Units (MMUs), shadow registered

for programming while in use. On chip twiddle and coefficient generator uses advanced compression

- Real only and complex 32-bit IEEE floating point, 32-bit, 24-bit, 16-bit, and 8-bit integer data types supported 40-bit automatic block floating point supported for extreme precision applications

- ARM for portable high level software, fault tolerance management. Arm instructions extended by rFPGA

- Ultra power optimized Radix-2, Radix-3, Radix-4, Radix-5, Radix-8, Radix-16, Radix-32, Radix-64, Radix-128, and Radix-256 on chip butterfly structures. Future TCSP chips will scale to Radix-1024 and beyond

- Fully static 300/500 MHz clock speed target, if final chip faster, everything scales up directly. If clock on the board product is lowered, TCSP power dissipation lowered by same amount

- Engineered to be dynamically re-programmed by on chip ARM for fast changing application modes

- Candidate to be the "standard" Space scalable DSP. Very low latency allows multiple TCSP's to easily cascade

on a board or MCM. Two TCSP's cascaded with no external components performs a 32-bit, 64K complex FFT

at 300 to 500 MSPS, 16-bit at 1 GigaHz, 16-bit and real only at 2 GigaHz. Three TCSP's back to back will do a

16 Million point complex FFT (or 4K x 4K 2-D) at a 2 GigaHz sample rate, or 4 GSPS if data is 8-bit.

- Vector processing approach achieves a substantial reduction in software engineering. Comprehensive DSP data flow communication scheme distributed throughout the chip, maximizes sustainable throughput.

- Targeted 32-bit binary complex sustained sample rate of 500 MHz.

Targeted 32-bit binary real sustained sample rate of 1000 MHz.

- Targeted 32-bit IEEE 754 floating point complex sustained sample rate of 500 MHz.

Targeted 32-bit IEEE 754 floating point real sustained sample rate of 1000 MHz.

- Targeted 24-bit binary complex sustained sample rate of 500 MHz.

Targeted 24-bit binary real sustained sample rate of 1000 MHz.

- Targeted 16-bit binary complex sustained sample rate of 1000 MHz.

Targeted 16-bit binary real sustained sample rate of 2000 MHz.

- Targeted 8-bit binary complex sustained sample rate of 2000 MHz.

Targeted 8-bit binary real sustained sample rate of 4000 MHz.

- All fixed point modes supported by no overhead block floating point:

32-bit binary + 8-bit exponent, 24-bit binary + 8-bit exponent, 16-bit binary + 8-bit exponent and 8-bit binary + 8-bit exponent

- Final processor could achieve greater than 32-bit binary precision, decision could be made at layout

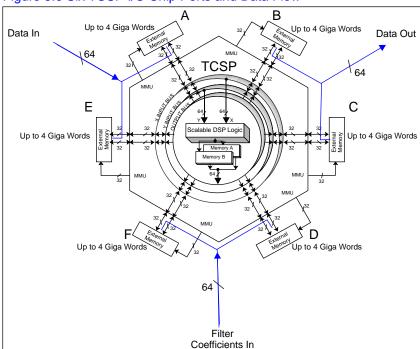

Figure 1.1 Transform Concentric Signal Processor (TCSP) Block Diagram Port B Unique six port chip ring bus, equivalent to a massive on chip crossbar circuit MMUB  $\otimes \otimes \cdots$ IEEE Float Pt. Logic DSP Module<sub>0</sub> Port F (LVDS) data naginary memory DSP Module<sub>1</sub> data imaginary memory Data Flow Logic DSP Module<sub>N</sub> DSP Module<sub>2</sub> data maginary memory DSP Module<sub>3</sub> Port A data imaginary memory data maginary memory data real memory DSP Module<sub>5</sub> DSP Module<sub>4</sub> Input Bus Y data real memory Input Bus X

Figure 1.1 is a high level diagram of the TCSP chip. The memory, rFPGA fabric, and ARM "drop-in" cores are shaded for identification.

Dort E

Output Bus Phase 1 Objective (1.) Address market needs through on going customer interaction to produce a sound implementation maximizing synergy between the commercial, military, and space requirements. Illustrate the capabilities of the proposed architecture for currently available and soon to be available rad hard chip geometries.

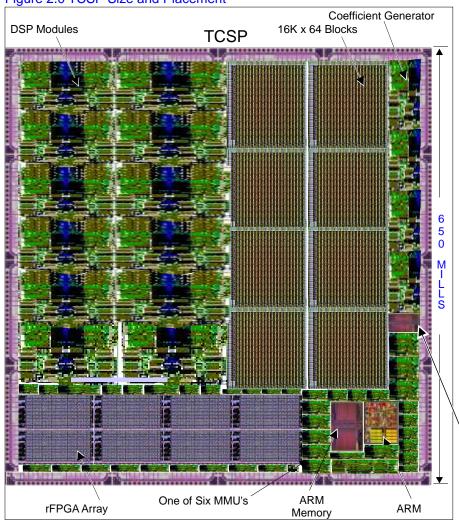

Figure 2.0 TCSP Size and Placement

In the era of billion transistor chips, one of the most significant challeges of an aggressive architecture is the efficient communications of all the on chip functional blocks.

Figure 2.0 shows the major building blocks of the TCSP's selected architecture.

It is a major task of this program to engineer this interconnect across a wide range of DSP applications and achieve the necessary "economies of scale" needed to propel the TCSP into the Military and commercial mainstream.

Coefficient Compression Memory

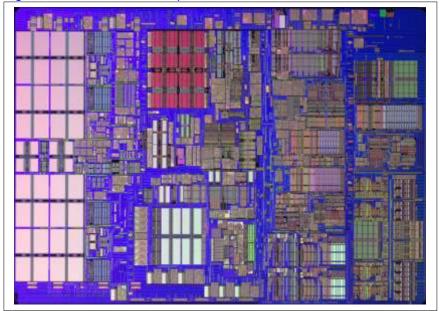

As an example of the significance of the on chip interconnect, see Figure 3.0, Motorola's sixth generation PowerPC processor, the G6.

The interconnect on this eight metal layer chip(the blue area), takes up at least 40% of the silicon. Interconnect dissipates power.

The TCSP architecture presented here addresses the interconnect issue not only within the chip, but within multiple TCSP chips on a board.

Figure 3.0 Motorola G6 Microprocessor

Phase 1 Objective (2.) Investigate new algorithms such as odd radix FFT and multi-tap FIR functions for the proposed architecture that will maintain its software heritage.

The proposed Vector Unit data path was designed to include very high radix structures, including odd radix-3 and radix-5 functionality. This was extensively simulated to insure compatibility with the other high level data path functions and the proposed software tool set.

Additionally, the proposed on-chip Memory Management Units (MMU) had to be engineered to include the new memory address generation and management functions to insure utility of all possible mixed and split radices.

The radix-3 and radix-5 give the TCSP additional horsepower for more efficient applications.

The proposed Vector Unit was also engineered to perform flexible FIR functions. Although the vast majority of image and signal FIR applications can be performed with the on chip rFPGA fabric. the Vector Unit FIR functions were straight forward to implement. These FIR functions can be used to update coefficients by performing extensive, high

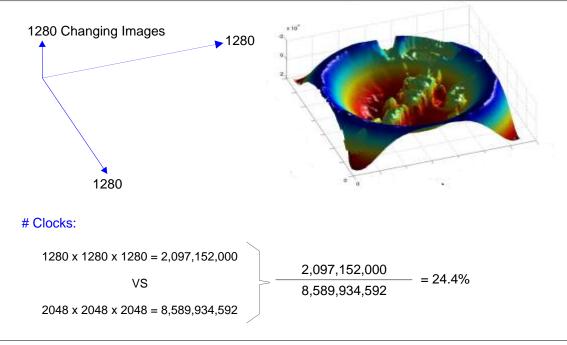

Figure 4.0 Odd Radix 3-D image Processing Impact

precision (32+ bits), matrix math operations.

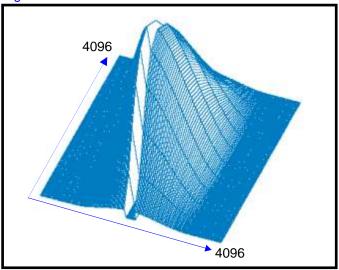

To illustrate the value of the odd radices. Consider the three dimensional Figure 4.0. If there are 1280 pixels in all three dimensions then we are dealing with 1280x1280x1280 = 2,097,152,000 values.

If a DSP processor does not have a radix 5 function (1280= 256 x 5) then each direction would have to be zero padded out to the next power of two, i.e. 2048 (256 x 8).

Now, we have 2048x2048x2048=8.589,934.592 values to process, even though we are only interested in 2,097,152,000 values. Since, the proposed TCSP is a synchronous fully static processor, it would do this required processing in less than one quarter of the time, i.e. 2,097,152,000 divided by 8,589,934,592, a very significant reduction in processing time. If the clock rate is reduced, a 75% reduction in power dissipation would be achieved. Phase 1 Objective (3.) Determine whether the current 5 port, 24-bit two's complement complex I/O bus structure is sufficient, and if there needs to be more ports or additional types of ports.

After many application simulations, including several data intensive multi-processor target applications, it was determined that an additional complex port would serve the board and MCM designers well. Additionally at least one port should be LVDS compatible

All six ports will be 32-bit complex (32-bits real + 32-bits imaginary) or double as 64-bit ports.

As illustrated in Figure 5.0, consider a large data intensive (4 Giga word) board level application with continuous data coming into memory A, as addressed by the MMU on port A, while the TCSP chip addresses and uses the data already stored in memory E.

At the same time coefficients are being addressed and used from memory D, while the coefficients are being addressed and updated in memory F. (The on chip FPGA fabric could be modifying the coefficients.)

And finally, at the same time the output memory B is being addressed for the data out, while memory C is being addressed for storing the results from the TCSP.

On the next frame of data, all the memories will trade tasks, the output will come from C memory, while the results from the TCSP will be stored in the B memory, etc.

In this manner, all inputs and outputs are fully addressed and double buffered, thereby allowing continuous real time processing.

This data flow is dynamic and controlled from the on chip scheduler, as commanded. For applications that only need to use internal on chip memory these ports can be powered down.

At the board level, flexible I/O such as this facilitates easy cascading of multiple TCSP chips and eliminates external components that multiply in number as more TCSP's are used.

Figure 5.0 Six TCSP I/O Chip Ports and Data Flow

Phase 1 Objective (4.) Maintain the high throughput, latency insensitive approach across all the proposed hardware and software additions.

DSPA has engineered the TCSP to have a unique latency insensitive approach to the synchronization of the four element technologies:

- Vector unit

- Reconfigurable FPGA fabric

- ARM microprocessor

- 8 Megabit SRAM

The Vector unit illustrated is an efficiently pipelined processor that uses low latency techniques to perform the following functions:

#### **VECTOR FUNCTIONS:**

Vector Add

Performs a binary addition operation with the input data and the coefficient data.

**Vector Subtract**

Performs a binary subtraction operation with the input data and the coefficient data.

**Vector Multiply**

Performs a fractional two's complement multiplication operation with the input data and the coefficient data.

Vector Multiply/Accumulate

Performs a fractional two's complement multiplication and accumulation of the result operation with the input data and the coefficient data.

#### COMPLEX MATH FUNCTIONS:

Complex Add

Performs a complex binary add operation with the input data and the coefficient data.

Complex Subtract

Performs a complex binary add operation with the input data and the coefficient data.

Complex Multiply

Performs a fractional two's complement complex multiplication operation with the input data and the coefficient data.

Complex Multiply/Accumulate

Performs a fractional two's complement complex multiplication and complex accumulation of the result operation with the input data and the coefficient data

Complex Magnitude

Performs a fractional two's complement square of the real input data added to the fractional two's complement square of the imaginary input data.

Phase 1 Objective (4.) Maintain the high throughput, latency insensitive approach across all the proposed hardware and software additions. (Cont.)

#### **DSP FUNCTIONS:**

Radix 2 Butterfly

Performs a radix 2 based butterfly operation on the complex input data.

Radix 3 Butterfly

Performs a radix 3 based butterfly operation on the complex input data.

Radix 4 Butterfly

Performs a radix 4 based butterfly operation on complex input data.

Radix 5 Butterfly

Performs a radix 5 based butterfly operation on the complex input data.

Radix 8 Butterfly

Performs a radix 8 based butterfly operation on complex input data.

Radix16 Butterfly

Performs a radix 16 based butterfly operation on complex input data

Radix 32 Butterfly

Performs a radix 32 based butterfly operation on complex input data

Radix 64 Butterfly

Performs a radix 64 based butterfly operation on complex input data

Radix 128 Butterfly

Performs a radix 128 based butterfly operation on complex input data

Radix 256 Butterfly

Performs a radix 256 based butterfly operation on complex input data

Also multiplies the incoming data by a window function.

#### **REAL ONLY FFT FUNCTIONS:**

Real Only FFT-Double Length

Performs a double length FFT if the input data was real only, i.e. performing a 256 point complex FFT yields a 512 point real result.

Real Only FFT- Two at a Time

Performs dual FFT's if the input data was real only, i.e. performing a 256 point complex FFT yields two seperate 256 point real results.

#### LOGIC FUNCTIONS:

<u>AND</u>

Performs a logical AND of the input data with the coefficient data.

OR

Performs a logical OR of the input data with the coefficient data.

XOR

Performs a logical XOR of the input data with the coefficient data.

#### **USER DEFINED FUNCTIONS:**

**User Defined**

When combined with the rFPGA and ARM, several proprietary user specific instructions may be defined.

Phase 1 Objective (4.) Maintain the high throughput, latency insensitive approach across all the proposed hardware and software additions. (Cont.)

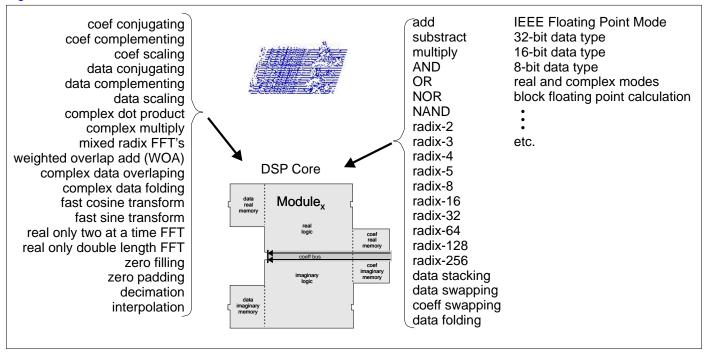

Figure 6.0 Scalable Core DSP Module

The base DSP step and repeat core module is illustrated in Figure 6.0. Considerable engineering over the last two decades has been put into making it scalable and comprehensive. This core is readily assembled from just a couple dozen library cells and is fully static. Internal to this core are the TCSP's advanced power optimizing techniques.

Figure 7.0 shows how the DSP core module stacks for increased functionality. This core stacks both functionally and physically during chip layout. As chip geometries shrink below 0.1 micron, more and more of these step and repeat modules can be easily laid down. These stackable modules also maintain their software compatibility with future generations.

Figure 7.0 Cascaded Core Modules

Phase 1 Objective (5.) Determine how much memory can be included on chip for the proposed architecture, and how it should be best sectionalized, particularly for adaptive algorithms.

One of the driving concepts for utilizing the TCSP's on chip 8 megabit memory is presented here.

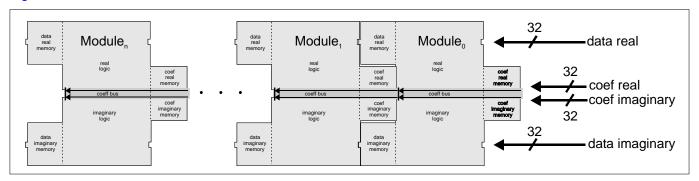

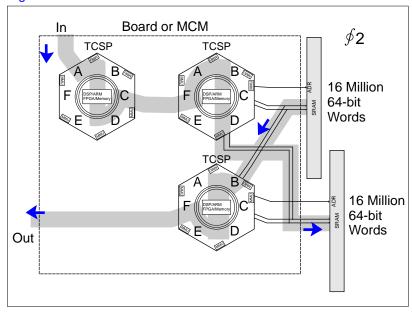

Consider a board or MCM with three TCSP's cascaded together as pictured in Figure 8.0.

Let's say it's a surveillance application and the focal plane array is 4K x 4K elements. We need to transform this 2-D picture using a 16 million point 1-D FFT.

The TCSP has a radix-256 FFT butterfly function, therefore three of these butterflies performed back to back is 256x256x256=16 million points.

Since 256x256=64K, we need 64K words within the first TCSP chip to store the results of two hundred and fifty-six radix-256 butterflies. (reference www.dsparchitectures.com/new\_page\_applica tions.htm) Comprehensive FFT App note.

When the first chip's 64K buffer is full, the second chip in the cascade can perform it's two hundred and fifty-six radix-256 butterflies and store the results in the external 16 million point memory. This is repeated until the 16 million point external memory is full, then the third TCSP chip can perform 64K radix-256 butterflies on the data.

Figure 9.0 shows the second phase of this process. This process is bubble free and it is continuous, since the internal 64K is double buffered.

If the three chips are all clocked at 500 MHz, then the input and output sample rate will be 500 MHz complex!

If the data is real only, then this rate doubles to 1 Giga Hertz.

If the data type is 16-bits (or 16-bits plus 8-bits of block floating point), this rates doubles again to 2 Giga Hertz.

Figure 9.0 Phase 2 Data Flow

As geometries shrink, the next step would be radix-512, requiring 512x512=256K double buffered, or 32 mega bits.

Note also, that the internal Coefficient Generator (CG) generates all the necessary twiddle factors on chip. Also, the 16 million words of double buffered external memory is managed by the on chip MMU's.

The double buffered 64K words (or 128K words) in both the second and third TCSP's were not used and can be used by the on chip rFPGA fabric or ARM processors to do other things concurrently. Such as I/O fabric protocol, adaptive filtering, compression, deconvolution, gain adjustments, off axis compensation, colorizing, etc.

After spending some time with the Honeywell and BAE Engineers we believe the 8 million bit memory is achievable.

Using the on-chip 64K double buffered memory, if we add just one more TCSP as shown in Figure 10.0, we now have a 4 Giga word processor or four channels of 1K x 1K x 1K 3-D image FFT's at 500 MSPS. Or 1 GigaSPS if data real, or 2 Giga Sample per Second if data real and 16-bit. If data is 8-bit and real then the sustained sample rate would be 4 GSPS.

Additionally, the four channels could be parallelized to process one 1Kx1Kx1K 8-bit channel at 16 Giga Samples per second!

Figure 10.0 Four TCSP's Back to Back Data Flow

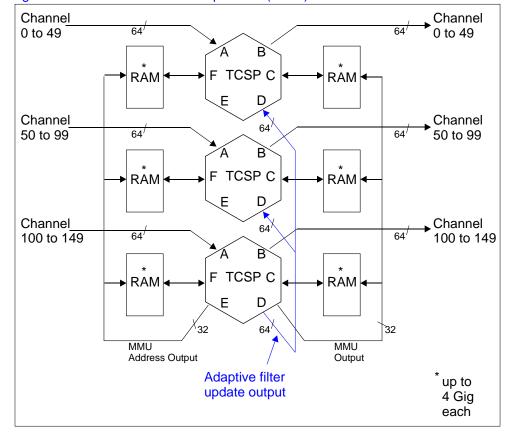

Figure 11.0 Same Instruction Multiple Data (SIMD)

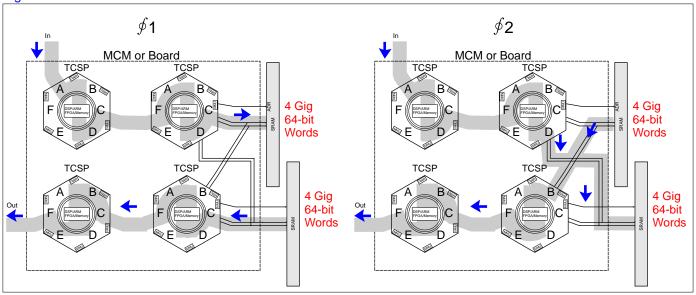

In addition to cascaded TCSP chips, high end Same Instruction Multiple Data (SIMD) multi-TCSP configurations were simulated with the TCSP Model.

Figure 11.0 illustrates a data intensive application that uses one of three available rFPGA's for adapting the coefficients in realtime. And just two of the eighteen (18) available MMU's are used to address all six large external memories. This configuration allows the unused TCSP resources to be

This configuration could ping pong the data back and forth through the TCSP's thousands of times before outputting. resolutions and data modes

could be changed on any pass.

powered down to save power.

Additionally, cascaded SIMD structures were simulated.

At a minimum, the following internal data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

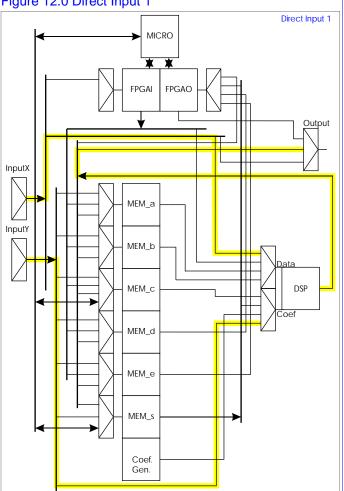

Figure 12.0 Direct Input 1

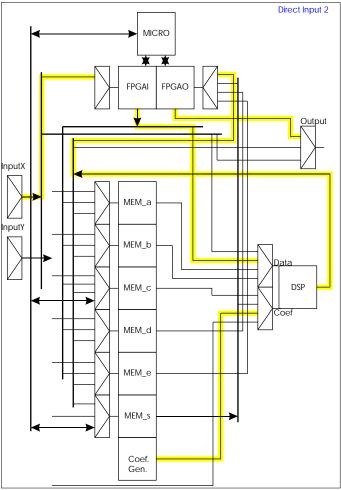

Figure 13.0 Direct Input 2

Figure 12.0 illustrates the internal TCSP data flow for applications that use the DSP unit directly, while the rFPGA, memory, and ARM do other things concurrently. Here the DSP uses input data and coefficients from off the chip.

Figure 13.0 illustrates the internal TCSP data flow for applications that use the DSP unit directly, while the rFPGA, memory, and ARM do other things concurrently. Here the DSP uses coefficients generated from its on chip generator, freeing up an I/O bus for other uses.

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

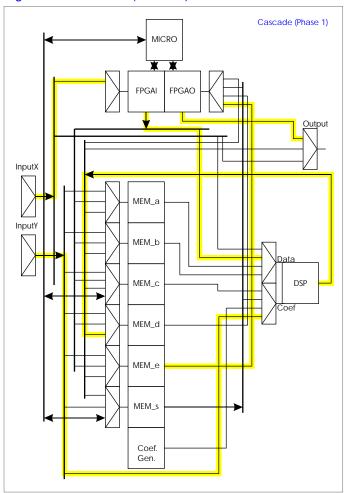

Figure 14.0 Cascade (Phase 1)

Figure 14.0 illustrates the internal TCSP data flow for applications that run the chip input data through the FPGA before and after running it through the DSP. Additionally, when used with Cascade Phase 2, the output data is double buffered and can be re-addresses for seamless TCSP to TCSP cascading.

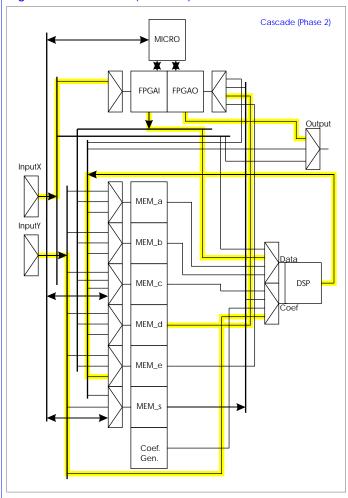

Figure 15.0 Cascade (Phase 2)

Figure 15.0 See Cascade Phase 1.

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

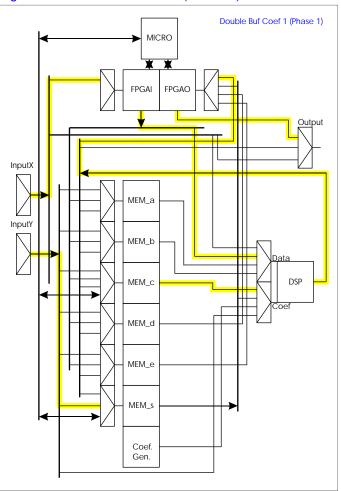

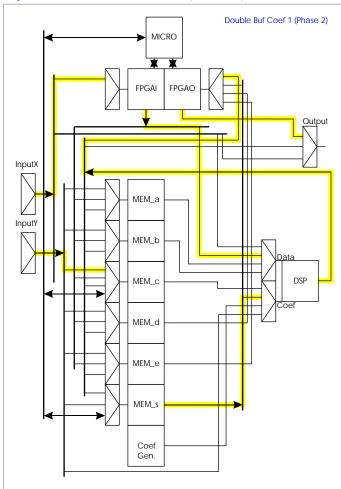

Figure 16.0 Double Buf Coef 1 (Phase 1)

Figure 17.0 Double Buf Coef 1 (Phase 2)

Figure 16.0 illustrates using the same double buffer technique used in the output cascading, input coefficients (for windowing) can be changed.

Figure 17.0 Double buffered coefficient output of Phase 1.

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

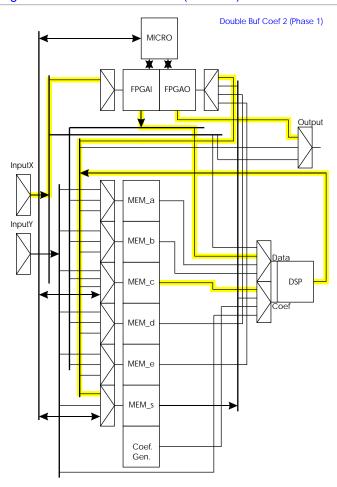

Figure 18.0 Double Buf Coef 2 (Phase 1)

Figure 18.0 In addition to external modification of the coefficients, these two phases (Coef 2 Phase1 &2) show coefficient modification via the FPGA and via the Microprocessor.

Pegal FPGAU MEM\_a

MEM\_c

MEM\_

Figure 19.0 See

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

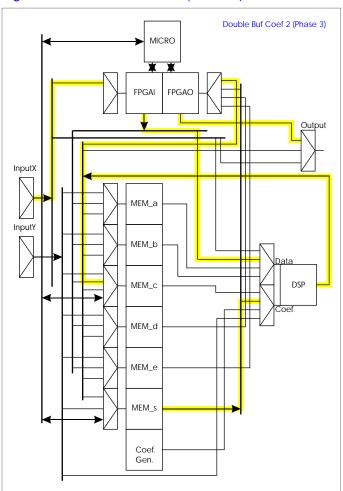

Figure 20.0 Double Buf Coef 2 (Phase 3)

Figure 20.0 illustrates third phase of the double buffered coefficient output modified by the FPGA.

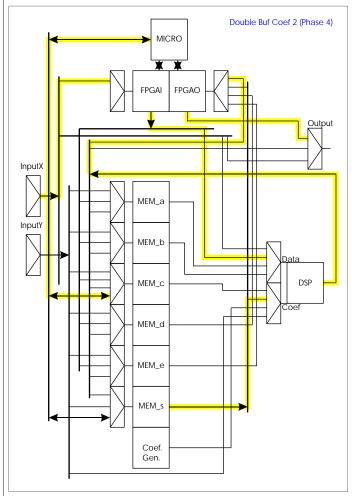

Figure 21.0 Double Buf Coef 2 (Phase 4)

Figure 21.0 illustrates fourth phase of the double buffered coefficient output modified by the FPGA.

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

Figure 22.0 Double Buf IO (Phase 1)

Figure 22.0 illustrates the internal TCSP data flow for double buffered input and output to and from the DSP

Figure 23.0 Double Buf IO (Phase 2)

Figure 23.0 illustrates second phase of the dual, double buffered DSP input and output.

At a minimum, the following *internal* data flows were simulated and are going to implemented within the TCSP. These data flows eliminate the need for an on-chip massive "crossbar" switch fabric.

#### Internal Data Flow

Figure 24.0 Internal Double Buf (Phase 1)

Figure 24.0 illustrates the dual processing datapath capability. In this case, the DSP is operating on data from and to internal memory, while external data is passing through.

Figure 25.0 Internal Double Buf (Phase 2)

Figure 25.0 illustrates the second phase of the internal memory double buffering.

Note: The input and output data could pass through the FPGA, etc.

Phase 1 Objective (6.) Determine whether it is technically possible and within the abilities of DSP Architectures Inc. to support adding FPGA capability on board the proposed chip.

As illustrated back in our data flow diagrams, the rFPGA hardware is linked to all the on chip resources to help in implementing the pre and post transform processing functions, the I/O switching fabric, as well as other stream-oriented operations.

After evaluating several potential FPGA fabric vendors, we believe the TCSP can embed M2000's core and we have focused on M2000 (www.m2000.fr). They offer FlexEOS Embedded FPGA Cores. Some of the applicable highlights are as follows.

A symmetrical, hierarchical architecture for fast, dense FPGA functions.

Optimized size.

High occupation factor.

Deterministic, fanout independent timing.

Completely flexible I/O assignment.

Multiple clock domains.

Compact bitstream for fast, dynamic re-configuration

Fast and predictable compilation time, for example: 33K logic gates = 3-4 minutes.

Generation of data to validate timing and logic at SOC level.

Efficient, automatic software flow that integrates with standard tools.

On-chip testing.

FlexEOS can be implemented on any silicon technology.

Fast logic: 300+MHz or faster depending on how heavily pipelined the design is. (Since the TCSP is pipelined and the system architecture is low latency, this is the case.)

Die Area:

- -8 mm<sup>2</sup> for 20k ASIC gates

- -15 mm<sup>2</sup> for 30/50k ASIC gates

- -60 mm<sup>2</sup> for 60/70k ASIC gates

Designs at the higher gate densities employ redundant/repairable architecture whereby the compiled configuration bit-stream is dynamically modified to map out the damaged sections. When this is combined with the ultra fast re-programming time, the result is higher fault tolerance and the ability to implement more fault tolerant types of pre-and post-processing TCSP algorithms.

#### Sample rFPGA TCSP Functions:

Bit processing

Automatic Gain Control (AGC)

I/Q Split Decimate Interpolate

Weighted Overlap Add (WOA)

Scalar Math/Logic

Simple FIRs/Dot Products

Point Spread Function Calculations

**Dominate Spectra Processing**

Averaging

Content Addressable Storage

Table Lookup

Difference processing Fast Histograms

Coefficient Adaptation

QR Decomposition

LMS/Genetic Adaptive Calculations

Rapid I/O Protocol Logic

Data format conversions

'King of the hill' tracking

Array subtraction for CFAR as illustrated in Objective 11 Thresholding for multiple real time adaptive thresholds Algorithm acceleration for the ARM microprocessor

Improved utilization of the DSP datapath by offloading simple vector

multipy/add's.

Demod/Viterbi decoding Power management

Accelerate and extend ARM calculations

Real only vs complex recombines

Block floating point management

Quadrature modulation/demodulation

Dynamic application mode management

Environmental detection and compensation

Etc.

Phase 1 Objective (7.) Investigate an on-chip microprocessor, how capable, and what on chip microprocessor. Determine the software advantages of different on chip microprocessors and how much on-chip microprocessor memory is possible.

After careful consideration of the abundance of available RISC cores, DSPA has selected the ARM720T core. This core is small and has unparalleled software support, along with being the most popular in the industry. The on chip ARM will allow DSPA to easily port the existing DSP24 application library to the TCSP, and make the growing application library transparent to future TCSP hardware upgrades.

The TCSP architecture is not demanding of the on chip RISC, the ARM will be used to communicate with the chips "outside" world and configure and control the TCSP's resources at a high level.

Fault tolerance and built in test circuitry will be a major task of the ARM.

Figure 26.0 shows the relative small size of the ARM 7, and its memory, as compared to the anticipated TCSP die size.

To accommodate as much application utility as possible, the size of the ARM's memory will be selected after the TCSP chip's sizing is close to being finalized.

Figure 26.0 ARM Core sizes

| Processor Generic Foundry Process                                               |          | Performance<br>MIPS/MHz<br>(Dhrystone 2.1) | Power Consumption<br>mW/MHz<br>(Typical') | Area<br>mm² | Frequency<br>MHz<br>(Worst case <sup>2</sup> ) |

|---------------------------------------------------------------------------------|----------|--------------------------------------------|-------------------------------------------|-------------|------------------------------------------------|

| ARM7TDMI 0.18µm                                                                 |          | 0.9                                        | 0.25                                      | 0.53        | 90                                             |

| ARM7TDMI-S                                                                      | 0.18µm   | 0.9                                        | 0.39                                      | 0.62        | 80-110                                         |

| ARM7EJ-S                                                                        | 0.18µm   | 1.0                                        | 0.45                                      | 0.95        | 80-110                                         |

| ARM720T                                                                         | 0.18µm   | 0.9                                        | 0.65                                      | 3.00        | 75                                             |

| ARM7TDMI                                                                        | 0.13μm   | 0.9                                        | 0.06                                      | 0.26        | 133                                            |

| ARM7TDMI-S 0.13μm                                                               |          | 0.9                                        | 0.10                                      | 0.32        | 100-133                                        |

| ARM7EJ-S 0.13μm                                                                 |          | 1.0                                        | 0.18                                      | 0.42        | 100-133                                        |

| ARM720T                                                                         | 0.13μm   | 0.9                                        | 0.20                                      | 2.40        | 100                                            |

| 0.18 µm at 1.8V, 0.13 µm                                                        | TCSP die | 2 3                                        | & synthesis & cell library<br>um at 1.08V |             |                                                |

| The TCSP is probably going to be 25  The ARM 7 is 2.4 mm²  The ARM 7 is 2.4 mm² |          |                                            |                                           |             |                                                |

Phase 1 Objective (8.) Measure the impact of increasing resolution. This includes the cost of a dedicated fixed point to and from IEEE floating point conversion and moving the architecture from 24-bits complex binary to 32-bits complex binary. Determine whether full IEEE floating point or boundary conversion is needed for the target set of applications and whether it can be added effectively to the TCSP chip.

DSPA has finished designing the TCSP simulator, this sections summarizes some of the applications coded so far.

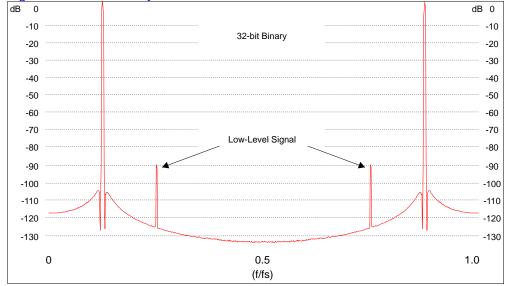

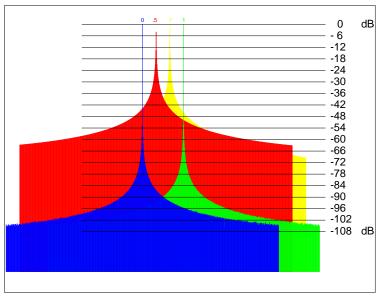

Figure 27.0 shows an initial two tone test using the chip model. The precision used here is the full 32-bit complex binary (32-bits of real, plus 32-bits of imaginary, with the addition of block floating point.

As illustrated a over 120 dB of signal range has been achieved, so far. Even more accuracy can be achieved when the full capability of the TCSP block floating point features are used, close to 200 dB of two tone differences are expected.

The TCSP's 32-bits plus 8 bits of block floating point is calculated at the full chip targeted speed of 300/500 MHz. Note: Large FPGA solutions such as the Xilinx Virtex-2 and future Virtex-4 struggle with 32-bit precision and with floating point.

Figure 27.0 32-bit Binary PSD

Four term Blackman-Harris window response. Future TCSP simulations will show that this data type approaches IEEE double precision floating point accuracy.

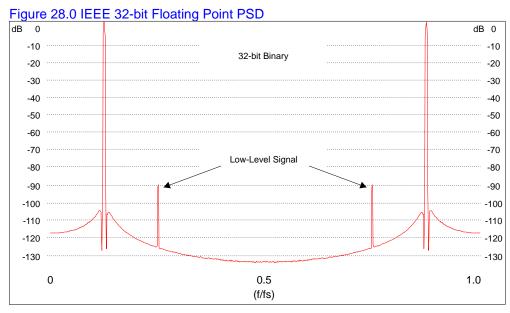

Figure 28.0 shows the IEEE floating point result after the 32-bit binary result is converted on chip. Based on past DSP applications, DSPA believes that converting the 40-bit data type to IEEE floating point on chip using a fast dedicated logic block is superior to implementing floating point throughout the processor, front to back.

Phase 1 Objective (8.) Measure the impact of increasing resolution. This includes the cost of a dedicated fixed point to and from IEEE floating point conversion and moving the architecture from 24-bits complex binary to 32-bits complex binary. Determine whether full IEEE floating point or boundary conversion is needed for the target set of applications and whether it can be added effectively to the TCSP chip.

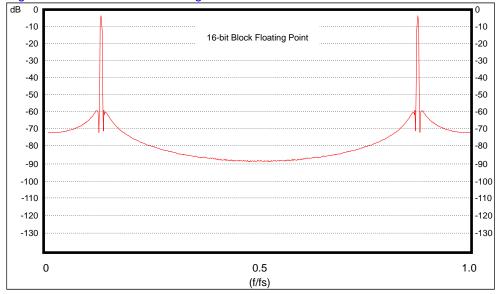

Figure 29.0 16-bit Block Floating Point PSD

Figure 29.0 illustrates the actual TCSP 16-bit data type FFT response.

This data type will be twice as fast as the 32-bit TCSP data types, i.e. 2 Giga Hertz sustained sample rate or higher.

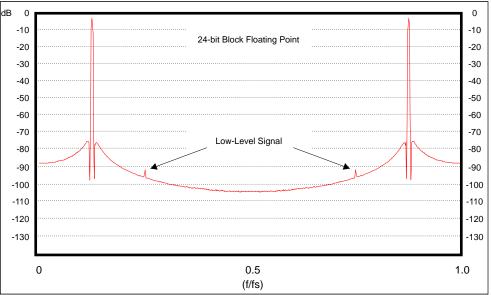

Figure 30.0 is the TCSP data type inherited from the wealth of applications the DSP24 and Sharp LH9124 have implemented for over a decade.

Most modern DSP applications need more that 16-bits of precision when taking advantage of the efficiencies of the frequency domain, this data type gives it to them.

When compared to the floating point and 32-bit binary data types, power savings of 25%, or more, can be had by using 24-bits. And the TCSP can easily switch between data types, within an application, to save power.

Figure 30.0 24-bit Block Floating Point PSD

Phase 1 Objective (8.) Measure the impact of increasing resolution. This includes the cost of a dedicated fixed point to and from IEEE floating point conversion and moving the architecture from 24-bits complex binary to 32-bits complex binary. Determine whether full IEEE floating point or boundary conversion is needed for the target set of applications and whether it can be added effectively to the TCSP chip.

Figure 31.0 Weak Signal Search

As a first attempt to illustrate the flexibility of the TCSP processor, Figure 31.0 shows the TCSP quickly switching between data types, switching between windows functions, and switching between algorithms to find an extremely weak signal in the presence of a very large signal. After four combinations, no small signal presence detected.

The "intelligence" for this signal search can be managed by the on-chip ARM processor, or if need the ARM processor accelerated with the on-chip rFPGA fabric.

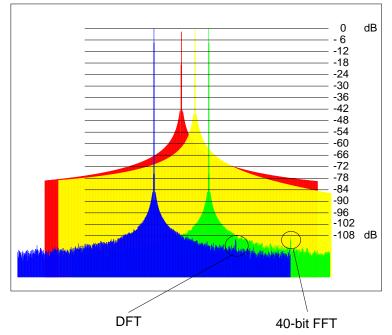

As shown here in Figure 32.0, the TCSP implements a 512K complex DFT (not FFT), (blue) to verify that there is any small signal there at all. Then, for much faster speed, switches over to a 32-bit data type 512K point FFT with comparable results.

The TCSP can rapidly switch resolution, data types, and algorithms dynamically as required.

Had the signal not appeared, the TCSP could have easily switched to a 32-tap, weighted overlap add, 64K point polyphase FFT. This could insure the signal was not hiding between bins.

A CFAR routine was also used to automatically find the signals.

Figure 32.0 Weak Signal Search

Phase 1 Objective (9.) In an effort to reduce overall application chip count, investigate moving memory management capability onto the proposed chip (in the form of the MMU24) along with on-chip twiddle factor generation.

To facilitate and reduce the application chip count, six on chip MMU's will be implemented on the TCSP. The MMU's will support both on chip memory management for single chip applications and off chip memory for extreme data intensive applications such as 3-D image processing. Additionally, the MMU's have been expanded to address 32 bits of address range each.

The TCSP's on chip coefficient/ twiddle factor generation eliminates several external components and saves even more in multi-TCSP applications. When the user is sourcing adaptive coefficients or window functions external to the TCSP, the Coefficient Generator (CG) can be dynamically turned off to save power.

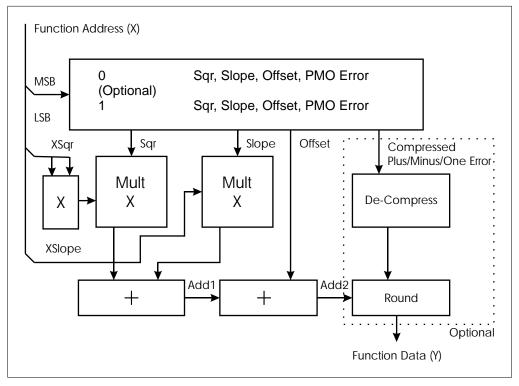

The block diagram of the on chip twiddle factor generation/decompression engine, the CG is shown in Figure 33.0.

Since, initial slope-fitting results indicate that the methodology will work, substantial engineering was done to reduce the plus or minus multone (PMO) errors and in determining the minimum

multplier/adder/rounder/ storage components.

In order to store bitaccurate coefficients, an adjustment of +1 or -1 or none must be made to the final interpolated data point. Depending on Frame size (interpolated points per curve), the storage of this extra adjustment will be several times larger than the bit storage requirement of the seeds

Figure 33.0 on chip Coefficient Generator (CG)

for the curve. To reduce this, the compression routine was modified to calculate data points to more significant digits, and to use multiple rounding techniques.

The modifying algorithms are as follows:

- Data generated to desired bit width plus 1 bit, truncate lower 1 LSB

- Data generated to desired bit width plus 1 bit, round at smallest LSB and truncate to bit width.

- Data generated to desired bit width plus 2 bits, truncate lower 2 LSB

- Data generated to desired bit width plus 2 bits, round at smallest LSB and truncate to bit width.

- Data generated to desired bit width plus 2 bits, round at smallest 0.5 bit and truncate to bit width.

- Data generated to desired bit width plus 2 bits, round at smallest LSB and 0.5 LSB and truncate to bit width.

- Data generated to desired bit width plus 3 bits, truncate lower 2 LSB

- Data generated to desired bit width plus 3 bits, round at smallest LSB and truncate to bit width.

- Data generated to desired bit width plus 3 bits, round at smallest 0.5 bit and truncate to bit width.

- Data generated to desired bit width plus 3 bits, round at smallest LSB and 0.5 LSB and truncate to bit width.

- Data generated to desired bit width plus 4 bits, truncate lower 2 LSB

- Data generated to desired bit width plus 4 bits, round at smallest LSB and truncate to bit width.

- Data generated to desired bit width plus 4 bits, round at smallest 0.5 bit and truncate to bit width.

- Data generated to desired bit width plus 4 bits, round at smallest LSB and 0.5 LSB and truncate to bit width.

Phase 1 Objective (9.) In an effort to reduce overall application chip count, investigate moving memory management capability onto the proposed chip (in the form of the MMU24) along with on-chip twiddle factor generation.

The results indicate that the PMO error is not very sensitive to extra bits. It is more a function of the round on data points that end in a long run of 1's or 0's that when rounded or borrowed from, generate a carry that ripples into higher significant bits. Overall, the standard round (add of 0.5) to the final data point, gave the most even PMO error results.

Work was done creating a masking routine to systematically find minimum mask sizes to control the bit widths of all aspects of the twiddle factor generation logic. The masks in Figure 34.0 were applied to the corresponding inputs in Figure 33.0 to control bit widths.

Figure 34.0 Compression Inputs

| XSqr | XSlope | Sqr | Slope | Offset | Add1 | Add2 |

|------|--------|-----|-------|--------|------|------|

|------|--------|-----|-------|--------|------|------|

Results for four of the most likely 1 million point twiddle factor generation blocks:

- 24 bit resolution, stored as 512 curves with 512 (Frame) interpolated points per curve.

- 24 bit resolution, stored as 128 curves with 2048 (Frame) interpolated points per curve.

- 32 bit resolution, stored as 1024 curves with 256 (Frame) interpolated points per curve.

- 32 bit resolution, stored as 512 curves with 512 (Frame) interpolated points per curve.

Phase 1 Objective (10.) Determine whether the entire chip and/or board system should be simulated with an integrated approach and/or what needs to be done to tie multiple vendor IP support tools together to form a whole.

Figure 35.0 is a picture of the current DSPA rad hard processor tool set.

The TCSP tool set will build upon this environment and its legacy of application software.

DSPA has converged on the following TCSP Software Environment:

**ARM** Design with ARM Cores for full chip physical integration is based on standard commercial tools.

Application Development supported by ARM via its' Realview Development Suite and many third party manufacturers.

## Realview Development Suite

- Code Generation Tools C and Embedded C++ compilers, Assembler and Linker for ARM and Thumb® instruction sets.

- An Integrated Development Environment for Windows CodeWarrior® IDE from Metrowerks® (PC version only)

- GUI debugger AXD and ARM symbolic debugger (armsd). Instruction set simulators

- Provides accurate simulation of ARM and Thumb core-based processors.

- Real-time Debug and Trace support.

- Allows development and benchmarking of code before hardware is available.

- User extensible to (C or C++) to add support for custom peripherals.

## Figure 35.0 Current RHDSP24 Development Tools

#### rFPGA

FlexEOS macro is delivered with the complete set of data for full SoC DFT, floor planning, physical verification. This includes the three main design environments.

- Full chip physical integration is based on standard commercial tools.

- Tools for data generation to validate timing and logic at SOC level using standard commercial tools.

- Configuration generation, download, and corruption recovery.

- Embedded test via BIST.

#### **DSP**

Application Development - Performed at a high level using scripts to drive System Simulations.

- Sophisticated ARM/FPGA/DSP processing using ARM Instruction Set Simulator combined with DSP scripts and custom FPGA hardware macros in C or C++.

- DSP Script compiler.

- Coefficient and Window generation tools.

Full RTL and Gate level simulation using standard commercial tools.

Phase 1 Objective (11.) Investigate how efficiently applications such as polyphase channelization, SAR radar, GMTI radar, wideband communications, and the vision systems, can be performed by the proposed architecture.

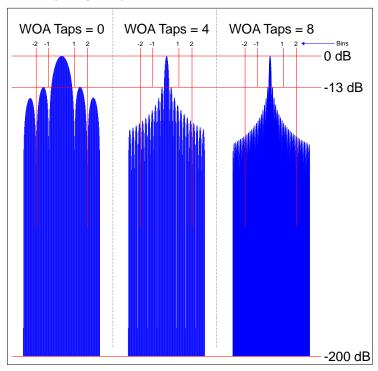

Figure 36.0 1024 Point FFT with no Window Bin Frequency Response

The test of any computing architecture is how comprehensively, efficiently and precisely it performs the targeted class of applications.

One application that is enjoying the lime light is polyphase filters. They can be efficient and application enabling. The following was simulated with the new TCSP C simulator.

Figure 36.0 shows three bin responses of an FFT's output. This FFT applied no window function at all.

When there is no weighted overlap add (WOA) applied before performing the FFT, WOA=0, then the response is classic, a fat main lobe that drops off slowly.

When four taps are applied, the side lope rejection stays the same, but the main lobe is much skinner.

Eight WOA taps gives an even skinner main lobe, and again the side lobes are the same height, a much sharper response than the straight FFT (i.e. WOA=0). This would be terrific for detecting the presence of precisely located signals, even millions of them.

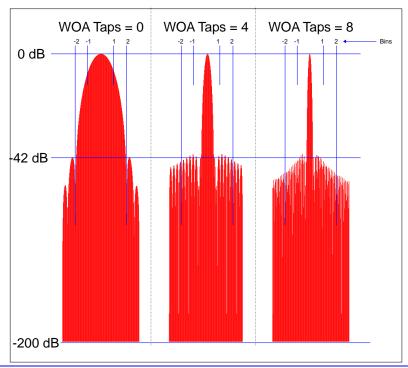

Referring to Figure 37.0 let's do this again, but this time with a Hamming window function applied before the FFT in the case of WOA=0 and before the weighted overlap add function for the four and eight tap examples.

Notice this time the main lobe width is fatter than the no window case above, for all three responses, but the side lobes are classically down to -42 dB.

The WOA=8 response would not only be great for detecting signals, but this time would also have quite a bit of out of band noise and interference rejection. WOA's of 32-taps and greater are easily managed by the TCSP.

An architecture that could efficiently perform filter banks such as this has several applications in radar, software radio, and even image processing.

Figure 37.0 1024 Point FFT with Hamming Window Bin Frequency Response

Using the TCSP simulator for the four tap WOA=4 case. This time we use the on chip ARM accelerated by the rFPGA to quickly calculate a Remez filter impulse response to be used in place of the window function.

Using the Remez exchange algorithm to calculate the coefficients, we can specify the stop band suppression and the width of the main lobe, as shown in Figure 38.0.

Notice this time we get -85 dB of side lobe suppression, and a fat main lobe all but filling the bin.

This response would be good for applications like software radio, and transmultiplexers that want very little cross talk between channels and flat response within the channel.

The TCSP platform can generate these impulse responses concurrently and on "the fly" as it configures itself for a wide range of filter bank requirements.

Figure 38.0 FFT with Remez Filter coefficients in place of the window function

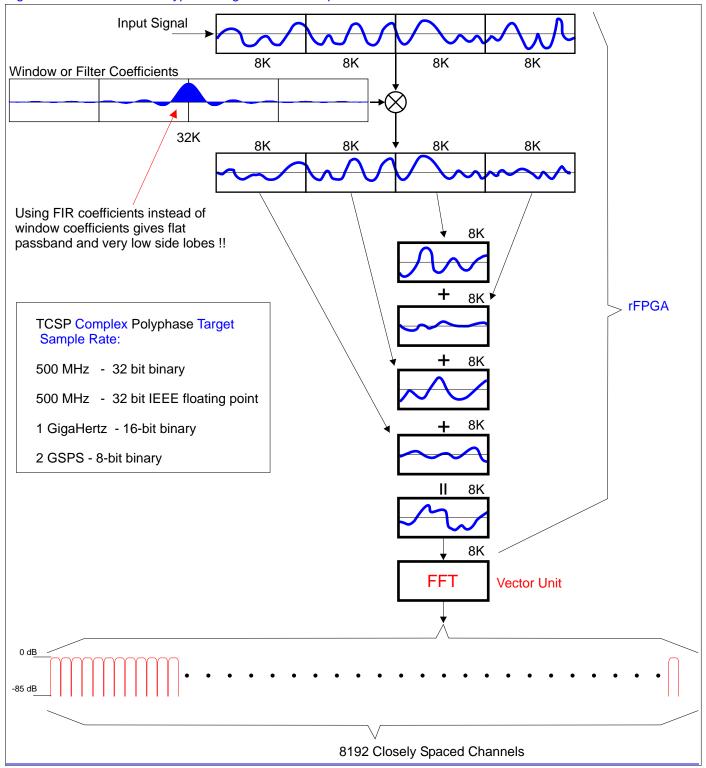

Figure 39.0 illustrates the actual polyphase application ran using the TCSP simulator. The weighted overlap add section before the FFT is performed by the FPGA fabric. The 8K channel channelizer as shown here can be performed by one TCSP chip. With the addition of just external memory, channelizers of 64K and beyond are possible, with 32-bit binary accuracy.

Figure 39.0 8K Channel Polyphase Digital Filter Example

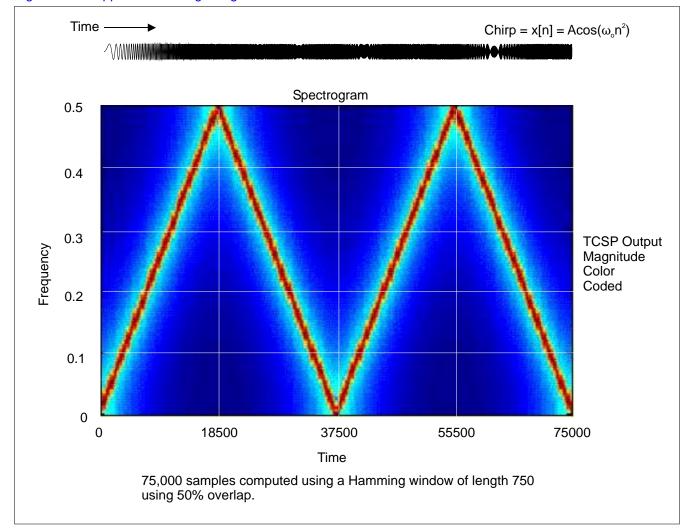

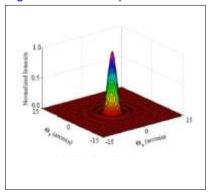

The TCSP simulator was applied to Radar Doppler processing as illustrated below in Figure 40.0, the Short Time Fourier Transform (STFT) takes a Radar chirp time domain signal (B), multiplies it against the sliding Hamming window (A), for a windowed result (C). (C) is then Fourier transformed using the FFT.

Hamming Α  $x[n] = A\cos(\omega_0 n^2)$ В 0 375 750 1125 1500 1875 2250 2625 3000 Hamming •  $x[n] = A\cos(\omega_0 n^2)$ С  $A \times B = C$ C → FFT

Figure 40.0 Doppler Processing using the Short Time Fourier Transform (STFT)

To process the full 75,000 tome domain samples, 200, 750 point real FFT's are performed, with 50% overlap.

Using the TCSP, a Radix-256 followed by a radix-3 = 768 a point transform.

Table 1.0 Short Time Fourier Transform (STFT) Execution Times

| One TCSP Chip                                              | Two cascaded TCSP chips                          |  |  |

|------------------------------------------------------------|--------------------------------------------------|--|--|

| 300 MHz                                                    | 300 MHz                                          |  |  |

| 768 points x 3.33 nSec x 200 slides x 2 passes = 1022 μsec | 768 points x 3.33 nSec x 200 slides = 511.4 µsec |  |  |

| 500 MHz                                                    | 500 MHz                                          |  |  |

| 768 points x 2 nSec x 200 slides x 2 passes = 614.4 µsec   | 768 points x 2 nSec x 200 slides = 307 µsec      |  |  |

Note: If final chip runs faster these execution times scale directly.

Table 1.0 gives the execution times for a 300 MHz TCSP chip and a 500 MHz TCSP chip. Notice that the window function (Hamming in this case) is free, it is included in the first pass of the TCSP's FFT calculation. Also, the 750 points are zero padded out to 768 points. That's just 18 points added to the 750 samples, as opposed to the 256 points that would have to be added, had we not had the Radix-3 structure.

Also note, that there is a small (>1%) performance latency penalty for waiting for the one chip solution above to turn wait for the pipeline to finish, before turning around. This penalty is small because of the TCSP's ability to stack, this will be discussed further in Objective (13.).

Figure 41.0 Doppler Processing using the STFT - Results

The 200 FFT's are performed and plotted as shown above in Figure 41.0.

In this case a narrow-band spectrogram is computed using a relatively long window of 768 samples. This gives us good frequency resolution as a shown.

For better time resolution, a shorter window would be used, say 250 samples. Also, the overlapping can be changes from the shown 50% to say 30% or less.

The point to be made here is that the TCSP with its wealth of radices, especially the odd radices, gives you many choices to optimize the performance per watt of the Doppler processing.

Additionally, this Doppler processing was done with the TCSP's 32-bit block data type. With this kind of full speed precision the most minute Doppler profile would show up quickly.

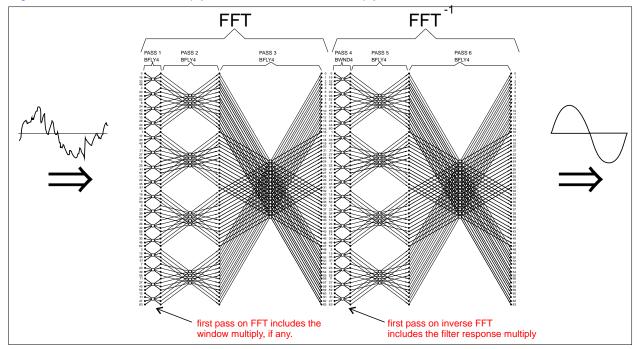

A key requirement for any Radar system is the fast calculation of the matched filtering section. Figure 42.0 illustrates a 4K Radar matched filter.

This was extensively simulated with the TCSP simulator, and a single chip TCSP can perform this function in just 4096 x 2 passes for the forward FFT, and 4096 x 2 passes for the inverse FFT.

Since the window multiply is free on the first pass of the TCSP's FFT, and the coefficient multiply on the inverse FFT is free, the approximate number of clocks is 4096x2x2= 16K clocks.

Running at 500 MHz, that's a sustained sample rate of 250 MSPS for 16-bit data, with one TCSP. Two TCSP's back to back would do the complete matched filter at a 500 MSPS rate. In fact, two TCSP's back to back, with no external componets, could do a 64K fast convolution matched filter at a 500 MSPS rate, with two full rFPGA's and plenty of on chip memory left over for other calculations concurrently.

Again, if this algorithm is needed, but at 100 MSPS instead of 500 MSPS, then an 80% power reduction can be realized by lowering the chip clock by 80%, then quickly increasing the clock for some other algorithm, if needed.

COMPRESSED ANALOG OUTPUT UNCOMPRESSED ANALOG INPUT LFM time History Compressed Pulse 50 **4K POINTS** 30 IFFT 20 Matched Filter F(k) MEMORY 1.5 x 10 REFERENCE WAVEFORM

Figure 42.0 Illustration of Frequency Domain Pulse Compression

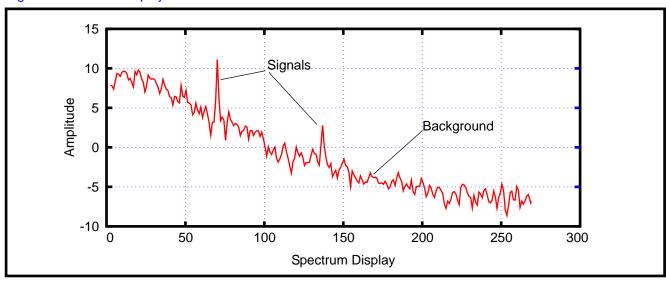

Figure 43.0 Radar Display

A typical radar output report may look something like Figure 43.0, two signal peaks in the present of constantly changing background noise.

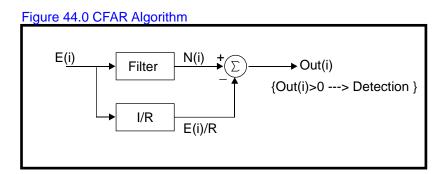

In this example the CFAR circuitry as shown in Figure 44.0 will trigger an event when the two signal shown exceed a set threshold above the background noise.

N(i)

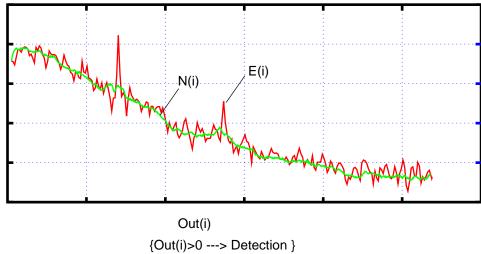

Figure 45.0 Realtime Fast Convolution Filter Output

Figure 45.0 shows the actual result of the fast convolution, the output of the filter N(i), the background noise.

Figure 46.0 overlays the filter output on the original input E(i). Notice how the signals rise above filtered the noise.

Figure 46.0 Filter Output on Top Of Input Signal

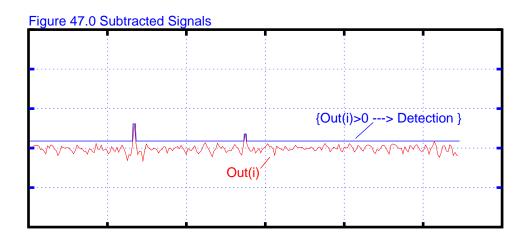

Finally, Figure 47.0 shows the output of the filter subtracted from the background noise, Out(i).

And the blue line shows the detection where the signals exceed the threshold.

To give you an indication of the predicted performance of the proposed TCSP chip:

There are 10 passes (program lines) to this application, each pass is made up of 4096 clocks

$4096 \times 10 = 40960$  total clocks for the complete algorithm.

If the TCSP runs at 300 MHz, then  $40960 \times (1/300 \text{MHz}) = 136.5 \text{ uSec}$ .

And if we use the Radix-256 pass followed by a Radix-16 pass, this reduces the 10 passes to 8, thereby:

4096 x 8 = 32768 clock x (1/300 MHz)= 109.2 uSec.

Additionally, the subtract for many channels could easily be done by the on-chip rFPGA for even more performance.

Figure 48.0 Two dimensional CFAR Realtime Filter

#### The Two-Dimensional Case

The CFAR algorithm can appear as a two-dimension problem. For example, a waterfall display, where the spectrum as a function of time, is presented to the operator to increase the detection probability. Another example is a acoustic emission "crack" detection system. In the two-dimensional case, the background level is estimated by averaging over a two dimensional window around the point of interest that excludes the very close neighbors of that point. The design of the averaging window is application specific, it usually resembles a spectrum-waterfall display, where the system looks for a verticle line on the display. A typical averaging window is illustrated in Figure 48.0. As in the one-dimensional case the noise estimation is a convolution operation between the two-dimensional input and the two-dimensional window function. Basically the algorithm is -1 the same as the one-dimensional case, with the FFT being two-dimensional.

The method for performing a two-dimensional FFT using the TCSP was explained and coded eariler. Basically, the two-dimensional transform can be performed as a one dimensional transform with a length of NxM, and with proper MMU addressing. In this case the TCSP can easily perform the 4096 x 4096. The transform length is 16 meg. Therefore, the optimal radix is  $(256 \times 256)$  x  $(256 \times 256)$ .

Note: The new Radix-3 and Radix-5 will pay big dividends in selecting "non-power of two" 2-D or 3-D sizes.

Figure 49.0 Sampled Image

A truely flexable DSP processor needs to excell at 2-D and 3-D image processing. Modern survailance systems and fast seekers need the autonomy and added capability of on board image processing.

The TCSP simulator shows that the TCSP can perform signal algorithms and image algorithms interactively. This efficient switching between one, two, and three dimensions goes a long ways towards making this architecture cost effective across a wide class of satellite and weapon system applications.

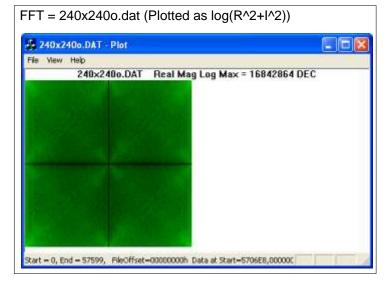

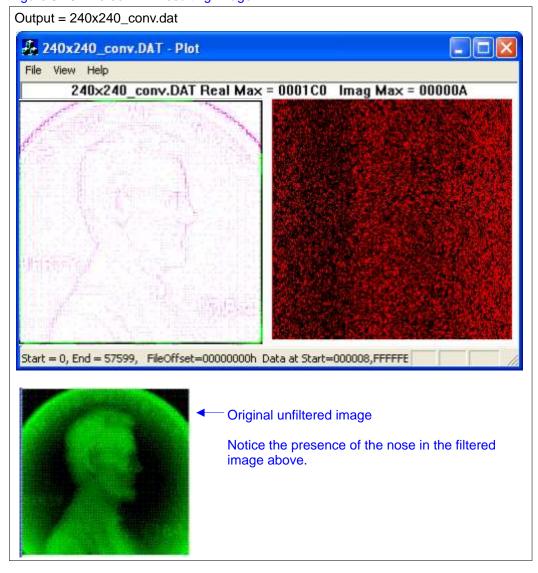

Consider the sampled image in Figure 49.0, a 240 x 240 digital camera photograph.

The TCSP code listed in Table 2.0 transforms this picture to the frequency domain as shown in Figure 50.0.

Notice now that unlike signal processing we have gone from something recognizable, to something chaotic. Whereas with the 1-D signal, it was the frequency domain that had nice coherent patterns.

This added dimension has complicated our architecture. If we want to use the same chip for all three dimensions, the third being moving 2-D images. Then a lot of thought needs to go into how we process massive amounts of data quickly and comprehensively.

The TCSP and its simple register programming handles the corner turning, digit reverse, process gain normalizing, pattern recognition, etc. fast and efficiently.

Figure 50.0 Image PSD

The results of this code indicate that the new mixed butterfly (MXBFx) and mixed twiddle factor( MXTFx) address functions and the new BFLY3 and BFLY5 DSP functions mesh well together and mesh well with the existing base address and DSP functions to provide an extensible integrated mixed and split radix signal processing environment.

Figure 51.0 Inverse FFT Resulting Image

Figure 51.0 shows the inverse FFT of the transformed picture, the TCSP transformed this image in one pass per line, that's 256 x 256 (zero padded out to 256) or 64K clocks. All the corner turning and data management was handled by the internal MMU's through simple and fast register programming. The MMU's registers are shadowed so they can be changes while being used. The MMU's could have managed thousands of these images at once.

The high pass filter of this image gives the edges, again the multiply against the high pass coefficients on the inverse transform is free, just as the input window function was.

As will be shown later in this section, involved blind deconvolution image processing will be performed by the TCSP. Blind deconvolution could go a long ways towards removing unwanted Radar clutter.

Table 2.0 contains the simple register programming to do sophisticated 2-D and 3-D image fast convolution.

### Table 2.0 Simple. Quick Register Programming for 2-D and 3-D Image and Signal Processing

```

Perform a 256 x 256 point 2-D, in place, transform in two seperate steps

Transform rows

transform columns