# NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

# THESIS

# NETWORK PROCESSORS AND UTILIZING THEIR FEATURES IN A MULTICAST DESIGN

by

Timur DILER

March 2004

Thesis Advisor: Thesis Co-Advisor: Su WEN Jon BUTLER

Approved for public release; distribution is unlimited

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   | Form Approved                                                                                                                                            | d OMB No. 0704-0188                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| searching existing data sources, gat<br>comments regarding this burden est<br>Washington headquarters Services, I                                                                                                                                            | ection of information is estimated to av-<br>hering and maintaining the data needec<br>imate or any other aspect of this collec<br>Directorate for Information Operations a<br>nagement and Budget, Paperwork Redu                                                                                                                                              | d, and completing a<br>tion of information,<br>nd Reports, 1215 Jef                                                                                               | nd reviewing the co<br>including suggestic<br>ferson Davis Highw                                                                                         | ollection of information. Send<br>ons for reducing this burden, to<br>way, Suite 1204, Arlington, VA                                                                                                                       |

| 1. AGENCY USE ONLY (Leav                                                                                                                                                                                                                                     | <i>e blank</i> ) <b>2. REPORT 1</b><br>March 20                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   | REPORT TYPE<br>VERED<br>Maste                                                                                                                            | AND DATES                                                                                                                                                                                                                  |

| 4. TITLE AND SUBTITLE:                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   | 5. FUNDING N                                                                                                                                             |                                                                                                                                                                                                                            |

| Network Processors and Utiliz                                                                                                                                                                                                                                | ng their                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| Features in a Multicast Design                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| 6. AUTHOR(S)<br>Timur DILER                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   | 8. PERFORMI<br>REPORT NUN                                                                                                                                | ING ORGANIZATION<br>/IBER                                                                                                                                                                                                  |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SP                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          | ING/MONITORING<br>EPORT NUMBER                                                                                                                                                                                             |

| <b>11. SUPPLEMENTARY NOTI</b> of the Department of Defense or the                                                                                                                                                                                            | <b>ES</b> The views expressed in this thesis a U.S. Government.                                                                                                                                                                                                                                                                                                 | are those of the auth                                                                                                                                             | or and do not reflec                                                                                                                                     | t the official policy or position                                                                                                                                                                                          |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT   12b. DISTRIBUTION CODE                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| Approved for public release; distribution is unlimited                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| 13. ABSTRACT (maximum 20                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          |                                                                                                                                                                                                                            |

| to the customization and per<br>router, which receives incom<br>sors and the associated softw<br>such as multicasting forward<br>focusing on the Intel IXP12<br>posed.This thesis presents an<br>layer-3 forwarder microACE<br>tecture and its active comput | ements of the rapidly growing In<br>formance needs of networking<br>ing packets and directs them to a<br>are control the routers and switch<br>der and firewalls quickly. This t<br>200 network processor. A mult<br>a approach to building a multice<br>that carries out unicast routing.<br>ing element (ACE). The layer-3<br>oftware modules, called micoble | systems. An in<br>specific routes en-<br>ches and allow se-<br>thesis introduces<br>icast design for<br>asting forwarder.<br>The design is ba-<br>unicast forward | aportant comportant<br>lsewhere in the<br>oftware designer<br>network proce<br>the IXP1200 or<br>r using the IXP<br>used on the Intel<br>ler microACE is | nent in a network is the<br>system. Network proces-<br>rs to deploy new systems<br>ssors and their features,<br>using microACE is pro-<br>1200 network processor<br>Internet exchange archi-<br>s used as a basic starting |

|                                                                                                                                                                                                                                                              | croace, network processors, Intel IX                                                                                                                                                                                                                                                                                                                            | XA, microengine                                                                                                                                                   |                                                                                                                                                          | PAGES 74                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                                          | <b>16. PRICE CODE</b>                                                                                                                                                                                                      |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT                                                                                                                                                                                                                  | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE                                                                                                                                                                                                                                                                                                                  | 19. SECU<br>CLASSIF<br>ABSTRA                                                                                                                                     | ICATION OF                                                                                                                                               | 20. LIMITATION OF<br>ABSTRACT                                                                                                                                                                                              |

| Unclassified                                                                                                                                                                                                                                                 | Unclassified                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                   | classified                                                                                                                                               | UL                                                                                                                                                                                                                         |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   | Standard Form 298                                                                                                                                        | 8 (Rev. 2-89)                                                                                                                                                                                                              |

Prescribed by ANSI Std. 239-18

Approved for public release; distribution is unlimited

#### NETWORK PROCESSORS AND UTILIZING THEIR FEATURES IN A MULTICAST DESIGN

Timur DILER Lieutenant Junior Grade, Turkish NAVY B.S., Turkish Naval Academy, 1998

Submitted in partial fulfillment of the requirements for the degrees of

## MASTER OF SCIENCE IN COMPUTER SCIENCE and MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

### NAVAL POSTGRADUATE SCHOOL March 2004

Author:

Timur Diler

Approved by: Su Wen Thesis Advisor

> Jon Butler Thesis Co-Advisor

John P. Powers Chairman, Department of Electrical and Computer Engineering

Peter Denning Chairman, Department of Computer Science

## ABSTRACT

In order to address the requirements of the rapidly growing Internet, network processors have emerged as the solution to the customization and performance needs of networking systems. An important component in a network is the router, which receives incoming packets and directs them to specific routers elsewhere in the system. Network processors and the associated software control the routers and switches and allow software designers to quickly deploy new systems such as multicasting forwarders and firewalls.

This thesis introduces network processors and their features, focusing on the Intel IXP1200 network processor. A multicast design for the IXP1200 using microACE is proposed.

This thesis presents an approach to building a multicasting forwarder using the IXP1200 network processor layer -3 forwarder microACE that carries out unicast routing. The design is based on the Intel Internet exchange architecture and its active computing element (ACE). The layer -3 unicast forwarder microACE is used as a basic starting point for the design. Software modules, called micoblocks, are developed to create a multicast forwarder that is flexible and efficient.

# **TABLE OF CONTENTS**

| I.   | INTR  | <b>ODUCTION</b> 1                             |

|------|-------|-----------------------------------------------|

|      | А.    | BACKGROUND 1                                  |

|      | В.    | THESIS PROBLEM STATEMENT                      |

|      | C.    | THESIS OVERVIEW 2                             |

| II.  | NETV  | VORK PROCESSORS 5                             |

|      | A.    | INTRODUCTION                                  |

|      | В.    | THE EVALUATION OF THE NETWORK PROCESSORS 5    |

|      |       | 1. First-Generation Systems                   |

|      |       | 2. Second-Generation Systems                  |

|      |       | 3. Third-Generation Systems                   |

|      | C.    | FEATURES OF NETWORK PROCESSORS                |

|      |       | 1. Flexibility with Programmability           |

|      |       | 2. Scalability 10                             |

|      |       | 3. Pipelined Processing 11                    |

|      |       | 4. Parallel Processing 12                     |

|      |       | 5. Memory Management 13                       |

|      | D.    | INTEL EXCHANGE ARCHITECTURE 14                |

|      |       | 1.         Data Plane         15              |

|      |       | 2. Control Plane 15                           |

|      |       | 3.         Management Plane         15        |

|      | Е.    | SUMMARY 15                                    |

| III. | INT   | EL IXP1200 ARHITECTURE                        |

|      | А.    | INTRODUCTION                                  |

|      | B.    | OVERVIEW OF IXP1200 17                        |

|      | C.    | IXP1200 COMPONENTS 18                         |

|      |       | 1. StrongARM Core 18                          |

|      |       | 2. MicroEngines 19                            |

|      |       | 3. SRAM and Internal SRAM Interface Unit 24   |

|      |       | 4. SDRAM and Internal SDRAM Interface Unit 25 |

|      |       | 5. PCI Unit 25                                |

|      | D.    | SUMMARY 25                                    |

| IV.  | IXP12 | 200 PROGRAMMING AND MICROACE STRUCTURE 27     |

|      | А.    | INTRODUCTION                                  |

|      | B.    | IXP1200 PROGRAMMING 27                        |

|      |       | 1. Software Development Kit 28                |

|      |       | 2. Instruction Set 29                         |

|      |       | 3. MicroEngine Assembly Syntax 31             |

|       |        | 4. Simple Packet Data Flow in IXP1200 33      |

|-------|--------|-----------------------------------------------|

|       | C.     | ACE PROGRAMMING MODEL 34                      |

|       |        | 1. IXA Application Programming Interface      |

|       |        | 2. Active Computing Element 35                |

|       |        | 3. MicroACE 36                                |

|       |        | 4. An Example of MicroACE Processing 37       |

|       |        | 5. The Dispatch Loop 38                       |

|       | D.     | SUMMARY                                       |

| V.    | A MU   | LTICASTING FORWARDER DESIGN USING MICROACE 41 |

|       | А.     | INTRODUCTION                                  |

|       | В.     | MULTICASTING FROM UNICAST FORWARDING 41       |

|       | С.     | MULTICASTING FORWARDER MICROACE 43            |

|       | D.     | SUMMARY                                       |

| VI.   | CONO   | CLUSIONS AND RECOMMENDATIONS 51               |

| LIST  | OF RE  | FERENCES                                      |

| INITI | AL DIS | STRIBUTION LIST                               |

# LIST OF FIGURES

| Figure 1.  | Software-Based Architecture.                     | 6  |

|------------|--------------------------------------------------|----|

| Figure 2.  | Scalability Achievement.                         | 11 |

| Figure 3.  | Parallelism in the IXP1200 NPU.                  | 13 |

| Figure 4.  | IXP1200 Block Diagram (From Ref. 9.).            | 18 |

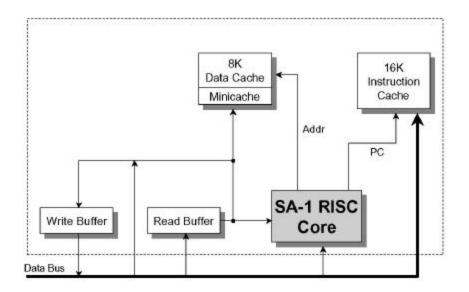

| Figure 5.  | StrongARM Block Diagram (After Ref. 9.).         | 19 |

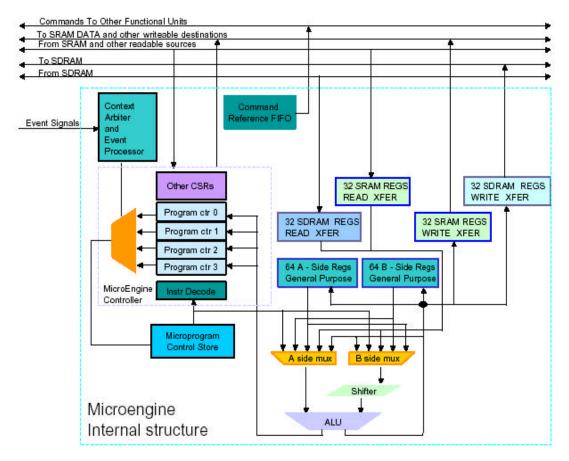

| Figure 6.  | MicroEngine Internal Structure (From Ref. 9.).   | 20 |

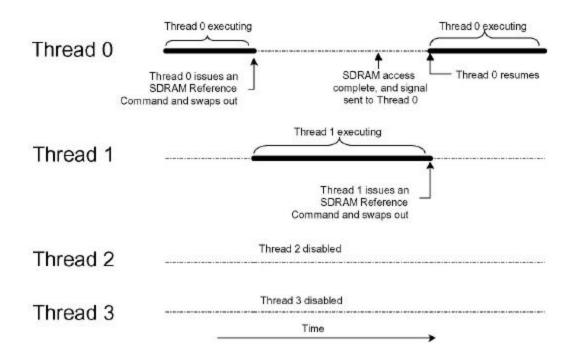

| Figure 7.  | Thread Context Swapping (From Ref. 9.).          |    |

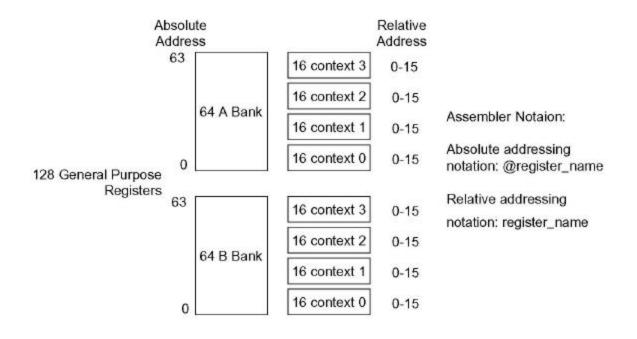

| Figure 8.  | GPR Addressing (From Ref. 9.).                   | 23 |

| Figure 9.  | Transfer Reg. Addressing (From Ref. 9.).         |    |

| Figure 10. | IXP1200 Macro Example (From Ref. 18.).           |    |

| Figure 11. | Simple Data Flow Hardware (From Ref. 9.)         |    |

| Figure 12. | Packet Flow (From Ref. 16.).                     | 35 |

| Figure 13. | MicroACE App. Using Pseudo-code (From Ref. 17.). | 37 |

| Figure 14. | IP Forwarding MicroACE (After Ref. 2,16.)        |    |

| Figure 15. | Dispatch Loop (From Ref. 2,17.).                 | 39 |

| Figure 16. | Basic Multicasting System                        | 42 |

| Figure 17. | Multicasting MicroACE (After Ref.2,16.)          | 45 |

| Figure 18. | Multicasting MicroACE Algorithm.                 | 46 |

| Figure 19. | Initialization Routine                           | 48 |

|            |                                                  |    |

# LIST OF TABLES

| Table 1. | Internet Growth Trends (From Ref. 1.)                  | 1  |

|----------|--------------------------------------------------------|----|

| Table 2. | MicroEngine Execution Pipeline (From Ref. 9.).         | 12 |

| Table 3. | IXP1200 SDK Items (From Ref. 2.).                      |    |

| Table 4. | MicroEngine Basic Inst. Set (From Ref. 15.).           |    |

| Table 5. | Manual Register Assignment Directives (After Ref. 15.) |    |

| Table 6. | Register Addressing (After Ref. 2,15.).                |    |

| Table 7. | Data Flow Steps (After Ref. 9.).                       |    |

| Table 8. | Multicast Identifier Examples.                         |    |

|          | 1.                                                     |    |

# ACKNOWLEDGMENTS

I would like to thank to my thesis advisors Prof. Su Wen and Prof. Jon Butler for their suggestions and advice during the development of this thesis.

I also would like to thank my Computer Science professors and Electrical and Computer Engineering professors, Prof. Jon Butler, Prof. Hersch Loomis and Prof. Douglas Fouts who made me enthusiastic about computer engineering again.

Special thanks to my wife and my daughter, for the sacrifices they made in support of my completing this thesis in their time.

This thesis is dedicated to my wife, Munevver Diler and my daughter Yagmur Diler.

## **EXECUTIVE SUMMARY**

The main goal of this thesis was to design a multicasting forwarder using Intel Internet exchange architecture and the IXP1200 network processor. The combat system computers on warships are connected to each other with a network to respond any attack immediately. The sensors and the weapons of the ships communicate with each other by using this network. The communication between systems must be lightweight to increase the respond time. This thesis can be used in these systems to eliminate network overheads. The sensors can send the information packets to control consoles by using unicast based multicasting to eliminate network overhead.

Originally, conventional CPU-based systems were used to build networking systems (routers and switches). They had sufficient computing capacity to handle the network requirements. Around 1990, the Internet begun to become a global network, and CPU-based systems could no longer handle the Internet applications requirements because of demand for wide bandwidth and high packet processing rates. In the middle of 1990, the application specific integrated circuit (ASIC) was introduced to address new requirements. ASIC is an integrated circuit with networking functions built- in permanently. ASICs are fast and have a high packet processing rate. However, since functions are permanently built into ASIC, they cannot be easily modified. As the number and variety of Internet applications grew, new networking functions were needed. It is very expensive and time consuming to design and produce new ASICs. This is one of the main reasons network processors were introduced. Network processors are processors that are designed for network processing and have special features to handle the high packet rate, new networking functions, and new services.

Network processors are fully programmable processors. This makes them flexible enough to address new application needs in a short time. They use parallelism and pipelining to increase the throughput and support high packet processing rates.

Intel designed and produced Internet Exchange Architecture (IXA) and its IXPxxxx family network processors. IXP1200 is one of them. Internet Exchange Architecture introduced the programming model Active Computing Element (ACE) to modularize network processor programming. The IXP1200 has six hardware multithreading RISC MicroEngines, and one StrongARM core RISC processor. Microengines and StrongARM work in parallel using a 5-stage pipelining execution queue.

Intel provides the IXP systems with a hardware testbed and platforms to help designers evaluate their applications. The Software Development Kit (SDK) is one of these platforms. SDK includes sample applications and library codes to help the designer.

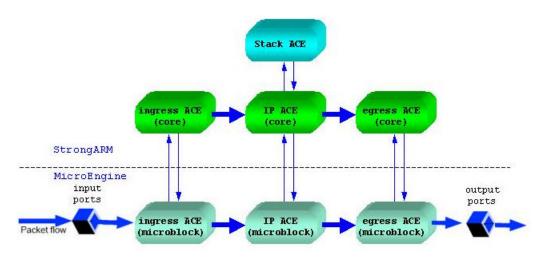

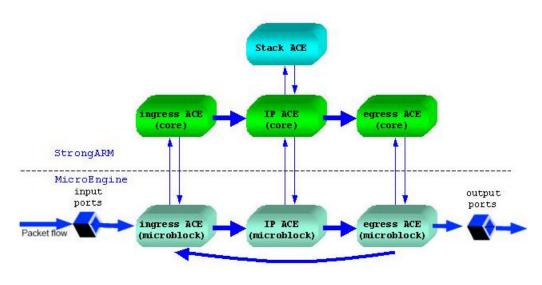

The ACE software programming structure divides the tasks performed by an IXPbased system and allows each task to be handled by a module. MicroACE has two components, microblocks which run in MicroEngines and a core component, which runs in the StrongARM core processor. Microblocks handle the common packets and provide a fast data path. If they encounter a packet requiring special handling, they pass it to the core component.

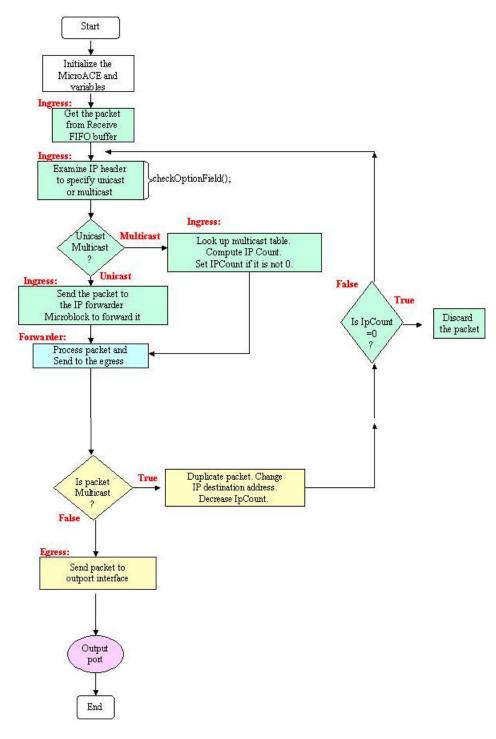

The multicast forwarder, simply a router that also performs multicast forwarding, forwards each packet to one or more receivers. This thesis investigates a unicast-based design that provides multicast service using the existing unicast forwarder. It is an effective and flexible methodology because the system does not require additional routing protocols or another routing algorithm. End hosts in the network are responsible for multicast state maintenance.

# I. INTRODUCTION

#### A. BACKGROUND

The Internet has improved the quality of our lives. It has made it more convenient to do our jobs, to communicate with each other, to shop, to conduct research and a host of other tasks. Today, the Internet is everywhere. Even the telephone system is changing from the old dedicated analog transmission system to voice-IP technology over the Internet. Military applications use computer network systems to communicate in the battle-field. On warships, data from the sensors can be used as input to weapon systems. This combination can be is achieved using a computer network. A sensor must send its information to the control consoles of the combat information center to decide about the threats. Our unicast-based multicast design can be used in the warship combat systems as multicasting forwarder. It provides effective and reliable way to deliver information to the consoles.

| Year:   | Number of Hosts on Internet: |

|---------|------------------------------|

| 1977    | 111                          |

| 1981    | 213                          |

| 1983    | 562                          |

| 1984    | 1,000                        |

| 1986    | 5,000                        |

| 1989    | 100,000                      |

| 1992    | 1,000,000                    |

| 2001    | 150 – 175 million            |

| 2002    | Over 200 million             |

| By 2010 | About 80% of the planet      |

The Internet grew rapidly especially after 1990, and it is still growing. Table 1 shows the growth of the Internet as measured by the total number of hosts.

Table 1.Internet Growth Trends (From Ref. 1.).

Since the number of hosts on the Internet is growing, applications and services also are being developed. These growing applications and services require high bandwidth to work reliably.

Networking technology has an important role in supporting this growth. Protocol systems, transmission media, processing systems like routers, switches, and bridges are the main components of computer networking.

To handle the huge demand on the Internet, networks must be fast, reliable, and flexible. As a result, processors used in networking hardware have evolved from general CPU to specialized packet handling type Network Processor Units that are faster and optimized for moving data.

#### **B.** THESIS PROBLEM STATEMENT

The main goal of this thesis was to propose a design of multicasting forwarding service that uses the existing IXP1200 ACE programming design module. To support the multicast design, this thesis explores the network processor and its features, and investigates the Intel IXP1200 network processor and its ACE programming model.

#### C. THESIS OVERVIEW

Chapter II examines network processors. First, it introduces the evaluation of the network processors. Second, it gives the features of network processors that must address the high bandwidth requirement. Third, it presents the Intel Internet Exchange Architecture technology.

Chapter III describes the hardware and the architectural concepts of the Intel network processor IXP1200. It explains the external and internal blocks of the IXP1200 and introduces the concepts of hardware multithreading, memory management, and interconnection between blocks.

Chapter IV explores the software component of the IXP1200. It explains the programming structure and models of IXP1200, including the software development kit, IXA application-programming interface, and the advanced programming model, the active computing element. Chapter V provides our design for a multicasting forwarder. Our methodology is done by modifying the layer-3 unicast forwarder microACE. The microACE of the unicast forwarder includes three main microblocks. We modify the ingress and egress microblocks to duplicate specific packets effectively converting from a unicast mode to a multicast mode.

The last chapter discusses the conclusions and recommendations for future work.

## II. NETWORK PROCESSORS

#### A. INTRODUCTION

Communication over the Internet is built on packet switching. The processing of packets is the main job of the network systems such as switches and routers [2]. These network systems examine each packet, and then decide what to do with them. Typically, this decision depends on the headers of the packets. They can be forwarded to interfaces of the system or returned to the sender as an error message.

The functions and the services that the network system provides depend on the architecture of the network system processor.

Bandwidth is important and critical to network applications. Because emerging Internet applications increase the network traffic, it is pushing the limit of the capacity of communication lines and semiconductor technologies. Therefore, network equipment providers are searching for better technologies and methods to handle, support and manage the traffic.

Network processors present a solution, which can help maximize bandwidth utilization and traffic flow [3,4]. Network processors are becoming the main component in the network systems to meet the new bandwidth, speed, and performance requirements.

A network processor, unlike the conventional computer processor unit (CPU), combines hardware functional units with software, and is designed and highly optimized to perform network functions [2,3,4]. For high bandwidth and performance, parallelism and pipelining are used in the design of Network Processors.

This chapter examines the features of Network Processors, focusing on the system processor IXP1200 in the INTEL Network Processor Architecture.

#### **B.** THE EVALUATION OF THE NETWORK PROCESSORS

Over the last 15 years, network systems especially router architectures, have evolved through three generations, each marked by improvements in packet processing mechanisms.

#### 1. First-Generation Systems

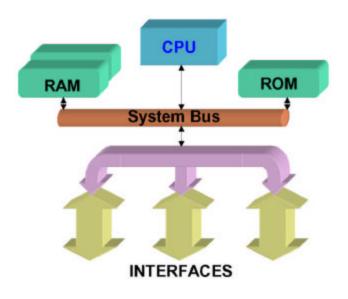

Up to the mid 1990's, router architecture was similar to the conventional PC systems. Figure 1 illustrates a CPU that performs networking functions, controlled by the router's operating system. Like conventional PCs, the router's operating system resides in the system's volatile memory in RAM and controls all the system's functions and services.

Figure 1. Software-Based Architecture.

In such a system, all tasks are controlled and performed by software, and routers built in this system are called software-based routers. Because routing is software-based, adding new functions and services to the router can be done by simply changing or adding new instructions to the software [2,3,4].

It is good for the vendors because it does not take much time to change or upgrade the router's software. They could quickly develop new or special purpose products within a short time.

The Cisco 2500 Router is an example of a software-based router (Figure 1). Cisco 2500 uses its Central Processor Unit to execute and conduct its routing instructions stored in nonvolatile RAM.

As Networking technology and applications changed, the drawback of this system became apparent. Software-based architectures had a limited ability to scale to higher bandwidth demands and new routing services [4]. For example, the majority of softwarebased routers can only support wire speed throughput for less than 155 Mbps [4]. When you want to make them perform complex networking functions, like filtering, policybased routing, and examining traffic statistics, the throughput of software-based routers is reduced. This creates a bottleneck in the network [4].

Networking technology was constantly developing, but software-based architecture could not keep up with the bandwidth demand and started to suffer in performance. In addition, maintaining this architecture became very expensive.

#### 2. Second-Generation Systems

After the mid 1990s, companies started to find new solutions to support high bandwidth and fast processing networking systems. Vendors used Application Specific Integrated Circuits (ASIC) and combined them with embedded Reduced Instruction Set Computer (RISC) processors yielding greater speed and performance. Companies that built high-speed network systems started to hire VLSI design engineers to design ASICs for their systems and products [2].

ASIC-based forwarding and switching have resulted in a new generation of very high-speed routers and switches. ASIC is an integrated circuit manufactured with embedded instructions to perform specific functions. The functions are programmed in silicon hardware permanently. So, for ASIC, since there is no memory instruction fetch cycle, it is significantly faster than software-based systems. It works at wire speed. That is, in the software-based architecture, the CPU must make memory accesses to execute instructions, and memory accesses take too much time compared with the execution time of ASICs.

With ASICs, manufacturers improved the performance by creating special chips that could do packet forwarding directly in the hardware. These chips make decisions about packet forwarding and, when packets need special treatment, they are forwarded to the RISC processor for special treatment. With very high packet forwarding speeds (approximately tens of millions of packets/second), routers became very inexpensive. They

7

became common in academic and industrial networks [2,4]. Now, one can buy sophisticated routers for \$100 or less.

ASIC technology became very popular because it can process packets at wire speed. But, after several years, its drawbacks started to be understood. ASICs are created by designing and fabricating networking functions into silicon permanently. In the meantime, Internet applications are becoming more complex. Thus, they need still more functionality. Some of those applications, such as Firewall Capability (stateful firewalls), Virtual Private Networks (VPN), and Quality of Service (QoS) implementation demand new processing capability from the network hardware [6].

To add a new function to an ASIC, you have to design and produce it from the beginning. This procedure takes from several months to two years. ASIC can be designed for several different functions, but since those functions are embedded into silicon, add-ing new functions, or designing new ASICs are very expensive and time consuming [6].

To summarize, ASICs have numerous disadvantages: They are costly, require much time to market, and exhibit difficulties in simulation, design, and modification [2].

#### 3. Third-Generation Systems

Network systems vendors can no longer afford to wait as long as two years designing and developing ASICs for an application. The network requirements could change during the development of a special purpose ASIC, and a lot of effort and money could be wasted [7].

The solution is Network Processors. Network Processors were introduced in the market in the late 1990s. Network Processors combine two approaches, hardware structure (about as fast as ASIC) and software that makes the system flexible.

Network processors are not for a special application. A vendor can produce different systems with different network functions with only one type of network processor. Today, designers can build a layer-3 unicast router; tomorrow designers can build a stateful firewall. Applications that are overwhelming for ASICs, because of the complex functionality, are implemented with network processors, such as Virtual Private Networks, firewalls, and Quality of Service mechanisms. These functions require more scalability, flexibility, and programmability. These features are implemented with parallelism and pipelining and are discussed in detail in the next section.

#### C. FEATURES OF NETWORK PROCESSORS

Network Processors brought new concepts and new technologies to networking systems. In this section, the INTEL IXP1200 Network Processor will illustrate the features of network processors in general. The IXP1200 has StrongARM, a core RISC processor, 6 pipelined Multithreaded (4 threads for each Microengine) RISC-type Microengines for packet processing, SDRAM to store packet data, SRAM to store packet headers and variables, and system buses to establish communications between the units.

#### **1.** Flexibility with Programmability

Internet technology and applications are changing every day. New network systems must be adapted to new protocols, functions and services at low cost. Unlike ASICs, Network Processors are not limited to a particular layer stack or a protocol.

Flexibility of network processors arises from programmability [2]. With frequently changing network requirements and standards, programmability is an important characteristic of network processors. Rather than designing and producing a new chip like ASIC, one can design and create systems for new protocols or applications by only developing new algorithms and implementing them in programs.

Programmability allows designers to reuse the components and programs for different versions of protocols. System software tools designed for network processors shorten the development time for a system. Tools allow extensive testing capabilities with intelligent debugging features [4] with real-world conditions.

The flexibility of Network Processors means one can develop any network system with a network processor for any network protocol or services by just programming the network processor. Network processors yield low cost, reduce the development cycle, and allow programs to be reused.

The flexibility of network processors also means new chips may allow system designers perform tasks that people never imagined before [6]. Network Processors let designers handle complex functions and edge systems, like quality of service implementation and firewall mechanisms.

Also vendors are not stuck with only switches and routers. With the Network Processor, they can design and manufacture new systems.

#### 2. Scalability

Scalability is an important issue for Computer Engineering. Processors and chips must handle the growing load demand by new applications and services. VLSI silicon systems have working limits, such as a maximum clock rate and latency. These conditions allow processors and chips to handle a limited amount of load for network systems packets.

With an increasing number of packets to be processed, systems must be scalable enough to handle that amount of packet load. It must have the ability to scale high data and packet rates. Responding each time by making faster processors for new systems is difficult and costly.

Instead of using faster processors for scalability, designers used parallelism, pipelining, and memory management to achieve scalability for network processors. These features are keys to scale high packet rates. Figure 2 shows simple internal structure of the IXP1200 to illustrate parallelism, pipelining, and memory management.

Figure 2. Scalability Achievement.

#### **3.** Pipelined Processing

Pipelining is one method of achieving scalability. With pipelining, instead of making processors faster, more instructions are executed with the same clock frequency.

The main goal of pipelining is to keep processors as busy as possible. Without pipelining, instructions are executed one-by-one. Instructions wait for completion of previous instruction execution cycle. Pipelining allows several instructions to be issued per clock cycle instead just one [8].

Pipelining increases throughput, at the expense of latency [8]. Latency in pipelined architecture is larger because every instruction must pass through all stages. If there are five stages, every stage block has a separate register block. At any time, several instructions are in the execution queue, having just completed some stages of their execution cycle, and waiting to pop from the queue. Unfortunately, dependencies among instructions in a pipeline can be cause delay. For example, there is branch delay for branch instructions. Branch delay is discussed in the next chapter. The six RISC MicroEngines in IXP1200 have five stage-pipelined structure. Table 2 shows each stage and its functionality. This allows all instructions to execute in one clock cycle [9].

| Pipeline Stage | Description                                                                |

|----------------|----------------------------------------------------------------------------|

| PO             | Lookup of instruction                                                      |

| P1             | Initial instruction decode and formation of the source register<br>address |

| P2             | Reads operand from source registers                                        |

| P3             | Perform ALU, shift, or compare operations and generate the condition codes |

| P4             | Write result to the destination register                                   |

Table 2.

MicroEngine Execution Pipeline (From Ref. 9.).

For Table 2, in stage P0, the instruction is fetched from the instruction store. In P1, the instruction is decoded and the operation to be performed is determined. In P2, the operands of the instruction are read from registers. In P3, operands are passed through the ALU [9]. In P4, the result from the fourth stage is written to the destination registers.

This design allows a complete instruction to be executed each clock cycle, except for branch instructions.

#### 4. Parallel Processing

Network processors employ more than one MicroEngine RISC processor in parallel to increase the packet rate. At any point in time, every RISC inside of the Network Processor can be computing a different networking function.

There must be a control mechanism to control the synchronization and communications between the RISCs. It can be another RISC processor or a simple control unit. The functions of each parallel processor can be determined by programming the network processor. Since the various RISCs process packets at the same time, this increases the packet rate.

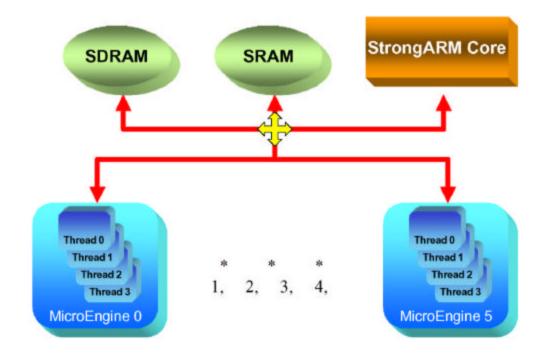

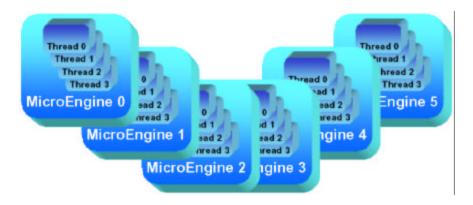

Intel's Network architecture uses this concept. The IXP1200 network processor has six RISC processors or MicroEngines (Figure 3) that can run in parallel. Each MicroEngine has four separate threads running in the MicroEngine concurrently. When a thread in a MicroEngine processes an instruction to access memory, it can permit another thread to run, while the previous thread performs its memory access.

Every MicroEngine has a separate program counter for each thread. One can partition memory into blocks for each thread or let them share memory with each other.

As shown in Figure 3, an IXP1200 Network Processor actually has six Microengines and each of these has four separate threads, and so it can have a total of 24 different threads in parallel. This approach allows the IXP1200 to handle high data rates.

Figure 3. Parallelism in the IXP1200 NPU.

#### 5. Memory Management

The most time-consuming process in computing is memory access. Reading and writing or transferring data from memory takes more time than most other processing jobs.

SRAM has low latency, but its cost is very high. SDRAM is cheaper than SRAM, but it has higher latency. Therefore, a trade-off between latency and cost must be considered when designing a new chip. As shown in Figure 2, the INTEL IXP1200 has 8 Mbytes SRAM and 256 Mbytes SDRAM. It uses SRAM to store the routing table for lookups where low latency is important, and SDRAM to store packet data, payload, or very large tables where latency is not important [9].

As mentioned in the previous section, while a thread in the same Microengine executes a memory reference command, the MicroEngine can swap threads that are ready to process. So, no one has to wait for a memory cycle to be completed. Therefore, a process does not have to be blocked while waiting for memory access to be completed. This eliminates the unused time frames. It keeps the Network Processors busy as much as possible.

#### D. INTEL EXCHANGE ARCHITECTURE

Networks and Internet have become a core component of daily operations [10]. The applications are getting bigger and more complex. The Intel Internet Exchange Architecture was designed to address the new application requirements.

IXA has all the features of the network processors mentioned in the previous section. The programmability and high packet rate performance allow systems to be developed in a short time.

There are four important features of the IXA [11]:

- Flexibility,

- High Performance (ability to process high packet and data rates),

- Scalability, and

- Software Portability.

To meet these requirements, Intel created the Intel IXPxxxx series Network Processors and Intel software portability framework. They are the components of the Intel Internet Exchange Architecture (IXA) [11].

There are three basic task levels in the IXA software architecture [10].

#### 1. Data Plane

The data plane takes care of packet processing. The forwarding of incoming packets is done at high speed. The data plane receives packets from a network interface, makes a classification, and determines the required action. Rules determine which action is taken on the packet.

The data plane handles the fast data path and is controlled by the MicroEngines.

#### 2. Control Plane

This part of the IXA application is the controller. It handles the time-consuming and complex tasks that are encountered while packet processing [11].

The control plane is implemented in the StrongARM core component. When the data plane encounters an unexpected packet or a packet that does not have any forward-ing table entry, it passes that packet to the control plane where that packet is processed.

#### 3. Management Plane

The management plane performs the managing functions. It is a manager program at the top of the hierarchy. The manager can be an application off the chip or a Linux application running on the chip [11]. The management program of the IXA application is part of the main system, and can have a user interface to interact with the user.

#### E. SUMMARY

Network systems, such as routers and switches, started as conventional central processing units. They have a CPU, RAM and ROM to store the operating system and interfaces to connect to the network. At the beginning, their performance was sufficient. With the rapid growth of the Internet and applications, they became a bottleneck. They could not reach the required speed for packet throughput.

To solve this bottleneck, ASIC was introduced. ASIC is an integrated circuit designed to perform the networking functions at wire speed. The networking functions are designed into silicon hardware permanently. ASIC played an important role in network systems. After different Internet and networking applications were introduced, the drawbacks of ASICs became apparent. Designing and producing ASICs to address the requirements of a new application was very expensive and time consuming. Finally, vendors introduced network processors. Network processors are now in every networking system. They contain more than one RISC processor to increase the packet processing performance using parallelism and pipelining, and they are programmable. This allows software reusability, and the product can be produced quickly.

Intel introduced its Internet Exchange Architecture for networking systems. With IXA, Intel designed IX technologies, which included the IXPxxxx network processor family and the ACE programming structure.

IXP1200 is one of the Intel's network processors. The next chapter examines the IXP1200 hardware and its concepts. IXP1200 has six multithreaded programmable RISC MicroEngines, StrongARM core processor, memory interfaces and buses.

## III. INTEL IXP1200 ARHITECTURE

#### A. INTRODUCTION

The previous chapter described the main concepts of network processors, including which features they have to address new bandwidth requirements.

Network processor functions are managed through system software; therefore, they provide the programmability and reusability features of software together with highperformance processing of the hardware in aiding system design. As a result, network processors enable designers to design and to manufacture more intelligent and compact network systems. Intel's network processor is part of their Internet Exchange Architecture. The IXPxxxx is a family of network processors produced by Intel. Currently, the second-generation IXP2xxx network processors are being developed.

The IXP1200 is one of the first network processors of the Intel IXA technology. This chapter presents an in-depth examination of Intel's IXP1200 structure and concepts with hardware.

Because of the complexity of Intel processors, some internal units unrelated to this thesis will not be discussed.

#### B. OVERVIEW OF IXP1200

IXP1200 addresses the requirements of today's networking technology. To achieve high-speed data manipulation, and high packet rate, the IXP1200 includes programmability, pipelining, parallel processing, and memory management. These give the IXP1200 flexibility, scalability, high performance, and low power consumption [9].

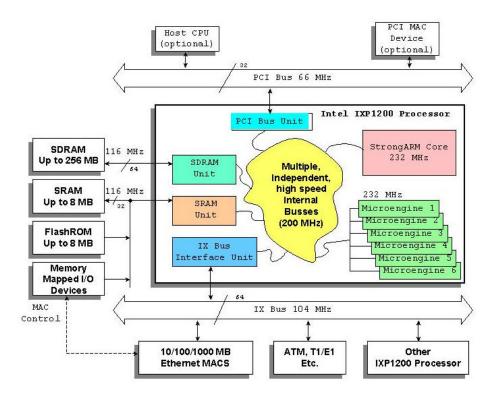

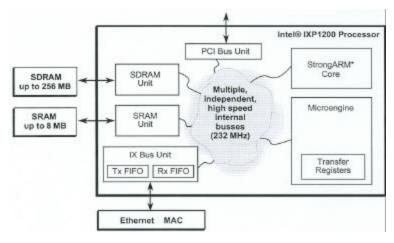

Figure 4 shows the internal blocks, the external, and internal interfaces of IXP1200. The IXP1200 contains one RISC StrongARM core processor, six multithreaded programmable RISC MicroEngines, memory interfaces, and system bus interfaces.

Figure 4. IXP1200 Block Diagram (From Ref. 9.).

Unlike ASICs, the IXP1200 allows the implementation of networking systems with software without considering the hardware structure. Within the software development environment, it is easy to develop, debug, and modify networking systems.

## C. IXP1200 COMPONENTS

#### 1. Strong ARM Core

The StrongARM is a 32-bit RISC microprocessor. It runs at 232 MHz. The StrongARM RISC core is a 5-stage pipelined processor. Figure 5 shows that it has 16 Kbytes of instruction cache, and 8 Kbytes of data cache. It also has 512 bytes of mini-cache to decrease transfers to and from the main data cache.

Figure 5. StrongARM Block Diagram (After Ref. 9.).

Depending on the system architecture, StrongARM may or may not be used. If the system has a main host CPU, the host CPU can maintain the system, upload the software, and operate the system. The StrongARM can do the exception handling and be the higher layer processor [9]. The StrongARM leaves the packet forwarding to the Micro-Engines, but runs the routing protocols. It controls the IXP1200 system, MicroEngines and interfaces between components. If there is not any host CPU, StrongARM can assume the role of a host processor and perform system maintenance.

#### 2. MicroEngines

IXP1200 contains six 32-bit multithreaded RISC Microengines. The Microengines can handle packet processing at a high rate. The six MicroEngines run in parallel to increase the total throughput of the system. The Microengines are fully programmable.

The MicroEngines, shown in Figure 6, have four hardware threads. Each of them has its own Program Counter to execute different instruction parts of the MicroEngine.

Figure 6. MicroEngine Internal Structure (From Ref. 9.).

The MicroEngines operate at 233 MHz. They are implemented as a 5-stage pipelined RISC processor. This pipelined structure makes the IXP1200 faster and scalable to higher rates in the future. A non-pipelined architecture would execute an instruction with, for example, five clock cycles. However, because of pipelining, the IXP1200 executes an instruction in each clock cycle. Table 1 in Chapter 1 shows the IXP1200 pipelined execution stages.

Branch instructions are a problem with pipelining architectures [7,8]. The instructions after the branch instruction may have already been inside the pipelining queue stages with their operands, but if the branch is taken, execution of these instructions will have to be aborted, consuming extra time and sacrificing performance. There are several solutions for this problem. The instructions can be pushed into a pipelining queue with the probability of not executing the branch instruction. By putting bubbles after the branch instructions, this problem can be solved, but this reduces the performance of the MicroEngine. Bubbles are no operation instructions. Instead of doing this, instructions before the branch would be put after the branch to maintain performance [9]. The instructions before the branch will be executed anyway whether the branch is taken or not. Another solution is using the guess-branch-taken instruction. When the guess-branch-taken instruction is used, the instruction at the branch destination will be started [9].

While a processor executes instructions, memory accesses consume a lot of time. To reduce this problem, the IXP1200 has several memory access reduction features.

The first is to store instructions in a separate memory near the MicroEngine. This special memory stores 1K x 32 bits instructions. Each instruction is 32 bits long.

The second feature is hardware thread context swapping. The IXP1200 has 8 Mbytes of SRAM, and 256 Mbytes of SDRAM. SRAM is used to store table lookups where low latency is an important issue [9]. SDRAM is used to store packet data, payload, and very large tables where latency is not very an important issue [9]. To access data that is external to the Microengine, like SRAM or SDRAM, the Microengine executes memory access and transaction commands. These commands are called Reference Commands.

Every MicroEngine has four hardware threads (Figure 7). Each thread has its own program counter. Four threads can be executing the same code or different code pieces of the MicroEngine's instruction store at any one time.

Figure 7. Thread Context Swapping (From Ref. 9.).

When Thread 0 executes a reference command to access memory, the Microengine does not wait for that thread to complete its memory access. The control unit gives execution priority to the other thread, Thread 1, and the Thread 0 swaps out. Thread 0 goes to sleep until Thread 1 completes its cycle. This is called Hardware Multithreading. There is a difference between hardware and software threading. With hardware threading each thread has its own program counter, register and memory block, if relative addressing is used. With software threading, there is only one program counter and register set. The operating system makes all threads of processes share execution time according to priorities. In the IXP1200, all multithreading coordination and context swapping are handled by hardware only. The programmer need not worry about programming the threads. In software threading, all thread processing is coordinated by the operating system.

Every MicroEngine has 256 32-bit registers. Of these 128 are general purpose registers (GPR) and the other 128 are transfer registers.

The MicroEngines use two types of addressing of registers, context relative addressing and absolute addressing. With context relative addressing, each thread in the same Microengine uses its registers block. It is assured that none of the threads overwrites another's registers. GPRs and transfer registers are divided into equal size blocks for each thread. If one or more threads require sharing some registers or communicating with each other, absolute addressing is used. With absolute addressing, the threads do not have to go beyond the MicroEngine to communicate with each other. Relative and absolute addressing is controlled on an instruction-by-instruction basis [9].

General-purpose registers are divided into two banks, the A bank and the B bank. This structure allows the IXP1200 to fetch two separate operands in the same clock cycle (one from SRAM and one from SDRAM). Each bank supports a port and a write port as shown in Figure 8.

Figure 8. GPR Addressing (From Ref. 9.).

GPRs are divided into four logical register regions. Each region has 32 registers. This structure eliminates the overhead of switching among threads [9]. Absolute addressing in GPRs allows sharing registers between threads in a MicroEngine. Each MicroEngine has 128 32-bit transfer registers (Figure 9). Transfer registers are intended for transferring data to and from memory components.

|                           | ddress                                                    |                                                                                                                                                    | Relative<br>Address                                  |                                                                                                  |

|---------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 128 Transfer<br>Registers | 31<br>32<br>SRAM Read<br>0<br>31<br>32<br>SRAM Write<br>0 | 8 context 3<br>8 context 3 | 0-7<br>0-7<br>0-7<br>0-7<br>0-7<br>0-7<br>0-7<br>0-7 | Assembler Notaion:<br>Absolute addressing notation:<br>@\$sram_xfer_name<br>@\$\$sdram_xfer_name |

|                           | 31<br>32<br>SDRAM Read<br>0                               | 8 context 3<br>8 context 3<br>8 context 3<br>8 context 3                                                                                           | 0-7<br>0-7<br>0-7<br>0-7                             | Relative addressing notation:<br>\$sram_xfer_name<br>\$\$sdram_xfer_name                         |

|                           | 31<br>SDRAM Write                                         | 8 context 3<br>8 context 3<br>8 context 3<br>8 context 3                                                                                           | 0-7<br>0-7<br>0-7<br>0-7                             |                                                                                                  |

Figure 9. Transfer Register Addressing (From Ref. 9.).

As shown in Figure 9, transfer registers are divided into two-memory type blocks. Sixty-four SDRAM transfer registers and sixty-four SRAM transfer registers are connected to the SRAM/SDRAM memory busses. The two blocks are divided into 32 read and write registers blocks.

#### **3.** SRAM and Internal SRAM Interface Unit

The IXP1200 has 8 Mbytes of SRAM to quickly store any data needed, such as lookup tables, free buffer lists, and data buffer queue. It is important to lookup these data with low latency. For example, in a routing table, the lookup table must be done quickly. This is because all processing depends on that lookup. So, lookup tables are stored in SRAM because SRAM is faster than SDRAM. While the lookup tables are stored in SRAM, SDRAM is for a large data structure like a Routing Table. The SRAM interface is 32 bits wide. It supports either pipelined or flow-through SRAMs. Recall that SRAM is not for bulk data, rather, it is used for fast access.

#### 4. SDRAM and Internal SDRAM Interface Unit

The IXP1200 has 256 Mbytes of SDRAM to store bulk data like routing tables. The SDRAM unit, like a SRAM unit takes Reference Commands from the MicroEngines and StrongARM and fetches data in an optimal fashion. The SDRAM has a 64-bit data bus and a 14-bit address bus.

### 5. PCI Unit

The PCI Unit is a standard 32-bit PCI 2.1 interface. It can run at 33 MHz with the standard number of loads [9]. It also runs at 66 MHz with a point-to-point configuration [9].

The main purpose of the PCI Unit is to communicate with the host system and make the IXP1200 reachable by the user who can modify it.

#### D. SUMMARY

The IXP1200 addressed current networking requirements. It succeeded in this by using parallelism, pipelining and programmability. To manage these features, the IXP1200 network processor contains six hardware multithreading RISC MicroEngines, one core StrongARM processor, memory interfaces and fast data buses. The MicroEngines work in parallel, and every one of them is a 5-stage pipeling RISC processor.

Each MicroEngine contains four hardware threads with separate program counters for each thread. Multi-threading allows each MicroEngine to increase its performance by not wasting time while waiting for memory access instructions.

Common packets are handled by MicroEngines while exception packets are handled by StrongARM, because MicroEngines perform fast data processing. Exceptions reduce the performance of the system. So, exceptions are handled by the StrongARM core processor.

Every MicroEngine and StrongARM is a programmable processor. The next chapter explains programming of the IXP1200. First, the basic programming concepts and structures are introduced. Second, advanced programming models, such as IXA API, and ACE, are explained. THIS PAGE INTENTIONALLY LEFT BLANK

## IV. IXP1200 PROGRAMMING AND MICROACE STRUCTURE

#### A. INTRODUCTION

In this chapter, the software of the IXP1200 network processor will be explained. This chapter includes two sections, IXP1200 programming and the MicroACE structure. In the first section, the IXP1200 Software Development Kit, instructions and programming structures such as assembly directives and macro will be explained. In the second section, advanced IXP1200 programming and MicroACE structure will be discussed.

Network processors are software-based processors. The functions and services depend on the program written for that processor. The software-based approach provides reusability, low-cost, rapid production, and easy maintenance. Each processor has its own assembly language programming structure, and concepts.

Network processor vendors offer a reference platform or an evaluation testbed [2]. These platforms help designers to produce, test, and evaluate their software and hardware implementations before adapting a network processor into a new network system. A reference platform includes the following five items [2]:

- Hardware testbed

- Development software

- Simulator and emulator

- Download and bootstrap software

- Reference implementations

With these tools, designers can write, test, simulate, and run the software without a current network system. Development software includes libraries and some sample codes to help the designer create his own code.

#### B. IXP1200 PROGRAMMING

#### 1. Software Development Kit

The Intel Corporation also provides a reference platform for its network processors [2,13]. This platform is divided into two sub-systems, a hardware testbed and a Software Development Kit (SDK) [2,13].

The hardware testbed is a PCI card that can be plugged into the PCI bus of a PC. The card has four 100-Mbps ports. After the software is written and tested with the IPX1200 SDK, it can be downloaded into the hardware testbed and run.

With an average personal computer and an IXP1200 hardware testbed, an inexpensive router can be built that forwards minimum-sized packets at a rate of 3.47 Mbps [14].

The Intel IXP1200 SDK has some software components to support IXP1200 software development. These components are shown in Table 3.

| Software                                               | Purpose                                                                          |

|--------------------------------------------------------|----------------------------------------------------------------------------------|

| C complier                                             | Compile C programs for the StrongARM                                             |

| Network Classification<br>Language (NCL) com-<br>plier | Compile NCL programs for the StrongARM                                           |

| MicroC complier                                        | Compile C programs for the MicroEngines                                          |

| Assembler                                              | Assemble programs for the MicroEngines                                           |

| Simulator                                              | Simulate an IXP1200 code to debug                                                |

| Downloader                                             | Load software into the network processor                                         |

| Monitor                                                | Communicate with the network processor and interact with running software        |

| Bootstrap                                              | Start the network processor running                                              |

| Reference Code                                         | Example programs for the IXP1200 that show how to imple-<br>ment basic functions |

Table 3. IXP1200 SDK Items (From Ref. 2.).

To work with this system, two operating systems are needed. Linux runs on the StrongARM, and Windows NT runs on the MicroEngines [2,16]. One does not need two separate PCs to work two operating systems. One main operating system and one emulator program that runs inside the main are sufficient to work with the SDK. For example, the main system can be Linux. For the secondary system a Windows emulator such as Wine can be used [2].

#### 2. Instruction Set

Because each IXP1200 MicroEngine is a RISC processor, it has few basic opcodes; the MicroEngine instruction set has 32 basic opcodes (Table 4) [15]. All instructions are 32-bits in length.

| Instruction                                                                   | Description                               |  |

|-------------------------------------------------------------------------------|-------------------------------------------|--|

| Arithmetic, Rotate, And Shift Instructions                                    |                                           |  |

| ALU                                                                           | Perform an arithmetic operation           |  |

| ALU_SHF                                                                       | Perform an arithmetic operation and shift |  |

| DBL SHIFT                                                                     | Concatenate and shift two longwords       |  |

| Branch and Ju                                                                 | mp Instructions                           |  |

| BR, BR=O, BR!=O, BR>O, BR>=O, BR <o,<br>BR&lt;=O, BR=count, BR!=count</o,<br> | Branch or branch conditional              |  |

| BR_BSET, BR_BCLR                                                              | Branch if bit set or clear                |  |

| BR=BYTE, BR!=BYTE                                                             | Branch if byte equal or not equal         |  |