# PICORADIO: COMMUNICATION/COMPUTATION PICONODES FOR SENSOR NETWORKS

Jan Rabaey et al.

University of California at Berkeley Berkeley Wireless Research Center 2108 Allston Way, Suite 200 Berkeley, CA 94704-1698

**2 January 2003**

**Final Report**

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED.

AIR FORCE RESEARCH LABORATORY Space Vehicles Directorate 3550 Aberdeen Ave SE AIR FORCE MATERIEL COMMAND KIRTLAND AIR FORCE BASE, NM 87117-5776

| REPORT DOCUM                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |                                            |                                                                    | Form Approved OMB No. 0704-0188                                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| Public reporting burder for this collection of information is estibated to average 1 hour p<br>and reviewing this collection of information. Send comments regarding this burden estin<br>Headquarters Services, Directorate for Information Operations and Reports (0704-0188),<br>law, no person shall be subject to any penalty for failing to comply with a collection of ir | nate or any other aspect of this collection<br>, 1215 Jefferson Davis Highway, Suite 12 | of information, incl<br>204, Arlington, VA | luding suggestions for reducing 22202-4302. Respondents sho        | g this burder to Department of Defense, Washington<br>uld be aware that notwithstanding any other provision of |  |

| 1. REPORT DATE (DD-MM-YYYY) 2. RE                                                                                                                                                                                                                                                                                                                                                | EPORT TYPE                                                                              |                                            | 3. DATES (                                                         | COVERED (FROM - TO)                                                                                            |  |

| 02-01-2003                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |                                            | xx-07-1999                                                         | to xx-12-2002                                                                                                  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |                                            | 5a. CONTRACT                                                       | NUMBER                                                                                                         |  |

| PICORADIO: COMMUNICATION/COMPUTATION                                                                                                                                                                                                                                                                                                                                             | ON PICONODES FOR S                                                                      | ENSOR                                      | 5b. GRANT NUMBER                                                   |                                                                                                                |  |

| NETWORKS                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |                                            |                                                                    | ELEMENT NUMBER                                                                                                 |  |

| Unclassified                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |                                            | 20. T 10 G10 H/1 I                                                 | SEELVIEI (1 1 (OVIEE)                                                                                          |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |                                            | 5d. PROJECT NI                                                     | UMBER                                                                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |                                            | 5e. TASK NUMI                                                      | BER                                                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |                                            | 5f. WORK UNIT                                                      | NUMBER                                                                                                         |  |

| 7. PERFORMING ORGANIZATION NAME AND University of California at Berkeley Berkeley Wireless Research Center 2108 Allston Way, Suite 200 Berkeley, CA94704-1698                                                                                                                                                                                                                    | ADDRESS                                                                                 |                                            | 8. PERFORMING<br>NUMBER                                            | G ORGANIZATION REPORT                                                                                          |  |

| 9. SPONSORING/MONITORING AGENCY NAME                                                                                                                                                                                                                                                                                                                                             | E AND ADDRESS                                                                           |                                            | 10. SPONSOR/M                                                      | IONITOR'S ACRONYM(S)                                                                                           |  |

| ,                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |                                            |                                                                    | IONITOR'S REPORT                                                                                               |  |

| 12. DISTRIBUTION/AVAILABILITY STATEMEN<br>APUBLIC RELEASE<br>,                                                                                                                                                                                                                                                                                                                   | ΥT                                                                                      |                                            |                                                                    |                                                                                                                |  |

| 13. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |                                            |                                                                    |                                                                                                                |  |

| 14. ABSTRACT refer to atch                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |                                            |                                                                    |                                                                                                                |  |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |                                            |                                                                    |                                                                                                                |  |

| 16. SECURITY CLASSIFICATION OF:                                                                                                                                                                                                                                                                                                                                                  | OF ABSTRACT N<br>Public Release C                                                       | NUMBER                                     | 19. NAME OF R<br>Mosher, Jan<br>Janet.Mosher@                      | ESPONSIBLE PERSON kirtland.af.mil                                                                              |  |

| a. REPORT  b. ABSTRACT  c. THIS PAGE  <br>Unclassified  Unclassified  Unclassified                                                                                                                                                                                                                                                                                               |                                                                                         |                                            | 19b. TELEPHOI<br>International Area C<br>Area Code Telephor<br>DSN | ode<br>ne Number                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |                                            |                                                                    | Standard Form 298 (Rev. 8-98)<br>Prescribed by ANSI Std Z39.18                                                 |  |

#### AFRL-VS-TR-2003-1013

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data, does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report has been reviewed by the Public Affairs Office and is releasable to the National Technology Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nationals.

If you change your address, wish to be removed from this mailing list, or your organization no longer employs the addressee, please notify AFRL/VSSE, 3550 Aberdeen Ave SE, Kirtland AFB, NM 87117-5776.

Do not return copies of this report unless contractual obligations or notice on a specific document requires its return.

This report has been approved for publication.

AMES LYKE

Project Manager

KIRT S. MOSER, DK-IV

Chief, Spacecraft Technology Division

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing this collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE (DD-MM-YYYY)                                                         | 2. REPORT TYPE                    | 3. DATES COVERED (From - To)     |

|-------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|

| 02-01-2003                                                                          | Final Report                      | July 1999 - December 2002        |

| 4. TITLE AND SUBTITLE                                                               |                                   | 5a. CONTRACT NUMBER              |

| Picoradio: Communication/                                                           | Computation PicoNodes f           | or Sensor F29601-99-1-0169       |

| Networks                                                                            |                                   |                                  |

|                                                                                     |                                   | 5b. GRANT NUMBER                 |

|                                                                                     |                                   |                                  |

|                                                                                     |                                   | 5c. PROGRAM ELEMENT NUMBER       |

|                                                                                     |                                   | 62301E                           |

| 6. AUTHOR(S)                                                                        |                                   | 5d. PROJECT NUMBER               |

| Jan Rabaey, Robert Broderson, Kanr                                                  |                                   |                                  |

| Ammer, Fred Burghardt, Rong Chen,                                                   |                                   |                                  |

| Karalar. Garv Kelson. Mika Kuusula.                                                 |                                   |                                  |

| Michael Montero, Dan Odell, Brian Otis, Huifnag Qin, Johnathan Reason, Shad Roundy, |                                   | ·                                |

| Ulrich Schuster, Marco Sgroi, Rahul S                                               | Shah, Michael Sheets, Mei Xu, Cl  | arlie Zhong AA                   |

| 7. PERFORMING ORGANIZATION NAME                                                     | 8. PERFORMING ORGANIZATION REPORT |                                  |

|                                                                                     |                                   | NUMBER                           |

| University of California a                                                          |                                   |                                  |

| Berkeley Wireless Research                                                          |                                   |                                  |

| 2108 Allston Way, Suite 2                                                           | 00                                |                                  |

| Berkeley, CA 94704-1698                                                             |                                   |                                  |

| 9. SPONSORING / MONITORING AGENO                                                    | V NAME(S) AND ADDDESS(ES)         | 10. SPONSOR/MONITOR'S ACRONYM(S) |

| Air Force Research Laborat                                                          | ` ,                               | DARPA/IPTO                       |

| Space Vehicles Directorate                                                          | •                                 | , -                              |

|                                                                                     |                                   |                                  |

| 3550 Aberdeen Ave. SE                                                               | Arlington VA 2220                 | NUMBER(S)                        |

| Kirtland AFB, NM 87117-57                                                           | / 0                               | ``                               |

| 42 DISTRIBUTION / AVAIL ADJUTY STA                                                  |                                   | AFRL-VS-TR-2003-1013             |

#### 12. DISTRIBUTION / AVAILABILITY STATEMENT

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED.

#### 13. SUPPLEMENTARY NOTES

#### 14. ABSTRACT:

This project addressed the "system-on-a-chip" implementation of a PicoNode, which can provide all the communication, computation, and geolocation functions necessary for an adaptive distributed sensor-and-monitor network. The program embodied many key principles of DARPA's initiatives in advanced computing, including adaptive computing and power-awareness. The program explored three complete design cycles. Sixty units of PicoNode I (460mW, 18cu.in.) were built. The chip-set for PicoNode II was functionally demonstrated, and a test-board was constructed. At 15mW, the chipset of the second generation represented a 23X improvement over the first generation. Significant progress on the final generation was achieved, including an FPGA version and an energy scavenging power train. Project goals of the final system: 0.15 cu.in. (30X improvement) and 1 mW (460X improvement).

#### 15. SUBJECT TERMS

WIRELESS, POWER-AWARE, PICO-RADIO, PLUG-AND-PLAY, NETWORKED SENSORS

| 16. SECURITY CLASSIFICATION OF: |                             | 17. LIMITATION<br>OF ABSTRACT | 18. NUMBER<br>OF PAGES | 19a. NAME OF RESPONSIBLE PERSON James Lyke |                                                                   |

|---------------------------------|-----------------------------|-------------------------------|------------------------|--------------------------------------------|-------------------------------------------------------------------|

| a. REPORT<br>Unclassified       | b. ABSTRACT<br>Unclassified | c.THIS PAGE<br>Unclassified   | Unlimited              | 72                                         | <b>19b. TELEPHONE NUMBER</b> (include area code) ( 505 ) 846-5812 |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std. 239.18

## TABLE OF CONTENTS

| 1 | INT | RODU   | CTION       |                                                           | 1  |

|---|-----|--------|-------------|-----------------------------------------------------------|----|

|   | 1.A | Proje  | СТ ОВЈЕСТ   | IVE                                                       | 1  |

|   | 1.B | APPRO  | АСН         |                                                           | 1  |

|   | 1.C | RECEN  | т Ассомі    | PLISHMENTS                                                | 1  |

|   | 1.D | TECHN  | NOLOGY TR   | ANSFER                                                    | 3  |

| 2 | TEC | CHNICA | AL OVER     | VIEW                                                      | 4  |

|   | 2.A | PicoN  | ODE I - PIO | CORADIO TEST                                              | 4  |

|   |     | 2.A.1  | PicoRadi    | o Test Bed Hardware and Development System                | 4  |

|   |     |        | 2.A.1.1     | Architecture and implementation                           | 4  |

|   |     |        | 2.A.1.2     | Concurrent design of electrical and mechanical components | 6  |

|   |     | 2.A.2  | PicoNode    | e III implementation on test bed                          | 7  |

|   |     |        | 2.A.2.1     | Protocol integration                                      | 8  |

|   |     |        | 2.A.2.2     | Application layer                                         | 8  |

|   |     |        | 2.A.2.3     | Network layer                                             | 9  |

|   |     |        | 2.A.2.4     | Datalink layer                                            | 10 |

|   |     |        | 2.A.2.5     | Low-power features                                        | 11 |

|   |     |        | 2.A.2.6     | Design flow                                               | 11 |

|   |     |        | 2.A.2.7     | Network management and maintenance                        | 13 |

|   |     |        | 2.A.2.8     | PicoRadio Test Bed deployment                             | 17 |

|   |     |        | 2.A.2.9     | Graphical user interfaces                                 | 19 |

|   | 2.B | PICON  | ODE II - T  | WO-CHIP PICONODE IMPLEMENTATION                           | 21 |

|   |     | 2.B.1  | Basebana    | l processor (BBP)                                         | 22 |

|   |     |        | 2.B.1.1     | BBP design methodology                                    | 24 |

|   |     | 2.B.2  | Wireless    | protocol processor (WPP)                                  | 26 |

|   |     |        | 2.B.2.1     | WPP design methodology                                    | 29 |

|   |     | 2.B.3  | Testing a   | nd results                                                | 30 |

|   |     | 2.B.4  | Lessons l   | earned                                                    | 35 |

|   | 2.C | PicoN  | ODE III - U | LTRA-LOW POWER PICONODE                                   | 35 |

|   |     | 2.C.1  | Protocol    | stack for PicoRadios                                      | 35 |

|   |     |        | 2.C.1.1     | Low energy ad hoc networking for PicoRadio                | 35 |

|   |          | 2.C.1.2   | PicoNode MAC and topology control                                                                                      | 36  |

|---|----------|-----------|------------------------------------------------------------------------------------------------------------------------|-----|

|   |          | 2.C.1.3   | Design methodology for PicoRadio.                                                                                      | 39  |

|   | 2.C.2    | Positioni | ng algorithms                                                                                                          | 40  |

|   |          | 2.C.2.1   | Determining position using RF phase differences                                                                        | 40  |

|   |          | 2.C.2.2   | Localization in sensor networks                                                                                        | 40  |

|   | 2.C.3    | PicoNode  | e III implementation strategies                                                                                        | 42  |

|   |          | 2.C.3.1   | Low power operating system for wireless networks                                                                       | 42  |

|   |          | 2.C.3.2   | Leakage current management in deep sub-micron IC's                                                                     | 42  |

|   |          | 2.C.3.3   | PicoNode III system implementation                                                                                     | 43  |

|   |          | 2.C.3.4   | Algorithms and VLSI implementations of low power digital baseband timing recovery systems for wireless communications. | 45  |

|   |          | 2.C.3.5   | Summary of PicoNode III chip set implementation                                                                        | 46  |

|   |          | 2.C.3.6   | PicoRadio RF transceiver                                                                                               | 49  |

|   |          | 2.C.3.7   | Energy scavenging                                                                                                      | 57  |

| 3 | REFEREN  | CES       |                                                                                                                        | 60  |

| 4 | PUBLICAT | TIONS     |                                                                                                                        | 611 |

| 5 | DECREES  | AWARD     | FD                                                                                                                     | 611 |

# 1 INTRODUCTION

## 1.A PROJECT OBJECTIVE

The objective of this project is to develop a "systems-on-chip" implementation of a PicoNode, which can provide all the communication, computation, and geolocation functions necessary for an adaptive distributed sensor-and-monitor network. The monolithic integration of the communication and computation components will allow orders of magnitude reduction in cost, size, and power consumption of the distributed sensor nodes. The final node will occupy less than **0.15 inch**<sup>3</sup>, and will consume less than **1 mW**. The node will feature the necessary flexibility to support a highly adaptive and programmable wireless link, and the dynamic trading off between communication and computation, as necessitated by the varying costs of communication.

# 1.B APPROACH

The use of state-of-the-art CMOS technology and the most advanced system-on-a-chip design methodology enables the integration of all the communications and computation functions required between the antenna and the sensor for a distributed sensor network in a single chip, called a PicoNode. This includes the analog RF communication and sensor interface circuitry, localization, as well as digital computation implemented as a balanced mixture of programmable, reconfigurable and dedicated components. A 3-phase progression of prototype implementations will lead to the final single-chip PicoNode, each time reducing the size and power dissipation with approximately a factor 10. PicoNode I will be made out commercial off-the-shelf components (Year 1), PicoNode II is a multi-chip implementation, integrating the most energy consuming portions of the design (Year 2), while PicoNode III represents the fully integrated sensor and monitor node (Year 3).

A system design approach, which jointly optimizes the algorithmic research, the node architecture and hardware, and the software environment, will be used. This process exploits the close industry interactions of the Berkeley Wireless Research Center, which provide access to state-of-the-art design tools, methodologies, and fabrication technologies.

#### 1.C RECENT ACCOMPLISHMENTS

- 60 units of PicoNode I operational and in active use. Average power dissipation of 460 mW for a total node-size of 18 inch<sup>3</sup>.

- Multi-hop ad-hoc network (media access + network + application layer) running on PicoNode I test-bed. Lifetime of node: 26 hours

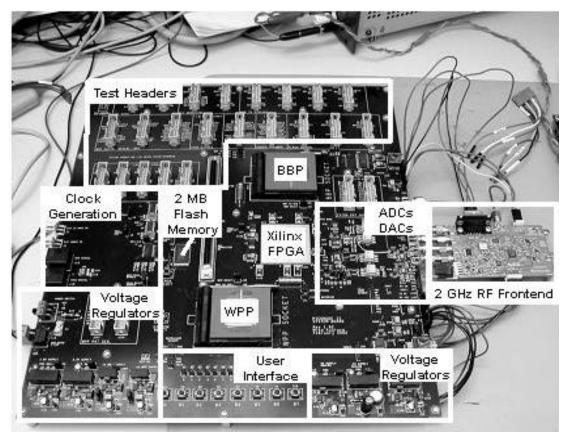

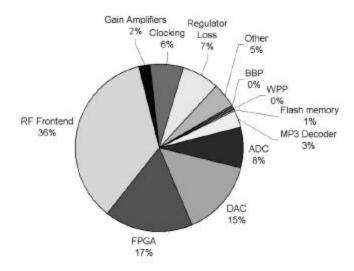

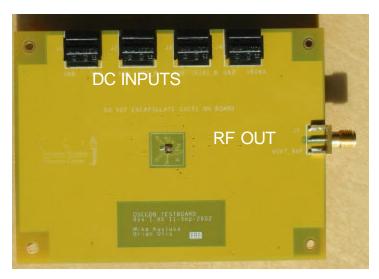

- Chip-set for PicoNode II completely functional. Both the protocol and baseband processor have been fabricated and tested. A test-board combining the two chips with an off-the-shelf RF front-end has been constructed and is operational, delivering a complete wireless transceiver solution. The peak power dissipation of the two digital chips is approximately 15 mW, which is below the estimated value of 20 mW. For the digital processing, this represents a reduction with a factor of 23 over PicoNode I.

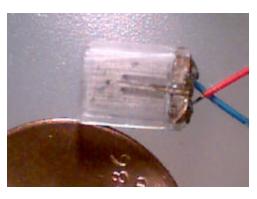

- PicoNode III: a <1mW, 0.6 inch<sup>3</sup> integrated wireless transceiver for wireless sensor network, powered by energy scavenging to be fully integrated and operational by the end of the project.

- ? The system-design of the node (component selection, partitioning, simulation) has been completed.

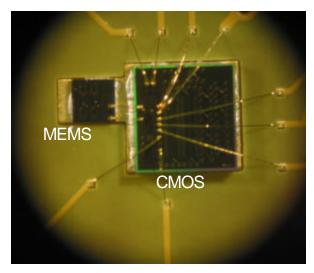

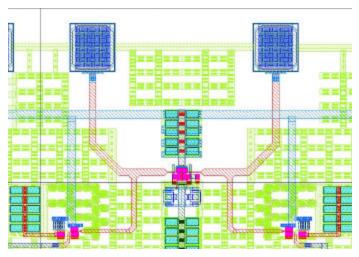

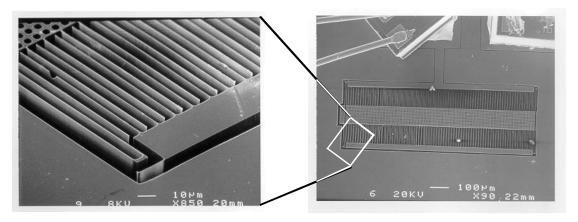

- ? An innovative low-energy front-end based on FBAR micro-resonators has been developed. Two test-chips have been designed, two of which have been tested. The operation of a complete radio chain has been demonstrated using a chip-on-board implementation. A fully integrated version is currently in fab and is expected back by late February.

- ? Behavioral specification of digital network processor (which combines the physical layer, data-link and multi-hop network protocols, localization, and application functions) is operational A full version of the processor has been emulated on a Vertex-II FPGA.

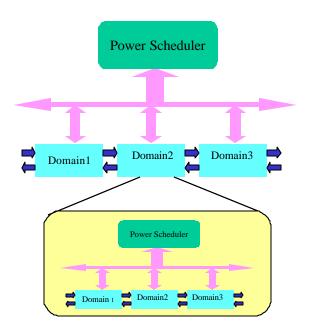

- ? The digital network processor introduces the concept of power-domains. Unused modules are powered down either completely or to the retention voltage to reduce leakage power. A power-down SRAM test chip has been designed and tested demonstrating the validity of the concept.

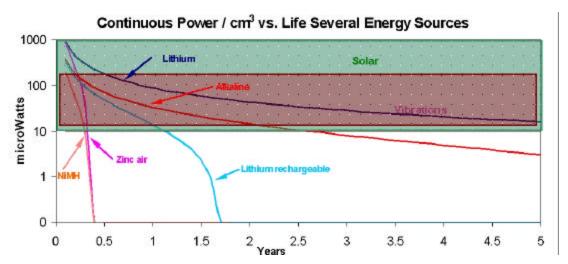

- ? Energy-scavenging power train, based on solar power has been tested and characterized. A prototype package has been designed.

This project fully met its original goals. Over the 3 generations, the power dissipation of the wireless transceiver node has been reduced by a factor of 460, while the volume of the node was reduced by a factor 30.

- RF front-end prototype chips:

- ? FBAR based oscillator has been fabricated and tested (300 mW).

- ? Test chips containing all components of the RF transceiver have been fabricated and are being tested.

- Digital network processor:

- ? Major components of the chip (memory controller, memory, MAC) have been evaluated and characterized.

- ? Behavioral spec has been operational

- ? FPGA version operational.

- Memory test chip has been fabricated and is being tested.

- Energy scavenging power train has been tested and characterized.

# 1.D TECHNOLOGY TRANSFER

The research in this project is performed at the Berkeley Wireless Research Center (BWRC), which is a University affiliated research consortium with 10 companies (Agilent, Atmel, Cadence, Ericsson, Hewlett Packard, Hitachi, Infineon, Intel, Qualcomm, and SGS-Thompson). A high priority in the design of the Center has been made to facilitate collaboration between researchers from the member companies and the Center faculty, staff and students thus providing the best possible situation for technology transfer. A number of the member companies are directly involved in the PicoRadio research and its results (Ericsson, Intel, Cadence, SGS-Thompson, Hewlett Packard, and Agilent).

Furthermore, this project is at the core of some very ambitious projects, applying low-energy wireless transceiver technology made available through this program. The most important one is the \$350 M University of California CITRIS Institute, which focuses on the development of societal scale information systems, addressing large problems that hamper society at large such as traffic management, energy consumption and disaster mitigation. PicoRadio sensor networks form the backbone of these societal-systems. An application that is already being prototyped is the Smart Home. The combination of integrated sensors, actuators, and controllers help to increase quality-of-living and the energy-efficiency of large office buildings. These projects are cooperative efforts between BWRC, the Berkeley Sensor and Actuator Center (BSAC), and Center for the Built-environment (CBE) and their many industrial partners.

Finally, the PicoRadio project has received major attention. The paper "PicoRadios for Wireless Sensor Networks: The Next Challenge in Ultra-Low Power Design," presented at the 2002 ISSCC conference has been awarded the ISSCC 2002 Jack Raper Outstanding Technology Directions Paper Award ISCC is the premier conference in the area of semiconductor integrated circuits. PicoRadio was featured in the *Wireless Review Magazine* as one of the exciting emerging technologies. Finally, PicoRadio technologies have been or will be featured in a number of keynote presentations in 2002 and 2003 (IBM Asceed, CoolChips VI in Japan, etc.).

# 2 TECHNICAL OVERVIEW

#### 2.A PICONODE I - PICORADIO TEST

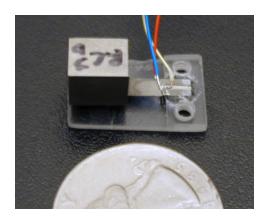

PicoNode I - PicoRadio Test Bed Boards

#### 2.A.1 PicoRadio Test Bed Hardware and Development System

## **2.A.1.1** Architecture and implementation

Authors: Fred Burghardt and Susan Mellers

In order to enable real-world investigation into system-level aspects of a PicoRadio network before the PicoNode devices are available (and also to help determine how a PicoNode should be designed), a prototyping environment was built. This environment is referred to as PicoRadio I, or the PicoRadio Test Bed.

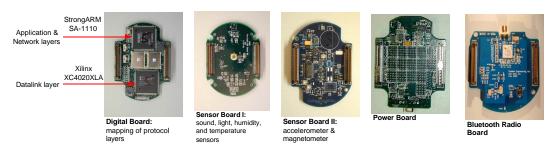

The PicoRadio Test Bed is a collection of hardware and the algorithms that run on the nodes. Each node is composed of two major parts: a set of custom circuit boards and a collection of software libraries that allow Pico Radio designers to make use of the hardware. The boards are small, stackable units that, when assembled, fit into a custom case designed by students from the Dept of Mechanical Engineering at UCB. The PicoRadio Test Bed is composed of two core boards: the digital board and the power board. The various boards comprising a PicoRadio Test Bed are shown in Figure 2.

The digital board contains a Strong ARM 1100 embedded microprocessor and a Xilinx XC4020XLA Field Programmable Gate Array (FPGA). The ARM is used to emulate functionality that may be mapped into a general-purpose processor or DSP core. It provides a CPU core and a variety of controllers for services such as standard I/O control and timers. The FPGA is used to emulate tasks that would be assigned to configurable or custom logic on a Pico Node.

The power board provides power to the digital board, and contains an auxiliary 5v supply. Dynamic voltage scaling is used to the ARM 1.5v core.

In addition to the core boards, a Test Bed node includes a radio board and, optionally, a sensor board. A Bluetooth radio is the RF front end for the Test Bed, because it models the short range of the PicoRadio III nodes.

Sensor board I was designed in cooperation with the Center for the Built Environment (CBE), part of the Dept of Architecture at UCB. Three of the sensors on the board are types most likely to be found in a Smart Building sensor network: temperature, humidity, and light intensity. The board also contains a microphone and speaker driver, which are intended to be part of an acoustic anemometer capable of measuring very low levels of air movement inside a building (Karalar 2002). This sensor board has been used extensively in data collection activities here at the Center and for system demonstrations at BWRC retreats.

Sensor board II was designed in cooperation with the Dept of Civil Engineering at UCB. The motivation was to provide a means of instrumenting earthquake simulations on structures. For this purpose, the board contains a two-axis accelerometer and a two-axis magnetometer. The magnetometer is primarily used to provide orientation for the accelerometer data so that node positioning is not critical. As an exercise, inclinometer and compass applications were designed to test the board; both use the nodes status LEDs as a display. These applications also provide for interesting demonstrations. A GPS circuit was included in the board design, but as of now the boards have not been populated for GPS.

Figure 2

An ARM/FPGA development infrastructure has been created to support this hardware. Design environments for both the processor and the FPGA are currently in use. The ARM environment includes project management, code composition, debugging, and compilation. The FPGA environment includes schematic capture, VHDL composition, simulation, synthesis, and program file compilation.

For the ARM, a "kernel" has been developed that provides easy access to resources such as the interrupt controller, timers, power control, a real-time clock, general-purpose I/O, serial ports, and a port abstraction for FPGA I/O. The kernel also contains data structure packages and support for pre-built FPGA circuit blocks. For the FPGA, a set of blocks are available that provide functions such as ARM I/O, Tx/Rx data paths, FIFOs, a TDMA MAC, and mappings for all I/O pins.

Full system deployment of sixty PicoRadio test bed nodes has been completed. Protocol development and test results are reported below.

#### 2.A.1.2 Concurrent design of electrical and mechanical components

Authors: Dan Odell and Michael Montero

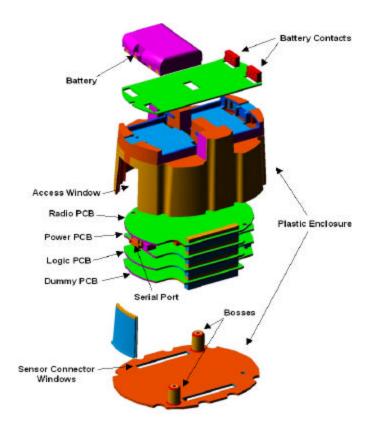

A case is required to protect the PicoNode I physical components. The node consists of four printed circuit boards (PCBs), two batteries, battery contacts, a power switch, an antenna, a case, a lid, and two edge windows for access to connectors. Many of these components have both mechanical and electrical requirements that they must fulfill. Designers of both the enclosure and the circuit boards must participate in the selection and design processes to ensure that the components meet the requirements of the entire system and not solely those of the electrical or mechanical domain.

In order to facilitate this collaborative design process, a unified domain design environment is being developed to address the needs of electro-mechanical product designs. The tool called DUCADE (Domain Unified Computer Aided Design Environment) enables designers from the electrical and mechanical domains to exchange pertinent design information throughout the life cycle of the product design. DUCADE allows PCB design and development to occur concurrently with the mechanical design of the product's enclosure. Issues such as thermal conductivity, geometric interference, and IC component placement are dealt with between both domain designers to promote parallel product design which will reduce the iterations of re-design and hence lower cost and time.

An enclosure was designed for the PicoRadio Test Bed "stack" and a prototype was created on Mechanical Engineering Department's Fused Deposition Modelling (FDM) machine. A production run of 150 cases was completed, and 50 fully assembled nodes are now available for deployment. Figure 3 shows a typical production PicoRadio Test Bed case, and Figure 4 shows an exploded view.

Node with final case. Sensor board is on top.

Case with lid and boards removed.

Figure 2

Figure 4: Exploded view of case with lid at bottom, to show battery socket area

# 2.A.2 PicoNode III implementation on test bed

Author: Johnathan Reason

With the exception of the Physical layer, the entire PicoNode III protocol stack has been integrated into PicoNode I. Over the past twelve months, we have subjected this protocol stack to extensive testing and debugging, which has led to some important functional refinements, particularly in the Datalink and Network layers. Additionally, we have developed a network management system that allows us to monitor and manage the performance of our network. At the BWRC retreat in June 2002, we made our debut demonstration of an ad hoc, multi-hop, sensor network using the PicoNode III protocols running on the Test Bed hardware. Based on lessons learned from this demonstration, subsequent demonstrations, and lab testing, we have achieved a low-energy, stable, and robust protocol stack.

## 2.A.2.1 Protocol integration

Integrating the PicoNode III protocols into the Test Bed hardware was a major milestone for three reasons. First, this was the first time all the layers of the protocol stack were brought together on a single platform. Thus, the functional verification of inter-layer semantics and internode communications actually took place in the Test Bed. Secondly, testing the protocol stack in a real world environment allowed us to identify some shortcomings in the functional behavior of each layer, especially regarding robustness. Lastly, the Test Bed implementation turned out to be a better starting point for the PicoNode III system on a chip (SoC) implementation than anticipated.

Currently, the PicoRadio network in the Test Bed contains three types of nodes: *sensors*, *controllers*, *and anchors*. Sensor nodes gather and forward sensor measurements. Controller nodes primarily initiate commands to the network (e.g., requests for sensor measurements) and serve as the end destination where sensor nodes forward their responses. Anchor nodes provide static position references within the environment by periodically broadcasting their location to the network. Controller and anchor nodes typically have a hard-wired power source and can optionally be configured to gather and forward sensor measurements too. Additionally, controller nodes are physically connected to a computer via a serial cable. In a typical deployment scenario, per room there might be one controller, at least four anchors, and thirty or more sensors.

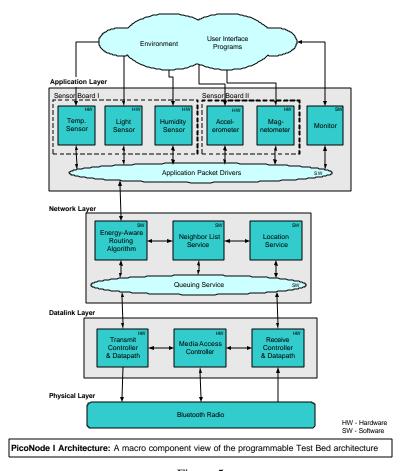

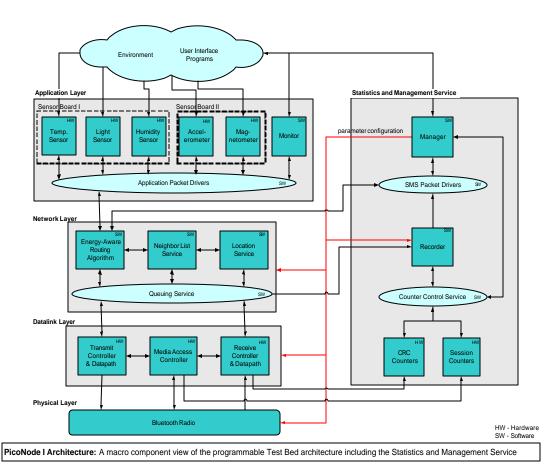

The figures and table below illustrate how each layer is mapped onto the Test Bed hardware and what primary components and functions comprise each layer. With the exception of the sensor boards, the Application layer is implemented in software that is executed on the StrongARM processor. The Network layer is solely implemented in software; however, it is important to note that this is only because we had very limited reconfigurable resources in the FPGA. To provide better power management, some parts of the Network layer will be implemented in hardware in the SoC platform of PicoNode III.

## 2.A.2.2 Application layer

The Application layer consists of one standard sensor board (Sensor Board I), one optional sensor board (Sensor Board II), the Monitor software module, and application drivers that provide the interface between the Application and Network layers. Each node is equipped with at least Sensor Board I, which provides a microphone and temperature, light and humidity sensors. Some nodes are also equipped with the second board that allows for more advanced applications like motion detection via an accelerometer and magnetometer. The Monitor is a small software module that interacts with the real world through user applications that control and monitor the network. The application drivers interpret incoming packets as controls that activate the various sensors, as well as assemble outgoing sensor measurements and Monitor requests into packets.

Figure 5

## 2.A.2.3 Network layer

The Network layer is comprised of four macro components: the Energy Aware Routing Algorithm, the Location Service, the Neighbor List Service and the Queuing Service. The Energy-Aware Routing Algorithm is the primary function of the Network layer and its details were described in the PicoRadio Year Two report for 2001 (see Section 2C.1.1). The Location Service is comprised of the algorithm and protocol that allows each node to dynamically discover its position relative to anchor nodes (see details in 2001 report Section 2C.2.1). In the PicoRadio network, a nodes location is analogous to the concept of network address found in most networks. Therefore, through the remainder of this report, we will use the terms location and network address interchangeably. Thus, the Location Service is considered a sub layer of the Network layer because it provides the means by which a PicoNode dynamically configures its network address. The Queuing Service provides the interface between the Network and Datalink layers.

| Layer       | Macro Component                                                             | Primary and Secondary Functions                                                                                                                                                                                    |  |

|-------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Application | Sensor Boards I & II                                                        | 1. Gather sensor measurements                                                                                                                                                                                      |  |

|             | Monitor Module                                                              | 2. Request sensor measurements                                                                                                                                                                                     |  |

|             | Application Drivers                                                         | 3. Assemble/disassemble control and measurement packets                                                                                                                                                            |  |

| Network     | Energy-Aware Routing Algorithm<br>Location Service<br>Neighbor List Service | Next-hop data routing/broadcast forwarding     Dynamic location configuration     Neighbor address resolution     a. neighborhood maintenance     b. dynamic MAC ID configuration     c. initialization management |  |

| Datalink    | MAC<br>MAC<br>TX/RX Datapaths                                               | <ol> <li>Access control</li> <li>Link reliability control</li> <li>Datapath control and flow</li> </ol>                                                                                                            |  |

| Physical    | Radio                                                                       | Transmit and receive bits                                                                                                                                                                                          |  |

Table 1: Components and Functions of each layer in the PicoRadio protocol stack

The Neighbor List Service (NLS) performs address resolution for the Network layer, a function that is commonly found in most networks (e.g., the Address Resolution Protocol in the Internet protocol suite). It accomplishes this by maintaining a table that contains a mapping between its one-hop neighbors' media-access (MAC) IDs and network addresses. Each entry in this table also includes other information useful for routing such as a link quality metric and a status indicator. In a typical query, the routing algorithm may provide the NLS with a location and receive back the triplet (*Status, MAC ID, Link Metric*). The NLS also manages the timing of events during the initialization process, which consists of discovering the neighborhood, computing its location, configuring its MAC ID, and joining the neighborhood.

One important contribution of the Test Bed is the major refinement of the NLS. Extensive testing showed that the performance of routing is strongly dependent on the maintenance strategy of the neighbor list table. For example, early versions of the NLS added and removed a neighbor to its table with only the notion of how frequently it heard (or didn't hear) special control messages from a neighbor. This approach proved to lack robustness in a real world scenario because it did not really capture link quality. In the current approach, a node only adds (or removes) a neighbor when the quality of the link between itself and its neighbor has been tested and the link metric is above (or below) an acceptable threshold. Additionally, we refined the layering position of this macro component, which was originally considered to be a sub layer of the Datalink layer. The new layering helped us maintain modularity and a simple interface, which greatly facilitated debugging.

#### 2.A.2.4 Datalink layer

The Datalink layer is comprised of three macro components: the Transmit Controller and Datapath (TCD), the Receive Controller and Datapath (RCD), and the Media Access Controller (MAC). The TCD and RCD interface with the Queuing Service of the Network layer and control the datapath functions: transmit/receive buffering, serialization/de-serialization, cyclic

redundancy checking, and line balancing. The PicoRadio Test Bed MAC supports the following features:

- Broadcast

- Request to Send (RTS) /Clear to Send (CTS) style unicast data transfers with medium reservation

- Receiver duty cycling

- Two-channel or multi-channel configuration

The receiver duty cycling feature or *cycled-receiver* is a concept borrowed from paging systems. It is widely used in many MAC designs (e.g., 802.11 sleep mode) as a way to reduce the receiver's idling power consumption. The idea is to turn the transceiver's idle mode into a low-power sleep mode by periodically duty cycling the receiver, as opposed to leaving the receiver on 100% of the time.

The Test Bed Bluetooth radios support 64 channels in the frequency range from 2.402 GHz to 2.480 GHz. In the two-channel configuration, we use one channel to send broadcast messages and another channel to send unicast messages. In the multi-channel configuration, we still only use one channel for broadcast messages, but we employ orthogonality in frequency for unicast messages. In particular, each node receives unicast messages on a locally independent channel that corresponds to its MAC ID. For example, a node with MAC ID 24 will receive unicast messages on channel 24. MAC IDs range from 1 to 63.

## 2.A.2.5 Low-power features

Each layer of the protocol stack has components that incorporate specific energy-aware or low-power features (e.g., medium reservation in the MAC). In addition, each macro component has been designed to support a power management interface, which can be used to turn components off when they are idling. Since there is no way to turn off the power to individual components in the Xilinx, power management is not actually implemented in the Test Bed. However, this feature of the component interfaces will be used by the power manager in the PicoNode III implementation.

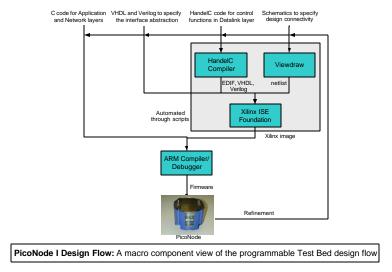

#### 2.A.2.6 Design flow

Figure 6 below illustrates the Test Bed design flow. Most of the design was captured using language-based tools. All the application drivers and network functions are implemented in C code. We use the ARM Compiler to target the SA-1110 processor. Most of the control functions in the Datalink layer are written in HandelC, which is a hardware language for concurrent programming. It is based on the Communicating Sequential Processes (CSP) programming language. HandelC uses a subset of ANSI C with some additional syntactical constructs to support hardware design. The HandelC compiler can produce optimized EDIF 2.0, VHDL, or

Verilog targeted for a specific FPGA (or CPLD). We use schematic capture primarily to specify design connectivity. We also use it partially to specify the interface abstraction between the FPGA, radio, and processor. We use the Xilinx ISE Foundation tools to perform all the other synthesis steps (e.g., mapping, place and route). The FPGA synthesis process is fully automated using custom scripts. Once a Xilinx image is synthesized, we use the ARM Debugger to simultaneous load the image and the ARM executable into the PicoNode's flash RAM.

Figure 6

Currently, there is no viable simulation engine in this design flow. Thus, all design verification and refinement is based on real hardware and real world experimentation. Although this might not be the ideal approach, we found it to be the most expedient approach. All of the tools we investigated for our design flow proved to be inadequate for at least one of the following reasons:

- No path to FPGA or ASIC synthesis

- Did not adequately simulate the intra- and inter-component concurrency and inter-layer semantics

- Too slow in simulating multi-node scenarios

Recently though, researchers at our center have developed a design flow that shows promise in overcoming these shortcomings. Their design flow uses MATLAB (i.e., Simulink and StateFlow) for design capture and simulation. From these high-level descriptions, FPGA and ASIC synthesis is possible. We are currently experimenting with this flow for part of the PicoNode III implementation. We are currently experimenting with this flow for part of the PicoNode III implementation.

#### 2.A.2.7 Network management and maintenance

To facilitate testing, debugging, and performance measuring, we designed a network management subsystem that we call the Statistics and Management Service (SMS). SMS is an independent subsystem that can optionally be enabled on each PicoNode I system. It operates by employing a request/response paradigm similar to the interaction between controllers and sensors. When SMS is enabled, a PicoNode can be configured as either an SMS controller or an SMS agent. An SMS controller sends requests for management data and SMS agents respond with the data. Typically, controller nodes are configured as SMS controllers and sensor nodes as SMS agents. The management data is a table of variables maintained by each SMS agent. An SMS controller can request a single variable (e.g., the number of CRC failures) or the entire table from a single node or a group of nodes. The management data contains the following entries:

- The number of RTS/CTS counts per data session

- CRC failure counts

- Packet header information

When management data arrives, an SMS controller will log it in a file for off-line processing.

The component view of SMS is depicted in the right half of Figure 7. SMS is comprised of four components: the Manager, Recorder, CRC Counter, and Session Counters. The Manager is a software component that implements the SMS controller/agent functionality. When a node is configured as an SMS controller, the Manager provides the interface to a user interface program that initiates requests. When a node is configured as an SMS agent, the Manager configures the other components to service SMS controller requests. The Recorder maintains the management data, which it records on a per packet basis. It can record all ingoing and outgoing packets or only packets of a specific type. The Recorder is used when an SMS Agent is configured to periodically send management data to an SMS controller. For single responses, the Manager can optionally read counter values directly through the Counter Control Service, which provides the interface to access the CRC and Session Counters. All inbound and outbound data must pass through the SMS Packet Drivers to be unpacked or packaged into packets.

#### SUMMARY OF PERFORMANCE

Using SMS for management data collection and Excel filters for off-line processing, we can make a variety of performance measurements, including:

- Broadcast packet loss rate (PLR)

- RTS/CTS session success rate

- Bit error rate (BER)

- Power estimates

- Route traces

- Response latency

Figure 7

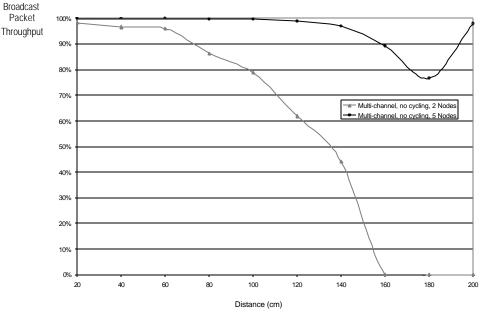

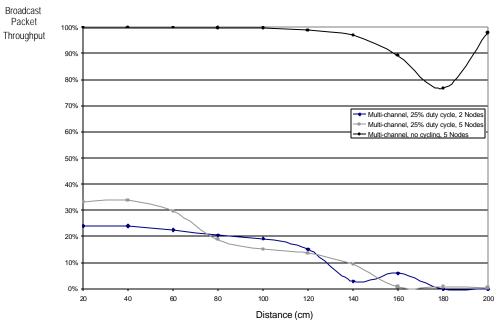

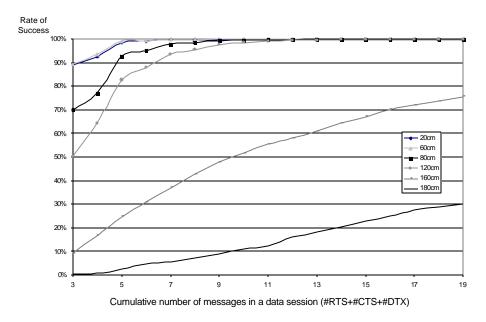

The figures below illustrate a sample of the performance measurements that can be extracted from SMS. For each figure, 1000 measurements were taken per data point with the controller node requesting management data at a rate of 5 packets per second. For the cycled-receiver MAC, the cycle period was 100 milliseconds with a 25%-duty cycle. Each node was equipped with a 6 dB attenuator to limit the transmit range to a few meters.

Figure 8 shows how the broadcast packet loss rate (PLR) varies with distance. We compare the results of a two-node and five-node neighborhood, where each node implements the multichannel, non-cycling MAC model described above (see Datalink layer section). For the two-node neighborhood, we have one controller and one sensor and vary the distance between them from 20 to 200 centimeters. For the five-node neighborhood, we have one controller node and four sensors nodes. The first three sensors are spaced at 20 centimeter increments from the controller and the fourth sensor is varied from 20 to 200 centimeters from the controller. This figure illustrates how just a few intermediate forwarding nodes can dramatically improve the broadcast reliability.

Packet loss rate for broadcast messages in a 2-node and 5-node neighborhood as a function of distance between the controller node and a particular sensor node. Forwarding by intermediate nodes dramatically improves the broadcast reliability.

Figure 8

In Figure 9, we consider the five-node neighborhood again, but this time we compare the multichannel, non-cycling MAC to a 25%-duty cycling, multi-channel MAC. This figure illustrates the trade-off between cycling the receiver's idle duty cycle (to conserve power) and broadcast reliability. The 25%-duty cycled MAC has a PLR three to five times worse than the non-cycled MAC. However, note that intermediate forwarding also improves the 25%-duty cycled MAC, This suggest that greater density might be able to compensate for much of this trade-off. We are still trying to verify this hypothesis.

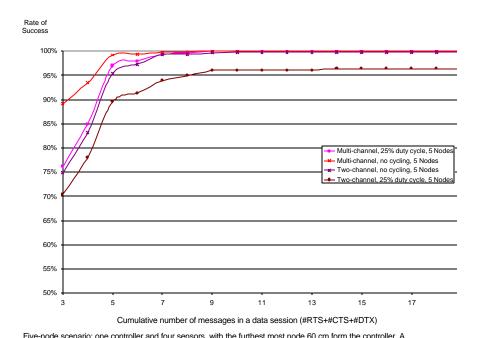

In Figure 10, for the same five-node neighborhood, we consider the impact varying distance has on the performance of unicast data transfers (or sessions). These results are for the multi-channel, non-cycling MAC. To complete a unicast session, it takes a minimum of three messages: one ready-to-receive (RTS), one clear-to-send (CTS), and one data transmission (DTX). Up to 60 centimeters, about 90% of all unicast sessions complete with the minimum number of messages. This is region of the graph is favorable because it also indicates the minimum session setup latency and the minimum session power consumption. Beyond 60 cm the rate of success with just three total messages drops off rapidly. However, up to 1.2 meters, at least 88% of all unicast sessions complete with six or less total messages.

A comparison of the broadcast packet loss rate (PLR) for 100% duty cycle receiver and a 25% duty cycle receiver. Duty cycling the receiver during idle time degrades broadcast reliability.

Figure 8

Five-node scenario: one controller and four sensors. The rate of success for unicast data sessions for a given number of cumulative messages at varying distances form the controller.

Figure 10

These results are useful because they allow us to tune the time constants of our RTS/CTS style MAC for different topology and deployment scenarios. Additionally, the same management data can be used to extract the average power consumption and the average response latency per node. Excel filters are currently under development to extract these results.

In Figure 11, we compare the unicast session performance of the multi-channel, cycled and non-cycled MACs to the two-channel, cycled and non-cycled MACs. For this comparison, we consider the five-node neighborhood with the furthest most sensor node 60 centimeters from the controller. These results show that the cycled-receiver and the two-channel MAC have the biggest impact on session performance for three to five message sessions. There is negligible impact for sessions that complete using six or more messages. In contrast, when these two MACs are combined, there is at least a 4% performance penalty for all sessions.

These examples demonstrate the utility of SMS, but by no means are they exhaustive. SMS is a powerful network management tool that is still maturing.

Figure 11

# 2.A.2.8 PicoRadio Test Bed deployment

comparison of the rate of success for different MAC techniques.

Authors: Johnathan Reason and Fred Burghardt

The Test Bed has been deployed in various forms and for various purposes for over the past two years.

#### SUMMARY OF EXPERIMENTS AND TEST RESULTS

**RSSI Profiling:** One early experiment attempted to determine the nature of the wireless environment within an area of the BWRC. Two nodes equipped with Proxim RangeLAN radios were connected using TDMA. Measurements were taken at various intervals and the results compared. These tests showed a periodic fading with distance, consistent with a multi-path environment. The results confirmed an initial assumption about the space.

**Local Positioning (Locationing):** Two experiments were performed using an algorithm based on least-squares triangulation using received signal strength indication (RSSI), a notoriously error-prone number (50% accuracy). In the first, experiment, one "target" node attempted to locate itself based on information from four "anchor" nodes. The anchors were pre-programmed with fixed XYZ coordinates. Results from this experiment were interesting but less than spectacular. The target node could reliably detect movement, but its idea of absolute position was generally poor. In the second experiment, demonstrated at the Winter 2001 BWRC retreat, the number of anchor nodes was increased to eight. The results were significantly better than the first experiment, confirming that redundancy is required for this algorithm using RSSI as a distance metric.

**Sensoring:** PicoRadio networks will initially be used in sensoring applications. To test an application layer for sensing light, temperature, and humidity, a sensor board was built and a series of experiments conducted at BWRC. In these experiments, a user requested information from the network via a graphical user interface running on a "controller" node. The requests were forwarded across a Test Bed network to sensor nodes placed at various points throughout the center. These nodes would take the measurement requested and return the data to the controller. The controller node logged the data to a file on a laptop via the serial port, and a separate program generated real-time or batch-oriented graphs. This application was demonstrated at the Summer 2001 BWRC retreat.

**Networking:** The most demanding use of the Test Bed is to emulate the PicoRadio network. Network routing in and of itself is complex and difficult to analyze and debug. To aid in this task, various data gathering mechanisms were embedded into the Test Bed implementation of the PicoRadio protocols. One use of the information gathered is to map routing activity in the network. A graphical user interface has been designed to display the current location of nodes in a deployment, the type of node, the type of information requested of returned, and the route this information took on the return path to a controller. The GUI shows a physical space with colored circles representing nodes; color indicates node type (sensor or controller). The circles 'flash' when receiving or sending data. A text box adjacent to the circle displays XYZ coordinates, subtype of node (temperature, etc), and last value. Lines between circles indicate data transmitted between nodes. The display is dynamic; lines appear and disappear as data flows through the network. The activity can be recorded and replayed at a later time at various speeds and in both directions. This application was demonstrated first at the Summer 2002 BWRC retreat and then at the June 2002 PAC/C PI meeting in Pittsburgh, Pa. A related demo showing network statistics such as retransmit counts and CRC failures on a line graph similar to the sensoring application was shown at the Winter 2002 BWRC retreat.

Compass and Inclinometer: Two sensor boards were built for the Test Bed. The first contains temperature, light, humidity sensors and a microphone. This board was used in the sensoring and audio direction finding studies. The second contains a two-axis accelerometer and a two-axis magnetometer. Two applications were designed that used the sensors on board #2: one application used the accelerometer to determine inclination from the horizontal, displayed on the eight status LEDs mounted on the digital board. The second application used the magnetometer to implement a compass, where the headings were also displayed on the LEDs. These applications were used mainly for entertaining demos. No one so far has used them for back-country expeditions as far as we know.

**Acoustic Anemometer:** Sensor board #1 was originally designed with a specific experiment in mind. Air flow through a space can be detected by variations in an audio signal passing through the space. The sensor board contains a speaker for producing tones and a microphone for detecting the tones. Signal processing on the received tones can be done in the FPGA and processor to measure the rate of flow of air along the axis connecting the nodes.

The Test Bed was used for a series of experiments in acoustic anemometry. Results were published in Karalar (2002).

**Audio Direction Finding:** A team from University of Illinois, Urbana-Champaign spent two weeks at the BWRC conducting data gathering to evaluate an algorithm to locate an object using sound. Results are pending.

## 2.A.2.9 Graphical user interfaces

Several GUIs were developed to aid in development of the protocols. Two were data entry tools and two were display tools.

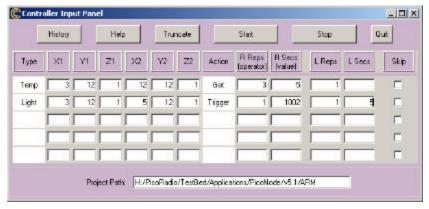

Figure 12 shows the Controller Input Panel. We use this tool to formulate and send requests for data. It provides for a "program" of five requests, some of which can be repetitive as indicated by the *L Reps* and *L Secs* columns on the right.

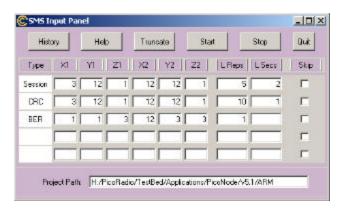

Figure 13 shows the SMS Input Panel. This GUI is much like the Controller Input Panel except that rather than requests for data this tool handles Statistics and Management Service requests.

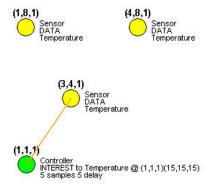

Figure 14 shows the Topology Mapping Tool. The green circle represents a controller and the text to the right of the circle show characteristics of a request for data that was just sent. The yellow circles show sensors that have responded in the past. Adjacent to a sensor circle is text related to a sample. The orange line between node 3,4,1 and the controller indicates that a data transfer is in progress.

Figure 11: The Controller Input Panel

Figure 12: The SMS Input Panel

Figure 14: The Topology Mapping Tool

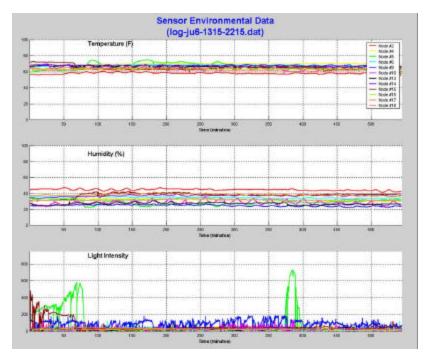

Figure 15 is a display of environmental data taken over about nine hours at the BWRC. The three windows show simultaneous temperature, humidity, and light readings. The lines in each graph represent nodes.

Figure 15: Display of environmental data at BWRC over a nine-hour period

# 2.B PICONODE II - TWO-CHIP PICONODE IMPLEMENTATION

Authors: M. Josie Ammer, Michael Sheets, and Mika Kuulusa

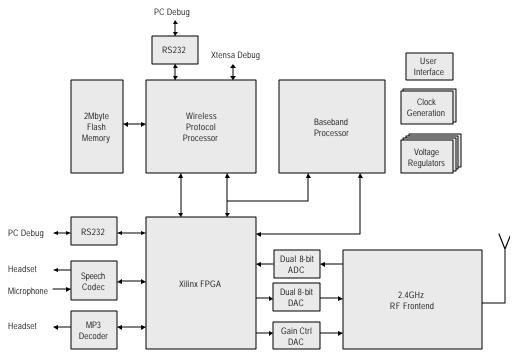

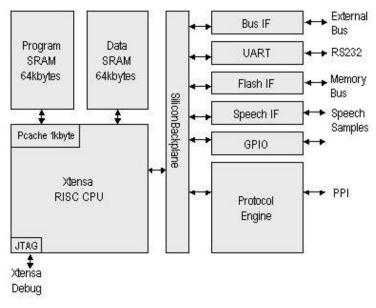

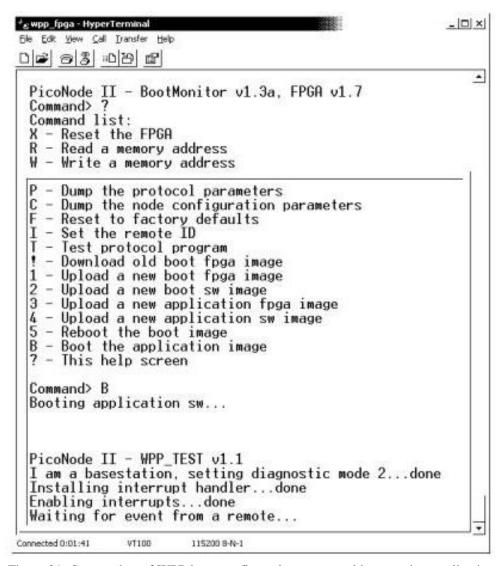

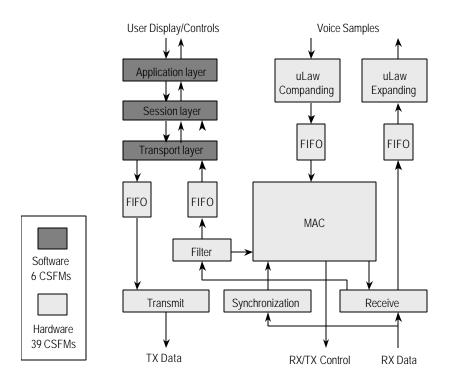

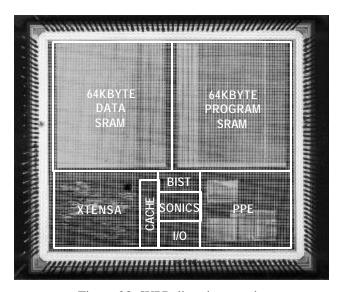

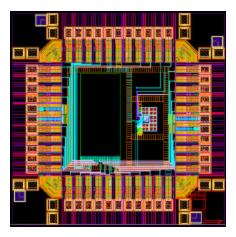

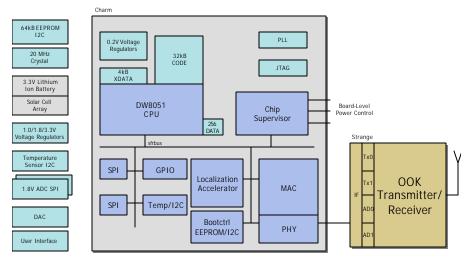

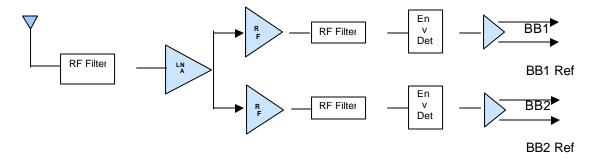

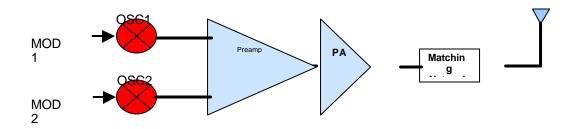

The PicoNode II protocol stack is realized with two custom ICs: Baseband Processor (BBP) implementing the PHY and Wireless Protocol Processor (WPP) implementing the DLL layer and above. The interface between them is designed to be simple with no external components so that a future revision could integrate them onto one chip. Figure 16 shows a block diagram of the system. Each chip and its design methodology are described below followed by testing, conclusions and results.

Figure 16: PN II system block diagram

# 2.B.1 Baseband processor (BBP)

The physical layer is made compatible with a commercially available RF front-end (performing down conversion from the carrier), ADC, and DAC. Although the commercial components have high power consumption resulting from their tight design specs, the PHY accommodates significantly relaxed specs for eventual integration with a custom, low-power analog front end (for instance, by only requiring a free-running clock with 50 ppm accuracy). The chip integrates all other PHY receiver and transmitter functions, such as carrier detect, timing recovery, synchronization, and detection.

The air-interface uses direct sequence spread spectrum (DSSS) with a length 31 spreading code at 25 Mcps (Million Chips per Second) and QPSK modulation resulting in a raw data rate of 1.6 Mbps. DSSS was selected to combat narrow band fading. QPSK modulation is chosen for its ease of low power implementation with DSSS. A 25 Mcps chip rate provides the raw data rate of 1.6 Mbps needed to support the twenty 64Kbps TDMA slots specified by the protocol. The primary receiver specifications are a +/- 100KHz maximum carrier frequency offset (+/-50 ppm from a 2GHz carrier reference), 5 dB minimum input signal-to-noise ratio at the ADC, and a 50ppm ADC sample clock. The BBP supports a typical indoor frequency-selective wireless channel with mobile units traveling at foot speeds.

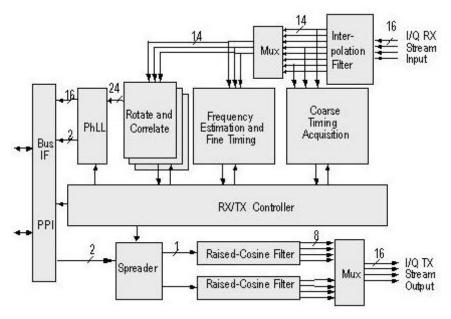

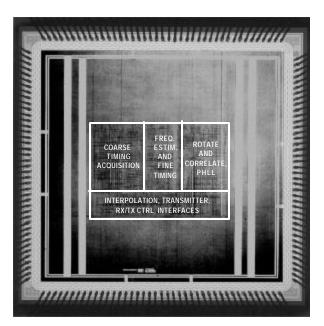

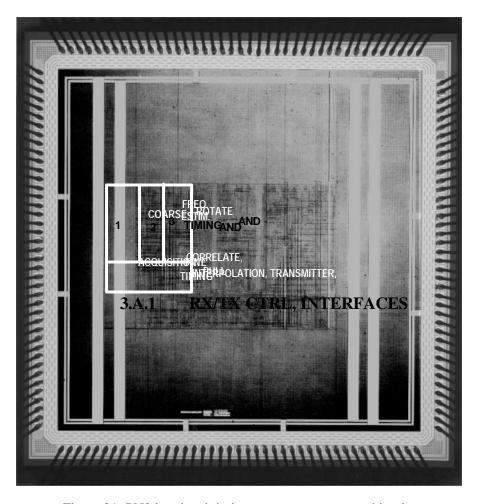

High-level system exploration in Simulink enabled algorithm refinement and power optimization of the physical layer. A block diagram is shown in Figure 17. The RX/TX Controller state machine interfaces with the WPP and controls the flow of the data from one datapath block to another. The BBP incorporates 5 gated clock domains that are adaptively switched on by the RX/TX Controller for maximal energy efficiency. Communication with the WPP is carried out through a 7-wire Physical-to-Protocol Interface (PPI) for RX/TX data and a system bus interface for initialization.

Figure 17: Baseband Processor (BBP) block diagram

During receive, the baseband signal is sampled by an off-chip 8-bit ADC at 100 Msps (4 samples per chip). This 100 MHz stream is split into 4 parallel streams of 25 MHz each so that the BBP could operate off the slower 25 MHz chip clock reducing power by allowing a lower operating voltage. Parallel filter techniques are used to process these four streams with an interpolation filter to increase the receiver timing resolution to 8 samples per chip. Performing on-chip interpolation of the signal is lower power than running the ADC at twice the rate.

Performing timing recovery in two successive stages reduces power consumption of this function by a factor of two. First, the coarse timing block performs carrier detect, and estimates timing to within 3/8 chip. Then, the fine timing block estimates timing to within 1/8 chip and estimates the carrier frequency offset to within 2.5 Hz.

The rotate and correlate block corrects the frequency offset, correlates the incoming signal with the spreading code, and performs early/late detection to track the optimal timing instant. The correlated symbols are fed into the phasor locked loop (PhLL) where the phase error is corrected using feedback and the QPSK symbols are demodulated. Where possible, coefficients were

restricted to factors of two, so that shift-and-add operations could be used instead of the more power hungry multiplication operations.

In the transmit mode, data bits are mapped into QPSK symbols, spread, raised-cosine filtered, and passed to an off-chip DAC. The transmitter datapath has a dual-channel spreader and two 25-tap raised-cosine filters (alpha = 0.30).

The BBP has several features that facilitate testing, including a full scan chain. Although the chip supports a programmable spreading code, hard-wired codes are used during test to reduce setup complexity. A loopback mode connects the transmitter output stream to the receiver input stream on the same chip, while the transmitter output pins are converted into a 64-bit test bus during receiver testing. Internal receiver signals such as the RX/TX controller state, code matched filter outputs, frequency estimate, and soft symbols, are output to this bus to aid in testing and debug.

#### 2.B.1.1 BBP design methodology

The design flow of the datapath-dominated BBP allows high-level design exploration using MATLAB/Simulink dataflow diagrams. The most efficient architectures in terms of power and area can be obtained by directly mapping these dataflow algorithms into hardware. Computational energy and area efficiencies that can be achieved with this approach are 2 to 3 orders of magnitude higher than the efficiency achieved by software processors (Brodersen 1997). In this way, the maximum parallelism can be obtained, allowing the minimum clock rate and supply voltage to be used, resulting in reduced energy per operation (Chandrakasan and Brodersen 1995). High-level power estimation and successive refinement are achieved with parameterized modules programmed in Synopsys Module Compiler. An in-house back-end design flow, called SSHAFT (Davis, et al. 2002), allows a direct path from Simulink and Module Compiler to heavily parallelized, direct-mapped ASIC implementations.

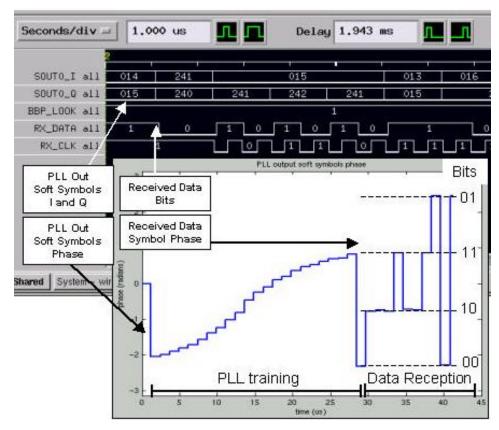

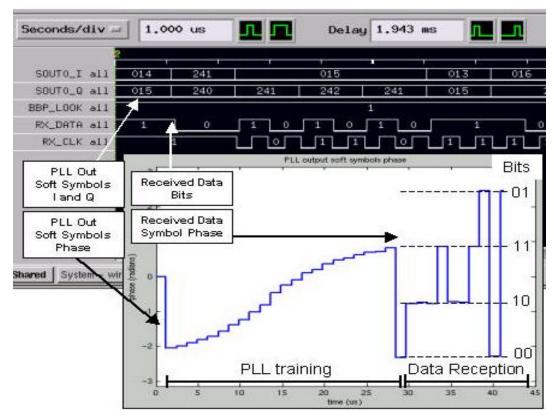

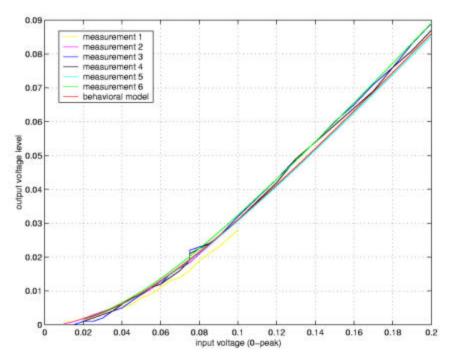

Since the entire design is encapsulated in Simulink, it can be simulated along with models of analog front-end. Therefore, the effect of analog nonidealities and fixed-point computation can be evaluated at a system level. Extensive system level simulations were done to ensure proper operation over the range of channel and circuit nonidealities. For instance, Figure 18 shows the locking behaviour of the PhLL.

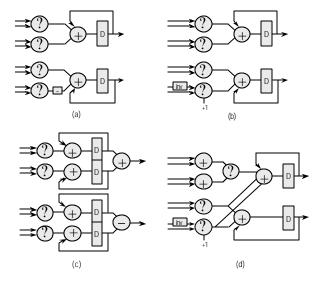

The SSHAFT flow enables early exploration for architectural tradeoffs between power consumption, speed, and die area. Fixed-point Simulink library models correspond to parameterized arithmetic units designed in Module Compiler. These modules can be quickly compiled with given parameters to form a gate-level netlist from which accurate power estimations can be made. For instance, four microarchitectures are available for complex multiply-accumulate (MAC) operations, as illustrated in Figure 19. The flow can be used to quickly decide which microarchitecture results in the lowest power for the particular input and output bit widths required by the algorithm.

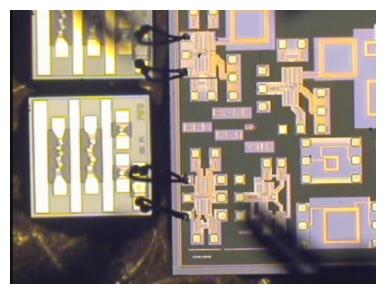

Figure 19: Simulation and matching chip test results of the BBP PhLL output

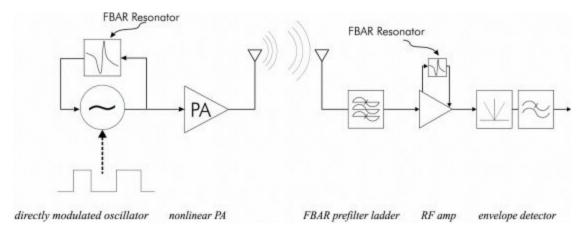

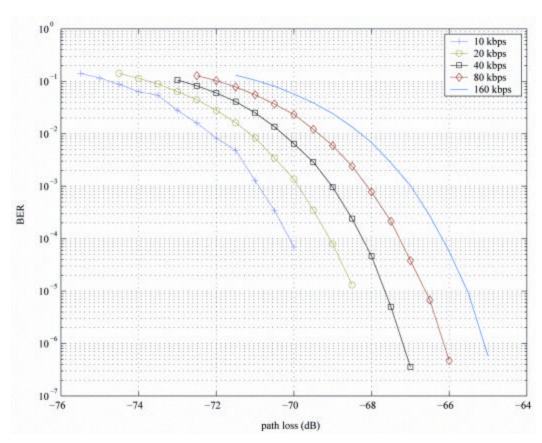

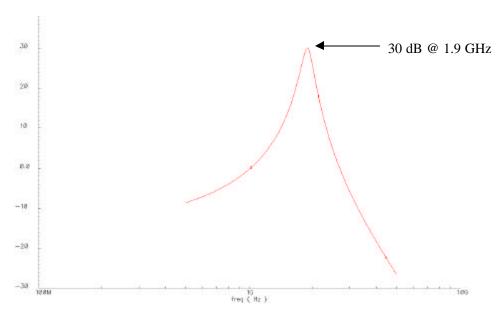

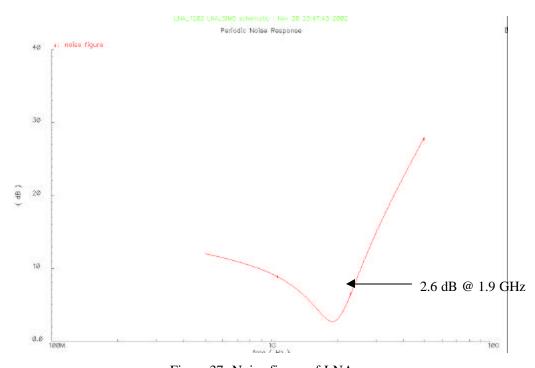

Figure 19 (a) through (d): Four architectures implementing a complex MAC operation