# AFRL-IF-WP-TR-2002-1566

# **MorphoSys PROJECT**

Dr. Nader Bagherzadeh

University of California, Irvine Department of Electrical and Computer Engineering ET 305 Irvine, CA 92697-1875

DECEMBER 2002

Final Report for 07 August 1997 – 31 August 2002

Approved for public release; distribution is unlimited.

INFORMATION DIRECTORATE AIR FORCE RESEARCH LABORATORY AIR FORCE MATERIEL COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OH 45433-7334

## NOTICE

USING GOVERNMENT DRAWINGS, SPECIFICATIONS, OR OTHER DATA INCLUDED IN THIS DOCUMENT FOR ANY PURPOSE OTHER THAN GOVERNMENT PROCUREMENT DOES NOT IN ANY WAY OBLIGATE THE US GOVERNMENT. THE FACT THAT THE GOVERNMENT FORMULATED OR SUPPLIED THE DRAWINGS, SPECIFICATIONS, OR OTHER DATA DOES NOT LICENSE THE HOLDER OR ANY OTHER PERSON OR CORPORATION; OR CONVEY ANY RIGHTS OR PERMISSION TO MANUFACTURE, USE, OR SELL ANY PATENTED INVENTION THAT MAY RELATE TO THEM.

THIS REPORT IS RELEASABLE TO THE NATIONAL TECHNICAL INFORMATION SERVICE (NTIS). AT NTIS, IT WILL BE AVAILABLE TO THE GENERAL PUBLIC, INCLUDING FOREIGN NATIONS.

THIS TECHNICAL REPORT HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION.

KERRY L. HILL Project Engineer Embedded Info Sys Engineering Branch Information Systems Technology Division

alfred J. Scarpelle

ALFRED J. SCARPELLI Team Leader Embedded Info Systems Engineering Branch Information Systems Technology Division

James & Willie

JAMES S. WILLIAMSON, Chief Embedded Info Systems Engineering Branch Information Systems Technology Division Information Directorate

Do not return copies of this report unless contractual obligations or notice on a specific document requires its return.

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |        |                                    |               |              | Form Approved<br>OMB No. 0704-0188                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|------------------------------------|---------------|--------------|--------------------------------------------------------|--|

| The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, searching |                       |        |                                    |               |              |                                                        |  |

| 1. REPORT DATE (D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S COVERED (From - To) |        |                                    |               |              |                                                        |  |

| December 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 07/1997 - 08/31/2002  |        |                                    |               |              |                                                        |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |        |                                    |               |              | . CONTRACT NUMBER<br>F33615-97-C-1126                  |  |

| MorphoSys PROJECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |        |                                    |               |              | . GRANT NUMBER                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | 5c     | . PROGRAM ELEMENT NUMBER<br>62301E |               |              |                                                        |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |        |                                    |               | 5d           | . PROJECT NUMBER                                       |  |

| Dr. Nader Bag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gherzade              | h      |                                    |               |              | ARPA                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |        |                                    |               | 5e           | . TASK NUMBER<br>AS                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |        |                                    |               | 56           | WORK UNIT NUMBER                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |        |                                    |               |              | 09                                                     |  |

| 7. PERFORMING OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |        | ND ADDRESS(ES)                     |               | 8.           | PERFORMING ORGANIZATION<br>REPORT NUMBER               |  |

| University of<br>Department of<br>ET 305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |        |                                    |               |              |                                                        |  |

| Irvine, CA 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |        |                                    |               | 10           | . SPONSORING/MONITORING                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |        | E(S) AND ADDRESS(E                 | 5)            | 10           | AGENCY ACRONYM(S)                                      |  |

| Information D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |        |                                    |               |              | AFRL/IFTA                                              |  |

| Air Force Research Laboratory<br>Air Force Materiel Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |        |                                    |               |              | . SPONSORING/MONITORING<br>AGENCY REPORT NUMBER(S)     |  |

| Wright-Patterson Air Force Base, OH 45433-7334                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |        |                                    |               |              | AFRL-IF-WP-TR-2002-1566                                |  |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT<br>Approved for public release; distribution is unlimited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |        |                                    |               |              |                                                        |  |

| 13. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |        |                                    |               |              |                                                        |  |

| Report contains co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |        |                                    |               |              |                                                        |  |

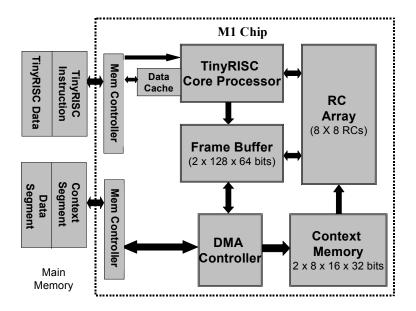

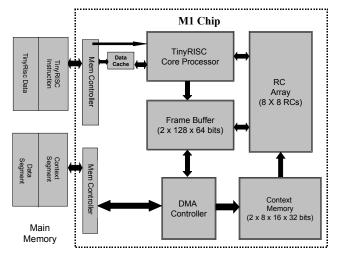

| <b>14. ABSTRACT</b> (Maximum 200 Words)<br>The MorphoSys architecture is a coarse-grain, reconfigurable computing architecture. This program was funded by<br>DARPA in support of the Adaptive Computing Systems (ACS) Technology Initiative. The architecture was successfully<br>functionally prototyped with the fabrication of the M1 chip. This report will review the MorphoSys architecture and the<br>M1 chip. The tools and application mappings are described. The design improvements to the M1 is detailed as the M2<br>chip design. Additionally, MorphoSys application domains are detailed. Technology transition success through the<br>DARPA Mission Specific Processing Technology Initiative, the MorphoSys related Morpho Technologies venture<br>capital startup, and Motorola licensing agreements are also touched upon. Finally, a program summary is provided.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |        |                                    |               |              |                                                        |  |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |        |                                    |               |              |                                                        |  |

| adaptive computing systems (ACS), coarse-grained reconfigurable computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |        |                                    |               |              |                                                        |  |

| 16. SECURITY CLAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SIFICATIO             | ON OF: | 17. LIMITATION                     | 18. NUMBER OF | 19a. NAME OF | RESPONSIBLE PERSON (Monitor)                           |  |

| a. REPORTb. ABSTRACTc. THIS PAGEOF ABSTRACTTAGESUnclassifiedUnclassifiedUnclassifiedSAR22619b. TELEPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |        |                                    |               |              | Hill<br>NE NUMBER (Include Area Code)<br>55-7698 x3604 |  |

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std. Z39-18

## **Table of Contents**

| List of Figure | 3                                                | vi |

|----------------|--------------------------------------------------|----|

| List of Tables |                                                  | ix |

| Acknowledgn    | nents                                            | X  |

| Foreword: Tee  | chnology Transfer                                | xi |

|                | and Introduction                                 |    |

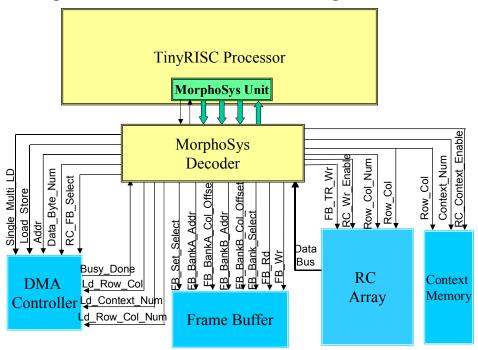

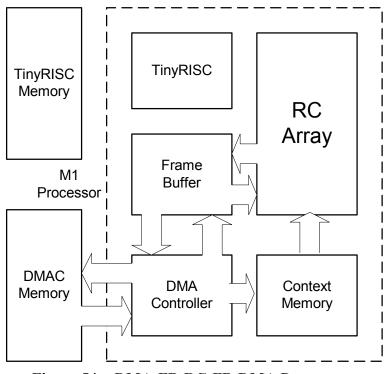

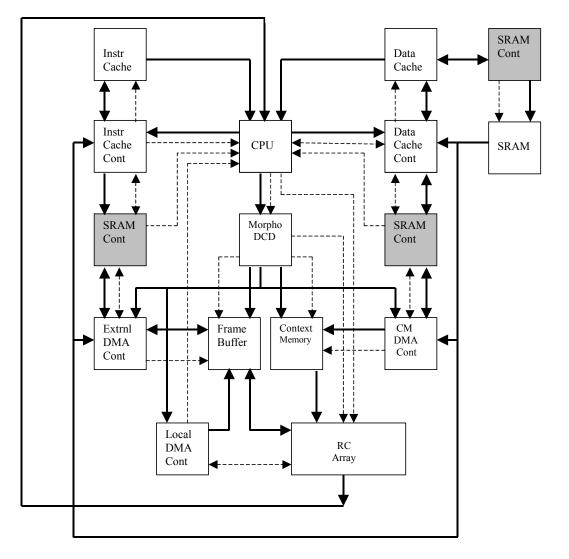

| 1.1. Mor       | phoSys Architecture                              |    |

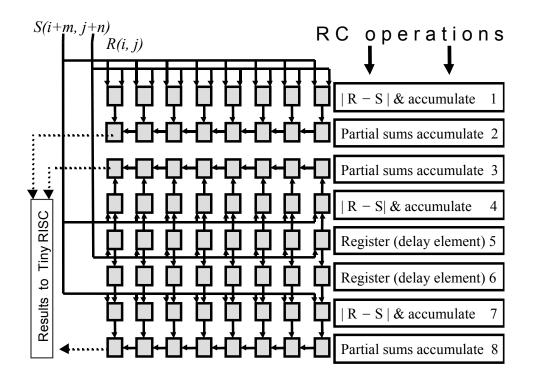

| 1.1.1.         | RC Array                                         |    |

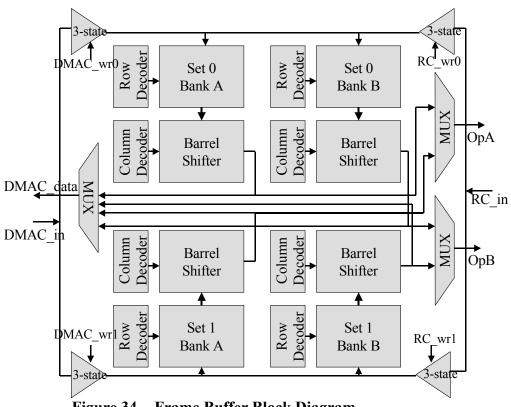

| 1.1.2.         | Frame Buffer and DMA Controller                  |    |

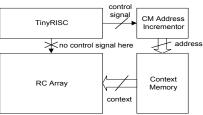

| 1.1.3.         | Context Memory                                   | 5  |

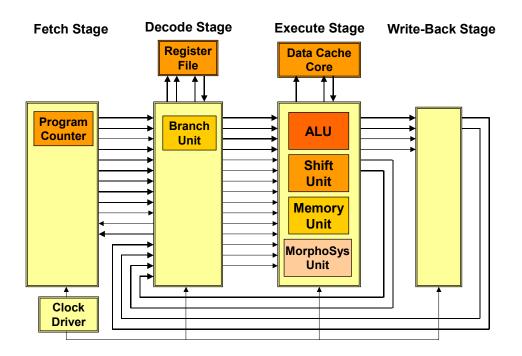

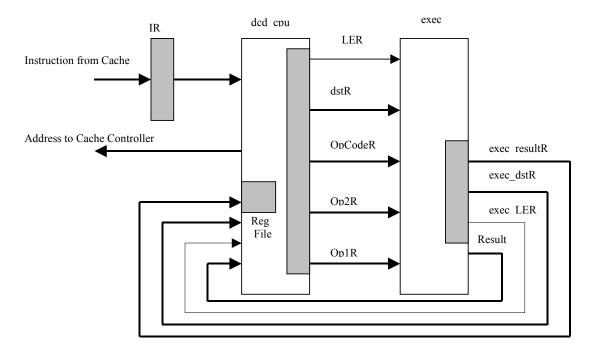

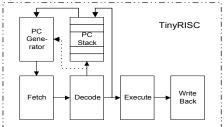

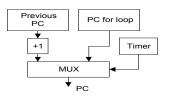

| 1.1.4.         | TinyRISC                                         | 6  |

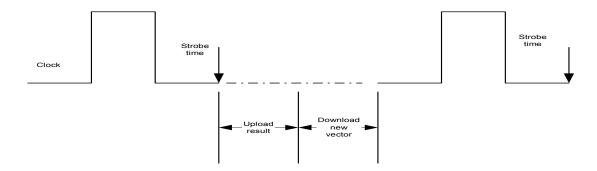

| 1.2. Mor       | phoSys Execution Model                           | 7  |

| 1.3. Exte      | ensions to the MorphoSys Model                   | 9  |

| 1.4. Rela      | ited Works                                       | 9  |

| 1.5. Sum       | mary of MorphoSys Architecture                   |    |

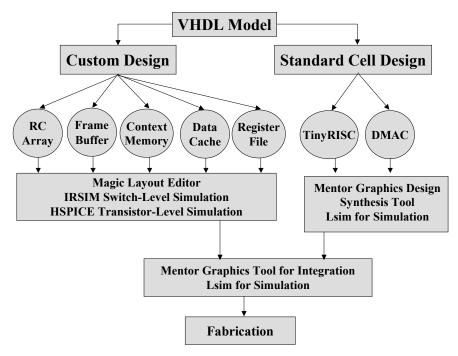

| 2. M1 Chip     | and VLSI Implementation of MorphoSys             |    |

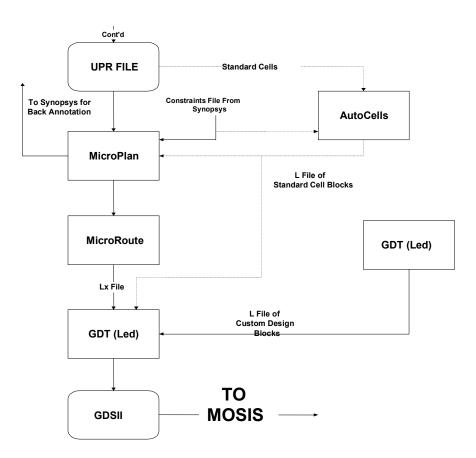

| 2.1. Des       | ign Methodology                                  |    |

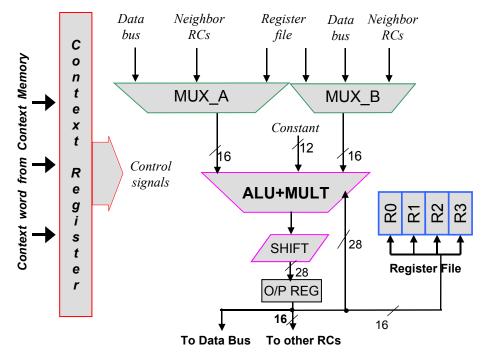

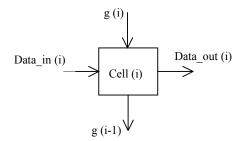

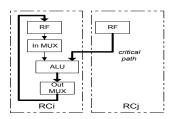

| 2.1.1.         | RC                                               |    |

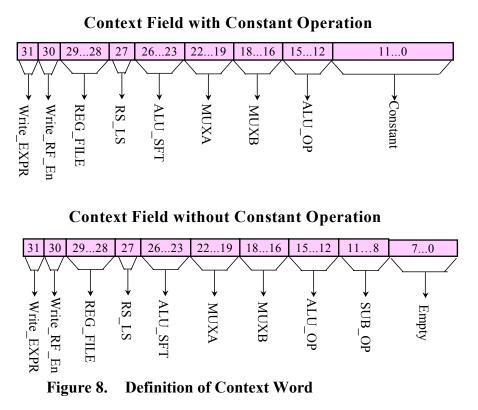

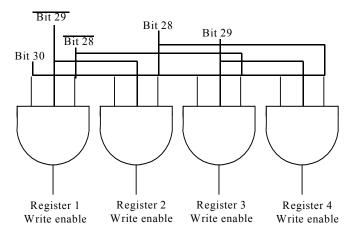

| 2.1.2.         | Context Register                                 |    |

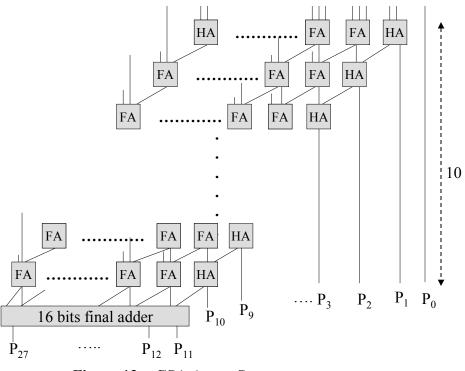

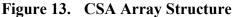

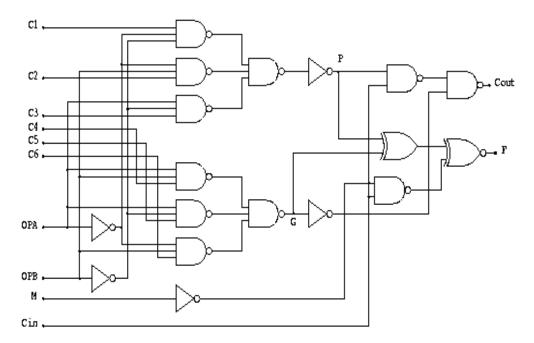

| 2.1.3.         | Multiplier                                       |    |

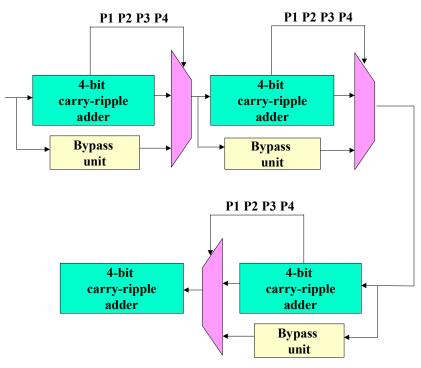

| 2.1.4.         | ALU                                              |    |

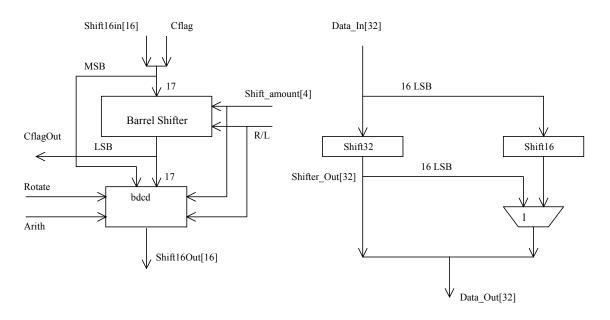

| 2.1.5.         | Shifter                                          |    |

| 2.1.6.         | One's Counter                                    |    |

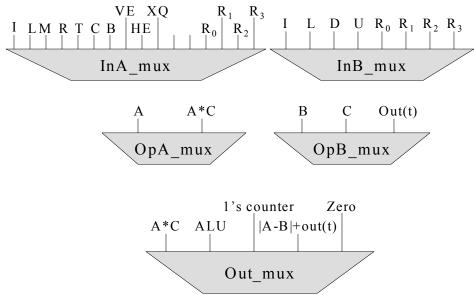

| 2.1.7.         | Muxes                                            |    |

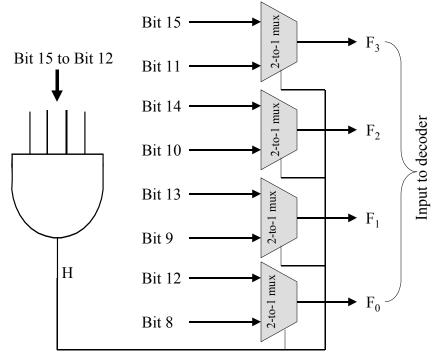

| 2.1.8.         | RC Decoder                                       |    |

| 2.1.8.1        | RC Simulation and Critical Path Analysis         |    |

| 2.1.9.         | TinyRISC                                         |    |

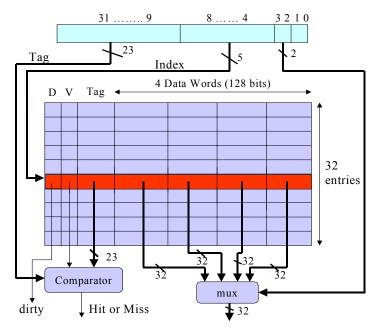

| 2.1.10.        | Context Memory                                   |    |

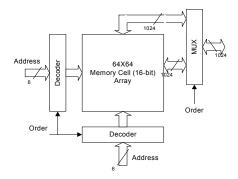

| 2.1.11.        | Frame Buffer                                     |    |

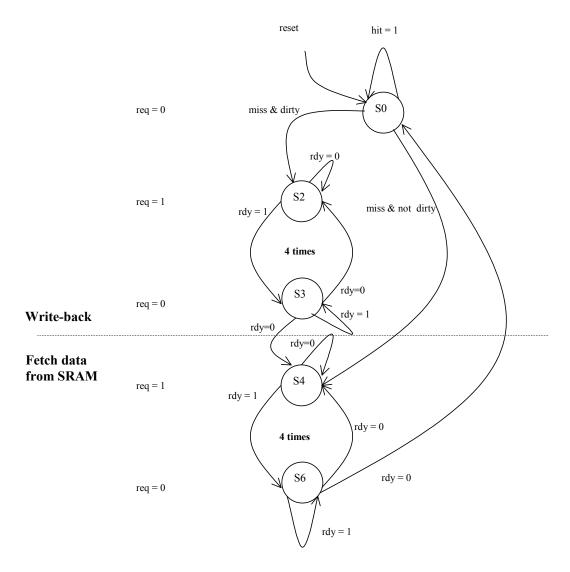

| 2.1.12.        | DMA Controller                                   |    |

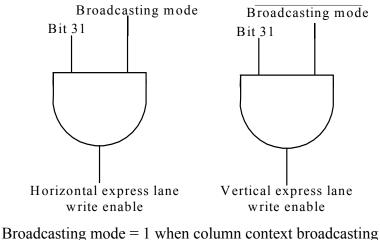

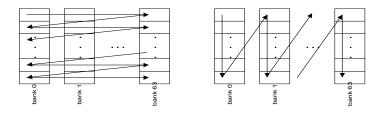

| 2.2. RC        | Array Interconnection Network and Global Routing |    |

| 2.3. The       | RC Array Layout                                  |    |

| 2.4. Phy       | sical Layout Design Methodology Development      |    |

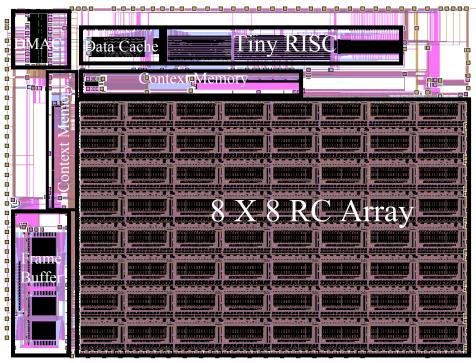

| 2.5. Mor       | phoSys M1 Layout and Top-Level Verification      |    |

|                | Testing                                          |    |

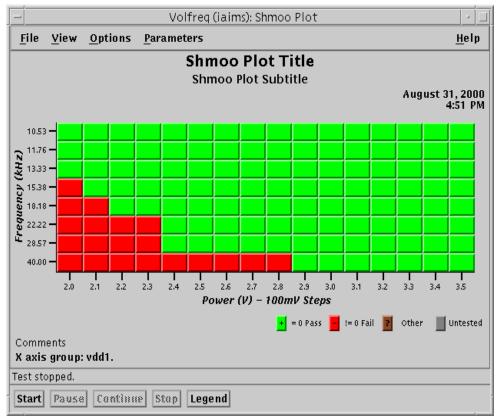

| 3.1. Gen       | eric Testing Methodology                         | 59 |

| 3.2. Pro       | Fest Testing Machine                             |    |

| 3.3. IMS       | Testing Machine                                  |    |

| 3.4. Test      | ing Results and Analysis                         |    |

| 3.4.1.         | Static Current of MorphoSys M1 Chip              |    |

| 3.4.2.         | Dynamic Current                                  |    |

| 3.4.3.         | Functionality Testing                            |    |

| 4. Program     | ning Environment and Performance Analysis        |    |

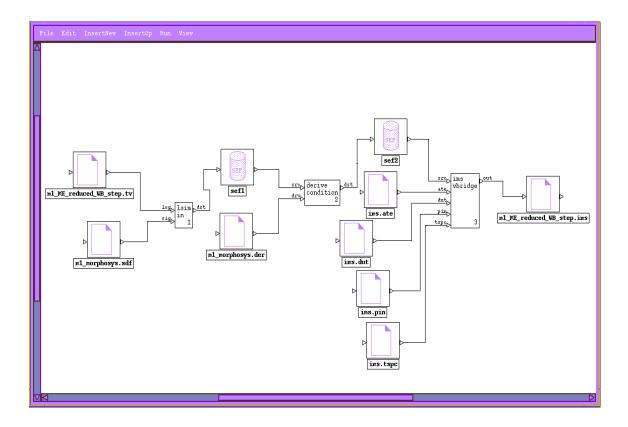

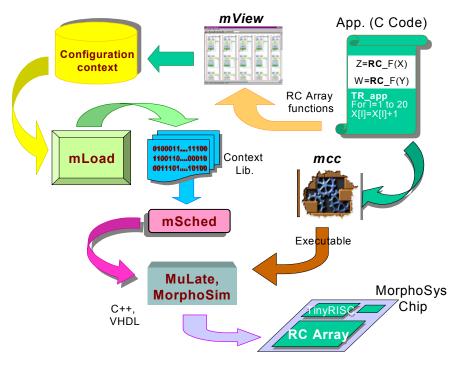

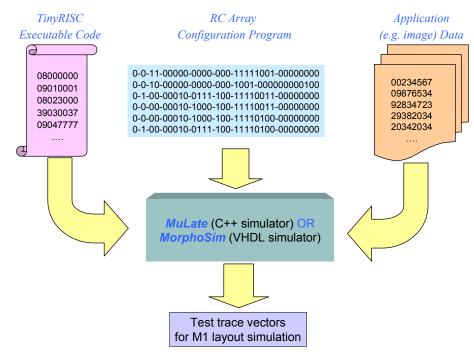

|                | gramming Environment                             |    |

|                | lication Mapping and Performance Analysis        |    |

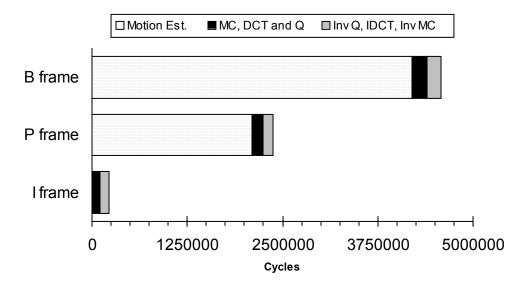

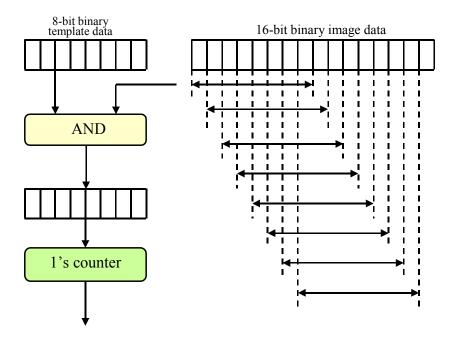

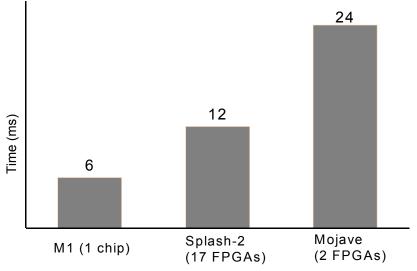

| 4.2.1. Moti   | on Estimation                                                  | 75  |

|---------------|----------------------------------------------------------------|-----|

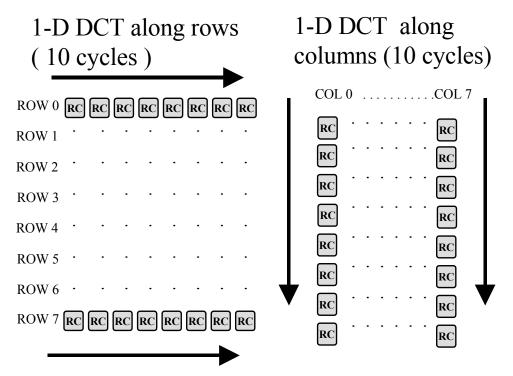

| 4.2.2. Disc   | rete Cosine Transform (DCT)                                    | 78  |

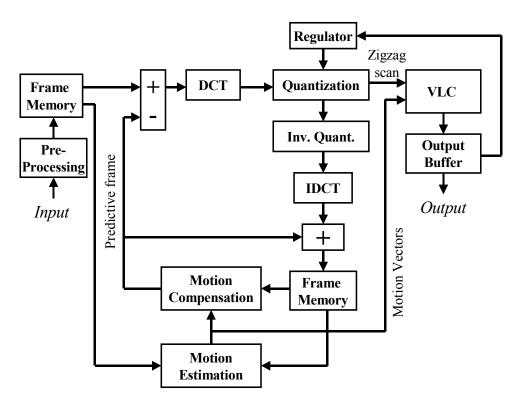

|               | G-2 Encoder Performance                                        |     |

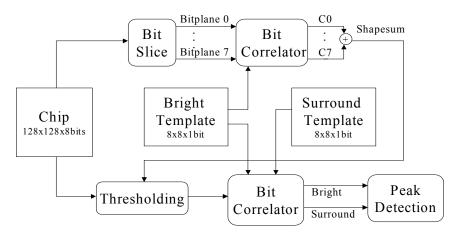

| 4.2.4. ATR    |                                                                | 84  |

| 4.3. Power Co | nsumption Estimation                                           | 90  |

|               | 1                                                              |     |

| •             | ۲<br>                                                          |     |

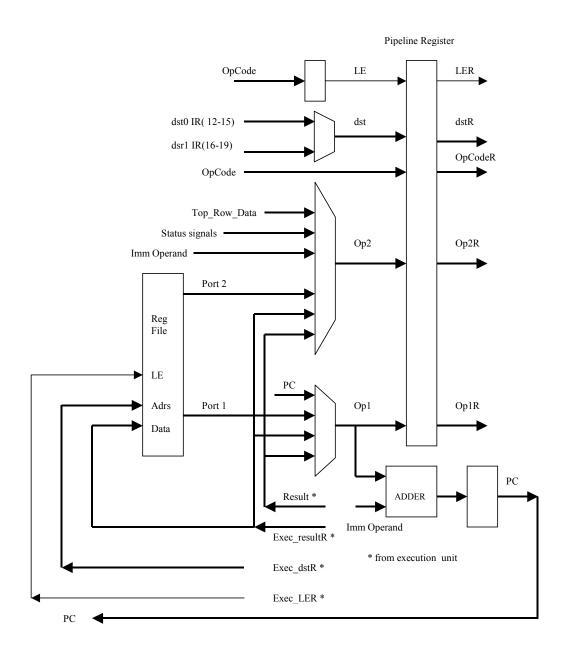

| 2             | сри                                                            |     |

|               | ution Unit                                                     |     |

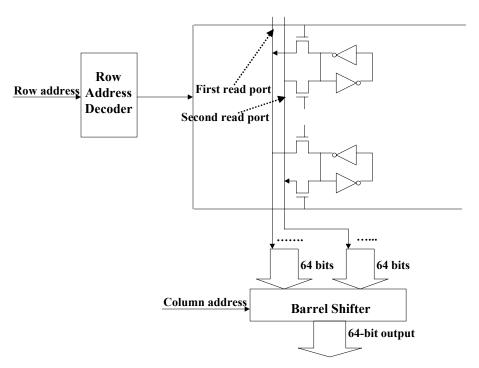

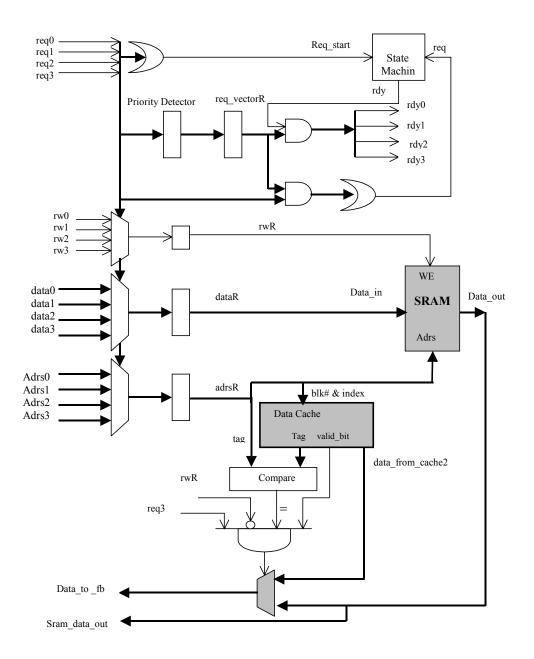

| 5.2. SRAM     |                                                                | 100 |

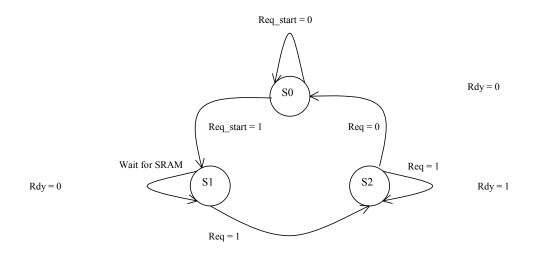

|               | ontroller (Arbitrator)                                         |     |

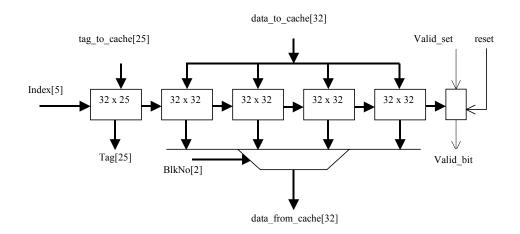

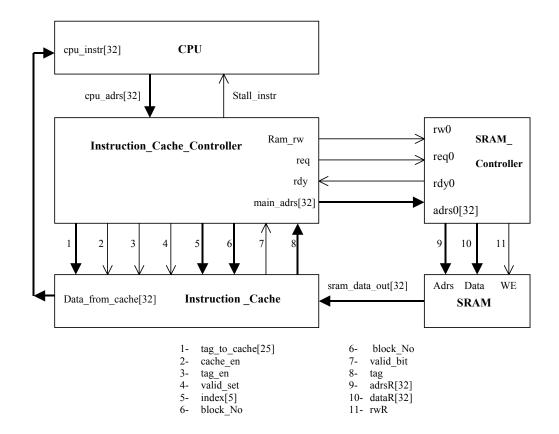

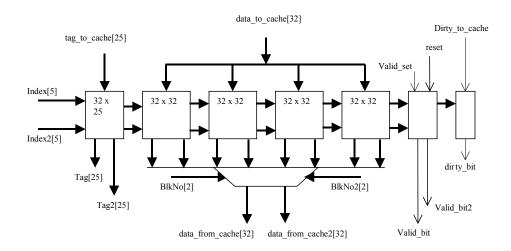

|               | n cache                                                        |     |

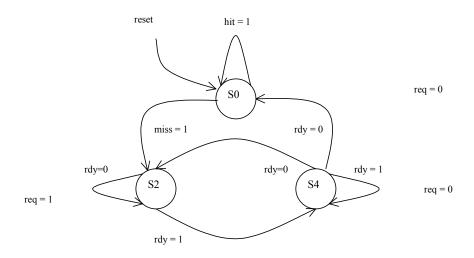

|               | n Cache Controller                                             |     |

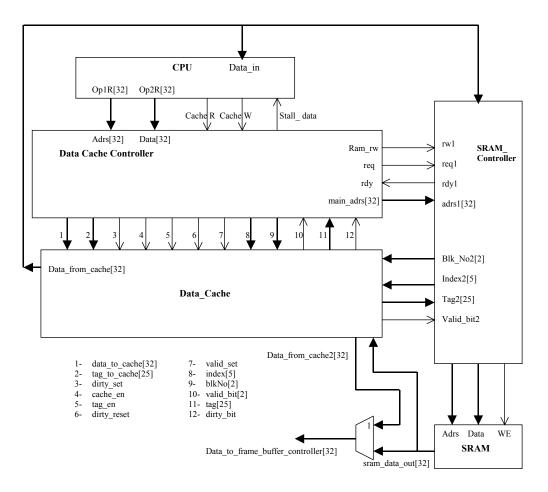

|               | ne Memory                                                      |     |

|               | ne Controller                                                  |     |

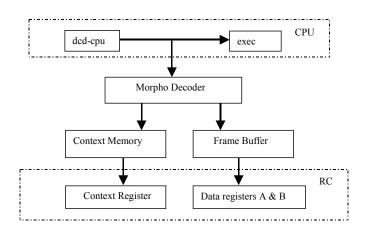

|               | Decoder                                                        |     |

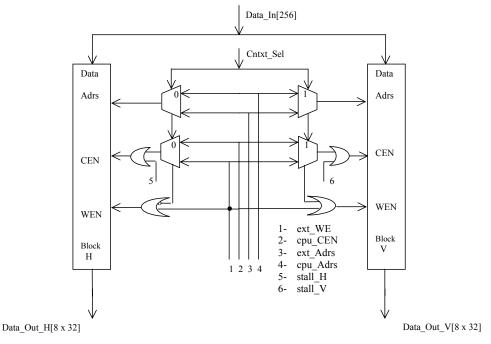

| 1             | Iemory                                                         |     |

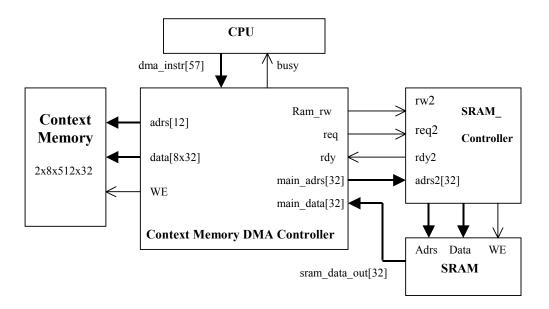

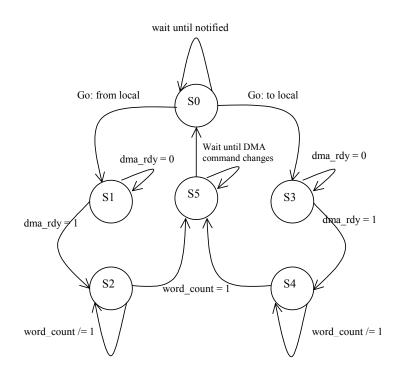

|               | t Memory DMA Controller                                        |     |

|               | Buffer                                                         |     |

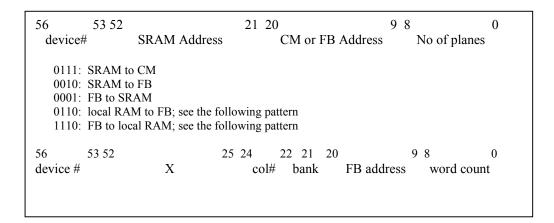

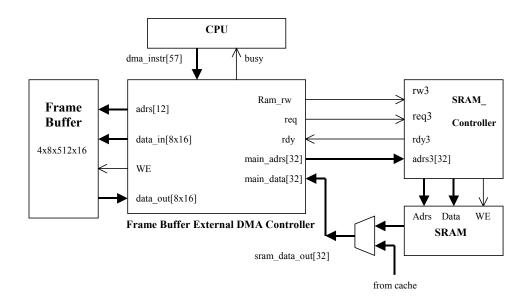

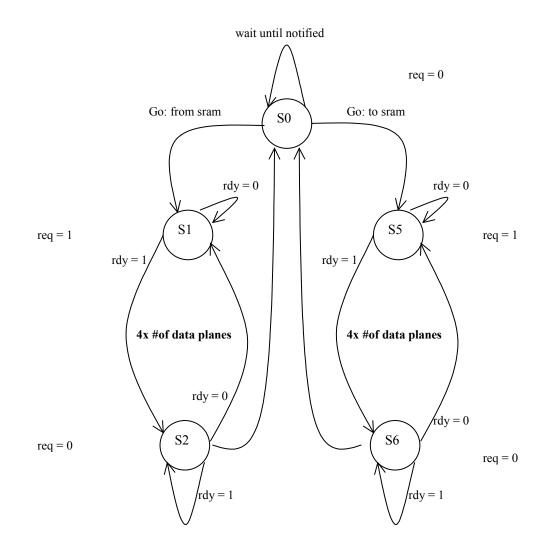

|               | Buffer External DMA Controller                                 |     |

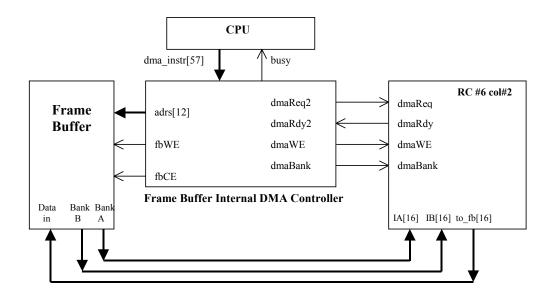

|               | Buffer Internal DMA Controller                                 |     |

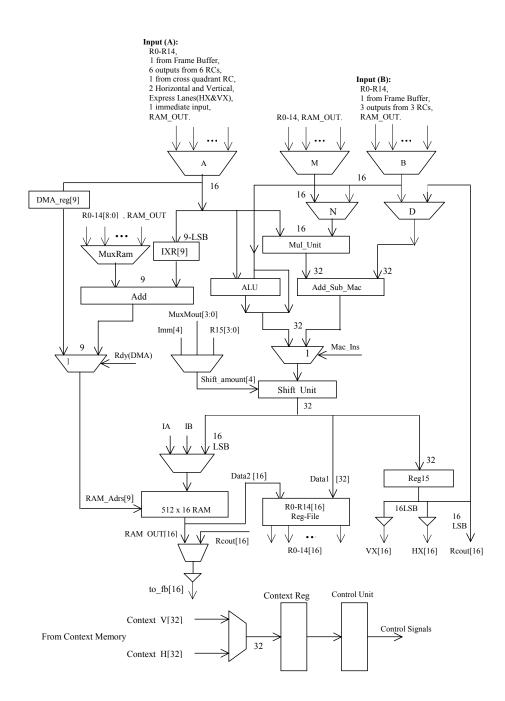

|               | ay                                                             |     |

|               | Unit                                                           |     |

| -             | Sub Mac Unit                                                   |     |

| -             | <br>[                                                          |     |

|               | unit                                                           |     |

|               | l RAM:                                                         |     |

|               | ster file                                                      |     |

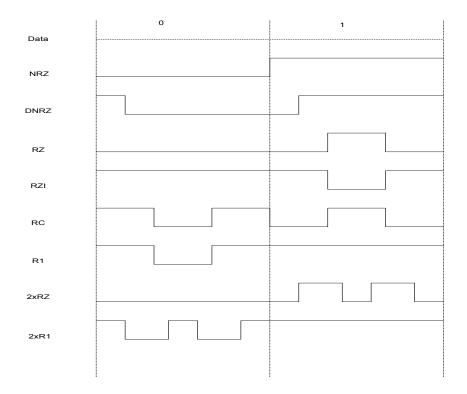

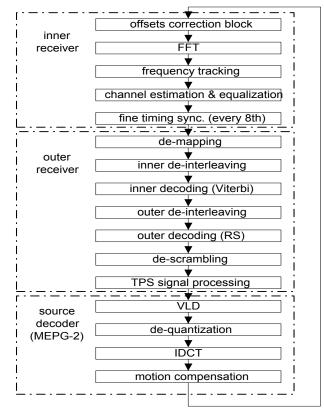

| Ŭ             | e Digital Video BroadcastingTerrestrial (DVB-T) Application    |     |

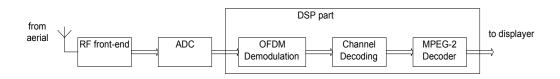

|               | ystem Design                                                   |     |

|               | B-T Receiver                                                   |     |

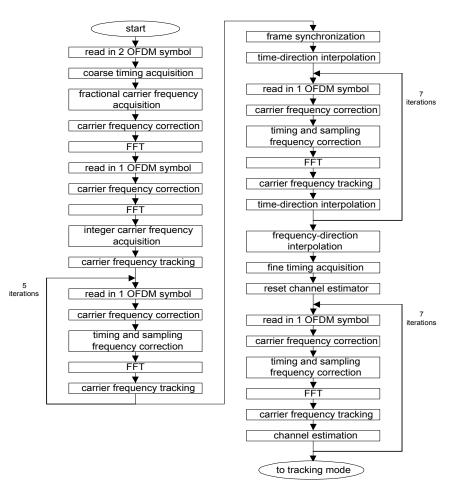

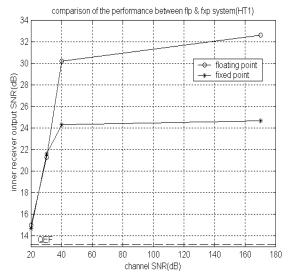

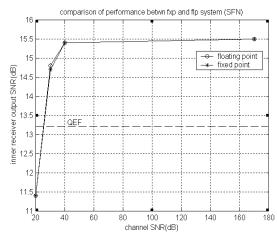

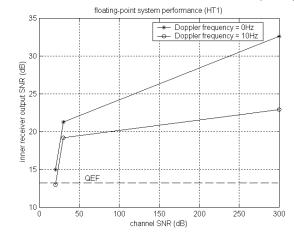

|               | ting-point System Design and Simulation                        |     |

|               | inel Simulator                                                 |     |

|               | meter Optimization (SNR Budgeting)                             |     |

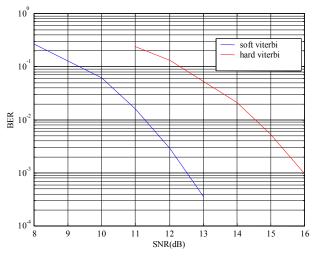

|               | d-point System Design and Simulation (Signal Quantization-Nois |     |

|               | Budgeting)                                                     |     |

|               | ys Architecture Revisited for DVB-T Application                |     |

|               | RISC modifications                                             |     |

|               | rray modifications                                             |     |

|               | Addifications                                                  |     |

| 6.3. Mapping  | DVB-T onto MorphoSys Architecture                              | 141 |

|               | ping Methodology                                               |     |

|               | ping Results                                                   |     |

|               | mary                                                           |     |

|               |                                                                |     |

| 9. References |                                                                | 160 |

| 10. List of ACRONYMS                             |  |

|--------------------------------------------------|--|

| Appendix A                                       |  |

| TinyRISC ISA-M1                                  |  |

| A.1 Instruction Formats                          |  |

| A.2 Instruction Codes                            |  |

| A.2.1 Arithmetic Instructions                    |  |

| A.2.2 Logical Instructions                       |  |

| A.2.3 Shift Instructions                         |  |

| A.2.4 Comparison Instructions                    |  |

| A.2.5 Load-Immediate Instructions                |  |

| A.2.6 Memory Access Instructions                 |  |

| A.2.7 Control Transfer Instructions              |  |

| A.2.8 MorphoSys Instructions                     |  |

| Appendix B                                       |  |

| mLoad                                            |  |

| B.1 Map.pl                                       |  |

| Appendix C                                       |  |

| DCT and Motion Estimation                        |  |

| C.1 DCT Context Configuration                    |  |

| C.2 DCT Assembly Code                            |  |

| C.3 Motion Estimation Context Configuration      |  |

| C.4 Part of Motion Estimation Assembly Code      |  |

| Appendix D                                       |  |

| Test Vector Format of ProTest                    |  |

| Appendix E                                       |  |

| Conversion Script for IMS Format                 |  |

| Appendix F                                       |  |

| Two New A-type Instructions in M2                |  |

| F.1 Read Status dr                               |  |

| F.2 Read RC specified by Col# from top row in dr |  |

| Appendix G                                       |  |

| MorphoSys-M2 Instructions                        |  |

| Appendix H                                       |  |

| RC Instruction Set Architecture - M2             |  |

## **List of Figures**

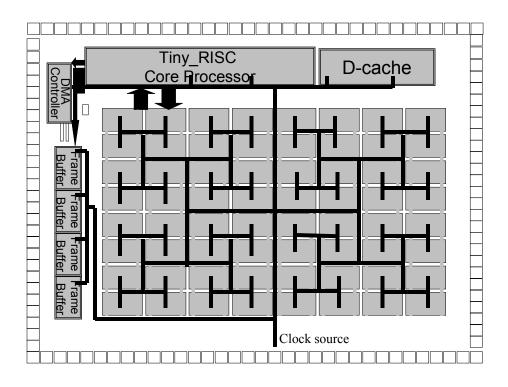

| MorphoSys Integrated Architectural Model                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

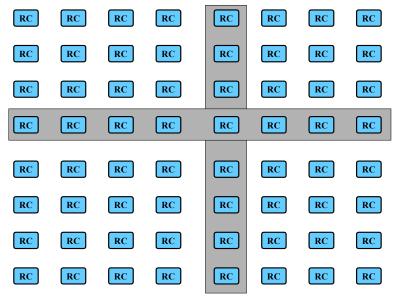

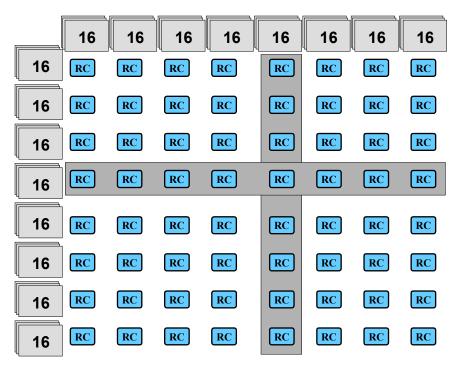

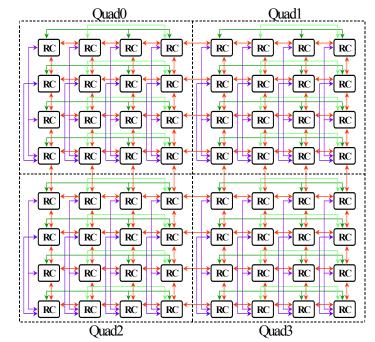

| An 8 by 8 RC Array                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

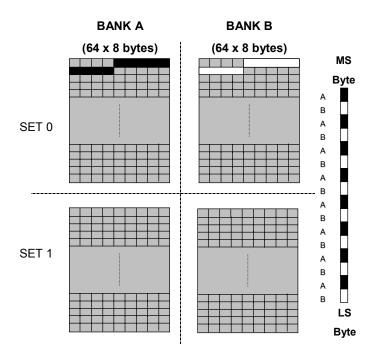

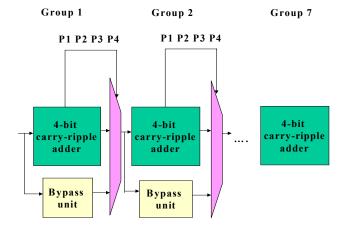

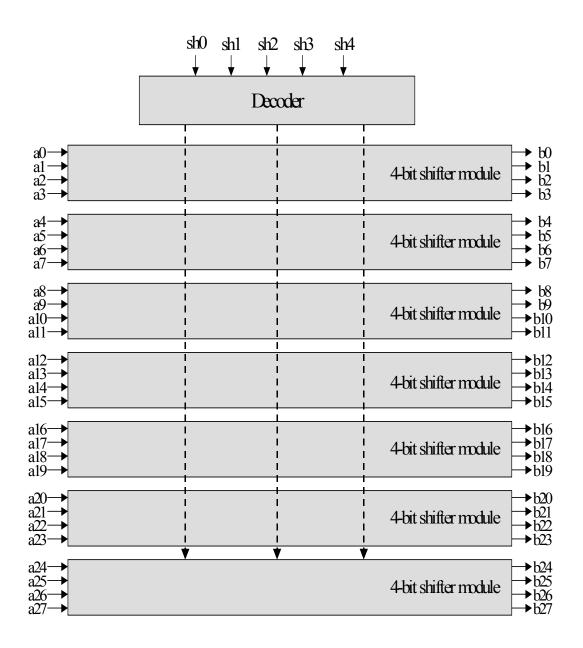

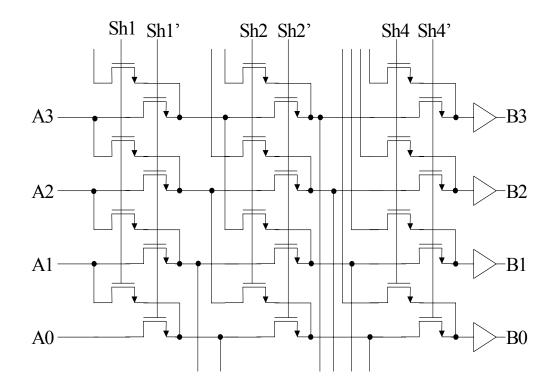

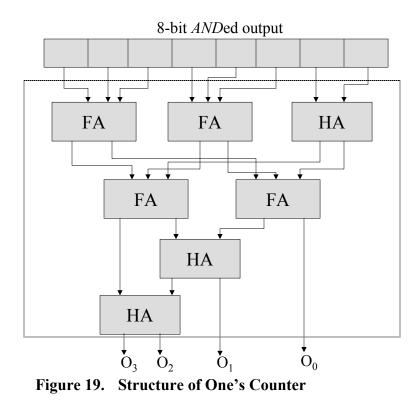

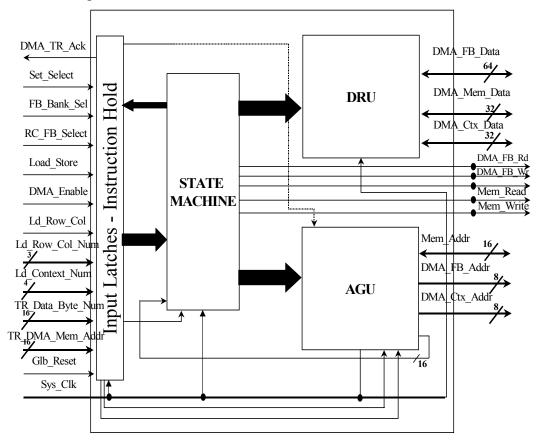

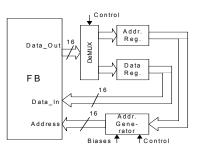

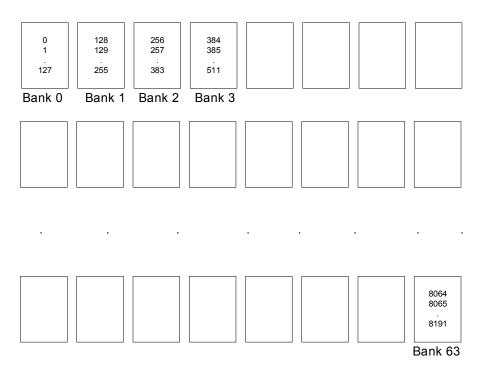

| Frame Buffer Block Diagram                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |