AFRL-IF-RS-TR-2003-28 Final Technical Report February 2003

# MICROELECTROMECHANICAL (MEMS)-BASED DATA STORAGE

**Hewlett Packard Laboratory**

Sponsored by Defense Advanced Research Projects Agency DARPA Order No. G176/06

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

The views and conclusions contained in this document are those of the authors and should not be interpreted as necessarily representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the U.S. Government.

AIR FORCE RESEARCH LABORATORY INFORMATION DIRECTORATE ROME RESEARCH SITE ROME, NEW YORK This report has been reviewed by the Air Force Research Laboratory, Information Directorate, Public Affairs Office (IFOIPA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

AFRL-IF-RS-TR-2003-28 has been reviewed and is approved for publication.

APPROVED:

WALTER A. KOZIARZ Project Engineer

FOR THE DIRECTOR:

JAMES A. COLLINS, Acting Chief Information Technology Division Information Directorate

## REPORT DOCUMENTATION PAGE

Form Approved OMB No. 074-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing this collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including

| suggestions for reducing this burden to Washington Hea<br>and to the Office of Management and Budget, Paperwoo                | adquarters Services, Directorate for In | formation Operations and Reports, 121 | 5 Jefferson Davis High                                          | way, Suite 1204, Arlington, VA 22202-4302,           |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|

| 1. AGENCY USE ONLY (Leave blank)                                                                                              | 2. REPORT DATE                          | 3. REPORT TYPE AND DATES COVERED      |                                                                 |                                                      |

|                                                                                                                               | FEBRUARY 2003                           |                                       | Final Aug 98 -                                                  |                                                      |

| 4. TITLE AND SUBTITLE MICROELECTROMECHANICAL                                                                                  | (MEMS)-BASED DATA                       | A STORAGE                             | 5. FUNDING N<br>C - F3060<br>PE - 63739<br>PR - E117<br>TA - 00 | 2-98-3-0232                                          |

| 6. AUTHOR(S) Peter Hartwell, Uija Yoon, Norman C. Tien, and Charles E. Hunt                                                   |                                         | WU - 43                               |                                                                 |                                                      |

| 7. PERFORMING ORGANIZATION NAM Hewlett Packard Laboratory 1510 Page Mill Road Palo Alto California 94304-1126                 | E(S) AND ADDRESS(ES)                    |                                       | 8. PERFORMIN<br>REPORT NU                                       | IG ORGANIZATION<br>IMBER                             |

| 9. SPONSORING / MONITORING AGEN<br>Defense Advanced Research Pro<br>3701 North Fairfax Drive<br>Arlington Virginia 22203-1714 | jects Agency AFRL/II<br>26 Elect        |                                       | AGENCY R                                                        | NG / MONITORING<br>EPORT NUMBER<br>-IF-RS-TR-2003-28 |

| 11. SUPPLEMENTARY NOTES  AFRL Project Engineer: Walter A. Koziarz/IFTC/(315) 330-2536/ Walter.Koziarz@rl.af.mil               |                                         |                                       |                                                                 |                                                      |

| 12a. DISTRIBUTION / AVAILABILITY ST<br>APPROVED FOR PUBLIC RELE                                                               |                                         | UNLIMITED.                            |                                                                 | 12b. DISTRIBUTION CODE                               |

| 13. ABSTRACT (Maximum 200 Words) This project developed and demo MEMS micromovers and electros                                | tatic motors required to                | o actuate these structure             | es, including s                                                 | uspension systems of                                 |

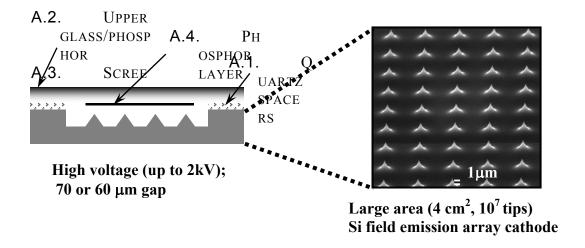

unprecedented high aspect ration by Hewlett Packard. Single and multiple level electrical interconnect fabrication techniques were developed and refined by Cornell University. A technique to fabricate large arrays of field emission tips was developed by U.C. Davis.

| 14. SUBJECT TERMS Micromover, Field Emission, I Interconnect, High-Density Da | 15. NUMBER OF PAGES<br>101<br>16. PRICE CODE |                                         |                            |

|-------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|----------------------------|

| 17. SECURITY CLASSIFICATION<br>OF REPORT                                      | 18. SECURITY CLASSIFICATION<br>OF THIS PAGE  | 19. SECURITY CLASSIFICATION OF ABSTRACT | 20. LIMITATION OF ABSTRACT |

| UNCLASSIFIED                                                                  | UNCLASSIFIED                                 | UNCLASSIFIED                            | UL                         |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. Z39-18 298-102

# **Table of Contents**

| Program Overview                                                       | 1  |

|------------------------------------------------------------------------|----|

| A. HEWLETT PACKARD                                                     | 1  |

| A.1. Introduction – Micromovers and Surface Drives                     | 1  |

| A.2. Process Short Loops                                               |    |

| A.2.1. Flexure etching.                                                |    |

| A.2.2. Flexure aspect ratio                                            |    |

| A.2.3. Platform flatness                                               |    |

| A.2.4. Metal on flexures                                               |    |

| A.3. Integrated Actuator Process Design                                |    |

| A.4. Fabrication                                                       |    |

| A.4.1. Process Improvements                                            |    |

| A.4.2. Completed device                                                |    |

| A.4.3. Process yield                                                   |    |

| A.5. Testing                                                           |    |

| A.5.1. Test setup                                                      |    |

| A.5.2. Mechanical properties                                           |    |

| A.5.3. Electrical performance                                          |    |

| A.6. Evaluation                                                        |    |

| A.6.1. Comparison to models                                            |    |

| A.6.2. In-plane Micromover performance with integrated actuator        |    |

| A.6.3. Z height Stability                                              |    |

| A.6.4. Comparison to design parameters for system                      |    |

| A.7. Two Axis Motion                                                   |    |

| A.8. Conclusions                                                       |    |

| B. CORNELL UNIVERSITY                                                  |    |

|                                                                        |    |

| B.1. Introduction and Goals                                            |    |

| 2 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                |    |

|                                                                        |    |

| B.2.2. Improved Process                                                |    |

| B.2.3. Two-Dimensional Micromover                                      |    |

| B.4. Conclusion:                                                       |    |

| B.5. Bibliography:                                                     |    |

|                                                                        |    |

| C. UNIVERSITY OF CALIFORNIA AT DAVIS                                   | 58 |

| C.1. INTRODUCTION                                                      | 58 |

| C.1.1. Previous work at UCD (background)                               | 58 |

| C.1.2. Need for these tasks                                            | 59 |

| C.2. Specific description of proposed tasks                            | 60 |

| C.2.1. Singly addressable tip array fabrication                        | 60 |

| C.2.2. Process description                                             | 61 |

| C.3. Singly-Addressable Arrays of Polysilicon Field-Emission Cathodes. | 62 |

| C.3.1. Experimental Details                                            | 62 |

| C.3.2. Discussion.                                                                                                                                 | 64        |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| C.4. Surface Treatment On Silicon Field-Emission Cathodes                                                                                          | 66        |

| C.4.1. Results and Discussion                                                                                                                      | 67        |

| C.4.2. Double-Gated Singly Addressable Polysilicon Tip Array                                                                                       | 71        |

| C.4.3. Surface treatment of the emission tips                                                                                                      |           |

| C.4.4. Study of Emission Behavior of UNCD Coated Silicon Field Emitter Array in Differ                                                             | ent Gases |

| and Pressures                                                                                                                                      |           |

| C.4.5. Effect Of Gases on the Field Emission Properties of UNCD Coated Silicon Field E                                                             | mitter    |

| Arrays 81                                                                                                                                          |           |

| C.5. Study of Field Emission Characteristics from Silicon Field Emitter Arrays Coated with                                                         |           |

| Ferroelectric Material                                                                                                                             |           |

| C.5.1. Deposition Process                                                                                                                          |           |

| C.5.2. Measurement Setup                                                                                                                           |           |

| C.5.3. Results and Discussion                                                                                                                      |           |

| C.6. PUBLISHED ARTICLES                                                                                                                            |           |

| C.7. REFERENCES                                                                                                                                    | 91        |

|                                                                                                                                                    |           |

| List of Figures and Tables                                                                                                                         |           |

| List of Figures and Tables                                                                                                                         |           |

| FIGURE A1. BIPOLAR MOTOR ELECTRODE PATTERNS. LEFT SHOWS STATE 1, RIGHT SHOWS STATE                                                                 | e 2. One  |

| ELECTRODE HAS CHANGED POTENTIAL CAUSING A SHIFT OF THE ROTOR BY ONE "STEP" TO                                                                      | THE       |

| RIGHT                                                                                                                                              | 2         |

| FIGURE A2: TYPICAL TEST STRUCTURE LAYOUT.                                                                                                          | 3         |

| FIGURE A3: SOI DRIE PROCESS FLOW CHART                                                                                                             | 4         |

| FIGURE A4 SEM PHOTOMICROGRAPH OF A COMPLETED NIFE COATED MICROMOVER                                                                                |           |

| FIGURE A5 CROSS-SECTIONAL SEM PHOTOMICROGRAPHS OF DEEP-ETCHED FLEXURES                                                                             |           |

| FIGURE A6: LEFT: LAYOUT OF A TYPICAL TEST STRUCTURE. THE CROSS-SECTION IS INDICATED I                                                              | 3Y LINE   |

| AA. RIGHT: SEM MICROGRAPH OF THE CROSS-SECTIONED DEVICE                                                                                            |           |

| FIGURE A7: SEM MICROGRAPHS OF EPOXY-POTTED CROSS-SECTIONS                                                                                          |           |

| FIGURE A8. SURFACE CONTOUR MAP OF MICRO-MOVER.                                                                                                     |           |

| FIGURE A9: SHORT LOOP INTERCONNECT TEST. (1) A SILICON WAFER IS COATED WITH A LOW-ST                                                               |           |

| NITRIDE (LSN) DIELECTRIC, A MO METALLIZATION, AND A LOW TEMPERATURE CVD OXID                                                                       | ` ′       |

| MASKING LAYER. (2) THE OXIDE, METAL, NITRIDE, AND SILICON STACK IS PLASMA ETCHED                                                                   |           |

| FLEXURE WITH AN INSULATED METAL LAYER ON TOP.                                                                                                      |           |

| FIGURE A10: (LEFT) CROSS-SECTIONAL SEM OF A FLEXURE WITH 100:1 ASPECT RATIO. (RIGHT)                                                               |           |

| SECTIONAL SEM OF SELF-ALIGNED INTERCONNECT METAL                                                                                                   |           |

| FIGURE A11: MODIFIED PROCESS FLOW FOR PRODUCING MICROMOVERS WITH METALLIZATION.                                                                    |           |

| SILICON WAFER IS COATED WITH A LOW-STRESS NITRIDE (LSN) DIELECTRIC, A MO METALI                                                                    |           |

| AND A LOW TEMPERATURE CVD OXIDE (LTO) MASKING LAYER. (2) THE OXIDE, METAL, A                                                                       |           |

| NITRIDE STACK IS PLASMA ETCHED. (3) DEEP CAVITIES ARE ETCHED INTO THE BACK SIDE O                                                                  |           |

| WAFER. (4) THE WAFER IS BONDED TO A CARRIER WAFER WITH PHOTORESIST. (5) FLEXURE                                                                    |           |

| DEEP ETCHED ON THE FRONT SIDE OF THE WAFER. (6) THE CARRIER WAFER IS REMOVED IN                                                                    |           |

| ACETONE                                                                                                                                            |           |

| FIGURE A12. FLEXURE FIRST PROCESS FLOW. (1) SOI SILICON WAFER IS COATED WITH A LOW-S'                                                              |           |

| NITRIDE (LSN) DIELECTRIC AND A MO METALLIZATION. (2) PHOTORESIST MASK IS USED T                                                                    |           |

| PATTERN THE METAL AND NITRIDE STACK. (3) FLEXURES ARE DEEP ETCHED WITH THE SAM                                                                     |           |

| (4) CARRIER WAFER WITH A RECESS, BONDED WITH PHOTORESIST, IS USED TO PROTECT THE WAFER DURING BACKSIDE PROCESSING. (5) DEED CAVITIES ARE EXCHEDING |           |

| SIDE OF THE WAFER DURING BACKSIDE PROCESSING. (5) DEEP CAVITIES ARE ETCHED INTO                                                                    | THE       |

| BACK SIDE OF THE WAFER WITH A THICK RESIST MASK. (6) THE CARRIER WAFER IS REMOVED                    |        |

|------------------------------------------------------------------------------------------------------|--------|

| ACETONE AND THE STRUCTURES ARE RELEASED IN A LIQUID HF DIP                                           |        |

| FIGURE A13.SEM IMAGE OF THE BACK-SIDE OF A COMPLETED SUSPENDED TEST STRUCTURE                        | 12     |

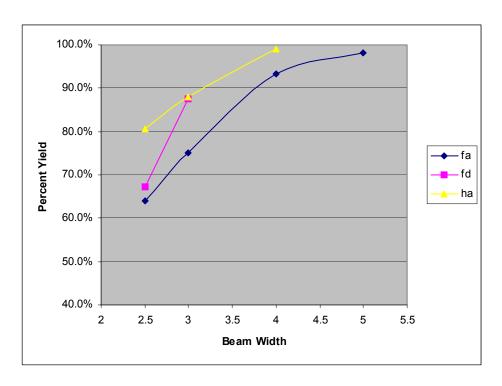

| FIGURE A14. PERCENT YIELD AS A FUNCTION OF FLEXURE WIDTH. YIELD DATA FROM THE REV B                  |        |

| MICROMOVER PROCESS DEMONSTRATES THAT WE CAN SUCCESSFULLY FABRICATE ARRAYS                            |        |

| WORKING MICROMOVERS AT HP LABS.                                                                      |        |

| FIGURE A15. SCHEMATIC OF MICRO-MOVER EVALUATION SYSTEM.                                              |        |

| FIGURE A16. MAGNET AND SHAKER CONFIGURATION FOR OFF CHIP EXCITATION OF MICRO-MOVE                    |        |

| FIGURE A17. PHOTOGRAPHS OF THE TEST SETUP AND THE SUPPORT EQUIPMENT RACK                             |        |

| FIGURE A18. CALIPER SOFTWARE, WRITTEN AT HP, TO MEASURE THE MOTION OF MEMS DEVICES                   |        |

| OPTICAL MEASUREMENTS ARE DONE BY DETERMINING THE GAP BETWEEN MOVING AND FIXE                         |        |

| MEMBERS USING IMAGE ANALYSIS ROUTINES. THE LEFT WIDNOW SHOWS THE USER INTERFA                        |        |

| BOTTOM RIGHT WINDOW IS THE DEVICE WITH THE MEASUREMENT REGION OF INTEREST SHO                        |        |

| THIN YELLOW LINE BRIDGING A TRENCH. THE TOP RIGHT WINDOW IS A DISPLAY OF THE IMAG                    |        |

| ANALYSIS ROUTINE. THE BRIGHTNESS PROFILE OF THE REGION OF INTEREST IS SHOWN IN TH                    |        |

| PROFILE" PLOT.                                                                                       |        |

| FIGURE A19. PHOTOGRAPH OF COFFIN INTEGRATED WITH MEMS TESTING SYSTEM                                 |        |

| FIGURE A20.COFFIN CAD DRAWINGS                                                                       |        |

| FIGURE A21 MEASURED SUSPENSION STIFFNESS RATIO (KZ/KX) AS A FUNCTION OF FLEXURE HEIG                 | НТ-ТО- |

| WIDTH ASPECT RATIO (AR). THE IDEAL DASHED LINE IS THE THEORETICAL LIMIT FOR A                        |        |

| RECTANGULAR CROSS-SECTIONED BEAM IN PURE BENDING.                                                    |        |

| FIGURE A22 LOSS IN STIFFNESS RATIO VERSUS DISPLACEMENT. THE ASPECT RATIO OF EACH SPEC                |        |

| INDICATED IN THE PLOT LEGEND.                                                                        |        |

| FIGURE A23 NONLINEAR STIFFNESS LOSS VERSUS DISPLACEMENT FOR VARIOUS ASPECT RATIOS.                   |        |

| CASE, THE MEASURED CHANGE IN KX/KZ IS PLOTTED AND FIT WITH A PARABOLA IN $X^2$                       |        |

| FIGURE A24. MEASURED BEAM PROFILES AND WIDTHS ESTIMATED WITH EQUATION (2)                            |        |

| FIGURE A25.NOMINAL STIFFNESS RATIO ( $K_{zo}/K_{x0}$ ) VS. ASPECT RATIO SQUARED. A LINEAR FIT TO T   |        |

| DATA IS INDICATED WITH A DASHED LINE, WHILE A SOLID LIKE INDICATED THE THEORETICA                    |        |

| From F. A.C. Margon course Margon by Purpose and Program of the Archive Course and                   |        |

| FIGURE A26. MICROMOVER MOTION BY INTEGRATED BIPOLAR ELECTROSTATIC MOTION. STEP SIZ                   |        |

| ABOUT 0.5 UM.                                                                                        |        |

| FIGURE A27. MICRO-MOVER STEPS AS A FUNCTION OF SQUARED VOLTAGE                                       |        |

| FIGURE A28. INITIALIZING ELECTRODE MOVEMENT                                                          |        |

| FIGURE A29. PLOT OF Z-AXIS DISPLACEMENT AS A FUNCTION OF VOLTAGE. POWER SUPPLY IS A SO               |        |

| 5 V/DIV. DISPLACEMENT IS 10 NM/DIV.                                                                  |        |

| FIGURE A 21. PLOT OF Z. AVIS MOVEMENT AS A PUNCTION OF STEPPING VOLTAGE                              |        |

| FIGURE A31. PLOT OF Z-AXIS MOVEMENT AS A FUNCTION OF STEPPING VOLTAGE                                |        |

|                                                                                                      |        |

| FIGURE A33. CALCULATED AND MEASURED VALUES FOR STEPS TO DECOG EVENT AS A FUNCTION OPERATING VOLTAGE. |        |

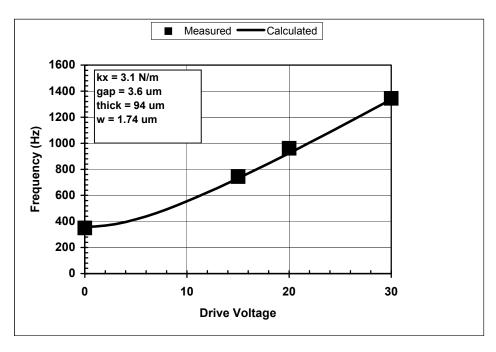

| FIGURE A34. CALCULATED AND MEASURED VALUES FOR THE DEPENDENCE OF IN-PLANE NATURA                     |        |

| FREQUENCY ON OPERATING VOLTAGE.                                                                      |        |

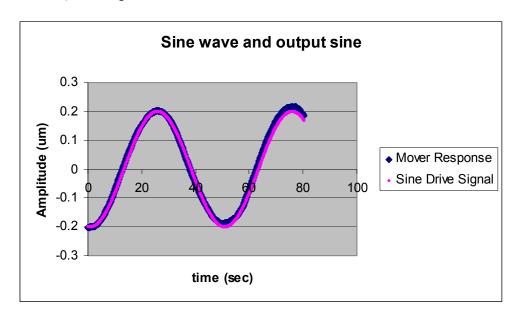

| FIGURE A35. RESPONSE OF MICROMOVER TO SINE WAVE ON PROPORTIONAL ELECTRODE.                           |        |

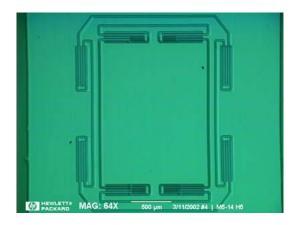

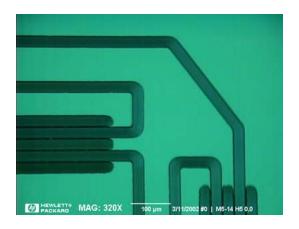

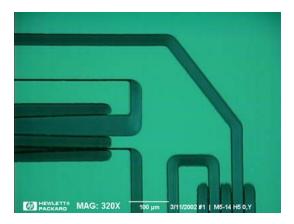

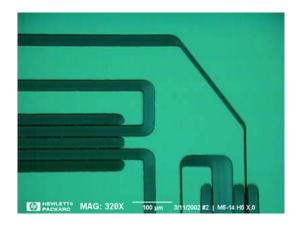

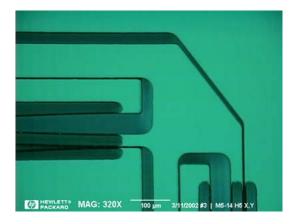

| FIGURE A36. A 4UM H-STYLE MICROMOVER, DEVICE NUMBER H5 FROM WAFER M5-14.                             |        |

| FIGURE A37. DEVICE H5 AT THE HOME POSITION.                                                          |        |

| FIGURE A38. DEVICE H5 AT THE Y MAX POSITION                                                          |        |

| FIGURE A39. DEVICE H5 AT THE Y MAX POSITION                                                          |        |

| FIGURE A40. DEVICE H5 AT THE X AND Y MAX POSITIONS.                                                  |        |

| FIGURE B. THE OVERALL OBJECTIVE OF THIS PORTION OF THE PROGRAM IS TO PROVIDE                         | 30     |

| INTERCONNECTION TO THE MICROMOVER                                                                    | 37     |

|                                                                                                      | 1 /    |

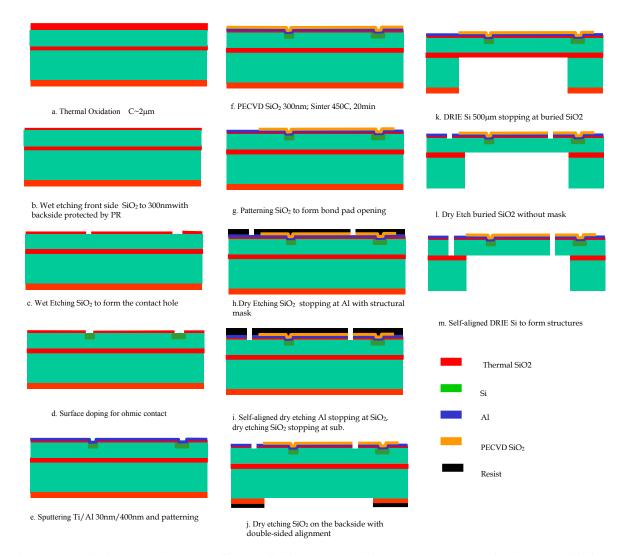

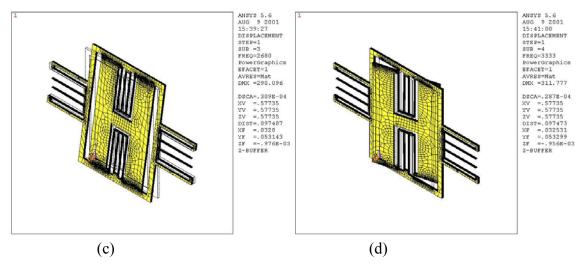

| FIGURE B1 THE BASIC PROCESS FLOW TO FABRICATE METAL INTERCONNECTS ON A SINGLE CRYSTAL               |      |

|-----------------------------------------------------------------------------------------------------|------|

| SILICON BEAM                                                                                        |      |

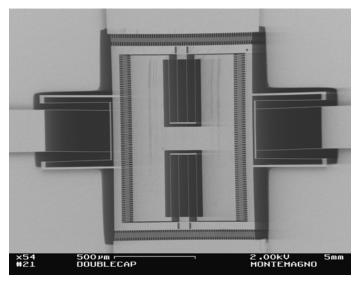

| FIGURE B2 A FABRICATED MOVER WITH AL INTERCONNECTION BEFORE BACKSIDE ETCHING                        | . 40 |

| FIGURE B3 CLOSE-UP VIEWS OF DIFFERENT PARTS. (A) A PART NEAR BOND PADS, (B) A PART OF THE           |      |

| COMB DRIVE, AND (C) A PART OF THE BEAM.                                                             |      |

| FIGURE B4 A MORE CLOSE-UP VIEW OF THE COMB DRIVE.                                                   |      |

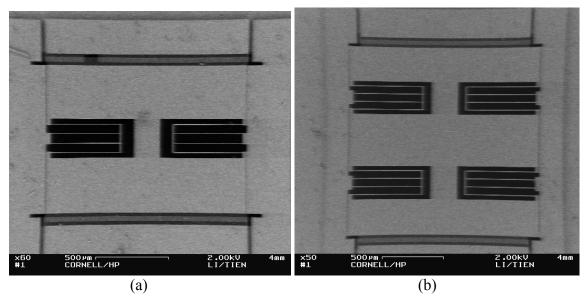

| FIGURE B5 A TWO-DIMENSIONAL MOVER BEFORE BACKSIDE ETCHING                                           | . 42 |

| FIGURE $B6$ A PICTURE OF BACKSIDE WHERE THE BURIED OXIDE BUCKLED AND BROKEN BECAUSE OF TI           | ΗE   |

| RESIDUE STRESS                                                                                      |      |

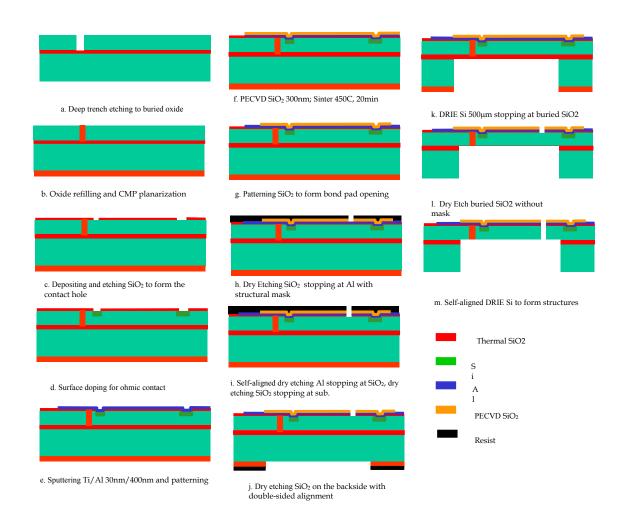

| FIGURE B7 THE IMPROVED PROCESS FLOW TO FABRICATE METAL INTERCONNECTS ON A SINGLE CRYST SILICON BEAM |      |

| FIGURE B8 A TWO-DIMENSIONAL MICROMOVER AFTER BACKSIDE ETCHING                                       |      |

| FIGURE B9 THE IMPROVED PROCESS FLOW TO FABRICATE METAL INTERCONNECTS ON A SINGLE CRYST              |      |

| SILICON BEAM WITH ISOLATION STRUCTURES                                                              |      |

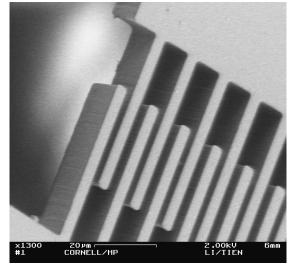

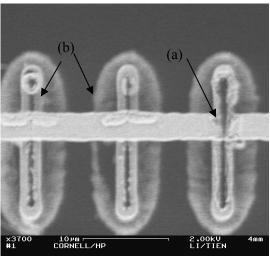

| FIGURE B10 A SEM PHOTO OF A FABRICATED STRUCTURE WITH AL INTERCONNECTION                            |      |

| FIGURE B11 A SEM PHOTO OF THE BACKSIDE OF A FABRICATED DEVICE                                       |      |

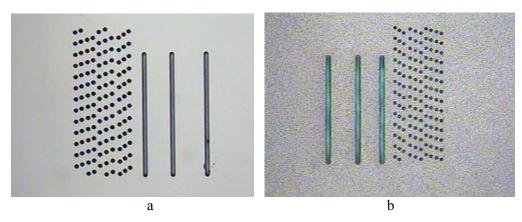

| FIGURE B12 (A) THE FILLED ISOLATION TRENCHES ARRAY AFTER CMP PLANARIZATION AS TEST                  |      |

| STRUCTURES, AND (B) A PART OF A TRENCH AT A HIGHER MAGNIFICATION. A VOID CAN BE SEEN I              | N    |

| THE TRENCH, BUT IT IS WELL SEALED ON THE SURFACE.                                                   |      |

| FIGURE B13 (A) A FRONT VIEW OF THE ISOLATION STRUCTURE WITH AL CROSSING IT, AND (B) A               |      |

| BACKSIDE VIEW OF THE ISOLATION STRUCTURE.                                                           | .47  |

| FIGURE B14 STRUCTURES TO CHARACTERIZE THE PERFORMANCE OF ISOLATION STRUCTURES. WIDTHS               |      |

| BEAMS ARE 2μM, 3μM AND 4μM FROM BOTTOM TO TOP                                                       |      |

| FIGURE B15 TWO FAILURE MECHANISMS OF ISOLATION STRUCTURES. (A) AL DISCONTINUITY CAUSED              |      |

| VOID IN OXIDE BAR, AND (B) SILICON RING                                                             |      |

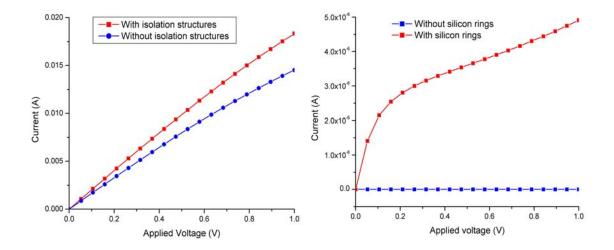

| FIGURE B16 I-V CURVES FOR ALUMINUM LINES OVER BEAMS WITH AND WITHOUT ISOLATION                      |      |

| STRUCTURES                                                                                          | . 49 |

| FIGURE B17 THE MEASURED RESISTANCES OF SILICON BEAMS WITH ISOLATION STRUCTURES BEFORE A             | ۸ND  |

| AFTER SILICON RINGS ARE REMOVED.                                                                    | . 49 |

| Figure B18 Long oxide bars (400 $\mu\text{m}$ ) with and without silicon proof mass attached to the |      |

|                                                                                                     | . 49 |

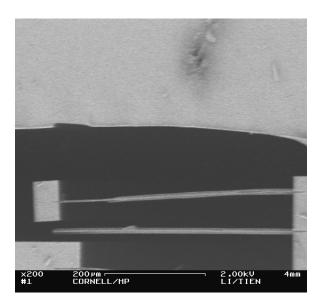

| FIGURE B19 A SEM PHOTO THE OXIDE-AL-OXIDE SANDWICH STRUCTURES USED AS INTERCONNECTS                 |      |

| OVER THE MOVABLE STRUCTURES. A LITTLE UNDERCUT OF AL CAUSED BY LATERAL ETCHING CA                   | N    |

| BE FOUND                                                                                            | . 50 |

| FIGURE B20 TWO TYPES OF RESONATORS TO TEST THE PERFORMANCE OF THE AL INTERCONNECTS. (A)             | )    |

| WITH ONE SET OF FOLDED SPRINGS, AND (B) WITH TWO SETS OF FOLDED SPRINGS                             | .51  |

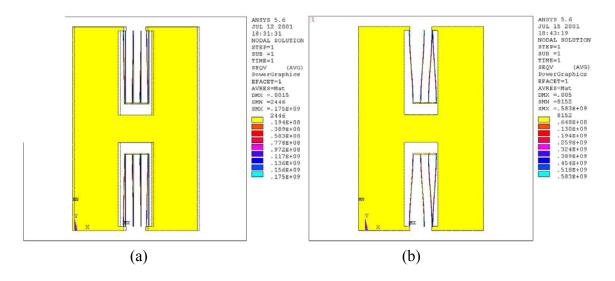

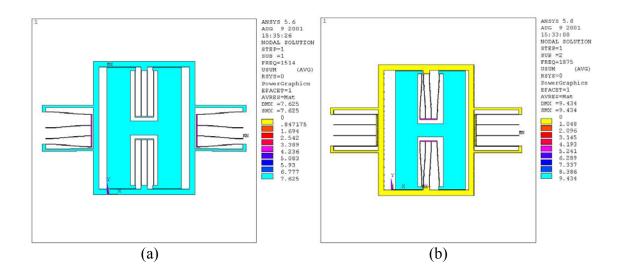

| FIGURE B21 USING ANSYS, THE SIMULATED STRESS DISTRIBUTION OF AL LINE ON THE RESONATOR. (            | A)   |

| WITH A DISPLACEMENT OF 15µM, AND THE MAXIMUM STRESS IS 17.5GPA. (B) WITH A                          |      |

| DISPLACEMENT OF 50μM, AND THE MAXIMUM STRESS IS 58.3GPA.                                            | .51  |

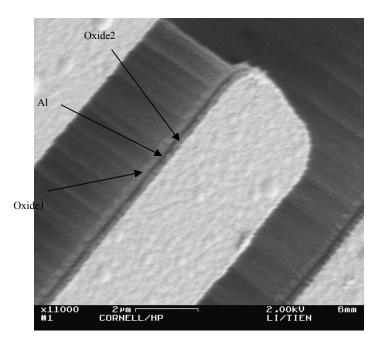

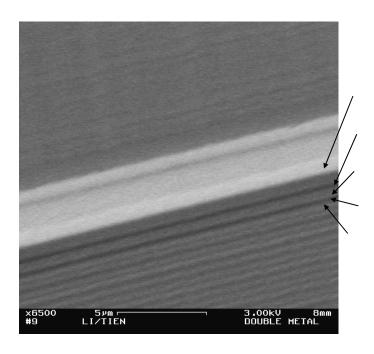

| FIGURE B22 A SEM PHOTO OF A FABRICATED BEAM USING THE INTERCONNECTION STRUCTURES WITH               |      |

| TWO-LEVEL AL LAYERS, OXIDE (500NM)/AL (300NM)/OXIDE (300NM)/AL (300NM)/OXIDE                        |      |

| (300nm)/Si structure                                                                                |      |

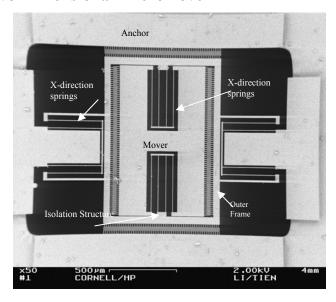

| FIGURE B23 THE SEM PHOTO A TWO-DIMENSIONAL MICROMOVER USING THE ISOLATION STRUCTURES                |      |

| FIGURE B24 THE FIRST FOUR MODES OF THE 2-DIMENTIONAL MICROMOVER SIMULATED BY ANSYS. T               | ΉE   |

| RESONANT FREQUENCIES ARE 1514HZ, 1875HZ, 2680HZ AND 3333HZ, RESPECTIVELY                            | . 54 |

| FIGURE B25 THE PROCESS FLOW TO FABRICATE DOUBLE SIDE METAL                                          | . 55 |

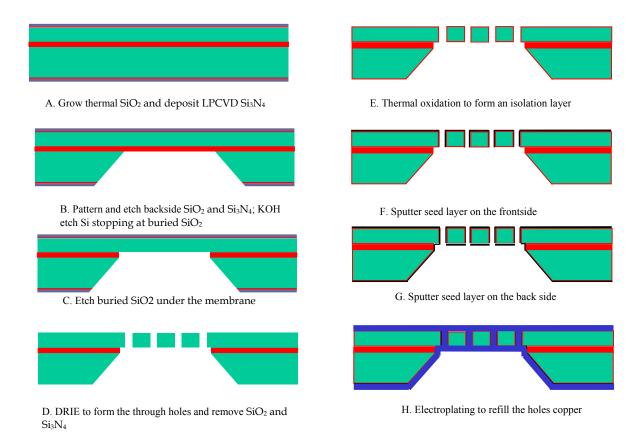

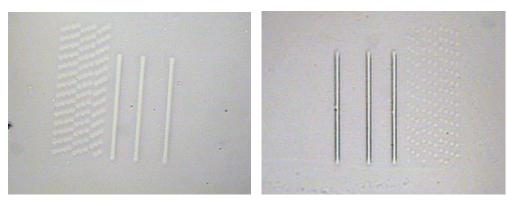

| FIGURE B26 MICROGRAPHS OF TESTING STRUCTURES ON FRONT SIDE (A) AND BACKSIDE (B) BEFORE              |      |

| COPPER PLATING.                                                                                     | . 56 |

| FIGURE B27 MICROGRAPHS OF TESTING STRUCTURES ON FRONT SIDE (A) AND BACKSIDE (B) AFTER               |      |

| COPPER PLATING                                                                                      | 56   |

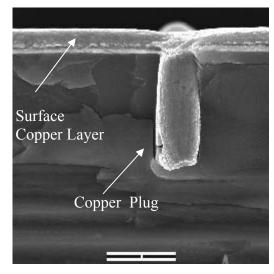

| FIGURE B28 CROSS-SECTIONAL SEM PICTURE OF A FILLED HOLE WITH A FLAT SURFACE                                                                  | 56  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

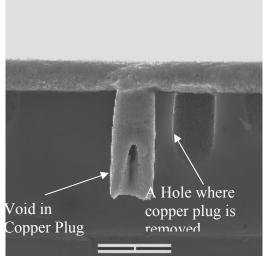

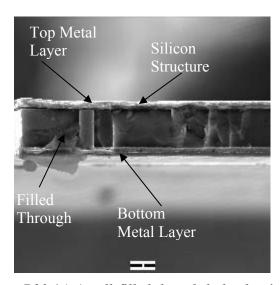

| FIGURE B29 A PLUG THAT IS BROKEN DURING SAMPLE PREPARING                                                                                     | 56  |

| FIGURE B30 (A) A WELL-FILLED THOUGH-HOLE PLUG INTERCONNECTING THE TOP METAL LAYER AND                                                        | ,   |

| THE BOTTOM METAL LAYER. (B) A CLOSE-UP VIEW                                                                                                  |     |

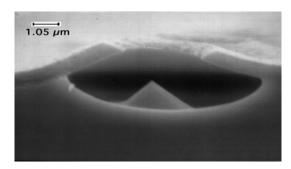

| FIGURE C1 AN ETCHED GATE DEVICE CONSISTING OF A SINGLE CRYSTAL SILICON EMITTER TIP, A SIO                                                    | 2   |

| DIELECTRIC LAYER, AND A POLYSILICON GATE.                                                                                                    |     |

| FIGURE C2: A) CONCENTRIC FOCUS GATE. B) APERTURE FOCUS GATE.                                                                                 |     |

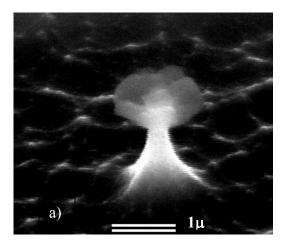

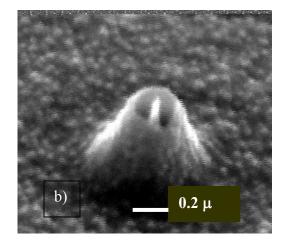

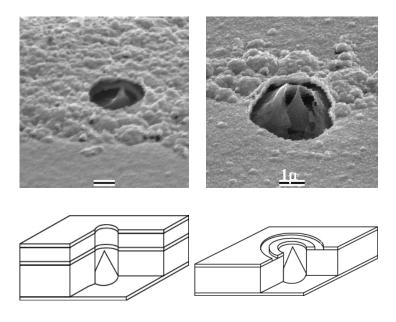

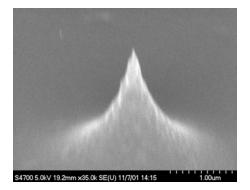

| FIGURE C3. A) POLYCRYSTALLINE SILICON TIP BEFORE OXIDATION SHARPENING. OXIDE CAP IS ON TO                                                    |     |

| THE TIP.B) A COMPLETED VOLCANO-TYPE FIELD-EMISSION CELL, HAVING 0.3 μ GATE OPENING A                                                         |     |

| APPROXIMATELY 15 NM TIP CURVATURE RADII.                                                                                                     |     |

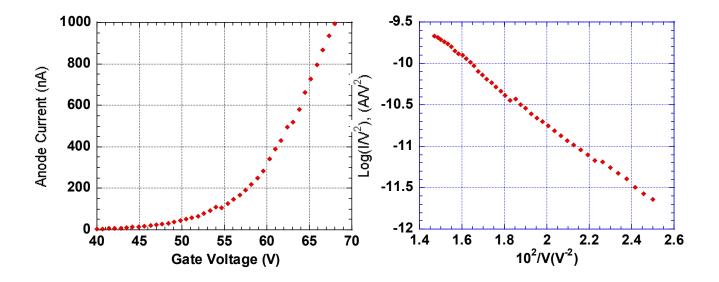

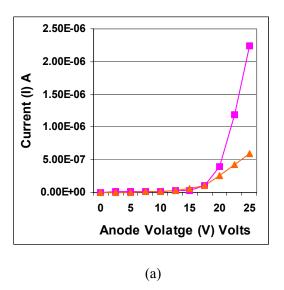

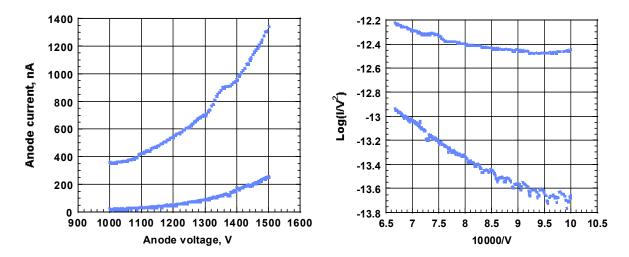

| FIGURE C4. A) (LEFT) ANODE CURRENT VS. GATE VOLTAGE PLOT AND B) (RIGHT) THE FOWLER-                                                          |     |

| NORDHEIM PLOT FOR THE ANODE CURRENT UP TO 1000 NA.                                                                                           | 65  |

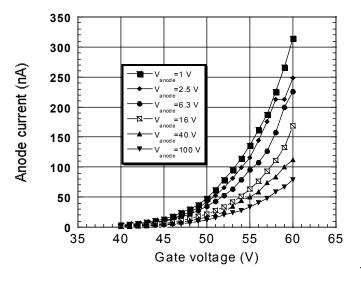

| FIGURE C5. ANODE CURRENT VS. GATE VOLTAGE AT DIFFERENT ANODE POTENTIALS RELATIVE TO GA                                                       |     |

| POTENTIAL (E.G. "TRIODE CHARACTERISTICS").                                                                                                   | 66  |

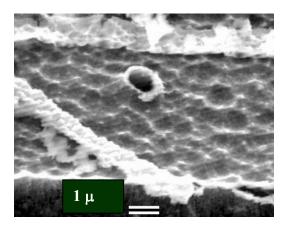

| FIGURE C6. SEM PICTURE SHOWING AN EXPLODED CELL, CAUSED BY EXCESSIVE STEADY-STATE                                                            |     |

| CATHODE CURRENT                                                                                                                              | 66  |

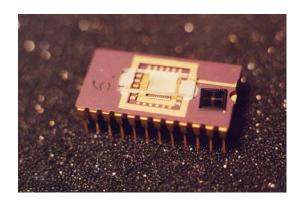

| FIGURE C7. TEST STRUCTURE. THE CATHODE IS MOUNTED ON TO A TO <sub>3</sub> TRANSISTOR PACKAGE                                                 | 67  |

| FIGURE C8. I-V CHARACTERISTICS (A) AND THE F-N CHARACTERISTICS (B) BEFORE (LOWER CURVE) A                                                    | ND  |

| AFTER (UPPER CURVE) THE SURFACE CONDITIONING BY LOW-ENERGY ELECTRON STIMULATED                                                               |     |

| DESORPTION UNDER LOW CURRENT LOADING.                                                                                                        | 68  |

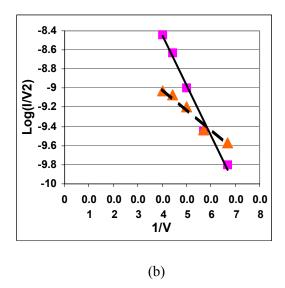

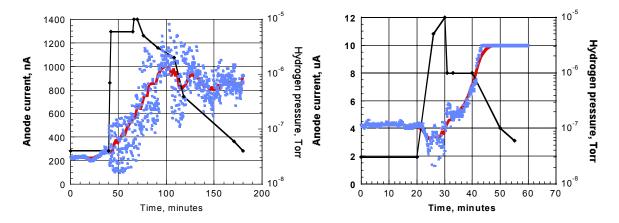

| FIGURE C9. THE EFFECT OF HYDROGEN TREATMENT ON SILICON FIELD-EMISSION ARRAY CATHODES                                                         |     |

| UNDER (A) (LEFT) HIGH (1500 V) AND (B) (RIGHT) LOW (22V) ANODE VOLTAGE                                                                       | 69  |

| FIGURE C10. I-V CHARACTERISTIC AND THE F-N CHARACTERISTIC BEFORE (LOWER CURVE) AND AFTE                                                      |     |

| (UPPER CURVE) THE "NATURAL" SURFACE CONDITIONING WAS PERFORMED BY INCREASING THE                                                             |     |

| PRESSURE OF RESIDUAL GASES.                                                                                                                  |     |

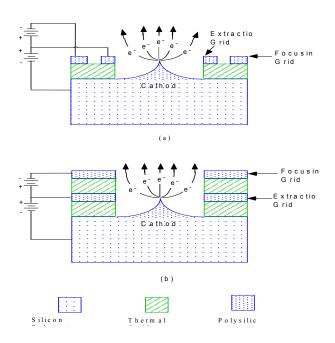

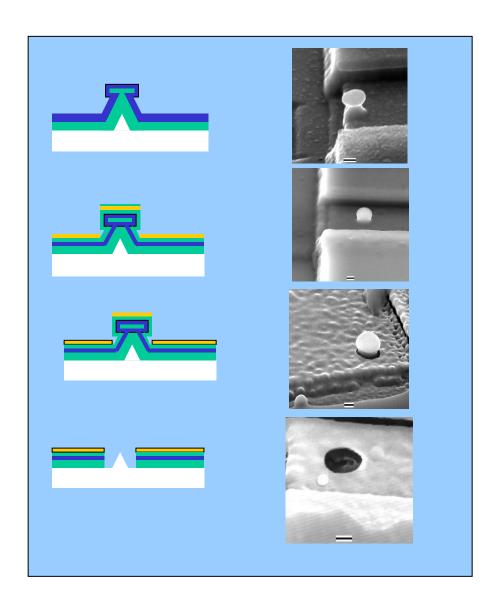

| FIGURE C11 THE SCHEMATIC DIAGRAM OF THE DOUBLE-GATED CELL FABRICATION PROCESS.                                                               |     |

| FIGURE C12 . THE COAXIAL TYPE OF FOCUSING FIELD-EMISSION CELL                                                                                |     |

| FIGURE C13 THE COPLANAR TYPE OF FOCUSING FIELD-EMISSION CELL                                                                                 |     |

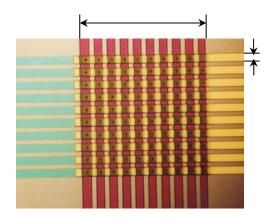

| Figure C14 . Optical micrograph (30X) of the $10x10$ matrix of the test device                                                               |     |

| FIGURE C15 TEST DEVICE PACKAGE.                                                                                                              |     |

| FIGURE C16 FOCUSING AT VARIOUS TERMINAL VOLTAGES AND CONSTANT ANODE CURRENT 80 NA. A                                                         | /   |

| EXTRACTING AND FOCUSING GRID POTENTIAL $\pm 215~V$ Anode voltage $\pm 500V$ B) extracting                                                    |     |

| GRID UNDER +230 V FOCUSING GRID GROUNDED, ANODE VOLTAGE +800 V                                                                               |     |

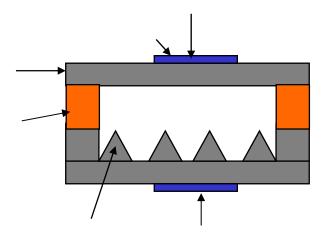

| FIGURE C17. TEST STRUCTURE: DIODE DESIGN FOR SI-TIP ARRAY TESTING                                                                            |     |

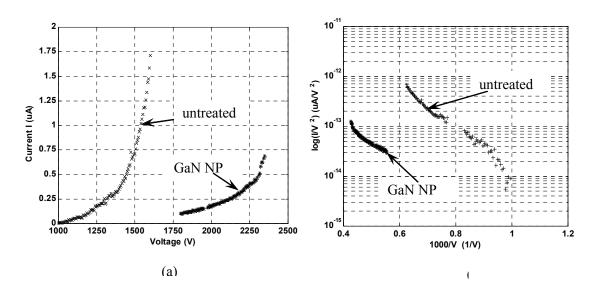

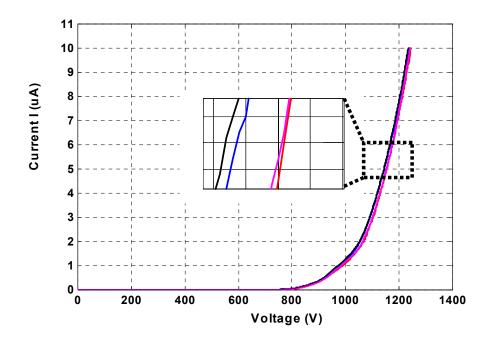

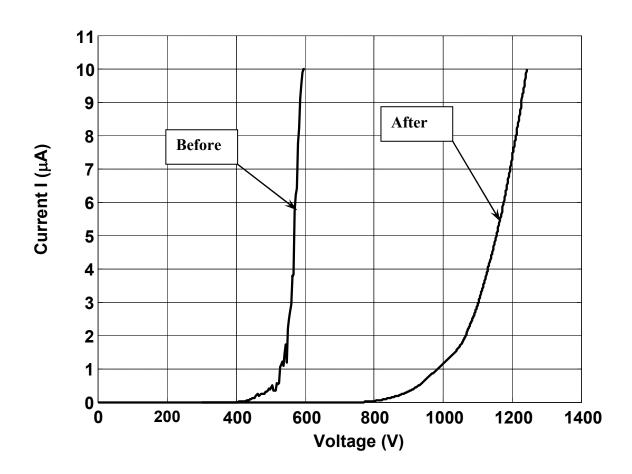

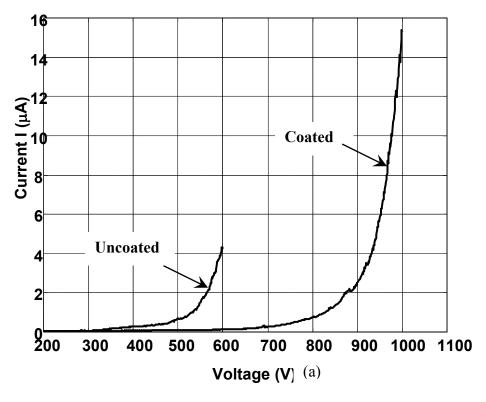

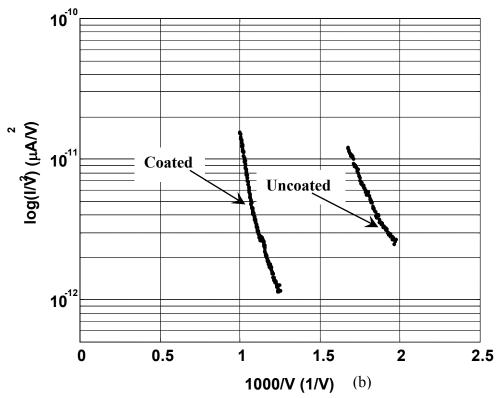

| FIGURE C18. (A) I-V CHARACTERISTIC AND (B) THE F-N CHARACTERISTIC OF THE BEFORE AND AFTER                                                    |     |

| THE EMITTER SURFACE WAS COATED WITH GAN NANOPARTICLES (NP)                                                                                   |     |

| FIGURE C19 (A) I-V CHARACTERISTIC AND (B) THE F-N CHARACTERISTIC OF THE BEFORE AND AFTER                                                     |     |

| EMITTERSURFACE WAS COATED WITH NANOCRYSTALLINE DIAMOND.                                                                                      | /// |

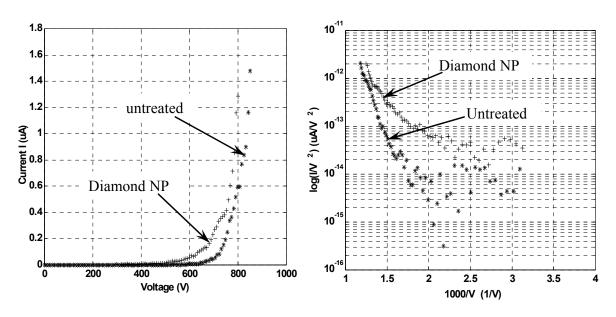

| FIGURE C20. CURRENT VERSUS TIME CHARACTERISTICS OF AN ARRAY OF SILICON EMITTER: (A)                                                          |     |

| UNTREATED; (B) COATED WITH GAN NANOPARTICLES; (C) COATED WITH NANOCRYSTALLINE                                                                | 77  |

| DIAMOND                                                                                                                                      |     |

|                                                                                                                                              |     |

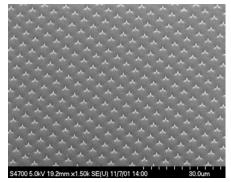

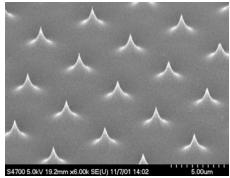

| FIGURE C22 BARE SILICON TIP ARRAY, FABRICATED BY SUBTRACTIVE TECHNOLOGY.  FIGURE C23 THE SAME SILICON ARRAY COATED WITH UNIFORM DIAMOND FILM |     |

|                                                                                                                                              |     |

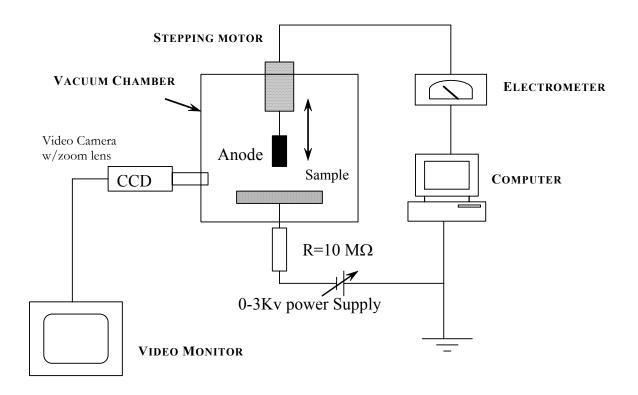

| FIGURE C24. MEASUREMENT SYSTEM TO OBTAIN I-V CHARACTERISTICS OF DIAMOND COATED SILICO ARRAYS                                                 |     |

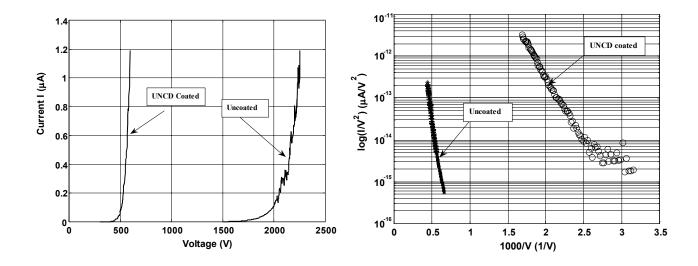

| FIGURE C25. I-V AND FOWLER-NORDHEIM CHARACTERISTICS OF UNCOATED AND UNCD COATED FIR                                                          |     |

| EMISSION ARRAY                                                                                                                               |     |

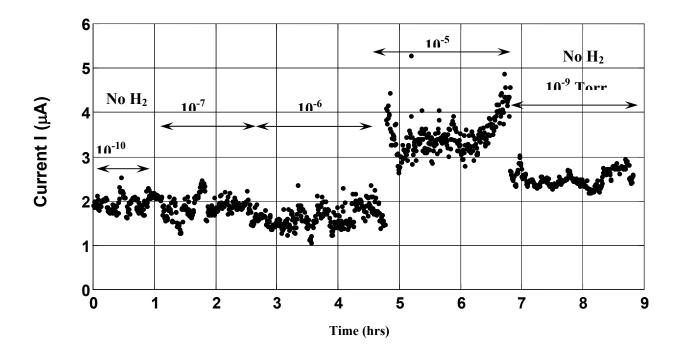

| FIGURE C26: PLOT OF THE EMISSION CURRENT LEVELS FROM UNCD COATED SILICON EMITTER ARRAY                                                       |     |

| HYDROGEN ATMOSPHERE AT THREE DIFFERENT PRESSURES $1 \times 10^{-7}$ , $1 \times 10^{-6}$ , $1 \times 10^{-5}$ Torr                           |     |

|                                                                                                                                              |     |

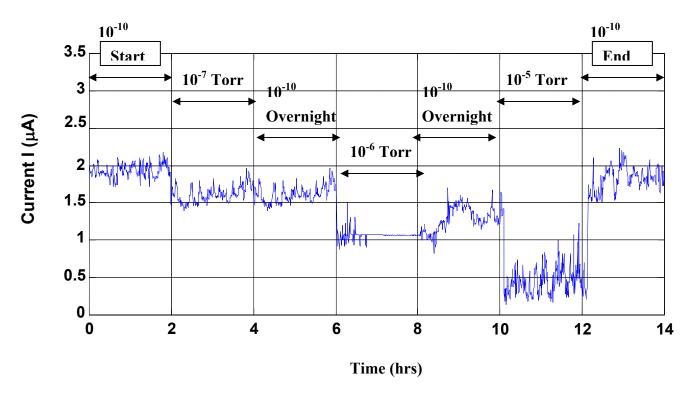

| FIGURE C27: PLOT OF THE EMISSION CURRENT FROM UNCD COATED SILICON EMITTER ARRAY IN                                 |       |

|--------------------------------------------------------------------------------------------------------------------|-------|

| NITROGEN ATMOSPHERE AT THREE DIFFERENT PRESSURES 1x10 <sup>-7</sup> , 1x10 <sup>-6</sup> , 1x10 <sup>-5</sup> TORR | 83    |

| FIGURE C28 I-V CHARACTERISTICS (AFTER 240 HRS OPERATION)                                                           | 83    |

| FIGURE C29 I-V CHARACTERISTICS (BEFORE AND AFTER 240 HRS OF OPERATION)                                             |       |

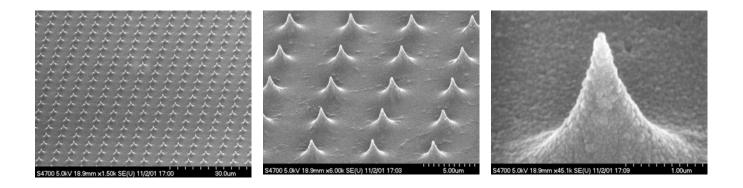

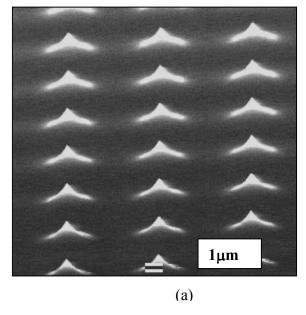

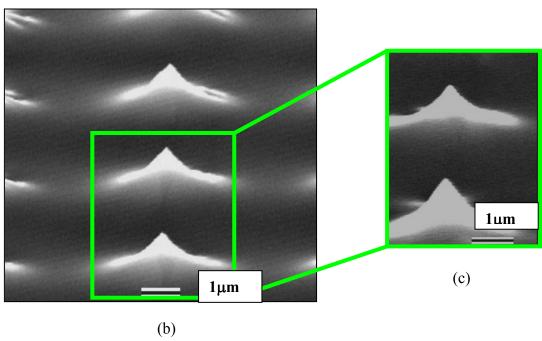

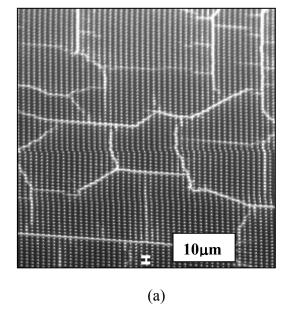

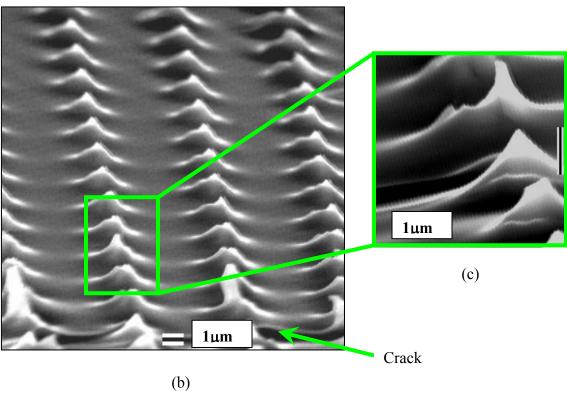

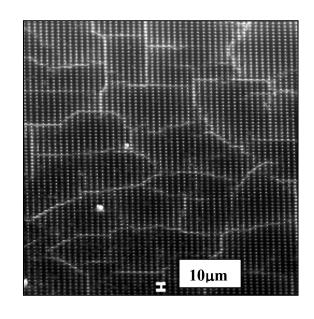

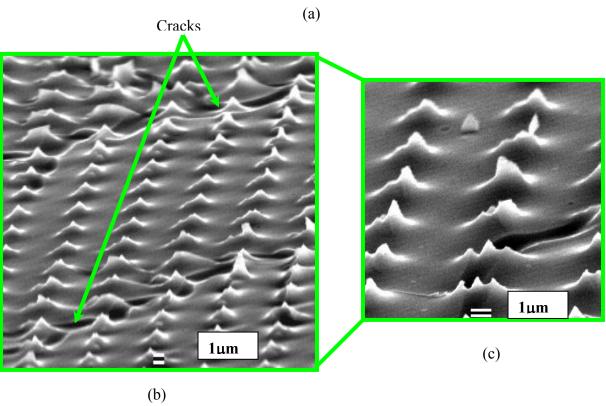

| FIGURE C30: SEM OF 1-LAYER PZT THIN FILM COATED SILICON EMITTER ARRAY                                              |       |

| FIGURE C31: SEM OF 2-LAYER PZT THIN FILM COATED SILICON EMITTER ARRAY                                              | 87    |

| FIGURE C32: SEM OF 3-LAYER PZT THIN FILM COATED SILICON EMITTER ARRAY                                              | 88    |

| FIGURE C33: (A) I-V CHARACTERISTICS (B) FN CHARACTERISTICS OF BARE (UNCOATED) AND ONE                              | LAYER |

| PZT COATED SILICON EMITTER ARRAY                                                                                   | 90    |

| TABLE A1. LOCATION OF MICROMOVER DEVICES ON 4" WAFER AND YIELD AT THAT LOCATION                                    | 13    |

| TABLE A2. YIELD DATA FROM MICROMOVER PROCESS.                                                                      | 14    |

| TABLE A3. MEASUREMENT OF DECOGGING DISTANCE AND COMPARISON WITH SIMULATION                                         | 26    |

| Table A4. Extracted device parameters for M5-18, D14                                                               | 33    |

|                                                                                                                    |       |

#### **PROGRAM OVERVIEW**

This final report documents the major accomplishments of the MBDS contract through its end date in February of 2002. The technical progress is reported by each of the three participants (Hewlett Packard Laboratory, Cornell University, and University of California at Davis) in separate sections below.

#### A. HEWLETT PACKARD

# HIGH ASPECT RATIO SUSPENSION DEVELOPMENT PETER HARTWELL, UIJA YOON HEWLETT PACKARD LABORATORIES

#### A.1. Introduction – Micromovers and Surface Drives

The MBDS data storage medium will be a flexurally suspended silicon plate that is scanned beneath the read/write field emission tips. This media plate must have a wide in-plane scanning range of  $\pm$ 0 µm, while maintaining a media-tip separation which is stable to within  $\pm$ 0 nm. To meet these requirements, the out-of-plane, z-axis stiffness of the flexure suspension must be at least 1000 times greater than both the x and y-axis suspension stiffnesses. From simple beam theory, such a stiffness ratio demands that the suspension have a height to width aspect ratio of at least 32:1.

The project is devoted to developing a fabrication process for these high aspect-ratio suspension structures. In addition, the static and dynamic response of fabricated suspension structures will be examined, allowing optimization of the suspension design. To allow a margin of safety, a target aspect ratio of 40:1 has been established. We have selected a bipolar electrostatic surface motor for the actuation of the micromover. This motor has the advantages of large travel ranges for a given operating voltage and allows data and motor to occupy the same area of the chip.

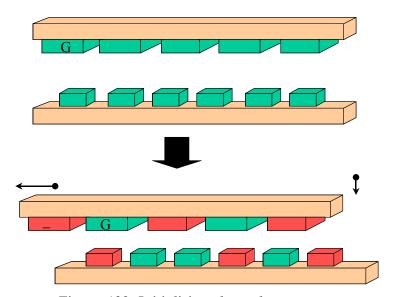

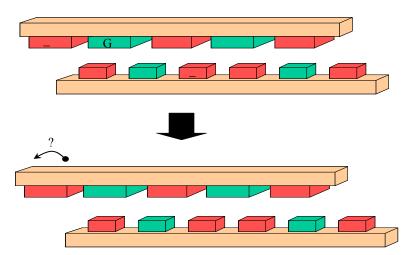

The HP bipolar electrostatic motor was first presented by Storrs Hoen at the 1997 International Conference on Solid-State Sensors and Actuators in Chicago in June, 1997. We will briefly describe the motor here for completeness. The bipolar electrostatic motor is a series of long, finger-like electrodes made on the surface of the micromover (rotor). The micromover wafer is mated with a second wafer (stator) with a similar electrode pattern. A gap of a few microns is maintained between the bonded wafers. The aligned electrode pairs form the electrostatic surface actuator. Electrodes are energized with one of two different voltages, hence the term bipolar. The rotor and stator electrodes are initially energized in a simple alternating pattern. Electric fields between the electrode pairs create a potential energy well causing the rotor to lock into the position of minimum inplane force. The equilibrium position can be changed by changing the electrode bias pattern on the stator. As shown in Figure A1, changing a single electrode from one bias to the other causes a shift in equilibrium position corresponding to one "step".

Figure A1. Bipolar motor electrode patterns. Left shows state 1, right shows state 2. One electrode has changed potential causing a shift of the rotor by one "step" to the right.

The size of a step can be calculated from the following formula:

$$d = \frac{P_r}{n_s}$$

where  $P_r$  = the pitch of the rotor electrodes and  $n_s$  = the number of stator

electrodes

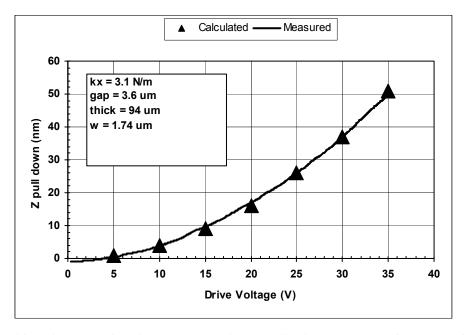

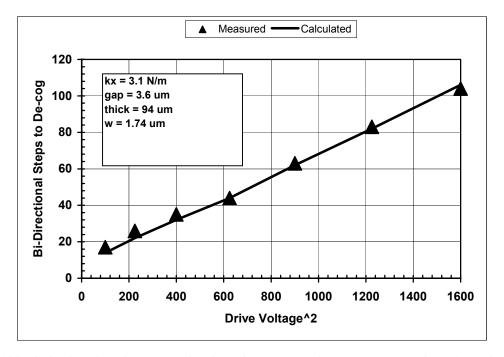

For example, with 7 stator electrodes in a group and a rotor electrode pitch of 3.5 um, the step size would be 0.5 um. Each progressive switch of one electrode advances the micromover 0.5 um. In addition to the inplane forces caused by the electric fields between electrodes, a large out of plane force component is also generated. The out of plane force acts is an attraction between the rotor and stator and is also termed pull down force. The pull down force is another reason a high stiffness ration is need for the micromover device.

The bias voltages on the electrodes are generally selected to be ground and some positive bias referred to as the drive voltage. The drive voltage is carefully selected to provide enough inplane force for desired travel distance without causing pull down. The higher the stiffness ratio of the flexural suspension, the larger drive voltage can be used.

This report will cover the development of the micromover platform and suspension suitable for using in the MDBS device with an integrated bipolar surface drive. The report documents short loops undertaken to develop process steps needed for the most challenging parts of fabrication. The fabrication process for the flexures and improvements made to the process, and process yield are then covered. Then, the development of testing apparatus to measure the parameters of the fabricated suspensions and evaluations of the devices relative to the project goals. Finally we will summarize the successes of this project and offer some insight into the future.

#### **A.2.** PROCESS SHORT LOOPS

#### A.2.1. Flexure etching

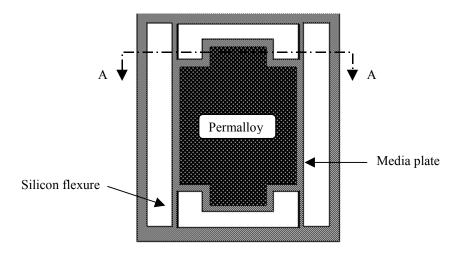

A process for the deep-reactive ion etching (DRIE) of high aspect ratio silicon structures has been developed. A typical suspended test structure is illustrated in Figure A2. In order to minimize the processing complexity, the surface drive electrodes will not be fabricated in this initial test process. Instead, a thin layer of permalloy will be deposited onto the media plate, allowing magnetic actuation of the flexures. This permalloy will not be included in the final fabrication process for the surface drive actuator.

Figure A2: Typical test structure layout.

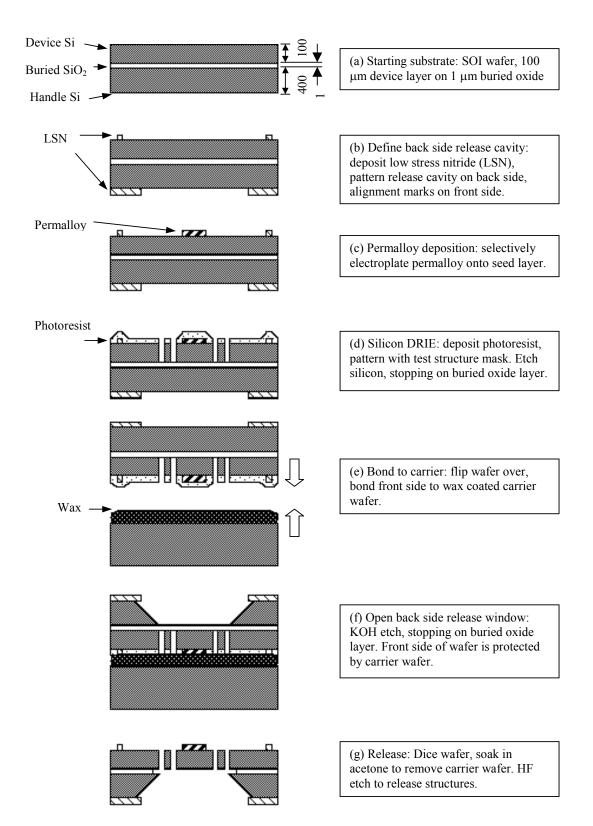

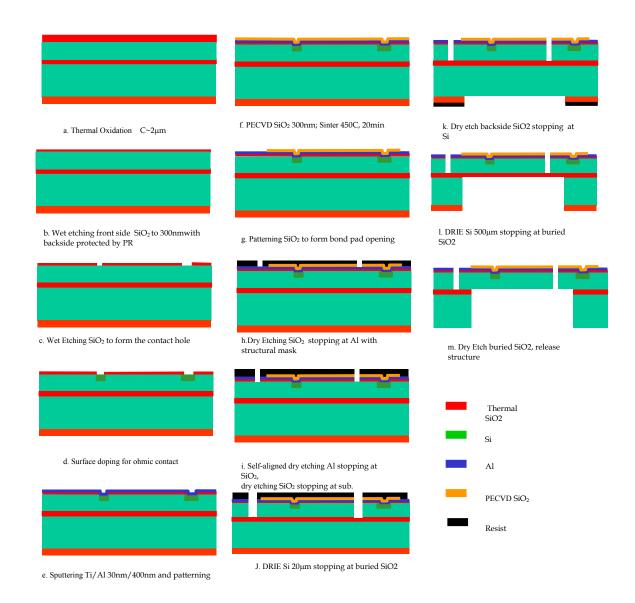

The simplified fabrication process flow chart is shown in Figure A3. The starting substrate is a silicon on insulator (SOI) wafer consisting of a 100 µm silicon device layer bonded to a 400 µm silicon handle wafer via a 1 µm buried SiO<sub>2</sub> (oxide) layer (Figure A3a). Initially, the wafer is coated with a 200 nm film of low stress silicon nitride (LSN) which will serve as a protective mask during subsequent KOH etching. The front and back sides of the wafer are then photolithographically patterned. The backside pattern defines a region where the handle wafer silicon will be removed from beneath each structure. The front side pattern consists of alignment marks that will be used to align subsequent layers to these backside cavities (Figure A3b). Next, a permalloy seed layer is sputtered onto the front of the wafer. Photoresist is deposited and patterned, and a 1 µm permalloy layer is selectively electroplated onto the seed layer. After stripping the photoresist, the seed layer is removed via ion milling (Figure A3c). The device layer silicon is then etched by DRIE using a photoresist mask (Figure A3d). The front side of the SOI wafer is bonded to a wax-coated carrier wafer to protect the etched structures from KOH etching and dicing (Figure A3e). The wafer is then immersed in KOH, etching deep cavities into the handle wafer (Figure A3). The SOI wafer is diced, and heated acetone is used to free the dice from the carrier wafer. Finally, a 1-minute soak in concentrated HF is used to remove the oxide membrane, freeing the suspended test structure (Figure A3g). The released test structures may then be actuated using an external magnet to test the static and dynamic behavior of each flexure suspension.

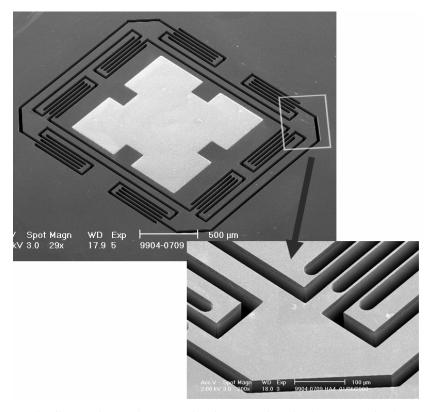

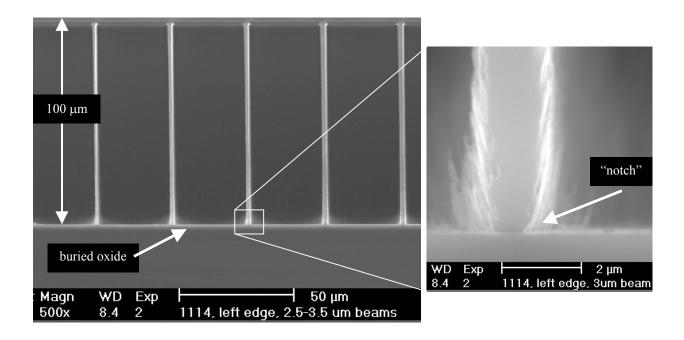

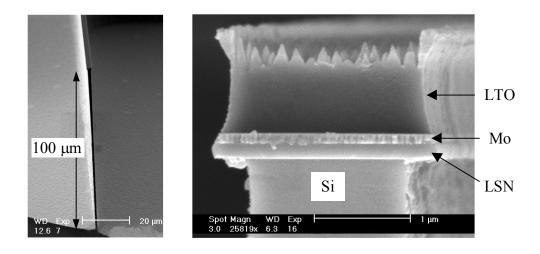

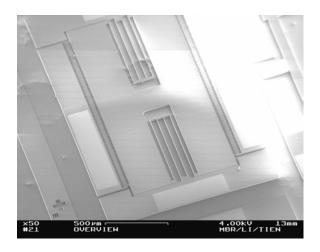

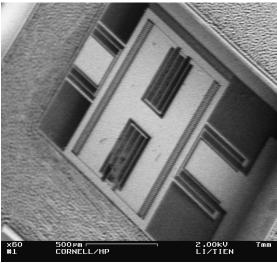

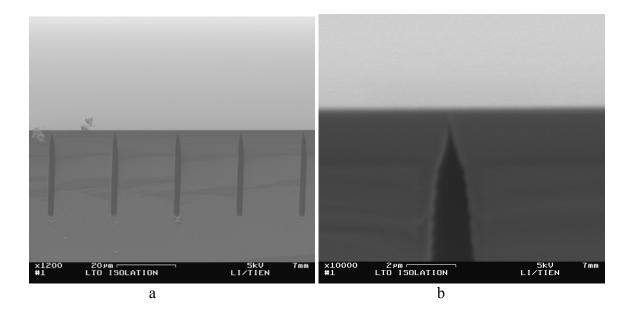

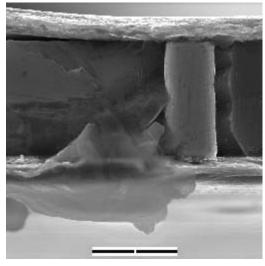

An SEM microphotograph of a typical released structure is shown in Figure A4, while cross-sectional views of the deep-etched flexures are illustrated in Figure A5.

Figure A3: SOI DRIE process flow chart

Figure A4 SEM photomicrograph of a completed NiFe coated micromover.

Figure A5 Cross-Sectional SEM photomicrographs of deep-etched flexures.

#### A.2.2. Flexure aspect ratio

Correlation of the mechanical performance of each deep-etched test structure with the fabrication process variables requires the ability to perform metrology on these structures. We have developed a method that allows us to cross-section suspended test structures after mechanical testing. By understanding how flexure geometry relates to suspension performance, we will be able to focus on controlling those processing variables that have the greatest impact on this performance.

Released, suspended test structures have been cross-sectioned as follows. First, a single test structure die is potted in low-viscosity epoxy. To eliminate air bubbles trapped around the deep etched flexures, the sample is loaded with 50 PSI of hydrostatic pressure before curing. The potted sample is then lapped until the desired location on the die is exposed. Finally, the lapped surface is mechanically polished with slurries of successively finer grit.

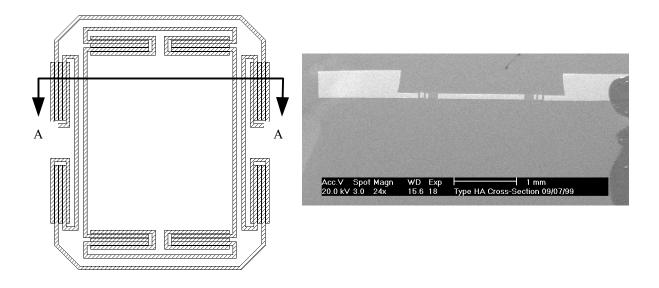

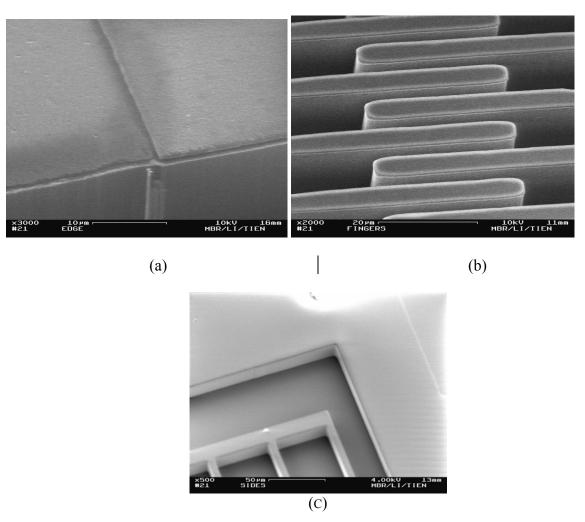

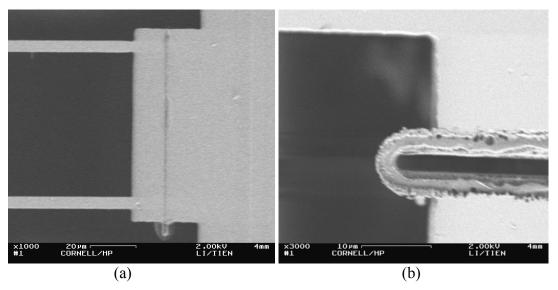

A typical cross-section obtained in this fashion is illustrated in Figure A6 below. Close-up images of the flexure suspension are illustrated in Figure A7.

Figure A6: Left: layout of a typical test structure. The cross-section is indicated by line AA.

Right: SEM micrograph of the cross-sectioned device

Figure A7: SEM micrographs of epoxy-potted cross-sections.

#### A.2.3. Platform flatness

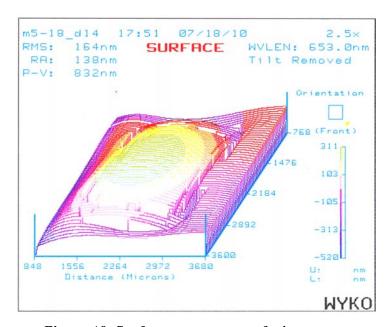

The MBDS device requires the media be at a constant distance away from the emitter. The media need be positioned at the focal point for the emitters and have a minimum of excursion from this distance. Currently we have designed the depth of focus (or allowable excursion) to be +/- 50 nm. Experiments are done to examine the platform flatness as fabricated.

Measurements using a WYKO white-light interferometer has determined that the micro-mover was not flat, but instead was bowed across the top. The WYKO data is presented as Figure A8 and shows a bow of 400 nm over a 1500 um wide micromover. The micromover shown in Figure A8 has the integrated actuator on one side and no materials on the back. While the bowing exceeds our desired specification, it is thought that the residual stress of the media material can be controlled to compensate for this bowing which is probably a result of the actuator structure.

Figure A8. Surface contour map of micro-mover

#### A.2.4. Metal on flexures

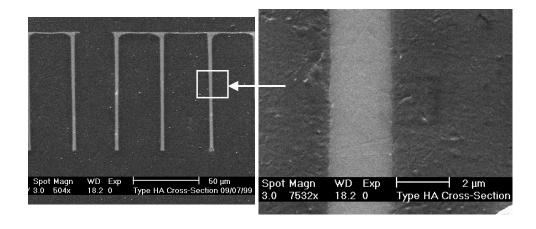

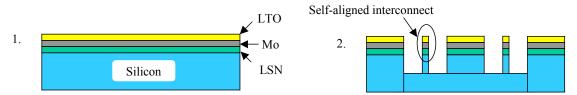

The electrostatic surface drive requires a metallization on one surface of the released rotor platform. Electrical interconnection must be made to the layer, passing over the flexure structure, to allow the correct bias signals to be applied to the motor electrodes. A process short loop was undertaken to create the structure and test the electrical interconnection. The process is shown schematically in Figure A9. A silicon wafer is coated with a low-stress nitride (LSN) dielectric layer, a Mo metallization, and a low-temperature CVD oxide (LTO) masking layer. The oxide, metal and nitride stack is then plasma etched. The patterned, three-layer stack will serve as a mask during the subsequent silicon etch that forms the high-aspect ratio flexures. This approach is used to produce Mo interconnect traces which run on top of the silicon flexures. The fact that the same mask is used to pattern the Mo, nitride and silicon produces interconnect that is self-aligned to the flexures. The exposed silicon on the front side of the wafer is plasma etched 100 um deep, forming high aspect-ratio flexures.

Figure A9: Short loop interconnect test. (1) a silicon wafer is coated with a low-stress nitride (LSN) dielectric, a Mo metallization, and a low temperature CVD oxide (LTO) masking layer. (2) The oxide, metal, nitride, and silicon stack is plasma etched to form flexure with an insulated metal layer on top.

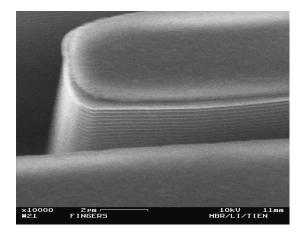

A cross-sectional view of the top surface of a flexure is shown in Figure A10. Based on the layout geometry, the flexure resistance was calculated to be 1.2 k $\Omega$  for a 3 micron wide flexure. The actual width of each metal trace was reduced to 2.4 microns by undercut during processing, resulting in a measured flexure resistance of 1.5 +/- 0.1 k $\Omega$ .

Figure A10: (left) Cross-sectional SEM of a flexure with 100:1 aspect ratio. (right) Cross-sectional SEM of self-aligned interconnect metal.

#### A.3. INTEGRATED ACTUATOR PROCESS DESIGN

As described in previously, suspended test structures have been fabricated by deep etching high aspectratio flexures into silicon on insulator (SOI) wafers. These structures incorporated a magnetic material for actuation. We also presented a process for fabricating metal interconnect lines over silicon flexures. A major limitation of the SOI process was that the structures were released by etching deep cavities into the back side of the wafer after the flexures had been formed on the front face of the wafer. Wafer handling during etching and lithography damaged the delicate flexures, resulting in low yield. A new process was developed to eliminate this problem. In addition, the new process integrates the capability of forming metal interconnect that is self-aligned to the deep etched flexures.

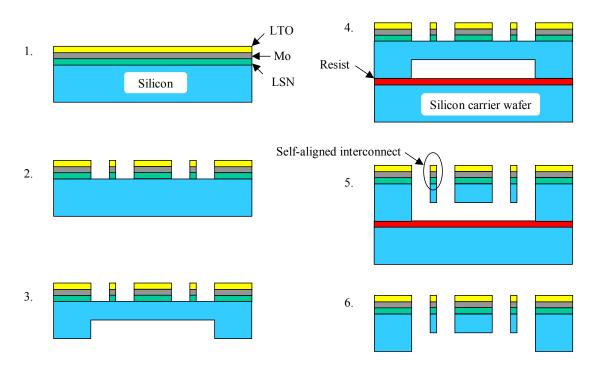

The modified process flow is illustrated in Figure A11. A silicon wafer is coated with a LSN dielectric layer, a Mo metallization, and a LTO masking layer. The oxide, metal, and nitride stack is then plasma etched to serve as a mask during the subsequent silicon etch that forms the high-aspect ratio flexures. This one mask step produces an interconnect that is self-aligned to the flexures. Next, deep cavities are plasma etched into the back side of the wafer. The etch is timed so that a 100 micron thick membrane of silicon remains at the bottom of each cavity. The wafer is then bonded to a carrier wafer using photoresist. The exposed silicon on the front side of the wafer is plasma etched, forming high aspect-ratio flexures into the silicon membrane. Finally, the finished device wafer is separated from the carrier wafer in an acetone bath.

Figure A11: Modified process flow for producing micromovers with metallization. (1) a silicon wafer is coated with a low-stress nitride (LSN) dielectric, a Mo metallization, and a low temperature CVD oxide (LTO) masking layer. (2) The oxide, metal, and nitride stack is plasma etched. (3) Deep cavities are etched into the back side of the wafer. (4) The wafer is bonded to a carrier wafer with photoresist. (5) Flexures are deep etched on the front side of the wafer. (6) The carrier wafer is removed in acetone.

#### A.4. FABRICATION

#### A.4.1. Process Improvements

The preceding section described a fabrication process where by suspended structures are created from two deep silicon etches. The first etch, from the back of the wafer, is timed so a 100 micron thick membrane of silicon remains at the bottom of each etch cavity. The second etch is done from the front of the wafer creating the suspending flexures. The flexure etch also includes the capability of forming metal interconnects that are self-aligned to the deep etched flexures. The process is referred to as "cavity first" given the order of the deep silicon etches.

Cavity first was an improvement from our previous processes using silicon on insulator (SOI) wafers for fabricating the suspended structures. Structures in the old process were released by etching deep cavities into the back side of the wafer after the flexures had been formed on the front face of the wafer. Wafer handling, during etching and lithography for the backside etch, damaged the delicate flexures and resulted in low yield. The older process is characterized by the "flexure first" order of the deep silicon etches. Suspended mover structures were successfully fabricated using the cavity first process.

However, continuing development of the cavity first process revealed other yield issues that needed to be addressed. As reported previously, the deep silicon etch used to fabricate the high aspect ratio (40:1 or greater) flexures required for the MBDS device has a very precise processing window. The etch was developed on bare silicon substrates. The Bosch deep silicon plasma etch is a predominately chemical reaction etch. The rate of reaction, and thus the silicon etch rate, is very dependent on process parameters such as temperature. The STS deep silicon etcher uses a helium cooled wafer chuck to ensure uniform and controlled process temperature of the substrate. A flexure etch on a wafer with deep cavities etched into the backside is subject to much different temperature conditions than a flexure etch done on a blank silicon wafer. The cavities serve as insulating pockets that prevent heat conduction to the helium cooled back of the wafer. The higher substrate temperature during the etch results in a degraded etch profile. The flexure etch process can not be used to make the desired high aspect ratio flexures on this type of substrate.

Non-uniformity in the silicon etch rate across the substrates created additional difficulties. Etch non-uniformity is typically a 5-10% variation in etch depth from the center of the wafer (faster etching) to the edge of the wafer. A 450 um deep backside etch has a depth variation of 30 um or more. The subsequent 100 um frontside etch now requires a 30% over etch to account for the 30 um of backside etch variation. This significant over etch of the flexures severely degrades the flexure profile.

It is thought that with significant etch development, the flexure etch could be changed to produce the correct structures on substrates with back side cavities. Given the significant amount of effort already placed into developing the flexure etch recipe, it was concluded that going back to a flexure first process would be the faster road to success. Flexure first will solve the temperature problems with the cavities. Etch non-uniformity is best taken care of by returning to SOI substrates with a 100 um silicon device layer.

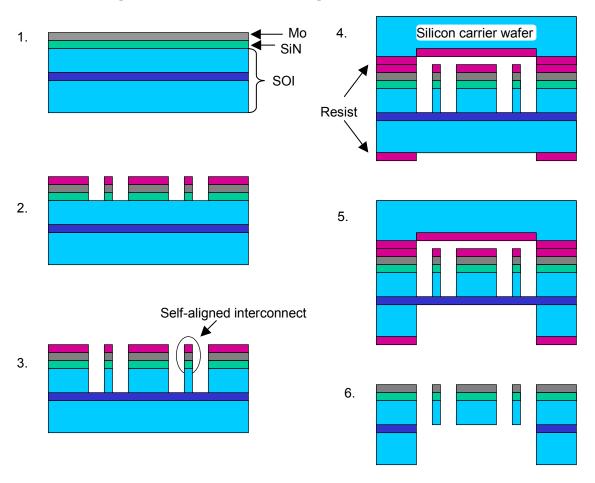

The new flexure first process solves the wafer damage during the subsequent backside etch by using a specially fabricated handle wafer as shown in the process flow in Figure A12.

A SOI silicon wafer is coated with a low-stress nitride (SiN) dielectric layer and a Mo metallization. The metal and nitride stack is then plasma etched using a photoresist masking layer. The resist is left in place and the stack now serves as a mask for the silicon etch that forms the high-aspect ratio flexures. A deep silicon etch, which stops on the buried oxide layer, is done to create the flexures. This approach produces

Mo interconnect traces on top of the silicon flexures and since the same mask is used to pattern all three materials, the result is interconnects self-aligned to the flexures. With the flexures etched, frontside processing is complete. A special carrier wafer with a 20 um deep recess is then resist bonded to the frontside of the wafer. The recess is larger than the device allowing the carrier wafer to be bonded without touching the fragile device area. Deep cavities are then plasma etched into the back side of the wafer using a thick resist mask. The cavity etch also stops on the buried oxide layer. The finished device wafer is separated from the carrier wafer in an acetone bath. This also removes the residual frontside and backside etch masks. Finally, the wafer is etched in hydrofluoric acid (HF) to remove the buried oxide layer and release the MEMS devices.

Key to the flexure first process is that the critical or precision deep etch is done on a wafer with no cavities. This ensures a good etch profile for the flexures as the substrate temperature is controlled. The profile for the backside cavity etch is not as critical. The cavities are also larger than the device area and a non-vertical etch profile, the result of substrate temperature variations, can thus be tolerated.

Figure A12. Flexure first process flow. (1) SOI silicon wafer is coated with a low-stress nitride (LSN) dielectric and a Mo metallization. (2) Photoresist mask is used to pattern the metal and nitride stack. (3) Flexures are deep etched with the same mask. (4) Carrier wafer with a recess, bonded with photoresist, is used to protect the front side of the wafer during backside processing. (5) Deep cavities are etched into the back side of the wafer with a thick resist mask. (6) The carrier wafer is removed in acetone and the structures are released in a liquid HF dip.

#### A.4.2. Completed device

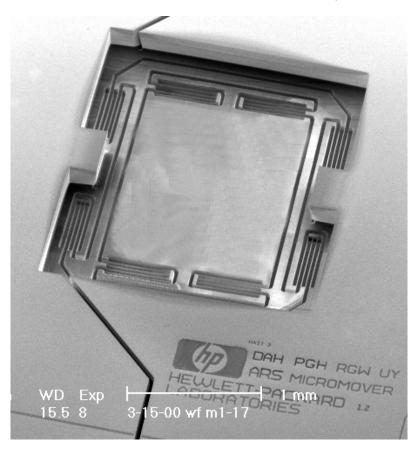

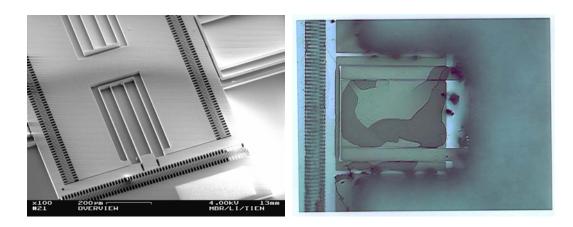

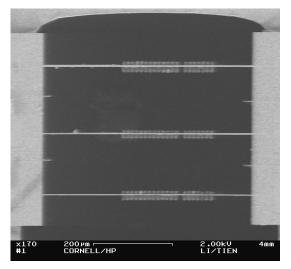

The revised flexure first process produced wafers with near 80% yield for micromover structures. A robust fabrication process allows integration of the suspended micromover structures with the proprietary HP bipolar electrostatic drive. The self aligned interconnect process is used to pattern and contact a set of actuator electrodes on the suspended mover structure. A second wafer, patterned with the other set of electrodes for the actuator, is bonded to the flexure side of the micromover wafer. The two wafers are bonded together with a precise wafer to wafer spacing. Figure A13 shows a device on the bonded wafer stack. The suspended micromover is seen at the bottom of a backside cavity.

Figure A13.SEM image of the back-side of a completed suspended test structure.

#### A.4.3. Process yield

Another area of great interest to the fabrication of micromover devices is effects relative to the position of the device on the wafer during the fabrication process. As the number of wafer pairs containing micromovers continues to increase, it becomes possible to look at yield statistics associated with the position of the device.

Eight rotor wafers were analyzed. Each wafer contains 93 of the HP designed micromover devices. The designs fall into 3 major categories but have variations. The total number of variations is 11. Initially, the parts have been inspect to determine if the flexural system is intact at the completion of the fabrication process.

Overall yield from the 8 wafers was 421 good devices out of a total of 744 for a yield of 56.5%.

Analysis of the results by device type show the following yields: type F 59.8%, type B 59.8%, type H 47.6%. The type H design is a "stage-in-a-stage" design with the two axis suspensions connected in series. Type F and B designs have the suspension systems connected in parallel. Results from the magnetic mover test vehicles indicated much higher yields for the type H movers in that process than for the type F or B movers. It is unclear what has caused this reversal of device yield by design.

Analysis can also be grouped by flexure dimension. The current set of designs incorporated 3 flexure widths: 2.5, 3, and 4 um as drawn in the CAD package. Given a nominal etch bias of 0.5 um, this should result in devices with flexure widths of 2, 2.5, and 3.5 um. The results were as follows: 2.5 um 43.7%, 3 um 58.0%, 4 um 56.3%. As expected, yield was lower for the narrowest flexures. However, yield appears to be consistent once a certain minimum width is achieved. For the MBDS device, a finished width of 2.5 um, giving a flexure aspect ratio of 40:1 in a 100 um thick deivce, is required. This appears to be greater than the minimum width, and good yield should be possible for this size flexure.

Two designs of micromovers used on the wafer include a hybrid flexure design with flexures of different widths in different areas of the suspension. The device account for 136 of the 744 total devices. Yields on these parts were 66.1% and 63.8%, considerably higher than the average yield from the wafers. This result indicates that a careful study of the forces and process steps responsible for yield loss and then a design tailored to be resistant to these forces and also meet the MBDS performance requirements could result in a much higher yield in the micromover process.

#### Micromover Yield(Rotor wafer) Good Dies/Total dies Column 8 13 14 15 2 3 4 5 6 9 10 11 12 16 Row 5/8 5/8 4/8 4/8 1/8 3/8 3/8 3/8 5/8 5/8 6/8 4/8 5/8 5/8 В 5/8 6/8 5/8 С 2/8 2/8 3/8 5/8 4/8 4/8 4/8 1/8 6/8 5/8 6/8 D 2/8 5/8 6/8 2/8 1/8 1/8 5/8 4/8 5/8 5/8 7/8 4/8 7/8 Ε 6/8 1/8 F 5/8 4/8 G 5/8 3/8 Н 5/8 8/8 2/8 5/8 6/8 5/8 5/8 5/8 7/8 4/8 7/8 6/8 6/8 6/8 3/8 5/8 6/8 7/8 6/8 6/8 6/8 6/8 7/8 5/8 3/8 5/8 7/8 5/8 K 2/8 5/8 1/8 4/8 5/8 6/8 4/8 6/8 4/8 7/8 6/8 5/8 6/8 1/8 L М N 0 2/8 2/8 4/8 3/8 P

Table A1. Location of micromover devices on 4" wafer and yield at that location.

Further analysis of the yield data and early performance testing (covered in a following section) led the team to update the micromover design and process. The new devices and process were referred to as HP Labs Rev B. (This lead to the first parts being called HP Labs Rev A). The data in Table A1 refers to Rev A parts.

One of the key elements of the micromover architecture is the ability to leverage the parallel nature of semiconductor processing. Dozens of micromovers can be fabricated at the same time on a single wafer.

The high performance of the MBDS system requires this to occur at the chip level. Our current system designs have arrays of 2x2 to 6x6 micromovers on a single chip, all operating simultaneously. In addition to meeting the required performance specifications, the micromover must also be designed to achieve an efficient packing in an array as well as a high yield so all array members are functioning.

Array packing has been a key design parameter for the micromover. Array yield has been examined by looking at device yield over the entire wafer. HP Labs fabricates micromovers on 100 mm substrates. The Rev B substrates contains 208 micromover devices spaced on a 5 mm grid. One can think of this grid as a "sparse array", similar to the array needed on a MBDS chip with every over device removed. A study of the sparse array on a wafer should yield statistics that will apply to a dense array on a chip.

|       | `     | YIELD       |         |       |

|-------|-------|-------------|---------|-------|

| Rev B | 1     | Flexure wid | th (um) |       |

|       | 2.5   | 3           | 4       | 5     |

| f     | 63.9% | 75.0%       | 93.3%   | 98.1% |

| h     | 80.6% | 88.0%       | 99.0%   |       |

| Rev A |       |             |         |       |

| f     | 60.0% | 60.7%       | 57.5%   |       |

| h     | 31.3% | 50.9%       | 56.3%   |       |

Table A2. Yield data from micromover process.

Table A2 shows yield data comparing two lots of micromovers, Rev A and Rev B, fabricated in the HP Labs micromover process. Rev B parts are a design revision of micromovers towards the requirements of the MBDS device and is a sample set of four wafers. Yield data for Rev A micromovers is summarized from before and represents a sample set of eight wafers. F and B refer to 2 styles of flexure configurations used in HP Labs micromovers. The flexure width is the as drawn dimension in the layout package. Since the substrates are a uniform thickness, changing the flexure width directly changes the flexure aspect ratio.

The table shows a significant increase in good parts from the Rev A lot to the Rev B lot. This can be attributed to significant design changes in the F style micromover and tweaks to the fabrication process. As expected, yield is higher for wider flexures due to their increased stiffness and resulting toughness to external forces. Most yield loss can be attributed to wet etching steps in the release portion of the fabrication process. It is very encouraging to see yield numbers approach 100% for the wider flexures – a major accomplishment in a research facility. In a production facility with automated handling equipment, it is safe to assume that yields will go up to similar levels for the narrow flexures.

Figure A14 illustrates the yield of micromovers as a function of flexure width. There is a knee in the curve where yield levels off and an increase in width is unnecessary for increased yield. This was also seen in the Rev A parts. Moving to a production facility should shift the knee in the plot to the left, allowing arrays of MDBS spec micromovers to be fabricated with high yield.

Figure A14. Percent yield as a function of flexure width. Yield data from the Rev B micromover process demonstrates that we can successfully fabricate arrays of working micromovers at HP Labs.

#### A.5. TESTING

#### A.5.1. Test setup

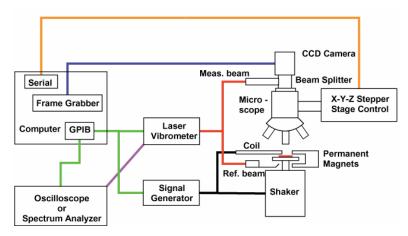

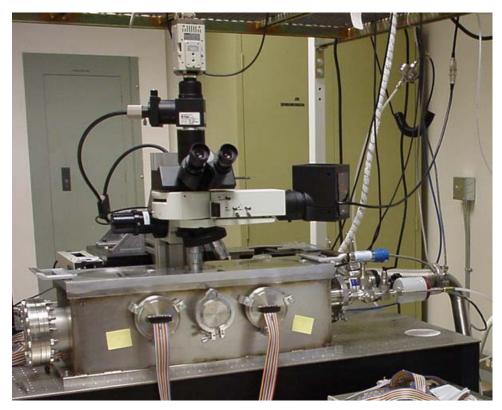

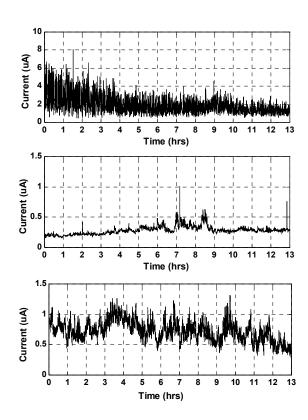

A new testing setup, as shown schematically in Figure A15 was constructed to characterize two-axis MEMS stage devices required by the MBDS project. The setup applies external forces to the device and then uses optical and interferometric position measurements to determine the response of the device. Testing is automated with an integrated computer system. This setup allows the testing and optimization of the magnetic micromovers short loop devices without the need for a completed MBDS device.

Figure A15. Schematic of micro-mover evaluation system.

The setup uses permanent and electro-magnets for in-plane actuation of a special run of prototype micro-movers (Figure A16). The movers are fabricated with a NiFe layer deposited on the stage area to respond in the magnetic fields. Special sample holders have also been designed to allow precise positioning in the magnetic field.

Figure A16. Magnet and shaker configuration for off chip excitation of micro-movers.

Once assembled, improvements to the DC magnet positions and to the AC coil geometry were installed. The result is enough in-plane force with the DC magnets to get full displacement of the micro-movers (30 um – the trench width around the mover). This allows device characterization at static displacements from equilibrium. The AC coil is wound to a large heat sink allowing 1-2 amps of current to be applied. The coil is easily able to excite the in-plane modes of the movers. The coil creates enough field that both in-plane axes of a device can be actuated without having to change the testing geometry.

Additionally, the movers are mounted on a vibration shake table to excite out-of-plane vibration modes. The shaker is integrated with the magnetic actuators to allow simultaneous in-plane and out-of-plane excitation of the devices.

Device responses are measured with optical based techniques. The system uses an optical microscope mounted on a XY positioning stage controlled with stepper-motors. A laser Doppler vibrometer (LDV) setup is used for measuring the out of plane response of the micro-mover test structures. A CCD camera mounted on the microscope is used with a frame grabber board and image analysis software to measure the in-plane response. The microscope is integrated into the magnetic testing system and allows precise, computer controlled positioning and focus of the measurement beams. This allows aiming the measurement beams anywhere on the test structure by moving only the optics and not the sample or excitation hardware.

The mechanical response of the testing system was characterized and an accelerometer was added to the sample holder to measure the exciter response. This serves as a reference measurement for the system. A dynamic signal analyzer is used to display the device response which is the difference between the reference and measurement signals.

Programs have also been written to computerize the data collection of the out-of-plane (Z-axis) natural frequency measurements. Integrating these programs with the motion control programs automates the testing and provides a faster, more repeatable characterization of the movers. The automation also enables a large number of movers to be tested to allow data to be collected for inter- and intra- wafer statistical analyses.

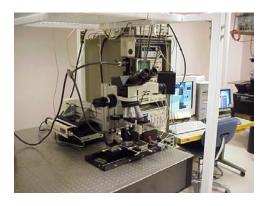

Figure A17. Photographs of the test setup and the support equipment rack.

The micro-mover evaluation system, as shown in the images in Figure A17, is an invaluable tool for characterizing micro-mover designs. With the off chip excitation system and integrated measurement techniques, precise, repeatable measurements the device parameters can be performed. The system enables prototype micro-movers to be evaluated and will determine whether MEMS XY stages can be fabricated with in the design specifications for the MBDS project.

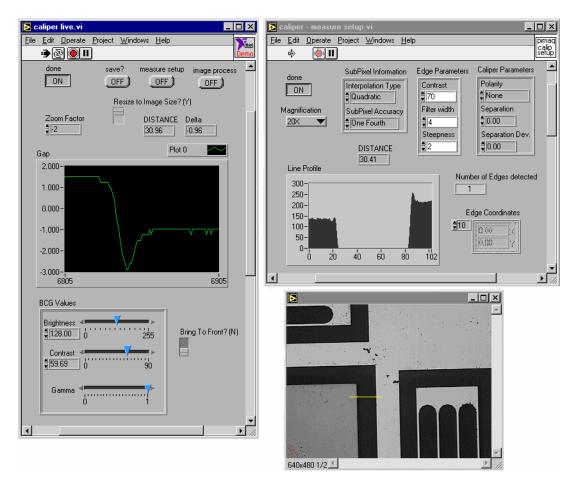

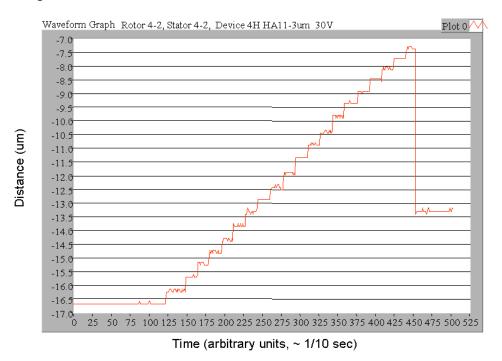

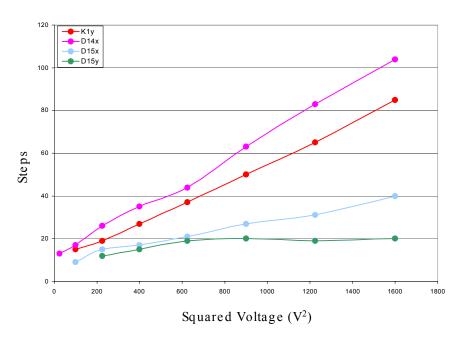

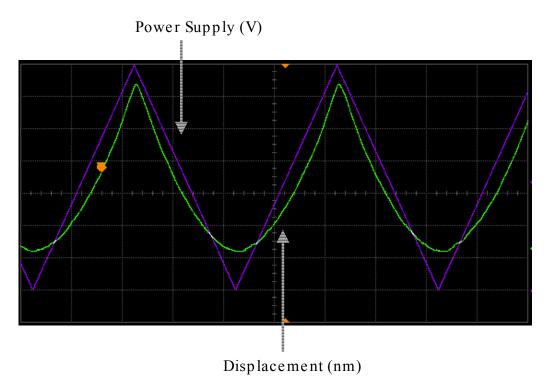

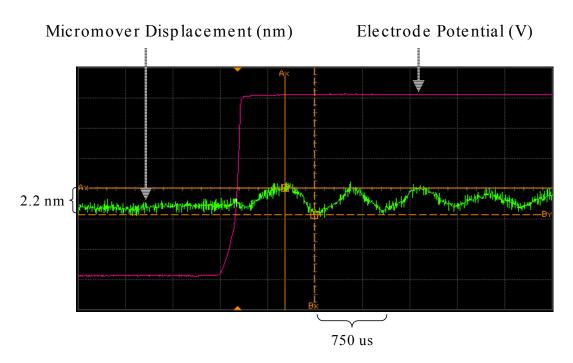

Once micromovers with the integrated actuator were completed, they were also tested with the measurement system. The step data Figure A26 was measured using the frame grabber board in the computer to acquire images from the CCD camera mounted on the microscope. The interface for the software, written at HP, is shown in Figure A18. A region of interest is defined on the images and the brightness profile is examined. Edge detection routines analyze the profile to determine the location of the edges of the trench in the silicon that defines the mover. Pixel size on the image was carefully calibrated to allow this gap to be converted to a measurement in microns. The trench width in the device layout was 30 um. Deviation from 30 um corresponds to device motion.

Figure A18. Caliper software, written at HP, to measure the motion of MEMS devices. Optical measurements are done by determining the gap between moving and fixed members using image analysis routines. The left widnow shows the user interface. The bottom right window is the device with the measurement region of interest shown as a thin yellow line bridging a trench. The top right window is a display of the image analysis routine. The brightness profile of the region of interest is shown in the "line profile" plot.

The caliper software has been optimized for speed and can achieve a frame/measurement rate of 30 Hz. The measurement rate is fast enough to allow DC motions of the device to be accurately monitored. Measurement limits and resolution are determined by the final objective lens used on the microscope. Maximum resolution with a 100X objective lens is about 100nm. Using a 10X objective lens, motions greater than 100 um can be measured with correspondingly lower resolution.

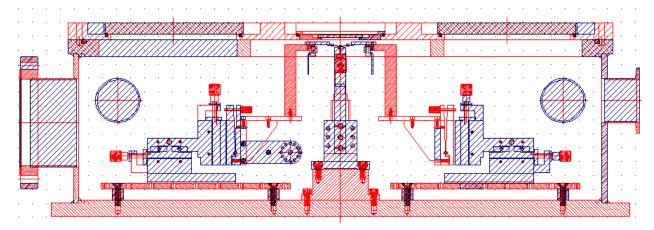

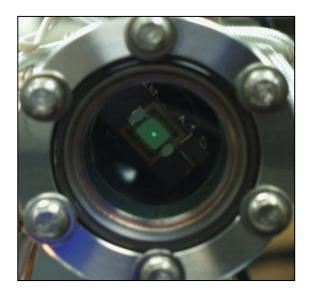

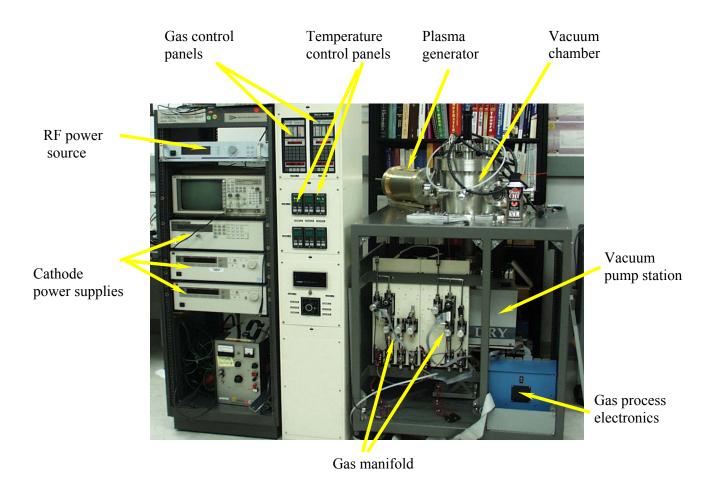

The MBDS device is required to operate in a high vacuum condition internal to the package. Proper development of the performance of the mover requires evaluating it under high vacuum. We have designed and constructed a custom, stainless steel vacuum chamber for integration with the LDV based measurement system. The vacuum chamber is approximately 8"x8"x24". A photograph of the vacuum chamber is presented in Figure A19. The chamber was designed for maximum flexibility to test packaged and unpackaged chips, rows, and whole wafers.

Figure A19. photograph of coffin integrated with MEMS testing system

The chamber holds two micromanipulators, each with a custom 15 pin probe card attached. Each probe card makes electrical contact with our standard configuration of 15 bond pads along one edge of the micromover chip. Mounts for probing samples were made to hold single chips, a row of chips, or a complete wafer.

In the center of the lid is a port allowing optical access to the micromover. This port is a sapphire window, 2" in diameter, to minimize distortions under pumped conditions. The sample can be mounted close enough to the window to allow the use of Mitutoyo long working distance lenses with a working distance greater than 30 mm. This allows a 20x lens to be used giving the optical test system a final magnification near 200x. Using the optical/video measurement technique previously reported, we can achieve a 200 nm resolution.

A CAD drawing of the vacuum chamber, probe manipulators, and other parts of the system is included as Figure A20.

Figure A20. Coffin CAD drawings

Initial electrical measurements at atmospheric pressure and under vacuum have been done. Micromovers have been successfully actuated under vacuum.

#### A.5.2. Mechanical properties

More than sixty different micromover structures from five wafers have been tested using the method described in the preceding section. The goal of this testing has been to answer two questions. First, for a particular suspension design, what is the relationship between the height-to-width aspect-ratio and the ratio of the in-plane to out-of-plane stiffness? Second, how does this ratio change as a function of in-plane displacement?

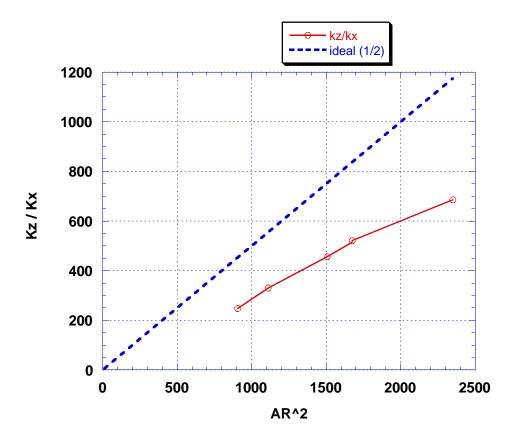

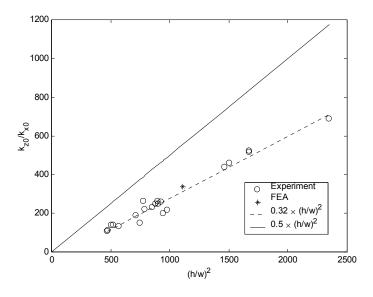

As described in the introduction, the micromover must provide a 40 micron range of motion in each of the two in-plane axes while restricting out-of-plane motion to less than 0.1 micron. To satisfy this requirement in the face of similar in-plane and out-of-plane loads, the micromover suspension must have a ratio of out-of-plane to in-plane stiffness that is better than 400:1. Linear beam theory predicts that a rectangular cross-sectioned beam will have a ratio of out-of-plane to in-plane stiffness that is proportional to the aspect ratio squared, or:  $kz/kx = (AR)^2$ . This theory provides a theoretical limit for the maximum achievable stiffness ratio. The fact that the micromover must move in two axes requires a cascaded suspension with flexures for each axis, reducing the stiffness ratio by a factor of two.

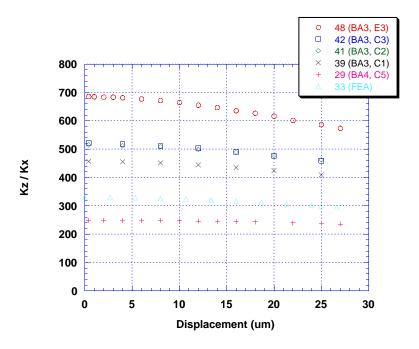

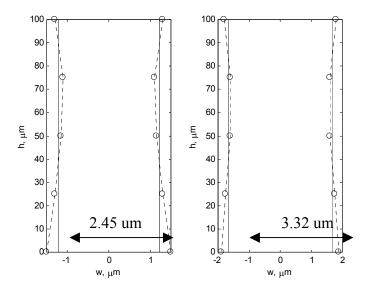

The stiffness ratios of multiple devices with aspect ratios varying from 30:1 to 48:1 were measured and are plotted along with this theoretical limit in Figure A21. The measured suspension stiffness ratios are lower than the theoretical limit because assuming that the flexures are in pure bending is an oversimplification. In reality, there are additional stiffness losses from thick links which couple the various flexures together, and from torsional bending in the links and flexures. Additionally, the plot shows that the measured dependence of the stiffness ratio on  $(AR)^2$  is sub-linear. This result stems from the fact that the torsional stiffness of the flexures declines with increasing aspect ratio, effectively increasing the torsional bending losses described above.

Figure A21 Measured suspension stiffness ratio (kz/kx) as a function of flexure height-to-width aspect ratio (AR). The ideal dashed line is the theoretical limit for a rectangular cross-sectioned beam in pure bending.

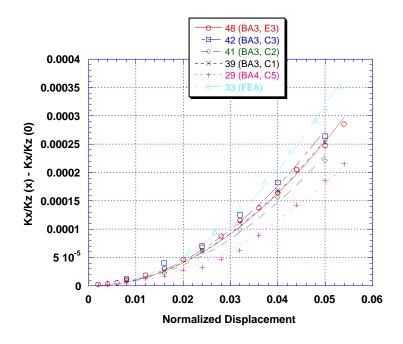

The dependence of the stiffness ratio on in-plane motion was also investigated. The measured results are shown in Figure A22 for suspensions with varying aspect ratios. In general, between a 10% to 20% loss in out-of-plane stiffness was observed over a 30 micron range of deflections. As the micromover translates in-plane, the flexures are deflected and the lever arm acting to produce torsional bending on each flexure is increased, reducing the out-of-plane to in-plane stiffness ratio. A model for this effect is given by:

$$kx/kz(x) - kx/kz(0) = a(x/L)^2,$$

where kx/kz(x) denotes the inverse of the stiffness ratio as a function of in-plane displacement (x), L is the flexure length, and a is a constant. The right hand side of this equation represents the loss in stiffness ratio as a function of displacement. This stiffness loss term is plotted in Figure A23. The behavior of each device follows the parabolic curve predicted by the model, but there is some unexplained scatter in the coefficient a used to model each device.

Figure A22 Loss in stiffness ratio versus displacement. The aspect ratio of each specimen is indicated in the plot legend.

Figure A23 Nonlinear stiffness loss versus displacement for various aspect ratios. In each case, the measured change in kx/kz is plotted and fit with a parabola in  $x^2$ .