# NAVAL POSTGRADUATE SCHOOL Monterey, California

# **THESIS**

DESIGN RECOVERY AND IMPLEMENTATION OF THE AYK-14 VHSIC PROCESSOR MODULE ADAPTER WITH FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY

by

Bryan J. Fetter

December 2002

Thesis Advisor: Russell W. Duren Second Reader: Hersch Loomis

Approved for public release; distribution is unlimited.

| REPORT DOCUME                                                                                                  | Form Approved OMB No. 0704-0188       |             |                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------|---------------------------------------------------|--|--|

| 1. AGENCY USE ONLY (Leave blank)                                                                               | YPE AND DATES COVERED Master's Thesis |             |                                                   |  |  |

| <b>4. TITLE AND SUBTITLE:</b> Design Recoverey and Implementation of Adapter with Field Programmable Gate Arra | 5. FUNDING NUMBERS                    |             |                                                   |  |  |

| 6. AUTHOR(S) Fetter, Bryan James 7. PERFORMING ORGANIZATION N                                                  | AME(S) AND ADDRES                     | SS(ES)      | 8. PERFORMING                                     |  |  |

| Naval Postgraduate School Monterey, CA 93943-5000                                                              |                                       |             | ORGANIZATION REPORT<br>NUMBER                     |  |  |

| 9. SPONSORING /MONITORING AGI<br>N/A                                                                           | ENCY NAME(S) AND A                    | ADDRESS(ES) | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER |  |  |

| <b>11. SUPPLEMENTARY NOTES</b> The vipolicy or position of the Department of Def                               |                                       |             | the author and do not reflect the official        |  |  |

| 12a. DISTRIBUTION / AVAILABILITY Approved for public release; distribution                                     | ·-                                    |             | 12b. DISTRIBUTION CODE                            |  |  |

| 13 ABSTRACT (maximum 200 wor                                                                                   | rds)                                  |             | _                                                 |  |  |

#### 13. ABSTRACT (maximum 200 words)

The rapid pace of change in the electronics industry and the significant reduction in military budgets over the past decade has forced many military aircraft to extend their service lifetimes. This has led to aircraft with outdated avionics systems being required to accomplish new and more complex missions. This thesis examines the process of reengineering an outdated avionics system to economically upgrade its capabilities through the FPGA implementation of a binary compatible replacement. The system targeted is the AN/AYK-14(V) Navy Standard Airborne Computer, specifically the XN-8 chassis used as the mission computer onboard the F/A-18 C/D aircraft. This thesis is also intended to provide a resource document on the AYK-14 for a study being conducted by the Naval Air Systems Command (NAVAIR) Advanced Weapons Laboratory (AWL). The design of the Input / Output module of the VHSIC Processor Module was recovered through research of documentation and hardware testing. The recovered design was modeled using VHDL, synthesized and implemented using computer-aided (CAD) design tools. This thesis shows that replacement of legacy systems through use of FPGA technology is a viable option, however, expansion of the design is recommended to create a truly binary compatible replacement.

|                                             | SUBJECT TERMS solescence, Legacy, FPGA, VHDL,VHSIC, Xilinx, SDRAM, AYK-14, Mil-Std-1553, State achine, AVNET, Bus Controller, Data Bus, Software Interrupts, Reengineering, Design Recovery  15. NUMBER OF PAGES 218 |                                               |                               |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|--|--|--|

|                                             |                                                                                                                                                                                                                      |                                               | 16. PRICE CODE                |  |  |  |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE                                                                                                                                                                       | 19. SECURITY<br>CLASSIFICATION OF<br>ABSTRACT | 20. LIMITATION<br>OF ABSTRACT |  |  |  |

| Unclassified                                | Unclassified                                                                                                                                                                                                         | Unclassified                                  | UL                            |  |  |  |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited.

# DESIGN RECOVERY AND IMPLEMENTATION OF THE AYK-14 VHSIC PROCESSOR MODULE ADAPTER WITH FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY

Bryan J. Fetter

Lieutenant, United States Navy

B.S. Aerospace Engineering, United States Naval Academy, 1993

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN AERONAUTICAL ENGINEERING

#### from the

#### NAVAL POSTGRADUATE SCHOOL DECEMBER 2002

Author: Bryan J. Fetter

Approved by: Russell W. Duren

Thesis Advisor

Hersch Loomis Second Reader

Max Platzer

Chairman, Department of Aeronautics and Astronautics

#### **ABSTRACT**

The rapid pace of change in the electronics industry and the significant reduction in military budgets over the past decade has forced many military aircraft to extend their service lifetimes. This has led to aircraft with outdated avionics systems being required to accomplish new and more complex missions. This thesis examines the process of reengineering an outdated avionics system to economically upgrade its capabilities through the FPGA implementation of a binary compatible replacement. The system targeted is the AN/AYK-14(V) Navy Standard Airborne Computer, specifically the XN-8 chassis used as the mission computer onboard the F/A-18 C/D aircraft. This thesis is also intended to provide a resource document on the AYK-14 for a study being conducted by the Naval Air Systems Command (NAVAIR) Advanced Weapons Laboratory (AWL). The design of the Input / Output module of the VHSIC Processor Module was recovered through research of documentation and hardware testing. The recovered design was modeled using VHDL, synthesized and implemented using computer-aided design (CAD) tools. This thesis shows that replacement of legacy systems through use of FPGA technology is a viable option, however, expansion of the design is recommended to create a truly binary compatible replacement.

## TABLE OF CONTENTS

| I.     | INT       | RODUCTION                                 | 1  |

|--------|-----------|-------------------------------------------|----|

|        | <b>A.</b> | THE LEGACY AVIONICS ISSUE                 | 1  |

|        | В.        | POTENTIAL SOLUTIONS TO THE LEGACY PROBLEM | 2  |

|        | C.        | REENGINEERING                             | 3  |

|        | D.        | PURPOSE OF STUDY                          | 4  |

| II.    | DES       | SIGN RECOVERY                             | 7  |

|        | A.        | OVERVIEW OF REENGINEERING PROCESS         | 7  |

|        | В.        | OVERVIEW OF THE AYK-14                    | 8  |

|        |           | 1. History of the AYK-14                  | 8  |

|        |           | 2. Processor Subsystem                    | 8  |

|        |           | 3. Memory Subsystem                       |    |

|        |           | 4. Input / Output Subsystem               | 9  |

|        |           | 5. Power Subsystem                        |    |

|        |           | 6. Chassis Subsystem                      | 9  |

|        | C.        | AYK-14 CONFIGURATION ON THE F-18C/D       | 10 |

|        | D.        | VPM PROCESSOR                             | 12 |

|        | <b>E.</b> | ADAPTER                                   | 14 |

|        | F.        | EXTERNAL BUS OPERATION                    |    |

|        |           | 1. Standalone Mode MBUS Operation         |    |

|        |           | 2. Standalone XBUS Operation              | 20 |

|        | G.        | EVENT SYSTEM                              |    |

|        |           | 1. Polled Event System                    | 25 |

|        |           | a. 1 <sup>st</sup> State: ESTATE = 01     |    |

|        |           | b. 2 <sup>nd</sup> State: ESTATE = 10     | 27 |

|        |           | c. 3 <sup>rd</sup> State: ESTATE = 11     |    |

|        |           | 2. Direct Events                          |    |

|        | Н.        | INPUT / OUTPUT MODULE OPERATION           |    |

|        |           | 1. I/O Channel Software                   |    |

|        |           | 2. I/O Channel Control Memory             |    |

|        |           | 3. I/O Channel Chain Programs             |    |

|        |           | 4. I/O Channel Software Interrupts        |    |

|        |           | 5. I/O Channel Events                     |    |

|        |           | 6. I/O Channel Basic Operation            |    |

|        | I.        | DISCRETE AND SERIAL MODULE                |    |

|        |           | 1. DSM Personalities and Modes            |    |

|        |           | 2. Smart I/O Operation                    |    |

|        | J.        | COMPUTER CONTROL UNIT                     | 39 |

| III. I | DESIG     | N IMPLEMENTATION                          | 41 |

|        | <b>A.</b> | FORWARD ENGINEERING PROCESS               |    |

|        |           | 1 Field Programmable Cate Array           |    |

|           | 2. VHSIC Hardware Design Language (VHDL) | 42         |

|-----------|------------------------------------------|------------|

|           | 3. FPGA Design Tools                     |            |

|           | 4. Finite State Machine Design           | 45         |

|           | 5. Modular Approach to Overall Design    | 47         |

| В.        | TARGET FOR DESIGN IMPLMENTATION          |            |

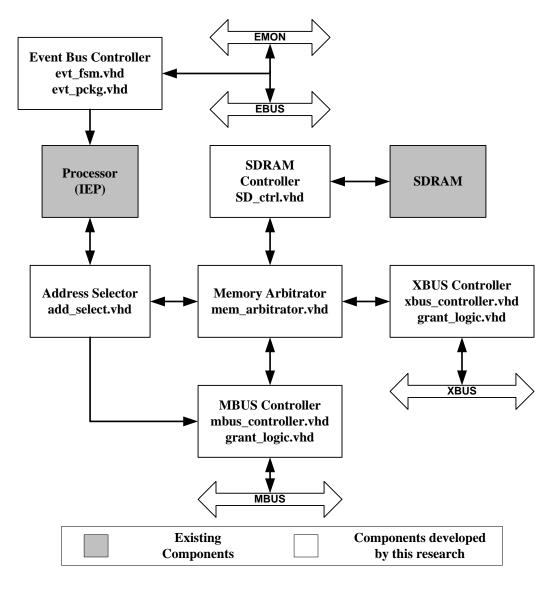

| С.        | COMPONENT DESIGN DESCRIPTION             | 49         |

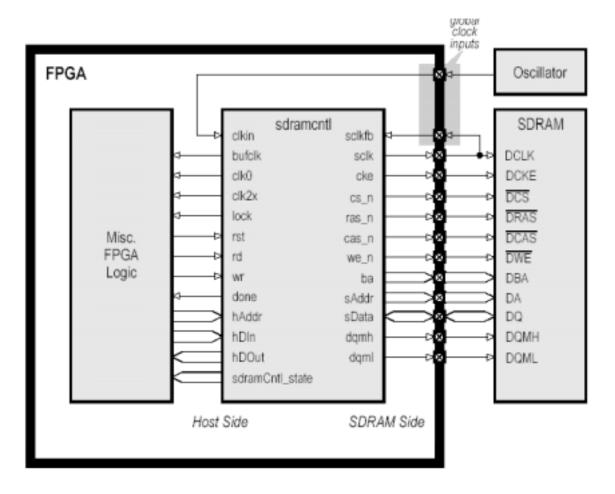

|           | 1. SDRAM Controller                      | 50         |

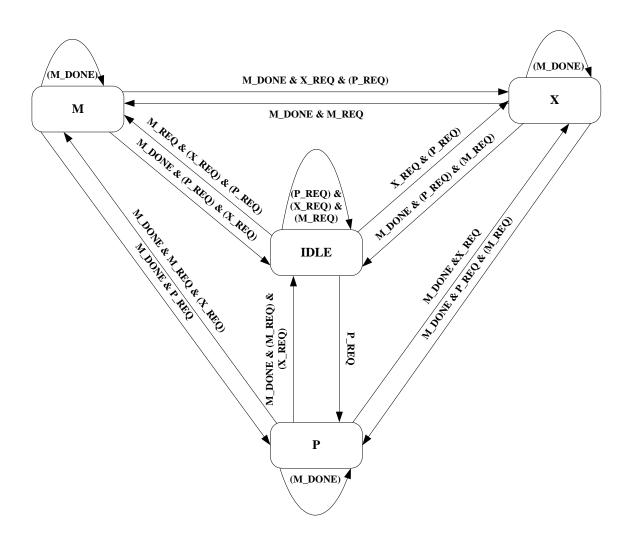

|           | 2. Memory Arbitrator                     | 53         |

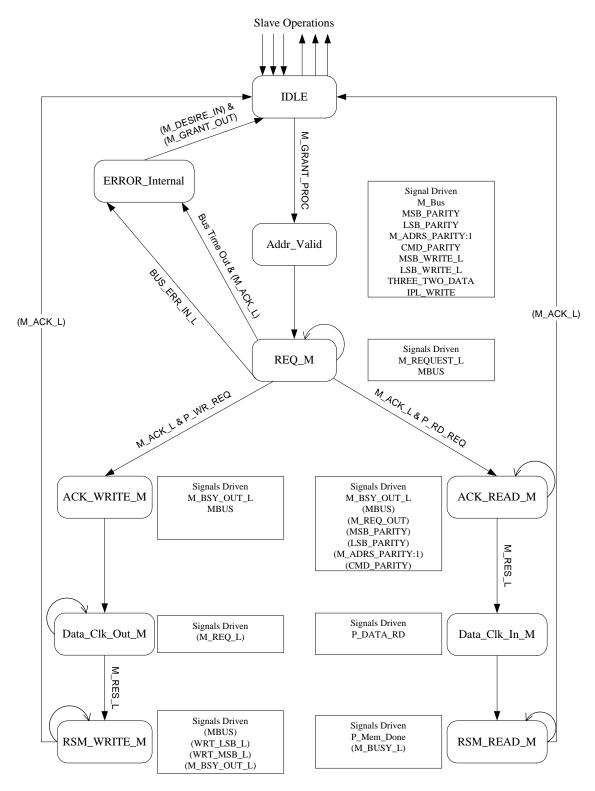

|           | 3. MBUS Controller                       |            |

|           | 4. XBUS Controller                       | 58         |

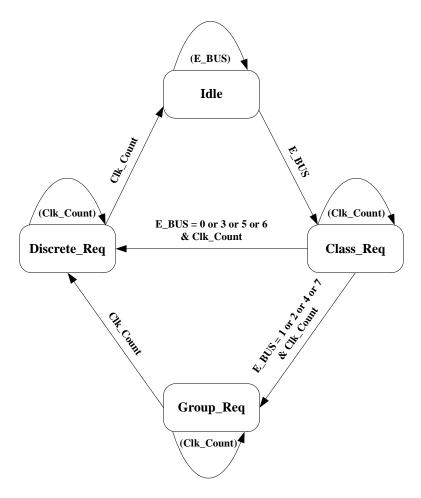

|           | 5. Event Bus Controller                  |            |

|           | 6. Top Level Design Interface            | 61         |

| IV. CONCI | LUSIONS                                  | 63         |

| APPENDIX  | X A: DOCUMENTATION LIST FOR THE AYK-14   | 65         |

| APPENDIX  | K B: DIRECT AND POLLED EVENTS            | 67         |

| APPENDIX  | X C: I/O INSTRUCTIONS                    | 69         |

| APPENDIX  | X D: XBUS COMMAND WORDS                  | <b>7</b> 3 |

| APPENDIX  | X E: VHDL SOURCE CODE                    | 101        |

| LIST OF R | EFERENCES                                | 199        |

| INITIAL D | ISTRIBUTION LIST                         | 201        |

## LIST OF FIGURES

| Figure 1.  | Engineering Processes                         | 7  |

|------------|-----------------------------------------------|----|

| Figure 2.  | AYK-14 Subsystems                             | 10 |

| Figure 3.  | AYK-14 Chassis 8 – CP2360                     | 11 |

| Figure 4.  | Six 1553 Data Bus Channels on F/A-18 C/D      | 12 |

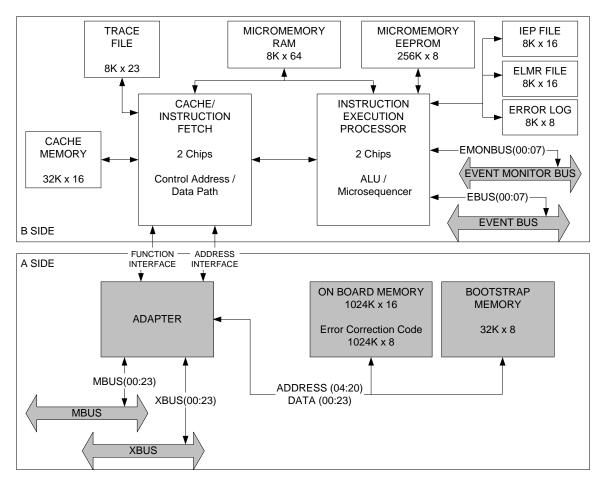

| Figure 5.  | VPM Block Diagram                             | 13 |

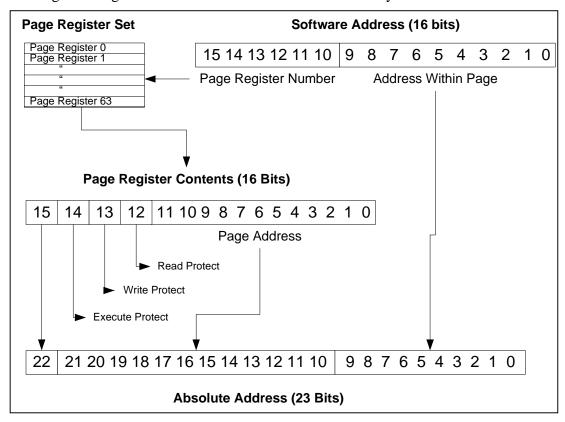

| Figure 6.  | Address Generation                            |    |

| Figure 7.  | Absolute Address Assignment                   | 16 |

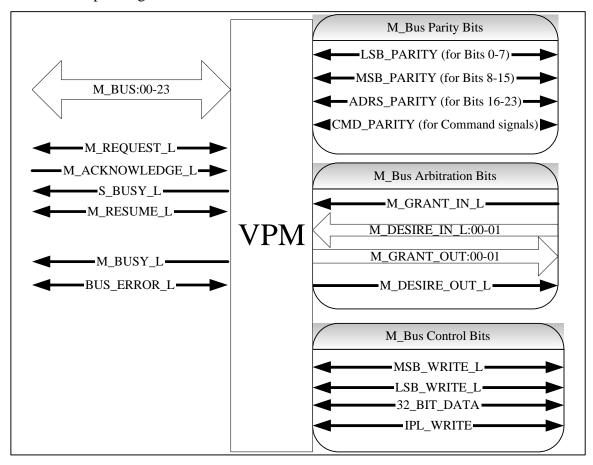

| Figure 8.  | MBUS Interface Signals                        | 18 |

| Figure 9.  | MBUS Standalone Operations                    | 19 |

| Figure 10. | XBUS Interface Signals                        | 21 |

| Figure 11. | XBUS Command Word Format                      | 22 |

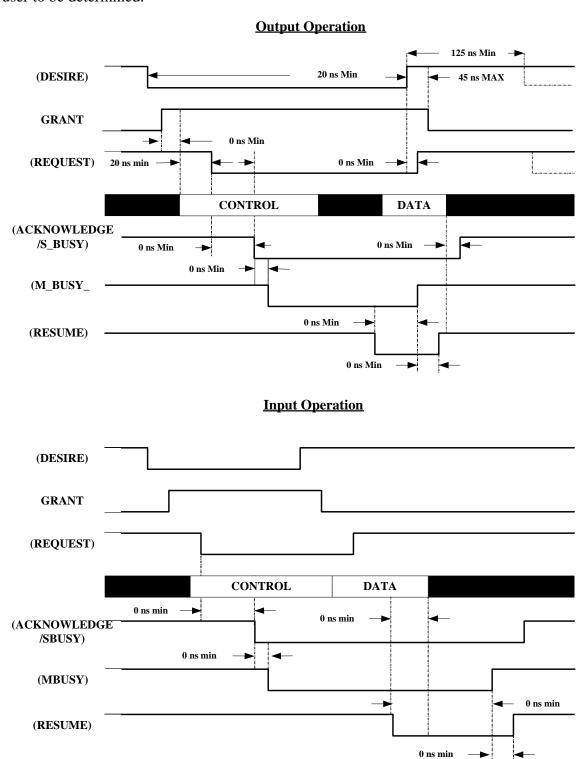

| Figure 12. | XBUS Timing Diagrams                          | 23 |

| Figure 13. | Software Execution Interrupts                 |    |

| Figure 14. | Event Monitor Bus Definition                  | 27 |

| Figure 15. | Event Bus Response Matrix                     | 28 |

| Figure 16. | Event Monitor State Sequence                  | 29 |

| Figure 17. | DSM Control Memory                            | 32 |

| Figure 18. | Input / Output Channel Events                 |    |

| Figure 19. | Discrete and Serial Module Interfaces         | 37 |

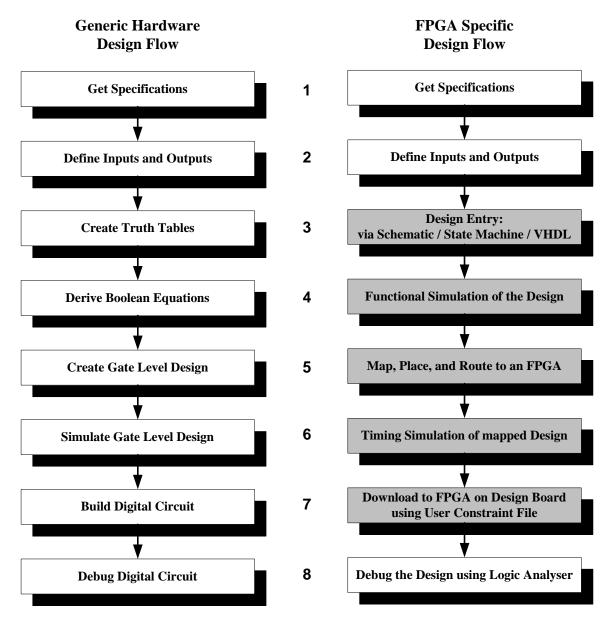

| Figure 20. | Hardware Design Flow                          | 44 |

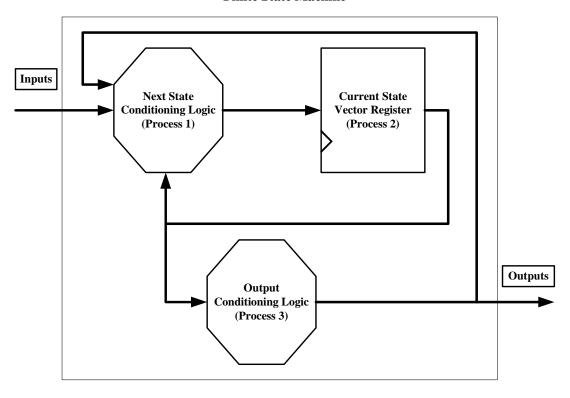

| Figure 21. | Finite State Machine Structure [After Ref. 9] | 45 |

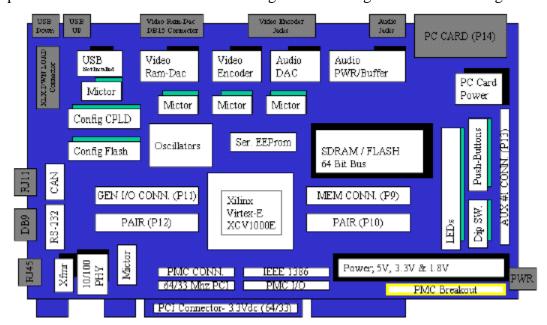

| Figure 22. | VIRTEX-E Development Board Functional Layout  | 48 |

| Figure 23. | Adapter Design Components                     |    |

| Figure 24. | SDRAM Functional Block Diagram                | 51 |

| Figure 25. | SDRAM Controller Interface                    |    |

| Figure 26. | Memory Arbitrator State Diagram               | 55 |

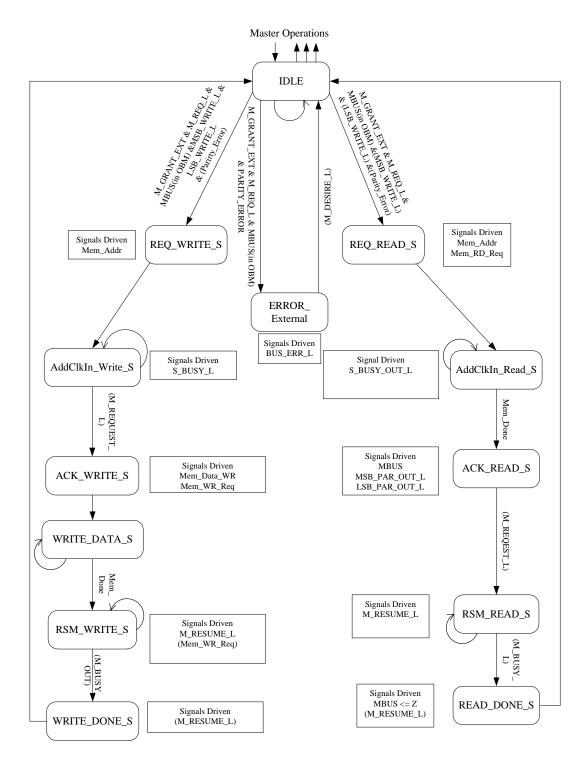

| Figure 27. | MBUS Controller State Diagram (Master)        |    |

| Figure 28. | MBUS Controller State Diagram (Slave)         |    |

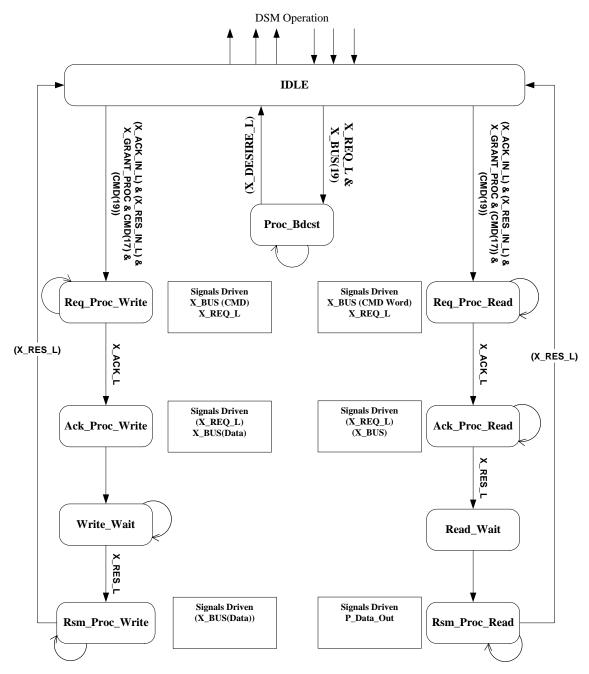

| Figure 29. | XBUS Controller State Diagram (Processor)     |    |

| Figure 30. | XBUS Controller State Diagram (DSM)           |    |

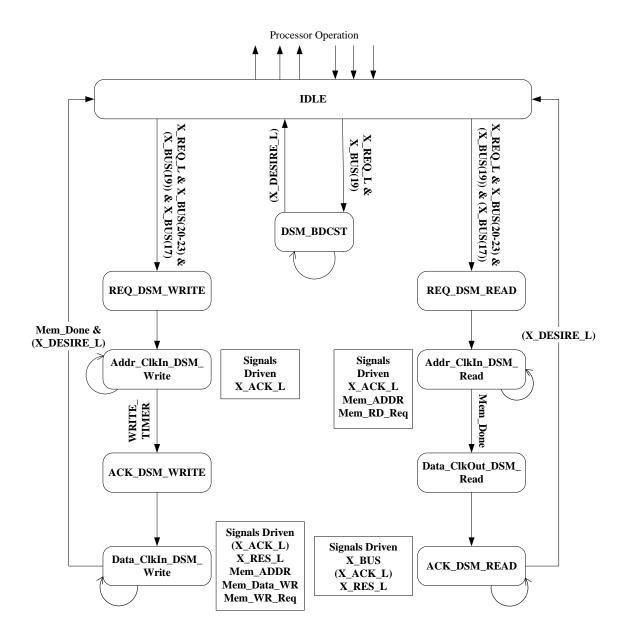

| Figure 31. | Event Controller State Diagram                |    |

## LIST OF TABLES

| Table 1. | Solutions to Replacing Legacy Processors [From Ref. 3] | 3 |

|----------|--------------------------------------------------------|---|

| Table 2. | I/O Channel Interrupts                                 |   |

| Table 3. | I/O Event Descriptions                                 |   |

| Table 4. | XBUS Commands – VPM to DSM                             |   |

#### **ACKNOWLEDGMENTS**

I would like to thank Professor Russ Duren for providing me with the opportunity, means, and guidance to complete this thesis. His instruction and mentoring has extended well beyond this thesis and I am truly grateful for his friendship and support. I would also like to thank Professor Hersch Loomis for his instruction during the design process and for his support. I would like to also thank Mr. Rex Coombs, PMA-209, for his time and exceptional level of support. The use of his lab, the supply of numerous documents, and the loan of an AYK-14 and CCU were essential factors in completing this thesis.

I am also extremely grateful to the U.S. Naval Test Pilot School for providing me with the opportunity and means to complete this thesis. I would specifically like to thank CDR Rich Brasel for allowing the completion of my thesis to be my primary duty. I would like to thank CDR Paul Sohl for his guidance and support during this difficult career transition. In addition, I would like to thank CDR C.J. Junge for his friendship, support, and inspiration.

My extreme thanks also goes to CDR Mike 'Croc' Croskrey for being my teammate on the AYK-14 recovery. I am indebted to you for your support on this thesis and on my transition from the Navy. It is a privilege to have been your classmate and your friend.

And finally my thanks goes to my wife and best friend, Michelle. I can never thank you enough for your unwavering support. I could never have completed this thesis without you by my side. To reach the stars, you must stand on the shoulders of giants. Thank you for being my giant!

#### I. INTRODUCTION

#### A. THE LEGACY AVIONICS ISSUE

The 1990's was a decade that ushered in many dramatic changes in the world. These changes had a profound effect on the U.S. government and the armed forces in particular. The two events that had the greatest effect on the military were the fall of communism and the technological revolution in the electronics industry.

The end of the Cold War left the military without a formidable adversary. This, in turn, led to budgetary changes that affected all branches of the military. More specifically, the funding for the acquisition of new military aircraft was greatly reduced. This occurred in parallel with a similar reduction in the budgets for modernization of existing, or 'legacy', aircraft. In order to deal with the shrinking budget, the operational lifetimes of many of these legacy aircraft were extended beyond their original service lifetimes. This has led to the average age of a U.S. Military aircraft being 20 years and continuing to increase. [Ref. 2:p. 1]

This increase in average age has reduced the effectiveness and readiness of the armed forces as a whole. According to the 'Committee on Aging Avionics in Military Aircraft', the U.S. Air Force reported a 10 percent decrease in readiness during the 1990's. The committee attributed this decline to the increasing age of the aircraft, "particularly the aging avionics systems on which they depend." [Ref. 2:p. 1] The shrinking budgets for upgrades to these avionics mean that the decline in readiness will most likely continue unless lower cost solutions can be found.

The technological revolution that has occurred during the 1980's and 1990's has brought with it great advances in electronics and computing. However, the economic impetus behind these advances has increasingly come from the commercial sector. As Reference 2 states "whereas the military once provided a large and profitable market for the electronics industry, the military electronics market today constitutes less than 1 percent of the commercial market." This means that the needs and requirements of the

<sup>&</sup>lt;sup>1</sup> The definition of legacy for this thesis will be as defined in [Ref. 1:p. 1] as any system that has been "designed, developed, and fielded."

military have had diminishing influence on the products that industry designs and produces.

The previously discussed budget shortfalls along with the reduction of influence in the commercial electronics sector have caused military avionics systems in general to fall further behind current technology. As these legacy avionics systems get older, the costs for modernization along with the costs to support the current systems continue to increase. Therefore, the need is clear for a way to modernize these aging systems that will lower these costs in the future.

#### B. POTENTIAL SOLUTIONS TO THE LEGACY PROBLEM

The solution to a problem as complex as the legacy avionics issue is not clear. The overall solution will lie in changes to design methods and acquisition policies that will continue to look for the benefits promised by COTS integration. Most importantly, the solution must also address the additional unforeseen problems that this integration has brought with it in a more far-reaching way.

This solution to the legacy avionics problem as a whole is too complex to be covered in one thesis. This thesis therefore will narrow the subject to address the area of microprocessors and their associated communication interfaces. This area can be considered of central importance to the problem as a whole. This is because microprocessors are so central to the performance of any avionics systems that any increase in performance of the processor will in turn almost guarantee an increase in performance of the entire system.

In his master's thesis, CDR Mike Croskrey [Ref. 1], investigates the possible solutions for the legacy avionics problem as they apply to microprocessors. He suggests several solutions to the problem and compares and contrasts the benefits and drawbacks of each. These solutions and their advantages are summarized in Table 1.

| Proposed Solution                                                                                                                                                                                                                                             | Advantages                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Upgrade to a COTS binary compatible microprocessor, when available.                                                                                                                                                                                           | <ul> <li>Maintains old code and allows incremental updates using the new processor</li> <li>Assures functionality of existing code</li> </ul>                                                                                                                   |

| Maintain old processor or capability of executing the old code with hardware  1) Keep old processor board and add a COTS processor board  2) Develop a dual instruction set processor  3) Port the old processor to an ASIC  4) Port old processor to an FPGA | <ul> <li>Maintains old code and allows incremental updates using the new processor</li> <li>Assures functionality of existing code</li> <li>ASICs are fast and have low power requirements</li> <li>FPGA relatively easy to modify if problems found</li> </ul> |

| Maintain the capability of executing the old code using a software emulator                                                                                                                                                                                   | Assures functionality of existing code                                                                                                                                                                                                                          |

| Port the old code to a new processor family                                                                                                                                                                                                                   | May increase throughput                                                                                                                                                                                                                                         |

| Translate the code to Higher Order Language (HOL)                                                                                                                                                                                                             | <ul> <li>Improves ability to maintain<br/>knowledgeable workforce</li> <li>Object oriented code facilitates reuse</li> </ul>                                                                                                                                    |

| Translate the code to COTS assembly language                                                                                                                                                                                                                  | Facilitates use of a more current processor                                                                                                                                                                                                                     |

Table 1. Solutions to Replacing Legacy Processors [From Ref. 3]

The solution that this thesis will focus on is the design and implementation of new hardware that is binary compatible with the existing processor and therefore able to execute the existing code. This hardware solution will also be binary compatible with all external interfaces since these components will not be redesigned as part of this thesis.

#### C. REENGINEERING

Forward engineering is the process of creating a new system and can be roughly broken down into three stages or processes. These stages include requirement specification, design, and implementation. The process of designing a system to replace an existing legacy system requires additional design steps in order to recover the design that is to be replaced. These additional steps can be grouped into a process called reverse engineering. Reverse engineering is the process of analyzing a subject that serves to identify its components and their interrelationship as well as produce a representation of

the system at a higher level of abstraction. Its primary purpose is to "increase the overall comprehensibility of the system for maintenance and future development." [Ref. 6, p16]

Reverse engineering can include the same steps defined in forward engineering but in reverse order. It also includes an additional step, or sub area, termed design recovery. Design recovery is a process in which domain knowledge, external information, and deduction are combined with observation to identify higher-level abstractions than those obtained directly. It is basically the process that combines all available resources to reproduce the information that allows a complete understanding of what the system does and how it does it. [Ref. 6]

In order to design and implement a new system that will replace an existing system, both the reverse and forward engineering processes must occur. This overall process, of both reverse and forward engineering, is termed reengineering. It can be defined as "the examination and alteration of a subject system to reconstitute it in a new form and the subsequent implementation of the new form." [Ref. 6, p15]

The concept of rapid prototyping is a process that provides the means to produce prototypes of a design early in the design process. These prototypes allow the testing of key aspects of the design continuously throughout the design stage so the effects of early design decisions can be determined before other design decisions are made. The benefit of these prototypes increases as the complexity of the overall design increases.

In reengineering, rapid prototyping has an additional benefit that can both speed the design process and validate the design. This additional benefit is the ability to test the prototype using the environment and tools available to test the original design. This is especially important in complex designs or designs that lack detailed documentation.

#### D. PURPOSE OF STUDY

The purpose of this study is to investigate the process of reengineering a legacy avionics system, particularly the memory and communication interfaces of an embedded microprocessor system. It will include the implementation of the recovered design using Field Programmable Gate Array (FPGA) technology. It targets the AN/AYK-14(V) Navy

Standard Airborne Computer; specifically the XN-8 chassis used onboard the F-18 C/D aircraft. This computer was chosen not only because it is representative of the legacy avionics challenge already addressed, but also because the AYK-14 is the focus of an analysis of alternatives being conducted by the Naval Air Systems Command (NAVAIR) Advanced Weapons Laboratory (AWL).

The secondary purpose of the design recovery will be to serve as a reference for designers and programmers who are continuing work on the AN/AYK-14.

#### II. DESIGN RECOVERY

#### A. OVERVIEW OF REENGINEERING PROCESS

Chapter I defined the terms that describe the process and the steps involved in engineering processes, which are illustrated in Figure 1.

Figure 1. Engineering Processes

The AYK-14 Reengineering Plan, adapted from Reference 6 and shown in Figure 1, helps to depict the steps that were followed in this thesis. The key point that is illustrated is that the AYK-14 reverse engineering phase only investigated to the level of the design. The requirements were not analyzed directly for numerous reasons. First, the primary goal of this project was to design a replacement for the AYK-14 processor that was binary compatible with the rest of the system, therefore there was little room for changes to the overall design that would better meet the requirements. Another reason was simply that the time and resources available to continue the design recovery to the requirements level were not available. It should be pointed out that the requirements were researched at a high level as part of the design recovery to aid in the understanding of the design and implementation.

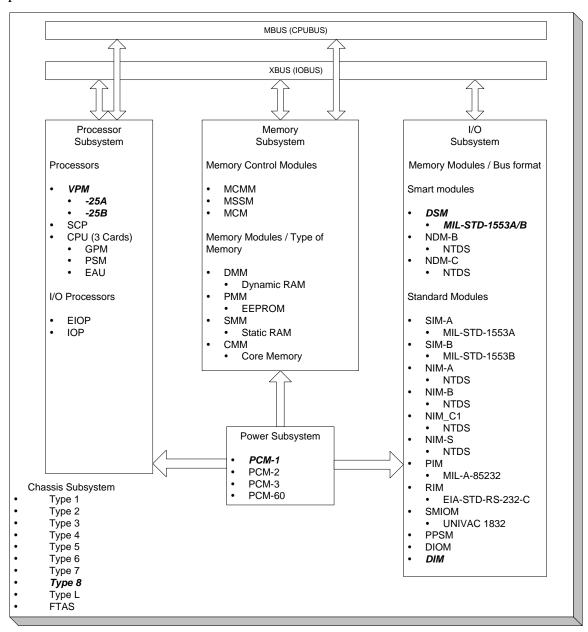

#### B. OVERVIEW OF THE AYK-14

An understanding of the mission and history of an avionics system is essential to the recovery of its design. This section will give a brief introduction to the AYK-14 to help define components and their roles. However, it is recommended that the reader refer to References 1 and 7 for a more detailed analysis and background on the system. The documentation supporting the AYK-14 was produced at varied times in the computer's lifecycle and therefore only considers equipment available at the time it was authored. This section is also intended to illustrate all of the major components of the system, even if they are outdated, in order to provide a reference when referring to the documentation. All of the documentation used in the design recovery is listed in Appendix A.

#### 1. History of the AYK-14

Development of the AYK-14 began in 1976 by Control Data Corporation. It was designated the Navy Standard Airborne Computer in 1986. Since then, the AYK-14 has been used on seven types of Navy and Marine Corps aircraft including the AV-8B, F-14D, and F/A-18C/D. It consists of a family of modules that fit into a plug-compatible backplane. These modules can be broken down into four groups by function and they include processor, I/O, memory, and power. As the AYK-14's requirements have changed and technology has improved, the modules in each subsystem have evolved to increase overall capability. Therefore, there are numerous versions of the AYK-14 based on platform requirements and modules present.

#### 2. Processor Subsystem

The processor in the AYK-14 has evolved through three generations of upgrades. The first generation is the central processor unit (CPU), which consists of three double-sided modules: general processor module (GPM), processor support module (PSM), and extended arithmetic unit (EAU). The second generation is the single card processor (SCP) that combines the three modules of the CPU into one module. The third generation processor is the very high-speed integrated circuit (VHSIC) processor module (VPM). An attribute of the VPM that is important to highlight is that it is the first processor to have onboard memory (1 M-word). The VPM is the processor that will be targeted for design recovery in this thesis.

There are two additional processors that are used solely for I/O functions. The first generation is the I/O processor (IOP), superceded by the extended I/O processor (EIOP).

#### 3. Memory Subsystem

The memory subsystem consists of memory control modules and memory modules. The memory control modules provide access of the memory modules to the processor over the memory bus (MBUS or CPUBUS). There are three control modules: memory control module with memory (MCMM), memory subsystem module (MSSM), and the memory control module (MCM). There are four memory modules with four different forms of memory: DRAM memory module (DMM), programmable memory module, using EEPROM, (PMM), semiconductor memory module, using SRAM, (SMM), and core memory module (CMM).

#### 4. Input / Output Subsystem

The I/O subsystem consists of a combination of I/O modules dependant upon the communication requirements. There are eight types of I/O modules that can be further classified as smart or standard. A smart I/O module has the ability to perform additional processing normally performed by the processor or I/O processor. This capability will be defined in greater detail in section H. The I/O modules interface with external equipment via buses or discretes. The I/O modules communicate with the processor via the I/O bus (IOBUS or XBUS). An AYK-14 can contain up to 16 I/O modules, with a maximum of five smart modules, depending on the Chassis used. The I/O modules and their classifications are listed in Figure 2.

#### **5. Power Subsystem**

The power subsystem is a single module that provides regulated power to all other systems. There are four types of module dependant upon the power requirements of the system. They are the power converter module PCM –1, PCM-2, PCM-3, and PCM-60.

#### 6. Chassis Subsystem

The chassis subsystem is the housing used to contain all of the modules. There are nine standard chassis types to meet the size and connection requirements of the different

AYK-14 roles. The chassis contains a backplane into which each module is plugged to provide communication.

Figure 2. AYK-14 Subsystems

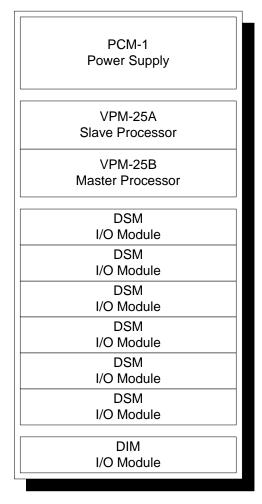

#### C. AYK-14 CONFIGURATION ON THE F-18C/D

The current AYK-14 configuration that is used on the F-18C/D is the CP-2360. It contains two VPMs (one 25B - Master, one 25A - Slave), six DSMs, one DIM, and one PCM-1 as shown in Figure 3. This is the configuration that was targeted for this thesis.

More specifically, the VPM processor as used in this configuration was the target of the reengineering process.

Figure 3. AYK-14 Chassis 8 – CP2360

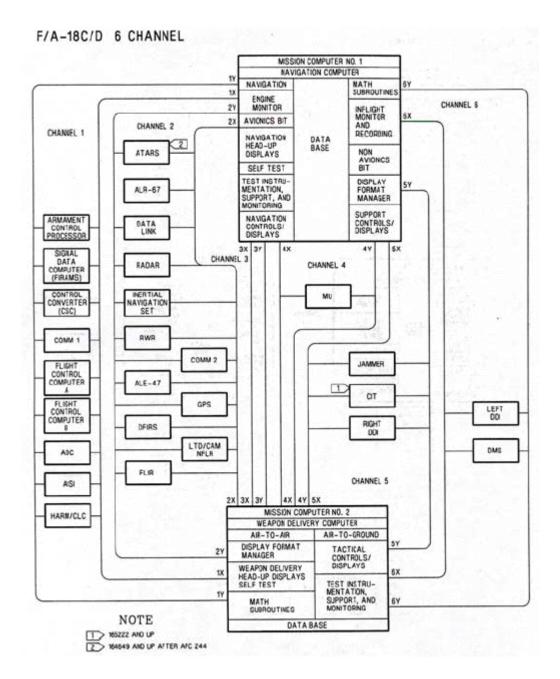

The avionics system uses two CP2360's as Mission Computers, designated MC1 and MC2. MC1 processes all navigation and monitoring tasks and MC2 processes all sensor and weapons control tasks. The Mission Computers communicate with the other systems over six 1553 data-bus channels, as illustrated in Figure 4.Earlier F/A-18 aircraft use a chassis with only five 1553 data-bus channels.

Figure 4. Six 1553 Data Bus Channels on F/A-18 C/D

#### D. VPM PROCESSOR

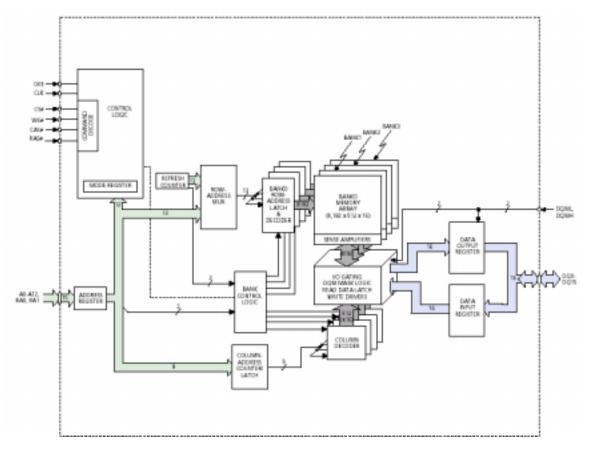

The VPM is a 16-bit Complex Instruction Set Computer (CISC) type processor with over 1 Million words of on-board memory. It is a 2-sided module that is organized into 3 major sections. These sections are the Instruction Execution Processor (IEP), Cache/Instruction Fetch (C/IF), and Adapter and are shown in Figure 5. The VPMs primary interfaces include the Input / Output Bus (XBUS or IOBUS), the memory bus

(MBUS), and the Event and Event Monitor busses (EBUS and EMON) along with multiple discretes. The A-side contains the 24 memory chips, the Adapter array, the MBUS and XBUS data and control signal buffers, and the external discrete receivers. The B-side contains four arrays, including the IEP and C/IF, 34 memory chips, and Event drivers and receivers.

Figure 5. VPM Block Diagram

The IEP section is comprised of the microsequencer chip, the arithmetic chip, and the micromemory. It is implemented using a microprogrammed processor that executes microcode programs. Microcode programs control elementary parts of the processor and define the software instruction set used for the AYK computer. Every software command executable by the VPM is interpreted in the IEP by a series of microcommands. These commands, or microcode, are stored in EEPROM and downloaded to SRAM at start-up. The microcode stored in these memories is called firmware. Some other functions of

firmware include running BITs, servicing Events, and I/O operations. The IEP design was recovered and implemented by CDR M. Croskrey in his master's thesis and his design serves as the instruction processor for the design developed here. For additional details concerning the IEP design recovery, refer to Reference 1.

The C/IF section is comprised of the cache control and address chip, the cache memory, the data path chip, and the trace file. It provides the on-chip cache for the IEP and manages requests for memory to the adapter. The use of an on chip cache has been shown to significantly increase throughput and overall performance of most processors, however, the design recovery and implementation of this section is left to future students continuing work on this project due to time constraints.

#### E. ADAPTER

The primary function of the adapter is to control the onboard memory interface and the XBUS and MBUS interfaces. It handles all requests for memory from either the data path array, other VPMs via the MBUS, or I/O modules via the XBUS. It interfaces with the event system and contains two sets of page registers used for I/O memory references.

The VPM is capable of operating in two memory modes dependant upon the other modules present. These modes are standalone and non-standalone. In standalone mode, the VPM performs the role of Memory Controller and arbitrates memory requests and M and X bus usage. In non-standalone mode, a memory controller, such as the MCMM, is required to manage the memory. Both VPMs in the CP-2360 operate in the standalone mode.

The VPM is a 16-bit processor and the IEP and C/IF use 16 bits addresses for memory. The VPM has a memory reach of 8 million locations, which requires 23 bits for addressing. In order to reach this amount of memory, the VPM uses memory paging. The VPM uses banks of 64 16-bit wide Page Registers. The upper 6 bits of the 16-bit Software Address points to one of the 64 page registers. The contents of this register are used to create the complete 23-bit address, with 3 bits being used for memory protection. This 23-bit address is considered the absolute memory address and can address any location in the VPM memory range. The absolute address generation is depicted in Figure

6 for clarity. The control address array contains four sets of 64 page address registers used for generating the absolute address for on-board memory references.

Figure 6. Address Generation

The VPM on board memory (OBM) consists of 1024K locations of 24 bit words. Each word contains 16 bits of data and 8 bits of error correction code. The memory is broken down into 256K of SRAM and 768K of EEPROM. The bootstrap memory consists of 32K addresses of 8-bit data organized as 16K of 16-bit word storage on a EEPROM. The lower 8K is loaded with bootloader programs for use on start-up or after a reset. The memory address range of the OBM is dependant upon the VPM's location and role within the Chassis. The memory map of the entire address range is shown in Figure 7.

|      | 0                | 64K | 1M                  | 1 2M 3N                              |              | M 4N                                 |               | И 5N                                 |               |                                      |

|------|------------------|-----|---------------------|--------------------------------------|--------------|--------------------------------------|---------------|--------------------------------------|---------------|--------------------------------------|

|      | MEM MOD or VPM-B |     | or VPM-B Master VPM |                                      | SLAVE VPM #1 |                                      | SLAVE VPM #2  |                                      | SLAVE VPM #3  |                                      |

|      | 000000<br>00FFF  |     | EEPROM<br>RAM       | 100000<br>1BFFFF<br>1C0000<br>1FFFFF | EEPROM       | 200000<br>2BFFFF<br>2C0000<br>2FFFFF | EEPROM<br>RAM | 300000<br>3BFFFF<br>3C0000<br>3FFFFF | EEPROM<br>RAM | 400000<br>4BFFFF<br>4C0000<br>4FFFFF |

| PAGI | PAGES 0-3F       |     | ES 0 - 3F 400-6FF   |                                      | 800 - AFF    |                                      | C00 - EFF     |                                      | 1000 - 12FF   |                                      |

|      |                  |     | 700-7               | 'FF                                  | B00 -        | BFF                                  | F00 -         | FFF                                  | 1300 -        | 13FF                                 |

Figure 7. Absolute Address Assignment

#### F. EXTERNAL BUS OPERATION

The MBUS and XBUS (or IOBUS) are independent, 24-bit bi-directional busses that provide communication between the modules of the AYK-14. The MBUS is used to provide memory access to every VPM's OBM and with memory modules. The XBUS is used for communications with I/O modules and for inter-processor communications (IPC).

The process of allowing modules to gain control of bus and transfer data on that bus is called bus arbitration. In standalone memory mode, the adapter of the Master VPM acts as the arbitrator for both busses. There are five primary control signals that are used for bus arbitration and control for each bus. These signals are DESIRE and GRANT for arbitration, and REQUEST, ACKNOWLEDGE, and RESUME for control.

Bus operations are initiated by the user and consist of two parallel word transfers. The first word is a 24-bit control word and is transferred from the VPM or smart I/O module to address a particular module and provide control information. The second word is a 16-bit data word that transfers data or status as input or output as determined by the function word.

#### 1. Standalone Mode MBUS Operation

The VPM standalone mode of operation uses the memory control logic of the VPM that eliminates the need for a separate memory control module. Each VPM has access to the OBM of any other VPM, as well as memory modules if used. The MBUS functions as a 23-bit physical (post-paged) address memory bus, with the OBM address

allocation as shown in Figure 7. Each VPM performs its own paging and all I/O memory references use page set 0 on the master VPM. There is no interprocessor communication of page register or page state changes. Therefore, the paging and protection contained in each VPM is applicable only to that VPM. A single memory bus is used to prevent the interleaving of off-board memory references.

In standalone mode, the MBUS arbitration logic supports two external desire/grant signal pairs plus the processor's own desire/grant pair for a total of three users. Additional users can be added by daisy chaining the desire/grant signals. The version of the AYK-14 used in this thesis only has two MBUS users so the details of daisy chaining will not be covered here.

A user requests use of the bus by activating its DESIRE signal (active low). The desire signals of both external users are resynchronized before being used in the arbitration logic. The internal desire signal is captured in a flip-flop before it enters the arbitration logic. The synchronous desire signals are fed into the prioritization logic to determine which user is granted control of the bus. The algorithm makes use of a last user register that keeps track of which user was granted control of the bus last. The result is a rotating priority scheme based on which user had the bus last. The module that last used the bus drops to the lowest priority and the one following it gets the highest priority.

The arbitration algorithm outputs the next-user, which is fed into a latch that opens during the last half of the clock cycle. When enabled, the latch captures the next-user, which causes the appropriate GRANT signal to be enabled. The asynchronous and synchronous (post flip-flop) desire signals must both be active as a condition for activating a grant signal. This is to ensure that the grant is not activated before the desire signals are synchronized.

In addition to the five hand-shaking control signals, the VPM utilizes 10 additional signals for MBUS error detection and control. The signals are listed in Figure 8 and they include four parity bits, four control signals, a busy signal and an error signal. The first two control signals, MSB\_WRITE and LSB\_WRITE, indicate the type of memory operation, read or write. The other two control signals exist for future capability. The busy signal, M\_BUSY, is used to indicate when the VPM is driving data on the bus.

The parity bits are used for error detection, with three used for the 24 address lines, for both the address and the data words, and one for the four command signals. The error control signal is used to indicate when a parity error is detected. The additional control signals are needed because all of the 24 bits are used for the address in the command word when operating in the standalone mode.

Figure 8. MBUS Interface Signals

After receiving control of the MBUS via a Grant signal, communication on the MBUS is initiated by the VPM activating a Request signal along with the 23-bit absolute memory address. The VPM also drives the four parity bits and the four additional control signals. The VPM who's OBM is in the range of the address checks the parity of the address and the command signals. If there is an error, it activates the Error signal and stops responding to the memory request. If the parity check is successful, the responding VPM activates the Acknowledge signal and clocks-in the address. The initiating VPM activates its MBUSY signal to indicate that it is ready to either read or write data on the

MBUS. It will also deactivate the desire signal to the arbitration logic to allow the next user to be determined.

Figure 9. MBUS Standalone Operations

If the control signals indicated a read command, the initiating VPM will deactivate the Request signal and the responding VPM will drive the requested data on the MBUS along with the corresponding parity bits. When this data is valid, the responding VPM activates the Resume signal to indicate that the data is valid. The initiating VPM will clock-in the data and deactivate its MBUSY signal to indicate that the data has been read. The responding VPM will then stop driving the MBUS and deactivate the Resume signal to terminate the operation.

If the control signals indicated a write command, the initiating VPM will drive the requested data on the MBUS along with the corresponding parity bits and then deactivate the Request signal. When the responding VPM sees the deactivation of the Request signal, it clocks-in the data and activates the Resume signal. In response to the Resume signal, the initiating VPM removes data from the MBUS and stops driving the four control signals and the MBUSY signal. The input and output operations are illustrated in Figure 9.

#### 2. Standalone XBUS Operation

The XBUS is the primary communication path between the processor and the I/O subsystems. All I/O control, instructions, and data transfer operations utilize this bus. For 'smart' I/O modules, the XBUS provides a means for direct access to OBM. The XBUS also provides an asynchronous channel for interprocessor communications. The XBUS interface signals are illustrated in Figure 10.

In standalone mode, the XBUS arbitration logic supports six external desire/grant signal pairs plus the processor's own internal desire signals for a total of seven users. Additional users can be supported through daisy chaining of desire and grant signals. The Adapter on the master VPM monitors the external desire signals along with its own internal desire signal. The adapter arbitration logic determines the next user through a rotating equal priority process implemented in the same fashion as the MBUS arbitration previously discussed.

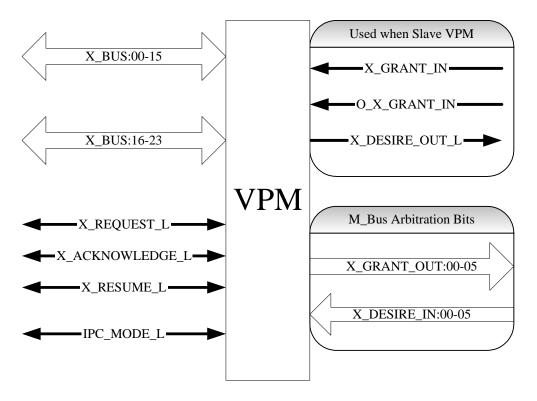

Figure 10. XBUS Interface Signals

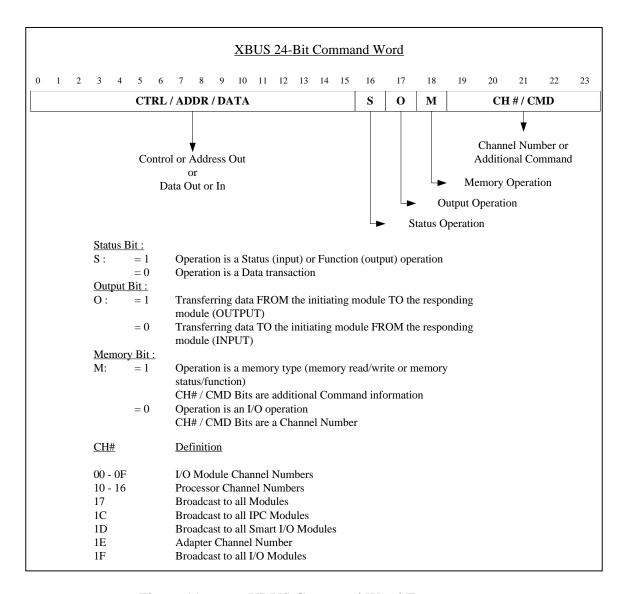

The first step in XBUS communication is the Desire signal. Any module requesting use of the bus will activate its desire signal and wait for a response from the adapter. Once the adapter has determined the next user through the arbitration logic, it activates the Grant signal to that module. The owner of the bus then activates the Request signal while simultaneously driving the 24-bit control word onto the bus. The upper 8 bits of the control word, or XBUS Command Field, contain control information regarding the type of operation requested and the intended recipient. The lower 16-bits contain either a control word, an address, or data depending on the type of operation requested. Figure 11 illustrates the breakdown of the Command word and summarizes the meanings of the fields.

Figure 11. XBUS Command Word Format

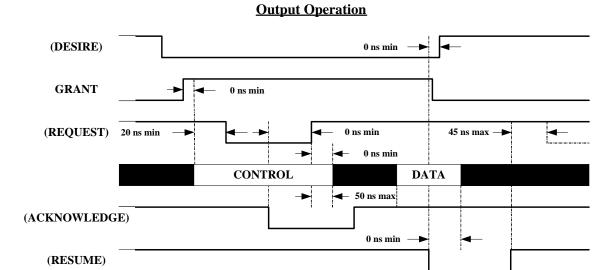

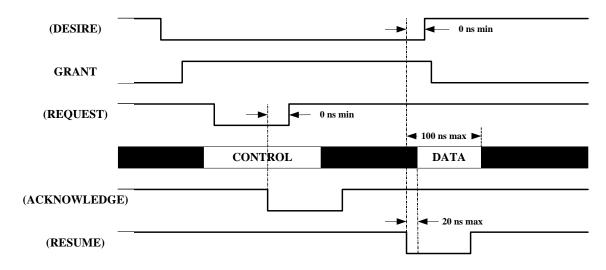

After the module that was addressed decodes the control word, it activates the Acknowledge signal in response. If the operation commanded is an output, the module that issued the control word drives 16 bits of data onto the bus. The receiving module clocks-in the data and activates the Resume signal to indicate receipt. If the operation is an input, the commanded module activates the Resume signal, to indicate that it is now driving the bus, followed by driving the 16 bits of data onto the bus. The data will remain active for the duration of the Resume signal. Upon deactivation of the Resume signal, the arbitration logic will update the priority list and begin the process again. For I/O module broadcast operations, the Master VPM always generates the bus Acknowledge and Resume signals regardless of initiating module. For processor module broadcast

operations, the initiating module generates the bus Acknowledge and Resume signals. These steps are illustrated in Figure 12 for both input and output operations.

## **Input Operation**

Figure 12. XBUS Timing Diagrams

When the XBUS is used for interprocessor communications, only bits 16-23 of the 24-bit bus are used for command and control along with the control and hand shaking signals. These 8 bits are referred to as the IPC BUS. Interprocessor communications consist of input and output transactions between VPMs and can be either from one VPM to another or broadcast to all VPMs in the system. The additional control signal used is

the IPC MODE signal and is connected to all VPMs. When activated, it causes all other VPMs to interpret Bits 16-23 as an IPC command.

#### G. EVENT SYSTEM

The event system is the mechanism by which the IEP is notified of conditions on the VPM, in other modules, or on other chassis that require servicing. It is controlled by the microsequencer array, part of the IEP, which monitors all sources for 'active' events. An active event is a condition or state that requires some type of action from the processor. Each event has a routine in firmware associated with it that can be called by the microsequencer to service the event.

The IEP, via firmware, checks for active events during idle loops when software is stopped or before each instruction is executed when software is running. The firmware interrogates for and handles all active events before it executes another software instruction. If more than one event is active, the microsequencer prioritizes the events based on a configuration dependant priority scheme. The event system provides a means of monitoring indicators, warnings, software chain execution, and external data transfers. There are two parallel subsystems in the event system; the polled event system and the direct event system.

The VPM also has an interrupt system similar to other processors in addition to the event system. Normal software execution is stopped for the handling of these interrupts. All of these software interrupts<sup>2</sup>, not automatically trapped by microcode, are signaled via activation of associated events. The interrupts to the VPM can come from any module in the Chassis and are divided into three classes based upon their source. Class I interrupts deal with hardware failures or functions. Class II interrupts indicate software failures or functions. And Class III interrupts are for I/O failures or functions. The interrupts can be locked out by class, via software commands, by setting bits 12 - 14 in status register 1. All interrupts and the events associated with them are listed in Figure 13.

<sup>&</sup>lt;sup>2</sup> The AYK-14 documentation refers to all three classes of processor interrupts as 'software interrupts' because they can interrupt normal execution of the software for handling.

|          |     |                             | Event | Event    |

|----------|-----|-----------------------------|-------|----------|

| Cl       | ass | Interrupt                   | Class | Discrete |

| Hardware | I   | Power Fault                 | 0     | 0/1      |

|          |     | Memory Timeout              | 5     | 1        |

|          |     | Memory Parity               | 5     | 2        |

|          |     | Hardware Fault Warning      | 5     | 3        |

|          |     | I/O Failure                 | -     | -        |

|          |     | Thermal Overload            | 0     | 2/3      |

|          |     | Hardware Fault              | 5     | 6        |

| Software | П   | CP Instruction Fault        | -     | -        |

|          |     | I/O Instruction Fault       | =     | -        |

|          |     | Floating Point              |       |          |

|          |     | Under/Overflow              | =     | -        |

|          |     | Executive Return            | -     | -        |

|          |     | Executive Mode Fault        | -     | -        |

|          |     | Memory Protect Fault        | 6     | 0        |

|          |     | RTC Overflow                | 6     | 1        |

|          |     | Monitor Clock Overflow      | 6     | 2        |

|          |     | System Reset                | 6     | 4        |

|          |     | Processor Interrupt 0       | 6     | 6        |

|          |     | Processor Interrupt 1       | 6     | 7        |

|          |     | Fixed Point Overflow        | -     | -        |

|          |     | Module Overtemp             | 5     | 7        |

|          |     | External Interrupt 2        | 3     | 6        |

|          |     | External Interrupt 3        | 5     | 4        |

|          |     | I/O Channel Abnormal        |       |          |

| I/O      | III | Interrupt (ERI)             | 7     | 0/4      |

|          |     | External Interrupt (EII)    | 7     | 1/5      |

|          |     | Output Chain Interrupt      |       |          |

|          |     | (OCI)                       | 7     | 2/6      |

|          |     | Input Chain Interrupt (ICI) | 7     | 3/7      |

Figure 13. Software Execution Interrupts

## 1. Polled Event System

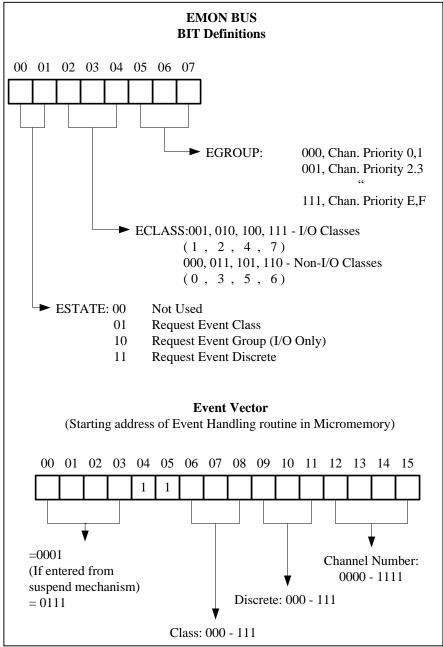

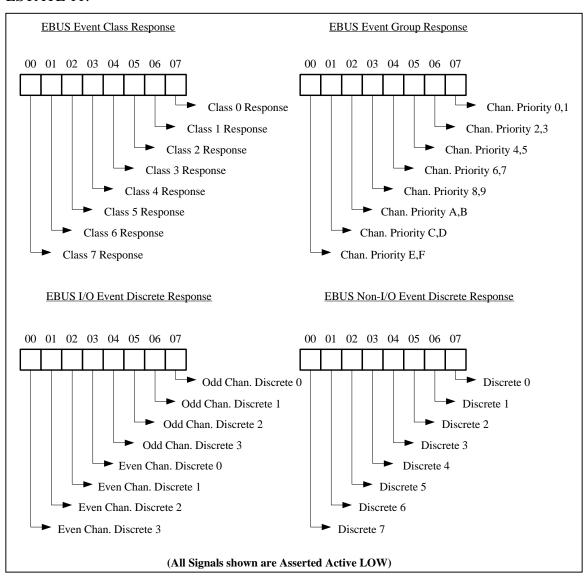

Polled events are events that occur on other modules that require servicing by the VPM processor. They deal primarily with software chain execution or external data transfers. They are referred to as polled events because the event monitoring system uses a polling sequence to determine which events are active. The event polling system consists of two 8-bit busses, the event monitor bus (EMON) and the event bus (EBUS). The EMON bus is driven by the VPM hardware and used to pass commands to manage the polling sequence. The EBUS is an open collector bus that is driven by the modules of the event system in response to commands on the EMON bus.

Polled events are organized by four attributes including priority, class, group, and discrete. Every event is assigned to one of three priority levels, and one of eight classes. An important note is that the event attribute of class is separate from the interrupt attribute of class. As an example, all class III interrupts shown in Figure 13 are listed in the event class seven. The binary form of the class, group, and discrete information of an event is used to form an event vector. This vector is used to point to the starting address in microcode of the event handling routine and is shown in Figure 14.

There are eight different classes of events, with four dedicated to I/O events and four to non-I/O events. The I/O events are further broken down into groups or channel pairs. Since there are only eight EBUS lines, the I/O modules must be grouped into the channel pairs to provide the ability for up to 16 I/O modules to activate events. This is explained in more detail when the polling sequence is covered. Within each class of events, there are eight discrete events for non-I/O events, and four for I/O events. All of the events are listed by class and discrete in Appendix B (See Microcode Reference Manual – p 4-17).

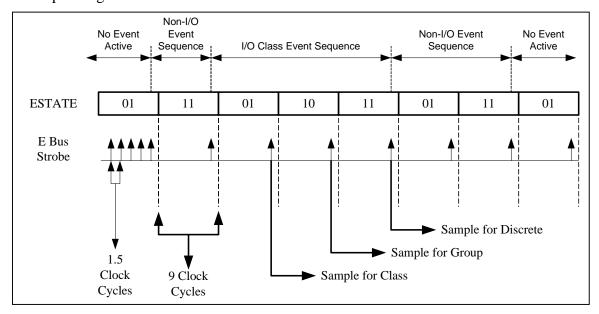

The event monitor continually queries the modules in the event system for events that have become active. It does this by cycling through a series states during which it determines which events are active, and which active event has the highest priority. These states are sent to the modules via the EMON bus and the modules responses are returned via the EBUS. The polling sequence is required because the modules on the EBUS do not each have discrete signals to indicate the presence of an event. The EMON bus is shown in Figure 14 along with a listing of the bits meanings.

#### a. $1^{st}$ State: ESTATE = 01

The first state in the polling sequence is ESTATE = 01. In this state, the event monitor is requesting any active events from any module capable of initiating a polled event. When any module detects this state on the EMON bus and has an active event, that module will drive the EBUS line corresponding to the class of event that is active. If there are no active events, the event monitor remains in this state. If an event is detected on the EBUS, the event monitor will determine the highest priority class of event that is active and drive the ECLASS lines with that class value. If that class is an

I/O class (Class = 1,2,4,7), the event monitor will then transition to ESTATE = 10. If it is a non-I/O class (Class = 0,3,5,6) the event monitor will proceed to ESTATE = 11.

Figure 14. Event Monitor Bus Definition

## b. $2^{nd}$ State: ESTATE = 10

If the highest priority event class with an active event is an I/O class, then the event monitor will enter ESTATE 10. Along with the ESTATE bits, the monitor now

drives the ECLASS bits with the highest priority class with an active event. In this state, the event monitor is requesting all modules with active events in the class output on the ECLASS lines to respond on the EBUS lines. There are two I/O modules, or pairs, assigned to each discrete line. The event monitor will determine the highest priority channel pair based on the EBUS response and drive the EGROUP lines of the EMON bus with that value. The priority scheme used is a function of the wiring of the interconnect assembly for the assigned slot in the chassis. The event monitor will then transition to ESTATE 11.

Figure 15. Event Bus Response Matrix

# c. $3^{rd}$ State: ESTATE = 11

If the highest priority event class with an active event is a non-I/O class, then the event monitor will enter ESTATE 11 directly from ESTATE 01. Along with the ESTATE bits, the monitor now drives the ECLASS bits with the highest priority class that has an active event. For an I/O class, the monitor will drive the highest priority channel pair, based on the determination from ESTATE 10, onto the EGROUP lines. For a non-I/O class, the monitor will drive the EGROUP lines to a known value corresponding to the class.

Figure 16. Event Monitor State Sequence

In this state, the module or module pair with the highest priority should now be the only one responding on the EBUS. For a non-I/O class, the responding module will drive the EBUS lines corresponding to the discrete events that it has active. For I/O modules, the EVEN module of the selected channel pair will respond on the lower four lines of the EBUS, and the ODD module will respond on the upper four lines. This restricts the I/O modules to only four events in each class.

The Class, Group, and Discrete values that are obtained are then used by the event monitor to generate the event vector, shown in Figure 14, for microcode handling of the highest priority event. After creating the event vector, the event monitor transitions back to ESTATE 01 and begins the sequence again. The EBUS responses to

each ESTATE is shown in Figure 15 and the timing for the polling process is shown in Figure 16 for additional clarity.

#### 2. Direct Events

Direct events are generated in the control address, data path, and adapter arrays and sent to the microsequencer array. There are also direct events that come from off the module as well as some generated internally in the microsequencer array. There are 63 events that can be stored for handling in the direct event register. Direct events provide a means of notifying the event monitor of an immediate request for service from the firmware. It is more direct than the polled events but the events are still subject to priority logic and can be masked as well.

Direct events from the direct event register and the events generated in the polling sequence are filtered through a class mask. This mask is controlled via firmware and provides a means to stop specific classes of events from being seen by the priority logic. The priority logic compares all unmasked events and determines the highest priority event, which is then serviced by the firmware.

#### H. INPUT / OUTPUT MODULE OPERATION

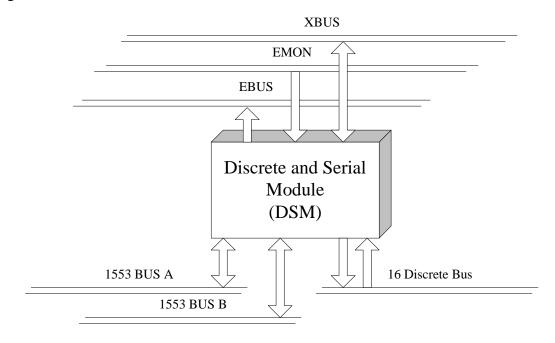

The I/O modules provide the communication link between the VPM processors and other equipment in the system. The VPM communicates with the I/O modules via the XBUS and Event bus. The I/O modules communicate with other equipment via discrete signals and buses, specifically the MIL-STD-1553 data bus for the configuration recovered. The I/O modules are categorized as smart or standard based upon the amount of on-board processing they are capable of executing.

#### 1. I/O Channel Software

There are three types of commands that are used to control the I/O modules operation. The first two types are 'user' commands that are used in operational programs and are considered software commands. Some of the capabilities provided are the ability to initiate and halt I/O channel operation, enable and disable I/O channel interrupts, load and store control memory words, and read I/O channel status.

The first type of command controls the initiation of all I/O channel operation. This command is the Input / Output Command Request (IOCR), Op Code 7400. This processor instruction, when encountered in the software during normal program execution, causes the processor to execute the instructions at a specific location in main memory called the command cell. The location of the command cell is 0060 and 0061 if the executing VPM is operating as the master, and 0062 and 0063 if it is operating as the slave. The IOCR is used in the main source code to start or stop I/O channel programs, monitor or modify channel operations, and modify Control Memory locations.

The second type of command is the set of processor executable commands that are used in the source code to control I/O operations. These commands can be broken down into three classes, including Command Instructions, Chain Instructions, and Command/Chain Instructions, and are listed in Appendix C. The Op Codes for these commands fall in the range E0-FF and are illegal unless executed following an IOCR command. These commands can be executed by the VPM or by a Smart I/O modules. These are the commands that are used in the programming of I/O channel functions.

The third type of command is the set of command words that can be sent as the control word of an XBUS operation. These commands are generated by the adapter and are used to either pass processor executed commands to the I/O module for additional action or to command I/O module action in response to an active event. These commands can be either broadcast or addressed to an individual module and can be either two word (command word and data word) or one word (command word only, data word is ignored) commands. All of these adapter generated commands are listed in Appendix D (Table A-2 and A-3 from design guide for I/O modules).

#### 2. I/O Channel Control Memory

Each I/O channel has associated with it a 16-bit by 16-word control memory. This memory is located on the VPM for standard I/O modules, but is located on the I/O module for Smart I/O modules. The format and definition of each word in a control memory is dependant upon the module, however, most modules contain the same basic words. The control memory contains parameters that are used in the operation of the associated I/O module, such as pointers to programs, word counts, and status words. As

an example, the Control Memory for the DSM is listed in Figure 17 with a brief explanation of each word's function.

| Location | Control Word                      | Description                                                |

|----------|-----------------------------------|------------------------------------------------------------|

| 0        | Spare                             |                                                            |

| 1        | Spare                             |                                                            |

| 2        | Spare                             |                                                            |

| 3        | Bit Jump Word (BJW)               | Used with bit jump Chain Instruction                       |

| 4        | Spare                             |                                                            |

| 5        | Buffer Address Pointer (BAP)      | Address of the next memory location in the data buffer     |

| 6        | Chain Address Pointer (CAP)       | Address of the next Chain Instruction to be executed       |

| 7        | Address Table Pointer (ATP)       | Used to calculate BAP as part of data transfer command     |

| 8        | Command Word 1 / Status Word 1    | Contains word used in 1553 protocol (depending on mode)    |

| 9        | Command Word 2 / Status Word 2    | Contains word used in 1553 protocol (depending on mode)    |

| A        | Message Control Word 1 (MCW1)     | Personality dependant mode and control information         |

| В        | Message Control Word 2 (MCW2)     | Control information common to all personalities            |

| С        | Discrete Control Word (DCW)       | Control info which selects mode of operation for discretes |

| D        | Discrete Input/Output Word (DIOW) | Used for masking of discretes                              |

| Е        | Interrupt Clear Word (ICW)        | Used in association with the Discrete Interrupt            |

| F        | Chain Table Pointer (CTP)         | Used to support Tabular Output Operations                  |

Figure 17. DSM Control Memory

## 3. I/O Channel Chain Programs

All I/O channel operation is initiated through the execution of the IOCR instruction by the processor. This instruction causes the processor to process the instruction in the command cell (memory locations 0060-61 or 0062-63). The instruction in the command cell will be an instruction that initiates activity on one of the I/O channels. There are two forms of I/O channel activity; I/O information transfer and I/O program execution or Chaining.

A chain program is a set of instruction, located in main memory, which perform an operation on an I/O channel. The program is made up only of chain instructions that are listed in Appendix C. The program normally transfers parameters between main memory and the I/O channel Control Memory, and initiates transfer of blocks or buffers of data or control words on the channel interface lines. Multiple I/O channels can have I/O chains active concurrently, with the event system providing regulation.

An important concept to emphasize is the difference in how chain programs are executed in standard and smart I/O modules. Standard I/O modules do not have the capability to execute software instructions (the first 2 types of commands previously discussed). Their chain programs are executed through the VPM processor executing the software commands in the chain program and sending corresponding commands (the third type of command previously discussed) over the XBUS to command the I/O module. The VPM time shares the execution of chain commands between the operational program and among the I/O modules with active chaining.

Smart I/O modules are capable of executing directly all of the software instructions that can be used in chain programs (i.e. all commands from Appendix C.) This means that once an I/O operation is initiated via an IOCR command, the VPM will continue processing the operational program and the smart I/O module will execute the chain program. It is able to do this by accessing the chain instruction directly from memory using the XBUS.

## 4. I/O Channel Software Interrupts

Class III software level interrupts are associated with I/O module operation. These interrupts can be enabled or locked out on an individual channel or as a group. They are handled via an interrupt handling routine that the processor is vectored to upon interrupt recognition. These interrupts are listed in Table 2.

| Class | Priority | Interrupt | Definition             |  |  |  |  |

|-------|----------|-----------|------------------------|--|--|--|--|

| III   | 1        | ERI       | Error Interrupt        |  |  |  |  |

| III   | 2        | EII       | External Interrupt     |  |  |  |  |

| III   | 3        | OCI       | Output Chain Interrupt |  |  |  |  |

| III   | 4        | ICI       | Input Chain Interrupt  |  |  |  |  |

Table 2. I/O Channel Interrupts

ERI interrupts are generated upon detection of an error condition. EII interrupts are generated when the I/O module receives a channel interrupt word. The interrupt word is stored in a table in main memory prior to generation of the interrupt. The address in the table is 80 plus the channel number (80-8F). OCI and ICI interrupts are generated when

the chain program on the associated channel encounters and executes the Interrupt Processor (IPR) instruction.

#### **5. I/O Channel Events**

There are four classes of events that can be set by I/O modules to signal active events to the VPM. These events are used to communicate the progress of data transfer operations and chain programs, and to signal software interrupts. All of the I/O events are listed by class and discrete in Figure 18 and a description of each is given in Table 3.

The event system provides a means for the processor to efficiently manage the numerous operations occurring on the I/O channels. It allows the processor to start an operation on an I/O channel and then to continue executing the executive code while the I/O channel performs its tasks. The events allow the I/O cannels to notify the processor when it has completed a task and either needs more information or is ready for another task. It is a means of providing parallel operation of all the I/O channels.

For example, when an I/O chain program is in progress on a channel, that channel will raise the Input or Output Chain Request Event. While this event is active, the processor will continue to execute instructions in the corresponding chain program. When the VPM executes an instruction that indicates a chain program is complete, the firmware will notify the I/O module via an XBUS command. The I/O module will then deactivate the chain event.

#### I / O Class Events

|                |                             | Event Bus Discrete            |                                    |                              |                                    |      |      |      |      |  |  |  |  |  |  |  |

|----------------|-----------------------------|-------------------------------|------------------------------------|------------------------------|------------------------------------|------|------|------|------|--|--|--|--|--|--|--|

| Event<br>Class | Name                        |                               | Even C                             | hannel                       | Odd Channel                        |      |      |      |      |  |  |  |  |  |  |  |

|                |                             | Name                          | Name                               | Name                         | Name                               | Name | Name | Name | Name |  |  |  |  |  |  |  |

| 1 (001)        | Indexed<br>Data<br>Transfer | Remote<br>Terminal<br>Command | Output<br>Data<br>Request 1        | Input<br>Data<br>Request 1   |                                    | RTC  | ODR1 | IDR1 |      |  |  |  |  |  |  |  |

| 2 (010)        | Data<br>Transfer            | Unique<br>Channel<br>Request  | External<br>Interrupt<br>Request 2 | Output<br>Data<br>Request 2  | Input<br>Data<br>Request 2         | UCR  | EIR2 | ODR2 | IDR2 |  |  |  |  |  |  |  |

| 4 (100)        | I/O<br>Chain                | Map                           | = 1                                |                              | External<br>Interrupt<br>Request 4 | MAP  | OCR  | ICR  | EIR4 |  |  |  |  |  |  |  |

| 7<br>(111)     | Class III<br>Interrupts     | I Channel                     |                                    | Output<br>Chain<br>Interrupt | Input<br>Chain<br>Interrupt        | ERI  | EII  | OCI  | ICI  |  |  |  |  |  |  |  |

Figure 18. Input / Output Channel Events

In Figure 18 it should be noted that the Even and Odd channels have the same events, however, the Acronyms for the events are listed for the Odd channel to provide a reference. Also, the repeated discrete events (i.e. ODR1, ODR2) provide for a hierarchy of event priorities.

## 6. I/O Channel Basic Operation

The operation of either standard or Smart I/O modules involve communication on the Event bus, XBUS, and possibly the MBUS. Multiple I/O channels can be operating chain programs or data transfers at the same time with the event system and priority logic providing deconfliction and minimizing the amount of time that the processor spends waiting for a response from the I/O module.

# **I/O Module Event Descriptions**

|                   |       | Class 1. Indianal Data Transfer                                                                                                                                          |  |  |  |  |  |  |  |  |

|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                   |       | Class 1: Indexed Data Transfer                                                                                                                                           |  |  |  |  |  |  |  |  |

| Remote            | D.T.G | Causes the Processor to request an Index Status Word from the I/O Module via the                                                                                         |  |  |  |  |  |  |  |  |

| Terminal          | RTC   | XBUS. The status word is used with the Address Table Pointer (CM-7) to generate                                                                                          |  |  |  |  |  |  |  |  |

| Command           |       | a new output Buffer Address Pointer (CM-5)                                                                                                                               |  |  |  |  |  |  |  |  |

| Output Data       | ODD1  | Causes the Processor to send a data word to the I/O module as determined by the                                                                                          |  |  |  |  |  |  |  |  |

| Request 1         | ODR1  | BAP. This is the highest priority ODR and is used to give priority to time-critical I/ O modules.                                                                        |  |  |  |  |  |  |  |  |

| _                 |       | Causes the Processor to request a data word from the I/O module and place it in                                                                                          |  |  |  |  |  |  |  |  |

| Input Data        | IDR1  | main memory at the location pointed to by the BAP. This is the highest priority                                                                                          |  |  |  |  |  |  |  |  |

| Request 1         | IDKI  | IDR and is used to give priority to time-critical I/O modules.                                                                                                           |  |  |  |  |  |  |  |  |

|                   |       | Class 2: Data Transfer                                                                                                                                                   |  |  |  |  |  |  |  |  |

| I Indiana         |       |                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Unique<br>Channel | UCR   | Causes the Processor to request a unique function word from the I/O module.  Depending upon the function code returned, the processor will perform a given               |  |  |  |  |  |  |  |  |