AFRL-IF-RS-TR-2003-2 Final Technical Report January 2003

# PROGRAMMING HIGH PERFORMANCE RECONFIGURABLE COMPUTERS (HPRC)

**CACI Technologies, Incorporated**

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

AIR FORCE RESEARCH LABORATORY INFORMATION DIRECTORATE ROME RESEARCH SITE ROME, NEW YORK This report has been reviewed by the Air Force Research Laboratory, Information Directorate, Public Affairs Office (IFOIPA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

AFRL-IF-RS-TR-2003-2 has been reviewed and is approved for publication.

APPROVED:

STEVEN L. DRAGER Project Engineer

FOR THE DIRECTOR:

MICHAEL L. TALBERT, Maj., USAF

Technical Advisor, Information Technology Division

Information Directorate

### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 074-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing this collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302,

| suggestions for reducing this burden to Washington Hea<br>and to the Office of Management and Budget, Paperwoi | adquarters Services, Directorate for Informa | ation Operations and Reports, 1215 | Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|----------------------------------------------------------------|--|

| 1. AGENCY USE ONLY (Leave blank)                                                                               | ,                                            |                                    | D DATES COVERED                                                |  |

|                                                                                                                | JANUARY 2003                                 |                                    | Final Apr 01 – Jul 02                                          |  |

| 4. TITLE AND SUBTITLE                                                                                          |                                              |                                    | 5. FUNDING NUMBERS                                             |  |

| PROGRAMMING HIGH PERFOR                                                                                        | RMANCE RECONFIGURA                           | BLE                                | C - F30602-00-D-0221/0005                                      |  |

| COMPUTERS (HPRC)                                                                                               |                                              |                                    | PE - 62702F                                                    |  |

|                                                                                                                |                                              |                                    | PR - 459T                                                      |  |

|                                                                                                                |                                              |                                    | TA - QF                                                        |  |

| 6. AUTHOR(S)                                                                                                   |                                              |                                    | WU - 06                                                        |  |

| Gregory D. Peterson                                                                                            |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| - P-P-0P-WW0 0P04-W-4-T-0W-W-4-W-4-W-4-W-4-W-4-W-4-W-4-W-4-W-4-                                                | E(0) AND ADDDESO(E0)                         |                                    | A DEDECRIMA ADDAMIZATION                                       |  |

| 7. PERFORMING ORGANIZATION NAM                                                                                 |                                              |                                    | 8. PERFORMING ORGANIZATION REPORT NUMBER                       |  |

| Prime:                                                                                                         | SUB:                                         |                                    | REPORT NOMBER                                                  |  |

| CACI Technologies, Incorporated                                                                                |                                              |                                    |                                                                |  |

| 14151 Park Meadow Drive                                                                                        | Electrical and Comp                          |                                    |                                                                |  |

| Chantilly Virginia 20151                                                                                       | Knoxville Tennesse                           | e 37996                            |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| 9. SPONSORING / MONITORING AGEN                                                                                |                                              | ES)                                | 10. SPONSORING / MONITORING                                    |  |

| Air Force Research Laboratory/IF                                                                               | TC                                           |                                    | AGENCY REPORT NUMBER                                           |  |

| 26 Electronic Parkway                                                                                          |                                              |                                    | AEDL 15 DO TD 0000 0                                           |  |

| Rome New York 13441-4514                                                                                       |                                              |                                    | AFRL-IF-RS-TR-2003-2                                           |  |

|                                                                                                                |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| 11. SUPPLEMENTARY NOTES                                                                                        |                                              |                                    |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| AFRL Project Engineer: Steven L                                                                                | Drager/IFTC/(315) 330-2                      | 2735/ Steven.Drager@               | @rl.af.mil                                                     |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| 12a. DISTRIBUTION / AVAILABILITY ST                                                                            |                                              |                                    | 12b. DISTRIBUTION CODE                                         |  |

| APPROVED FOR PUBLIC RELE                                                                                       | ASE; DISTRIBUTION UNI                        | LIMITED.                           |                                                                |  |

|                                                                                                                |                                              |                                    |                                                                |  |

| 13. ABSTRACT (Maximum 200 Words)                                                                               |                                              |                                    | I                                                              |  |

|                                                                                                                | nce Computing with Recor                     | ofigurable Computing               | offers great potential for increased                           |  |

|                                                                                                                |                                              |                                    | manas Computing architectures and                              |  |

The integration of High Performance Computing with Reconfigurable Computing offers great potential for increased performance and flexibility for a wide range of computing problems. High Performance Computing architectures and Reconfigurable Computing systems have independently demonstrated performance advantages for applications such as digital signal processing and pattern recognition. By exploiting the near hardware specific speed of Reconfigurable Computing systems incorporated into a computer cluster, there is potential for significant performance advantages over software-only or uniprocessor solutions. However, application development barriers exist that will slow the widespread adoption of this technology. This report presents the results of research seeking to overcome one of these barriers, the development of a programming framework for High Performance Reconfigurable Computing systems.

| 14. SUBJECT TERMS High Performance Computing | 15. NUMBER OF PAGES<br>76                   |                                         |                            |

|----------------------------------------------|---------------------------------------------|-----------------------------------------|----------------------------|

|                                              | 16. PRICE CODE                              |                                         |                            |

| 17. SECURITY CLASSIFICATION OF REPORT        | 18. SECURITY CLASSIFICATION<br>OF THIS PAGE | 19. SECURITY CLASSIFICATION OF ABSTRACT | 20. LIMITATION OF ABSTRACT |

| UNCLASSIFIED                                 | UNCLASSIFIED                                | UNCLASSIFIED                            | UL                         |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. Z39-18 298-102

### **Table of Contents**

| Introduction                                                   | 1  |

|----------------------------------------------------------------|----|

| Reconfigurable Computing                                       | 2  |

| High Performance Reconfigurable Computing                      | 3  |

| Related Work                                                   | 5  |

| Programming Environments                                       | 6  |

| Models of computation in Ptolemy II                            | 7  |

| Parallel Programming                                           | 8  |

| Reconfigurable Computing Development                           | 9  |

| Mathematical Foundations                                       | 13 |

| Overview                                                       | 15 |

| Reconfigurable Computing Node Analysis                         | 17 |

| High Performance Reconfigurable Computing Multi-Node Analysis  | 19 |

| High Performance Reconfigurable Computing Development Hardware | 22 |

| Reconfigurable Computing Model                                 | 22 |

| High Performance Reconfigurable Computing Model                | 25 |

| Model Applications                                             |    |

| HPRC Application Examples                                      | 29 |

| Image Segmentation                                             | 31 |

| Conclusions and Future Work                                    | 32 |

| Acknowledgements                                               | 33 |

| References                                                     | 34 |

| Appendix A: Firebird Host Source Code                          | 38 |

| Appendix B: MATLAB Makefile Code                               | 61 |

| How To Call Matlab Functions from C Programs:                  |    |

## **Table of Figures**

| Figure 1. High Performance Reconfigurable Computer (HPRC) Architecture      | 2          |

|-----------------------------------------------------------------------------|------------|

| Figure 2. Synchronous Iterative Algorithm                                   | 17         |

| Figure 3. Flow of Synchronous Iterative Algorithm for Multi Node Analysis   | 20         |

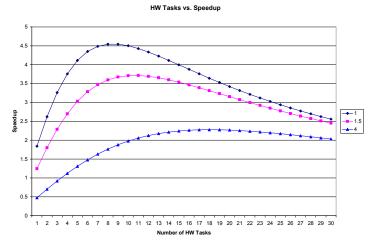

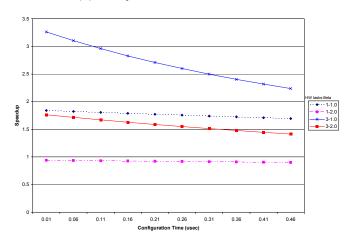

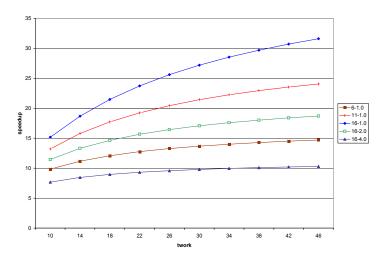

| Figure 4. Speedup Curves: a) Vary number of RC units, b) Vary configuration | time, and  |

| c) Vary total work                                                          | 24         |

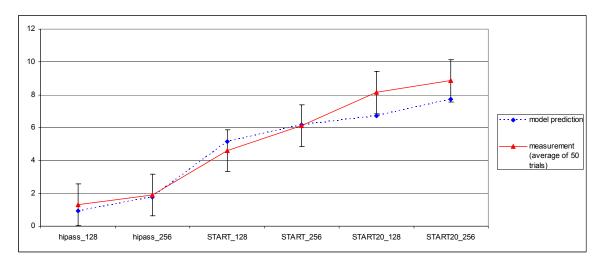

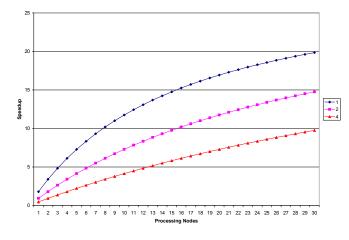

| Figure 5. Comparison of RC Model Prediction with Measurement Results        | 25         |

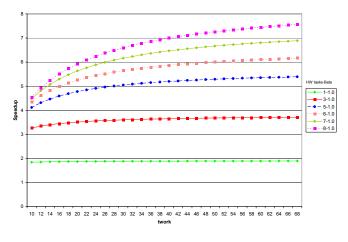

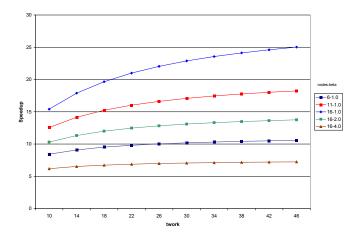

| Figure 6. Speedup Curves: a) Vary work for one FPGA per RC unit and b) Vary | y work for |

| two FPGAs per RC unit and c) Increasing number of nodes (one RC unit        | per node)  |

| work fixed                                                                  | 26         |

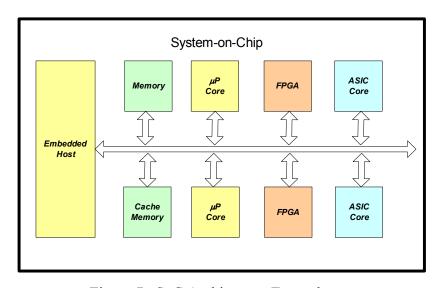

| Figure 7. SoC Architecture Example                                          | 28         |

|                                                                             |            |

| Table of Tables                                                             |            |

| Table 1. Symbols and Definitions                                            |            |

| Table 2. Model Parameters for Wildforce from Benchmark Application          | 23         |

| Table 3. Runtime Predictions and Measurements (time in seconds)             | 25         |

#### Introduction

A number of important defense and industrial applications present computational demands greatly exceeding the capabilities of consumer (desktop or mainframe) computers. For decades, these specialized demands have driven the development and evolution of a supercomputing industry. Moore's Law predicts the doubling of semiconductor performance every eighteen months. Because it has held true for nearly four decades (and most experts expect it to hold for at least the next 10-15 years), the capabilities of high performance computing enjoy the revolutionary impact of continued exponential growth. At the same time that processors have followed Moore's Law, the computational power of configurable logic has grown even faster. In less than two decades. FPGAs (Field Programmable Gate Arrays) have grown from small prototyping or "glue logic" applications to the point of now holding nearly ten million gates of logic. The impressive capacity and much-improved speed of FPGAs have made them useful in many applications, including some with significant computational demand. Although the combination of supercomputing platforms with configurable logic seems like an attractive approach for achieving tremendous performance, many challenges exist as The most appropriate architectures, computational models, runtime systems, applications, and development environments must be considered. This technical report discusses research aimed at developing an initial programming infrastructure for this emerging supercomputing technology.

High Performance Computing (HPC) is the use of multiple processors or processing nodes collectively on a common problem. Reconfigurable Computing (RC) is the combination of reconfigurable logic with a general-purpose microprocessor. The architectural intent is to achieve higher performance than typically available from software-only solutions with more flexibility than achievable with hardware ASICs. In RC architectures, the microprocessor performs those operations that cannot be done efficiently in the reconfigurable logic such as loops, branches, and possible memory accesses, while computational cores are mapped to the reconfigurable hardware [34].

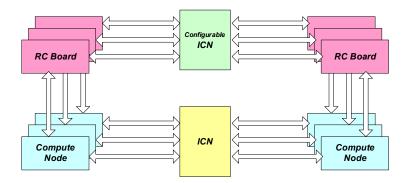

High Performance Reconfigurable Computing (HPRC) is the architectural combination of High Performance Computing and Reconfigurable Computing. The proposed HPRC platform as shown in Figure 1 consists of a number of distributed computing nodes connected by some interconnection network (the network can be a switch, hypercube, systolic array, etc. using Ethernet, Myrinet, or some other networking technology), with some or all of the computing nodes having RC element(s) associated with them. The HPRC platform will potentially allow users to exploit the performance speedups commonly achieved in parallel systems in addition to the speedup offered by reconfigurable hardware coprocessors. Many applications such as image or signal processing algorithms and various simulation algorithms stand to benefit from the potential performance of this architecture.

Figure 1. High Performance Reconfigurable Computer (HPRC) Architecture

The addition of a configurable network connecting the RC elements offers even more performance advantages for many applications such as discrete event simulation and many numeric computations. The additional network would provide a less inhibited route for synchronization, data exchange, and other communications between processing nodes. Research by Chamberlain [4,5,6], Reynolds et. al. [38,39,40], and Underwood et. al. [44] all confirm the performance benefits of a specialized configurable network for applications with barrier synchronization events or applications requiring the exchange of large amounts of data.

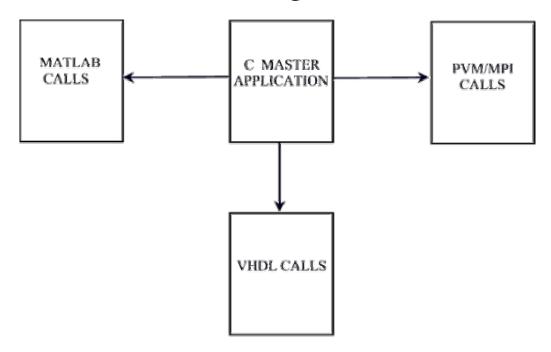

As individual platforms for computing, HPC and RC are challenging enough to program and utilize effectively. Combining these powerful domains will require the development of new analysis and design tools. In this report, we discuss efforts to develop a performance modeling infrastructure for HPRC, model communications between the various reconfigurable computing and processing elements, evaluate the most appropriate computation models for HPRC, and consider the programming effectiveness of different languages, tools, and libraries for HPRC.

A performance modeling framework with models describing this new architecture will help not only in understanding and exploiting the design space but will be a building block for many of these tools. The performance of the HPRC system is affected by architectural variables such as number of nodes, number of FPGAs, FPGA size, heterogeneity, and network performance, just to name a few, and the available permutations make the design space extremely large. Without a modeling framework to assist with the analysis of these issues, tradeoffs cannot be effectively analyzed, potentially resulting in grossly inefficient use of the resources.

### Reconfigurable Computing

Reconfigurable computing (RC) is the coupling of reconfigurable hardware such as FPGAs to general-purpose processors. Some examples of the potential coupling of the reconfigurable hardware are a PCI bus card with FPGA or PLD (Programmable Logic Device) devices, a reconfigurable co-processor mapped in the processors memory space, or an area of reconfigurable logic integrated on the same die with the processor. Research has shown that many of today's computationally intensive applications can

benefit from the speed offered by application specific hardware co-processors. For applications with multiple specialized needs, it is not feasible to have a different co-processor for every specialized function. Such diverse applications stand to benefit the most from the flexibility of RC architectures since one RC unit can provide the functionality of several ASIC co-processors in a single device. Several research groups have demonstrated successful RC architectures [12,13,15,16,18,25,27,28,44,46,48].

There are many RC systems available from companies such as Annapolis Microsystems [2], Nallatech [29], Virtual Computer Corporation [45], and research organizations such as University of Southern California's Information Sciences Institute (ISI) [18], The Chinese University of Hong Kong [25], and Carnegie Mellon University [13,28]. The Wildforce and Firebird units from Annapolis Microsystems [2] and the SLAAC units from ISI [18] are all PCI-bus cards with onboard memory. The Pilchard architecture developed by The Chinese University of Hong Kong [25] interfaces through the memory bus for closer coupling with the processor. The PipeRench reconfigurable fabric [13,28] is an interconnected network of configurable logic and storage elements that uses pipeline reconfiguration to reduce overhead which is one of the primary sources of inefficiency in other RC systems.

### **High Performance Reconfigurable Computing**

The proposed HPRC platform consists of a system of RC nodes connected by some interconnection network (switch, hypercube, array, etc.). Each of the RC nodes may have one or more reconfigurable units associated with it. This architecture provides the user with the potential for more computational performance than traditional parallel computers or reconfigurable coprocessor systems alone.

The HPRC architecture offers many architecture options. Starting with the traditional HPC aspects of the HPRC architecture, there are many network and processor considerations. These options alone make performance analysis complicated and interesting. Adding in the options available for RC such as the coupling of reconfigurable hardware to the processor, number of reconfigurable units, size of FPGA(s), dedicated interconnection network, and others, the analysis problem becomes enormous. Understanding these issues and how they affect the overall system performance is vital in exploiting this potentially powerful architecture. An analytical modeling framework addressing these issues will be a key tool towards understanding through analysis.

HPRC could prove a very useful platform for applications involving heavy number crunching and rigorous computations. Examples of these would be signal and image processing algorithms. It can also be used to perform time-consuming simulations – it is natural to expect them to improve simulation times considerably given that they use two speed-up techniques simultaneously. A number of algorithms to solve graph problems also seem promising for HPRC applications.

Parallel supercomputers have moved from vector supercomputing technologies to microprocessor-based massively parallel computers. With the promulgation of both powerful computers and fast communications technologies, a huge amount of potential computational capabilities exists. Grid-based computing technologies seek to exploit these resources, particularly the cycles that would otherwise be lost for idle computers. Communications libraries, distributed job schedulers, and related software developments combined with the availability of powerful, inexpensive computational and communications infrastructure has lead to the popularity of Beowolf clusters. Using a number of clustered commodity PCs, an organization can create a powerful parallel computing infrastructure. The primary difference between Beowolf clusters and high performance computers is the optimized interconnection networks used by HPC platforms.

Although FPGA boards are not as inexpensive (yet), one can assemble a powerful HPRC platform for a modest hardware investment. In this report, we discuss several applications that illustrate the potential for HPRC applications to speed up computations. For a number of important defense applications, such as in signal and image processing, there is significant potential for HPRC to help accelerate these critical applications.

One possible criticism of the HPRC approach for defense applications, especially for signal and image processing, is that a Beowolf cluster or HPC platform augmented with reconfigurable computing elements may have limited potential for packaging in embedded systems. Hence, aerospace or man-portable use of this technology may not be practical.

As Moore's Law continues its inexorable pace, the number of transistors available for use on integrated circuits continues to grow exponentially. By the end of the decade, chips with over a billion gates will be available. With this tremendous growth, the question of how these transistors can be exploited is a concern. Even now, design engineer productivity is severely lagging behind current demands. To address this, large circuits will include a collection of processors, cores for specific functions, and reconfigurable logic. In short, HPRC platforms will be available on a chip. Hence, this effort not only addresses programming HPRC platforms one would expect to find in a machine room or equipment rack, it also addresses critical needs in application development for next-generation embedded systems.

This trend towards the convergence of parallel processing and reconfigurable computing is already evident. Reconfigurable logic device manufacturers such as Xilinx, Altera, Atmel, Cypress, and others are already bringing together their reconfigurable logic devices with embedded microprocessors and microcontrollers. In the case of the Xilinx Virtex II Pro family, multiple PowerPC cores are integrated on the same die as tens of millions of gates of FPGA circuitry. In addition, a number of high-speed communications links are provided to get data into and out of the parts. HPRC on a chip is not only technically feasible it is currently commercially available. The problem of effectively programming these platforms remains.

### **Related Work**

A significant amount of related work has been performed under the auspices of the DARPA Adaptive Computing Systems (ACS) program. The most relevant work under the ACS program addresses the application development task. The Synopsys Nimble Compiler effort targets the synthesis of C onto reconfigurable logic, but is not oriented for high performance computing tasks. The USC/ISI DEFACTO effort exploits the SUIF project to address compilation of more abstract representations onto reconfigurable hardware, and includes some nice capabilities to map to customized ALU/CPU structures for a given program. Once again, this is a very low-level view of the partitioning and mapping problem. The compilation technology from these programs can be applied to compiling function blocks to reconfigurable computing elements once partitioning is completed and the blocks are mapped to RC elements.

Efforts from Northwestern University and UT exploit visual programming languages like Khoros or MATLAB to ease the reconfigurable hardware programming task. These approaches provide an excellent programming model for applications developers. These projects do not currently support the migration of functionality between CPUs and RC elements in either a static or dynamic manner. This effort addresses static mapping between CPUs and RC elements in a HPRC architecture, while considering the evaluation capabilities required for a dynamic mapping capability.

There are several Java-related ACS programs for applications targeting FPGAs. Brigham Young University researchers have developed the JHDL Java-based hardware description language environment for programming FPGAs. The approach enjoys the benefits of code portability inherent with Java, while still achieving good hardware performance on the FPGA devices. With respect to hardware/software systems, the approach suffers from the reduced performance typically encountered with Java interpreters or compilers, which limits its applicability to high performance computing environments. A related effort from Lava Logic (a division of TSI Telesys) targets the use of Java for programming reconfigurable devices by developing hardware implementations for Java bytecodes, but it suffers from the same high performance computing software drawbacks as the JHDL effort. The Xilinx JBITS effort targets the use of the fine-grain reconfigurability of the Virtex family of FPGA devices. This ability to perform finegrain reconfigurability during operation promises a performance boost, but focuses on low-level design issues. Hence, we can easily leverage such advances, but the work discussed here addresses a different programming problem.

The System Level Applications of Adaptive Computing (SLAAC) program provides the primary demonstration vehicle for the DARPA ACS program. The SLAAC RC architecture has been developed and used for a number of technology demonstrations. In addition SLAAC completed compilation work to map C to VHDL on Annapolis Microsystems RC boards. The Virginia Tech ACS work uses the BYU JHDL design environment, but it does not have automatic partitioning onto multiple FPGAs. The manual intervention required for this task is significant; supporting multiple RC boards further complicates the design task. The SLAAC API is being developed at Virginia

Tech to make porting application host code between reconfigurable computing boards easier.

In an attempt to better support portability of vector, signal, and image processing applications, the embedded systems community created the VSIPL API for commonly used functions. Vendors for various HPC platforms support the VSIPL API by providing a library of functions optimized for their particular machines. Because a variety of vendors support VSIPL, applications developers can develop their applications using familiar programming languages/tools like C/C++, MATLAB, or Khoros, and can more easily port their applications to other platforms. Unfortunately, the VSIPL library does not currently support parallel processing, although preliminary work has begun on developing a parallel VSIPL extension. A reasonable strategy for making effective use of HPRC platforms would exploit the parallel VSIPL infrastructure for HPC platforms to provide hardware/software codesign support for automatic partitioning and mapping of tasks between multiple processors and multiple FPGAs. The proposed research takes important steps in this direction and helps validate the appropriateness of the approach.

### **Programming Environments**

It would be ideal to have a tool that would let users design their application and map it onto the HPRC system without having to know the details of parallel processing or reconfigurable computing. Such a tool would essentially achieve the following:

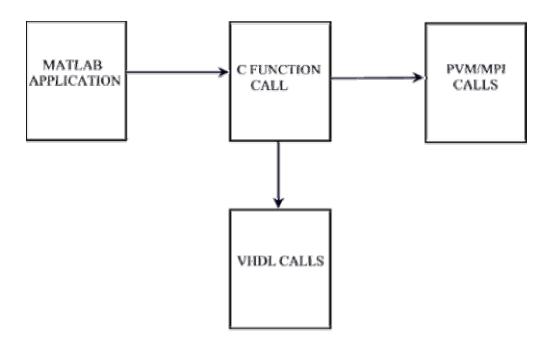

In this research, we are investigating the efficacy of using the Ptolemy II framework [21,22,37], MATLAB, Khoros, or other popular tools to program HPRC platforms. We know that the modeling framework for the HPRC architecture is also suitable to the design of Systems on a Chip (SoC), because the design and architecture of HPRC and SoCs will be homomorphic. Both the architectures contain Reconfigurable Units (RC units) and also share some of the same design methodologies in Hardware/Software Codesign [23].

Previous work at UT focused on the use of Khoros, a graphical design environment primarily used for image processing applications. The CHAMPION program used Khoros to capture algorithms, and then provided a set of VHDL libraries to map the application to a reconfigurable computing board with one or more FPGAs. A partitioning algorithm automatically broke the application into pieces that were then mapped to the collection of available FPGAs. Using this approach, speedups of up to 2000x were achieved in mapping applications to FPGAs.

MATLAB is another tool for capturing algorithms and is widely used. We discuss the interfaces provided with MATLAB for using parallel processing and how we can develop the interface between a processor running a MATLAB program and the FPGAs we would like to use to accelerate portions of the MATLAB problem. First, we discuss

some issues related to computational models and how we are investigating the models of computation one may wish to consider for HPRC applications.

### Models of computation in Ptolemy II

Ptolemy is a software framework developed at the University of California, Berkeley and is used for modeling, simulation and design of concurrent, real-time embedded systems. The advantage of this tool is that it allows heterogeneous mixing of different "models of computation". A model of computation varies from another mainly in its notion of "time". Ptolemy II is a JAVA-based component-assembly framework and its GUI allows the user to create designs that involve one or more interacting components (which could be of different models of computation) [24].

"Models of computation" are architectural patterns, which focus on relationships between concurrent or sequential components. Ptolemy II includes a suite of *domains*, each of which realizes a model of computation. It also includes a component library, in which most components are *domain polymorphic*, in that they can operate in several of the domains. Most are also *data polymorphic*, in that they operate on several data types. The domains that have been implemented are listed below.

CT: continuous-time modeling,

DE: discrete-event modeling,

FSM: finite state machines,

PN: process networks,

SDF: synchronous dataflow

CSP: communicating sequential processes, (only in the full release)

DDE: distributed discrete events (experimental),

DT: discrete time, (experimental),

Giotto: periodic time-driven (experimental) and

GR: 3-D graphics (experimental).

SR: Synchronous Reactive (experimental).

TM: Timed Multitasking (experimental).

The first aim of the research into computational models is to demonstrate the feasibility of using HPRC for the applications/computational models chosen. For each computational model, the process of dividing tasks between the processors and the reconfigurable units is done by hand. In so doing, a better understanding of the types of applications and the implementation approaches that are most appropriate for HPRC architecture. This insight is critical to the ultimate goal is to find a way to efficiently automate the process while achieving high performance. The applications we consider for HPRC include different computational models, so these demonstration applications help in understanding which computational models are most appropriate for HPRC

platforms. Although a sampling of results has been obtained using Ptolemy II and other tools for HPRC applications, this work is still preliminary and in progress. Some comments are included in the application discussion below concerning their computational model and the effectiveness in mapping the application/computational model to HPRC.

### **Parallel Programming**

The Grid is the name given for the vast collection of interconnected computers distributed throughout the world, combined with the software tools and infrastructure required to develop and execute applications on these computational resources. A wide variety of tools provide support for job scheduling, including such tools as Condor, Utopia, and LSF. Other tools such as the Internet Backplane Protocol for Logistical Computing help in caching data for distributed grid applications. Distributed operating system work, including the Globus project, seek to exploit grid resources as well by allowing tasks to be spawned off to other machines and migrated as necessary.

The programming infrastructure to support communicating processes executing on the grid is a quite difficult problem. Early efforts to provide these capabilities include PVM and MPI, which are libraries of communications and control functions to coordinate processes on the grid. PVM is quite popular and widely distributed, with support for a wide variety of architectures. It supports a dynamic process model; hence tasks can be created or destroyed at runtime. In contrast, MPI supports a CSP-like computational model in which tasks continue for the entire life of the distributed program. MPI built upon much of the experience in using PVM and is widely used for HPC platforms because most HPC platforms provide a high performance, native MPI implementation. Hence, for heterogeneous systems or for problems with dynamic process behavior, PVM is preferred. Otherwise, MPI is the most common communications library used for parallel processing. Efforts to extend MPI to support dynamic process creation and destruction have not been successful, although an early implementation of PVMPI was completed. PVM or MPI are used in our work for parallel applications.

The NetSolve project is being developed at the University of Tennessee's Innovative Computing Laboratory. NetSolve is a client-server system that enables users to solve complex scientific problems remotely. The system allows users to access both hardware and software computational resources distributed across a network. NetSolve searches for computational resources on a network, chooses the best one available, and using retry for fault-tolerance solves a problem, and returns the answers to the user. A load-balancing policy is used by the NetSolve system to ensure good performance by enabling the system to use the computational resources available as efficiently as possible

The problem description file (PDF) is the mechanism through which Netsolve enables services for the user. The pdf has been written which explains the problem .The pdf also explains the inputs and output files , the size of the matrix and the C code to which it links. Servers are introduced to the Netsolve agent and indicate the collection of programs that they support. Clients wishing to use Netsolve ask the agent to supply a list

of the best machines available for their particular problem. The client will then interact with the chosen server to perform the problem.

Netsolve is a good fit for HPRC applications at this point because the FPGA bitstreams for the RC elements are not portable to other RC boards of FPGA families. The most practical way to support HPRC applications with the grid is to use Netsolve. Research in to the performance of Netsolve, its effectiveness for HPRC, and how to extend Netsolve to provide any necessary extensions is discussed later in the report.

### **Reconfigurable Computing Development**

Reconfigurable computing comes from a broader application of programmable logic device technology. Programmable logic devices provide designers with the ability to modify circuit functionality after its fabrication. Examples of programmable logic devices include programmable arrays of logic (PALs), complex programmable logic devices (CPLDs), field programmable system level integrated circuits (FPSLICs), and field programmable gate arrays (FPGAs), with FPGAs the most commonly used devices for reconfigurable computing.

Currently, reconfigurable computing systems are typically comprised of processing nodes associated with co-processing boards with FPGAs. This co-processing model uses software executing on the processor for general computation and control, with the reconfigurable hardware accelerating computational intensive operations. Following some promising research results, the emerging system on a chip market will likely provide SoCs with configurable logic.

Computing systems, particularly those employed in embedded applications, are increasingly benefiting from the use of programmable logic. Many developers use programmable logic devices (PLDs) to rapidly develop customized circuitry for various applications, and then ship the systems with the configured programmable logic devices. FPGAs used to be widely used for system prototyping or implementing glue logic on boards. The reduced device costs, increased capacities, faster operational speeds, and shrinking product time to market requirements now result in the common deployment of FPGAs in embedded systems as a substitute for ASICs. Such systems typically have a static configuration throughout their lifetime.

In some cases, the configurations of the programmable logic devices can be updated after the system is fielded, resulting in a configurable computing system. This ability to configure a system can reduce maintenance costs and extend product lifetimes via system upgrades in the field accomplished by updated configurations. In contrast, reconfigurable computing systems frequently change the programming of the logic devices during operation. Recent developments in programmable logic device technology (density, speed) have made reconfigurable computing practical.

Reconfigurable computers provide the user with the ability to dynamically change the logical operation of its computational elements. Configurable computers also provide the

ability to change the logical operation of computational elements, but in a more constrained manner.

Reconfigurable computing promises to provide a wide variety of benefits to system designers. A primary reason for the initial use of programmable logic devices is the relative ease in employing them in designs. Configuration requires seconds to perform, as opposed to the weeks required for fabricating an ASIC. If there are errors in the logic implementation, attractive system improvements, or changes to the specification, designers can make changes as necessary before the system is deployed. These benefits are equally applicable for configurable and reconfigurable systems.

The use of configurable or reconfigurable systems provides similar benefits in fixing errors, adding features, or providing other updates to systems throughout their life cycle. By modifying the functionality with a new configuration of the programmable logic, minimal update costs may be required. If one combines this model of providing upgrades or bug fixes with internet-connected configurable systems, radical improvements in the ability to maintain embedded systems become possible. Because reconfigurable computing provides this capability to modify system functionality to fix bugs or add features, cost reductions during design as well as after deployment result in significantly reduced life cycle costs. For products with long lifetimes, this cost reduction can be substantial.

The use of programmable logic results in accelerated development cycles yielding a reduced time to market. By avoiding the extended design and fabrication times required for ASICs, designers can reach the market more quickly. If design flaws or engineering change orders arise near the end of the design process, modifications to programmable logic can usually be implemented quickly with the existing parts. In the case of an ASIC-based design, a new version of the ASIC will typically be required, resulting in additional costs and delays. By avoiding these additional costs and delays, reconfigurable computing systems can reach the market more quickly. Because the timeliness in reaching the market often determines if a product is profitable or not, one cannot overstate the importance of the schedule risk mitigation due to reconfigurable hardware.

The flexibility coming from the ability to reconfigure components of a system based on environmental or operational conditions enables systems to be fielded for a broad range of applications and for dynamic or unknown environments. A single reconfigurable computing system can be applied to image processing, signal processing, cryptographic, and string matching problems through reconfigurations. An ASIC-based hardware approach would require a large investment in hardware resources while a software solution may not achieve the require performance. In this context, the flexibility of reconfigurable computing provides unmatched capabilities.

By optimizing the hardware to address the specific task at hand, reconfigurable computing platforms can often perform operations using much less power than general purpose hardware or software based solutions. Even custom or specialized hardware may not provide the power savings obtainable from customizing the hardware used to the

specific application. For example, in a number of signal and image processing applications, variable word sizes can be implemented with programmable logic to provide sufficient accuracy but no more. Reconfigurable computers can reduce the number of gates used in the design by optimizing word sizes as needed, whereas digital signal processors, microcontrollers, or general purpose processors must be designed with a static word size that can not be changed to reduce power.

Reconfigurable computers can support a very large number of gates through the use of multiple configurations. In effect, a given set of programmable logic devices can replace a much larger collection of ASICs. This will result in a reduction in the physical size required for the electronics comprising embedded systems.

Programmable logic devices provide an ideal capability to detect, identify, and isolate faulty hardware elements in embedded systems. With the ability to support testing configurations and to adapt to detected faults, reconfigurable computers can support a variety of critical applications. By enabling graceful system degradation in the presence of faults, much cheaper and more reliable critical systems can be fielded.

Last, and certainly not least, designers can achieve higher performance by using reconfigurable computing to adapt to the environmental conditions during operation. In one recent cryptography example, engineers achieved higher performance with an FPGA-based reconfigurable computing solution than available with an ASIC developed for the same task after a long and expensive development [33].

With reconfigurable computing systems, key attributes that determine its capabilities include the speed and granularity of reconfiguration. The ability to reconfigure programmable logic quickly makes it practical to change configurations more frequently during operation. The technology used in the programmable logic device dictates the granularity of reconfiguration that can most effectively be supported. The ability to selectively reconfigure parts of the programmable logic is known as fine-grain reconfiguration. Many families of programmable logic devices do not support the random access and modification necessary to support fine-grain reconfiguration. For these parts, most or all of the part must be reconfigured at the same time. Because the time to configure an entire part takes a large number of cycles, the performance penalty associated with such reconfigurations renders it impossible to support frequent function modifications while still attaining high performance. Hence, reconfigurable systems assembled from such parts have a coarse granularity of reconfiguration. In contrast, some newer generations of programmable logic devices support the fine-grain reconfigurability that enables hardware optimization based on the operations and data at hand.

Reconfigurable computers must include runtime systems to support the configuration data for the programmable logic device elements, much like a processor uses a sequence of instructions. For systems with slower, coarse-grain configuration, the programmable logic devices may be updated when each new application is run, or during changes between operational phases. As the frequency of reconfigurations increases and their

granularity decreases, the runtime support required becomes more sophisticated. Memory banks or configuration caches may hold the necessary configuration data, as with instruction and data caches. Although in principal, dynamic optimization of configurations is possible via the runtime system, in practice current limitations in the design tools currently make it impractical. Work with the Xilinx Jbits interface is improving the runtime and design environment to make such systems practical in the future. This research does not directly address runtime reconfiguration or configuration caching, but the performance modeling framework is intended to support these capabilities with little, if any, modification.

Reconfigurable computers bring together aspects of both hardware and software systems. Not surprisingly, debate rages about the best design languages, methodologies, and tools for reconfigurable computing systems. Many of the same issues and arguments concerning systems design and hardware/software codesign are applicable.

Most development efforts to map applications onto reconfigurable computers uses VHDL or Verilog for capturing the design, typically at the register transfer level. In doing so, hardware designers can use the same design capture, simulation, and synthesis languages and tools already used for ASIC development. In practice, the productivity from directly using HDLs lags behind industry needs. Designers write much of the HDL code at RTL, and too often do not employ language constructs such as VHDL generics, configurations, and generate statements to create portable, flexible designs. In addition, the synthesis tools provide roughly equivalent capability for FPGAs as with ASICs, enabling the reuse of much of ASIC design flows and tools.

The same domain specific attributes that make hardware description languages effective for designing electronic systems prove to be a significant limitation to the widespread adoption of VHDL or Verilog for capturing designs intended for reconfigurable computers. Software and systems engineers are not familiar with these hardware description languages and resist using them.

At the system design level, a number of proposed extensions to C or C++ have been forwarded by various companies to address behavioral design. Because C/C++ is widely used by systems engineers to develop system prototypes or executable specifications, it is hoped providing a facility to develop hardware designs in some C/C++ dialect will improve productivity and bring systems and hardware engineers closer together. Adoption of a C/C++ dialect potentially will potentially enable a much larger pool of designers to describe hardware because C/C++ users dwarf the HDL user population. The amount of infrastructure required with these C/C++ extensions may approach or even exceed that of using HDLs.

In an attempt to leverage the surging popularity of the Java programming language, as well as its support for code portability and for reuse via object-oriented facilities, researchers at BYU developed JHDL (see http://www.jhdl.org). The JHDL approach exploits the explosion in software development tools for Java and the much larger population of Java programmers to ease in the general adoption of reconfigurable

computing. JHDL lowers many of the barriers to entry for potential developers, and significantly simplifies the mapping of functionality between hardware and software. Nonetheless, performance limitations for Java hinder its adoption for high-performance applications.

A number of challenges remain for developers using reconfigurable computers. The verification of RC systems faces all the challenges of ASIC verification combined with the additional complexity of multiple configurations. Fine-grain adaptation of configurations provides a higher bar for systems verification.

Design languages, tools, and methodologies for RC systems continue to be a topic of research and development. The same productivity gap between available gates and designed gates currently hindering ASIC designers affects RC designers as well. Tools that support more abstract design while automatically extracting a problem's parallelism and the most appropriate configurations are needed. Addressing this problem is the focus of this research.

For software engineers, the notion of an instruction set architecture greatly reduces the difficulty in developing applications. This abstraction of a processor provides sufficient insight into the hardware to enable its effect use without overwhelming the programmer. Currently, reconfigurable computers lack such a standard "programmable configuration architecture" to serve a role like that of an instruction set architecture. This lack of a programmable configuration architecture could pose significant portability problems for the industry in the future.

Understanding the impact of architectural changes is just beginning; the changes to models of computation are not well understood yet. This remains as an exciting area of basic research with wide-reaching implications. For example, just as the notion of virtual memory has resulted in significant improvements in software, the notion of the virtualization of hardware will provide similar benefits for hardware design.

### **Mathematical Foundations**

Performance analysis and architecture design for HPC and RC systems are challenging enough in their individual environments. For the proposed HPRC architecture, these issues and their interaction are potentially even more complex. Given these observations, it is evident that a mathematical modeling framework is a necessary tool for analyzing various performance metrics. Although substantial performance analysis research exists in the literature with regard to High Performance Computing (HPC) architectures [1,3,7,14,17,26,31,32,34,35,36,43] and even some with respect to Reconfigurable Computing (RC) [8,9,34], the analysis of these architectures working together has received little attention to date and currently there is a gap in the performance analysis research with regard to an HPRC type of architecture.

A modeling framework covering the common metrics found in HPC and RC research will fill this gap enabling performance analysis of the architecture and the analysis design

tradeoffs. The development of a modeling framework for a complex architecture such as HPRC presents several challenges and questions which will need to be addressed: *modeling communication time* (node-to-node, processor-to-RC unit, and RC unit-to-RC unit), *modeling computation time* (software in processor and firmware in RC unit), *modeling setup costs* (application setup, RC unit configuration, and network configuration), and *modeling load imbalance* (application tasks or data imbalance and hardware versus software imbalance).

HPC performance is commonly measured in terms of speedup and efficiency. The basic definition for *speedup* in HPC is the ratio of the execution time of the best possible serial algorithm on a single processor to the parallel execution time of the parallel algorithm on an *m*-processor parallel system:

$$S(m) = \frac{R(1)}{R(m)}$$

where R represents the execution time (1)

Efficiency is defined as the ratio of speedup to the number of processors, m:

$$Eff(m) = \frac{S(m)}{m} = \frac{R(1)}{m \cdot R(m)}$$

(2)

We can also discuss *speedup* and *efficiency* for reconfigurable computing. Rather than processing nodes running software algorithms in parallel on a common problem as in HPC, in RC we have hardware and software algorithms working together on a common problem. In general, we will define *RC speedup* as the ratio of the execution time of the best possible software only algorithm on a single processor to the execution time of the RC algorithm executing in software and hardware:

$$S_{RC} = \frac{R_{software}}{R_{RC}}$$

where R represents the execution time (3)

We should note that depending on the algorithm and implementation, there may be a hardware/software load imbalance. We will discuss this further in a later section but this essentially means that the execution may have a percentage of hardware/software overlap ranging from fully parallel (both are busy 100% of the time) to no overlap where the passing from software to hardware is essentially serial. A higher percentage of overlap will result in the greatest potential for speedup leading to the idea of efficiency. The definition of *RC efficiency* will be slightly different from HPC efficiency. For HPC, we have software tasks divided among a number of processing nodes all working in parallel to produce some amount of speedup. The efficiency is a result of this speedup relative to the overhead induced from the number of nodes working in parallel. For RC, we have *k* software tasks, and one or more hardware tasks, *n*. The efficiency will be the speedup achieved relative to the additional RC system overhead (setup, communication, configuration, etc.). We will assume this overhead is related to the total number of hardware and software tasks even though these tasks are not necessarily performing the same functions, resulting in the following definition for *RC efficiency*:

$$Eff_{RC} = \frac{S_{RC}}{n+k} = \frac{R_{software}}{(n+k) \cdot R_{RC}} \tag{4}$$

Again for HPRC performance metrics, we will consider *speedup* and *efficiency*. Our general definition for *HPRC speedup* is the ratio of the execution time of the best possible serial software only algorithm executing on a single processor to the parallel execution time of the parallel HPRC algorithm executing in software and hardware at some load balance on an *m*-node system (where a node is a workstation with or without RC units):

$$S_{HPRC}(m) = \frac{R(1)}{R_{HPRC}(m)}$$

where R represents the execution time (5)

We will discuss the details of the load balance implications in a later section. Similar to the case for RC efficiency, we define HPRC efficiency where n is the total number of hardware tasks and k is the total number of software tasks across all nodes of the system:

$$Eff_{HPRC}(m) = \frac{S_{HPRC}(m)}{n+k} = \frac{R(1)}{(n+k) \cdot R_{HPRC}(m)}$$

(6)

Other metrics such as power, cost, physical size, etc. are important especially in embedded systems. For these metrics, we can form cost functions from the performance analysis equations and optimize the metric as appropriate.

#### Overview

To effectively use the proposed HPRC architecture, we must be able to analyze design tradeoffs and evaluate the performance of applications as they are mapped onto the architecture. Performance models are commonly used tools for analyzing and exploiting available computational resources in HPC environments. Some commonly used modeling techniques in the analysis of computing systems are analytic models, simulations, and measurements. The best suitable modeling approach depends on the required accuracy, level of complexity, and analysis goal of the model. We can employ one or more of these modeling approaches to better understand the tradeoffs in mapping applications to HPRC resources as well as the most effective ways of doing so.

To develop a representative modeling framework for HPRC we will begin by investigating and characterizing the RC architecture and expanding this model to multiple nodes representative of an HPRC platform. In the RC environment, the focus will be on FPGA configuration, processor to FPGA communication, data distribution between FPGA and processor, memory access time, computation time in hardware and software, and other RC application setup costs. Next, we apply this knowledge to the multi node environment building on the earlier load balance work by Peterson [35]. We will develop an analytic modeling methodology for determining the execution time of a synchronous iterative algorithm and the potential speedup. *Synchronous iterative algorithms*, present in a large class of parallel applications, are iterative in nature and each iteration is separated from the previous and subsequent iterations by a synchronization operation. Examples of synchronous iterative algorithms include simulations and many image processing and data classification algorithms.

What follows below is the first iteration of the model using our available hardware and firmware. Table 1 lists the symbols and definitions used in this section.

Table 1. Symbols and Definitions

|    | Symbol          | Definition                                                                        | Symbo                         | l Definition                                                                           |

|----|-----------------|-----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|

|    | m               | Number of workstations                                                            | n                             | Number of hardware tasks                                                               |

|    | $S_P$           | Speedup                                                                           | $t_{RC}$                      | Time for a parallel hardware/software task to complete                                 |

|    | $R_P$           | Runtime on parallel system                                                        | $t_{RC\_work}$                | Total work performed in hardware and software                                          |

|    | $R_{RC}$        | Runtime on RC system                                                              | $t_{avg\_task}$               | Average completion time of hardware or software task on RC system in a given iteration |

|    | I               | Number of iterations                                                              | β                             | Load imbalance factor between hardware and software                                    |

|    | $t_{overhead}$  | Iteration overhead operations                                                     | $\sigma$                      | Hardware acceleration factor for RC system                                             |

|    | $t_{SW}$        | Time to complete software tasks                                                   | $R_I$                         | Runtime on a single processor                                                          |

|    | $t_{HW}$        | Time to complete hardware tasks                                                   | r                             | Number of hardware tasks not requiring new configuration                               |

| RC | $t_{parallel,}$ | Time to complete parallel task on multi node system                               | d                             | Number of hardware tasks not requiring new data set                                    |

|    | $t_P$           | Time to complete parallel host software tasks                                     | $t_{config}$                  | Time for FPGA configuration                                                            |

|    | $t_{work}$      | Total work performed in hardware and software on all nodes of a multi-node system | $t_{data}$                    | Time for data access                                                                   |

|    | $eta_k$         | RC node Load imbalance factor at node <i>k</i> in a multinode system              | t <sub>host</sub> serial      | Host serial operations                                                                 |

|    | α               | Load Imbalance factor<br>between host nodes in a<br>multi-node system             | $t_{node}$ serial             | RC node serial operations                                                              |

|    | $\sigma_{k}$    | Hardware acceleration factor for node <i>k</i> in mutinode system                 | $t_{host}$ overhead           | Iteration overhead operations for hosts                                                |

|    |                 |                                                                                   | t <sub>node</sub><br>overhead | Iteration overhead operations for RC nodes                                             |

### **Reconfigurable Computing Node Analysis**

Our performance model analysis will begin with a single RC node running a synchronous iterative algorithm. These restrictions will allow us to investigate the interaction between the processor and RC unit.

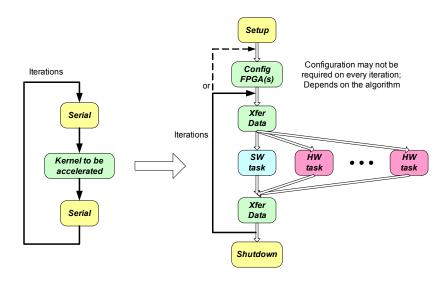

First, we will assume we have a segment of an application that has I iterations and all iterations are roughly the same as shown in Figure 2. The RC unit has at least one FPGA (there may be other reconfigurable devices which provide control functions) and tasks can potentially execute in parallel in hardware (RC unit(s)) and in software on the processor. We should point out that the hardware and software task trees can be arbitrarily complex. Figure 2 shows a simple hardware/software tree structure. Additionally, hardware can be reused within a given iteration if the number of tasks or size of the task exceeds the number of available FPGAs.

Figure 2. Synchronous Iterative Algorithm

For a synchronous iterative algorithm, the time to complete a given iteration is equal to the time for the last task to complete either in hardware or software. For each iteration of the algorithm, there are some operations which are not part of the kernel to be accelerated and are denoted  $t_{serial,i}$ . Other overhead processes that must occur such as configurations and exchange of data are denoted  $t_{overhead,i}$ . The time to complete the kernel tasks executing in software and hardware are  $t_{SW,i}$  and  $t_{HW,i}$ . respectively. For I iterations of the algorithm where n is the number of hardware tasks, the runtime,  $R_{RC}$ , can be represented as [35]:

$$R_{RC} = \sum_{i=1}^{I} [t_{serial,i} + \max(t_{SW,i}, \max_{1 \le j \le n} [t_{HW,i,j}]) + t_{overhead,i}]$$

(7)

To make the math analysis cleaner, we will make a couple of reasonable assumptions. First, we will assume that each iteration requires roughly the same amount of computation allowing us to remove the reference to individual iterations in equation (7).

Second, we will model each term as a random variable and use their expected values. Thus we define  $t_{serial}$  as the expected value of  $t_{serial,i}$  and  $t_{overhead}$  as the expected value of  $t_{overhead,i}$ . The mean time required for the completion of the parallel hardware/software tasks is represented by the expected value of the maximum  $(t_{SW}, t_{HW})$ . Finally, we will assume that each of the random variables are independent and identically distributed (iid). We can then write the run time as:

$$R_{RC} = \sum_{i=1}^{I} (E[t_{serial,i}] + E[\max(t_{SW,i}, \max_{1 \le j \le n} t_{HW,i,j})] + E[t_{overhead,i}])$$

$$= I(t_{serial} + E[\max(t_{SW}, \max_{1 \le j \le n} t_{HW,j})] + t_{overhead})$$

(8)

If the iterations are not iid, we must retain the first form of equation (8) and the math analysis is more difficult.

We can rewrite the RC system hardware/software tasks in terms of the total work. We will assume that all hardware tasks are the same and that the time to complete a software tasks is the same as that for a hardware task. With these simplifying assumptions, we will define  $E[t_{avg\_task}]$  is the expected average task completion time (including hardware and software tasks) within an iteration for the RC system. Therefore the total work completed on the RC system, measured in runtime is given by:

$$t_{RC\_work} = E[t_{SW} + \sum_{n} t_{HW}] = (n+1) \cdot E[t_{avg\_task}]$$

(9)

The division of tasks between hardware and software creates an RC load imbalance [35] which we will represent as  $\beta$ . Considering the affect of the imbalance on the task completion time, the expected value of the maximum task completion time can be expressed as the average task time within an iteration multiplied by the RC load imbalance factor:

$$E[\max(t_{SW}, \max_{1 \le j \le n}(t_{HW,j})] = \beta \cdot E[t_{RC\_system}]$$

(10)

Combining equations (9) and (10) we can rewrite the maximum task completion time as,

$$E[\max(t_{SW}, \max_{1 \le j \le n} (t_{HW,j}))] = \frac{\beta \cdot t_{RC\_work}}{n+1}$$

(11)

Note that if the load is perfectly balanced  $\beta$  is the ideal value of 1 and the total work is divided equally among the hardware and software tasks. If the tasks are performed serially (no concurrent hardware/software operation),  $\beta$  is the worst case value of (n+1), where n is the number of hardware tasks. Thus as the load imbalance becomes worse,  $\beta$  increases ranging from a value of 1 to (n+1).

Noting that the total work measured in time for a software-only solution is not equivalent to the total work measured in time on an RC system solution, we introduce an acceleration factor  $\sigma$  to account for the difference. Since the goal of RC systems is to speed up an application, only tasks that would be faster in hardware are implemented in hardware. For example, an FFT in software may take longer to execute than an equivalent implementation in the hardware. Given the total work that will be completed

in hardware and software on an RC system, we can represent the software only run time on a single processor as:

$$R_1 = I \cdot (t_{serial} + t_{SW} + \sigma \cdot \sum_n t_{HW})$$

(12)

The overhead for an RC system consists of the FPGA configuration time and data transfer time. The configuration time for the FPGA(s) is  $(n-r) \times t_{config}$ , where r is the number of hardware tasks not requiring a new configuration. The time to transfer data to and from the RC unit is  $(n-d) \times t_{data}$ , where d is the number of hardware tasks not requiring a new data set.

The speedup,  $S_{RC}$ , is defined as the ratio of the run time on a single processor to the run time on the RC node:

$$S_{RC} = \frac{R_1}{R_{RC}} = \frac{t_{serial} + t_{SW} + \sigma \cdot \sum_{n} t_{HW}}{t_{serial} + \frac{\beta \cdot t_{RC\_work}}{n+1} + [(n-d) \cdot t_{data}] + [(n-r) \cdot t_{config}]}$$

(13)

Using equation (13) we can investigate the impact of load imbalance and various overhead issues on the algorithm performance by varying  $\beta$ ,  $t_{config}$ ,  $t_{data}$ ,  $t_{RC\_work}$ , r, d, and n.

## High Performance Reconfigurable Computing Multi-Node Analysis

Now that we have a model for a single RC node and an understanding of the basic HPC issues involved in a set of distributed nodes, we will turn our focus to expanding the model for multi-node analysis. An example of the HPRC architecture was shown in Figure 1. For now, we will not consider the optional configurable interconnection network between the RC units in our modeling analysis.

We will again start our performance model analysis using a synchronous iterative algorithm this time running on a platform consisting of multiple RC nodes. The restriction of synchronous iterative algorithms will allow us to investigate the communication and synchronization that occurs among nodes between iterations. We will begin our model by restricting our network to a dedicated homogeneous system where there is no background load (i.e. all nodes are identical, same processor and same RC system configuration).

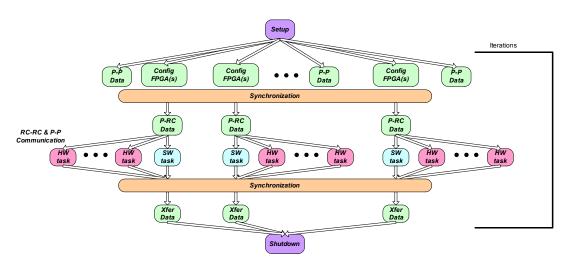

Again, we will assume we have a segment of an application having *I* iterations that will execute on parallel nodes with hardware acceleration. Additionally, we will assume that all iterations are roughly the same as is shown in Figure 3. Software tasks can be distributed across computing nodes in parallel and hardware tasks are distributed to the RC unit(s) at each individual node.

For a synchronous iterative algorithm, the time to complete an iteration is equal to the time for the last task to complete on the slowest node whether it be hardware or software.

For each iteration of the algorithm, there are some calculations which cannot be executed in parallel or accelerated in hardware and are denoted  $t_{master\_serial,i}$ . There are other serial operations required by the RC hardware and they are denoted  $t_{node\_serial,i}$ . Other overhead processes that must occur such as synchronization and exchange of data are denoted  $t_{master\_overhead,i}$  and  $t_{node\_overhead,i}$  for the host and RC systems respectively. The time to complete the tasks executing in parallel on the processor and RC unit are  $t_{SW,i,k}$  and  $t_{HW,i,j,k}$  respectively. For I iterations of the algorithm where n is the number of hardware tasks at node k and m is the number of processing nodes, the runtime,  $R_P$ , can be represented as [35]:

$$R_{P} = \sum_{i=1}^{I} \left[ t_{master\_serial,i} + t_{node\_serial,i} + \max_{1 \le k \le m} (t_{SW,i,k}, \max_{1 \le j \le n} [t_{HW,i,k,j}]) + t_{master\_overhead,i} + t_{node\_overhead,i} \right]$$

$$R_{P} = \sum_{i=1}^{I} \left[ t_{master\_serial,i} + t_{node\_serial,i} + \max_{1 \le k \le m} (t_{RC,i,k}) + t_{master\_overhead,i} + t_{node\_overhead,i} \right]$$

$$(14)$$

Figure 3. Flow of Synchronous Iterative Algorithm for Multi Node Analysis

Again, to make the math analysis cleaner, we will make a couple of reasonable assumptions. First, we will assume that each iteration requires roughly the same amount of computation thus we can remove the reference to individual iterations in equation (14). Second, we will also assume that each node has the same hardware tasks and configuration making the configuration overhead for each node the same. Third, we will model each term as a random variable and use their expected values. Thus we define  $t_{master\_serial}$  and  $t_{node\_serial}$  as the expected value of  $t_{master\_serial,i}$  and  $t_{node\_serial,i}$ . Similarly, we define  $t_{master\_overhead}$  and  $t_{node\_overhead,i}$  and  $t_{node\_overhead,i}$ . The mean time required for the completion of the RC hardware/software tasks is represented by the expected value of the maximum  $t_{RC,k}$  ( $1 \le k \le m$ ). Finally, assuming that the random variables are each independent and identically distributed (iid), the run time can then be expressed as:

$$R_{P} = \sum_{i=1}^{I} \left( E[t_{master\_serial,i}] + E[t_{node\_serial,i}] + E[\max_{1 \le k \le m} (t_{RC,i,k})] + E[t_{master\_overhead,i}] + E[t_{node\_overhead,i}] \right)$$

$$R_{P} = I(t_{master\_serial} + t_{node\_serial} + E[\max_{1 \le k \le m} (t_{RC,k})] + t_{master\_overhead} + t_{node\_overhead})$$

$$(15)$$

As discussed in section 0, we can rewrite the total work at node k in terms of the average task completion time rather than the maximum (see equation (9)). Again assuming the random variables are iid, from equation (9) we can express the total work across all m nodes in the HPRC platform as:

$$t_{work} = \sum_{k=1}^{m} t_{RC\_work,k} = \sum_{k=1}^{m} (n+1) \cdot E[t_{RC\_system,k}] = m \cdot (n+1) \cdot E[t_{RC\_system}]$$

(16)

As discussed earlier for RC systems, when tasks are divided a load imbalance exists. We will represent the RC load imbalance at a particular node k as  $\beta_k$ . Additionally, there exists an application load imbalance across all of the nodes of the HPRC platform. We will represent this node-to-node load imbalance as  $\alpha$ . We will assume the host node application load imbalance  $\alpha$  and RC system load imbalance  $\beta_k$  are independent. Additionally, we will assume that the RC system load imbalance at any node is independent of the others. The completion time can then be expressed as the average task completion time within an iteration multiplied by the load imbalance factors (which together have a multiplicative effect):

$$E[\max_{1 \le k \le m} (t_{RC,k})] = \alpha \cdot \beta_k \cdot E[t_{RC\_system}]$$

(17)

Combining equations (16) and (17) we can rewrite the maximum task completion time as,

$$E[\max_{1 \le k \le m}(t_{RC,k})] = \frac{\alpha \cdot \beta_k \cdot t_{work}}{m \cdot (n+1)}$$

(18)