# **TECHNOLOGY SURVEY**

Technology Utilization Division

# MICROELECTRONICS IN SPACE RESEARCH

DISTRIBUTION STATEMENT A Approved for Public Release Distribution Unlimited

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA SP-5031

Technology Utilization

Division

TECHNOLOGY **SURVEY**

# MICROELECTRONICS IN SPACE RESEARCH

Prepared under contract for NASA by **Research Triangle Institute** Durham, North Carolina

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

Washington, D.C.

August 1965

#### NOTICE

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

> FOR SALE BY THE SUPERINTENDENT OF DOCUMENTS U.S. GOVERNMENT PRINTING OFFICE WASHINGTON, D.C., 20402 - PRICE 60 CENTS

## Foreword

The Administrator of the National Aeronautics and Space Administration has established a technology utilization program for "the rapid dissemination of information . . . on technological developments . . . which appear to be useful for general industrial application." From a variety of sources, including NASA Research Centers and NASA contractors, space-related technology is collected and screened; and that which has potential industrial use is made generally available. Information from the Nation's space program is thus made available to American industry, including the latest developments in materials, processes, products, techniques, management systems, and analytical and design procedures.

This publication is part of a series intended to provide such technical information. It reviews the status of microelectronics with emphasis on topics of particular importance in space research about which information was available. The Solid State Laboratory of the Research Triangle Institute in Durham, North Carolina, prepared this report.

> **THE DIRECTOR**, Technology Utilization Division National Aeronautics and Space Administration

# Preface

The primary purpose of this report is to provide information on the contributions to the microelectronics field which have originated in NASA research programs. Also included is a review of the status of microelectronics in which the limitations of the various technologies are highlighted. Considerable emphasis has been placed on silicon integrated device technology because of its relatively large importance. Microelectronics is defined here as those technologies by which circuit functions are realized in inseparable solid structures which duplicate the behavior of collections of conventional lumped parameter components. This then eliminates from consideration microminiaturization aimed solely at size reduction of components and circuits / Although some of the concepts are original to this  $\rho_{nc}$ report, a preponderance of the material has been obtained from NASA information sources and from the open literature. While it is intended that this report be reasonably comprehensive, the particular research which is described is that for which information was most available. Other equally significant results have probably been generated in other NASA programs.

This report was prepared by the Solid State Laboratory of the Research Triangle Institute, Durham, North Carolina, under Contract NASr-236 with the Office of Technology Utilization and Policy Planning, National Aeronautics and Space Administration, Washington, D.C. The purpose of this contract is to determine, evaluate, and report on NASA's scientific and technological contributions to the field of microelectronics. L. E. Richtmyer, Office of Technology Utilization and Policy Planning, was project director for NASA.

This information was collected and the report written in the period between July 1 and December 31, 1964, by R. M. Burger. Other members of the Solid State Laboratory who contributed directly to the generation of this report are B. M. Berry and L. K. Monteith. The information contained in this report represents the contributions of a large number of people and

VI

organizations and material has been reproduced freely from NASA furnished documents and reports. The open literature has been surveyed for reports on NASA activities and personal contact has been made with the major organizations within NASA who are participating in microelectronics research and development. Of particular help in collecting this information have been the technology utilization officers at the various NASA Research Centers.

### CONTENTS

|                                                  | Pa |

|--------------------------------------------------|----|

| FOREWORD                                         | -  |

| PREFACE                                          |    |

| INTRODUCTION                                     | -  |

| CHAPTER 1. REVIEW OF MICROELECTRONICS            | -  |

| Thick Films                                      | -  |

| Advantages and Limitations                       | -  |

| Screen Circuit Processes                         |    |

| ر کے Pyrolytic Techniques                        | -  |

| Ao Thin Films                                    | -  |

|                                                  |    |

| Advantages and Limitations                       | -  |

| Tantalum Thin Film Techniques                    |    |

| Silicon Integrated Devices                       |    |

| Advantages and Limitations                       | -  |

| Silicon Integrated Device Technology             |    |

| Multichip Silicon Integrated Devices             |    |

| General Device Considerations                    |    |

| Testing of Microelectronic Devices               |    |

| Integrated Circuit Design Theory                 |    |

| Logic Devices                                    |    |

| Linear Integrated Circuits                       |    |

| Reliability                                      |    |

| Applications                                     |    |

| CHAPTER 2. TECHNOLOGY AND TECHNIQUES             |    |

| Perspective                                      | -  |

| Thick Film Circuits                              |    |

| Cermet Resistors                                 | -  |

| Screened Dielectric Formulations                 | -  |

| Single-Crystal Semiconductor Films               |    |

| Gold-film Thickness Determination                |    |

| Single-Crystal Beryllium Oxide (BeO)             |    |

| Hermeticity Test for Integrated Circuit Flatpack |    |

| Flatpack Holder for Testing Integrated Circuits  |    |

| CHAPTER 3. DEVICE DESIGN AND DEVELOPMENT         |    |

| Perspective                                      |    |

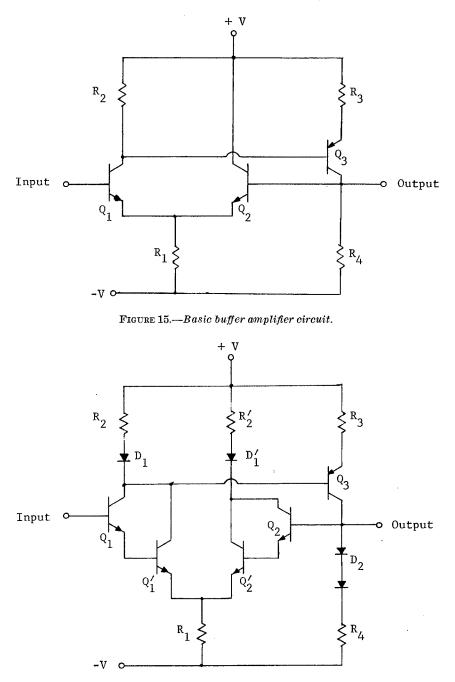

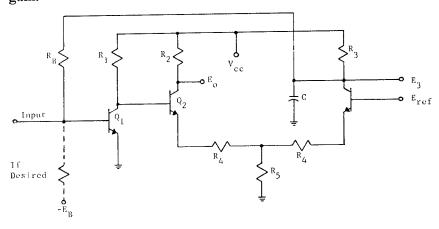

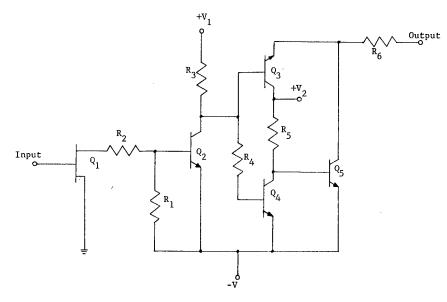

| Buffer Amplifier                                 |    |

| An Integrated Analog Switch                      |    |

| Integrated Low-Level DC Differential Amplifier   |    |

| DC Comparator                                    |    |

| Integrated Instrumentation Amplifier             |    |

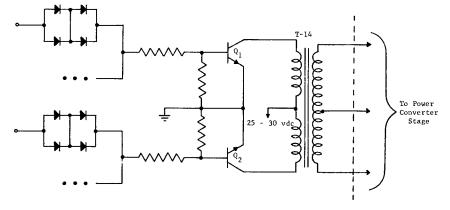

| Static Inverter Preamplifier and Power Amplifier |    |

|                                                           | Page       |

|-----------------------------------------------------------|------------|

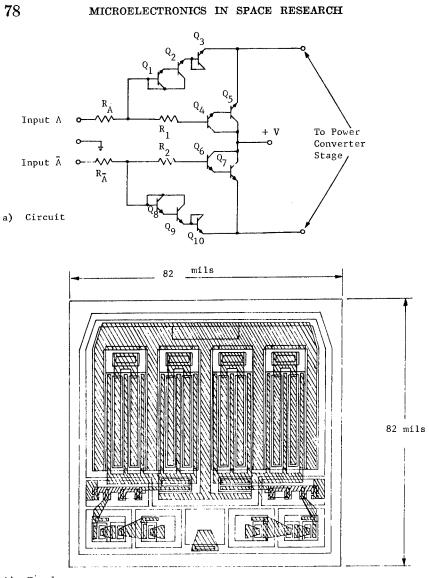

| Integrated Micropower Circuits                            | 81         |

| Short Reports                                             | 84         |

| Thin Film Active Device Research                          | 84         |

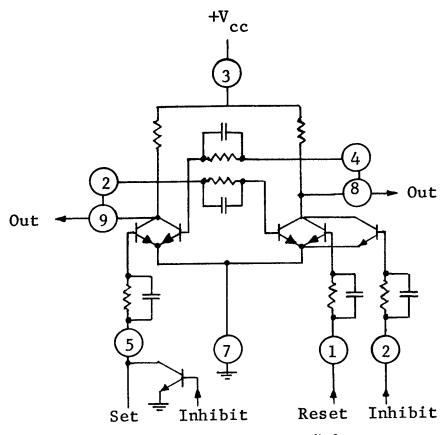

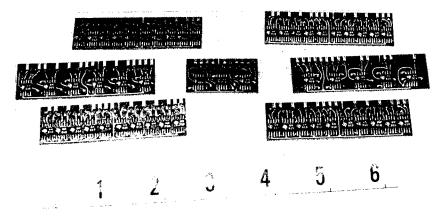

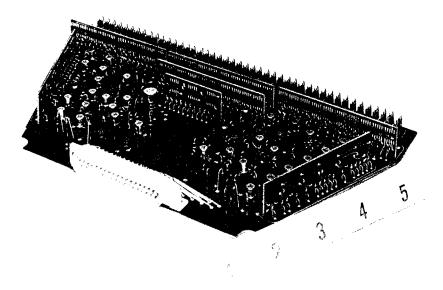

| Thin Film Flip-Flop                                       | 85         |

| Diode Matrix                                              | 85         |

| Radiation Study of Microelectronic Devices                | 85         |

| CHAPTER 4. RELIABILITY                                    | 87         |

| Perspective                                               | 87         |

| Reliability Determination by Performance Studies          | 87         |

| Redundancy Made Possible by Microelectronic Devices       | 88         |

| Reliability Without Redundancy                            | 90         |

| Interconnection Reliability                               | 92         |

| CHAPTER 5. APPLICATIONS                                   | 95         |

| Perspective                                               | <b>9</b> 5 |

| Interplanetary Monitoring Platform (IMP)                  | <b>9</b> 5 |

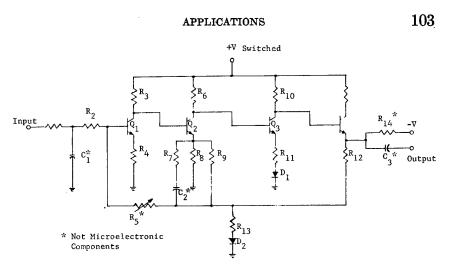

| Digital Tape Recorder Analyzer                            | 100        |

| Record and Playback Amplifiers                            | 101        |

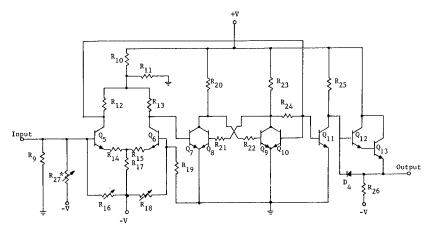

| OGO Data Processor                                        | 104        |

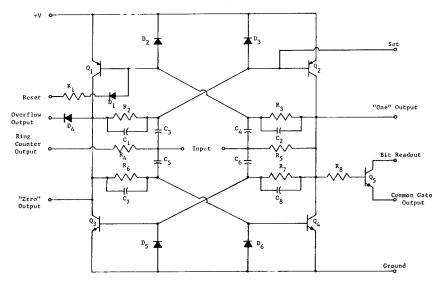

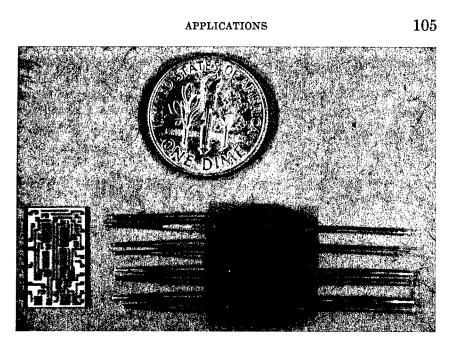

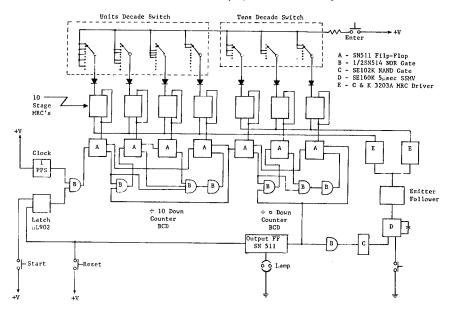

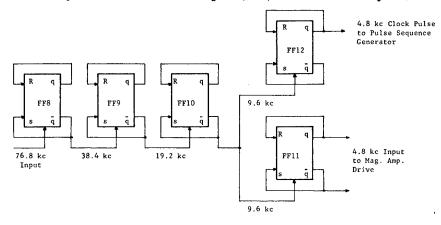

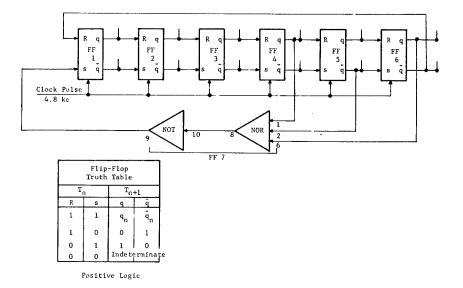

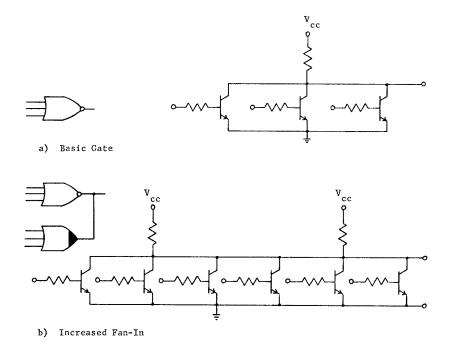

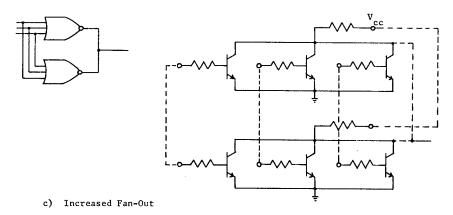

| Programable Timing Circuit                                | 105        |

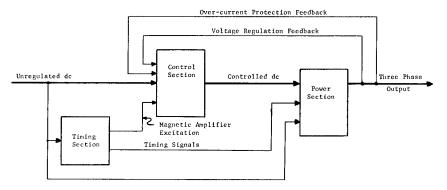

| Static Inverter                                           | 108        |

| Ground Support Equipment                                  | 112        |

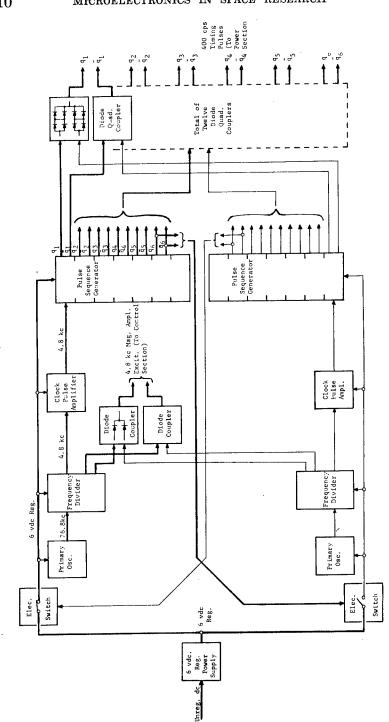

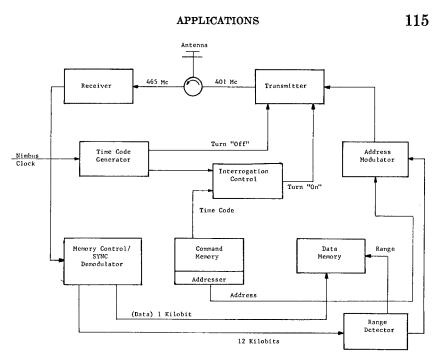

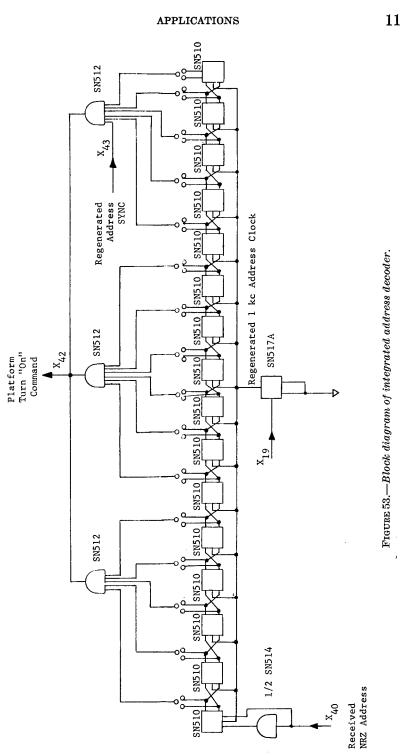

| The Interrogation, Recording and Location (IRL) Subsystem | 114        |

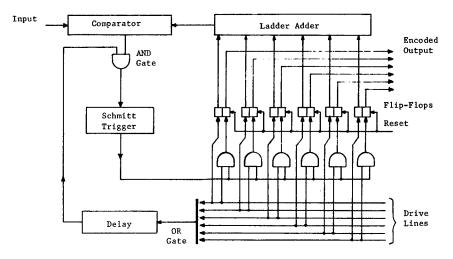

| A/D Converters                                            | 118        |

| A/D Converter for Reentry Telemetry System                | 118        |

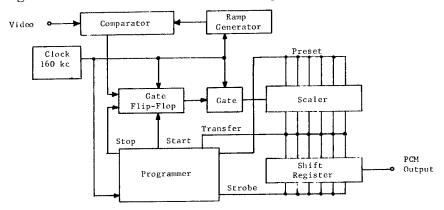

| A/D Converter for Slow-Scan Television                    | 120        |

| Spacecraft Telemetry and Command Subsystem                | 121        |

| Short Reports                                             | 122        |

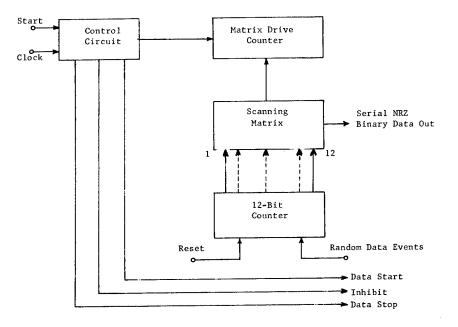

| Random Event Counter                                      | 122        |

| Synchronous Program Control Counter                       | 123        |

| Apollo Guidance Computer                                  | 123        |

| Apollo TV Cameras                                         | 124<br>124 |

| Spacesuit Telemetry and Communication                     | 124        |

| Space Instrumentation Development                         | 124        |

| Space Power Supply                                        | 124        |

| Ranging Coder                                             | 125        |

| Multiplexing Switch                                       | 125        |

| Miscellaneous                                             | 123        |

| CHAPTER 6. CONCLUSIONS                                    | 127        |

| BIBLIOGRAPHY                                              | 127        |

# Introduction

The challenge of space research is requiring an expansion of skills in a variety of technologies. The many useful results which emanate from this effort are often obscured by the more glamorous program results and by the usual communication difficulties between working engineers. An additional problem is that of evaluating particular developments. In this report, an attempt is made to gather together activities in microelectronics from the space research effort, to describe the results in terms which may indicate their usefulness to other fields, and to place them in perspective with other developments in microelectronics. While these objectives have not been completely attained, the material herein should be useful and interesting to a variety of people.

Microelectronics is descriptive of those technologies by which electronic circuit functions are fabricated in small solid structures; these can be both reliable and inexpensive. The availability of microelectronic devices allows the electronics engineer to implement many missions which otherwise would not be feasible or which would be done less efficiently. Nowhere will microelectronics have a greater impact than in space research.

It is coincidental that the National Aeronautics and Space Administration was organized in 1958 almost concurrently with the initiation of the strong research and development effort which was to lead to microelectronic devices. The initial impetus for microelectronics came from the military requirements for more reliable systems. Early microelectronics development activities, which were funded primarily by the Air Force, existed in parallel with the early space research programs which necessarily depended upon existing hardware. As space research activities expanded and became more sophisticated, the limitations of existing hardware became more serious. Attention is therefore being focused on the development of new hardware capabilities, particularly in using microelectronics. Almost every NASA center and major contractor is involved in microelectronics efforts; these range from basic material studies to sophisticated applications. All are focused sharply upon the unique requirements of space research, especially that of very long certain life.

Despite the fact that many space requirements are for small numbers of individual parts, the largest user of silicon integrated devices to date has been a space program (the Apollo guidance computer). Under the auspices of NASA some very significant developments of integrated circuits have occurred. It is obvious that NASA is and will continue to be an important customer for microelectronic devices and systems and will set some of the trends in microelectronic device research and development. This should be comparable to the influence of military, telephone system, and computer applications.

There is a strong trend toward introducing microelectronics into space hardware. While integrated silicon devices and thin film devices have already been involved in actual space probes, a large majority of current equipment has been designed with conventional components. Now, however, almost all new equipment is being designed to include microelectronics to some extent. It is obvious that within several years over three-fourths of space electronic systems will contain microelectronic devices and it is only in those particular applications for which microelectronic techniques are not applicable that conventional circuit techniques will be employed.

Microelectronics is classified here into three different technologies: thick film, thin film, and silicon integrated devices. This latter is by far the most important for future applications and is used here as a basis for comparison. A version of thin film technology is being applied by the Bell Telephone Laboratories and IBM is using thick film circuits in a large computer system. For large system applications, decisions made several years in advance determine system design and do not always represent the state-of-the-art for the devices used.

The main purpose of this report is to present the results of completed research. Most of this is in the application of microelectronic devices; therefore, that section of the report is largest. Industries seeking to apply these devices to their own problems will find this applications experience of considerable interest. The second purpose of the report is to review the state-of-the-art of microelectronics in order to put the real and potential accomplishments of NASA in perspective. Since a great deal of literature is already available on microelectronics and its progress, this review only briefly describes the technologies involved and then identifies particular limitations and problems which exist.

This report is divided into five major chapters; the first of these is a review of microelectronics irrespective of NASA studies. The next four chapters describe different categories of NASA activities in microelectronics; technology and techniques for fabricating and evaluating microelectronics devices; actual design and development of devices, i.e., the implementation of specific requirements for space

#### INTRODUCTION

electronic equipment; reliability which is an important aspect of space research; and applications of microelectronic devices to a variety of equipment. Since telemetry systems are major parts of all space research experiments, a preponderance of the applications reported are concerned with them. It is interesting to note that microelectronic devices are also being used in ground support equipment.

3

,

Chapter 1

# Review of Microelectronics

In the four years since microelectric devices became available in sample quantities, this technology has progressed rapidly. Today over 180 000 silicon integrated devices are shipped each month and an industrial capacity exists for an order of magnitude increase. Each month the technical literature heralds new devices and techniques. No end appears in sight to the accompanying changes which are revolutionizing traditional concepts of electronics. It is difficult to describe a state-of-the-art for so dynamic a technology.

Microelectronic devices are classified here as thick film, thin film and silicon integrated devices. The first is concerned primarily with circuits prepared by printing patterns of paste or slurry through fine screens onto ceramic substrates and subsequent firing to change their nature, but is broadened to include film prepared by pyrolytic deposition techniques. The second of these is concerned with electronic circuits fabricated primarily by the masked deposition of materials through vacuum evaporation. The silicon integrated device technology is concerned with the realization of electronic circuits in and on single crystal silicon substrates primarily by junction formation. Proponents of film devices may question equating the advent of microelectronics with the introduction of silicon integrated devices; however, silicon technology has provided the stimulus for rapid advance which was lacking in the other techniques and thus justified its use as a reference. There is, in fact, an overriding tendency to compare all other devices to silicon integrated devices.

In the past thin films and silicon structures have been pitted against each other; thick films have also been in the fray. The advent of the new series of IBM computers will maintain for thick films an important place in microelectronics, if for no other reason than the magnitude of IBM's impact on the electronics industry. In most cases, however, reliability and economy of silicon integrated devices make them desirable for the realization of electronic functions. In specialized applications representing extremes of power or frequency other techniques are necessary.

It is very likely that silicon integrated device technology will be married to the film technology. This will be at the subsystem level

6

but will depend on improved silicon passivation for a practical packaging method. A number of silicon integrated circuits will probably be mounted on a substrate on which film components and interconnection paths will have been formed. Inductors, piezoelectric crystals, and other devices may be compatibly mounted for optimum function realization.

All applications of microelectronics have certain common objectives which must be examined when a choice is made between technologies. For microelectronics, the objectives are given below :

- 1. Function Realization—While it is obvious that no particular technology will be chosen if it cannot perform the required function, this requirement is sometimes overlooked. For example, a system cannot be fabricated entirely by one technology unless all required functions are realizable by that technology, which is seldom the case.

- 2. High Reliability—Closely related to cost but overriding it in many space and military applications is reliability. While it is possible that the several technologies will provide structures of equivalent reliability, there is a basic tenet that other things being equal the structure requiring fewer different materials will be more reliable. The silicon structure has advantages in this respect.

- 3. Low Cost—Many devices are still procured on the basis of cost. This is most important in the nonspace, nonmilitary applications which determine volume production. Devices produced in volume are also most often chosen for the more critical applications in order to take advantage of product stability, production experience, and applications information. The batch production processes of the silicon integrated device technology and availability of standard components have an advantage but highly mechanized volume production of devices by other technologies may become competitive.

These three objectives (low cost, high reliability, function realization) are not exclusive but, in most cases, override all others.

The scope of present applications of microelectronics is not large when compared to their potential. This results primarily from the necessary lead time required to put any new technique such as microelectronics into widespread use. For microelectronic devices in particular, this has been difficult since it has been necessary to discard many of the traditional concepts of system design and to develop new ones. In other cases the necessary device types to warrant a system redesign have not been available and even when they are available, the advantages to be gained from a system redesign do not often

overcome the cost. Thus applications, while appearing to move slowly when examined on the basis of available useful equipment and considering the enthusiasm of most engineers engaged in the microelectronics field, are nevertheless advancing at a rapid pace when the limiting factors are considered. The actual pace can be expected to increase rapidly in the near future particularly in space programs.

In the following sections, each of the separate technologies will be discussed in terms of the necessary processes and the resulting structures and their capabilities; a concluding section compares the three technologies.

#### THICK FILMS

Thick film structures are prepared by screening and firing or by pyrolytic deposition. They generally contain only conductors, resistors and capacitors. Other components must be added as discrete entities. The substrate is usually a ceramic wafer.

#### ADVANTAGES AND LIMITATIONS

This technology is not new, but has been in existence for a number of years. In fact, at least one company has been making such units for over twenty years and is now producing over 45 million units/year at costs ranging from under ten cents to three dollars. As with all technologies, however, there are limitations. Most important of these is the inability to provide active components except by individual insertion with attendant high cost and extra connections. There are also the usual limitations upon the value, tolerance and stability of the resistors and capacitors. Attempts have been made to circumvent some of these problems by the development of new materials and new deposition techniques. In pyrolytic deposition, for example, chemical compounds containing the desired materials are thermally decomposed at the substrate over the entire surface; the pattern is then etched or machined into the surface layer.

A big advantage of the thick film technique is its high volume use and relatively low cost. It is also a flexible technique in which a variety of patterns can be achieved with little variation in the process. As long as resistance ratios on the pattern are no more than 5 and capacitors are less than 0.05  $\mu$ f, thick film circuits can be made very rapidly and even higher resistance ratios (up to 100) can be processed routinely.

The primary limitations on the use of thick film circuits are ones of size and reliability. It can be argued for example that conventional discrete components can be assembled into circuits which are of comparable or less total volume and weight than thick film circuits. At the same time even though the thick film circuits are formed at high

$\mathbf{7}$

8

temperatures and are thus relatively stable, it is also true that conventional circuit techniques are quite reliable. Thus the question is raised as to why one should go to thick film circuits if there are not significant improvements in reliability or in volume and weight or in power consumption. The best argument for thick film circuits (and thin film circuits) is the ability to form a number of connections in the process thereby eliminating the troublesome one-at-a-time welded or soldered connections. On the basis of cost vs. incremental improvement in performance, thick films do not have much to offer and to a large extent have been passed over in microelectronic considerations. On the other hand, due to the large commercial utilization of such circuits which includes the recent use by IBM of these techniques in a very large computer program involving ultimately millions of circuits, it is likely that thick films are here to stay, not only in the commercial field but also in space and military systems. For this reason they must be considered as a serious competitor of other microelectronic techniques.

An even more significant possibility is that integrated silicon devices may be placed onto ceramic wafers with thick film components (or possibly thin film ones) which cannot be economically fabricated in the silicon and that such a technique will provide a complete system capability. If, for example, silicon integrated devices and certain high value resistors and coupling capacitors can be placed onto a suitable ceramic substrate as a basic system building block, it is possible to envision a very practical and powerful technology for achieving large electronic systems with a high degree of reliability and with attendant low cost.

#### SCREEN CIRCUIT PROCESSES

Despite the very large number of screen circuits which have been available on the market for a considerable period of time the exact processes by which these circuits are made are not generally known. This is because the vast majority of the circuits have been used on the consumer or industrial equipment market and their development has not been supported by government funding. As a result, many techniques have been considered proprietary. Nevertheless, the basic processes for making screen circuits are known and only the details of the formulation and the process parameters cannot be given.

Screen circuits ordinarily consist of conductor and resistive layouts in relatively simple patterns. Conductor crossovers are avoided and few capacitors are used. The majority of formulations for conductors are available from chemical companies, particularly Du Pont, and consist primarily of gold, platinum, palladium, silver, or mixtures of these, depending upon the particular requirement. These conductive formulations are fired at temperatures between 600 and 1100° C.

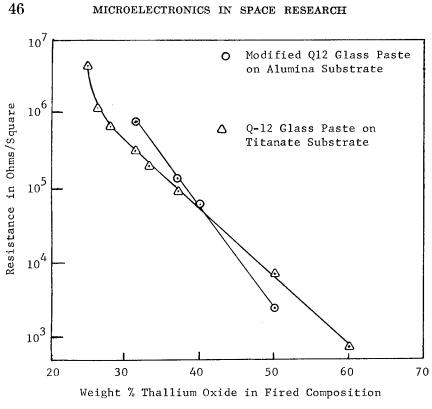

Resistive formulations consist of palladium, silver, carbon, glass frit and other additives designed to achieve specific properties. A new development tailored for high resistance applications includes thallium oxide and glass frit. These resistive formulations can be bought from a number of commercial suppliers. Little information is available on formulations for dielectric coatings, although it is thought that most such coatings consist of glass with additives such as barium titanate to increase the dielectric constant.

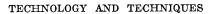

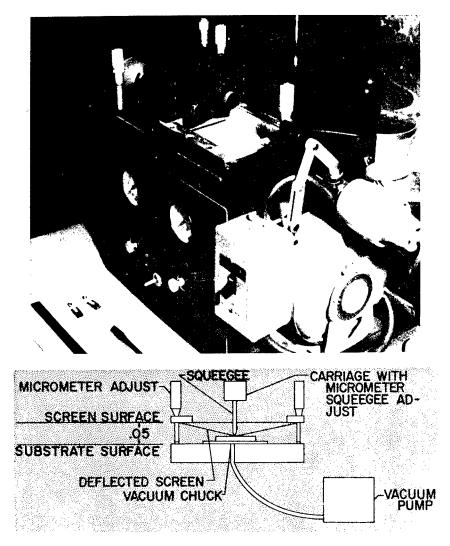

With suitable formulations for the screen circuit process, the procedure is as follows. A series of screens is fabricated, with geometries to fulfill the circuit design, for impressing the pastes or slurries upon the ceramic substrate. These screens can be made of silk or stainless steel, the latter being more durable. The mesh size of the screen varies with the application, but generally falls in the range of 150 to 200 mesh. Finer screen sizes result in incomplete circuit patterns since the paste may not extrude through to the ceramic surface. Coarser screens may cause voids in the pattern and have lower resolution. The application of the pastes and slurries is the same as that used by artists in the silk screen process for many years. After application, the pattern on the wafer is air dried, vacuum dried, or gently heated in order to drive out part of the binder. When several different pastes are to be fired, the additional patterns may be put onto the wafer before firing any of them. More often each deposit is fired separately so that the entire process is repeated for each type of paste. The firings usually are in order of decreasing temperature. Both static kiln furnaces and conveyor furnaces are employed, the latter being used in production processing where the wafers are placed on a continuous belt and passed through a suitable temperature profile. Total firing time typically is about 1 hour although the firing temperatures and times vary with the materials employed. Since the films obtained are relatively thick, on the order of one micron, the matching of thermal coefficients of expansion is important. If they are not accurately matched, the deposited film will crack or craze upon removal from the furnace particularly for glass dielectric formulations. Other components such as large capacitors, diodes, and transistors can be directly soldered to the first conductors. The completed screen circuit wafer can be tested and used with pressure type connectors, although soldered connections are more reliable.

A variety of substrates is available, but a high quality alumina is most desirable. In some cases the alumina substrates are overcoated with glass to give a smooth surface and desirable expansion coefficient to the substrate for particular processing requirements.

Many kinds of circuits made by screening are available. One supplier advertises linear and digital circuits, RC networks, audio filters,

785-727 0-65----2

notch filters and other components in almost any standard value and tolerance. In order to achieve this versatility, the components except for the small capacitors and resistors are inserted and in some cases bonded to the ceramic substrate. The form of the substrate varies among manufacturers. In one case the alumina has lead wires directly bonded to it and is packaged in a suitable epoxy. In another case a supplier uses very small circular wafers and assembles them in a TO-5 transistor type can. In other cases the screen circuit is protected only by a film or left uncoated.

#### PYROLYTIC TECHNIQUES

As noted previously, other methods for depositing thick films exist, the most important of which is the vapor or pyrolytic deposition process. Suitable chemicals are decomposed at the substrate surface and unwanted material is removed in a subsequent step by etching or sandblasting. Vapor sources include metal-organic compounds and metal halides. One of the more common processes uses tin chloride in solution with a catalytic agent. This is sprayed onto a glass covered alumina substrate and decomposes to give a thin oxide coating which is then patterned into film resistors. In this case, conductor patterns can be formed on top of the tin oxide by electroless plating of copper and dielectric patterns made by decomposition of ethylorthosilicate or by glass frit formulations. Components and circuits obtained by these and similar processes are commercially available and comparable to screen circuits. The relative advantages of these two thick film circuit technologies are determined largely by their reliability and cost (in some cases, the performance capabilities may be different). No clear choice now exists.

#### THIN FILMS

Historically, the development of the thin film technology for the fabrication of electronic circuits somewhat parallels semiconductor technology for it was not until transistors became available that the potential rewards associated with the development of thin film techniques became apparent. The applications which appeared possible for thin films involved the resistors, capacitors and interconnections of electronic circuits. Before the advent of the transistor these portions of the electronic circuits were relatively small, reliable, and inexpensive. The change in this situation caused a large increase in the attention given to thin film techniques.

Much research was performed on ferromagnetic thin films and during the past decade thin film magnetic memories have become available and are being used in computer systems. This however, is a peripheral subject with respect to the present discussion. In this

report thin films are considered only for the fabrication of electronic circuits such as are used in the logic portions of a computer, signal handling circuits and all of the other diverse circuits which include both active and passive components. For these, thin films have been slow to mature, although they are included now in operating equipment. At least three dozen electronic companies have some capability for supplying thin film circuits. These companies range from several small ones specializing in and supplying only thin film circuits, through the larger diversified component and device suppliers, to the large corporations supplying electronic systems.

It is interesting to note that thin film circuit research has encouraged corresponding rapid developments in the vacuum art. Equipment available for vacuum deposition of thin films has progressed from crude bell jars operating at  $10^{-6}$  torr with homemade mask holders to extremely versatile automatic vacuum systems containing extremely complex mask changing apparatus, capable of multiple depositions without breaking the vacuum, and operating to  $10^{-10}$  torr. The commercial availability of such equipment is one very good reason for the existence of the multitude of organizations possessing the equipment and the implied capability for fabricating successful circuits.

#### ADVANTAGES AND LIMITATIONS

Despite this large developmental effort and equipment investment the application of thin film circuits has been slow. Some of the reasons for this are:

- 1. Well made thin film circuits with their inserted active components representing the state-of-the-art are smaller than can be achieved by fabrication of circuits with available miniature discrete components.

- 2. The reliability of thin film composite circuits does not necessarily exceed that of conventional component circuits. There are apparently some unique failure modes associated with thin film circuits on which additional research must be done.

- 3. To date thin film circuits are, if anything, more expensive than conventional component circuits. These costs are, of course, related to the volume of production but there are some inherent expenses which seem difficult to avoid.

- 4. It has been stated many times that the key to a rapid expansion of the use of thin film circuits is a thin film active device. Experimental examples of such devices are just appearing from the laboratories, but there are apparently many improvements to be made before these can become competitive.

- 5. The electronic industry is characterized by a large inertia, i.e., there is a long time between the development of a new technology

and its wide use. It is only now that the industry is adapting itself across the board to the use of transistors. Microelectronics circuits, which are available, are starting to be phased into equipment. This will be a slow process and most effort will be given to that particular technology which offers the most right now in the important criteria of reliability and cost, viz, not thin films, but silicon integrated devices.

What then is the role for thin films in the advancing electronic art? The momentum of the research and development efforts relating to thin films is such that very definite roles for them will be defined, and that they will be widely used. Some of the advantages of thin films are:

- 1. Thin film circuits do not exhibit spurious interactions any more than do conventional component circuits. For this reason, a one to one extrapolation can be made from conventional components to thin films; the sometimes troublesome interactions characteristic of silicon integrated devices are not present. This results in a bias towards thin film techniques by engineers who are familiar with conventional circuit design and also offers a high frequency circuit capability which has not yet been demonstrated by the silicon technology.

- 2. Silicon circuits are inherently small and have limited power handling capabilities. When the size increases in order to accommodate higher power, the cost goes up rapidly. In this higher power end of the circuit spectrum, thin films for use as passive components and for interconnections are very practical. High resistance, high power resistors, for example can be made with thin films but not as part of a silicon integrated device.

- 3. Thin film circuits are believed to be considerably more radiation resistant than are semiconductor integrated circuits. This apparent ability to operate in a radiation environment for longer periods of time than silicon integrated circuits has been a prime justification in thin film circuit development. Despite some doubts as to the accuracy of this reasoning, the requirement for radiation resistant electronics is such as to demand further investigation.

- 4. Thin film circuits can consist of a multitude of materials, each chosen to be optimum for its particular application. This allows a more complete assortment of component parameter values and circuit types than is possible with silicon. Counter to this, however, is a belief that the addition of new materials to a given electronic structure may introduce new failure modes and may detract from the reliability.

- 5. Thin films can be deposited upon a silicon substrate and used to improve the capabilities of silicon integrated devices. This adds additional processing steps to the fabrication, increases cost, and perhaps decreases reliability. The hybrid integrated circuit, however, is currently obtaining increasing popularity because of its capability for obtaining certain extreme parameter values impossible in silicon alone.

- 6. Another hybrid technology involves the deposition on a substrate of thin films for passive components and interconnections, after which silicon integrated circuits are inserted. A favorite method for accomplishing this is to provide ball type electrical connections to the silicon integrated structure, facing it down on a thin film substrate and bonding it by soldering or other appropriate techniques. This approach, in which the best attributes of both the silicon and thin film technology can apparently be used, possesses a large potential.

Each of the points made above for thin films could, perhaps, be made for thick film structures; it is difficult to tell which is better able in a particular case to provide the best answer. Thick film structures might be expected to be more reliable due to the high temperature processes employed in their fabrication but techniques have been developed for many more materials with thin films than with thick films. Also for thick films there is apparently no foreseeable chance to obtain an active device structure; this is not the case with thin films. If size is important, thin films are at present made by techniques which allow higher resolution in the structures.

Most of the comments made above apply to all thin films. However, in the subsequent discussion of the capabilities and fabrication processes it is necessary to separate the two more important of these techniques, i.e., vacuum deposition and the sputtering of tantalum films.

#### FABRICATION OF VACUUM DEPOSITED THIN FILM CIRCUITS

The equipment for fabricating thin film circuits consists basically of a vacuum system, masks, evaporation sources, and substrate heaters. The complexity of this equipment may vary a great deal ranging from an "oil" pumped, 18-inch bell jar system with mask changers and evaporation sources to a complex in-line system of multiple vacuum chambers which allow substrate transfer from one processing chamber to the next without breaking the vacuum.

Regardless of complexity, the actual processes are basically the same. Given a circuit design, suitable masks are made which define the areas of deposition for the various materials. Translating a circuit into

mask form is not difficult. Objectives in mask design are avoidance of crossovers, minimization of interconnection lengths, minimum area for the desired parameter tolerances, graded power dissipation and a realizable mask geometry. A typical circuit may require four masks: the first for the resistor pattern, the second for bottom capacitor plate, the third for dielectric coating and the final one for top capacitor plates and interconnections. With some processes an additional pattern is needed in order to provide suitable materials for soldering external leads to the circuit. Masks are normally formed by photoetching openings in thin copper-nickel alloy sheets.

The masks are mounted in a changer; while a variety of designs are available, a typical one has a rotary plate on which the masks are mounted and is stepped sequentially in front of the substrate. Positioning is often achieved by aligning suitable holes in the masks with locater pins. Alternative systems involve movement and location of the substrate rather than the mask. The exact mechanism is unimportant, as long as the alignment is close enough for the desired resolution in the deposited pattern. Tolerances of several thousandths of an inch between successive masks are possible.

Source heaters are provided for heating the appropriate materials to evaporation temperatures. There are a variety of designs for sources. Aluminum, a very common material in thin film circuits, is most often evaporated from a stranded tungsten coil filament which is directly heated by passage of current. Silicon monoxide, the most common evaporated dielectric, requires the use of carefully designed evaporation sources which prevent line of sight evaporation from the solid silicon monoxide to the substrate. This is to avoid the ejection of particles from the source to the substrate which causes defects in the films. These sources are normally fabricated from sheets of refractory metal and are heated by passage of large currents. Nickelchrome alloys, such as Nichrome or Chromel, which are employed for resistors can be evaporated from coiled tungsten wire or by direct passage of current through the alloy wire. A variety of other materials is also employed, each requiring some attention to the design of the evaporation source. Information on sources is available both in the scientific literature and from the suppliers of evaporation sources.

Both alumina and glass substrates are employed for thin films. These substrates are mounted in the vacuum in a suitable holder. It is usually necessary to heat the substrate at various stages of the deposition process, both for cleaning the substrate and for good adhesion of the deposited material. This is accomplished by a suitable resistance heater mounted behind the substrate. Normally the evaporation

sources are mounted at the bottom of the vacuum system, with the substrate at the top. In some of the more advanced systems very high vacuums are possible down to the  $10^{-10}$  torr range and the evaporation sources may be heated by electron beam bombardment.

Normally all depositions are made without breaking the vacuum. This has been found necessary in order to avoid defects in the films brought about by contamination in the air. Dust is a particularly nasty problem. In some cases the adherence of the successive depositions will be poor if there has been exposure to the atmosphere.

With the apparatus described, the deposition of the thin film circuits is a relatively straightforward process. In general, substrates are placed in the holders, the vacuum is obtained, the substrates are heated for cleaning, and the materials evaporated through their respective masks in sequence. The substrates are then removed from the vacuum chamber, tested, resistors adjusted if necessary, active components inserted, lead wires attached, and the circuit encapsulated. Particular processes, of course, differ in detail due to the variety of materials which can be handled in a vacuum evaporation scheme. While Nichrome is popular for thin film resistors, rhenium, titanium, nickel, and other resistive materials have also been vacuum deposited. For dielectric coatings silicon monoxide <sup>1</sup> has bee nused most often but other dielectrics such as magnesium fluoride have also been employed. The silicon monoxide is sometimes oxidized to silicon dioxide during evaporation in order to improve its dielectric properties. Just as with tantalum, as described in the next section, titanium can be anodized to form a dielectric suitable for capacitors. Conductors used include aluminum, silver, copper, and other good metallic conductors.

The parameters of the components which can be obtained by vacuum deposition processes are quoted at various limits by the device suppliers. A typical range of resistance may be quoted at 10 ohms to 1 M $\Omega$  by a supplier after which a recommendation is made that resistance values be kept between 500 ohms and 20 k $\Omega$ . Vacuum deposited capacitors may be as large as 0.01  $\mu$ f on a practical size substrate, but some manufacturers even in this range prefer to use attached chipcapacitors with a barium titanate dielectric. The tolerance on these components is a function of their size, typical values being  $\pm 20$  percent for untrimmed resistors and  $\pm 10$  percent for capacitors. Long term stability of the resistors is quoted as 0.1 percent for resistors and 1 percent for capacitors. The temperature coefficient observed for the materials and processes normally used ranges from  $\pm 50$  to  $\pm 1000$

<sup>&</sup>lt;sup>1</sup> The term silicon monoxide is used although the oxide may well not be a stoichiometric compound and the Si: O ratio may vary throughout the layer. The same is true for silicon dioxide.

$ppM/^{\circ}C$  for resistors up to  $\pm 1000 ppM/^{\circ}C$  for capacitors. The complexity of the actual circuit and the tolerances which are possible with a particular system determine the substrate size. Single logic stages or amplifiers may be obtained on substrates approximately 0.3 inch square while multiple circuit configurations with over 30 circuits on a substrate have been formed on larger substrates. Normal power ratings for thin film circuits are on the order of a few watts per square inch of the substrate. Resistor and interconnection lines can be as small as 3 mils wide, but a width of 10 mils is more common and gives better results.

The lead wires of inserted active devices may be attached to the thin film substrate by a variety of bonding techniques. Soldering is most common but thermal compression bonding, ultrasonic bonding and welding are also employed. A recent innovation is bonding the active device chip directly to the thin film by small solderable copper ball connections. A variety of encapsulations have been employed for thin films including various epoxies, varnishes, and an overcoating of silicon monoxide. More recently small devices have been supplied in hermetically sealed packages due to problems identified with the other encapsulants.

#### TANTALUM THIN FILM TECHNIQUES

Since 1959, tantalum thin film circuit technology has been the subject of increasing interest. The advantages of using a tantalum film are high annealing temperature, film stability, anodic adjustability of resistors, and high dielectric strength and dielectric constant of its oxide for capacitor use. Unfortunately, it is not possible to fabricate transistors or diodes on tantalum patterns. However, these devices can usually be mounted directly onto the substrate.

The high melting point of tantalum requires deposition by cathodic sputtering rather than by vacuum evaporation (electron beam heating can be used, but is usually less desirable). The sputtered films adhere better than evaporated films and are more uniform. Sputtering is more economical of material because the deposit is localized but the deposition is difficult to monitor and to mask for geometry control.

Sputtering is a vapor deposition process in which an electrical discharge is set up between two plates in the presence of a low pressure inert gas such as argon. The ionized gas atoms are accelerated by the high electric field to the tantalum cathode and release their kinetic energy, knocking off tantalum atoms (a few of which may become ionized) which are then free to diffuse to the glass substrate on the anode.

In the sputtering process, the vapor deposition chamber is used only to produce thin films. The resistor and capacitor geometry patterns

and circuit layout are done externally by high-resolution photoengraving techniques, which permits the fabrication of high density microcircuits.

For tantalum thin film resistors, a uniform and stable film with a predetermined sheet resistivity must be obtained on the glass or ceramic substrate. Nonuniformity in the resistance of sputtered tantalum films is due to the presence during deposition of temperature gradients and of electric charge on the substrate.

Resistance adjustment and stabilization are obtained by anodic oxidation of the tantalum at temperatures over  $350^{\circ}$  C. Resistance values are monitored externally during trimming. Adjusted values to within  $\pm 3$  percent are typical, but values can be trimmed to better than  $\pm 0.02$  percent where extreme precision is required.

Stabilization of the resistor is obtained by gold doping and oxide formation. A layer of gold with a thickness of about 7 percent of the tantalum is diffused into the tantalum film at a temperature of around 400° C for about 30 minutes. The film obtained has the same resistivity as the original undoped film, but is much more stable and has a temperature coefficient close to zero. A heat treatment for 25 hours at 250° C forms a protective oxide coating thicker than any that could grow during the resistor's lifetime. This oxide cover provides effective protection from the atmosphere and makes further encapsulation unnecessary unless additional mechanical protection is required. Finally, conductive material is deposited over the film and circuit patterns are produced employing standard photoengraving techniques. Conducting lands are usually obtained by depositing gold. A titanium layer between the gold and tantalum creates a more reliable high-strength bond.

Typical resistor characteristics obtained on a 0.31 inch square glass substrate are shown in table I.

#### TABLE I.—Typical Resistor Characteristics

| Working sheet resistivity | 50–600 ohm/square                                 |

|---------------------------|---------------------------------------------------|

| Range                     | 10 to 1.5 Megohm                                  |

| Tolerance                 | <0.02 to 10 percent                               |

| Temperature coefficient   | -250 to $+50$ ppM/°C                              |

| Power dissipation         | >4.6 watt/cm <sup>2</sup> of substrate            |

| Noise                     | $0.01 \ \mu V \ (rms) / volt \ across \ resistor$ |

|                           |                                                   |

In special cases, tantalum thin film resistors can be fabricated to dissipate enough power to thermally-fracture the glass substrates without otherwise failing.

Introducing reactive gases such as nitrogen, oxygen and hydrocarbons into the argon sputtering atmosphere changes the electrical properties and structure of the resulting tantalum film. The intro-

duction of nitrogen to the sputtering chamber affects the specific resistivity of the sputtered film. Between  $10^{-6}$  torr and  $4 \times 10^{-5}$  torr, a 5-fold increase in specific resistivity is noted with a limiting value of  $250\mu$  ohm-cm being attained at background pressures greater than  $5 \times 10^{-5}$  torr for 1000 A=0.1 micron films. The temperature coefficient of resistance (TCR) is affected similarly starting at a high value for relatively pure tantalum and decreasing to a negative value of 60 ppM/°C at a nitrogen background pressure of  $3 \times 10^{-5}$  torr. Thus, the consistent fabrication of precision resistors with reproducible parameters is possible by using nitrogen at various background pressures in the sputtering process. However, the exact dependence of the TCR and specific resistivity varies from system to system and extreme care must be taken during the fabrication process. It is necessary to start with a specific resistivity in the film of less than  $75\mu$ ohm-cm to attain reproducible electrical properties for the resulting tantalum nitride films.

The precision of thin film capacitors is a function of the uniformity and reproducibility of the thickness of the oxide dielectric and the electrode area. A means to attain the high precision required for microcircuit capacitors is the anodic oxidation of tantalum films. An electrochemical cell consisting of a tantalum anode and a platinum cathode in a heated electrolyte is used to form the oxide dielectric. A potential of 100–150 volts de applied to the cell for a specified time converts the tantalum metal to a very uniform pentoxide ( $Ta_2O_5$ ). The oxide thickness is directly proportional to the applied voltage at room temperature and forming constants of 25 A/V are typical. The capacitor characteristics are, therefore, predictable.

A method for improving capacitor yields has been suggested. After the tantalum has been anodized, a layer of aluminum is evaporated over it. This aluminum layer is then removed by etching, with care taken to ensure that the etch does not undercut the glass substrate or destroy the mask. The film is then reanodized to the previous final voltage, and counterelectrodes of aluminum are evaporated to form a capacitor. The area of the counterelectrode determines the final capacitance values. For a specified anodizing potential, capacitance values from 30 to 30 000 pf can be obtained by varying the counterelectrode size. This process is believed to fill in film defects with aluminum oxide.

Table II lists some typical characteristics for capacitors fabricated on 0.2 inch diameter glass substrates.

The range of breakdown voltage is satisfactory for logic circuits operation in which voltages of 10 V or less are applied.

TABLE II.—Typical Capacitor Parameters

| Capacitance                | $1.0 \ \mu f/in.^2$ |

|----------------------------|---------------------|

| Temperature coefficient    | 250 ppM/°C          |

| Dissipation factor at 1 kc | < 0.01              |

| Breakdown voltage          | > 25 V              |

The rapid increase in the dissipation factor with increasing frequency for tantalum thin film capacitors limits their use in high frequency logic circuits. Improvements to extend this frequency limitation are the use of a relatively thick layer of tantalum and the application of a conductive metal underlay, such as aluminum, under the tantalum. Capacitors having a Q of 50 at 5 Mc have been fabricated by underlaying the tantalum film with aluminum and by using thick counterelectrodes of copper.

It has often been stated that one advantage of tantalum thin-film circuitry is the fact that the same metal is used to fabricate the resistors and capacitors, yielding unified technology. However, this advantage is lost, somewhat, by the improved fabrication methods that have come about in tantalum technology. The methods of gold or nitrogen doping and protective anodization employed for resistors are not particularly compatible with thick low-resistivity layers of tantalum or aluminum underlayers used for capacitors. However, tantalum thin-film resistors and capacitors have performed well and both merit further development for future microelectronic circuit use.

#### SILICON INTEGRATED DEVICES

The development of silicon integrated devices, to electronics, ranks with the inventions of the electronic vacuum-tube and the transistor. Regardless of future trends in microelectronics, silicon integrated devices will play a major role. Less than 5 years after the initial research, thousands of such devices can be found in operating systems and the entire electronic industry is experiencing a reorganization to adjust to the resulting changes. Research on silicon integrated devices started in 1959 and today over twenty companies (the actual number varies from week to week) are offering more than 300 different devices for sale.

#### ADVANTAGES AND LIMITATIONS

Even the most conservative critic will now concede that in systems requiring digital elements, silicon integrated devices are competitive with conventional circuits and thus should be given first consideration in any new equipment design. For linear or analog circuits, an opti-

20

mistic statement is that in the near future it will be possible to design and fabricate any function which can now be performed with transistors and which does not require inductance or large values of capacitance. Even for circuits traditionally requiring these functions, in many cases it will be possible to obtain designs in integrated form which circumvent that need. With advancing technology, three trends in silicon integrated devices are evident. The first of these is due to the evolving technology for fabricating a multitude of circuits on a silicon chip rather than one or two as is now the case. The second trend results from using other materials to enhance the silicon integrated circuit. The prime example of this is the development of optoelectronic techniques utilizing gallium arsenide diodes as photon sources. The third trend is toward the functional device wherein the operating solid structure performs electronic functions needed in a system but cannot be broken down into equivalent conventional com-The order given for these three trends is that in which ponents. practical results can be expected.

It is useful to examine the reliability, cost, size and power requirements of silicon integrated devices. With respect to reliability no basic limitations have yet been found. As with any new device many early design and production methods turn out to be inadequate. With these eliminated or corrected, however, the life of silicon integrated devices is very long. Systems can be designed so that properly screened devices seem not to fail at all. The silicon integrated 3-input NOR gate being used for the Apollo guidance computer has a failure rate of less than 0.005 percent/1000 hr= $5/10^8$  hr (at 90 percent confidence level) estimated from actual operating use.

The costs of silicon integrated devices cover a wide range. For new devices with significantly enhanced capabilities and available in sample quantities only, the price per unit may be hundreds of dollars, but for high production devices with no demanding specifications, prices are below \$3 each in quantity. For high-quality production devices, typical prices range from \$20 to \$50. This is just an indication that the predicted cost competitiveness of silicon integrated devices is being realized. Most common logic functions can be obtained less expensively in silicon integrated devices than using conventional components. It can be expected that the trend will be toward lower prices for all silicon integrated devices for which a volume market is found.

In discussing microelectronic devices, their size and weight are often compared to those of conventional circuits performing the same function. Integrated silicon devices do offer a very significant reduction in size and weight; in fact, so much so that the emphasis on their size and weight has to a large extent been forgotten. In most commercial,

industrial, and military applications, the size and weight of the system is no longer significantly affected by further size reduction of integrated devices; the input, output and interconnections of these systems are the limiting factors. In space research where size and weight are still extremely important, integrated circuits are being used to good advantage. Equally important, if not more so than size and weight, is the low power requirement of the integrated device. More significant reductions can be obtained in the overall size and weight of a space research experiment by reducing the power requirements of the electronics than by shrinking the device structures.

Power dissipation of silicon integrated devices is between one and several hundred milliwatts per device, dependent upon the function of the device and its design. Both ends of this power spectrum are being pushed by further research and development. For space research and other applications in which power is at a premium, devices which operate at microwatt power levels are needed. The high power end of the spectrum is being pushed because it is necessary to obtain enough power from silicon integrated devices to perform some useful function. The upper limit is set by the ability of the package to remove heat from the integrated device. There is a high power level at which the utility of integrated devices will be less than that of conventional component circuits. Thin film circuits have the ability to operate at higher temperatures and thus have more efficient heat transfer so more power can be handled.

Some of the attributes of silicon integrated devices are listed below. They apply primarily to the monolithic device rather than to the multichip structure which is sometimes also classified as an integrated silicon device.

- 1. Batch Processing—One important attribute of silicon integrated devices is that up to 400 devices are processed as a unit up to the stage where leads are attached and they are encapsulated. This allows a high degree of process control and device uniformity with relatively low unit cost.

- 2. Processing Simplicity—The number of processes which are involved in the fabrication of a silicon integrated device is very small when compared to the total number of separate processes required to fabricate the components of the conventional equivalent circuit.

- 3. Device Diversity—The identical processes can fabricate a variety of integrated devices by variation of the necessary photographic patterns.

- 4. Materials—In the silicon integrated device a small number of different materials are employed. For example, one class of

devices employs silicon, silicon oxide, aluminum and gold; no other materials are necessary. In other types of integrated devices, additional materials may be employed. They may be other conductors or contacting materials or a resistive metal employed for thin film resistors. Even with these, the number of different materials involved in the integrated device is small. This tends to promote high reliability.

- 5. Area Factor—The surface area of the single crystal silicon die on which the integrated device is fabricated is very important. It influences yield and thus cost, allowable power dissipation, required power to operate, package size, and functional capability. For a given structure the present lower limit on area may be set by dissipation, current carrying ability, capacitor and resistor parameters, or by resolution limits of the photoengraving process. For low power circuits the latter is most important since for a fixed resolution, the only tradeoffs are between component tolerances and circuit size.

- 6. Inverted Economics—Because of the greater area required for capacitors and resistors on silicon integrated devices, these components add more cost to the integrated devices than do transistors or diodes. This is the reverse of the situation for circuits designed with vacuum tubes and separate transistors. The inversion of relative cost of the active and passive circuit components will continue to have significant impact upon the design of integrated circuits.

#### SILICON INTEGRATED DEVICE TECHNOLOGY

The processing technology by which silicon integrated devices are realized varies little from one manufacturer to another. The details are different, however, and these details can be extremely important. In general a new fabrication facility will have a shakedown period before successful devices are produced. This period is spent adjusting processing methods and testing alternative methods to find a successful combination. The only criterion for success is the consistent production of good units. The major steps involved are:

- 1. substrate preparation 4. oxidation

- 2. photoengraving 5. epitaxy

- 3. diffusion 6. chemical processing

- 7. interconnection, lead attachment, and encapsulation.

#### Substrate Preparation

The substrate on which silicon integrated devices are formed is a wafer of single crystal silicon which may be between 0.7 and 1.5 inches in diameter. This circular wafer is cut from a single crystal

which is grown either by pulling the crystal from a melt or by the float-zone method. The former is characterized by a lower dislocation density while the latter is more free from dissolved impurities, primarily oxygen. In the usual fabrication facility, silicon wafers are obtained to a specification from a separate group which may or may not be part of the same company. Silicon wafers are difficult to specify because inadequate knowledge is available on what is really needed. Six of the properties which may be specified are

Base material type and impurity.—This is a gross specification indicating whether n- or p-type material is required. The particular impurities which are employed to dope the silicon have normally been boron or phosphorous, but other impurity dopants are available and are employed in particular applications. Although not normally specified, it is desirable that the silicon have a high resistivity before doping in order to minimize compensation effects.

Orientation.—Crystals sliced from a grown ingot normally have a specified crystalline orientation which may be confirmed by X-ray diffraction. The orientation is important for the dicing operation and for wafers on which epitaxial layers will be grown. Wafers with a <100> orientation have cleavage planes at a 90° angle; so when the wafers are scribed with a diamond tool and broken a high yield is obtained. In a <110> orientation the cleavage planes are at 60° angles and the yield is lower. The normal orientation tolerance is  $1.5^{\circ}$ .

Resistivity.—The resistivity may or may not be an important parameter, depending upon the particular design approach used for the integrated circuit. For epitaxial devices the substrate silicon material is a passive supporting structure, and its resistivity is relatively unimportant. However, if parts of the substrate are used in active structures of the integrated device, the resistivity is very important. The resistivity tolerance is affected not only by the accuracy of the doping and crystal growing procedures but also by the variation of resistivity along a diameter of a circular wafer, which results from temperature gradients existing in the growing process. Wafers with a 20 percent tolerance on the average resistivity can be obtained and a 10 percent tolerance on the variation of resistivity on a single wafer is realizable.

*Etch pit count.*—When a silicon wafer is etched, in a so-called preferential solution, pits are formed at the sites of crystalline dislocations. The density of these is employed as a measure of the crystal perfection and is sometimes specified. Float-zone crystals are characterized by a large dislocation density (up to 50 000/cm<sup>2</sup>) while some

suppliers of pulled crystals claim a zero etch pit count. A specification on pulled crystals of less than 1000 etch pit counts/cm<sup>2</sup> is readily obtainable. The dislocation density is important in its relation to device yield, particularly for epitaxial structures wherein the crystalline imperfections are propagated throughout the epitaxial layer.

Surface finish.—Silicon wafers may be purchased either as-cut from the ingot or with subsequent surface preparation steps already performed. The diamond slicing operation is followed by mechanical lapping and polishing. The final surface employed for the first wafer processing step may be either a mechanically polished surface with a mirror-like finish or a chemically polished surface. When a mechanically polished surface is used, it is assumed that in subsequent processing, the mechanical damage is removed either by oxidation or by gas etching in the epitaxial furnace. The chemically polished surface is not optically flat but is characterized by the so-called lemon peel undulation; this is sufficiently small so as not to interfere with the photoengraving process.

Dimensions.—Specification of dimensions is obvious. If the wafers are obtained with as-cut surfaces, then the thickness should be approximately twice that needed in the device processing in order to allow for polishing and lapping one surface of the wafer. An 8-10 mil thick wafer is used most often. This keeps breakage to a minimum and does not waste material. The diameter of the wafers is not critical unless limited by processing equipment. There is a trend toward wafers of greater than 1 inch diameter in order to have more devices processed on a wafer. The upper limit is set by crystal uniformity and allowed parameter spread.

Wafers with polished surfaces are ready for subsequent processing which will take one of several different paths. If an epitaxial layer is to be provided, the wafers are put into the epitaxial process directly. If dielectric isolation is to be provided then the actual substrate used in device fabrication involves considerably more processing before it is ready for use. If diffusion isolation is to be employed the wafers are put directly into the photoengraving, oxidation and diffusion steps.

The substrate preparation for dielectric isolation is rather complex as noted above. The first step is to etch into one side of the wafer a grid pattern several mils deep. After this the surface is oxidized, then a thick layer of polycrystalline silicon is deposited over the oxide by pyrolytic deposition processing similar to that used in epitaxy. This layer must have sufficient thickness to provide mechanical support for the final structure. After deposition, part of the original silicon wafer material is removed by a combination of mechanical polishing and etching so that a grid pattern of oxide is

exposed on the surface. This surface of the silicon wafer then consists of a large number of single crystal silicon squares completely isolated from each other and from the substrate by the silicon oxide layer. This wafer is then ready for further processing.

#### Photoengraving

The techniques of photoengraving are necessary for planar processes and interconnections in silicon integrated device technology. The photoengraving masks which give the geometry definition on the silicon wafer are obtainable from commercial organizations or may be made in-house if the necessary equipment is available. This includes high resolution photographic and photoreduction equipment, step and repeat camera, and precision drafting equipment. Using these and the circuit topology layout provided by the design engineer, a series of photographic masks are prepared which define the areas for diffusion, contacts, or for interconnection patterns.

Wafer cleanliness to the point of obsession is extremely important for the photoengraving process but the means for achieving it will not be discussed here. Normally the photoresist is placed on a wafer by an eye dropper or similar dispensing apparatus while the wafer is spinning at high speed on a vacuum chuck. After the photoresist is allowed to air dry, it is usually baked at a low temperature before the printing operation. The patterns are aligned under a microscope. All masks after the first must align with the existing patterns on the wafer to high degrees of accuracy. Commercial apparatus is available which allows this to be done. All photoresist operations up to this step must be performed in yellow red (non-blue) light in order to avoid exposure of the resist. After alignment, the wafer with the mask tightly pressed against its surface is exposed to light with a high ultraviolet content. This changes the polymerization of the resist. The wafers are developed in proprietary developing solutions or xylene and dried. Then the wafers are baked in a vacuum oven in order to harden the remaining resist and improve its acid resistance. This pattern is then etched through the silicon oxide so that a suitable pattern of openings exists through which diffusing impurities will pass. In forming contact or interconnection patterns of metal, it is most common to use a reverse process wherein the unwanted metal is removed from the surface leaving behind the desired pattern. After the resist is used for the etching operation, it is then removed from the surface before subsequent silicon processing. This is a very difficult operation; one method is to heat the wafer in hot sulfuric acid for a short period of time.

The most common resists for the photoengraving operation are Kodak Photoresist (KPR) and Kodak Metal Etch Resist (KMER).

<sup>785-727 0-65-----3</sup>

Other resists are available which have valuable application for particular processes. An example is the AZ resists made by the Shipley Company (popularly known as Positop). Each group uses the one it happens to have the best success with.

The state-of-the-art of photoengraving is such that it is an inexact science. There is much to learn about all the steps required in obtaining patterns with the desired qualities. At the same time it is apparent that photoengraving techniques have been very successful in both the integrated silicon device technology and in the fabrication of silicon transistors. Photoengraving has been proven far superior to other techniques for obtaining close geometry control in very intricate patterns. The main problems associated with photoengraving are that the quality of the resist is variable, the optimum processing steps are poorly defined, better resolutions are desirable, mask making is expensive, and surface preparation and printing techniques need further development. With experience the photoengraving process is gradually coming under better control and if research is performed in some of the specific areas mentioned, it is only a matter of timeuntil improvements are found.

#### Diffusion

Impurity diffusion is another one of the basic tools of silicon integrated device technology. It consists of a mixture of science and art as do the other basic processes. While mathematical theories describing simple kinds of diffusion are known, the diffusions are performed on the basis of empirically determined methods. As with photoengraving, wide variations may be found in the details of the diffusion processes at different integrated circuit facilities. These variations include the use of different types of impurity sources, different diffusion procedures and different degrees of control. The basic process requires a suitable impurity (dopant) source, almost always either a phosphorus or boron compound. The dopant is transported in vapor form by a carrier gas, usually nitrogen, over the silicon wafers and then discharged. The entire system is contained in a glass or quartz tubing depending on the temperature. The silicon wafers rest on a quartz boat at a thermally flat region of the furnace which is held very precisely at a specified temperature. Diffusion temperatures range from 900° C to 1200° C. Typical impurity sources for phosphorus are phosphorus pentoxide, phosphorus oxychloride, red phosphorus, ammonium phosphate, phosphorus tribromide, and phosphine. For boron, typical impurity sources are boric acid, boron tribromide, methyl borate, boron trichloride, and diborane. The liquid sources, phosphorus oxychloride and boron tribromide, are the most common.

There is some evidence that the gas sources, phosphine  $(PH_3)$  and diborane can be used to more advantage.

Diffusion furnaces may be purchased from a number of commercial suppliers. The control of these furnaces and their design has improved a great deal over the last several years. Thermal flat zones held to  $\pm 1^{\circ}$  C or less at a temperature of about 1100° C may be as long as 18 inches. Two zone furnaces are available if required for particular impurity sources. Quartz tubing and quartz boats for holding the wafers during diffusion are commercially available. Flow meters, gas handling equipment and all other necessary accessories for diffusion are well known.

By following any of the prescribed processes, acceptable diffusion results can be obtained. Normally the diffusion parameters are varied by changing the temperature of the furnace. As silicon integrated device technology becomes more sophisticated, a higher degree of control than is now possible will probably be required. Some of the inadequacies which exist in diffusion technology are: (1) agreement between theory and practice is difficult to obtain, (2) data describing diffusion processes vary a great deal between laboratories due to the use of different models, (3) present diffusion operations are largely empirical and many of the second order effects are not understood. For example, the interaction between oxidation and diffusion and data on the dependence of the diffusion coefficients on concentration are not available.

In summary the present techniques of diffusion are sufficiently well developed so as to be no problem for most contemporary silicon integrated devices. However, better control and understanding is desirable in order to make devices which are more exactly alike and whose characteristics can be predicted more accurately.

#### Oxidation

The ability of the thermally grown oxide on the surface of the silicon wafer to mask against impurity diffusions and to protect the junction from the environment is very important in planar silicon technology and thus to silicon integrated device technology. Everyone who has inspected surfaces covered with these oxides is familiar with the clear interference colors they cause. The clarity of the color, however, exceeds the clarity of our understanding of the properties of the oxide. Examine the requirements for the oxide in the silicon integrated device structure:

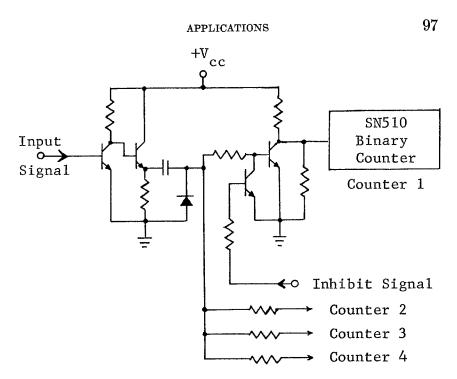

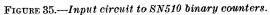

- 1. It is first used as a diffusion mask which process inherently contaminates it with impurity (dopant).