# Models, Algorithms and Architectures for Reconfigurable Computing

DARPA Contract No.: DABT63-96-C-0049

Final Technical Report

## Submitted by:

Principal Investigator: Viktor K. Prasanna

Department of Electrical Engineering-Systems

University of Southern California

Los Angeles, CA 90089-2562.

Ph: (213) 740-4483, Fax: (213) 740-4418

prasanna@usc.edu

Subcontractor: Krishna Palem ReaCT-ILP Laboratory New York University palem@cs.nyu.edu

20000313 082

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |                                                            | Form Approved<br>OMB No. 0704-0188                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                               |                                                            |                                                                     |  |  |

| AGENCY USE ONLY (Leave<br>Blank)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2. REPORT DATE<br>03/06/2000                                                                  | REPORT TYPE AND DATES COVERED     Technical Report - Final |                                                                     |  |  |

| and the second s |                                                                                               |                                                            | 5. FUNDING NUMBERS DARPA Contract Number: DABT63-96-C-0049          |  |  |

| 6. AUTHORS<br>Viktor K. Prasanna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               |                                                            |                                                                     |  |  |

| 7. PERFORMING ORGANIZATION N<br>University of Southern California<br>Departments of Contracts and Gra<br>University Park<br>Los Angeles, CA 90089-1147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8. PERFORMING ORGANIZATION REPORT NUMBER                                                      |                                                            |                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                            | 10. SPONSORING / MONITORING AGENCY<br>REPORT NUMBER                 |  |  |

| 11. SUPPLEMENTARY NOTES None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                            |                                                                     |  |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT DISTRIBUTION UNLIMITED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               |                                                            | 12b. DISTRIBUTION CODE                                              |  |  |

| The Models, Algorithms, and Architectures for Reconfigurable Computing (MAARC) project developed a sound framework for algorithmic configurable computing and for exploiting this technology for embedded signal and image processing applications. Fundamental configurable computing models and performance metrics were developed to evaluate the scalability of configurable hardware. The developed models and the performance metrics were utilized to analyze dynamic reconfiguration and design model based algorithm mapping techniques for signal processing applications. Mapping techniques were developed to identify the core computational kernels of signal processing applications and map them onto configurable hardware. The mapping techniques are efficient and yield significant performance speed-ups and logic utilization. An interpretive simulation framework was proposed to analyze and visualize dynamic reconfiguration and the proposed mapping techniques. A prototype of the framework, Dynamically Reconfigurable Systems Interpretive Simulation and Visualization Environment (DRIVE) was developed and demonstrated. A model based compiler framework and compiler optimization technologies were designed targeting reconfigurable platforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                               |                                                            |                                                                     |  |  |

| <ol> <li>SUBJECT TERMS         Reconfigurable Computing, Modeling, FPGA, Hybrid Architectures, HySAM Model, Mapping Technique Algorithm Synthesis, String Matching, FFT, DCT, Model-based ATR.     </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                               |                                                            | iques, 15. NUMBER OF PAGES 451 16. PRICE CODE                       |  |  |

| 17. SECURITY CLASSIFICATION<br>OF REPORT<br>UNCLASSIFIED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CATION 18. SECURITY CLASSIFICATION 19. SECURITY CLASSIF OF ABSTRACT UNCLASSIFIED UNCLASSIFIED |                                                            | IFICATION 20. LIMITATION OF ABSTRACT UNCLASSIFIED                   |  |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                               |                                                            | Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. Z39-1 298-102 |  |  |

### **Contents**

### I USC Efforts

## 1 Summary of Accomplishments

- 1.1 Models for Configurable Computing

- 1.2 Performance Metrics for Evaluating Configurable Systems

- 1.3 Algorithmic Techniques

- 1.3.1 Algorithm Specialization

- 1.3.2 Mapping onto Coarse Grained Configurable Architectures

- 1.3.3 Mapping Computations onto Hybrid Reconfigurable Architectures

- 1.3.4 Dynamic Precision Computations

- 1.3.5 String Matching and Genetic Programming

- 1.3.6 Instance-dependent Mapping Techniques

- 1.3.7 Model-based ATR on Configurable Hardware

- 1.3.8 Mapping Irregular Applications onto Configurable Hardware

- 1.4 DRIVE Software

- 2 References

- 3 Copies of Reports/Publications

- 4 DRIVE Software Source Listing

- 5 Final Review Presentation Slides

## II NYU Efforts

## 1 Summary of Accomplishments

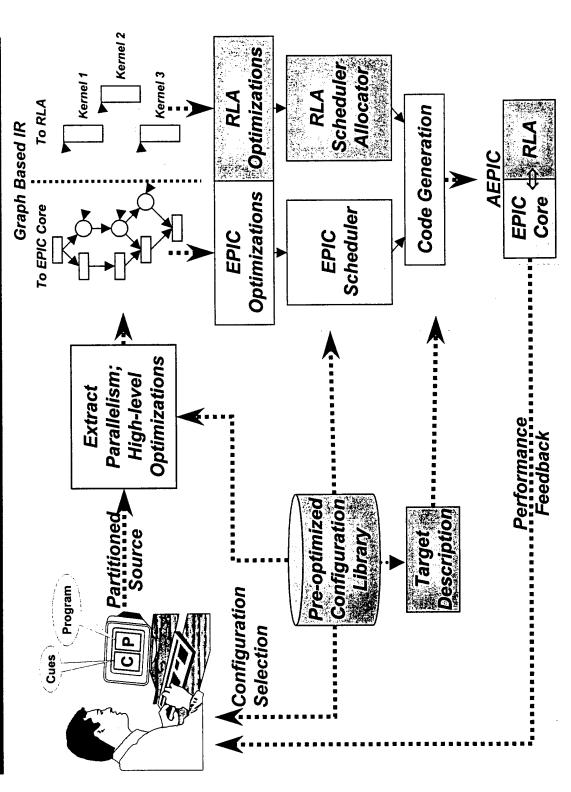

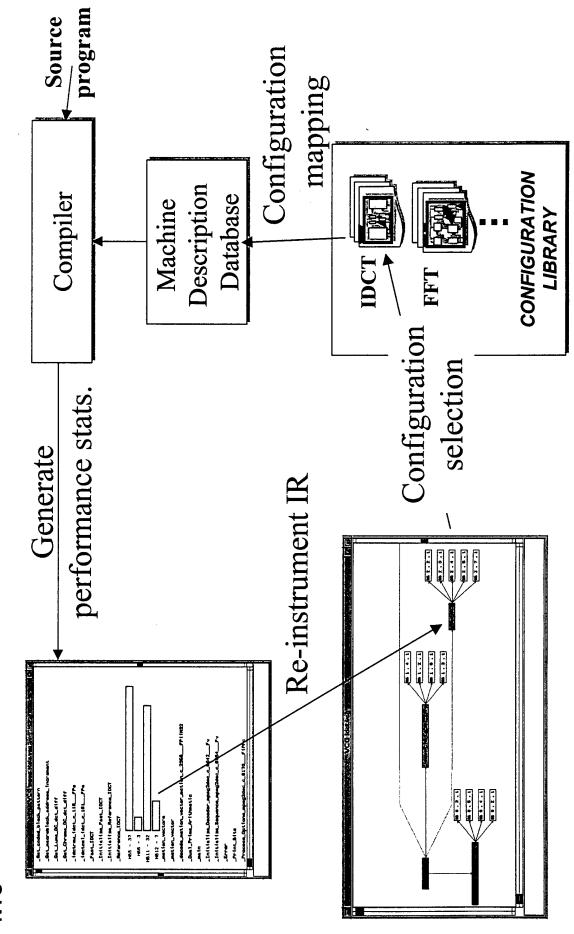

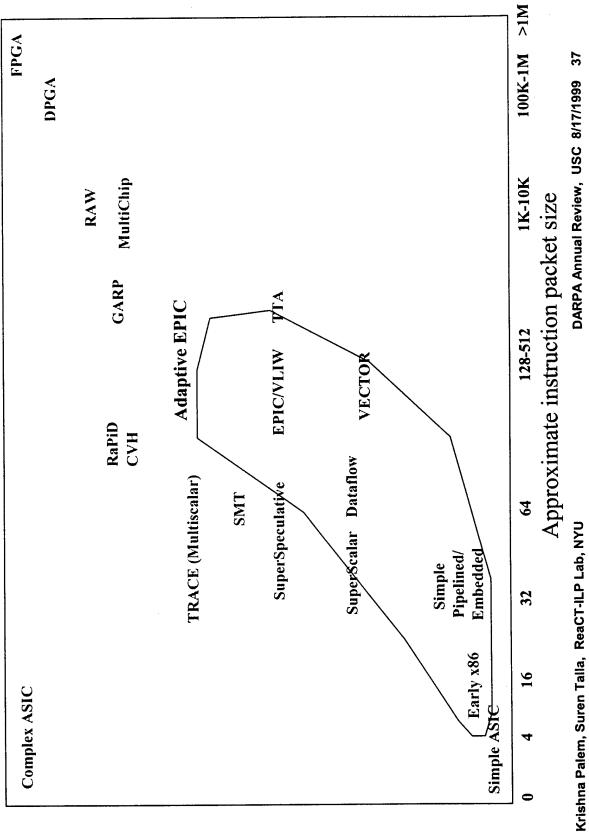

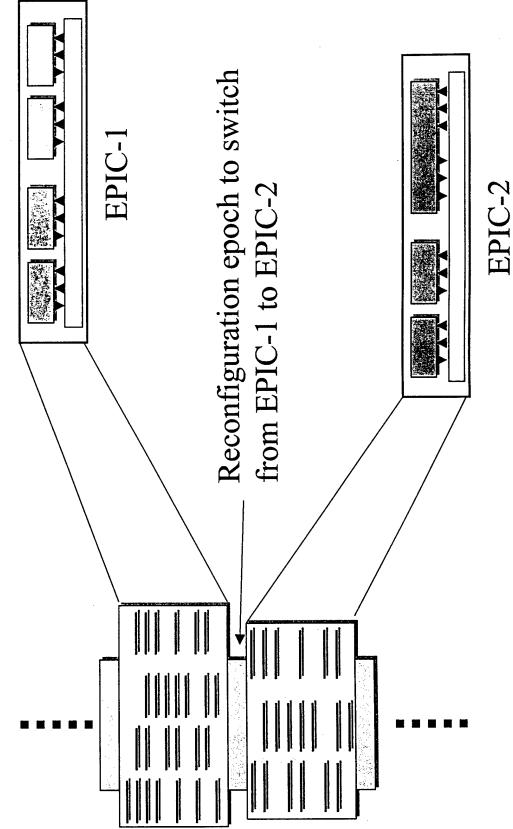

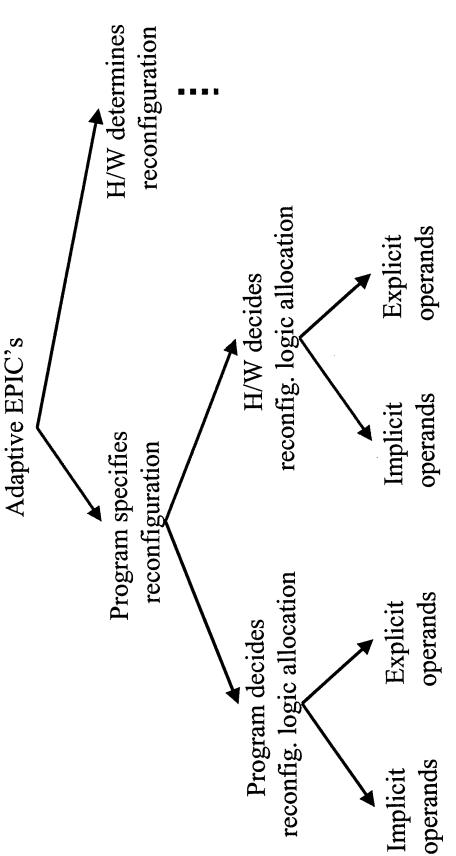

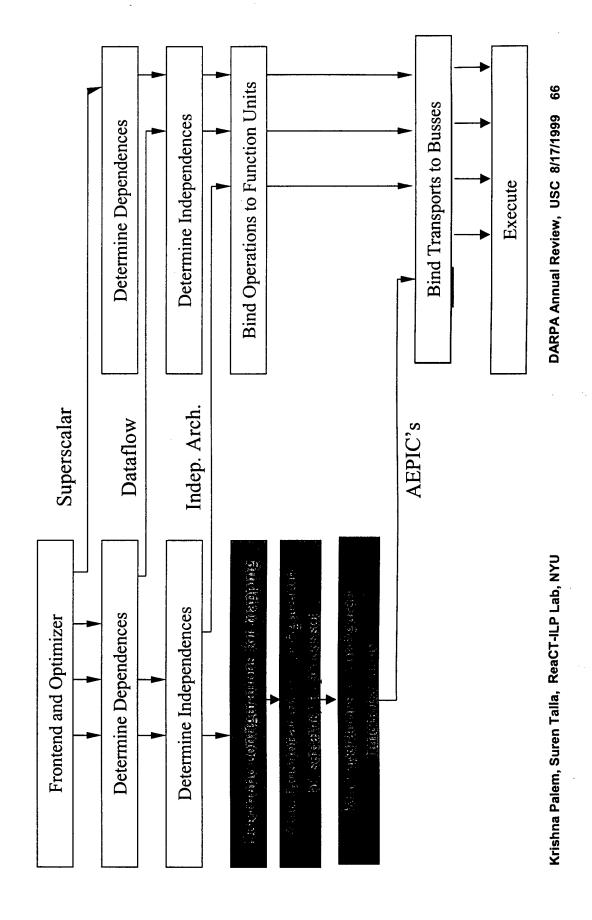

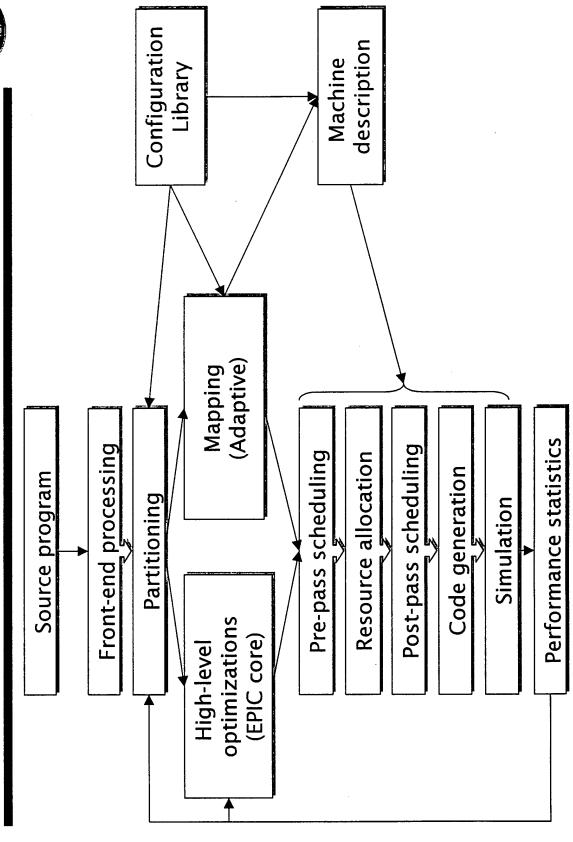

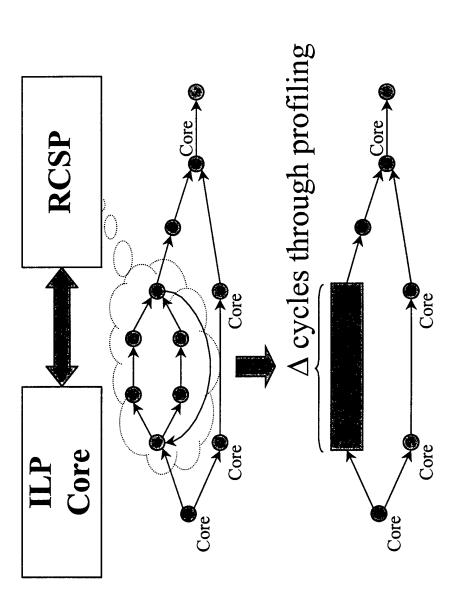

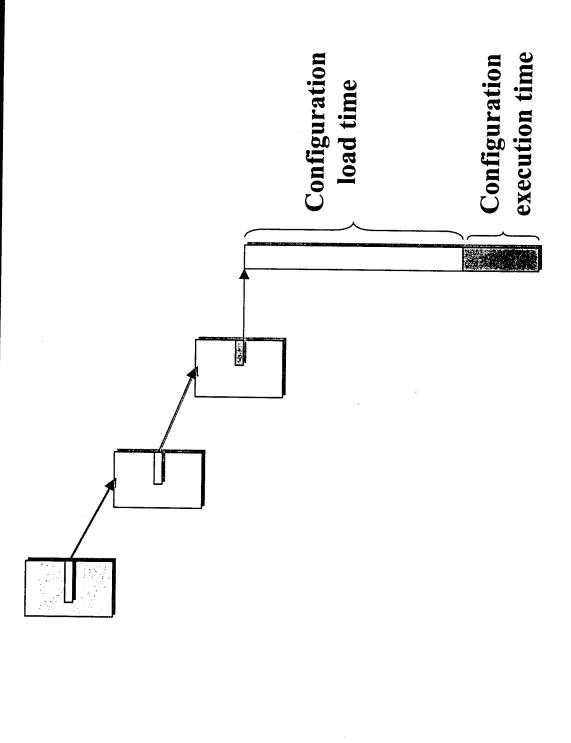

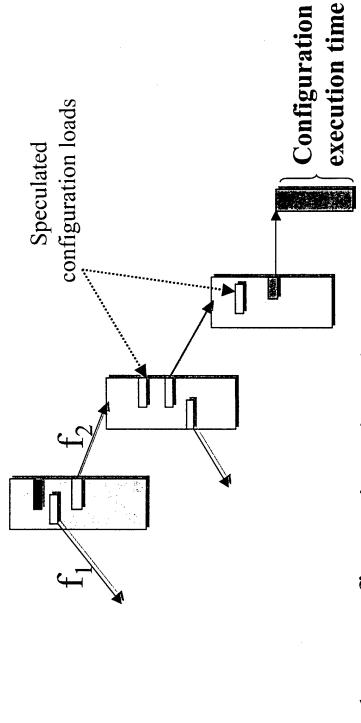

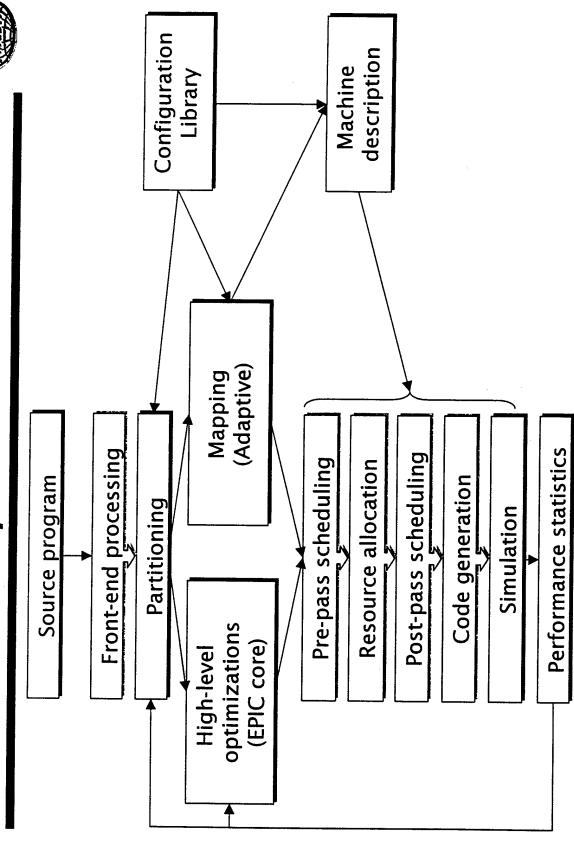

- 1.1 Model for Compilation onto Adaptive Systems

- 1.2 Compilation Framework

- 1.3 Compilation Techniques

- 2 Final Review Presentation Slides

### Abstract

The MAARC project developed a sound framework for algorithmic configurable computing and for exploiting this technology for embedded signal and image processing applications. The project was executed by the MAARC research group at USC in collaboration with the ReaCT-ILP lab at New York University. The USC efforts developed fundamental configurable computing models and performance metrics to evaluate the scalability of configurable hardware. The developed models and the performance metrics were utilized to analyze dynamic reconfiguration and design model based algorithm mapping techniques for signal processing applications. Mapping techniques were developed to identify the core computational kernels of signal processing applications and map them onto configurable hardware. The mapping techniques are efficient and yield significant performance speedups and logic utilization. An interpretive simulation framework was proposed to analyze and visualize dynamic reconfiguration and the proposed mapping techniques. A prototype of the framework, Dynamically Reconfigurable Systems Interpretive Simulation and Visualization Environment (DRIVE) was developed and demonstrated. As part of the collaborative effort the NYU group designed a model based compiler framework and compiler optimization technologies targeting reconfigurable platforms. This report summarizes the accomplishments of these efforts and the details are provided in the manuscripts submitted as part of the report. The first part of the report describes the accomplishments by the USC MAARC group and the second part describes the accomplishments of the NYU ReaCT-ILP group.

# Part I USC Efforts

# 1 Summary of Accomplishments

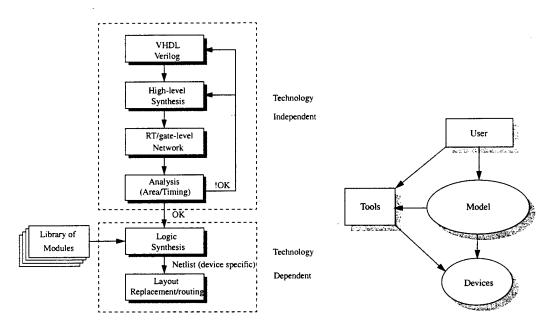

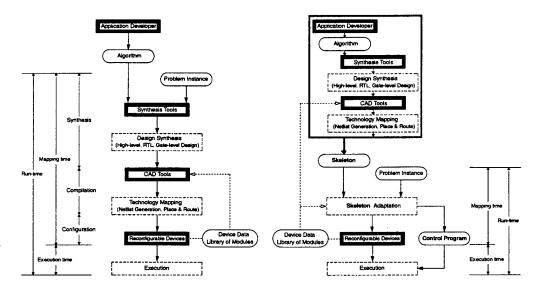

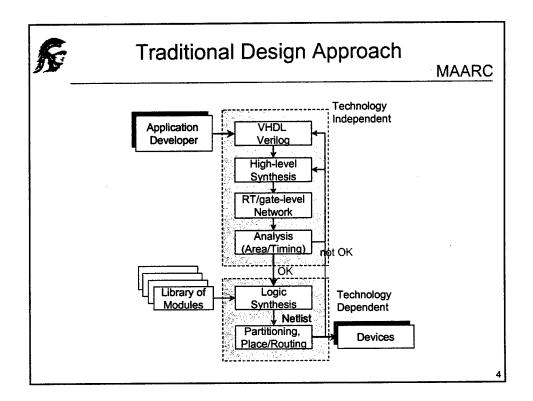

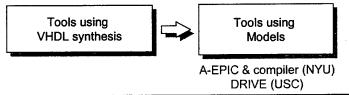

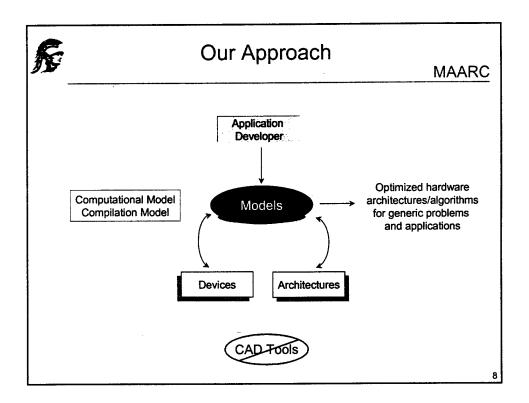

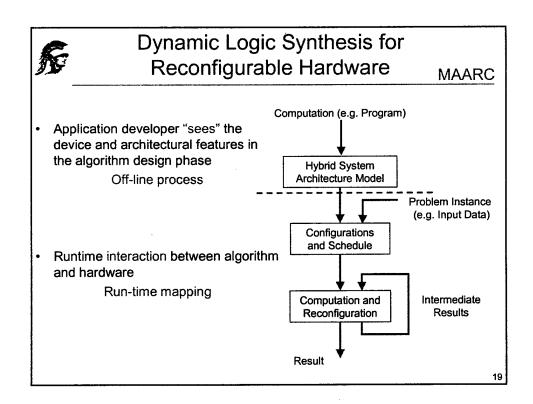

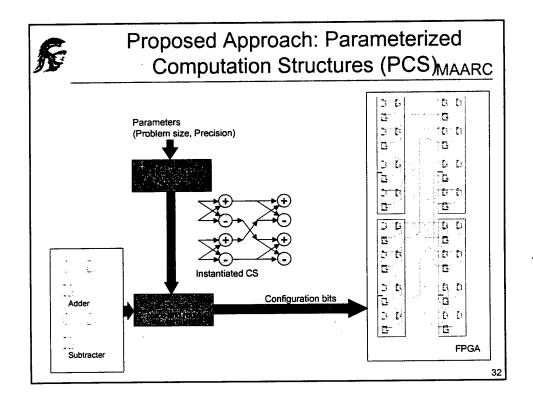

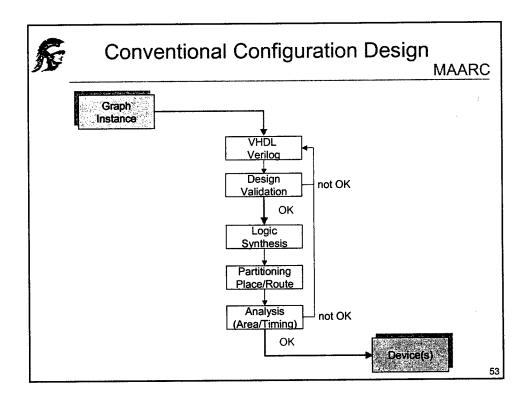

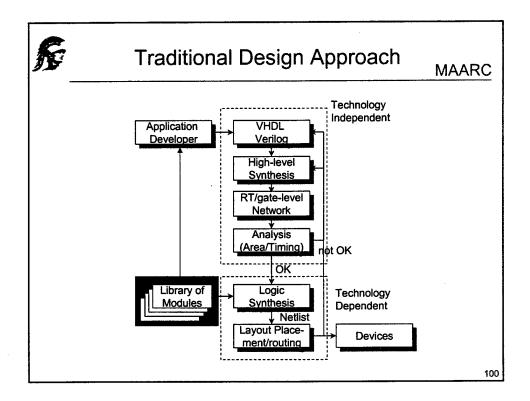

## 1.1 Models for Configurable Computing

One major problem in using FPGAs to speed-up a computation is the design process. The "standard CAD approach" used for digital design is typically employed. The required functionality is specified at a high level of abstraction via an HDL or a schematic. FPGA libraries specific to a given device (e.g. Xilinx, Altera, etc.) and time consuming placement and routing steps are required to perform the logic mapping. This approach of *logic synthesis* as opposed to algorithm synthesis allows the user to specify the design using a behavioral model. But this abstraction is achieved at the expense of performance. The semantics and nature of the algorithm are lost in the mapping phases.

The model based mapping environment takes into account the capabilities and limitations of current as well as projected hardware technologies. In this effort parameterized models for algorithm design and analysis have been developed which possess the following characteristics:

- Cost models for analysis of reconfigurable architectures.

- Techniques for partitioning and placement of designs exploiting algorithm and input structure.

- Cost analysis incorporating the cost of reconfiguration and partial and dynamic reconfigurability.

- Impact of off-chip communication in designing reconfigurable computing solutions.

- Tradeoffs between reconfigurability and redundancy of hardware.

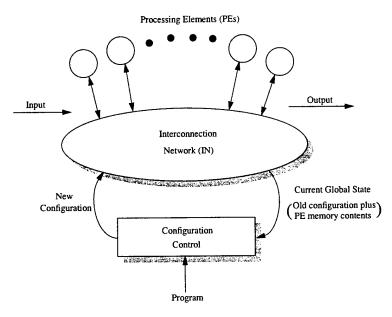

A Configurable Linear Array model of coarse grained architectures has been developed. The model consists of identical powerful PEs, where the datapaths as well as the functionality of the PEs can be dynamically configured. I/O is performed only at the boundaries which limits the required memory bandwidth. The model has been utilized to map homogeneous computations onto coarse grained architectures [9].

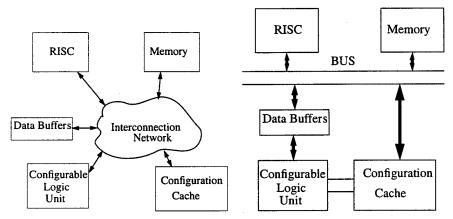

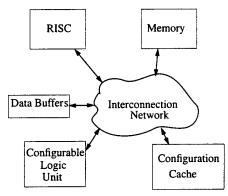

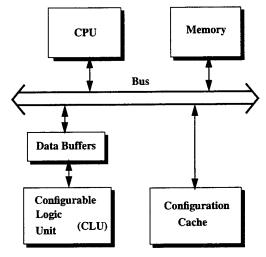

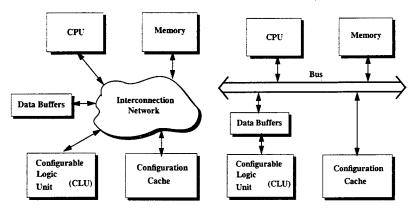

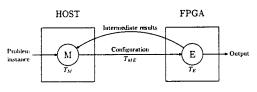

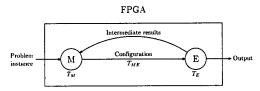

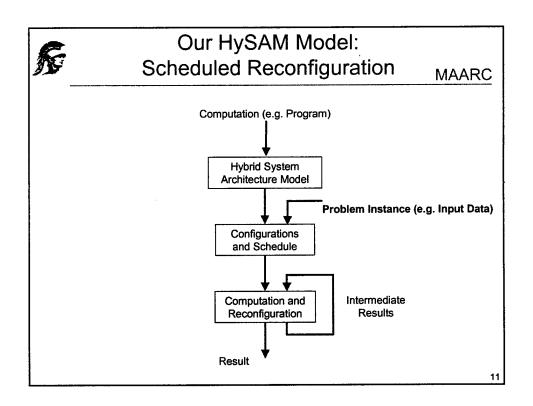

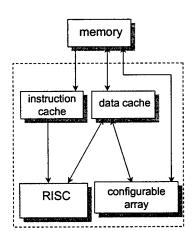

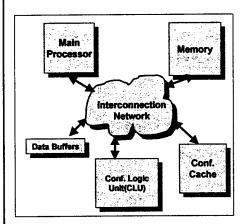

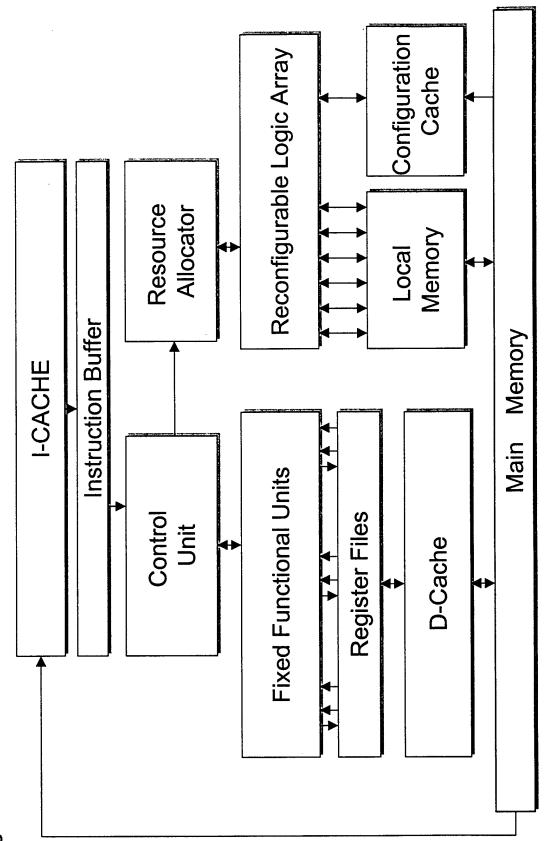

Hybrid System Architecture Model (HySAM), a parameterized model of reconfigurable architectures has been developed. The model encompasses systems with configurable logic attached to a traditional microprocessor. HySAM is a compilation model and facilitates

development of architecture independent mapping algorithms. The model has been utilized to develop mapping algorithms for various problems [1, 2, 3].

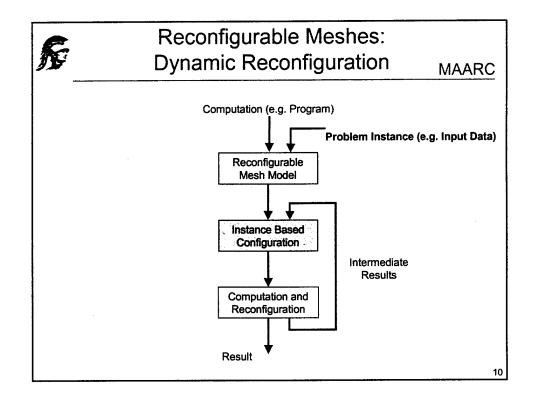

## 1.2 Performance Metrics for Evaluating Configurable Systems

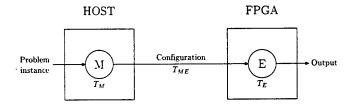

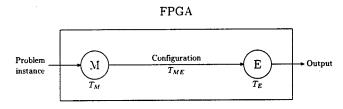

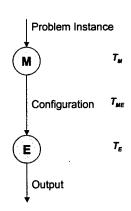

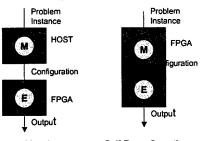

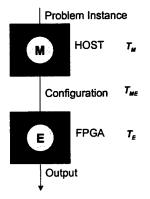

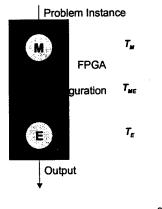

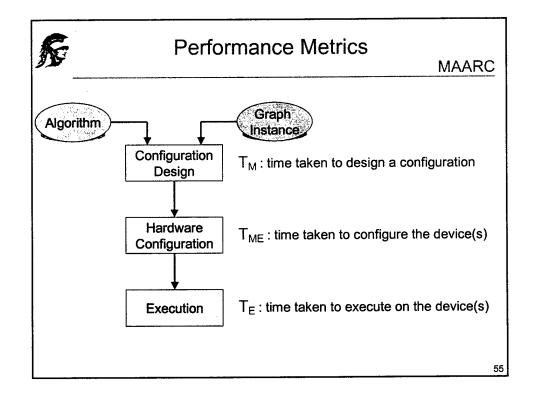

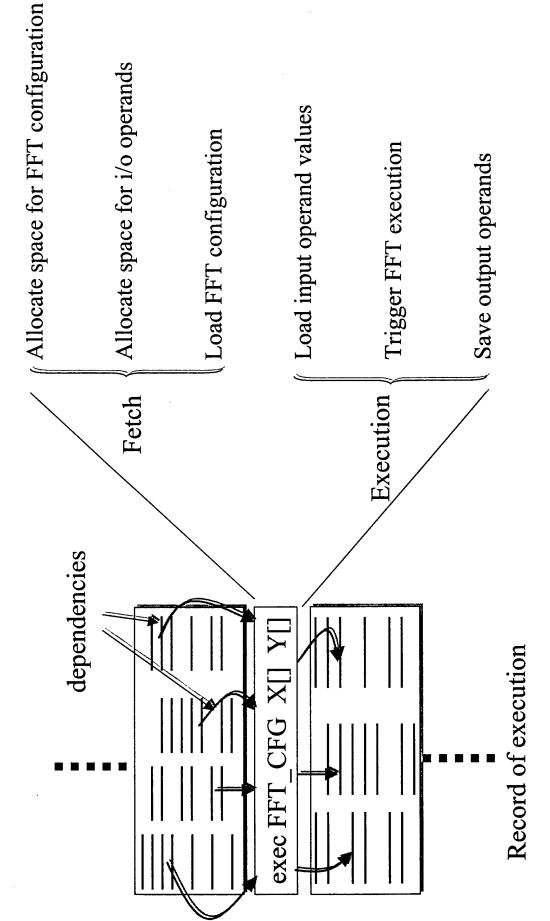

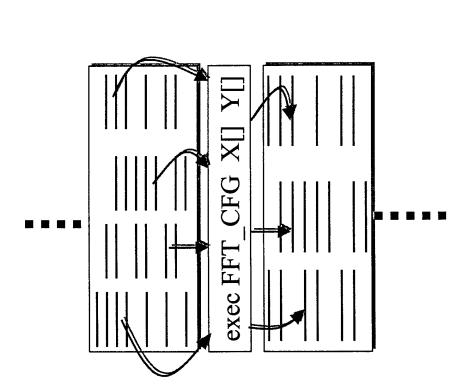

A configurable computing solution can be based on generic implementation of the problem in a HDL. But for efficient designs, the nature of the algorithm and the specific input have to be exploited. In designing such configurations, the mapping from a specific instance to actual configuration plays an important role. A configurable computing solution has three components:

- 1. Design compilation to generate the configurations.

- 2. Configuring the logic on the device.

- 3. Execution of the computation tasks on the configured hardware.

The performance of the configurable computing solution can be measured by the total time:

$$T = T_d + T_c + T_e$$

$T_d$ ,  $T_c$  and  $T_e$  correspond to the three steps mentioned above.  $T_d$  is the design time,  $T_c$  is the configuration time (including the reconfiguration time), and  $T_e$  is the actual execution time on configurable logic.

The design time,  $T_d$ , is the time needed to map a description of the design in a HDL to low level netlist format by using various high level synthesis tools and technology mapping tools. In current configurable computing designs the design time,  $T_d$ , varies anywhere from hours to weeks of computation time on a traditional workstation. The configuration time,  $T_c$ , varies from milli-seconds to seconds. The execution time,  $T_e$ , varies from nano-seconds to milli-seconds for typical tasks. The execution time in hardware (once the hardware is configured) is usually much lower than that in software because of hardware efficiency. To obtain high performance, techniques are being developed to exploit the structure in the input instance. In such cases, the configurations are generated for each input instance.

The total time to compute a solution has to include the time elapsed from the time the input data is submitted to the time all the the outputs are obtained. This total latency is the metric used in traditional performance measures. But, existing framework takes into account only the actual execution time,  $T_e$ , of the developed design in evaluating the performance of the design. It is incorrect to compare only the execution time, especially

when the design compilation time is many orders of magnitude greater than the execution time (typical designs take hours to weeks on workstations to compile). In this effort the performance comparison was based on the total time elapsed rather than just the execution time.

## 1.3 Algorithmic Techniques

### 1.3.1 Algorithm Specialization

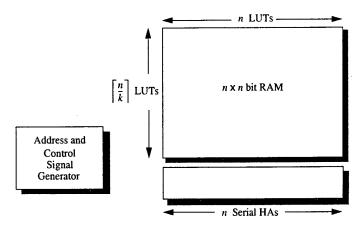

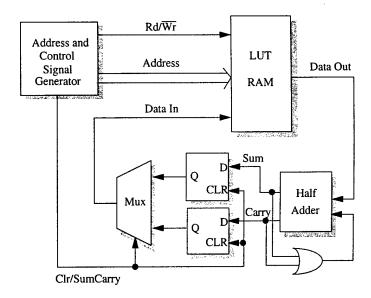

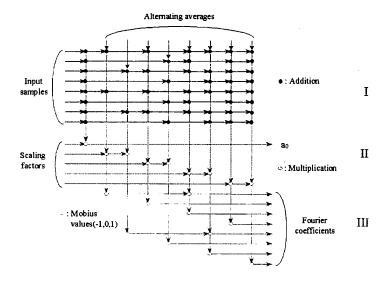

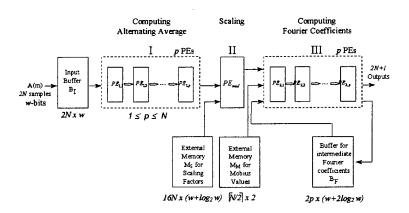

Configurable architectures have architectural characteristics different from traditional computing architectures. It is necessary to explore the space of algorithms for a given problem to map onto configurable architectures. This effort proposed a fast parallel implementation of Discrete Fourier Transform (DFT) using FPGAs. The design is based on the Arithmetic Fourier Transform (AFT) using zero-order interpolation. For a given problem of size N, AFT requires only  $O(N^2)$  additions and O(N) real multiplications with constant factors. The design employs 2p+1 PEs  $(1 \le p \le N)$ , O(N) memory and fixed I/O with the host. It is scalable over p  $(1 \le p \le N)$  and can solve larger problems with the same hardware by increasing the memory. All the PEs have fixed architecture. The proposed implementation is faster than most standard DSP designs for FFT. It also outperforms other FPGA-based implementations for FFT, in terms of speed and adaptability to larger problems [8].

### 1.3.2 Mapping onto Coarse Grained Configurable Architectures

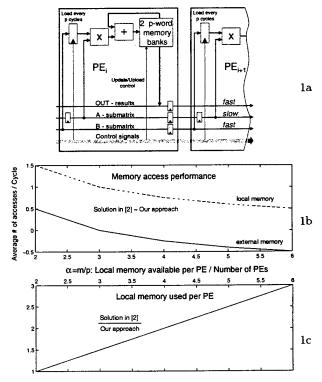

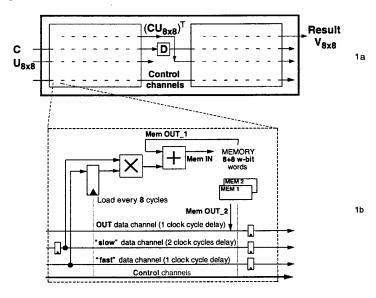

Some configurable architectures address the problem of reconfiguration cost by using coarse grain reconfigurable logic blocks. This reduces the flexibility but also significantly decreases the reconfiguration cost. This effort developed an efficient design for 2D-DCT on dynamically configurable coarse grained architectures. A novel technique for deriving computation structures for two dimensional homogeneous computations was developed. In this technique, the speed of the data channels is dynamically controlled to perform the desired computation as the data flows along the array. This results in a space efficient design for 2D-DCT that fully utilizes the available computational resources. Compared with the state-of-the-art designs, the amount of local memory required is reduced by 33% while achieving the same high throughput [9].

### 1.3.3 Mapping Computations onto Hybrid Reconfigurable Architectures

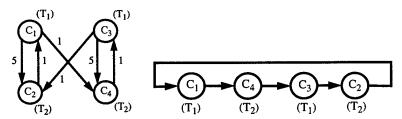

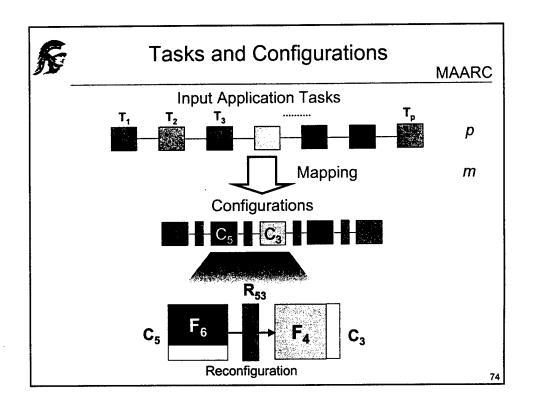

Loop statements in traditional programs consist of regular, repetitive computations which are the most likely candidates for performance enhancement using configurable hardware.

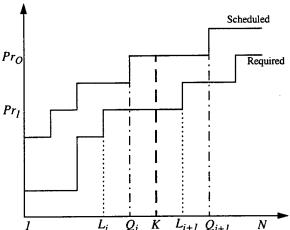

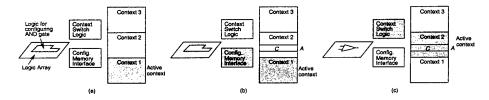

This effort developed a formal methodology for mapping loops onto reconfigurable architectures. The HySAM parameterized abstract model of reconfigurable architectures developed in this effort (see Section 1.1) is used to define and solve the problem of mapping loop statements onto reconfigurable architectures. A polynomial time algorithm was developed to compute the optimal sequence of configurations for one important variant of the problem [2]. These techniques were also utilized to develop algorithms for mapping loop computations onto multi-context devices [4].

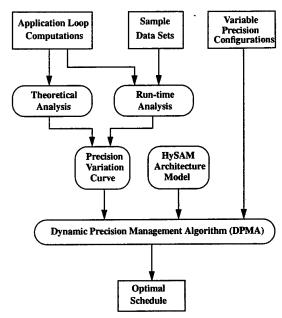

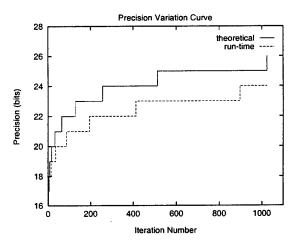

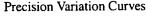

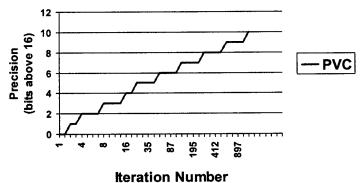

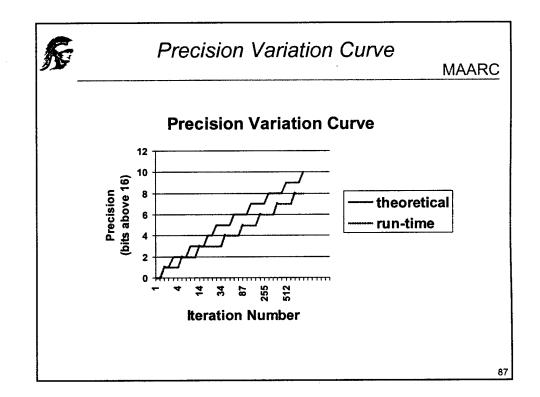

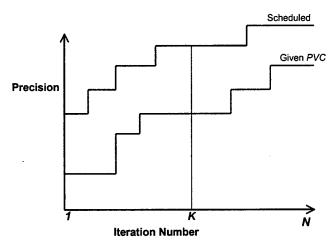

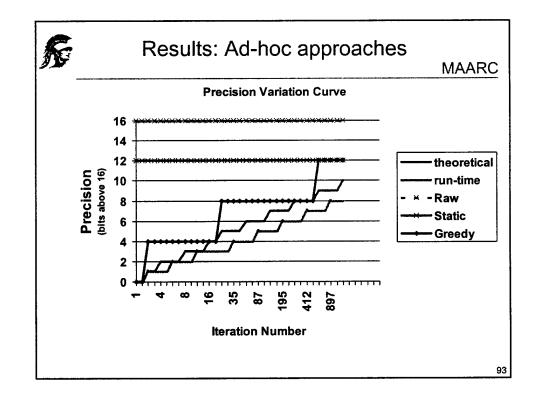

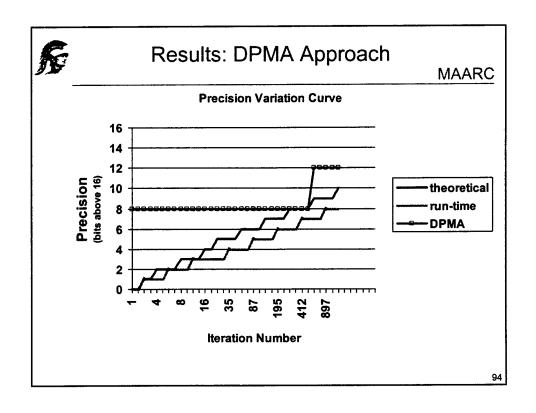

### 1.3.4 Dynamic Precision Computations

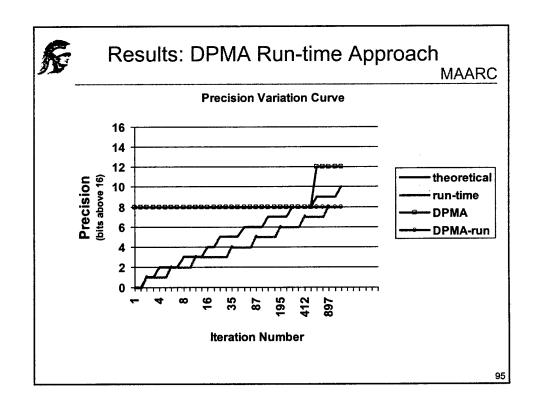

Reconfigurable architectures promise significant performance benefits by customizing the configurations to suit the computations. Variable precision for computations is one important method of customization for which reconfigurable architectures are well suited. This effort developed a formal methodology to manage the variable precision computations. For managing dynamic precision in loop computations, intelligent choices on the use of appropriate modules from the available set of modules with different precision need to be made. These configurations then have to be scheduled to achieve optimal execution schedule. An optimal schedule is based on the metrics defined in Section 1.2. Exploiting dynamic precision using the proposed Dynamic Precision Management Algorithm (DPMA) resulted in a 33% reduction in the computation of a multiplication operation on Xilinx FPGA architecture [3] (see Table 1).

| Algorithm | Execution   | Reconfiguration | Total  |

|-----------|-------------|-----------------|--------|

|           | Time $(ns)$ | Time $(ns)$     | (ns)   |

| Standard  | 655360      | 20480           | 675840 |

| Static    | 532480      | 17920           | 550400 |

| Greedy    | 468010      | 56320           | 524330 |

| DPMA      | 471160      | 33280           | 504440 |

| DPMA-run  | 409600      | 15360           | 424960 |

Table 1: Execution times using various approaches

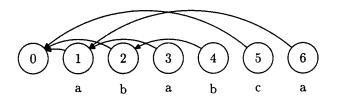

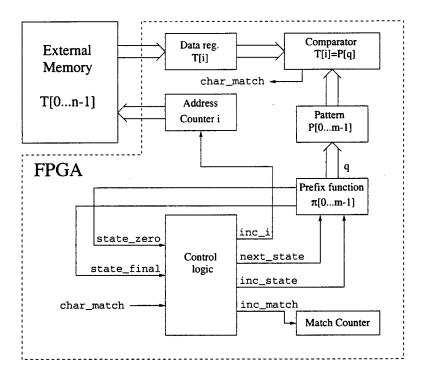

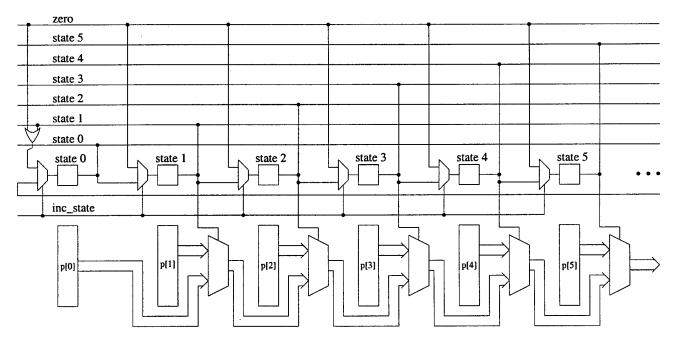

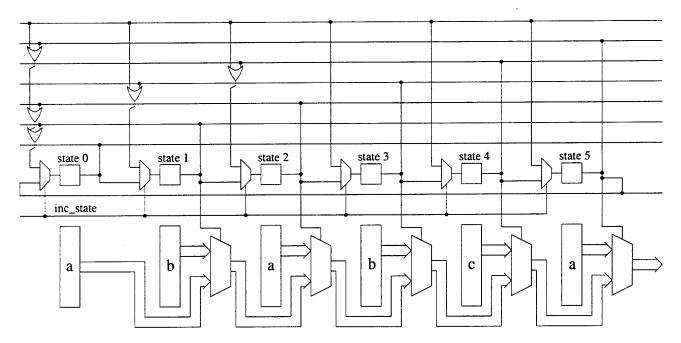

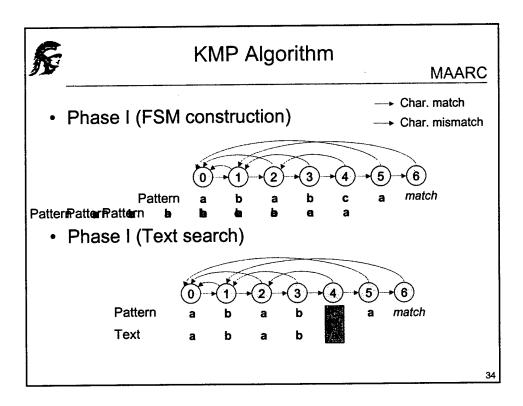

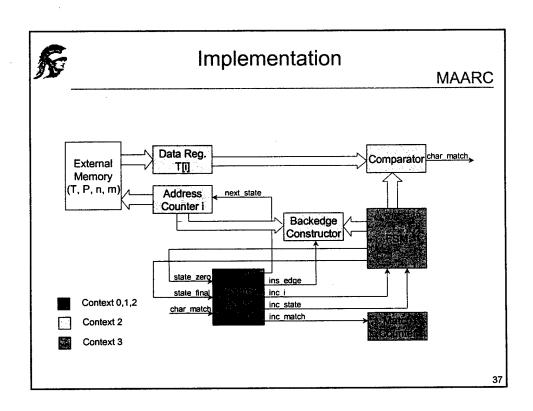

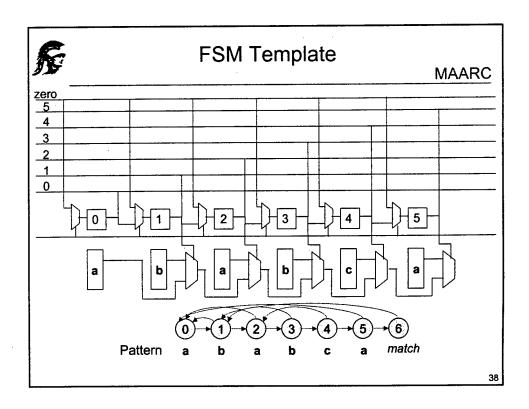

#### 1.3.5 String Matching and Genetic Programming

An efficient design for string matching on multi-context FPGAs was derived. A novel technique for deriving data-dependent configurations was demonstrated. Based on this, speedups of the order of 10<sup>6</sup> over the conventional CAD tools design flow were obtained

(including both the mapping time and the execution time on hardware) [11]. The speed-up obtained using the multi-context FPGA is illustrated in Table 2.

| Approach          | $T_d + T_c + T_e$ |            |            | Speedup        |                |                |

|-------------------|-------------------|------------|------------|----------------|----------------|----------------|

|                   | $n = 10^4$        | $n = 10^5$ | $n = 10^6$ | $n = 10^4$     | $n = 10^5$     | $n = 10^6$     |

| Multicontext FPGA | 1.8 ms            | 18.3 ms    | 183.1 ms   | 1.0            | 1.0            | 1.0            |

| CAD tool mapping  | 76.0 s            | 76.0 s     | 76.2 s     | $\approx 10^5$ | $\approx 10^4$ | $\approx 10^3$ |

| Software mapping  | 21.8 ms           | 39.3 ms    | 204.1 ms   | 12.1           | 2.1            | 1.1            |

| Sun Ultra 1       | 30 ms             | 80 ms      | 680 ms     | 16.6           | 4.4            | 3.7            |

Table 2: Speedups for string matching different string sizes, n

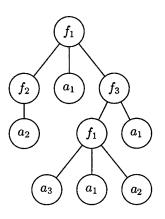

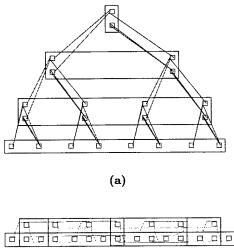

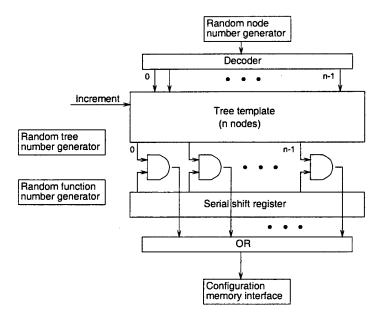

The solution to string matching was extended to the area of genetic programming (GP). A fast, compact representation of the tree structures in FPGA logic was developed which can be evolved as well as executed without external intervention. The tree representation permits execution of all tree nodes in a parallel, pipelined fashion. Furthermore, the compact layout enables multiple trees to execute concurrently, dramatically speeding up the fitness evaluation phase. Compared with software implementations, a speedup of 19 for an arithmetic intensive problem and a speedup of almost three orders of magnitude for a logic operation intensive problem were achieved by implementations on a XC6264 FPGA device [10].

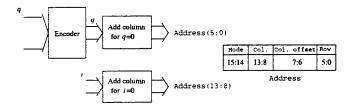

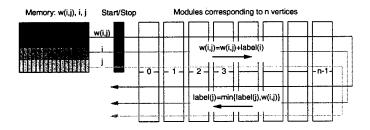

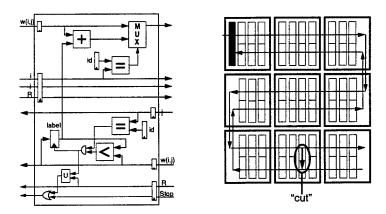

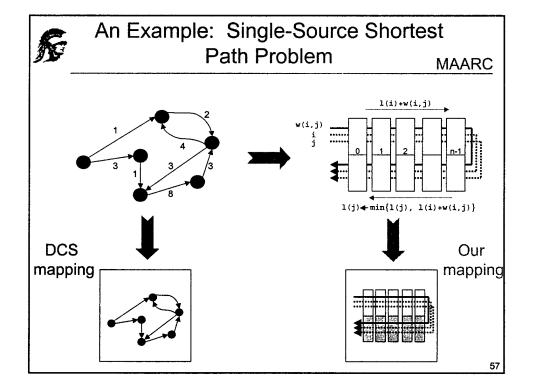

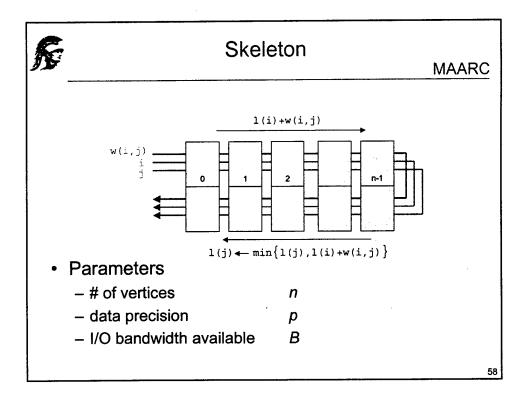

### 1.3.6 Instance-dependent Mapping Techniques

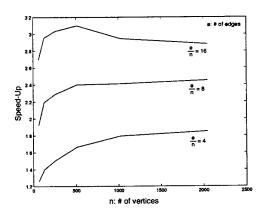

Configurable architectures can achieve performance improvement compared to ASICs by exploiting the structure in the algorithm and the input. Developing designs based on the structure of the input is Instance-dependent mapping. Mapping techniques for such an approach were developed and utilized in mapping graph problems to configurable hardware. High-level designs are synthesized for graph problems and adapted to the input graph instance at run-time. The proposed approach leads to reconfigurable solutions with superior time performance. The time performance metric includes both the mapping time and the execution time as defined in Section 1.2. For example, in the case of the single-source shortest path problem, the estimated run-time speed-up is  $10^6$  compared with the state-of-the-art. In comparison with software implementations, the estimated run-time speed-up is asymptotically 3.75 and can be improved by further optimization of the hardware design or improvement of the configuration time [7] (see Table 3).

| Problem Size      | Clock Rate |          | Execution Time |          | Mapping Time |          | Speed-up            |

|-------------------|------------|----------|----------------|----------|--------------|----------|---------------------|

| vetices×edges     | Current    | Proposed | Current        | Proposed | Current      | Proposed |                     |

| $16 \times 64$    | 1.79       | 15       | 8.94           | 21.42    | 4 hours      | 22 msec  | $6.5 	imes 10^6$    |

| $64 \times 256$   | 1.14       | 15       | 56.14          | 79.02    | 4 hours      | 82 msec  | $1.7 	imes 10^6$    |

| $128 \times 515$  | 0.78       | 15       | 164.10         | 199.72   | 8 hours      | 161 msec | $1.8 \times 10^{6}$ |

| $256 \times 1140$ | 0.34       | 15       | 752.94         | 493.17   | 16 hours     | 319 msec | $1.8 \times 10^6$   |

Table 3: Performance comparison with the state-of-the-art approach

### 1.3.7 Model-based ATR on Configurable Hardware

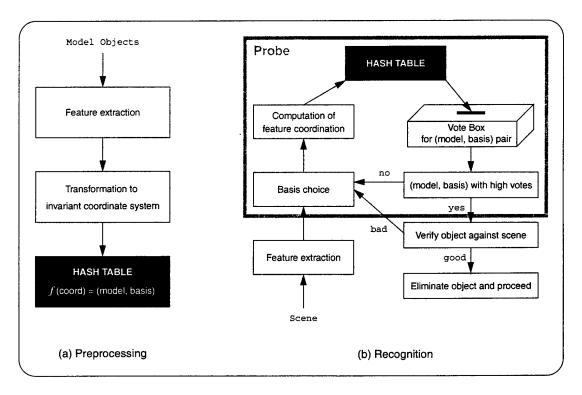

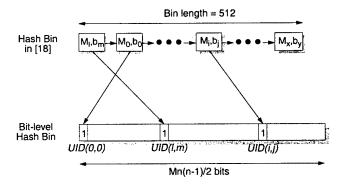

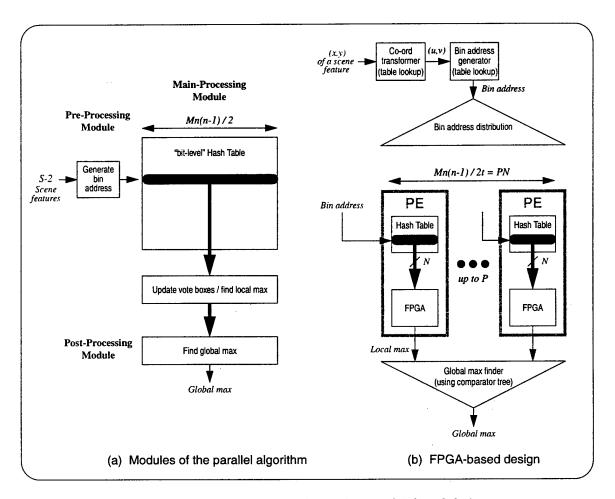

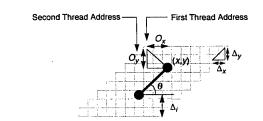

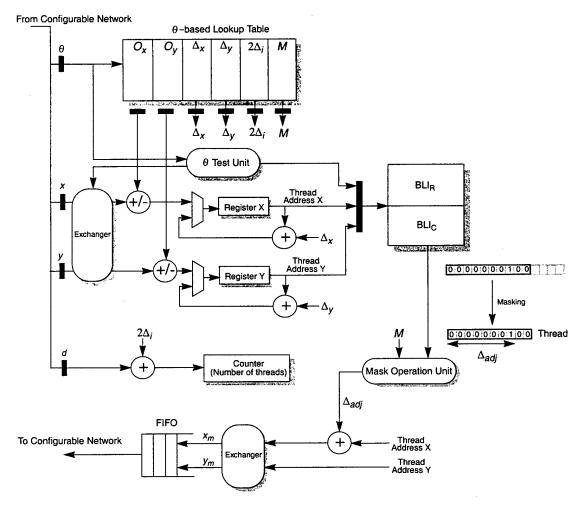

Model-based ATR uses geometric hashing as a technique for object recognition in occluded scenes. In this effort a design technique for parallelizing geometric hashing on an FPGA-based platform was developed. The hash table used in this approach is first transformed into a bit-level representation. By regularizing the data flow and exploiting bit-level parallelism in hardware, the proposed design achieves high performance. Using the proposed approach, given a scene consisting of 256 feature points, a probe can be performed in 1.65 milliseconds on an FPGA-based platform having 32 Xilinx 4062s. In earlier implementations, the same probe operation was performed in 240 milliseconds on a 32K-node CM2 and in 382 milliseconds on a 32-node CM5. Also, the same operation takes 40 milliseconds on a 32-node IBM SP-2. By parameterizing the application and the device characteristics, an area-time efficient design based on these parameters has been derived. Furthermore, the proposed approach can be applied to many geometric hashing methods and is portable to other FPGA devices [6].

### 1.3.8 Mapping Irregular Applications onto Configurable Hardware

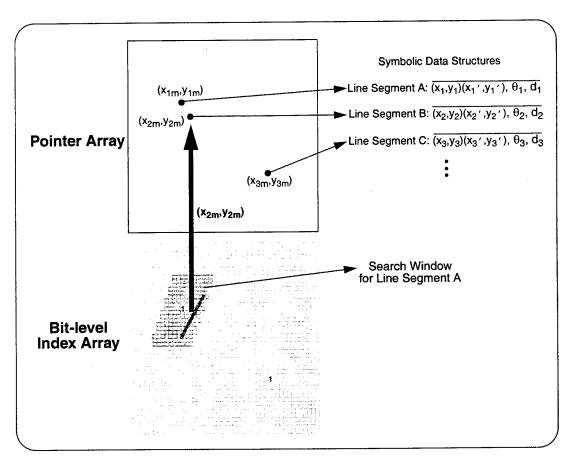

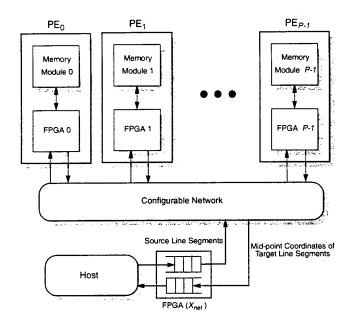

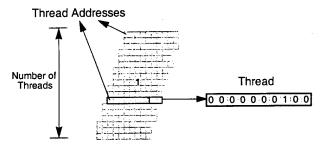

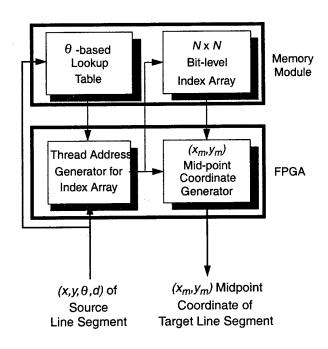

Most intermediate and high-level vision tasks manipulate symbolic data. A kernel operation in these vision tasks is to search symbolic data satisfying certain geometric constraints. Such operations are data-dependent and their memory access patterns are irregular. In this effort a fast parallel design for symbolic search operations using configurable hardware has been developed. The symbolic data is manipulated using a pointer array and a bit-level index array. Depending on the input data, a corresponding search window is calculated and symbolic search operations are performed in parallel. Performance estimates using 16 Xilinx XC6216s and memory modules are very promising. Given 3519 line segments (extracted from an  $1024 \times 1024$  pixel image), the operation can be performed in 1.11 milliseconds on an FPGA-based platform. On a Sun UltraSPARC Model 140, the same operation implemented

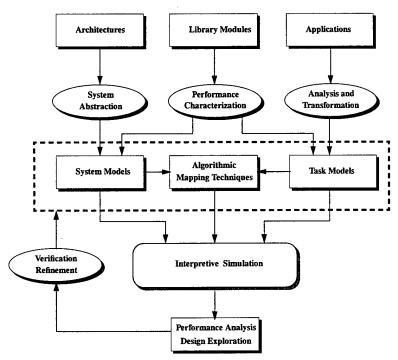

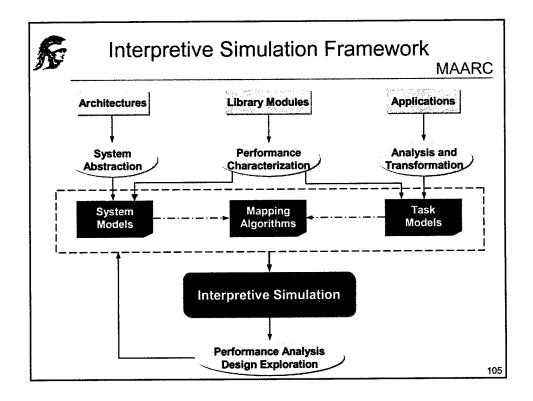

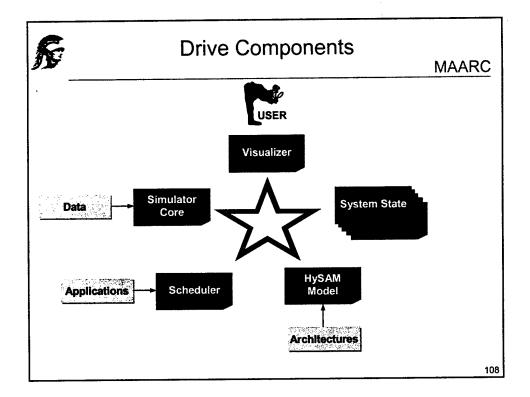

### 1.4 DRIVE Software

Current simulation tools for reconfigurable architectures are based on existing CAD design flow and perform mapping of designs to low level hardware for simulation. Furthermore, there are very few tools which provide any ability to study the dynamic behavior of reconfigurable hardware. Most of the existing simulation environments are based on simulation of High-level Description Language(HDL) or schematic designs that implement an application.

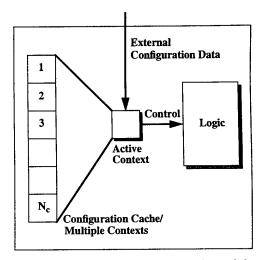

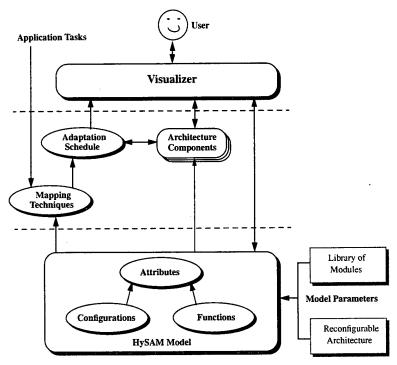

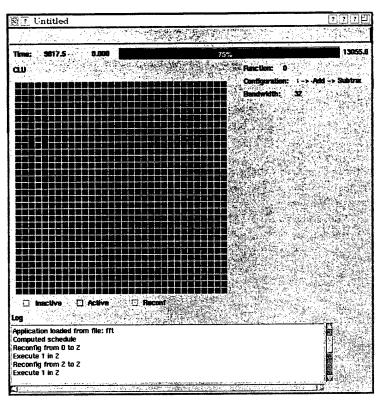

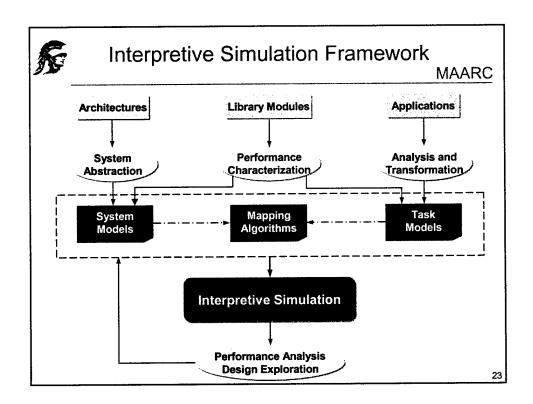

As part of this effort, a novel interpretive simulation and visualization environment based on modeling and module level mapping approach was developed. The Dynamically Reconfigurable systems Interpretive simulation and Visualization Environment(DRIVE) can be utilized as a vehicle to study the system and application design space and performance analysis. Reconfigurable hardware is characterized by using a high level parameterized model. Applications are analyzed to develop an abstract application task model. Interpretive simulation measures the performance of the abstract application tasks on the parameterized abstract system model. This is in contrast to simulating the exact behavior of the hardware by using HDL models of the hardware devices.

The **DRIVE** framework can be used to perform interactive analysis of the architecture and design parameter space. Performance characteristics such as total execution time, data access bandwidth characteristics and resource utilization can be studied using the **DRIVE** framework. The simulation effort and time are reduced and systems and designs can be explored without time consuming low level implementations. The proposed approach reduces the semantic gap between the application and the hardware and facilitates the performance analysis of reconfigurable hardware. This approach also captures the simulation and visualization of dynamically reconfigurable architectures. The HySAM model (see Section 1.1) is currently utilized by the framework to map applications to a system model. The proposed approach can be utilized to analyze reconfigurable architectures and application performance and facilitate adoption of such architectures by a larger spectrum of users.

### References

[1] K. Bondalapati. Modeling and Mapping for Dynamically Reconfigurable Architectures. PhD thesis, University of Southern California. Under Preparation.

- [2] K. Bondalapati and V.K. Prasanna. Mapping Loops onto Reconfigurable Architectures. In 8th International Workshop on Field-Programmable Logic and Applications, September 1998.

- [3] K. Bondalapati and V.K. Prasanna. Dynamic Precision Management for Loop Computations on Reconfigurable Architectures. In *IEEE Symposium on FPGAs for Custom Computing Machines*, April 1999.

- [4] K. Bondalapati and V.K. Prasanna. Hardware Object Selection for Mapping Loops onto Reconfigurable Architectures. In *International Conference on Parallel and Dis*tributed Processing Techniques and Applications, June 1999.

- [5] S. Choi, Y. Chung, and V.K. Prasanna. Configurable Hardware for Symbolic Search Operations. In *International Conference on Parallel and Distributed Systems*, December 1997.

- [6] Y. Chung, S. Choi, and V.K. Prasanna. Parallel Object Recognition on an FPGA-based Configurable Computing Platform. In *International Workshop on Computer Architectures for Machine Perception*, October 1997.

- [7] A. Dandalis, A. Mei, and V.K. Prasanna. Domain Specific Mapping for Solving Graph Problems on Reconfigurable Devices. In *Reconfigurable Architectures Workshop*, April 1999.

- [8] A. Dandalis and V.K. Prasanna. Fast Parallel Implementation of DFT using Configurable Devices. In *International Workshop on Field-Programmable Logic and Applica*tions, September 1997.

- [9] A. Dandalis and V.K. Prasanna. Space-Efficient Mapping of 2D-DCT onto Dynamically Configurable Coarse-Grained Architectures. In *International Workshop on Field-*Programmable Logic and Applications, September 1998.

- [10] R.P.S. Sidhu, A. Mei, and V.K. Prasanna. Genetic Programming using Self-Reconfigurable FPGAs. In *International Workshop on Field Programmable Logic and Applications*, September 1999.

- [11] R.P.S. Sidhu, A. Mei, and V.K. Prasanna. String Matching on Multicontext FPGAs using Self-Reconfiguration. In ACM/SIGDA International Symposium on Field Programmable Gate Arrays, February 1999.

# **Reconfigurable Meshes: Theory and Practice** <sup>1</sup>

Kiran Bondalapati and Viktor K. Prasanna

Department of Electrical Engineering-Systems

University of Southern California

Los Angeles, CA 90089-2562

#### **Abstract**

Configurable computing has recently gained much attention with the promise of delivering an order of magnitude performance improvement over general purpose processors. In this paper we contrast the abstract models of reconfigurable architectures and actual hardware available for configurable computing systems.

There is a wealth of ideas related to abstract models of reconfigurable architectures and fast parallel algorithms which exploit the reconfiguration potential in non-trivial ways. We summarize these abstract models and illustrate the power of these models using several example algorithms. We identify the practical problems in implementing these models in VLSI and describe some prototype implementations. Commercial FPGA devices which are being touted as the solution for building configurable computing systems are also examined. The MAARC<sup>2</sup> project at USC endeavors to bridge this gap between the abstract and the real worlds.

<sup>&</sup>lt;sup>1</sup>This work was supported by DARPA under contract DABT63-96-C-0049 monitored by Fort Hauchuca.

<sup>&</sup>lt;sup>2</sup>Models, Algorithms and Architectures for Reconfigurable Computing, http://maarc.usc.edu

# 1 Introduction

Configurable computing has recently gained much attention with the promise of delivering an order of magnitude performance improvement over general purpose processors. The paradigm of computing in space, i.e., laying out a series of computations on several functional units, as opposed to computing in time, i.e., a series of computations executed in sequence on a single functional unit, is being actively explored. There are several directions in which research is being carried out to realize the potential of configurable computing.

The idea of a VLSI array of processors overlaid with a reconfigurable bus system and an abstract model based on this architecture was proposed in [23]. Several abstract models of reconfigurable architectures and fast parallel algorithms for many problems have been described in the literature. These models include the bus automaton [30], content addressable array parallel processor (CAAPP) [33], polymorphic processor array (PPA) [21], among others. Efficient algorithms for fundamental data movement operations [23, 24], sorting [2, 11, 27, 28], arithmetic [15, 29], graph problems [24], image processing [14, 16] and computational geometry [12] have been developed on reconfigurable meshes. There have been several research prototype implementations of reconfigurable architectures which are related to the abstract models. Such architectures include the GCN [33], YUPPIE [22], CLIP [10], PADDI [7], ABACUS [5], DPGA [8].

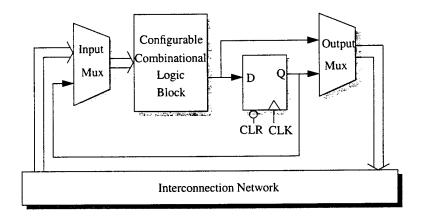

Currently the architectures which are being utilized to design reconfigurable systems have their root in Field Programmable Gate Array (FPGA). FPGAs consist of a matrix of fine grain computational elements, usually implemented using lookup tables, with a hierarchy of programmable interconnect. Traditionally, FPGAs have been used for logic design and hardware emulation. Their suitability as computing engines for reconfigurable architectures is being explored in SPLASH [6], DEC PeRLe [3], Teramac [1], among others. But FPGA architectures have been primarily designed to emulate random logic without frequent reconfiguration. Also, on-chip memory capacities are too small, reconfiguration times are relatively long (several milliseconds) and partial reconfiguration is difficult.

The advent of static RAM based FPGA devices has given rise to new opportunities in reconfigurable computing area. These devices provide features which allow changing the device configuration on the fly. But reconfiguration cost is still the prohibitive factor in using them for configurable computing. The other major factor is the lack of software tools which allow synthesis of applications exploiting dynamic reconfiguration. Research is also being carried out in designing coarser grain architectures which incorporate reconfigurable features such as MATRIX [25], BRASS Garp [36], RaPiD [9], CMU CVH [37], COLT [4].

This paper looks at the two extremes of the configurable computing world, the abstract models and actual devices. Though the abstract models have been shown to be very powerful, they are difficult to realize in VLSI. There have been several research prototypes of devices that show promise of implementing reconfigurability. But configurable computing cannot deliver the promise until commercial devices strive to deliver the reconfiguration potential possible with current VLSI technology.

In Section 2 we describe and characterize several variants of the reconfigurable mesh model. In Section 3 we illustrate the power of reconfiguration by describing algorithms for EXOR, Addition, Sorting, Prefix operations and Component labeling. We examine the technical issues in implementing these models and give brief descriptions of several implementations in Section 4. Some commercial devices which look promising for designing configurable systems are also explored in this section. Concluding remarks are made in Section 5.

# 2 Reconfigurable Meshes

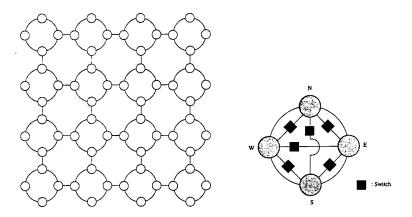

A reconfigurable-bus architecture consists of a multi-dimensional array of processing elements (PEs) connected to a bus through a fixed number of I/O ports. This bus architecture is capable, on a per instruction basis, of configuring a topology that contributes to solving the problem at hand. Bus reconfiguration is achieved by locally configuring the switches within each PE. Different shapes of buses such as rows, columns, diagonals, zig-zag, and staircase can be formed by configuring the switches/ports.

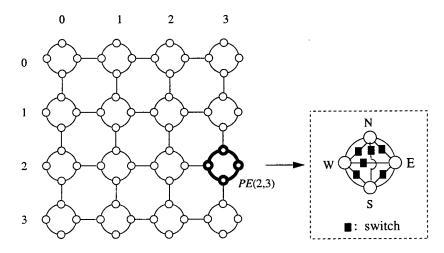

A two dimensional processor array with a reconfigurable-bus system of size MN consisting of identical processors connected as a  $M\times N$  rectangular mesh system is called a reconfigurable mesh. An example of a  $4\times 4$  reconfigurable mesh is shown in Figure 1. A set of four I/O ports labeled N, E, W and S, connect each PE to its four neighbors to the north, east, west and south, respectively. Each PE has locally controllable switches which configure the connection patterns between the four I/O ports. The switches allow the broadcast bus to be divided into sub-buses, providing smaller reconfigurable meshes. The bus and all I/O ports are assumed to be m-bit wide. The connection patterns are represented as  $\{g_1,g_2,...\}$ , where each of  $g_i$  represents a group of switches connected together. For example  $\{NS,E,W\}$  represents the connection pattern with N and S connected and E and W unconnected.

Figure 1: Reconfigurable Mesh.

The basic computational unit of the reconfigurable mesh is the Processing element (PE) which consists of a switch, local storage and an ALU (Fig. 1). In a unit time, a PE can perform:

- 1. Setting up of a connection pattern.

- 2. Read from or write onto a bus or local storage.

- 3. Logical or arithmetic operations on local data.

Various models of reconfigurable meshes have been proposed in the literature. Most of these models are synchronous in nature and permit unconditional global switch setting in addition to local switch control. Unconditional global switch setting is performed by the broadcast of a global instruction from a central controller. Reconfigurable mesh models can be characterized by the following parameters:

- Width It refers to the data width of the PE. The two classes of models which have been proposed are bit and word models. The main difference is the width of the input operands of the PE. Also, log n bits (where n is the size of the reconfigurable mesh) need to be accessed when the processor needs to know its position before setting its configuration. Note that the Width parameter is not directly related to the bus width of the reconfigurable mesh.

- **Delay** One critical factor in the analysis of reconfigurable algorithms is the time needed to propagate a signal. Some models assume this to be a unit-time operation no matter how far the signal has to travel, while other models assume this to be a function of the number of processors. Time analyses which assume constant time are called *unit-delay models* and logarithmic time are called *logarithmic-delay models*.

- Bus Access Each PE connects to the bus through its ports and will either read or write to

it. Similar to shared memory machines the models can be classified as CRCW, CREW,

ERCW, and EREW based on how the bus is accessed. The most common models are

the ERCW models but the CRCW models have also been extensively studied. The

CRCW models typically assume that a wired-or operation is performed on a concurrent write by multiple PEs onto the bus.

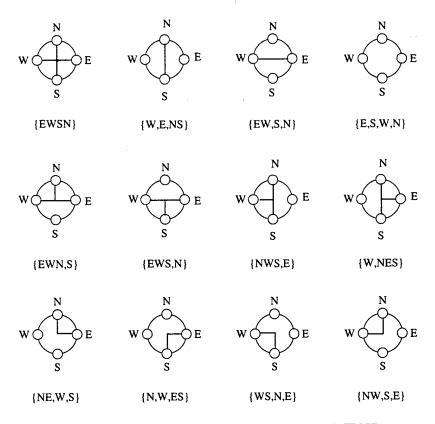

- Connection Patterns Each PE can set the connection between its four ports based on local data or global instruction. There are a total of 15 different connection patterns possible. Different models differ in the number of connection patterns(a subset of 15) which they allow. These models can also be classified based on whether they allow cross-over of the port connections. The models which allow cross-over of connections(such as N-S and E-W) have been shown to be more powerful than the non-cross-over models.

### 2.1 Various Models

Since the introduction of the reconfigurable mesh [23], several models have appeared in the literature. Following variations of the models have been studied extensively and efficient algorithms have been developed for several problems:

- PARBS The most general and the most powerful is the PARBS model [32]. In this model no restriction is placed on the allowed connections among the 4 I/O ports in each PE. Thus, all 15 connection patterns are possible and algorithms for a variety of applications have been developed on this model [11, 14, 29, 32].

- RMESH This consists of two-dimensional mesh of size  $n \times n$ , with each PE connected to a broadcast bus [23]. This bus, like the mesh, is also constructed as an  $n \times n$  grid, where PEs are located at the intersection of the grid lines. Further each bus link between adjacent PEs has a switch embedded in it, where the two PEs at either end of the link can control the switch. When all the switches are closed, all the  $n^2$  PEs are connected together. If all the PEs disconnect the switches to the north, then we obtain row buses. Similarly column buses can be obtained. The connection patterns allowed in RMESH are shown in Figure 2.

- MRN/LRN The Reconfigurable Network (RN) [2] is a general model in which no restriction is placed on the bus segments that connect the PE or on the placement of the

Figure 2: Connection patterns allowed in RMESH.

PEs. I.e. PEs may not lie at grid points and a bus segment may join an arbitrary pair of PEs. Variants of this model under the mesh restriction are the MRN and LRN. Connection patterns allowed in MRN are shown in Figure 3. In LRN a bus may consist of any connected path of edges. However, only *linear* buses are composed, so that a bus component is attached to at most one other bus component at each end.

Figure 3: Connection patterns allowed in MRN.

• **Polymorphic Torus** A polymorphic torus architecture [18, 22] is identical to the PARBS architecture except that the rows and columns of the underlying mesh wrap around.

Jang et. al. proposed a **Bit Model** [13] of reconfigurable mesh which can simulate (asymptotically) most of the word based models of the reconfigurable mesh in the same amount of

time using the same VLSI area. The basic PE in the Bit Model consists of a switch, local storage and a 1-bit ALU. The switch consists of six bit-level switches which can be closed or opened using local information within the PEs. The switch can realize any of the possible 15 connection patterns among its 4 I/O ports. The bus architecture is similar to the RMESH architecture and can carry O(1) bits of data.

### 2.2 Related Models

### REBSIS

In the reconfigurable buses with shift switching (REBSIS) [20] model, each word level switch consists of several bit level switches. In each connection pattern each of the bit level switches share a common connection pattern to control the bit level buses in a uniform way. Based on a control bit pattern the switch performs rotate-shift on the input bit pattern. It has been proved that that the REBSIS model is more powerful than several word models [20] but the Bit Model [13] of reconfigurable mesh has been shown to be able to simulate the REBSIS model using the same area.

• RMBM A more general reconfigurable network model called the reconfigurable multiple bus machine (RMBM) [31] was proposed to investigate effects of switch models on relative computational power of reconfigurable network models. This model separates the computational aspects from the connection configuration aspects. The RMBM model has processors, buses, fuse lines and sets of switches. Each processor has one write port and several read ports. The switches can be classiffied into connect switches, segment switches and fuse switches. The connect switches connect a particular port of a processor to one of the buses, the segment switches segment the bus and the fuse switches connect two or more buses together. There are restricted versions of this model which differ in the classes of switches which they allow.

# 3 Some Illustrative Algorithms

Lot of work has been done in exploiting the power of reconfigurable meshes. Algorithms for basic computations such as Or, And, Exor, Addition, Multiplication etc. have been designed and shown to be optimal on several variants of the reconfigurable mesh models. Using these basic data operations and additional non-trivial techniques of exploiting reconfiguration, algorithms for problems in image processing, computational geometry, graphs etc. have been designed. In this section some algorithms are described to illustrate the power of these architectures.

# 3.1 EXOR Computation

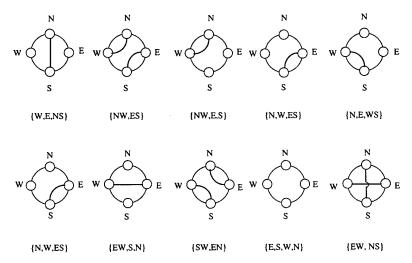

The EXOR of N bits of data can be computed on a reconfigurable mesh of size  $2n \times 3$  in  $\theta(1)$  time using the unit-time delay model and in  $\theta(\log n)$  time using the log-time delay model [24]. The basic idea behind the algorithm is described here.

Based on a single input bit a  $3 \times 2$  array of PEs set their local switch configurations to one of the two patterns as shown in Figure 4. If the input bit is 1 the top two rows cross-over and the 1-signal toggles to the other row and if the input bit is 0 then the 1-signal passes through

the PEs, in the same row. When a 1-signal is applied to the top row input of the first processor of the system the EXOR of all the inputs appears at the last processor in the mesh. A 1-signal out of the top row indicates a result of 0 and a 1-signal out of the middle row indicates a result of 1.

An example EXOR computation of 3 input bits with 18 PEs is shown in Figure 4. The highlighted path shows the flow of the 1-signal from the left to the right. The result of the EXOR computation appears at the output after a constant delay in the unit-time delay model.

Figure 4: EXOR computation

### 3.2 Addition

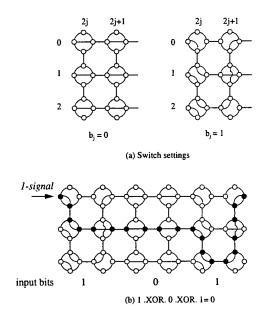

Addition of two n-bit numbers can be carried out in a similar way as EXOR computation. Each PE sets its switch pattern based on either a carry generate or a carry propagate configuration. If the two input bits  $a_i$  and  $b_i$  are different then the PE connects its West input to the East output port, which is a carry propagate configuration. If the input bits are the same then none of the switches are connected. The carry generate at a PE is implemented by the PE writing a 1 on its East port when both the bits  $a_i$  and  $b_i$  are 1.

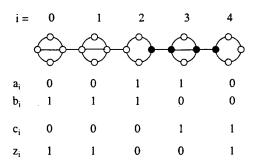

An example addition of two 5-bit numbers is shown in Figure 5. The bits  $c_i$  indicate the intermediate carry bits and  $z_i$  are the result bits.

Using a similar idea and constructing a k-stage ripple carry adder it was shown that addition of n k-bit numbers ( $1 \le k \le n$ ) can be performed in constant time using a  $n \times nk$  bit model of reconfigurable mesh [11].

### 3.3 Parallel Prefix

Parallel Prefix is an important operation that can be used to sum values, broadcast data, solve problems in image processing and graph problems etc. [24]. Assume processor  $p_i$ ,  $0 \le i \le n-1$ , initially contains the data element  $a_i$ . The parallel prefix problem requires  $p_i$  to compute  $a_0 \otimes a_1 \otimes \ldots \otimes a_i$ , where  $\otimes$  is an associative operator such as addition (+).

Figure 5: Addition of two 5-bit numbers.

The given n values are assumed to be distributed one per processor on a reconfigurable mesh of size n. The binary associative operation  $\otimes$ , is assumed to be a unit-time operation. First, parallel prefix is performed along the rows so that each processor knows the initial prefix of those values restricted to its row. Next, in the last column the parallel prefix is performed to determine row-wise prefix solutions. Finally, within each row, the prefix of previous of the previous rows is broadcast so that all the processors can update their entry appropriately. Parallel prefix can be computed in every row simultaneously in  $\log n^{1/2}$  iterations by appropriately setting switches, broadcasting and updating values at each iteration.

## 3.4 Sorting

There are several sorting algorithms on reconfigurable mesh models. We describe here the algorithm presented in [11]. Sorting of a sequence can be decomposed into sort of its subsequences and data movement between the sorted subsequences. The reconfigurable mesh algorithm uses a variation of Leighton's eight-stage column sort [17]. The stages are a combination of stages of  $n^{1/4}$  sorters, each capable of sorting  $n^{3/4}$  numbers, and  $n^{1/4}$ -shuffle network stages.

The input sequence of n numbers is assumed to be initially stored in the top row of the reconfigurable mesh. The sequence is partitioned into subsequences of  $n^{3/4}$  numbers each. Sorting of a subsequence is done by computing the ranks of all the numbers and then storing each number according to its rank by using shuffle networks [11]. Sorting of  $n^{3/4}$  numbers in constant time is carried out using a  $n \times n^{3/4}$  reconfigurable mesh. In the first step, each of the  $n^{3/4}$  PEs broadcast their numbers along each column of n PEs. Then the mesh is divided into  $n^{3/4}$  submeshes each of size  $n^{1/4} \times n^{3/4}$ . The rank of number  $x_i$  is computed by submesh i using row broadcasts. The results of the comparisons made after this row broadcasts are added to give the rank of each number. The addition can be done in constant time as stated in Section 3.2. The  $n^{1/4}$ -shuffle stage can also be implemented in constant time using a sequence of broadcast operations.

# 3.5 Component Labeling

The problem is to label the connected components of a digitized image. Given an  $n \times n$  image which is distributed as a pixel per processor onto the processors of a reconfigurable mesh of size  $n \times n$ , the connected components can be labeled in  $\theta(\log n)$  time under the unit-time delay model [24].

In the first step each processor examines the pixels in each of its four neighbors and

sets its four switches so that a connection is maintained only between neighboring black pixels. This  $\theta(1)$  operation creates a subbus over each component. Given a linked list of processors overlaid by a reconfigurable subbus, the minimum(maximum) of the value stored in these processors can be computed in  $O(\log n)$  iterations. Each iteration computes the local minima(maxima) and discards the other elements. Each iteration uses a constant number of broadcast steps and comparison operations, and hence the total running time is as stated above.

# 3.6 Summary of Results

We present a brief summary of algorithms on the reconfigurable mesh models. A comprehensive bibliography of results can be found in [26]. All results are with respect to the unit-time delay reconfigurable mesh model.

| Problem                                            | Mesh Size       | Time                                       |

|----------------------------------------------------|-----------------|--------------------------------------------|

| EXOR of n bits                                     | $2n \times 3^*$ | Constant                                   |

| Prefix-And of $n$ 1-bit numbers                    | $1 \times n^*$  | Constant                                   |

| Maximum(Minimum) of $n \log n$ -bit numbers        | $n \times n$    | Constant                                   |

| Addition of $n$ $k$ -bit numbers, $1 \le k \le n$  | $n 	imes nk^*$  | Constant                                   |

| Multiplication of two $n$ -bit numbers             | $n \times n^*$  | Constant                                   |

| Division of two <i>n</i> -bit numbers              | $n \times n^*$  | Constant                                   |

| Histogram of an $n \times n$ image (h gray levels) | $n \times n$    | $O(\min(\sqrt{h} + \log(\frac{n}{h}), n))$ |

| Sort of $n O(\log n)$ bit numbers                  | $n \times n$    | Constant                                   |

| Convex Hull of n points                            | $n \times n$    | Constant                                   |

| Smallest enclosing rectangle of n points           | n 	imes n       | Constant                                   |

| Triangulation of $n$ planar points                 | $n^2 	imes n$   | Constant                                   |

| All-pairs nearest neighbors of $n$ points          | $n \times n$    | Constant                                   |

| Two-set dominance counting of $n$ points           | $n \times n$    | Constant                                   |

| Connected components of an $n \times n$ image      | $n \times n$    | $O(\log n)$                                |

<sup>\* -</sup> the bit model of reconfigurable mesh is used.

# 4 Practical Considerations and Architectures

The choice of an architecture is strongly influenced by physical fabrication constraints. The reconfigurable mesh has nearly constant diameter and a dynamically reconfigurable bus system. It is very attractive in terms of implementation because of the two dimensional topology, low pin requirement and highly regular structure, which are well suited for today's VLSI and packaging technology.

There are several physical constraints that have to be overcome to successfully implement these architectures. Some of the features of the reconfigurable mesh models which should be examined in the context of hardware technology are:

Reconfiguration The ability to set the local configurations of switches is one of the key

aspects of reconfigurable meshes which is exploited in designing efficient algorithms.

Assumptions made in the model impact the design since more flexibility in allowed

switch patterns usually implies more area because of larger control memory etc. Most implementations support global control signals but implementing dynamic change of configuration based on local data is very expensive and is difficult to provide in general purpose implementations.

- Signal Delay There is potentially a large signal delay due to a long chain of shorted path, set up because of configuration. The signal propagation time grows linearly with the length of the wire carrying the signal. There are also unpredictable delays in VLSI because the wire capacitance is affected by the number of processors connected to the wire carrying the signal.

- Recent VLSI implementations have addressed these issues and suggest that the broadcast delay, although not constant, is very small. For example, only 16 machine cycles are required to broadcast on a 10<sup>6</sup> processor YUPPIE. GCN has shorter delays by adopting all-active and pre-charged circuit for local switches. ABACUS architecture propagates a signal through 18 PEs in a single 8ns clock cycle. Broadcast delay can be further reduced by using optical fibers for reconfigurable bus system and using electrically controlled directional coupler switches for connecting and disconnecting two fibers.

- Clock Timing In reconfigurable meshes variable length shorted path can be established based on the algorithm. If a fixed length clock is designed to accommodate the worst case shorted path, the clock for the system will be degraded. The constant time algorithms in the literature do not consider the clock implementation. Many clocking schemes are possible to accommodate the worst case path while not affecting the average clock performance. One such proposal is variable length clock that adjusts the length of clock to the length of the path. Global distribution of control signals also affects the clock signals. Detailed discussion of such issues is beyond the scope of this paper.

### 4.1 Architectures

We look at two variants of reconfigurable architectures. One class of architectures are based on the abstract models and try to approximate the features of the models. We describe the YUPPIE and the ABACUS architectures which are representative research prototypes. The other class consists of architectures which have evolved from commercial FPGA designs. We look at the features offered by two FPGAs, namely, XILINX 6200 and the NSC CLAy. Though these devices have not been designed for reconfigurable computing engines, they are a result of demand for fast reconfigurable components.

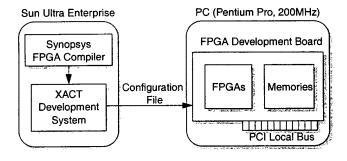

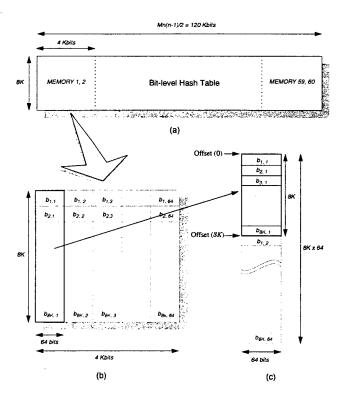

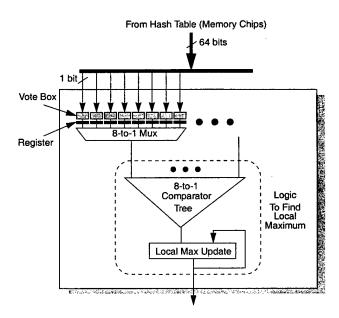

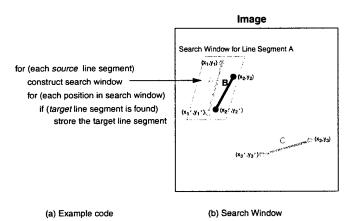

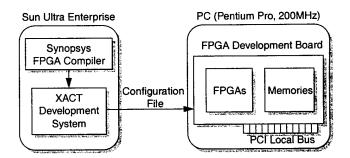

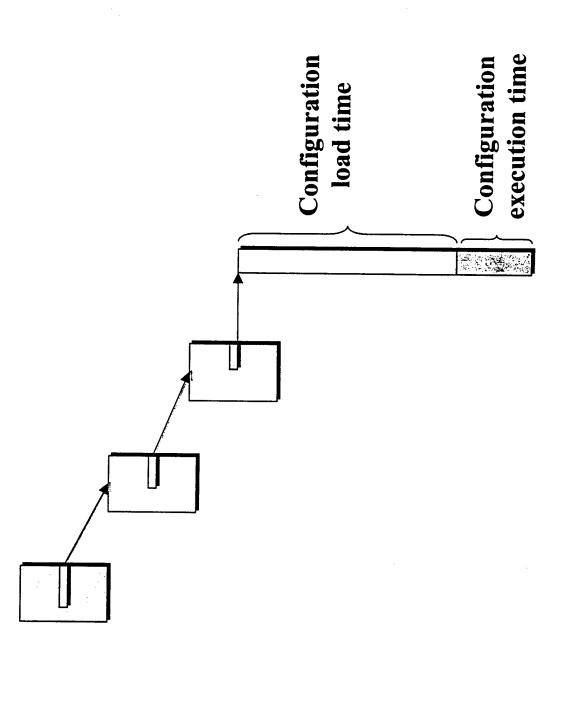

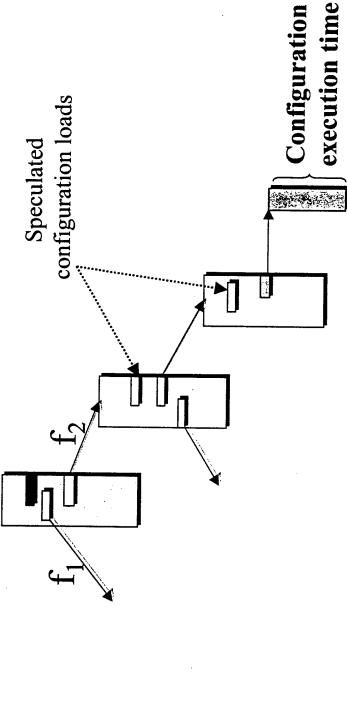

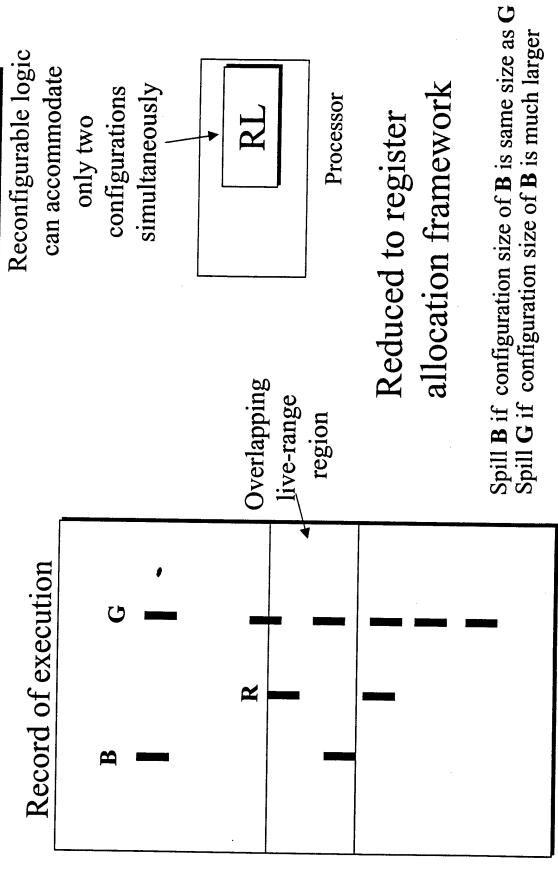

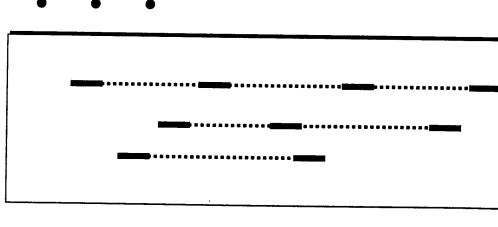

## 4.1.1 Polymorphic Torus Architecture - YUPPIE