Volume 48, Numbers 1-4, September 1999

# MICROELECTRONIC ENGINEERING

An International Journal of Semiconductor Manufacturing Technology

Including Nanoelectronic Engineering

Proceedings of the 11th biennial conference on **Insulating Films on Semiconductors**

> June 16-19, 1999 Kloster Banz, Germany

# 19991123 118

Edited by

Max Schulz DISTRIBUTION STATEMENT ARolf Brendel Approved for Public Release Distribution Unlimited

COMPLETE VOLUME

Elsevier

## MICROELECTRONIC ENGINEERING

Editor-in-Chief (Europe) MARC VAN ROSSUM IMEC Kapeldreef 75 B-3001 Leuven Belgium

#### Editor (USA)

JOHN RANDALL Texas Instruments Mail Station 3701 13570 N. Central Expressway Dallas, TX 75243 U.S.A.

#### Editor (Japan)

YOSHINUBO ÁOYAGI Institute of Physical and Chemical Research (RIKEN) Wako-shi Saitama, 351-01 Japan

#### Advisory Editors (Japan)

- M. Komuro, Electrotechnical Laboratory, Tsukuba

- S. Matsui, NEC Corp., Tsukuba

- T. Nishimura, Mitsubishi Electric Corp., Itami

- Y. Shiraki, The University of Tokyo, Tokyo

- T. Takigawa, Toshiba Corp., Kawasaki

- N. Yokoyama, Fujitsu Laboratories Ltd., Atsugi

#### Advisory Editors (U.S.A.)

- A.R. Neureuther, University of California, Berkeley, CA

- G. Owen, Hewlett Packard, Palo Alto, CA

- H. Pfeiffer, IBM, Hopewell Junction, NY

- L. Swanson, FEI Company, Hillsborough, OR

- L.F. Thompson, Bell Laboratories, Murray Hill, NJ

- K.D. van der Mast, FEI Company, Hillsboro, OR

- E.D. Wolf, Cornell University, Ithaca, NY

#### **Founding Editor**

W.C. Nixon, Cambridge University, U.K.

#### Advisory Editors (Europe)

- H. Ahmed, Cambridge University, U.K.

- G. Declerck, Interuniversitair Micro-Elektronica Centrum, Louvain, Belgium

- M. Gentili, CNR Istituto di Elettronica dello Stato Solido, Rome, Italy

- A. Heuberger, Fraunhofer Abteilung für Mikrostrukturtechnik, Berlin, Germany

- M.E. Jones, Imperial College, London, U.K.

- D.P. Kern, Universität Tübingen, Germany

- H. Launois, L2M CNRS, Bagneux, France

- R.A. Lawes, Rutherford Appleton Laboratory, Chilton, U.K.

- P. Paniez, CNET/DTM/TMF, France

- J. Perrocheau, ELISA, Les Ulis, France

- P. Vettiger, IBM, Rüschlikon, Switzerland

- E. Wolfgang, Siemens AG, Munich, Germany

#### **Editor Emeritus**

S. Namba, Osaka University, Japan

#### Aims and Scope

The aim of *Microelectronic Engineering* is to bring together in one publication the results of European, American and Japanese work in the rapidly expanding field of integrated microelectronic, optic and optoelectronic devices. *Microelectronic Engineering* is an archival, peer-reviewed journal. It publishes full research papers, short communications, and review articles. The scope of this Journal includes materials, methods and designs for microfabrication, processing and inspection for microelectronic and optoelectronic elements from centimeters to nanometers.

The wide range of topics covered by the journal include: 1. Lithography

- optical lithography (submicron dimensions, deep u.v. lithography)

- · electron optical methods and systems

- X-ray optical methods and systems

- resists

- limits

- 2. Pattern Transfer

- ion technology

- plasma etching

- self-organisation

## 3. Materials

- metallization

- microstructuring growth processes

- silicon on insulators

- compound semiconductors

- dielectrics (low K and high K)

- interconnect architectures

- 4. Inspection and Testing

- electron beam testers

- laser probes

- signal and image processing

- metrology

- 5. Advanced Processing

- process integration

- three dimensional integration

- defect free processes

- manufacturing science

- · rapid thermal processing

- process modelling

- equipment modelling

- laser assisted processing

- 6. Micromechanical Structures

- fabrication

- design

- 7. Advanced Devices

- nanometer structures

- dimension-sensitive devices properties

- effect of small scaling

| REPORT DO                                                                                                                                     | CUMENTATION PAG                                                                                                                           | )E                                                                           | Form Approved OMB No. 0704-0188                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| athering and maintaining the data needed, a<br>ollection of information, including suggestion<br>pavis Highway, Suite 1204, Arlington, VA 222 | and completing and reviewing the collection<br>ns for reducing this burden to Washington H<br>202-4302, and to the Office of Management a | of information. Send co<br>eadquarters Services, D<br>nd Budget, Paperwork F | he time for reviewing instructions, searching existing data source<br>mments regarding this burden estimate or any other aspect of th<br>Directorate for Information Operations and Reports, 1215 Jefferso<br>Reduction Project (0704-0188), Washington, DC 20503. |

| . AGENCY USE ONLY (Leave blank)                                                                                                               | 2. REPORT DATE                                                                                                                            | 3. REPORT                                                                    | TYPE AND DATES COVERED                                                                                                                                                                                                                                             |

|                                                                                                                                               | 1999                                                                                                                                      |                                                                              | Conference Proceedings                                                                                                                                                                                                                                             |

| TITLE AND SUBTITLE                                                                                                                            |                                                                                                                                           |                                                                              | 5. FUNDING NUMBERS                                                                                                                                                                                                                                                 |

| Insulating Films on Semicon                                                                                                                   | ductors                                                                                                                                   |                                                                              | F61775-99-WF057                                                                                                                                                                                                                                                    |

| AUTHOR(S)                                                                                                                                     |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

| Conference Committee                                                                                                                          |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

| PERFORMING ORGANIZATION N/                                                                                                                    | AME(S) AND ADDRESS(ES)                                                                                                                    |                                                                              | 8. PERFORMING ORGANIZATION                                                                                                                                                                                                                                         |

| University of Erlangen                                                                                                                        |                                                                                                                                           |                                                                              | REPORT NUMBER                                                                                                                                                                                                                                                      |

| Staudtstrasse 7<br>Erlangen D-91058<br>Germany                                                                                                |                                                                                                                                           |                                                                              | N/A                                                                                                                                                                                                                                                                |

| SPONSORING/MONITORING AGE                                                                                                                     |                                                                                                                                           |                                                                              | 10. SPONSORING/MONITORING                                                                                                                                                                                                                                          |

|                                                                                                                                               |                                                                                                                                           |                                                                              | AGENCY REPORT NUMBER                                                                                                                                                                                                                                               |

| EOARD<br>PSC 802 BOX 14<br>FPO 09499-0200                                                                                                     |                                                                                                                                           |                                                                              | CSP 99-5057                                                                                                                                                                                                                                                        |

| 1. SUPPLEMENTARY NOTES                                                                                                                        |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

| 2a. DISTRIBUTION/AVAILABILITY ST<br>Approved for public release;                                                                              |                                                                                                                                           |                                                                              | 12b. DISTRIBUTION CODE                                                                                                                                                                                                                                             |

| 3. ABSTRACT (Maximum 200 words)                                                                                                               |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

| This is an interdisciplinary co<br>effect (MIS, MOS) semicond                                                                                 |                                                                                                                                           | semiconductor/insula<br>g, characterization ar                               | tor interfaces, and the physics and technology of field<br>nd measurement techniques, radiation and hot carrier                                                                                                                                                    |

|                                                                                                                                               |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

|                                                                                                                                               |                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                    |

| . SUBJECT TERMS                                                                                                                               |                                                                                                                                           | ·                                                                            | 15. NUMBER OF PAGES                                                                                                                                                                                                                                                |

| EOARD, Semiconductors, S                                                                                                                      | emiconductor Growth                                                                                                                       |                                                                              | 447<br>16. PRICE CODE                                                                                                                                                                                                                                              |

| . SECURITY CLASSIFICATION                                                                                                                     | 18. SECURITY CLASSIFICATION                                                                                                               | 19, SECURITY CI                                                              |                                                                                                                                                                                                                                                                    |

| OF REPORT                                                                                                                                     | OF THIS PAGE                                                                                                                              |                                                                              |                                                                                                                                                                                                                                                                    |

|                                                                                                                                               | OF THIS PAGE<br>UNCLASSIFIED                                                                                                              |                                                                              | ASSIFIED UL                                                                                                                                                                                                                                                        |

An International Journal of Semiconductor Manufacturing Technology Including Nanoelectronic Engineering

ing Natioelectronic Enginee

Volume 48 (1-4)

Proceedings of the 11th biennial conference on Insulating Films on Semiconductors

> June 16–19, 1999 Kloster Banz, Germany

> > Edited by

Max Schulz Rolf Brendel

AQF00-02-0494

DTIC QUALITY INSPECTED 4

## MICROELECTRONIC ENGINEERING

Editor-in-Chief (Europe) M. Van Rossum IM IMEC, Kapeldreef 75, B-3001 Leuven, Belgium

| <b>Editor (Japan)</b><br>Y. Aoyagi     | Institute of Physical and Chemical Research (RIKEN), Wako-shi, Saitama, 351-01,<br>Japan                            |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <b>Editor (U.S.A.)</b><br>J.N. Randall | Texas Instruments, Mail Station 3701, 13570 N. Central Expressway, Dallas,<br>TX 75243, U.S.A.                      |

| Advisory Editors (Ja                   | ipan)                                                                                                               |

| M. Komuro                              | Electrotechnical Laboratory, 1-1-4 Umezono, Tsukuba, Ibaragi 305, Japan                                             |

| S. Matsui                              | Fundamental Research Laboratories, NEC Corporation, 34 Miyukigaoka, Tsukuba,<br>Ibaragi 305, Japan                  |

| T. Nishimura                           | LSI Research and Development Laboratory, Mitsubishi Electric Corporation, 4-1<br>Mizuhara, Itami, Hyougo 664, Japan |

| Y. Shiraki                             | Research Center for Advanced Science and Technology, The University of Tokyo,<br>Meguro, Tokyo 153, Japan           |

| T. Takigawa                            | Research and Development Center, Toshiba Corporation, 1 Komukaitoshiba-cho, Kawasaki, Kanagawa 210, Japan           |

| N. Yokoyama                            | Fujitsu Laboratories Ltd., Atsugi Laboratory, 10-1 Morinosato-Wakamiya, Atsugi,<br>Kanagawa 243-01, Japan           |

## Advisory Editors (U.S.A.)

| A.R. Neureuther   | University of California, Department of Electrical Engineering, Berkeley, CA 94720, |

|-------------------|-------------------------------------------------------------------------------------|

|                   | U.S.A.                                                                              |

| G. Owen           | Circuit Technology R&D, Hewlett Packard, 3500 Deer Creek Road, P.O. Box 10350,      |

|                   | Palo Alto, CA 94303-0867, U.S.A.                                                    |

| H. Pfeiffer       | IBM, General Technology Division, Hopewell Junction, NY 12533, U.S.A.               |

| L. Swanson        | FEI Company, 7451 N.E. Evergreen Park Way, Hillsborough, OR 97124-5830,             |

|                   | U.S.A.                                                                              |

| L.F. Thompson     | Bell Laboratories, 600 Mountain Avenue, Murray Hill, NJ 07974, U.S.A.               |

| K.D. van der Mast | FEI Company, 7451 N.W. Evergreen Parkway, Hilsboro, OR, U.S.A.                      |

| E.D. Wolf         | School of Electrical Engineering, Knight Laboratory, Cornell University, Ithaca, NY |

|                   | 14853, U.S.A.                                                                       |

|                   |                                                                                     |

#### Advisory Editors (Europe)

| H. Ahmed                    | Microelectronics Research Centre, Cavendish Laboratory, Madingley Road, Cam-                                                                           |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| G. Declerck                 | bridge CB3 0HE, U.K.<br>Interuniversitair Micro-Elektronica Centrum, Kapeldreef 75, 3030 Louvain, Belgium                                              |

| M. Gentili                  | CNR – Istituto di Elettronica dello Stato Solido, Via Cineto Romano 42, I-00156<br>Rome, Italy                                                         |

| A. Heuberger                | Fraunhofer Abteilung für Mikrostrukturtechnik, Dillenburgerstrasse 53, 1000 Berlin<br>33, Germany                                                      |

| M.E. Jones                  | Imperial College of Science, Technology and Medicine, Room 558, Sherfield Building, London SW7 2AZ, U.K.                                               |

| D. Kern                     | Universität Tübingen, Institut für Angewandte Physik, Auf der Morgenstelle 10, 72076 Tübingen, Germany                                                 |

| H. Launois                  | L2M CNRS, 196 Avenue Henri Ravera, 92225 Bagneux, France                                                                                               |

| R.A. Lawes                  | Rutherford Appleton Laboratory, Chilton, Didcot, Oxon OX11 0QX, U.K.                                                                                   |

| P. Paniez                   | CNET/DTM/TMF, 28 chemin du vieux Chêne, BP 98, 38243 Meylan Cedex, France                                                                              |

| J. Perrocheau               | ELISA, Z.A. Courtaboeuf, 18 Avenue du Québec, B.P. 736, 91962 Les Ulis Cédex,<br>France                                                                |

| P. Vettiger                 | IBM Research Division, Zurich Research Laboratory, Säumerstrasse 4, CH-8803<br>Rüschlikon, Switzerland                                                 |

| E. Wolfgang                 | Siemens AG, Zentralbereich Technik, Zentrale Forschung und Entwicklung,<br>Forschungslaboratorien (ZFE ME23), P.O. Box 830952, 8000 Munich 83, Germany |

| Editor Emeritus<br>S. Namba | Faculty of Engineering Sciences, Osaka University, Toyonaka-shi, Osaka, Japan                                                                          |

|                             |                                                                                                                                                        |

| Founding Editor             |                                                                                                                                                        |

| W.C. Nixon                  | Cambridge University, Engineering Department, Trumpington Street, Cambridge CB2 1PZ, U.K.                                                              |

.

nfos'99

Proceedings of the 11th biennial conference on **Insulating Films on Semiconductors**

> June 16-19, 1999 Kloster Banz, Germany

> > Edited by

Max Schulz Rolf Brendel

Volume 48/1-4 1999

Amsterdam - Lausanne - New York - Oxford - Shannon - Tokyo

Abstracted/indexed in:

Cambridge Scientific Abstracts Current Contents Engineering Index INSPEC Science Citation Index

#### © 1999 Elsevier Science B.V. All rights reserved.

This journal and the individual contributions contained in it are protected under copyright by Elsevier Science B.V., and the following terms and conditions apply to their use:

#### Photocopying

Single photocopies of single articles may be made for personal use as allowed by national copyright laws. Permission of the publisher and payment of a fee is required for all other photocopying, including multiple or systematic copying for advertising or promotional purposes, resale, and all forms of document delivery. Special rates are available for educational institutions that wish to make photocopies for non-profit educational classroom use.

Permissions may be sought directly from Elsevier Science Rights & Permissions Department, PO Box 800, Oxford OX5 1DX, UK; phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.co.uk. You may also contact Rights & Permissions directly through Elsevier's home page (http://www.elsevier.nl), selecting first 'Customer Support', then 'General Information', then 'Permissions Query Form'.

In the USA, users may clear permissions and make payments through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA; phone: (978) 7508400, fax: (978) 7504744, and in the UK through the Copyright Licensing Agency Rapid Clearance Service (CLARCS), 90 Tottenham Court Road, London W1P 0LP, UK; phone: (+44) 171 436 5931; fax: (+44) 171 436 3986. Other countries may have a local reprographic rights agency for payments.

#### **Derivative Works**

Subscribers may reproduce tables of contents or prepare lists of articles including abstracts for internal circulation within their institutions. Permission of the publisher is required for resale or distribution outside the institution.

Permission of the publisher is required for all other derivative works, including compilations and translations.

#### **Electronic Storage or Usage**

Permission of the publisher is required to store or use electronically any material contained in this journal, including any article or part of an article. Contact the publisher at the address indicated.

Except as outlined above, no part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the publisher.

Address permissions requests to: Elsevier Science Rights & Permissions Department, at the mail, fax and e-mail addresses noted above.

#### Notice

No responsibility is assumed by the Publisher for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions or ideas contained in the material herein. Because of rapid advances in the medical sciences, in particular, independent verification of diagnoses and drug dosages should be made.

Although all advertising material is expected to conform to ethical (medical) standards, inclusion in this publication does not constitute a guarantee or endorsement of the quality or value of such product or of the claims made of it by its manufacturer.

| 5-5-1<br>-                   |                                                                                                                                | MICROELECTI<br>ENGINEERI |           |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|

| ELSEVIER                     | Microelectronic Engineering 48 (1999) v-xii                                                                                    | www.elsevier.nl/loc      | ato / mag |

|                              | Contents                                                                                                                       | www.eisevier.ni/ioc      | cate/mee  |

| Preface                      |                                                                                                                                |                          | xiii      |

| Committees                   |                                                                                                                                |                          | xiv       |

| Review and outlo             | ok at the turn of the century                                                                                                  |                          |           |

| 40 years MOS tech<br>P. Balk | nology - From empiricism to science                                                                                            |                          | 3         |

| Outlook of MOS d<br>H. Iwai  | evices into the next century                                                                                                   |                          | 7         |

| Ultrathin dielectri          | ics                                                                                                                            |                          |           |

| •                            | steps of ultrathin gate oxides<br>H. Nohira, K. Takahashi                                                                      |                          | 17        |

| sub-50 nm CM                 | limits of ultrathin SiO <sub>2</sub> and Si-O-N gate dielectrics<br>OS<br>ſ. Sorsch, G. Timp, D. Muller, B. Weir, P. Silverm   |                          | 25        |

|                              | raps on the tunneling characteristics of ultrathin (1<br>E. Sangiorgi, T. Sorsch, I. Kizilyalli                                | .5-3nm) oxides           | 31        |

| activated oxyge              | in nm-thick gate SiO <sub>2</sub> growth at low temperatures<br>m<br>I. Futatsuyama, Y. Ueda, K. Moriizumi, H. Matsu           | U U                      | 35        |

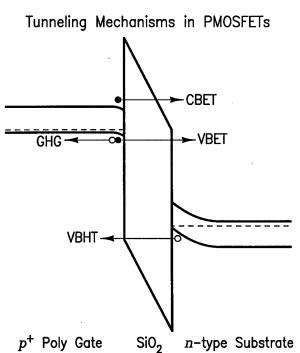

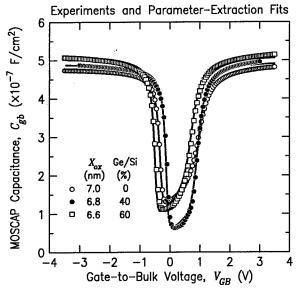

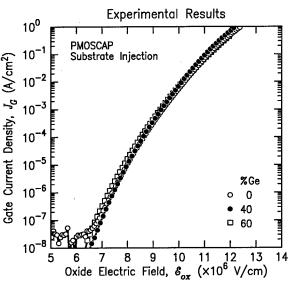

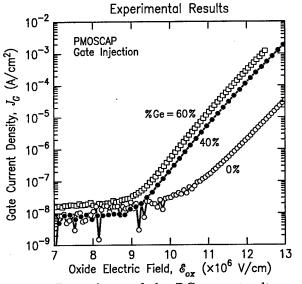

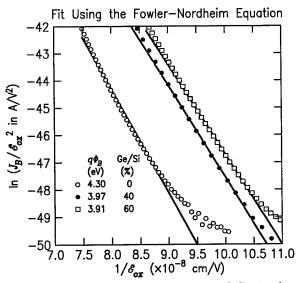

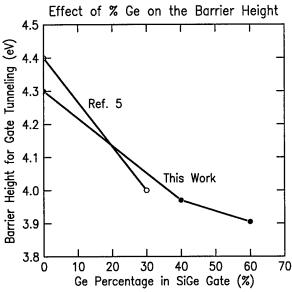

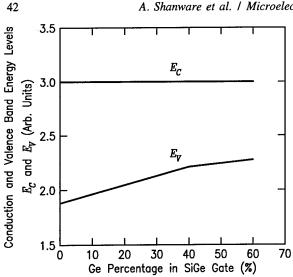

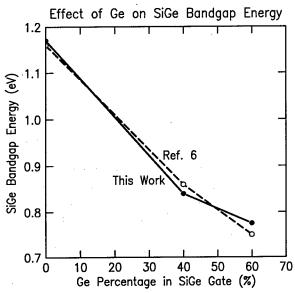

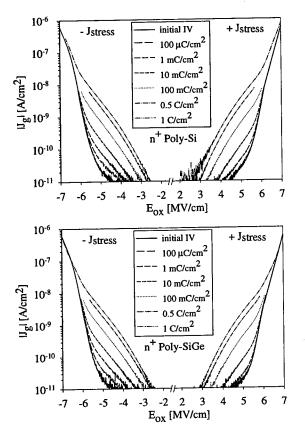

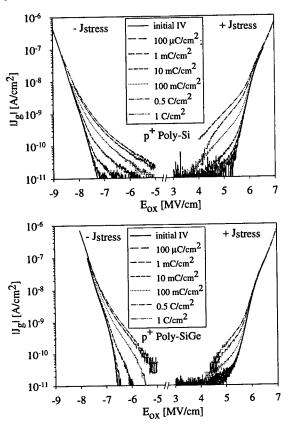

| •                            | ontent in poly-Si <sub>1-x</sub> Ge <sub>x</sub> gate material on the tunnel                                                   |                          | 55        |

| A. Shanwar<br>J. Hauser, J.  | e, H. Massoud, A. Acker, V. Li, M. Mirabedini, K<br>. Wortman                                                                  | . Henson,                | 39        |

| •                            | fect on the reliability of ultrathin gate oxides and o<br>S. De Gendt, P. de Bokx, P. Mertens, M. Heyns                        | oxynitrides              | 43        |

|                              | nperature acceleration of thin oxide time-to-breakd<br>R. Degraeve, N. Pangon, T. Nigam, G. Groeseneke                         |                          | 47        |

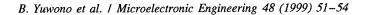

| B. Yuwono,                   | thin oxide and nitride films in the 1nm to 2nm rang<br>, T. Schloesser, A. Gschwandtner, G. Innertsberger<br>W. Krautschneider |                          | 51        |

| vi                 | Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                                                                       |     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

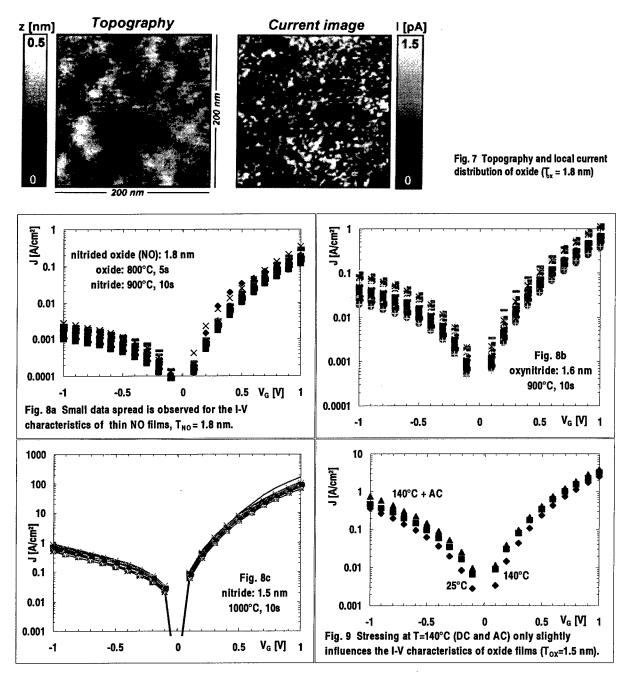

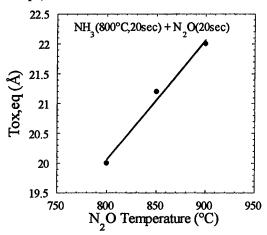

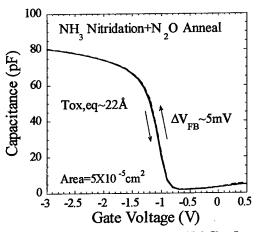

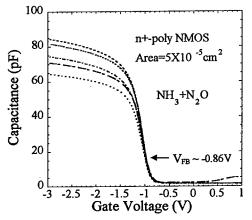

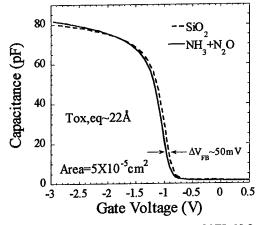

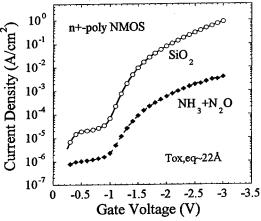

| thermal            | gh-quality stack nitride/oxide gate dielectrics prepared by in-situ rapid N <sub>2</sub> O oxidation of NH <sub>3</sub> -nitrided Si<br>ong, H. Luan, C. Lee, A. Mao, S. Lee, J. Gelpey, S. Marcus, D. Kwong | 55  |

| nitrogen           | of ultrathin gate oxides grown in low-pressure $N_2O$ ambient or on $\alpha$ -implanted silicon                                                                                                              |     |

| A. B               | auer, M. Beichele, M. Herden, H. Ryssel                                                                                                                                                                      | 59  |

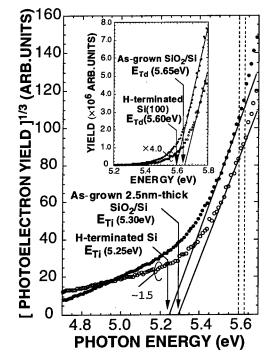

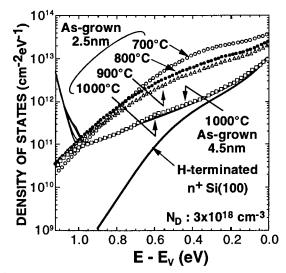

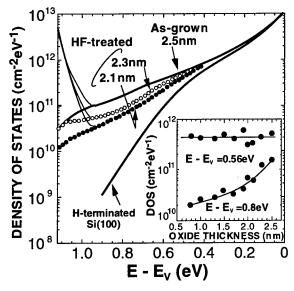

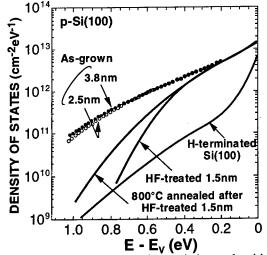

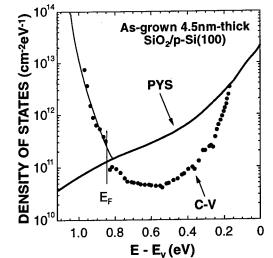

|                    | on yield spectroscopy of electronic states at ultrathin SiO <sub>2</sub> /Si interfaces liyazaki, T. Maruyama, A. Kohno, M. Hirose                                                                           | 63  |

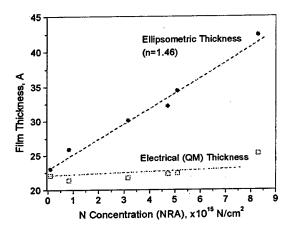

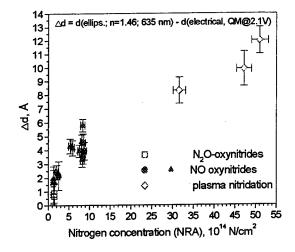

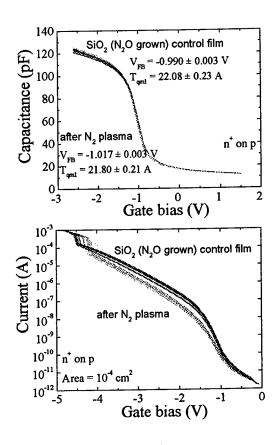

|                    | trided gate dielectrics by plasma-assisted processing<br>usev, D. Buchanan, P. Jamison, T. Zabel, M. Copel                                                                                                   | 67  |

|                    | tomically flat SiO <sub>2</sub> /Si interface formation mechanism based on the oxidation kinetics                                                                                                            |     |

|                    | oh, M. Nagamine, H. Satake, A. Toriumi                                                                                                                                                                       | 71  |

|                    | al surface structure on electronic properties of hydrogenated                                                                                                                                                |     |

|                    | urfaces<br>ittrich, V. Timoshenko, M. Schwartzkopff, E. Hartmann, J. Rappich,<br>ashkarov, F. Koch                                                                                                           | 75  |

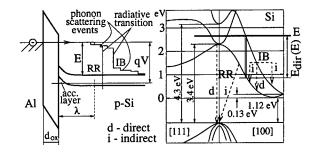

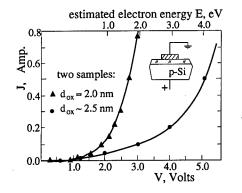

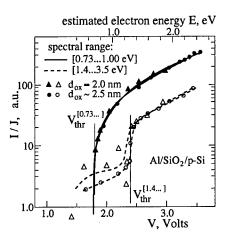

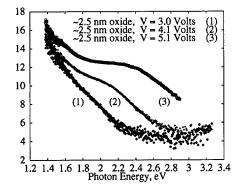

| N. A               | -2.5 nm)/p-Si tunnel junction as a light emitter<br>sli, S. Gastev, I. Grekhov, P. Seegebrecht, A. Shulekin, S. Tyaginov,<br>Vexler, H. Zimmermann                                                           | 79  |

|                    | ics of ultrathin (4-7nm) gate oxides for SiGe quantum well MOS                                                                                                                                               |     |

| structure<br>S. Ka | ar, P. Zaumseil                                                                                                                                                                                              | 83  |

| Theory and         | l modeling                                                                                                                                                                                                   | ·   |

|                    | nsformation processes during oxidation of silicon<br>asquarello                                                                                                                                              | 89  |

|                    | n scattering at the Si-SiO <sub>2</sub> interface<br>i, F. Koch                                                                                                                                              | 95  |

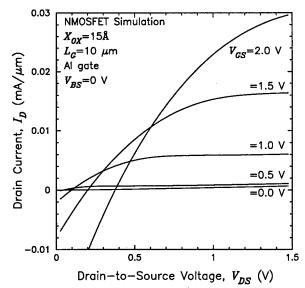

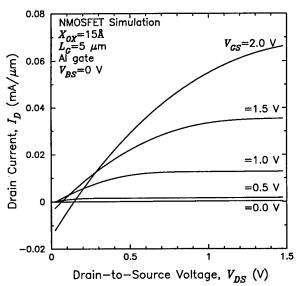

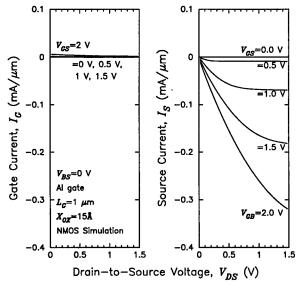

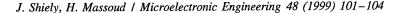

| in the pr          | of the drain-current characteristics of MOSFETs with ultrathin oxides<br>esence of direct tunneling<br>iely, H. Massoud                                                                                      | 101 |

|                    |                                                                                                                                                                                                              |     |

|                    | of polysilicon grain boundaries on MOS based devices<br>Eccleston                                                                                                                                            | 105 |

-

| Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                                           | vii |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Quantum mechanical characterization of E'-type centers in a-SiO <sub>x</sub> films<br>S. Karna, H. Kurtz                                                                         | 109 |

| Nature of the P <sub>b1</sub> interface defect in (100)Si/SiO <sub>2</sub> as revealed by electron spin resonance <sup>29</sup> Si hyperfine structure A. Stesmans, V. Afanas'ev | 113 |

| Structure and electronic property of Si(100)/SiO <sub>2</sub> interface<br>C. Kaneta, T. Yamasaki, T. Uchiyama, T. Uda, K. Terakura                                              | 117 |

| A new model for TDDB lifetime distribution of SiO <sub>2</sub><br>N. Matsukawa, K. Kanebako                                                                                      | 121 |

| Traps and degradation                                                                                                                                                            |     |

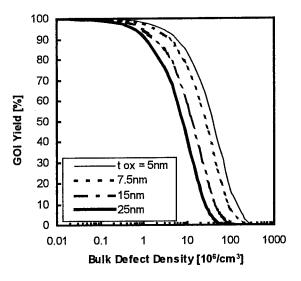

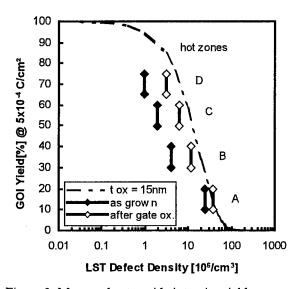

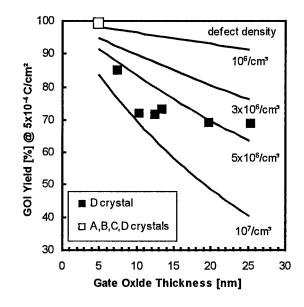

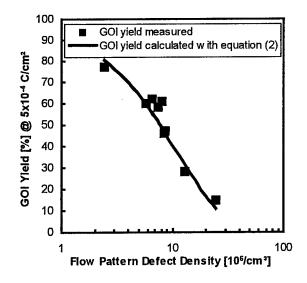

| Dependence of gate oxide integrity on grown-in defect density in<br>Czochralski grown silicon                                                                                    |     |

| U. Lambert, A. Huber, J. Grabmeier, G. Obermeier, J. Vanhellemont, R. Wahlich, G. Kissinger                                                                                      | 127 |

| Suppression of thermal degradation in standard Si/SiO <sub>2</sub> by noble gases<br>A. Stesmans, V. Afanas'ev                                                                   | 131 |

| Relation between hydrogen and the generation of interface state precursors<br>H. Sii, J. Zhang, R. Degraeve, G. Groeseneken                                                      | 135 |

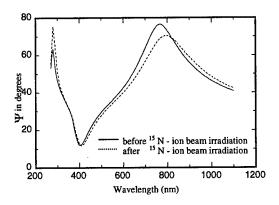

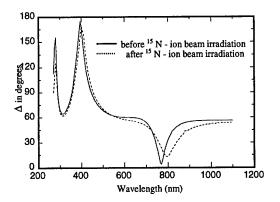

| Hydrogen migration in wet-thermally grown silicon dioxide layers due to high dose <sup>15</sup> N ion beam irradiation                                                           |     |

| K. Maser, U. Mohr, R. Leihkauf, K. Ecker, U. Beck, D. Grambole, R. Grötzschel, F. Herrmann, J. Krauser, A. Weidinger                                                             | 139 |

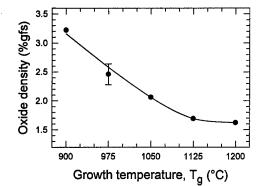

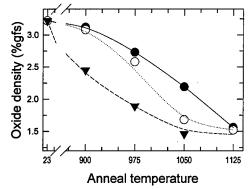

| Relationship between hole trapping and oxide density in thermally grown SiO <sub>2</sub><br>B. Mrstik, V. Afanas'ev, A. Stesmans, P. McMarr                                      | 143 |

| Evidence for spatial distribution of traps in MOS systems after<br>Fowler Nordheim stress                                                                                        |     |

| M. Kerber, U. Schwalke, G. Innertsberger                                                                                                                                         | 147 |

| Separation of electron and hole traps by transient current analysis<br>A. Spinelli, A. Lacaita, M. Rigamonti, D. Ielmini, G. Ghidini                                             | 151 |

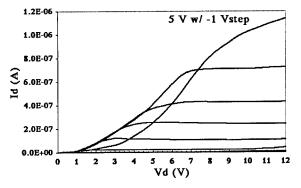

| Validation of the voltage step technique for determination of slow state density in MOS gate oxides                                                                              |     |

| M. Spillane, S. Taylor, M. Uren                                                                                                                                                  | 155 |

| viii                                   | Contents / Microelectronic Engineering 48 (1999) v–xii                                                                               |     |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Two types of traps at<br>J. Albohn, W  | the $Si/SiO_2$ interface characterized by their cross sections . Füssel, N. Sinh, K. Kliefoth, H. Flietner, W. Fuhs                  | 159 |

| from low to high                       | during dynamic operation in 0.25µm CMOS technology<br>temperature<br>). Goguenheim, N. Revil, E. Vincent                             | 163 |

|                                        | neration in Si/SiO <sub>2</sub> /Si structures<br>Devine, W. Warren, K. Vanheusden                                                   | 167 |

| on the theory of p                     | rk for soft and hard breakdown in ultrathin oxides based<br>point contact conduction<br>. Suñé, R. Rodríguez, M. Nafría, X. Aymerich | 171 |

| silicon oxynitride                     | d nitrogen atom: an electron trap in MOS devices with<br>e as the gate dielectric<br>Y. Novikov, V. Gritsenko, H. Wong               | 175 |

| Measurements                           |                                                                                                                                      |     |

| charge profiling                       | onductive oxides on silicon using non-contact surface<br>-O. Lee, M. Brubaker, E. Kamieniecki, J. Ruzyllo                            | 181 |

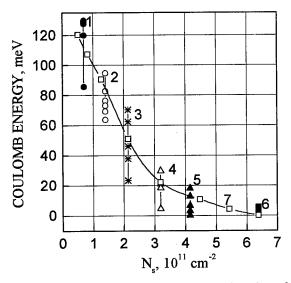

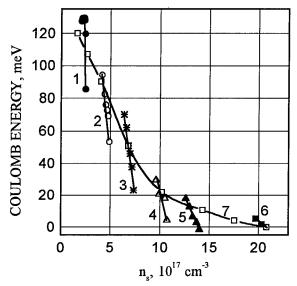

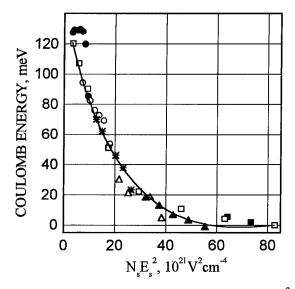

| under surface qua                      | and Coulomb blockade energy in submicron nMOSFETs<br>antization conditions<br>kova, M. Petrichuk, N. Garbar, E. Simoen, C. Claeys    | 185 |

| On the origin of Flicl<br>Y. Maneglia, | ker noise in MOSFETs<br>D. Bauza                                                                                                     | 189 |

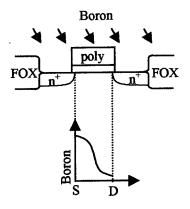

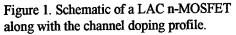

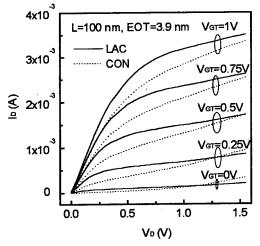

| charge pumping                         | annel length asymmetric channel MOSFETs by using<br>, V. Ramgopal Rao, C. Parikh, J. Vasi, B. Cheng, J. Woo                          | 193 |

| Technology                             |                                                                                                                                      |     |

|                                        | or the growth of ultrathin gate oxide<br>Bearda, M. Houssa, L. Loewenstein, I. Cornelissen,                                          |     |

S. De Gendt, K. Kenis, I. Teerlinck, R. Vos, M. Meuris, M. Heyns 199

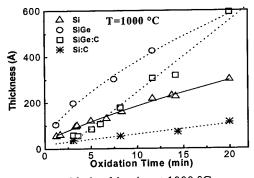

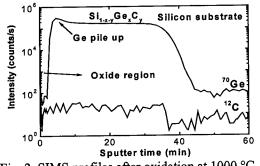

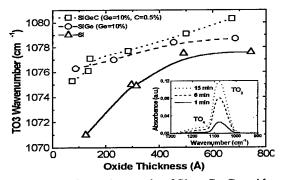

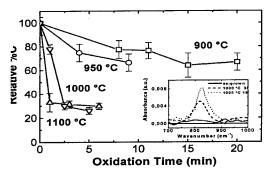

## Thermal dry oxidation of Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> strained layers grown on silicon B. Garrido, A. Cuadras, C. Bonafos, J. Morante, L. Fonseca, M. Franz, K. Pressel 207

| Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                                                        | ix  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

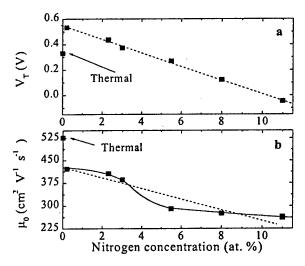

| Electrical characterization of n-channel MOSFETs with oxynitride gate dielectric formed by low-pressure rapid thermal chemical vapor deposition P. Masson, P. Morfouli, J. Autran, J. Wortman | 211 |

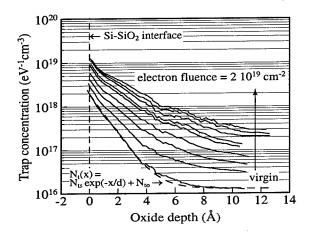

| The effects of radiation-induced defects on $H^+$ transport in SiO <sub>2</sub><br>R. Stahlbush                                                                                               | 215 |

| Surface potential influence on defect passivation kinetics probed by chromium gated metal-oxide-silicon devices LÅ. Ragnarsson, P. Lundgren                                                   | 219 |

| Low temperature-high-pressure grown thin gate dielectrics for MOS applications V.R. Rao, W. Hansch, S. Mahapatra, D. Sharma, J. Vasi, T. Grabolla, I. Eisele                                  | 223 |

| SiGe nMOSFETs with gate oxide grown by low temperature plasma anodisation<br>L. Riley, S. Hall, J. Harris, J. Fernandez, B. Gallas, A. Evans, J. Clarke,<br>J. Humphrey, R. Murray, C. Jeynes | 227 |

| Ion beam synthesis of narrow Ge nanocluster bands in thin SiO <sub>2</sub> films<br>J. von Borany, KH. Heinig, R. Grötzschel, M. Klimenkov, M. Strobel,<br>KH. Stegemann, HJ. Thees           | 231 |

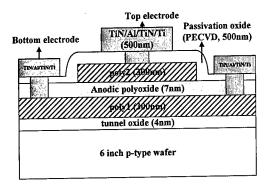

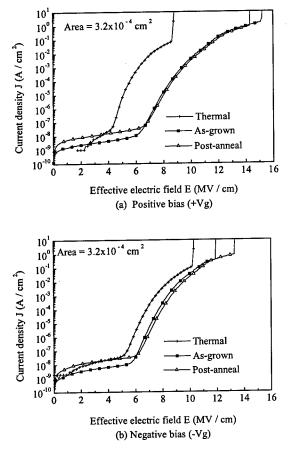

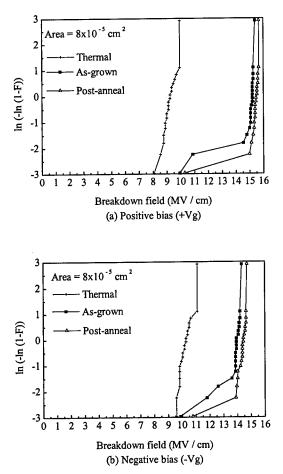

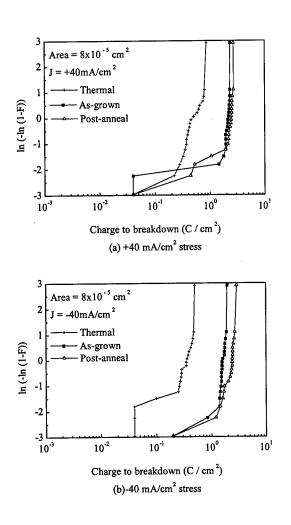

| Characteristics of novel polysilicon oxide by anodic oxidation<br>B. Yeh, J. Liu, M. Chiang                                                                                                   | 235 |

| Silicon carbide                                                                                                                                                                               |     |

| Electronic properties of SiO <sub>2</sub> /SiC interfaces<br>V. Afanas'ev                                                                                                                     | 241 |

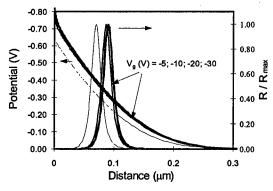

| Effect of post oxidation processing on dry oxides on n-type 4H-SiC<br>C. Anthony, M. Uren                                                                                                     | 249 |

| Reliability of metal-oxide-semiconductor capacitors on 6H-silicon carbide<br>M. Treu, R. Schörner, P. Friedrichs, R. Rupp, A. Wiedenhofer,<br>D. Stephani, H. Ryssel                          | 253 |

| Degradation of 6H-SiC MOS capacitors operated at high temperatures<br>M.Bassler, V. Afanas'ev, G. Pensl, M. Schulz                                                                            | 257 |

| Oxidation of 6H-SiC (0001)<br>L. Simon, L. Kubler, A. Ermolieff, T. Billon                                                                                                                    | 261 |

| Electrical characterization of the amorphous SiC-pSi structure<br>V. Lysenko, I. Tyagulski, Y. Gomeniuk, I. Osiyuk, A. Mikhnov                                                                | 265 |

| x Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                                                                                                                                                                     |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

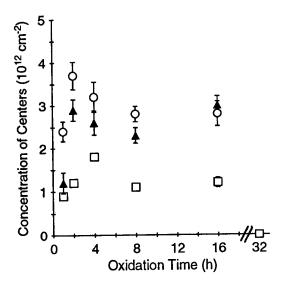

| Dangling bond defects in SiC: The dependence on oxidation time<br>P. Macfarlane, M. Zvanut                                                                                                                                                                                                                   | 269     |

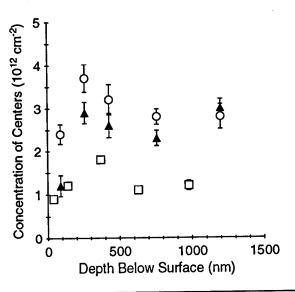

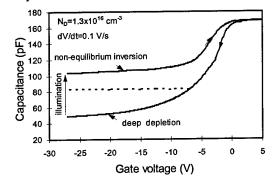

| A simple method for the evaluation of the recombination parameters in SiC MOS structures                                                                                                                                                                                                                     |         |

| T. Rudenko, E. Sveinbjörnsson, M. Sadeghi                                                                                                                                                                                                                                                                    | 273     |

| Defect studies in epitaxial SiC-6H layers on insulator (SiCOI)<br>E. Hugonnard-Bruyère, J. Cantin, H. von Bardeleben, F. Letertre,<br>L. DiCioccio, T. Ouisse                                                                                                                                                | 277     |

| Alternative dielectrics                                                                                                                                                                                                                                                                                      |         |

| <ul> <li>Characteristics of tantalum pentoxide dielectric films deposited on silicon by excimer-lamp assisted photo-induced CVD using an injection liquid source M. Mooney, P. Hurley, B. O'Sullivan, J. Beechinor, JY. Zhang, I. Boyd, P. Kelly, JP. Sénateur, G. Crean, C. Jimenez, M. Paillous</li> </ul> | 283     |

| Structural properties of thin films of high dielectric constant materials on silicon H. Lu, N. Yasuda, E. Garfunkel, T. Gustafsson, J. Chang, R. Opila, G. Al                                                                                                                                                |         |

| The effects of chemical bonding and band offset constraints at Si-dielectric interf<br>on the integration of alternative high-k gate dielectrics into aggressively-scale<br>CMOS Si devices                                                                                                                  | ed      |

| G. Lucovsky, J. Phillips                                                                                                                                                                                                                                                                                     | 291     |

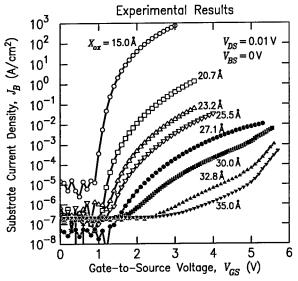

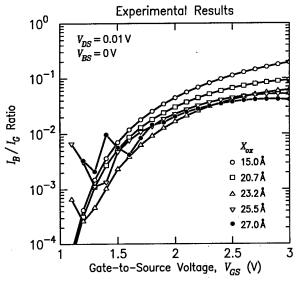

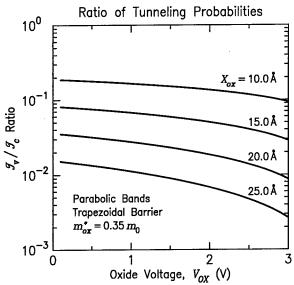

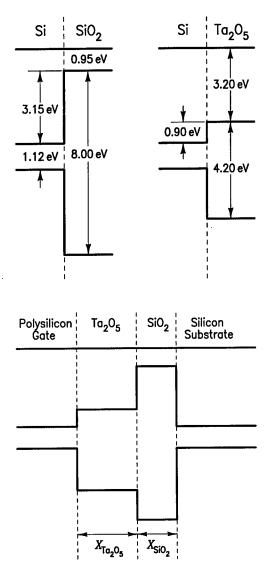

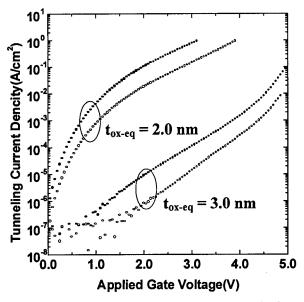

| Modeling the trends in valence-band electron tunneling in NMOSFETs with ultrathin SiO <sub>2</sub> and SiO <sub>2</sub> /Ta <sub>2</sub> O <sub>5</sub> dielectrics with oxide scaling A. Shanware, H. Massoud, E. Vogel, K. Henson, J. Hauser, J. Wortman                                                   | 295     |

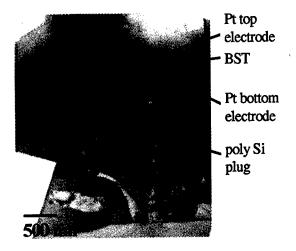

| A novel low-temperature (Ba,Sr)TiO <sub>3</sub> (BST) process with Ti/TiN barrier for<br>Gbit DRAM applications<br>G. Beitel, H. Wendt, E. Fritsch, V. Weinrich, M. Engelhardt, B. Hasler,<br>T. Röhr, R., Bergmann, U. Scheler, KH. Malek, N. Nagel, A. Gschwand                                            | dtner.  |

| W. Pamler, W. Hönlein, C. Dehm, C. Mazuré                                                                                                                                                                                                                                                                    | 299     |

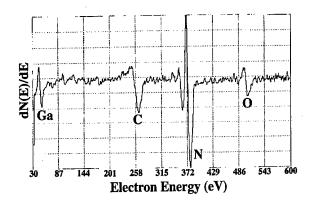

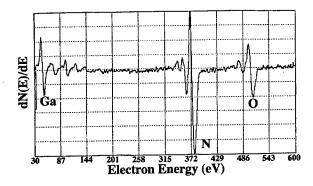

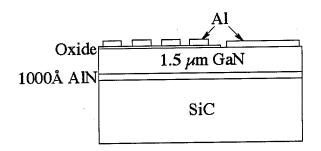

| Charge redistribution at GaN-Ga <sub>2</sub> O <sub>3</sub> Interfaces: A microscopic mechanism for<br>low defect density interfaces in remote plasma processed MOS devices<br>prepared on polar GaN faces                                                                                                   | ·       |

| R. Therrien, H. Niimi, T. Gehrke, G. Lucovsky, R. Davis                                                                                                                                                                                                                                                      | 303     |

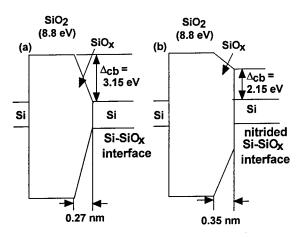

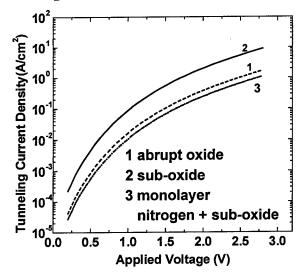

| The effect of interfacial suboxide transition regions on direct tunneling in oxide and stacked oxide-nitride gate dielectrics                                                                                                                                                                                | ۰.<br>ب |

| H. Yang, H. Niimi, Y. Wu, G. Lucovsky, J. Keister, J. Rowe                                                                                                                                                                                                                                                   | 307     |

\_\_\_\_\_.

| Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                                           | xi  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Silicon on insulator                                                                                                                                                             |     |

| Recent advances in wafer bonding of silicon and alternative materials<br>S. Blackstone                                                                                           | 313 |

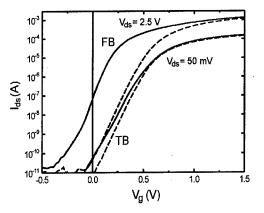

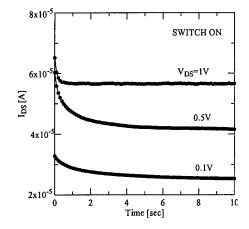

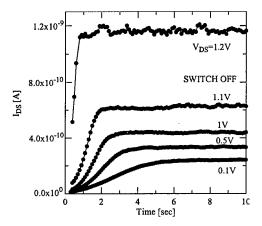

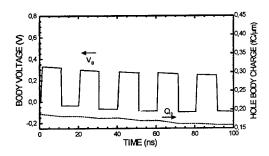

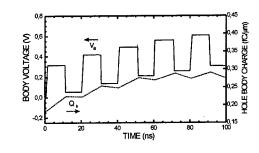

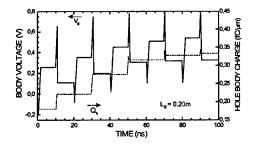

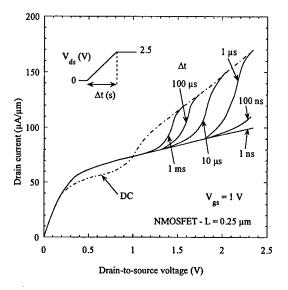

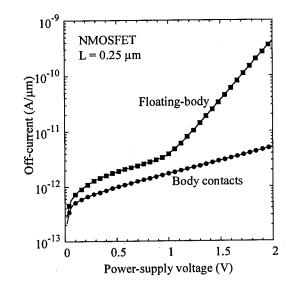

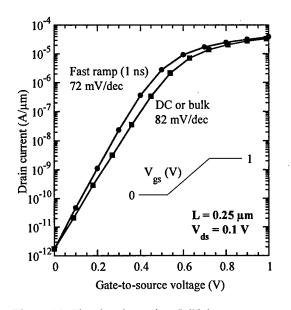

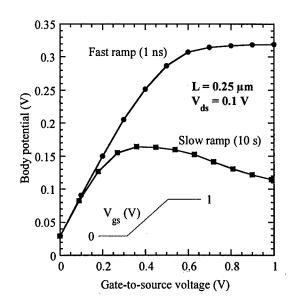

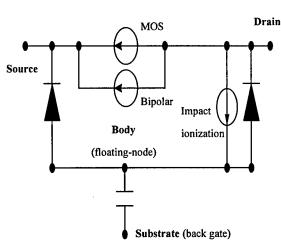

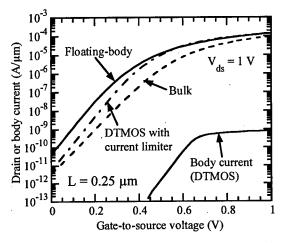

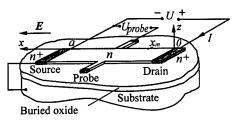

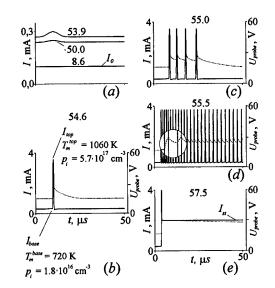

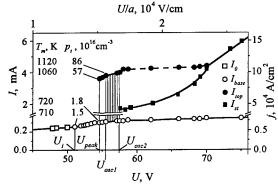

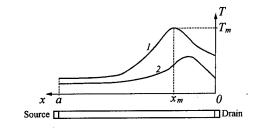

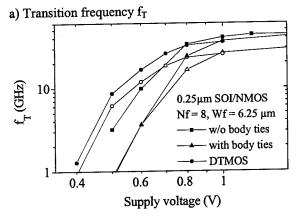

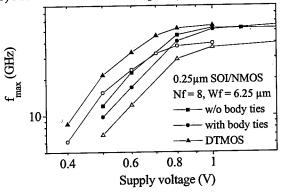

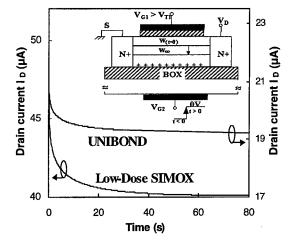

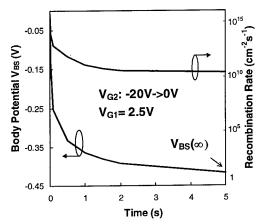

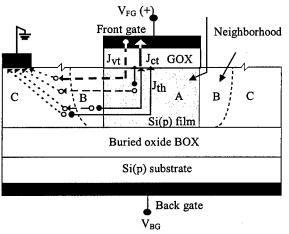

| Physics and characterization of transient effects in SOI transistors<br>A. Lacaita, L. Perron                                                                                    | 319 |

| CMOS/SOI technologies for low-power and low-voltage circuits<br>JL. Pelloie, C. Raynaud, O. Faynot, A. Grouillet, J. Du Port de Pontcharra                                       | 327 |

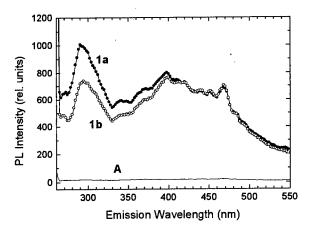

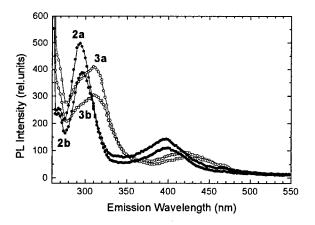

| Photoluminescence spectra of SIMOX buried oxide layers prepared under<br>various conditions<br>L. Rebohle, A.G. Revesz, W. Skorupa, H.L. Hughes                                  | 335 |

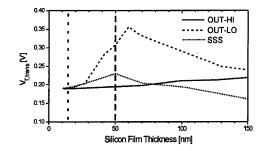

| Investigation of SOI MOSFETs with ultimate thickness<br>T. Ernst, D. Munteanu, S. Cristoloveanu, T. Ouisse, S. Horiguchi,<br>Y. Ono, Y. Takahashi, K. Murase                     | 339 |

| High-amplitude and high-frequency oscillations of temperature and current<br>in SOI structures<br>V. Dobrovolsky, L. Ishchuk, G. Ninidze, M. Balucani, A. Ferrani                | 343 |

| The effect of confinement and temperature on the initial hole trapping efficiency<br>of buried oxide films<br>M. Zvanut, Wang Chun, R.Stahlbush                                  | 347 |

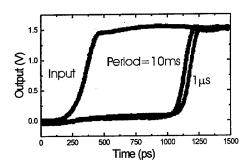

| Designing MOS/SOI transistors for high-frequency and low-voltage applications<br>V. Ferlet-Cavrois, A. Bracale, C. Marcandella, O. Musseau, J. Pelloie,<br>C. Raynaud, O. Faynot | 351 |

| Model for the extraction of the recombination lifetime in partially depleted<br>SOI MOSFETs<br>D. Munteanu, S. Cristoloveanu                                                     | 355 |

| Hydrogen thermal stability in buried oxides of SOI structures<br>D. Ballutaud, A. Boutry-Forveille, A. Nazarov                                                                   | 359 |

| Reactions and diffusion during annealing-induced H <sup>+</sup> generation in SOI buried oxides K. Vanheusden, D. Fleetwood, R. Devine, W. Warren                                | 363 |

| Direct sub-µm lateral patterning of SOI by focused laser beam induced oxidation R. Deutschmann, M. Huber, R. Neumann, K. Brunner, G. Abstreiter                                  | 367 |

| Sub-band-gap impact ionization events in transient regimes of floating body<br>SOI devices<br>A. Ionescu, A. Chovet                                                              | 371 |

•

| xii                                          | Contents / Microelectronic Engineering 48 (1999) v-xii                                                                                                              |     |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Theory of the MOS/SO<br>M. Badri, B. M       |                                                                                                                                                                     | 3   |

| n-MOSFET with b                              | mperature kink-effect in SIMOX SOI fully depleted<br>ias temperature instability of buried oxide<br>Barchuk, V. Lysenko, JP. Colinge                                | 3   |

| boron doped silico                           | properties of the SOI structure formed from the heavily<br>n with using of the smart-cut technology<br>. Popov, V. Stas, A. Gutakovskii, A. Plotnikov, V. Obodnikov | 3   |

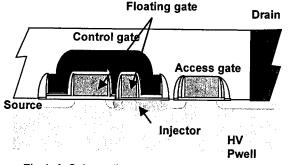

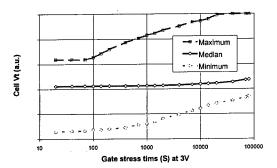

| Non-volatile memory                          |                                                                                                                                                                     |     |

| Low voltage flash men<br>M. Mastrapasq       | nory by use of substrate bias<br>ua                                                                                                                                 | 3   |

| Oxide scaling limit for<br>J. Stathis, D. D  | future logic and memory technology<br>iMaria                                                                                                                        | 3   |

| Reliability of thin diele<br>A. Modelli      | ectric for non-volatile applications                                                                                                                                | 4   |

|                                              | O interpoly dielectric of FLOTOX EEPROM cells<br>, A. Kux, R. Kakoschke, H. Palm                                                                                    | 4   |

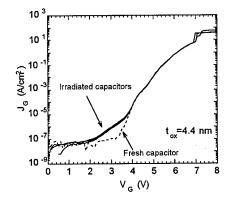

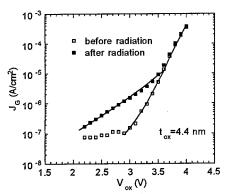

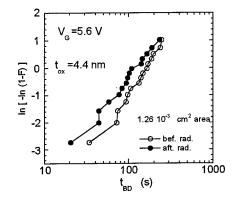

| -                                            | rs with poly-Si and poly-Si <sub>0.7</sub> Ge <sub>0.3</sub> gate material<br>Holleman, C. Salm, P. Woerlee                                                         | 4   |

|                                              | data retention in sub-half-micron embedded EEPROMs,<br>, J. Dijsktra, F. Kuper, R. Verhaar                                                                          | 4   |

| Off-stochiometric silic<br>F. Irrera, F. Rus | on oxides for applications in low-voltage flash memories                                                                                                            | 4   |

|                                              | down of SiO <sub>2</sub> -layers due to hot and ballistic electron transport<br>Schreiber, T. Barfels, A. von Czarnowski                                            | 4   |

|                                              | SiO <sub>2</sub> for quantum dot memory applications artín, X. Martínez, M. Garriga, X. Aymerich                                                                    | . 4 |

Microelectronic Engineering 48 (1999) xiii

#### MICROELECTRONIC ENGINEERING

www.elsevier.nl/locate/mee

## Preface

The INFOS'99 conference on Insulating Films on Semiconductors was organized by the University of Erlangen-Nürnberg at the Kloster Banz Conference Center near Lichtenfels, approximately 80 km north of Erlangen in Germany. This conference was the 11th sequel of the series started 1979 in Durham England. INFOS'99 attracted 130 participants from industry, research institutes, and universities. Attendants were registered from 20 different nations. The biennial European conference series specializing in insulating films on semiconductors will be continued by INFOS'01 to be held in Udine, Italy in the year 2001.

Since INFOS'99 was the last conference in this century of this series specializing on insulating films on semiconductors, this proceedings volume presents a review of the achievements of the MOS technology made in the past forty years and gives an outlook into the future of the next century by two invited talks. The present status of our understanding the insulating properties of films and their interface to semiconductors is surveyed by further 11 invited and 80 contributed papers. Special emphasis was given at this conference to the understanding of the growth, the properties, and the limits of ultrathin gate oxides on silicon; however, sessions devoted to oxide traps, alternative dielectrics, degradation and cleaning of the interface were also included among others. Oxides on silicon carbide were discussed at this conference for the first time. Non-volatile memory and silicon-on-insulator (SOI) properties were discussed in special workshops.

The organizational load of the conference was distributed on many collaborators. The service of the program committee, of the session chair persons, and of many conference attendees who reviewed all the publication manuscripts during the conference, was very much appreciated and made the quick publication of these proceedings possible. Special thanks also go to the coworkers from the Institute of Applied Physics at the University of Erlangen and from the Center of Applied Energy Research (ZAE Bayern) who helped to run the conference. The administration work of the registration and the finances by Mrs. G. Loy is also gratefully acknowledged. The staff of the Hanns Seidel Foundation made the stay at Kloster Banz during the conference very pleasant; this service to the conference is also gratefully acknowledged.

Erlangen, July 1999

M. Schulz R. Brendel

Microelectronic Engineering 48 (1999) xiv

## **Conference Chairman:**

M. Schulz, University of Erlangen, Institute of Applied Physics, Staudtstr. 7, D-91058 Erlangen/Germany

#### Workshop Organizers:

"Advanced Silicon on Insulator Materials and Devices" S. Cristoloveanu, LPCS Grenoble, France

"The Physics and Technology of Non-Volatile Memory Devices" E. Sangiorgi, Universita di Udine, Italy

#### **Program Committee:**

V.V. Afanasev, St. Petersburg, Russia P. Balk, DIMES, Delft, The Netherlands S. Cristoloveanu, LOCS, Grenoble France

- R. Degraeve, IMEC, Leuven, Belgium

- W. Eccleston, University of Liverpool, UK

- O. Engström, Chalmers University, Sweden

- W. Hönlein, Siemens AG, München, Germany

- F. Koch, Technical University, München, Germany

- F. Kuper, Philips Semiconductors, Nijmegen, The Netherlands

- V.G. Litovchenko, Academy of Science, Kiev, Ukraine

- J. Morante, Universitat Barcelona, Spain

- J. Moreland, Wacker Siltronic, Burghausen, Germany

- H. Przewlocki, Institute of Technology, Warsaw, Poland

- E. Sangiorgi, Universita di Udine, Italy

- M. Schulz, University of Erlangen-Nürnberg, Erlangen, Germany

- A. Stesmans, Universiteit Leuven, Belgium

- M. Uren, DERA, Malvern, UK

- D. Vuillaume, CNRS Institut d'Electronique, Lille, France

#### **International Advisors:**

H. Iwai, Toshiba Kawasaki, Japan D.J. DiMaria, IBM Yorktown Heights, NY USA H.Z. Massoud, Duke University, Durham NC USA

#### Local Committee:

M. Schulz, Conference Chair R. Brendel, Proceedings Editor G. Loy, Secretary

## We wish to thank the following for their contribution to the success of this conference:

Stifterverband für die Deutsche Wissenschaft European Office of Aerospace Research and Development Airforce Office of Scientific Research United States Air Force Research Laboratory Infineon Technologies Wacker Siltronic IEEE Electron Device Society

www.elsevier.nl/locate/mee

## REVIEW AND OUTLOOK AT THE TURN OF THE CENTURY

Microelectronic Engineering 48 (1999) 3-6

#### MICROELECTRONIC ENGINEERING

www.elsevier.nl/locate/mee

## 40 years MOS technology - from empiricism to science

Pieter Balk

DIMES, Delft University of Technology, 2600 GB Delft, The Netherlands

This paper summarizes the development of the MOS field effect technology from the early beginnings. It will deal with its empirical basis and present some examples of the way the technology progressed: the search for the ideal semiconductor-dielectric system, the continuous battle against impurities and the tenacity with which the problem of the interaction of hydrogen with Si/SiO<sub>2</sub> interfacial defects has defied complete interpretation. A few highlights from the period under discussion will conclude the review.

#### 1. INTRODUCTION

It took 35 years after Lilienfeld's first 1925 patent on a field effect device to turn his idea into a usable structure where a substantial modulation of the conduction could be attained. To reach this point fundamental insight into the characteristics of metals, semiconductors and insulators and into the behavior of contacts between these materials had to be acquired and basic knowledge of their technology had to be obtained. Only on this foundation could the MOS field effect technique live up to its potential and develop over the next 40 years -from 1960 till today- into a technology of great economic importance for the fabrication of ever faster devices of ever smaller dimensions at an ever lower price.

#### 2. EMPIRICAL BASIS

Field effect devices, as described in two patents of Lilienfeld [1,2] and in a later patent by Heil [3] would only become attractive when implemented in the silicon technology. However, in the forties and fifties the development of this technology was directed towards bipolar devices, whereas field effect devices received hardly any attention.

Nevertheless, the bipolar work produced some important insights for our topic of interest. One was the possibility to reduce the high density of interface states (broken bonds) [4], as found underneath the gate electrode on "real" (etched) surfaces, by thermal oxidation [5[. Equally important was separating the conduction of the surface inversion layer from the bulk conduction by using a source and a drain diode. In this manner a hundred percent modulation of this parameter in field effect devices with MOS gate system could be easily obtained. Last, but not least, thermally oxidized silicon had found an important application for local masking in the planar process [6], which is essential for the fabrication of small devices and integrated circuits.

#### 3. FURTHER DEVELOPMENT

The first properly operating MOS field effect devices became available around 1960 [7]. They utilized a 200 nm gate oxide and an Al gate. These devices had stable characteristics and constituted a good starting point for further development of the technique up to the present time.

This development demanded new and more sensitive methods for electrical characterization, as charge pumping [8], to explore the distribution of interface states in the gate area of devices, and RTS (random telepraph signal) studies, which allow electrical characterisation of single interface traps in small devices [9,10]. For atomic identification of defects ESR (electron spin resonance) [11-13] has proven to be a powerful approach.

0167-9317/99/\$ - see front matter © 1999 Elsevier Science B.V. All rights reserved. PII: S0167-9317(99)00327-5 In the field of material science questions to be dealt with were : Is there an alternative for the  $Si/SiO_2$  system? What parameters determine the carrier mobility in the channel? What is the mechanism of carrier transport and trapping in the dielectric in relation to its defect structure? In which ways can this structure be optimized? What is the role of impurities and the micromorphology of the interface in determining the properties of the MOS system? In what manner can these parameters be affected?

In the following we will try to characterize the developments in the MOS field during the past 40 years using three examples : the search for alternatives for the Si/SiO<sub>2</sub> system; controlling impurities in SiO<sub>2</sub>; the interaction between hydrogen and Si/SiO<sub>2</sub> interfacial defects. It will not be our intent to give an exact description of our present understanding. We will rather indicate how our insight developed and what complications were encountered along the way.

## 4.THE CHOICE FOR Si/SiO<sub>2</sub>

Notwithstanding the potential advantages of other semiconductors, silicon has one very attractive feature : the open flexible structure of its glassy oxide SiO<sub>2</sub>, thermally grown on crystalline Si, which provides a relatively easy fit to this substrate and thus a low density of interface states [14]. Moreover, its properties are conveniently modified by incorporation of small amounts of dopants like N [15], F [16] or Cl [17]. Only in recent years the rather low value of the dielectric constant along with the small available area in advanced DRAM capacitors has created renewed demand for alternative materials with higher dielectric constant. Unfortunately, with the exception of Si<sub>3</sub>N<sub>4</sub>, the alternative dielectrics that may be of interest are polycrystalline, which tends to cause gate leakage. By optimization of the technology and the use of very thin SiO<sub>2</sub> interlayers one has learned to live with this problem. Thus, high  $\varepsilon$  dielectrics like Ta2O5 and TiO2, and ferro-electrics like BaSrtitanate appear to be making the grade [18].

Since the sixties there has been an interest in producing MOS devices on non-Si substrates, like Ge, GeSi, SiC or some III-V compound. The aim would be, for example, obtaining a higher channel mobility or a higher operating temperature (because of a larger bandgap). This requires finding a dielectric which would provide a similarly good fit to the substrate as  $SiO_2$  does to Si. For Ge the search for a suitable dielectric has been unsuccessful. For the binary semiconductors one has an extra element to contend with and also in this case break-throughs have not been reported.

#### 5. CONTROLLING IMPURITIES

Metallic impurities generally have a deleterious effect on the properties of MOS structures. The drift in device characteristics caused by Na in the gate oxide may be strongly reduced by trapping this impurity in a thin phosphosilicate glass film grown on top of the thermal oxide, originally (and accidentally) obtained as a "byproduct" of doping the source and drain of n-channel devices in the planar technology. Compromises between polarisibility of the film (which negatively affects its stability) and the maximum protection against Na drift can be made very precisely since the SiO2- $P_2O_5$  system has been well characterized [19]. Using this approach, the maximum tolerable Na concentration in production equipment could be allowed to increase to a level which was considered easy to control. Unfortunately, the development towards thinner gate oxides forced to the use of ever thinner and less concentrated phosphosilicate films which ultimately caused the complete loss of protection against Na.

For this reason a second method, the use of a gaseous Cl compound (for example TCE, trichloroethene,  $C_2HCl_3$ ) became dominant in the seventies [20]. The chlorine compound not only cleans the furnace tube, but, by injecting it as an additive to the oxidant, is instrumental in substantially reducing the Na concentration in the gate oxide. An added advantage of the Cl-method was that it is simpler to use.

Present day ultra-clean processing techniques, which were introduced around 1990, constitute an integral approach to device fabrication. They are not only concerned with metallic impurities, but also consider the roughening of the surface, which effectively causes the film thickness to vary over the surface, and the deposition of particulate matter and organics. Gaseous Cl compounds are still part of the cleaning process. However, also liquid etching appears to be an unavoidable step in the ultra-clean technology [21].

## 6. HYDROGEN AND INTERFACIAL DEFECTS

The interaction between hydrogen and interface states has occupied the attention of the MOS community throughout its history. Only at the present time the problem appears to approach a solution. Part of the difficulty is the omnipresence of hydrogen in MOS structures and the difficulty of determining its concentration and state of bonding [22].

Passivation of silicon dangling bond interfacial traps by reaction with molecular hydrogen [23,24] or atomic hydrogen (formed at the Al-SiO<sub>2</sub> interface) [25] at temperatures around 400 ° C was early recognized as an effective way to enhance the transconductance in field effect devices. Heating in forming gas ( a mixture of  $H_2$  and  $N_2$  ) was originally performed to improve the bond between gate electrode and gate dielectric, and to provide improved electrical contact to source and drain. In later years indications were obtained that under irradiation in MOS systems containing hydrogen also the reverse process, the depassivation of interface traps, could take place. In this case hydrogen would be transported through the oxide and react at the interface as OH<sup>-</sup> radicals [26], H atoms [27] or, as a later insight, protons [28].

Experiments, in which samples were exposed to atomic H at different temperatures, indicated the existence of an equilibrium concentration of passivated interface states [29]. It was also concluded from experiments with atomic H that not all interface states generated are of the dangling bond type [30] but that some may have a rather different structure. One possibility is the interfacial defect which has been suggested to occur in UVirradiated samples, where H would be bonded to a lone electron pair at the bridging O-atom in the Si-O-Si network at the interface [31]. The latter structure has been also proposed to be the long known oxidation-induced fixed charge center, which would be located at or near the interface [32]. A complicating factor in this work is that the generation of interface states appears to depend on the detailed structure of the MOS system ( thermally grown SiO<sub>2</sub>; various types of SOI).

#### 7. HIGHLIGHTS

The results of the past 40 years in our field have shown the development of a considerably deeper insight in the details of increasingly complex systems of strongly reduced dimensions ( by a factor of 50 for the thickness of gate oxide) during this period [33]. New phenomena were particularly reported during the first 20 years. We will only mention here the effects of quantisation in inversion layers [34] and carrier trapping in dielectrics [35]. The rapidly growing MOS technology provided high quality samples for physical experimentation, which in turn contributed strongly to the development of the field. An excellent demonstration of this development over the second 20 years may be found in the proceedings of the international biennial conference on insulating films on semiconductors ( Infos ), published since 1979.

A period of 40 years equals approximately the duration of a professional's life; it is about the maximum time span one can report on from direct experience. Many scientists, presently working in the MOS area, have not personally known the workers of the first hour, who made such decisive contributions in shaping the field. As typical representatives of this group I would like you to remember Sir Neville F.Mott (Cambridge) : growth of SiO<sub>2</sub> [36]; Nic Klein (Haifa) : dielectric breakdown [37]; Ed Nicollian (Murray Hill, N.J. /Charlotte N.C. : hydrogen in SiO<sub>2</sub> [38] ; electrical measurement techniques [39]. They passed away, but their work had a strong impact on our field. Their names stand for scientific excellence, and are also typical for the international character of the MOS community.

#### REFERENCES

- 1. J.E.Lilienfeld, U.S.Patent 1745175 (1925).

- 2. J.E.Lilienfeld, U.S.Patent 1900018 (1928).

- 3. O.Heil, U.K.Patent 439457 (1935).

- 4. W.Shockley and G.L.Pearson, Phys.Rev. 74, 232 (1935).

- 5. M.M.Atalla, E.Tannenbaum and E.J.Scheibner, Bell Syst.Tech.J. 38, 749 (1959).

- 6. J.A.Hoerni, IRE Electron Devices Meet., Washington D.C., (1960).

- 7. D.Kahng, U.S.Patent 3102230 (1960).

- G.Groeseneken, N.Beltran and H.E.Maes, IEEE Trans. Educ. 31, 42 (1984).

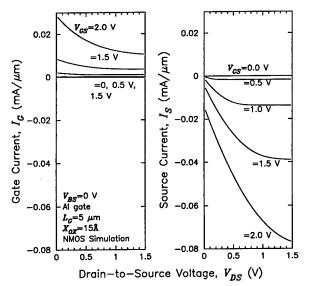

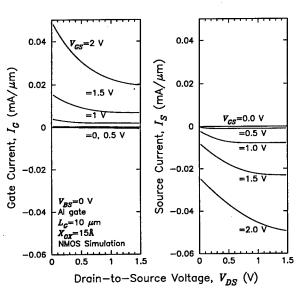

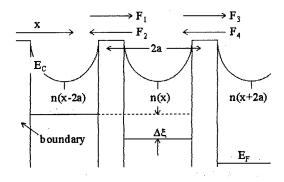

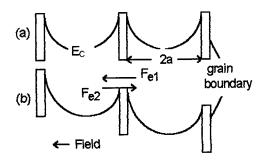

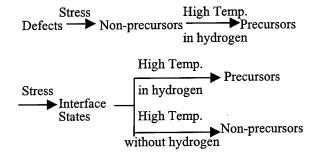

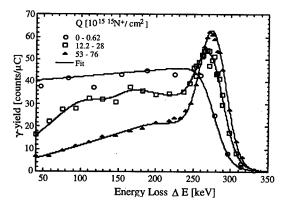

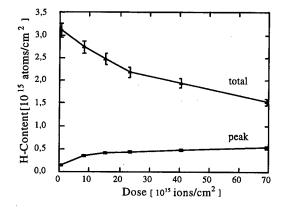

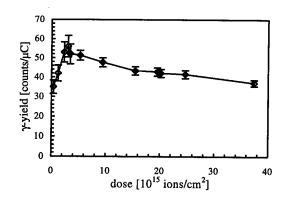

- M.J.Kirton and M.J.Uren, Adv. in Phys. 38, 367 (1988).