Transistor Level Micro Placement and Routing for Two-Dimensional Digital VLSI Cell Synthesis

Michael Anthony Riepe

CSE-TR-390-99

**April** 1999

DISTRIBUTION STATEMENT A

Approved for Public Release

Distribution Unlimited

Computer Science and Engineering Division Room 3402 EECS Building

### THE UNIVERSITY OF MICHIGAN

Department of Electrical Engineering and Computer Science Ann Arbor, Michigan 48109-2122 USA

19990616 038

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Form Approved<br>OMB NO. 0704-0188                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comment regarding this burden estimates or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503. |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                  |

| 1. AGENCY USE ONLY (Leave blan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2. REPORT DATE                                                                                                                                                                                                                                                                                                                                                                                                                                | 3. REPORT TYPE AND DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MICRO PLACEMENT ANI<br>DIGITAL VLSI CELL SYN                                                                                                                                                                                                                                                                                                                                                                                                  | ROUTING FOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NDING NUMBERS                                                                                                                                                                                                                                                                                                                                                    |

| 6. AUTHOR(S) Michael Anthony Riepe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AH04-94-G-0327                                                                                                                                                                                                                                                                                                                                                   |

| 7. PERFORMING ORGANIZATION Univerity of Michigan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RFORMING ORGANIZATION<br>PORT NUMBER                                                                                                                                                                                                                                                                                                                             |

| Department of Electrical<br>1301 Beal Ave.<br>Ann Arbor, MI 48109-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                  |

| 9. SPONSORING / MONITORING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AGENCY NAME(S) AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PONSORING / MONITORING<br>GENCY REPORT NUMBER                                                                                                                                                                                                                                                                                                                    |

| U.S. Army Research Office<br>P.O. Box 12211<br>Research Triangle Park, No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e<br>C 27709-2211                                                                                                                                                                                                                                                                                                                                                                                                                             | AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .033790.70-EL                                                                                                                                                                                                                                                                                                                                                    |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                  |

| The views, opinions and/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | r findings contained in this rep<br>he Army position, policy or do                                                                                                                                                                                                                                                                                                                                                                            | oort are those of the author(s) ecision, unless so designated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | and should not be construed as by other documentation.                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                  |

| 12a. DISTRIBUTION / AVAILABILIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Y STATEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12 b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                |

| 12a. DISTRIBUTION / AVAILABILIT Approved for public releas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                |

| Approved for public release  13. ABSTRACT (Maximum 200 word The automated synthes is an important comport approaches based on the straightforward one-dire known. However, these down when faced with efficient modeling and formed explicitly and the merged structures are suplacement. The synthese chains are broken at the ing placement, an order chain. Different chain of                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                               | SI leaf cells, referred to as the integrated circuit design end of Uehara & VanCleempura problem for which optimally applicable to static CMOS ar methodology is centered aring. Chains of diffusionarea and global routing. In a scally compatible adjacent traiting a static transistor chain is sulting sub-chains passed to and a location and orientation to by changing the relative serious control of the control o | ne cell synthesis problem, invironment. Traditional it pose this problem as a l solution methods are circuits and they break around techniques for the merged transistors are ddition, more arbitrary insistors to overlap during formation step. These the placement step. Duron is assigned to each subizes of the sub-chains and                              |

| Approved for public release  13. ABSTRACT (Maximum 200 work The automated synthes is an important compor approaches based on the straightforward one-dire known. However, these down when faced with efficient modeling and formed explicitly and the merged structures are suplacement. The synthese chains are broken at the ing placement, an order chain. Different chain of their routing contribution.  14. SUBJECT TERMS                                                                                                                                                                                                                                                                                            | de; distribution unlimited.  des)  of mask geometry for VLS  nent of any structured custom  e classic functional cell style mensional graph optimization  e approaches are only directly more exotic logic styles. Ou  optimization of geometry sha  heir ordering optimized for a  upported by allowing electric  sis flow in TEMPO begins w  e diffusion breaks and the res  ring is found for each chain a  orderings affect the placement | SI leaf cells, referred to as the integrated circuit design end of Uehara & VanCleempura problem for which optimally applicable to static CMOS ar methodology is centered aring. Chains of diffusionarea and global routing. In a scally compatible adjacent traiting a static transistor chain is sulting sub-chains passed to and a location and orientation to by changing the relative serious control of the control o | ne cell synthesis problem, invironment. Traditional to pose this problem as a land solution methods are accircuits and they break around techniques for the merged transistors are addition, more arbitrary ansistors to overlap during formation step. These the placement step. Duron is assigned to each subtizes of the sub-chains and onal compaction step. |

## TRANSISTOR LEVEL MICRO PLACEMENT AND ROUTING FOR TWO-DIMENSIONAL DIGITAL VLSI CELL SYNTHESIS

by

Michael Anthony Riepe

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 1999

### **Doctoral Committee:**

Professor Karem Sakallah, Chair Professor Richard Brown Professor John Hayes Assistant Professor Marios Papaefthymiou Professor Rob Rutenbar, Carnegie Mellon University

### **ABSTRACT**

# TRANSISTOR LEVEL MICRO PLACEMENT AND ROUTING FOR TWO-DIMENSIONAL DIGITAL VLSI CELL SYNTHESIS

### by Michael Anthony Riepe

Chair: Karem A. Sakallah

The automated synthesis of mask geometry for VLSI leaf cells, referred to as the cell synthesis problem, is an important component of any structured custom integrated circuit design environment. Traditional approaches based on the classic functional cell style of Uehara & VanCleemput pose this problem as a straightforward one-dimensional graph optimization problem for which optimal solution methods are known. However, these approaches are only directly applicable to static CMOS circuits and they break down when faced with more exotic logic styles.

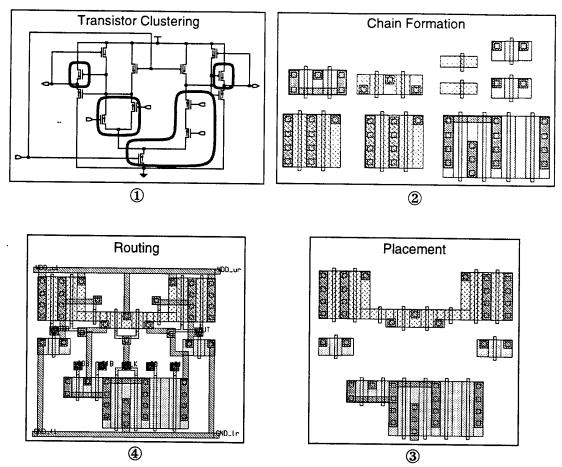

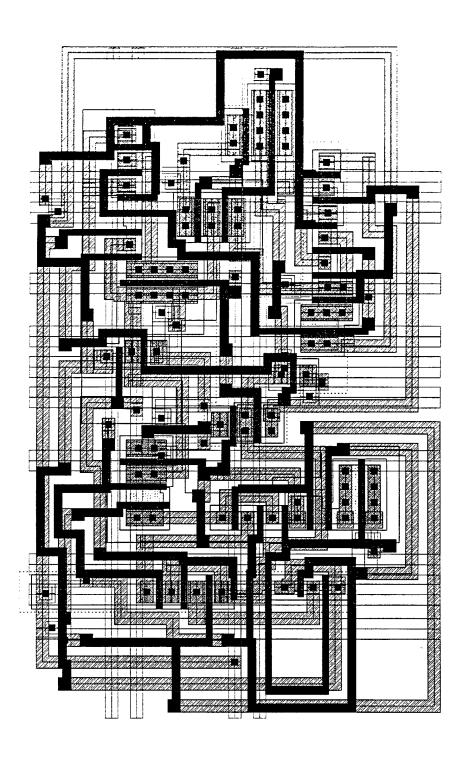

There is an increasing need in modern VLSI designs for circuits implemented in high-performance logic families such as Cascode Voltage Switch Logic (CVSL), Pass Transistor Logic (PTL), and domino CMOS. Circuits implemented in these non-dual ratioed logic families can be highly irregular with complex geometry sharing and non-trivial routing. Such cells require a relatively unconstrained two-dimensional full-custom layout style which current methods are unable to synthesize. In this work we define the synthesis of complex two-dimensional digital cells as a new problem which we call transistor-level micro-placement and routing. To address this problem we develop a complete end-to-end methodology which is implemented in a prototype tool named TEMPO. A series of experiments on a new set of benchmark circuits verifies the effectiveness of our approach.

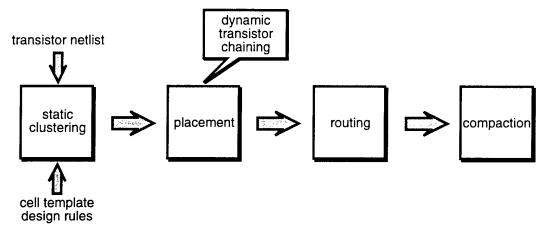

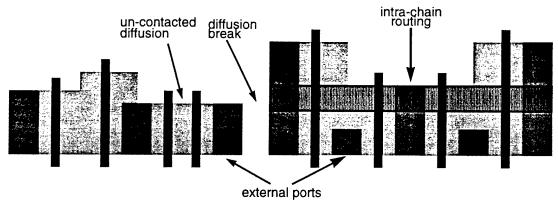

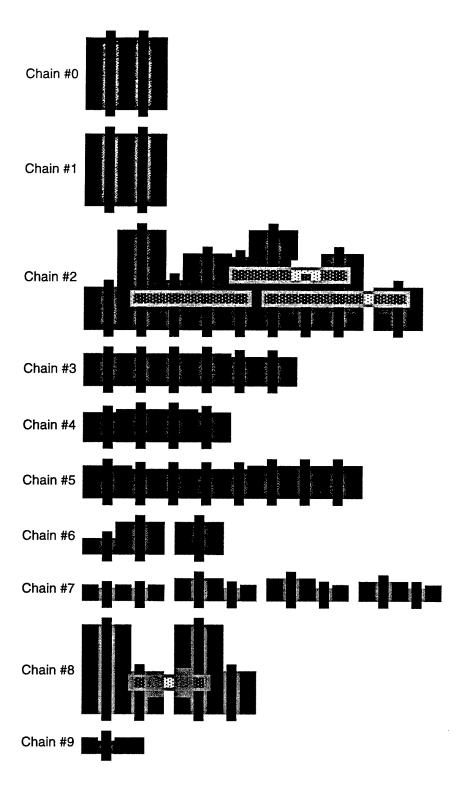

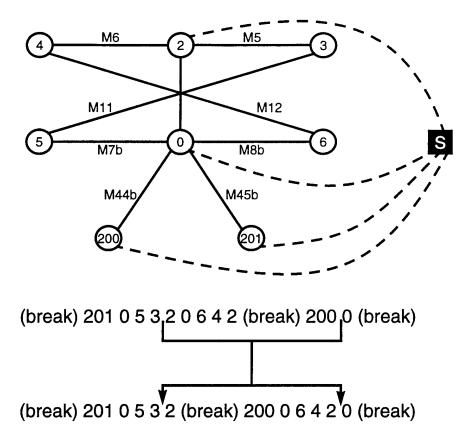

Our methodology is centered around techniques for the efficient modeling and optimization of geometry sharing, and is supported at two different levels. Chains of diffusion-merged transistors are formed explicitly and their ordering optimized for area and global routing. In addition, more arbitrary merged structures are supported by allowing electrically compatible adjacent transistors to overlap during placement. The synthesis flow in TEMPO begins with a static transistor chain formation step. These chains are broken at the diffusion breaks and the resulting sub-chains passed to the placement step. During placement, an ordering is found for each chain and a location and orientation is assigned to each sub-chain. Different chain orderings affect the placement by changing the relative sizes of the sub-chains and their routing contribution. We conclude with a detailed routing step and an optional compaction step.

Two roads diverged in a yellow wood,

And sorry I could not travel both

And be one traveler, long I stood

And looked down one as far as I could

To where it bent in the undergrowth;

Then took the other, as just as fair,

And having perhaps the better claim,

Because it was grassy and wanted wear;

Though as for that the passing there

Had worn them really about the same,

And both that morning equally lay

In leaves no step had trodden black.

Oh, I kept the first for another day!

Yet knowing how way leads on to way,

I doubted if I should ever come back.

I shall be telling this with a sigh

Somewhere ages and ages hence:

Two roads diverged in a wood, and I—

I took the one less traveled by,

And that has made all the difference.

The Road Not Taken, Robert Frost (1874–1963)

© Michael Anthony Riepe 1999

All Rights Reserved

In memory of my father

### **ACKNOWLEDGMENTS**

This dissertation represents the end of a long and winding road which I have followed here at the University of Michigan, and I did my best to explore every fork. I will always be indebted to my advisor, Karem Sakallah, for his patient support. He always let me follow my own course, but his well timed advice never failed to prove its value. Karem always treated me as a colleague and a friend, and I expect our relationship to continue and grow after I leave his immediate care.

I am also grateful to the remaining members of my committee, John Hayes and Marios Papaefthymiou of the Advanced Computer Architecture Lab, Richard Brown from the Solid State Electronics Lab, and Rob Rutenbar from Carnegie Mellon University. My association with John and Marios through the weekly CAD reading group contributed immensely to my enjoyment of this field. In my second life as a member of the GaAs MIPS and PUMA research groups I have built a tremendous variety of skills in the field of VLSI circuits, and my involvement with these projects provided the inspiration for the ideas that culminated in this work. I can thank Rich for keeping my electrical engineering skills intact while I was forced to program computers, and for providing a tremendously stimulating environment in which to explore new ideas. I owe a special thanks to Rob for his generous collaboration, as a great deal of this work grew from the ground-breaking research of his past and present students at Carnegie Mellon.

My stay at Michigan would have been far less interesting in the absence of the vigorous intellectual environment provided by my friends and fellow students in ACAL. I wish to thank Dave Nagel, Mike Upton, Tom Huff, Ajay Chandna, and P.J. Shearhart of the GaAs MIPS project for showing me that it is possible to graduate and move on. I will also never forget Tim Stanley, a close friend whose time with us was far too short. The past and present students of Karem's CAD group deserve special mention. These include Tim Burks, Matthew Jones, João Paulo Marques De Silva, Jeff Bell, Victor Kravets, Jesse Whittemore, Joon #1 and Joon #2, and honorary members David van Campenhout, Phiroze Parakh, and Juan Antonio Carballo. As vice president and only other member of the physical CAD research cabal (until the arrival of Joon #2, I guess he can be secretary) Phiroze receives a special medal of honor. We spent many evenings at the whiteboard

discussing our problems and he is responsible for more of this work than I care to admit.

Somehow I managed to gather together many friends outside of the engineering department. I do not want to leave anybody out, so I will mention nobody by name. You all know who you are. I thank you for helping to keep me sane and for always providing a source of diversion when the weather was good. Come to think of it, the weather didn't have to be all that good! On second thought I will make an exception and mention one name. After all, Omar did mention me in his acknowledgments. As a result, everyone in the field of solid state optics now knows that I broke Omar's collar bone.

Finally I have to thank my family for their love and constant support. To my parents, I guess maybe you raised me right after all, I know how proud you must be.

#### **PREFACE**

In this dissertation we define a number of special terms for concepts which are especially critical to understanding. For clarity, and to allow the reader to locate these definitions when needed, we will call out these terms in **bold** the first time that they are used. We will also call them out in places where their meaning may be clarified through example or further explanation. When we wish to emphasize a point we may call a word or phrase out in *italics*.

When describing computational algorithms we make use of a functional pseudo-code format adapted from the book "Introduction to Algorithms" by Cormen, Leiserson & Rivest [20]. We wish to minimize any similarity to a particular computer language, and our philosophy was to limit the number of semantic-free symbols to an absolute minimum as well. An example of a short algorithm (Kruskal's Minimum Spanning Tree algorithm) is given below:

```

MST-KRUSKAL (G, w)

1

A \leftarrow \emptyset

2

for each vertex v \in V[G]

3

MAKE-SET(v)

sort the edges of E by non-decreasing weight w

4

5

for each edge (u, v) \in E, in order

6

if FIND-SET(u) \neq FIND-SET(v)

7

A \leftarrow A \cup \{(u, v)\}

8

UNION(u, v)

9

return A

```

This pseudo-code adopts the following conventions.

- 1. Algorithms are written in the proportional Courier font to resemble computer printouts. Variables, for example A above, are marked in italics. Reserved words such as if and for are marked in bold. Function names are specified in all capital letters. Detailed algorithm steps which are more clearly written in proper English sentence form, for example line #4 above, are written in ordinary un-formatted text.

- 2. We distinguish the assignment operator from the equality operator by using two

- different symbols. The equal sign "=" is used to indicate an equality comparison while the left-arrow symbol " $\leftarrow$ " is used to indicate assignment. We freely make use of standard mathematical operators such as the set membership operator  $a \in b$ .

- 3. We eliminate superfluous parentheses whenever possible. They are only used to indicate cases of ambiguous operator precedence and to mark the operands of function calls and function definitions.

- 4. Indentation is used to indicate block structure. We eliminate all semantic-free symbols such as "begin" and "end" block delimiters and "do" statements in for and while loops.

- 5. Variables are all assumed to be local to a given procedure. We do not show the definition or initialization of variables unless necessary. The type of a variable is assumed to be correct for its use and can be derived from context. By default ordinary variables are assumed to be initialized to a zero or null value. Data structures such as the set v above are assumed to be empty when initialized. Input parameters to functions are assumed to be passed by value.

- 6. The elements of array variables are accessed with the use of the post-fix square bracket operator "[]". Arrays are assumed to have been initialized with adequate space to hold any objects assigned to them.

- 7. For brevity we often make use of standard functions, such as the set functions MAKE-SET(), FIND-SET() and UNION() above, without defining them. They should be assumed to perform the expected actions without any side effects. If there is some ambiguity in the meaning of the name we will describe the action of the function in explanatory body text which accompanies each algorithm.

### TABLE OF CONTENTS

| DEDICATION                                                       |

|------------------------------------------------------------------|

| ACKNOWLEDGMENTSiii                                               |

| PREFACEv                                                         |

| TABLE OF CONTENTSvii                                             |

| LIST OF FIGURESx                                                 |

|                                                                  |

| LIST OF TABLESxv                                                 |

| LIST OF APPENDICESxv                                             |

| CHAPTER 1 Introduction                                           |

| 1.1 Motivation                                                   |

| 1.2 Problem Definition and Previous Work                         |

| 1.2.1 One-Dimensional Cell Synthesis                             |

| 1.2.2 One and One-Half Dimensional Cell Synthesis                |

| 1.2.3 Two-Dimensional Cell Synthesis                             |

| 1.3 Proposed Methodology                                         |

| 1.3.1 Static Transistor Clustering                               |

| 1.3.2 Transistor Placement                                       |

| 1.3.3 Cell Routing                                               |

| 1.3.4 Cell Compaction                                            |

| 1.4 Contribution                                                 |

| 1.5 Summary                                                      |

| 1.6 Dissertation Outline                                         |

| CHAPTER 2 Placement Modeling Issues                              |

| 2.1 Introduction                                                 |

| 2.2 Direct Versus Indirect Placement                             |

| 2.3 Indirect Placement: The Slicing Tree                         |

| 2.4 Indirect Placement: Two-Dimensional Compaction Constraints32 |

| 2.4.1 Configuration and Orientation Selection                    |

| 2.4.2 Relative Object Placement                                  |

| 2.4.3 The Pairwise Relative Placement Problem                    |

| 2.4.4 Solving the Compaction Constraint Graphs                   |

| 2.4.5 Constraint Graph Cycles and Infeasibility40                |

| 2.4.6 The Cost function                                          |

| 2.5 Summary                                                      |

| CHAPTER 3 Placement Using the Sequence Pair Representation 49    |

| 3.1 The Sequence Pair Representation                          | 49  |

|---------------------------------------------------------------|-----|

| 3.2 Solving the Sequence Pair Constraint Graphs               | 54  |

| 3.2.1 Single Source Longest Path in Directed Acyclic Graphs   | 54  |

| 3.2.2 Single Source Longest Path with Incremental DAG Updates |     |

| 3.3 Optimization Formulations                                 | 67  |

| 3.3.1 ILP Optimization                                        | 67  |

| 3.3.2 Branch-and-Bound Optimization                           | 72  |

| 3.3.3 Simulated Annealing Optimization                        | 77  |

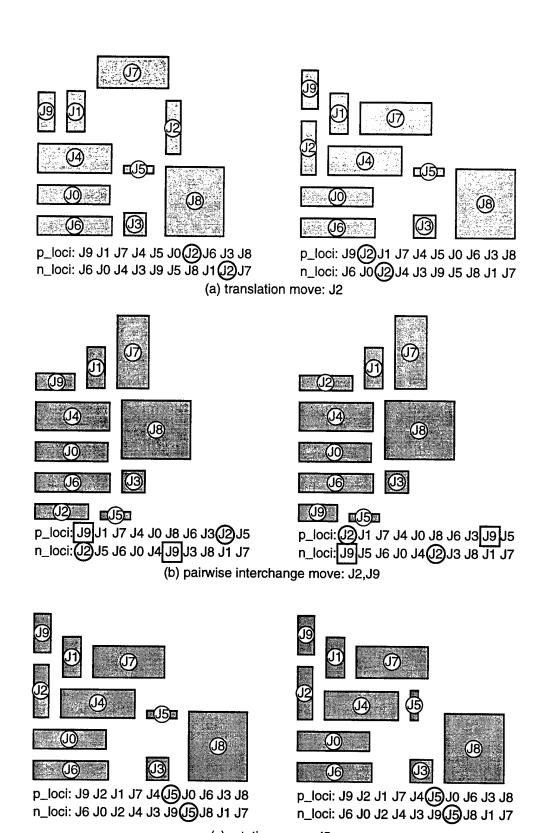

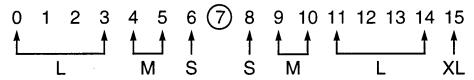

| 3.3.3.1 Solution Space Modeling and the Move Set              | 79  |

| 3.3.3.2 Cost Function                                         | 81  |

| 3.3.3.3 Annealing Control                                     | 83  |

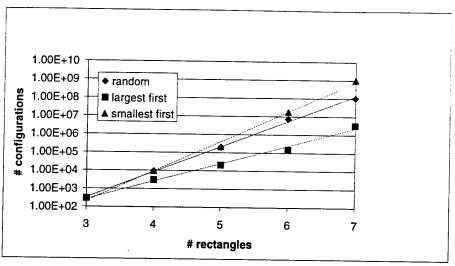

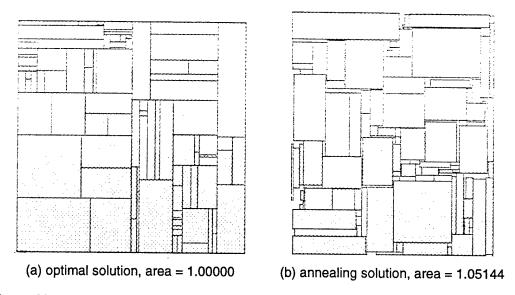

| 3.4 Experimental Evaluation                                   |     |

| 3.4.1 Branch and Bound Algorithm Experiments                  | 91  |

| 3.4.2 Simulated Annealing Algorithm Experiments               | 93  |

| 3.5 Summary                                                   |     |

| CHAPTER 4 Transistor Level Micro-Placement and Routing        | 99  |

| 4.1 Methodology                                               | 99  |

| 4.2 Transistor Chaining                                       | 99  |

| 4.2.1 Overview                                                |     |

| 4.2.2 Terminology                                             |     |

| 4.2.3 Transistor Chain Width Minimization                     |     |

| 4.2.4 Transistor Chain Height Minimization                    |     |

| 4.2.5 Complications                                           |     |

| 4.2.6 Static vs. Dynamic Transistor Chain optimization        |     |

| 4.2.7 Transistor Chain Geometry Generator                     |     |

| 4.3 Transistor Clustering                                     |     |

| 4.4 Transistor Level Micro-Placement                          | 119 |

| 4.4.1 Modeling of the placement search space                  | 122 |

| 4.4.2 Support for Dynamic Transistor Chaining                 |     |

| 4.4.3 Support for Arbitrary Geometry Sharing                  | 127 |

| 4.4.4 Cell Template                                           | 128 |

| 4.4.5 The Placement Cost Function                             | 130 |

| 4.4.6 Routing Model                                           |     |

| 4.4.6.1 Routing Length Estimation                             |     |

| 4.4.6.2 Routing Area Insertion                                |     |

| 4.5 Routing                                                   |     |

| 4.6 Compaction                                                |     |

| 4.7 Summary                                                   |     |

| CHAPTER 5 Experimental Evaluation                             | 143 |

| 5.1 Implementation                                            | 143 |

|                                                               |     |

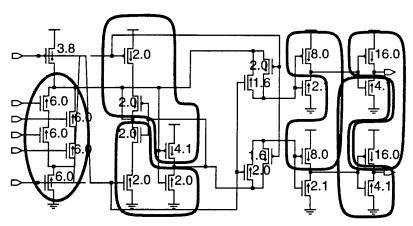

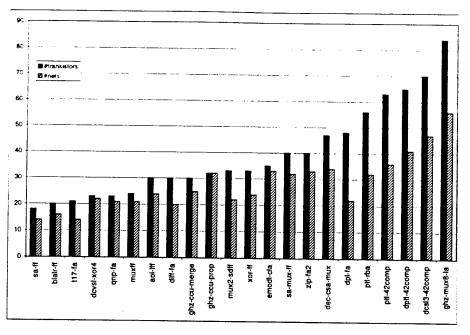

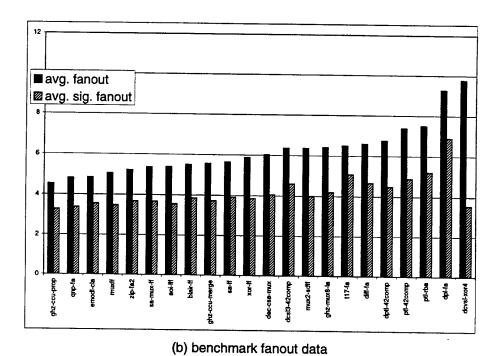

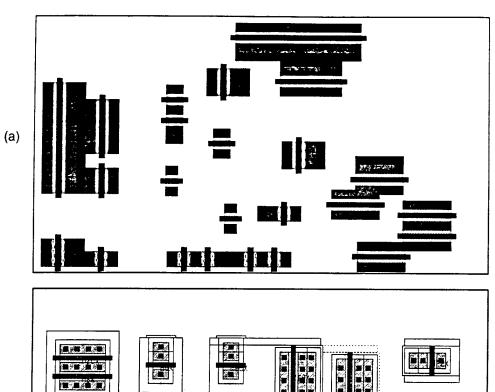

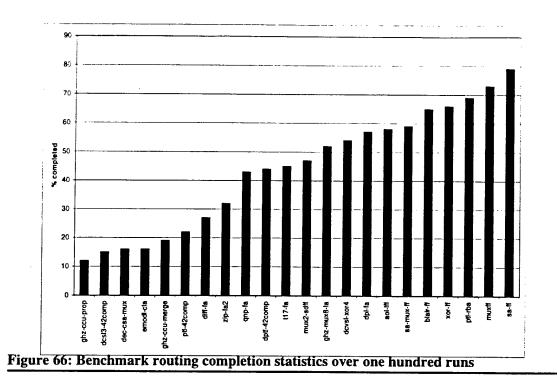

| 5.2 Benchmark Circuits                                 | 144 |

|--------------------------------------------------------|-----|

| 5.3 Experimental Results                               | 148 |

| 5.4 Summary                                            | 161 |

| CHAPTER 6 Conclusions and Future Work                  |     |

| 6.1 Summary                                            | 163 |

| 6.2 Contributions                                      | 166 |

| 6.3 Future Work                                        | 169 |

| 6.4 Conclusions                                        |     |

| APPENDICES                                             | 176 |

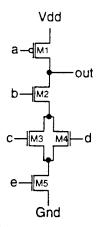

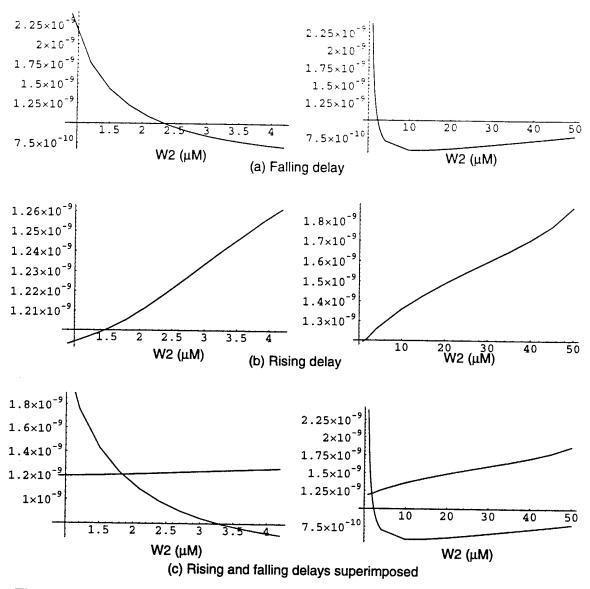

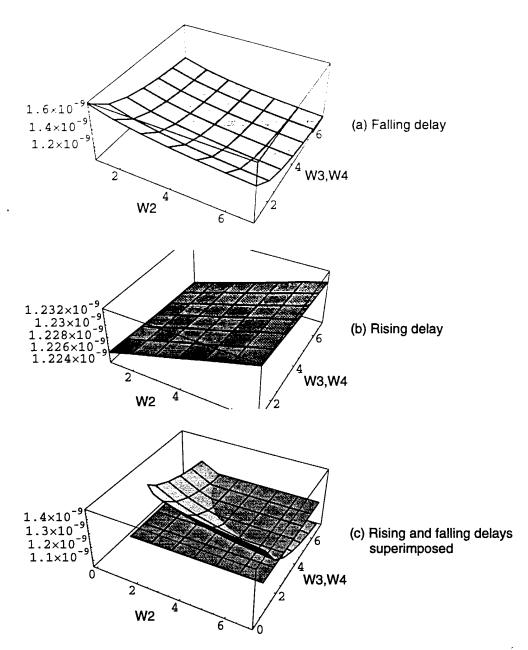

| APPENDIX A Transistor Sizing Methodology               | 177 |

| A.1 Introduction                                       | 177 |

| A.2 Previous Work                                      | 177 |

| A.3 The <i>Topt</i> Transistor Optimization Tool       | 180 |

| A.3.1 The <i>Topt</i> Input Specification              | 181 |

| A.3.2 The <i>Topt</i> Nonlinear Optimization Algorithm | 184 |

| APPENDIX B Experimental Data                           | 195 |

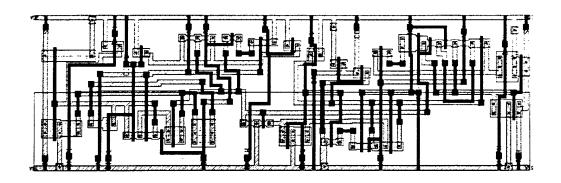

| APPENDIX C LAS Layouts                                 | 199 |

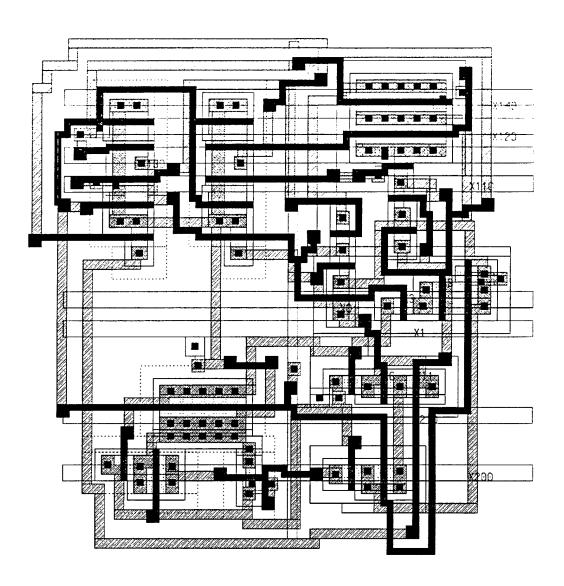

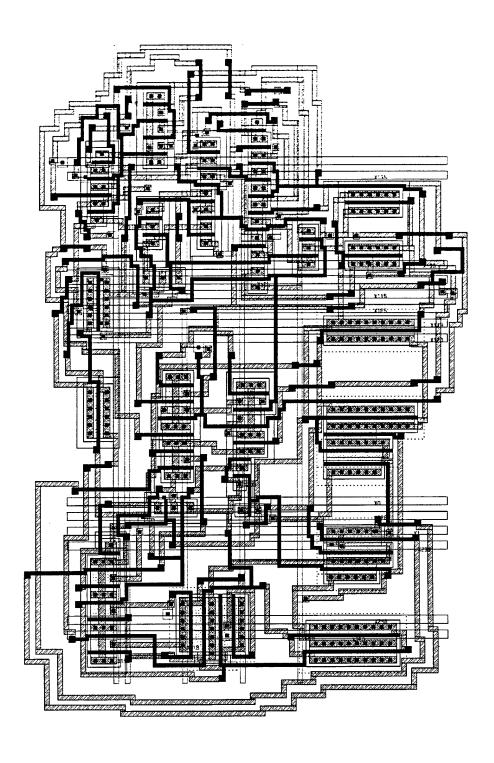

| APPENDIX D TEMPO Layouts (Pre-Compaction)              |     |

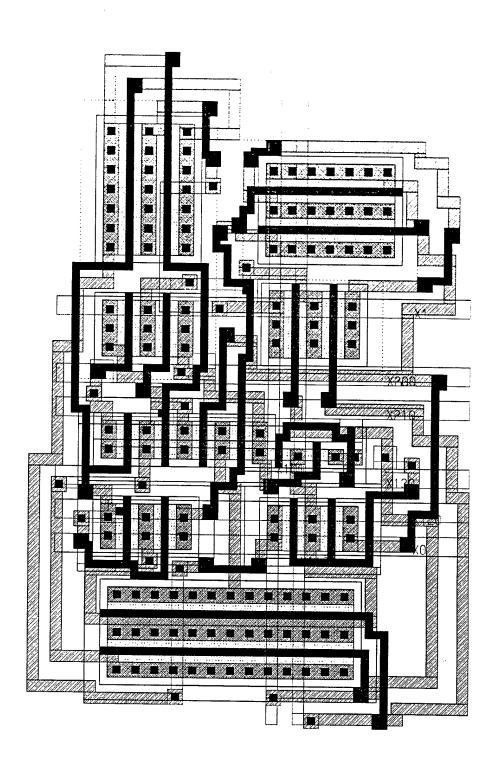

| APPENDIX E TEMPO Layouts (Post-Compaction)             |     |

| BIBLIOGRAPHY                                           | 268 |

### LIST OF FIGURES

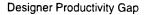

| Figure 1:  | A projection of the increasing gap between design complexity and designer productive ity                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

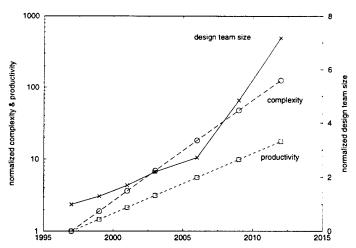

| Figure 2:  | An example of a cell designed in the "functional cell" style of Uehara and VanCleemput [119]                                                                        |

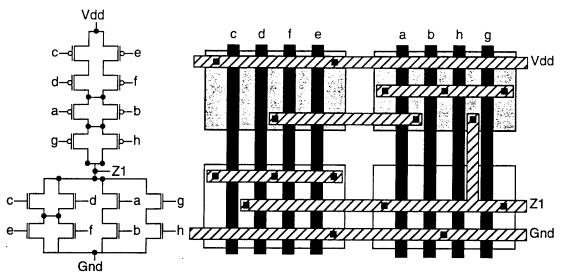

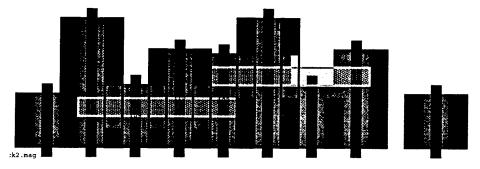

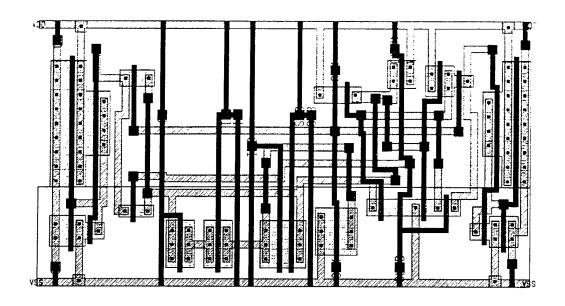

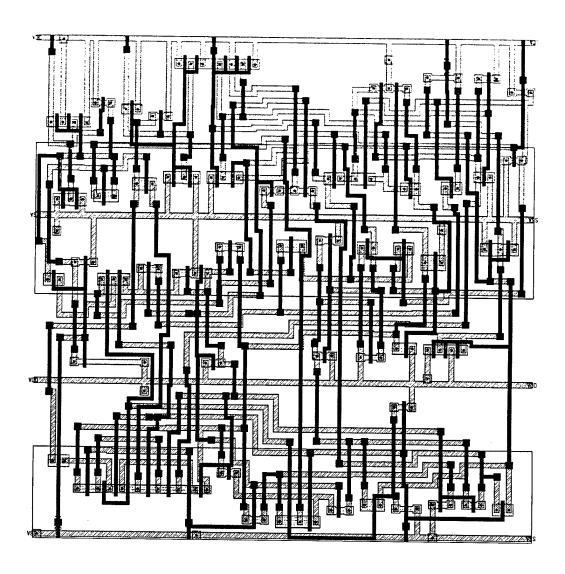

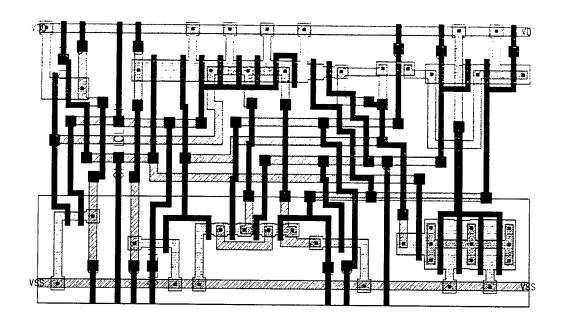

| Figure 3:  | A manually designed cell showing complex two-dimensional layout structure (not to scale.)                                                                           |

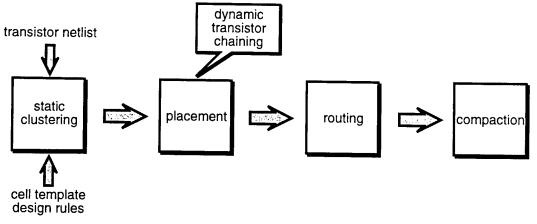

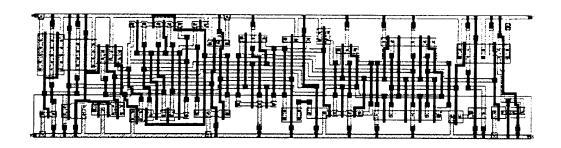

| Figure 4:  | Basic steps in the proposed cell synthesis flow                                                                                                                     |

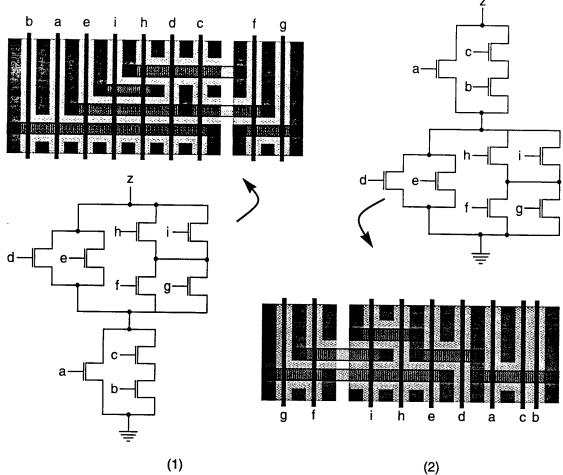

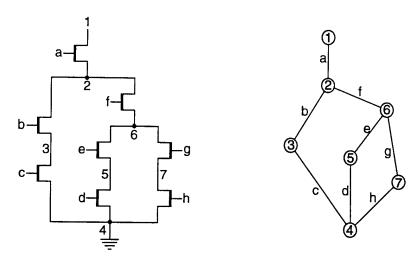

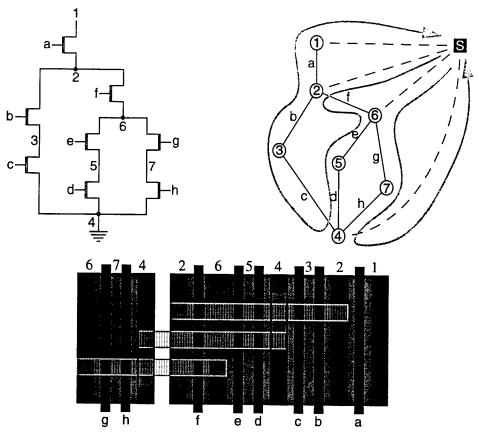

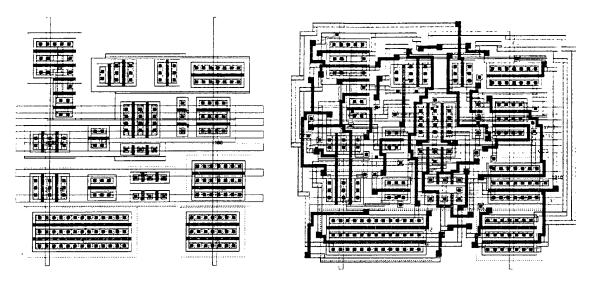

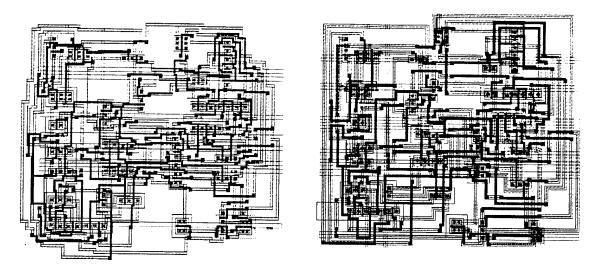

| Figure 5:  | Proposed methodology for two-dimensional cell synthesis                                                                                                             |

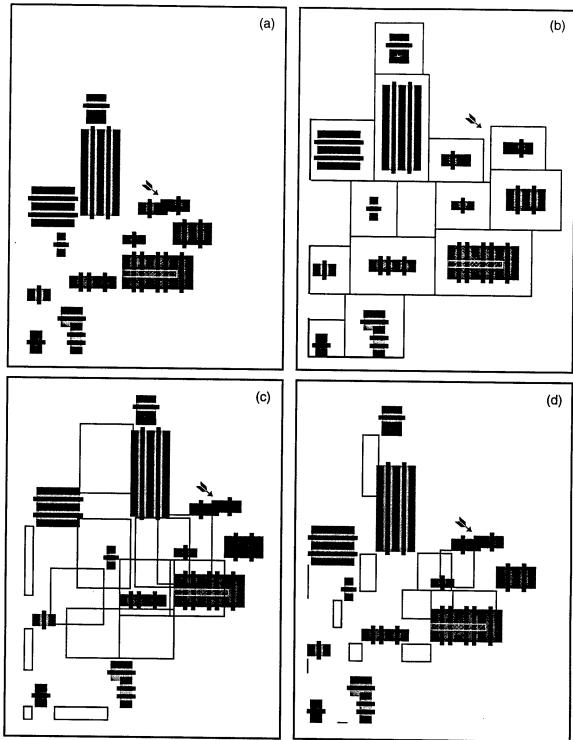

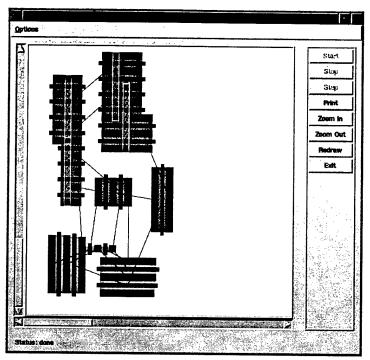

| Figure 6:  | A screen shot of the KOAN tool taken at an early stage of placement showing many object overlaps                                                                    |

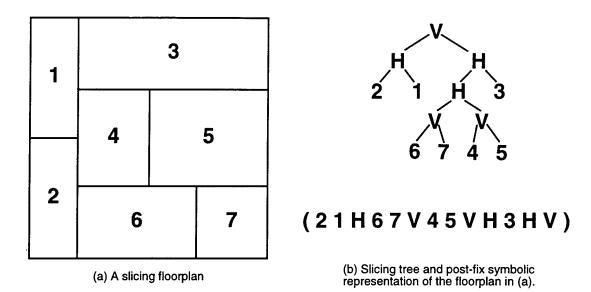

| Figure 7:  | Slicing floorplans                                                                                                                                                  |

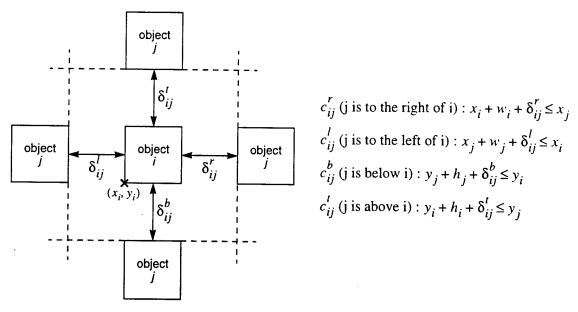

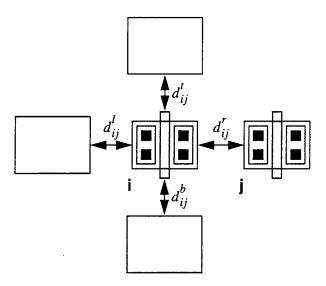

| Figure 8:  | The geometric "compaction" constraints generated between two objects i and j.32                                                                                     |

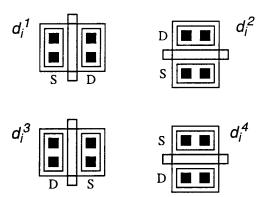

| Figure 9:  | The four possible orientations of a FET and the corresponding decision variable.33                                                                                  |

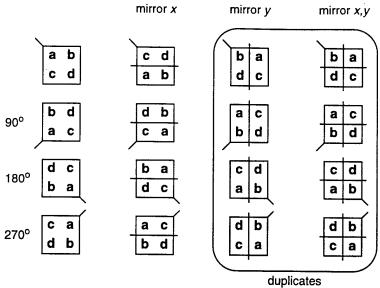

| Figure 10: | The possible orientations of an arbitrary block which can be obtained through mirroring and rotating. Eight of the sixteen resulting orientations are duplicates 34 |

| Figure 11: | The four possible relative placement of two FET objects i and j and the corresponding decision variable                                                             |

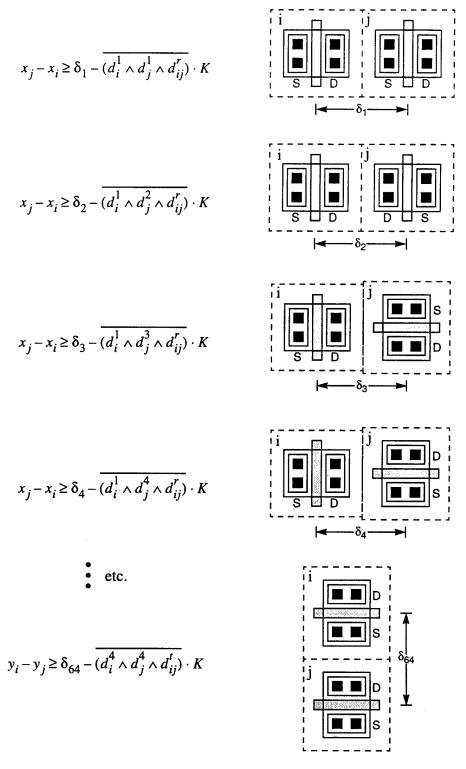

| Figure 12: | The 64 possible placements for a pair of CMOS transistors (right) and the corresponding design rule constraints (left). K is a suitably large number                |

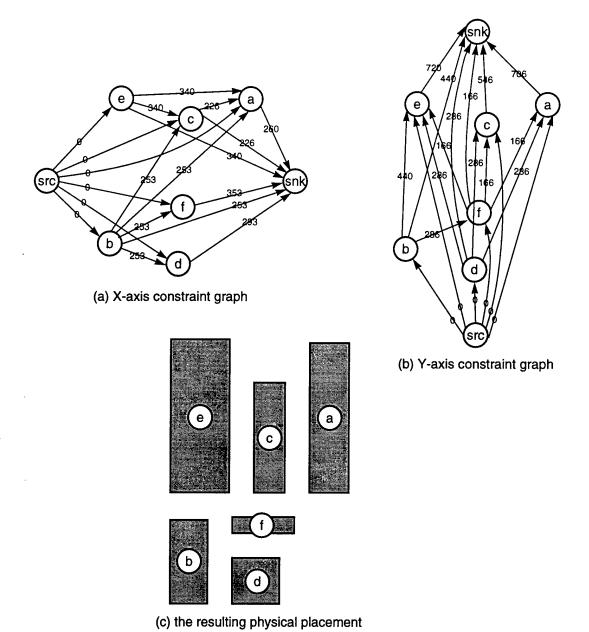

| Figure 13: | An example of two constraint graphs and their associated physical packing39                                                                                         |

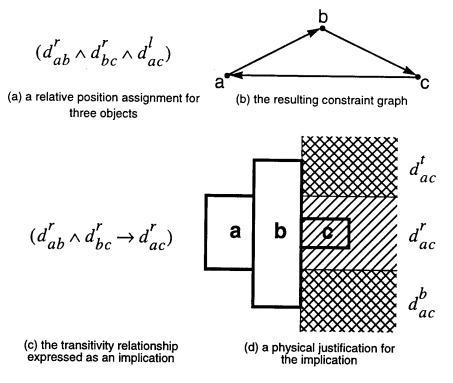

| Figure 14: | An example of the transitivity relationship between design rule constraints 40          |

|------------|-----------------------------------------------------------------------------------------|

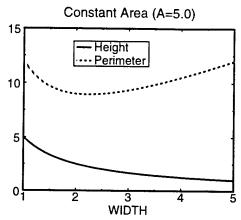

| Figure 15: | The cell height and perimeter as a function of its width for a constant area42          |

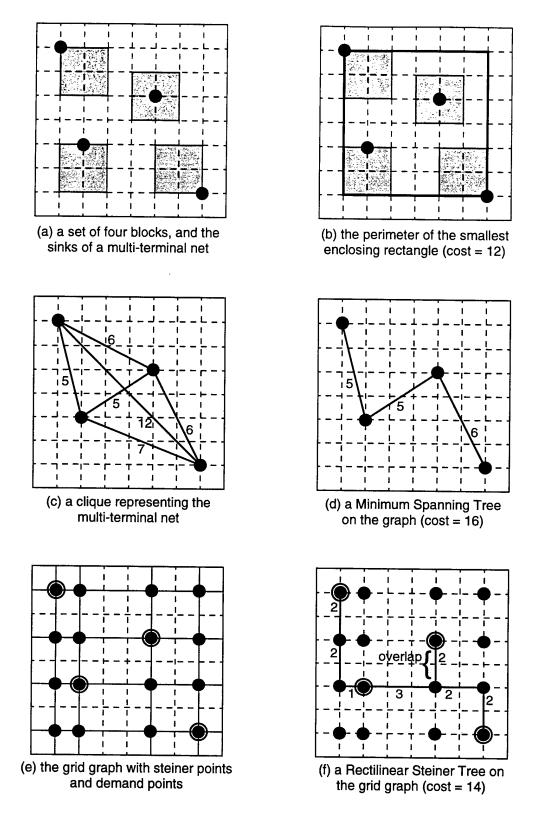

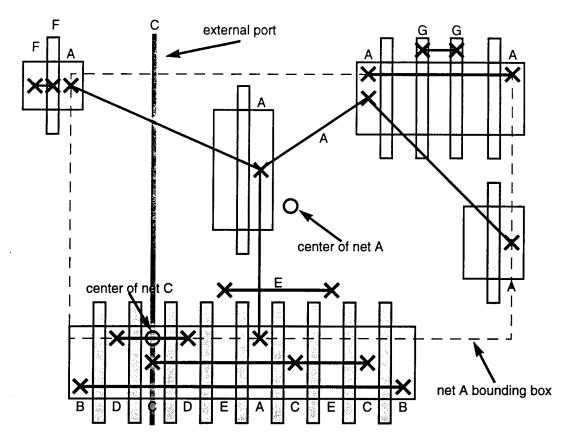

| Figure 16: | An example illustrating several different methods for routing cost estimation. 44       |

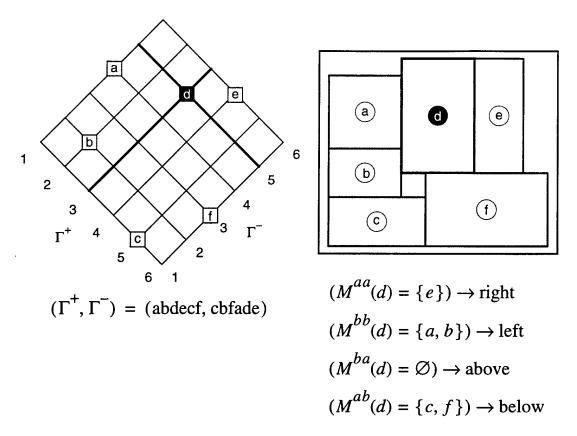

| Figure 17: | The symbolic sequence pair placement representation                                     |

| Figure 18: | The effect of a single nearest-neighbor pair swap in a sequence pair 53                 |

| Figure 19: | An example of incremental edge deletions from a DAG62                                   |

| Figure 20: | An example of incremental edge and vertex insertions in a DAG                           |

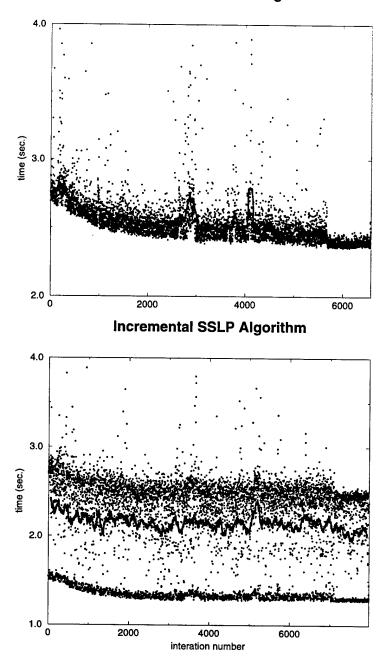

| Figure 21: | Constraint graph solution times for the incremental and non-incremental SSLP algorithms |

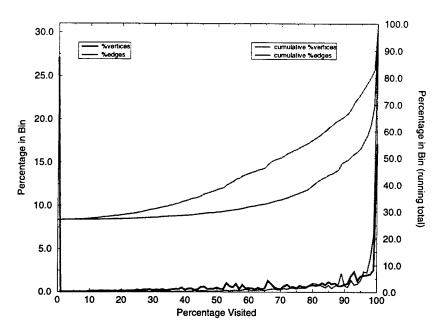

| Figure 22: | The percentage of edges and vertices reset by the incremental SSLP algorithm67          |

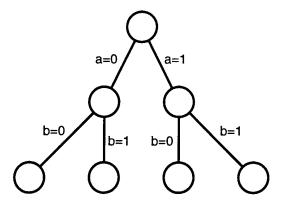

| Figure 23: | A branch-and-bound search tree                                                          |

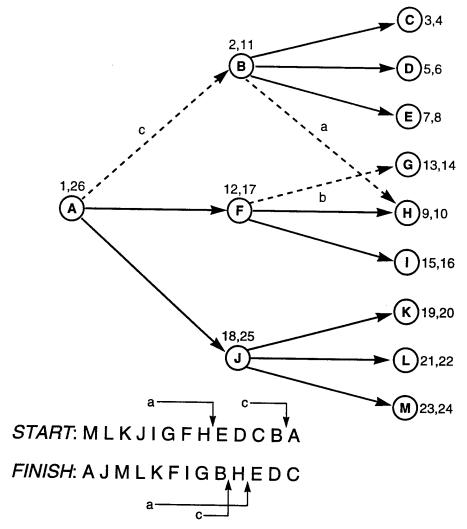

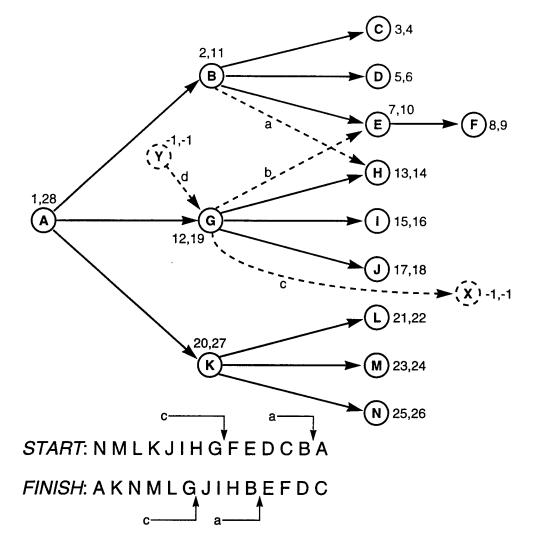

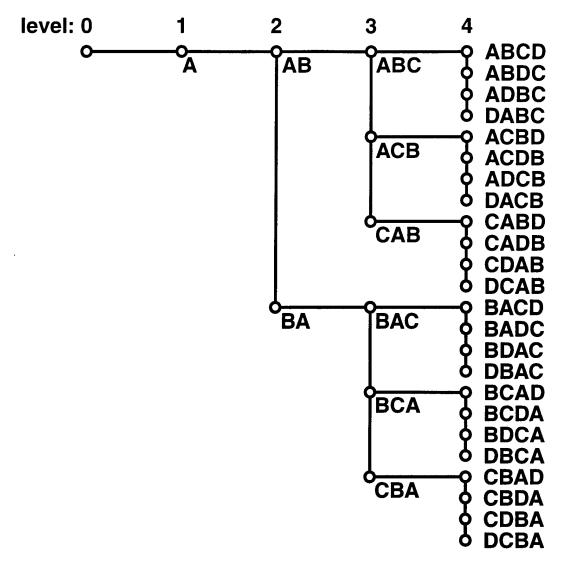

| Figure 24: | Branch-and-Bound permutation generation                                                 |

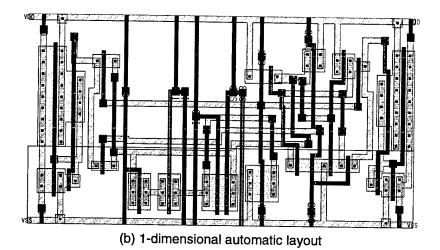

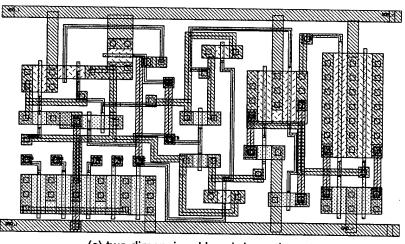

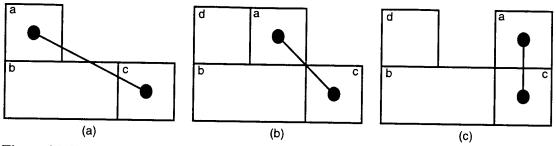

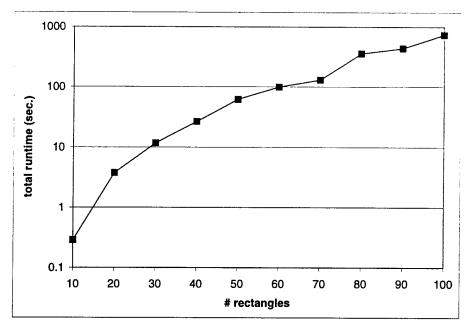

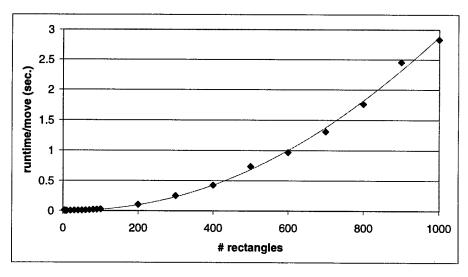

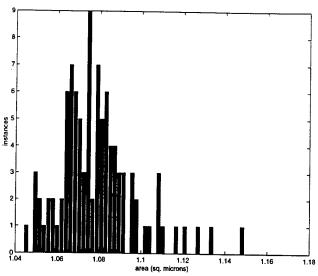

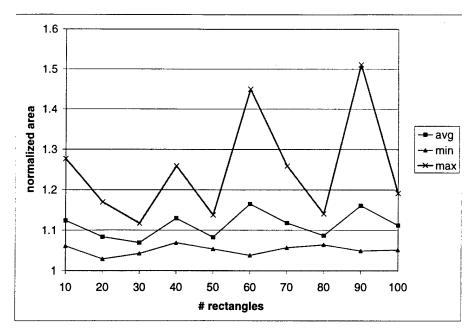

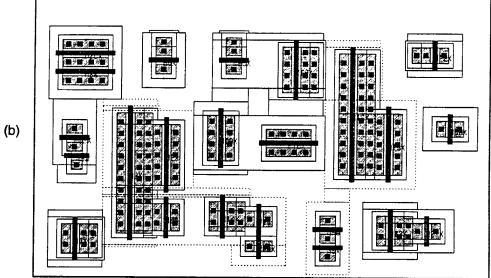

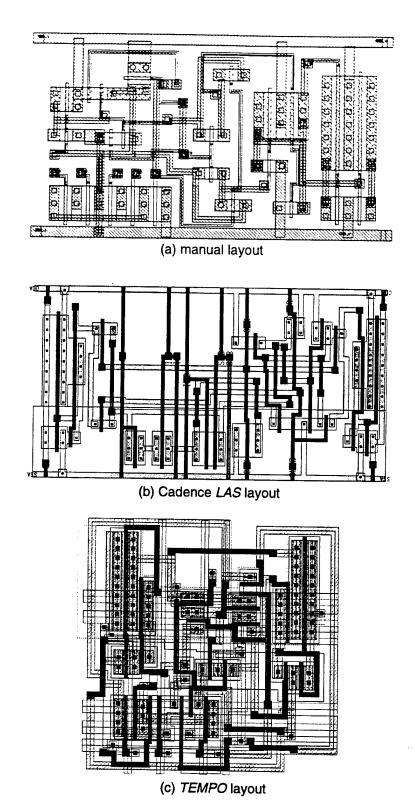

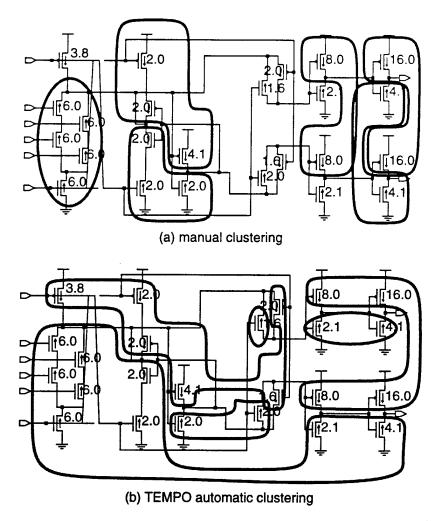

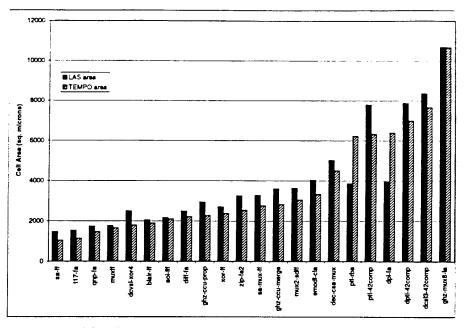

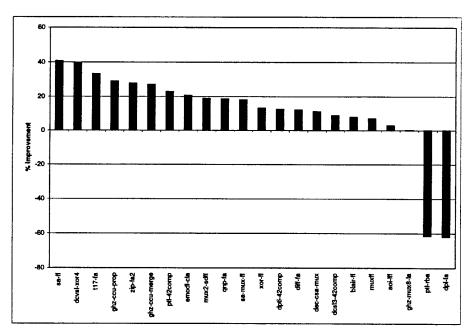

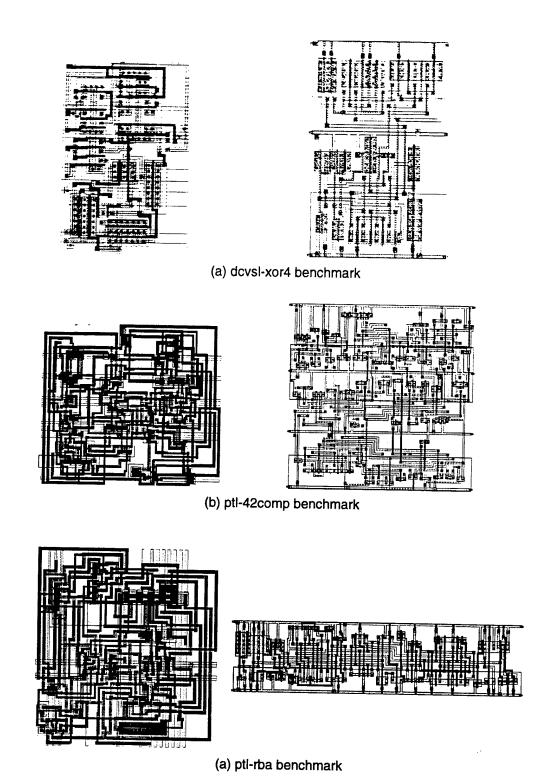

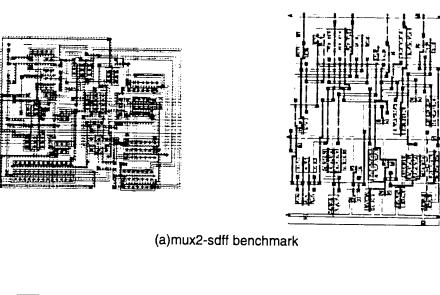

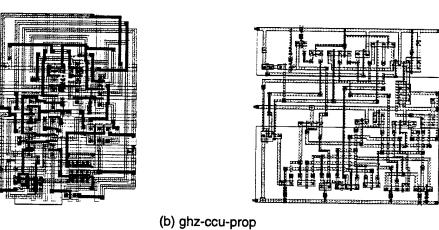

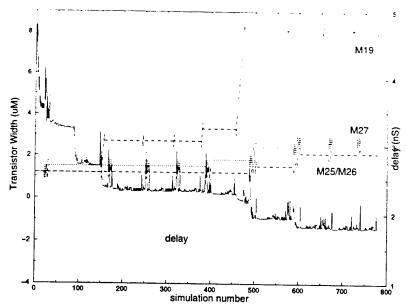

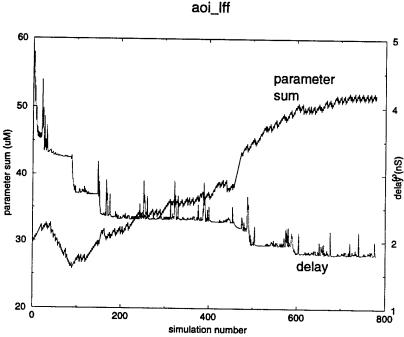

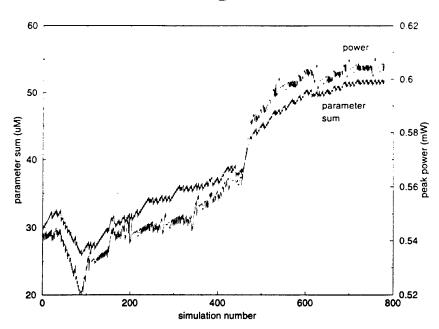

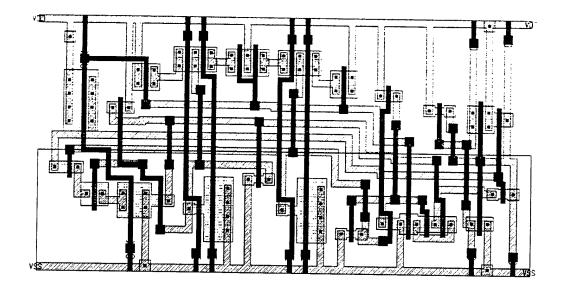

| Figure 25: | Example of routing effects in branch-and-bound placement                                |